# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 113641206 B (45) 授权公告日 2021. 12. 28

- (21) 申请号 202111201666.X

- (22)申请日 2021.10.15

- (65) 同一申请的已公布的文献号 申请公布号 CN 113641206 A

- (43) 申请公布日 2021.11.12

- (73) 专利权人 成都时识科技有限公司 地址 641400 四川省成都市高新区天府大 道1577号中国-欧洲中心18层 专利权人 上海时识科技有限公司

- (72) 发明人 乔宁 卜亮宇 周凯 常胜 白鑫 刘浩 代米尔吉•图芭 柯政 范健均 张林

- (74) 专利代理机构 深圳紫藤知识产权代理有限 公司 44570

代理人 汪阮磊

- (51) Int.CI. G05F 1/56 (2006.01)

- (56) 对比文件 CN 112039492 A,2020.12.04

- US 6104249 A,2000.08.15

- US 6084470 A,2000.07.04

- JP 2010226355 A,2010.10.07

- US 4687984 A,1987.08.18

- US 6433626 B1,2002.08.13

- CN 102880219 A,2013.01.16

- CN 112925378 A, 2021.06.08

- TW 201737011 A,2017.10.16

- US 5343164 A,1994.08.30

- US 5081423 A,1992.01.14

- US 5661432 A,1997.08.26

- CN 108462479 A, 2018.08.28

- CN 1196615 A,1998.10.21

- JP H03136409 A,1991.06.11

- CN 101777880 A,2010.07.14

- US 6643324 B1,2003.11.04

- US 5736899 A,1998.04.07

张晓洁. 跨导电容低通滤波器的研究与设 计.《中国优秀硕士学位论文全文数据库(信息 科技辑)》.2021,(第07期),第1135-169页.

## 审查员 肖琛

权利要求书3页 说明书8页 附图7页

#### (54) 发明名称

配置滤波功能的集成电路

#### (57) 摘要

本发明涉及一种配置滤波功能的集成电路。 为解决现有技术中线性度不足、谐波抑制较差的 技术问题,本发明中的配置滤波功能的集成电路 包括:第一电路部,电性连接第一输入电流源及 第二输入电流源,所述第一电路部用于接收第一 差分输入信号;及第二电路部,电性连接第三输 入电流源、第四输入电流源以及第五输入电流 m 源,所述第二电路部用于接收第二差分输入信 号。所述第五输入电流源的电流大小符合以下公 式:所述第五输入电流源的电流等于所述第一输 入电流源的电流与所述第二输入电流源的电流 云 差值的两倍。本发明可以提高配置滤波功能的集 成电路的线性度,谐波抑制效果显著提升,并以

较低的功耗和面积实现了稳定输出共模的效果。

100

1.一种配置滤波功能的集成电路,其特征在于,包括:第一电路部、第二电路部、第一输入电流源、第二输入电流源、第三输入电流源、第四输入电流源和第五输入电流源,其中:

第一电路部,包括第一输入端、第二输入端、第一输出端和第二输出端,其中,第一输入端用于接收第一差分输入信号,第二输入端用于接收第一输入电流源输入的第一电流,第一输出端用于输出第二电流至第二输入电流源;

第二电路部,包括第三输入端、第四输入端、第三输出端和第四输出端,其中,第三输入端用于接收第二差分输入信号,第四输入端用于接收第三输入电流源输入的第三电流,第三输出端用于输出第四电流至第四输入电流源;

第五输入电流源,电连接第一电路部的第二输出端和第二电路部的第四输出端;其中 所述第五输入电流源的电流大小符合以下公式:

所述第五输入电流源的电流=(所述第一输入电流源的电流-所述第二输入电流源的 电流)+(所述第三输入电流源的电流-所述第四输入电流源的电流);

其中,所述第一电路部包括:

第一晶体管,包括通过第一电容接收所述第一差分输入信号的第一晶体管控制极,和 电性连接所述第一输入电流源的第一电极,及电性连接所述第二输入电流源的第二电极, 其中所述第一晶体管的第二电极通过第二电容接地;以及

第二晶体管,包括与所述第一晶体管的第二电极电性连接的第二晶体管控制极,与所述第一晶体管的第一电极电性连接的第三电极;以及

所述第二电路部,包括:

第三晶体管,包括通过第三电容接收第二差分输入信号的第三晶体管控制极,和电性连接第三输入电流源的第五电极,及电性连接第四输入电流源的第六电极,其中所述第三晶体管的第六电极通过第四电容接地,所述第三晶体管的第五电极通过第五电容与所述第一晶体管的第一电极电性连接;以及

第四晶体管,包括与所述第三晶体管的第六电极电性连接的第四晶体管控制极,和与所述第三晶体管的第五电极电性连接的第七电极,及与所述第二晶体管的第四电极电性连接的第八电极;

其中所述第二晶体管的第四电极与所述第四晶体管的第八电极电性连接第五输入电流源。

2. 如权利要求1所述的配置滤波功能的集成电路,其特征在于,

所述第一输入电流源的电流与所述第三输入电流源的电流大小相等,所述第二输入电流源的电流与所述第四输入电流源的电流大小相等,所述第五输入电流源的电流= (所述第一输入电流源的电流-所述第二输入电流源的电流)×2。

3. 如权利要求1所述的配置滤波功能的集成电路,其特征在于,所述集成电路还包括:

偏置晶体管,所述偏置晶体管的控制极用以与所述第一晶体管控制极和所述第三晶体管控制极电性连接,偏置晶体管的第九电极电性连接第六输入电流源,偏置晶体管的第十电极电性连接第七输入电流源,其中所述偏置晶体管的控制极与所述偏置晶体管的第十电极电性连接。

4.如权利要求3所述的配置滤波功能的集成电路,其特征在于,所述集成电路还包括:第一电阻,其中所述偏置晶体管的控制极通过所述第一电阻与所述第一晶体管控制极

电性连接:以及

第二电阻,其中所述偏置晶体管的控制极通过所述第二电阻与所述第三晶体管控制极电性连接。

- 5.如权利要求1-4任意一项所述的配置滤波功能的集成电路,其特征在于,所述第一电容与所述第三电容大小相等,所述第二电容与所述第四电容大小相等。

- 6.如权利要求1-4任意一项所述的配置滤波功能的集成电路,其特征在于,所述第一晶体管为P型晶体管,所述第二晶体管为N型晶体管;

或者,所述第一晶体管为N型晶体管,所述第二晶体管为P型晶体管。

7.如权利要求6所述的配置滤波功能的集成电路,其特征在于,当所述第一晶体管为P型晶体管且所述第二晶体管为N型晶体管时,所述第三晶体管为P型晶体管且所述第四晶体管为N型晶体管:

或者,当所述第一晶体管为N型晶体管且所述第二晶体管为P型晶体管时,所述第三晶体管为N型晶体管且所述第四晶体管为P型晶体管。

- 8. 如权利要求1-4任意一项所述的配置滤波功能的集成电路,其特征在于,所述第一晶体管与所述第三晶体管具有相同的尺寸,所述第二晶体管与所述第四晶体管具有相同的尺寸。

- 9.一种配置滤波功能的集成电路,其特征在于,包括:第一电路部、第二电路部、第一输入电流源、第二输入电流源、第三输入电流源、第四输入电流源和第五输入电流源,其中:

第一电路部,包括第一输入端、第二输入端、第一输出端和第二输出端,其中,第一输入端用于接收第一差分输入信号,第二输入端用于接收第一输入电流源输入的第一电流,第一输出端用于输出第二电流至第二输入电流源;

第二电路部,包括第三输入端、第四输入端、第三输出端和第四输出端,其中,第三输入端用于接收第二差分输入信号,第四输入端用于接收第三输入电流源输入的第三电流,第三输出端用于输出第四电流至第四输入电流源;

第五输入电流源,电连接第一电路部的第二输出端和第二电路部的第四输出端;共模晶体管,电性连接匹配输入电流源和所述第五输入电流源,所述共模晶体管用以接收共模信号,其中所述匹配输入电流源的电流大小符合以下公式:

所述匹配输入电流源的电流=所述第五输入电流源的电流-((所述第一输入电流源的电流-所述第二输入电流源的电流)+(所述第三输入电流源的电流-所述第四输入电流源的电流);

其中,

所述第一电路部包括:

第一晶体管,包括通过第一电容接收所述第一差分输入信号的第一晶体管控制极,和电性连接所述第一输入电流源的第一电极,和电性连接所述第二输入电流源的第二电极,其中所述第一晶体管的第二电极通过第二电容接地;以及第二晶体管,包括与所述第一晶体管的第二电极电性连接的第二晶体管控制极,和所述第一晶体管的第一电极电性连接的第三电极;

所述第二电路部包括:

第三晶体管,包括通过第三电容接收所述第二差分输入信号的第三晶体管控制极,和

电性连接所述第三输入电流源的第五电极,和电性连接所述第四输入电流源的第六电极, 其中所述第三晶体管的第六电极通过第四电容接地,所述第三晶体管的第五电极通过第五 电容与所述第一晶体管的第一电极电性连接;

第四晶体管,包括与所述第三晶体管的第六电极电性连接的第四晶体管控制极,和与所述第三晶体管的第五电极电性连接的第七电极,和与所述第二晶体管的第四电极电性连接的第八电极,其中所述第二晶体管的第四电极与所述第四晶体管的第八电极电性连接第五输入电流源;以及

所述共模晶体管包括用以接收所述共模信号的共模晶体管控制极,和电性连接所述匹配输入电流源的第十一电极,和电性连接所述第五输入电流源的第十二电极。

- 10. 如权利要求9所述的配置滤波功能的集成电路,其特征在于,所述第一输入电流源的电流与所述第三输入电流源的电流大小相等,所述第二输入电流源的电流与所述第四输入电流源的电流大小相等,所述匹配输入电流源的电流=所述第五输入电流源的电流—(所述第一输入电流源的电流—所述第二输入电流源的电流)×2。

- 11. 如权利要求10所述的配置滤波功能的集成电路,其特征在于,所述集成电路包括:

偏置晶体管,所述偏置晶体管的控制极用以与所述第一晶体管控制极和所述第三晶体管控制极电性连接,偏置晶体管的第九电极电性连接第六输入电流源,偏置晶体管的第十电极电性连接第七输入电流源,其中所述偏置晶体管的控制极与所述偏置晶体管的第十电极电性连接。

- 12.如权利要求11所述的配置滤波功能的集成电路,其特征在于,所述集成电路还包括:

- 第一电阻,其中所述偏置晶体管的控制极通过所述第一电阻与所述第一晶体管控制极电性连接;以及

- 第二电阻,其中所述偏置晶体管的控制极通过所述第二电阻与所述第三晶体管控制极电性连接。

- 13.如权利要求9-12任意一项所述的配置滤波功能的集成电路,其特征在于,所述第一电容与所述第三电容大小相等,所述第二电容与所述第四电容大小相等。

- 14. 如权利要求9-12任意一项所述的配置滤波功能的集成电路,其特征在于,所述第一晶体管为P型晶体管,所述第二晶体管和所述共模晶体管为N型晶体管;

- 或者,所述第一晶体管为N型晶体管,所述第二晶体管为P型晶体管。

- 15.如权利要求14所述的配置滤波功能的集成电路,其特征在于,当所述第一晶体管为P型晶体管、所述第二晶体管为N型晶体管时,所述第三晶体管为P型晶体管、所述第四晶体管为N型晶体管;

- 或者,当所述第一晶体管为N型晶体管且所述第二晶体管为P型晶体管时,所述第三晶体管为N型晶体管且所述第四晶体管为P型晶体管。

- 16. 如权利要求9-12任意一项所述的配置滤波功能的集成电路,其特征在于,所述第一晶体管与所述第三晶体管具有相同的尺寸,所述第二晶体管与所述第四晶体管具有相同的尺寸。

# 配置滤波功能的集成电路

#### 技术领域

[0001] 本发明涉及一种配置滤波功能的集成电路,并具体涉及一种具备高线性度的带通滤波器。

## 背景技术

[0002] 随着电子技术的发展,集成电路的需求与应用也越来越广泛。其中带通滤波器通常是电能质量管理中的重要部件,因此,带通滤波器的形式不断演进以符合产业需求。而传统上,基于运算放大器的有源电阻电容式带通滤波器通常具有较高功耗和较大面积的缺点。此外,习知的有源跨导电容式带通滤波器虽在某种程度上解决了有源电阻电容式带通滤波器的前述缺陷,然以往的有源跨导电容式带通滤波器在其运行上的线性度仍存在一定程度的不足。鉴于以往有源跨导电容式带通滤波器在实际应用上仍备受限制,有其必要发展更新型的带通滤波器。

## 发明内容

[0003] 有鉴于此,本发明的目的是提供一种具备高线性度的配置滤波功能的集成电路,以解决现有技术的问题。具体为:

[0004] 一种配置滤波功能的集成电路,包括:

[0005] 第一电路部、第二电路部、第一输入电流源、第二输入电流源、第三输入电流源、第四输入电流源和第五输入电流源,其中:

[0006] 第一电路部,包括第一输入端、第二输入端、第一输出端和第二输出端,其中,第一输入端用于接收第一差分输入信号,第二输入端用于接收第一输入电流源输入的第一电流,第一输出端用于输出第二电流至第二输入电流源;

[0007] 第二电路部,包括第三输入端、第四输入端、第三输出端和第四输出端,其中,第三输入端用于接收第三差分输入信号,第四输入端用于接收第三输入电流源输入的第三电流,第三输出端用于输出第四电流至第四输入电流源;

[0008] 第五输入电流源,电连接第一电路部的第二输出端和第二电路部的第四输出端; 其中所述第五输入电流源的电流大小符合以下公式:

[0009] 所述第五输入电流源的电流=(所述第一输入电流源的电流-所述第二输入电流源的电流)+(所述第三输入电流源的电流-所述第四输入电流源的电流)。

[0010] 在某类实施例中,所述第一电路部包括:第一晶体管,包括通过第一电容接收所述第一差分输入信号的控制极,和电性连接所述第一输入电流源的第一电极,及电性连接所述第二输入电流源的第二电极,其中所述第一晶体管的第二电极通过第二电容接地;及第二晶体管,包括与所述第一晶体管的第二电极电性连接的控制极,与所述第一晶体管的第一电极电性连接的第三电极;及所述第二电路部,包括:第三晶体管,包括通过第三电容接收第二差分输入信号的控制极,和电性连接第三输入电流源的第五电极,及电性连接第四输入电流源的第六电极,其中所述第三晶体管的第六电极通过第四电容接地,所述第三晶

体管的第五电极通过第五电容与所述第一晶体管的第一电极电性连接;及第四晶体管,包括与所述第三晶体管的第六电极电性连接的控制极,和与所述第三晶体管的第五电极电性连接的第七电极,及与所述第二晶体管的第四电极电性连接的第八电极;其中所述第二晶体管的第四电极与所述第四晶体管的第八电极电性连接第五输入电流源。

[0011] 在某类实施例中,所述第一输入电流源的电流与所述第三输入电流源的电流大小相等,所述第二输入电流源的电流与所述第四输入电流源的电流大小相等,所述第五输入电流源的电流= (所述第一输入电流源的电流—所述第二输入电流源的电流)×2。

[0012] 在某类实施例中,所述配置滤波功能的集成电路还包括:偏置晶体管,偏置晶体管的控制极用以与所述第一晶体管控制极和所述第三晶体管控制极电性连接,偏置晶体管的第九电极电性连接第六输入电流源,偏置晶体管的第十电极电性连接第七输入电流源,其中所述偏置晶体管的控制极与所述偏置晶体管的第九电极电性连接。

[0013] 在某类实施例中,所述配置滤波功能的集成电路还包括:第一电阻,其中所述偏置晶体管的控制极通过所述第一电阻与所述第一晶体管控制极电性连接;及第二电阻,其中所述偏置晶体管的控制极通过所述第二电阻与所述第三晶体管控制极电性连接。

[0014] 在某类实施例中,所述第一电容与所述第三电容大小相等,所述第二电容与所述第四电容大小相等。

[0015] 在某类实施例中,所述第一晶体管为P型晶体管,所述第二晶体管为N型晶体管。或者,所述第一晶体管为N型晶体管,所述第二晶体管为P型晶体管。在某类实施例中,当所述第一晶体管为P型晶体管、所述第二晶体管为N型晶体管时,所述第三晶体管为P型晶体管、所述第四晶体管为N型晶体管;或者,当所述第一晶体管为N型晶体管且所述第二晶体管为P型晶体管的,所述第三晶体管为N型晶体管且所述第四晶体管为P型晶体管。

[0016] 在某类实施例中,所述第一晶体管与所述第三晶体管具有相同的尺寸,所述第二晶体管与所述第四晶体管具有相同的尺寸。依据本发明的实施例,一种配置滤波功能的集成电路,包括:

[0017] 第一电路部、第二电路部、第一输入电流源、第二输入电流源、第三输入电流源、第四输入电流源和第五输入电流源,其中:

[0018] 第一电路部,包括第一输入端、第二输入端、第一输出端和第二输出端,其中,第一输入端用于接收第一差分输入信号,第二输入端用于接收第一输入电流源输入的第一电流,第一输出端用于输出第二电流至第二输入电流源;

[0019] 第二电路部,包括第三输入端、第四输入端、第三输出端和第四输出端,其中,第三输入端用于接收第三差分输入信号,第四输入端用于接收第三输入电流源输入的第三电流,第三输出端用于输出第四电流至第四输入电流源;

[0020] 第五输入电流源,电连接第一电路部的第二输出端和第二电路部的第四输出端; 共模晶体管,电性连接匹配输入电流源和所述第五输入电流源,所述共模晶体管用以接收 共模信号,其中所述匹配输入电流源的电流大小符合以下公式:

[0021] 所述匹配输入电流源的电流=所述第五输入电流源的电流-((所述第一输入电流源的电流-所述第二输入电流源的电流)+(所述第三输入电流源的电流-所述第四输入电流源的电流))。

[0022] 在某类实施例中,所述第一电路部包括:第一晶体管,包括通过第一电容接收所述

第一差分输入信号的控制极,和电性连接所述第一输入电流源的第一电极,和电性连接所述第二输入电流源的第二电极,其中所述第一晶体管的第二电极通过第二电容接地;及第二晶体管,包括与所述第一晶体管的第二电极电性连接的控制极,和所述第一晶体管的第一电极电性连接的第三电极;所述第二电路部包括:第三晶体管,包括通过第三电容接收所述第二差分输入信号的控制极,和电性连接所述第三输入电流源的第五电极,和电性连接所述第三晶体管的第六电极通过第四电容接地,所述第三晶体管的第五电极通过第五电容与所述第一晶体管的第一电极电性连接;第四晶体管,包括与所述第三晶体管的第六电极电性连接的控制极,和与所述第三晶体管的第五电极电性连接的第十电极,和与所述第二晶体管的第四电极电性连接的第八电极,其中所述第二晶体管的第四电极与所述第二晶体管的第八电极电性连接所为电流源;及所述共模晶体管包括用以接收所述共模信号的控制极,和电性连接所述匹配输入电流源的第十一电极,和电性连接所述第五输入电流源的第十一电极,和电性连接所述第五输入电流源的第十二电极。

[0023] 在某类实施例中,所述第一输入电流源的电流与所述第三输入电流源的电流大小相等,所述第二输入电流源的电流与所述第四输入电流源的电流大小相等,所述匹配输入电流源的电流=所述第五输入电流源的电流—(所述第一输入电流源的电流—所述第二输入电流源的电流)×2。在某类实施例中,所述配置滤波功能的集成电路还包括:偏置晶体管,偏置晶体管的控制极用以与所述第一晶体管控制极和所述第三晶体管控制极电性连接,偏置晶体管的第九电极电性连接第六输入电流源,偏置晶体管的第十电极电性连接第七输入电流源,其中所述偏置晶体管的控制极与所述偏置晶体管的第九电极电性连接。在某类实施例中,所述配置滤波功能的集成电路还包括:

[0024] 第一电阻,其中所述偏置晶体管的控制极通过所述第一电阻与所述第一晶体管控制极电性连接;及第二电阻,其中所述偏置晶体管的控制极通过所述第二电阻与所述第三晶体管控制极电性连接。

[0025] 在某类实施例中,所述第一电容与所述第三电容大小相等,所述第二电容与所述 第四电容大小相等。在某类实施例中,所述第一晶体管为P型晶体管,所述第二晶体管为N型 晶体管;或者,所述第一晶体管为N型晶体管,所述第二晶体管为P型晶体管。

[0026] 在某类实施例中,当所述第一晶体管为P型晶体管、所述第二晶体管为N型晶体管时,所述第三晶体管为P型晶体管、所述第四晶体管为N型晶体管;或者,当所述第一晶体管为N型晶体管、所述第二晶体管为P型晶体管时,所述第三晶体管为N型晶体管、所述第四晶体管为P型晶体管。

[0027] 值得一提的是,本发明提及的第一电极、第二电极等仅用于区分不同的晶体管,并非暗示该晶体管必然有未提及的其他电极,例如,第四晶体管包括第四晶体管控制极、第七电极和第八电极。本领域的技术人员将能够理解本发明所使用的用语以及相关微电子学基本概念,晶体管本名是半导体三极管(也称作三端子晶体管),主要分为两大类:双极性晶体管(BJT)和场效应晶体管(FET)。晶体管有三个极,例如双极型晶体管(例如三极管)的三个极,分别为发射极(Emitter)、基极(Base)和集电极(Collector);场效应晶体管(例如MOS管)的三个极,分别为源极(Source)、栅极(Gate)和漏极(Drain),其中基极或栅极也称为控制电极,例如本申请中的第一晶体管控制电极、第二晶体管控制电极等。

[0028] 本发明提高的能够有效地改进线性度,实现具备高线性度的配置滤波功能的集成

电路,相比于现有技术,具有如下有益效果:

[0029] (1)通过电流源I5的加入,有效提高了带通滤波器的线性度。

[0030] (2) 电流源I5能够有效抑制第二晶体管 $M_2$ 和第四晶体管 $M_4$ 电流变化的差异,使第五输入电流源的电流= (所述第一输入电流源的电流—所述第二输入电流源的电流) + (所述第三输入电流源的电流—所述第四输入电流源的电流),或者所述第五输入电流源的电流= (所述第一输入电流源的电流—所述第二输入电流源的电流) × 2,这样不仅能有效抑制外部输入的共模噪声,且能够提高输出线性度。

[0031] 同时,显著提升了输出信号质量和功率谱密度,如图3A、3B对比结果,图4A、4B对比结果。

[0032] (3)进一步提出了解决电流源不匹配的新型稳定输出共模的电路,晶体管Mc及电流源 $I_8$ 的加入,可以有效抑制第一制晶体管 $M_1$ 和第三晶体管 $M_3$ 进入线性区,解决了由于电流源间的不匹配导致输出共模变化太大的技术问题,弥补了实际制造情况下的不匹配,避免了输出共模电压点在实际制造下存在的较大扰动,提高了带通滤波器的性能。

[0033] (4)本发明提出的解决电流源不匹配的新型稳定输出共模的电路,在仅增加两个器件的情况下,有效提高了输出共模信号的稳定性,具有较低的功耗以及较小面积的优异特性。

[0034] 由上述特点可知,藉由本发明所教示的配置滤波功能的集成电路电路设计,能够有效地改进线性度、提升输出信号质量和谐波抑制能力,实现具备高线性度的有源跨导电容式带通滤波器,并以较低的功耗和面积实现了稳定输出共模的效果。

[0035] 为了能更进一步了解本发明的特征以及技术内容,请参阅以下有关本发明的详细说明与附图,然而附图仅提供参考与说明用,并非用来对本发明加以限制。

## 附图说明

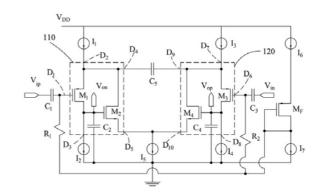

[0036] 图1是本发明的实施例配置滤波功能的集成电路的示意图;

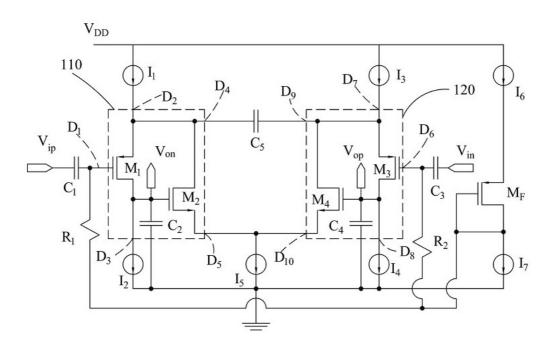

[0037] 图2是本发明的实施例配置滤波功能的集成电路的示意图;

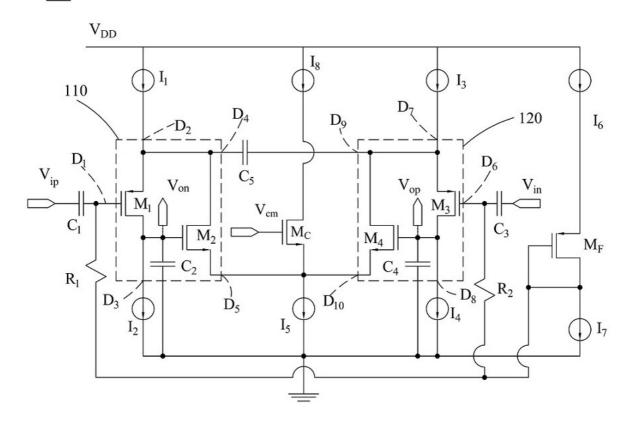

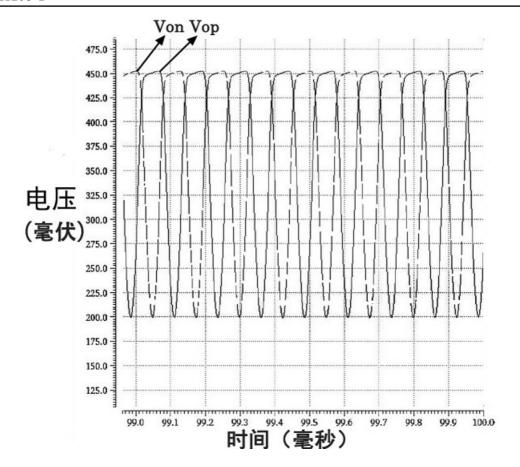

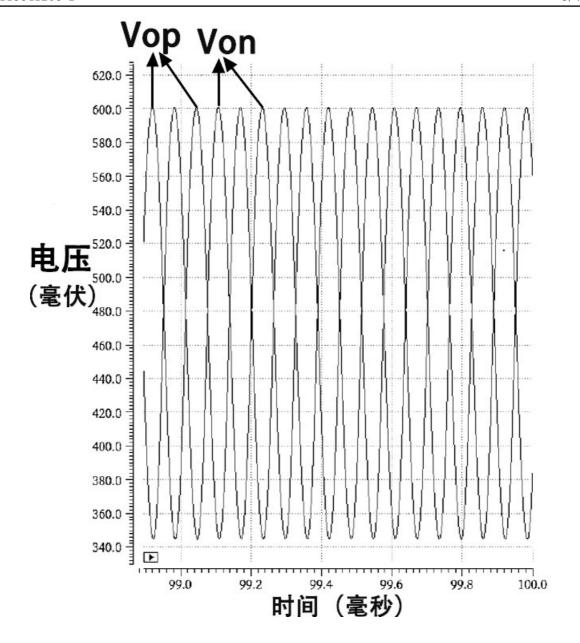

[0038] 图3A是本发明的实施例配置滤波功能的集成电路的输出波形图;

[0039] 图3B是本发明的实施例配置滤波功能的集成电路的输出波形图:

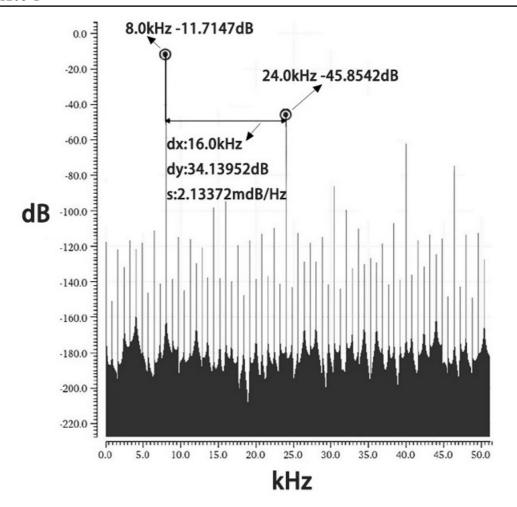

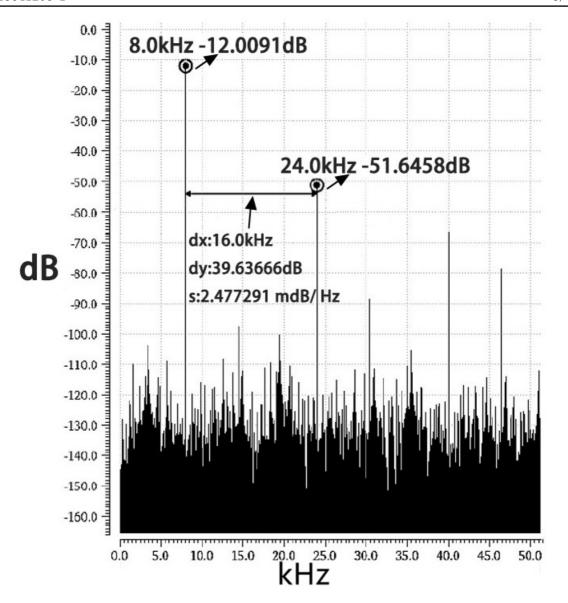

[0040] 图4A是本发明的实施例配置滤波功能的集成电路的功率谱密度图;

[0041] 图4B是本发明的实施例配置滤波功能的集成电路的功率谱密度图:

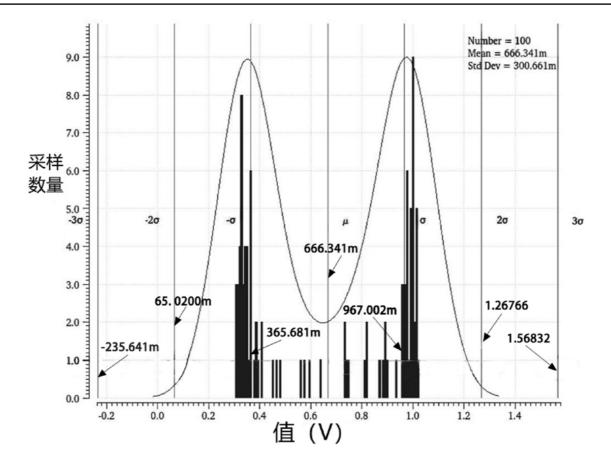

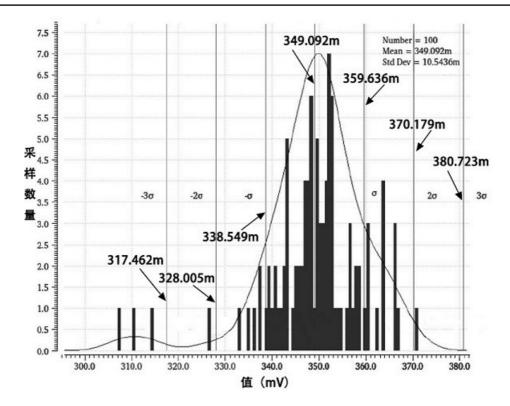

[0042] 图5A是本发明的实施例配置滤波功能的集成电路输出的蒙特卡洛分析图;

[0043] 图5B是本发明的实施例配置滤波功能的集成电路输出的蒙特卡洛分析图。

#### 具体实施方式

[0044] 下面将结合本发明实施例中附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明的实施例,本领域具有通常知识者在没有做出创造性劳动的前提下所获得的所有其他实施例,都属本发明保护的范围。此外,本发明所提到的"第一"及"第二"等用语并不代表任何顺序、数量或者重要性,只是用于区分不同的部分。而本发明所提到的方向用语,例如「上」、「下」、「前」、「后」、「左」、「右」、「顶」、「底」、「水平」、「垂直」等,仅是参考附加图式的方

向。因此,使用的方向用语是用以说明及理解本发明,而非用以限制本发明。附图仅仅用以示意性地加以说明,并未依照其真实尺寸进行绘制。而关于本文中所使用的"电性连接"或"电性耦接",可指二或多个组件实体地电性接触或间接地电性接触。

[0045] 在全篇说明书与权利要求所使用的用词,除有特别注明外,通常具有每个用词使用在此领域中、在本发明的内容中与特殊内容中的平常意义。某些用以描述本发明的用词将于下或在此说明书的别处讨论,以提供本领域技术人员在有关本发明的描述上额外的引导。

[0046] 请参阅图1,图1展示了本发明的第一实施例的配置滤波功能的集成电路的示意图。本实施例配置滤波功能的集成电路功能上等效为带通滤波器100,带通滤波器100主要包括第一电路部110、第二电路部120、第一电流源 $I_1$ 、第二电流源 $I_2$ 、第三电流源 $I_3$ 、第四电流源 $I_4$ 、第五电流源 $I_5$ 、第六电流源 $I_6$ 、第七电流源 $I_7$ 和偏置晶体管 $I_8$ 等主要部件。

[0047] 第一电路部110包括第一晶体管 $M_1$ 、第二晶体管 $M_2$ 和第二电容 $C_2$ 。其中,本发明的一个实施例中使用MOS晶体管,本领域技术人员可根据实际设计需求,将MOS晶体管相应地替换为三极管或其他晶体管,后续实施例也是同样的道理。

[0048] 该实施例中,第一晶体管 $M_1$ 为PMOS或PNP管,第二晶体管 $M_2$ 为NMOS或NPN管,但不仅限于此。

[0049] 第一晶体管 $M_1$ 的栅极/基极(第一晶体管控制极)于第一节点D1进一步通过第一电容 $C_1$ 接收外部输入的第一差分输入信号 $V_{ip}$ 。第一晶体管 $M_1$ 的源极/发射极(第一电极)于第二节点D2电性连接第一电流源 $I_1$ 以接收其电流。而第一晶体管 $M_1$ 的漏极/集电极(第二电极)与第二晶体管 $M_2$ 的栅极/基极(第二晶体管控制极)相接,并于第三节点D3进一步与第二电流源 $I_2$ 电性连接。此外,第一晶体管 $M_1$ 的漏极/集电极(第二电极)与第二晶体管 $M_2$ 的栅极/基极(第二晶体管控制极)也电性连接第二电容 $C_2$ 以接地。第二晶体管 $M_2$ 的漏极/集电极(第三电极)与第一晶体管 $M_1$ 的源极/发射极(第一电极)相接以形成负反馈,而第二晶体管 $M_2$ 的源极/发射极(第四电极)于第五节点D5进一步与第五电流源 $I_5$ 电性连接。

[0050] 如图1所示,第二电路部120与第一电路部110镜像对称。第二电路部120包括第三晶体管 $M_3$ 、第四晶体管 $M_4$ 和第四电容 $C_4$ 。与上述第一实施例相对应地,第三晶体管 $M_3$ 为PMOS或PNP管,而第四晶体管 $M_4$ 为NMOS或NPN管。

[0051] 第三晶体管 $M_3$ 的栅极/基极(第三晶体管控制极)于第六节点D6进一步通过第三电容 $C_3$ 接收外部输入的第二差分输入信号 $V_{\rm in}$ 。第三晶体管 $M_3$ 的源极/发射极(第五电极)于第七节点D7电性连接第三电流源 $I_3$ 以接收其电流。而第三晶体管 $M_3$ 的漏极/集电极(第六电极)与第四晶体管 $M_4$ 的栅极/基极(第四晶体管控制极)于第八节点D8相接,以进一步与第四电流源 $I_4$ 电性连接。此外,第三晶体管 $M_3$ 的漏极/集电极(第六电极)与第四晶体管 $M_4$ 的栅极/基极(第四晶体管控制极)也电性连接第四电容 $C_4$ 以接地。第四晶体管 $M_4$ 的漏极/集电极(第七电极)与第三晶体管 $M_3$ 的源极/发射极(第五电极)于第九节点D9相接以形成负反馈,且第四晶体管 $M_4$ 的漏极/集电极(第七电极)与第三晶体管 $M_3$ 的源极/发射极(第五电极)于第九节点D9处通过第五电容 $C_5$ 与第一电路部110的第四节点D4相接。此外,第四晶体管 $M_4$ 的源极/发射极(第八电极)于第十节点D10与第一电路部110的第五节点D5相接。亦即,第四晶体管 $M_4$ 的源极/发射极(第八电极)亦与第二晶体管 $M_2$ 的源极/发射极(第四电极)及第五电流源 $I_5$ 电性连接以接收其电流。其中,第一电容 $C_1$ ,第二电容 $C_2$ 和第五电容 $C_5$ 影响带通滤波器的传递函

数,其中第一电容C<sub>1</sub>影响电路高通性能,第二电容C<sub>2</sub>和第五电容C<sub>5</sub>影响电路低通性能。

[0052] 接着,偏置晶体管 $M_F$ 的栅极/基极(偏置晶体管 $M_F$ 的控制极)通过第一电阻 $R_1$ 于第一节点D1与第一晶体管 $M_1$ 的栅极/基极(第一晶体管控制极)偏置点电性连接,第二电阻R2的一端连接第三晶体管的栅极(第三晶体管控制极)偏置点D6,另一端连接偏置晶体管 $M_F$ 的栅极。此外,偏置晶体管 $M_F$ 的源极/发射极(第九电极)电性连接第六电流源 $I_6$ ,而偏置晶体管 $M_F$ 的栅极/基极(偏置晶体管 $M_F$ 的控制极)亦与其漏极/集电极(第十电极)相接,并进一步电性连接第七电流源 $I_7$ 。

[0053] 通过上述配置,第二晶体管 $M_2$ 的栅极/基极(第二晶体管控制极)可产生输出信号  $V_{on}$ ,而第四晶体管 $M_4$ 的栅极/基极(第四晶体管控制极)可产生输出信号 $V_{on}$ 。

[0054] 在一实施例中,第一电路部110的第一晶体管 $M_1$ 和第二电路部120的第三晶体管 $M_3$ 具有相同的尺寸,而第一电路部110的第二晶体管 $M_2$ 和第二电路部120的第四晶体管 $M_4$ 具有相同的尺寸。此外,第一电流源 $I_1$ 和第三电流源 $I_3$ 具有相同大小的输出电流,且第二电流源 $I_2$ 和第四电流源 $I_4$ 具有相同大小的输出电流。而第一电容 $C_1$ 和第三电容 $C_3$ 具有相同的电容值,第二电容 $C_2$ 和第四电容 $C_4$ 具有相同的电容值。值得注意的是,本领域技术人员能够理解,在实际制造中,器件值会存在一定的工艺偏差。

[0055] 带通滤波器100通过调整第五电流源 $I_5$ 来控制NMOS管第二晶体管 $M_2$ 和NMOS管第四晶体管 $M_4$ 的有效跨导。一般来说,当第一差分输入信号 $V_{\rm ip}$ 与第二差分输入信号 $V_{\rm in}$ 间的信号幅度比较大的情形下,相对于信号幅度低的情况下,第二晶体管 $M_2$ 和第四晶体管 $M_4$ 的有效跨导变化也会随着变大。而流经第二晶体管 $M_2$ 和第四晶体管 $M_4$ 的两电流之和亦会随着第一差分输入信号 $V_{\rm ip}$ 与第二差分输入信号 $V_{\rm in}$ 产生一定的偏差,此偏差可能导致输出信号 $V_{\rm on}$ 和输出信号 $V_{\rm op}$ 的线性度较差。因此,本实施例中,通过第五电流源 $I_5$ 的设置,使流经第二晶体管 $M_2$ 和第四晶体管 $M_4$ 的两电流之和始终等于第一电流源 $I_1$ 和第二电流源 $I_2$ 间电流差值的两倍(即 $I_5=2\times(I_1-I_2)$ ),借以抑制流经第二晶体管 $M_2$ 和第四晶体管 $M_4$ 的两电流的变化差异。藉由第五电流源 $I_5$ 的控制,不仅能有效抑制外部输入的共模噪声,亦能够提高输出信号的线性度。

[0056] 加入电流源 $I_5$ 之后能显著提高电路的线性度,应了解的是,于实际制造情况下,第一电流源 $I_1$ 、第二电流源 $I_2$ 和第五电流源 $I_5$ 的实际电流值可能存在偏差而无法匹配,即偏差导致等式 $I_5=2\times(I_1-I_2)$ 不再成立,容易导致带通滤波器不能正常工作或性能欠佳。举例来说,倘若第五电流源 $I_5$ 的电流数值小于第一电流源 $I_1$ 和第二电流源 $I_2$ 间电流差值的两倍(即 $I_5<2\times(I_1-I_2)$ ),容易导致第一晶体管 $M_1$ 和第三晶体管 $M_3$ 进入线性区,此时 $M_1$ 和 $M_3$ 的有效跨导会急剧下降,由此影响带通滤波器性能。第一晶体管 $M_1$ 和第三晶体管 $M_3$ 进入线性区的原因在于,第一电流源 $I_1$ 、第二电流源 $I_2$ 和第五电流源 $I_5$ 的不匹配,将导致流经第一晶体管 $M_1$ 和第三晶体管 $M_3$ 的电流小于给第一晶体管 $M_1$ 和第三晶体管 $M_3$ 是供偏置的第二电流源 $I_2$ 和第四电流源 $I_4$ 。于此情况下,第二电流源 $I_2$ 和第四电流源 $I_4$ 将进一步促使输出信号 $V_{on}$ 和输出信号 $V_{op}$ 之值被抬高。当第二晶体管 $M_2$ 和第四晶体管 $M_4$ 的栅极/基极到漏极/集电极的电压高于所要求的开启电压,则第二晶体管 $M_2$ 和第四晶体管 $M_4$ 的栅极/基极到漏极/集电极的电压和第四晶体管 $M_4$ 的跨导值急剧衰减,导致带通滤波器的传输函数失效,带通滤波器100即无法正常工作或性能欠佳。

[0057] 在一实施例中,可通过提高第五电流源 $I_5$ 的数值来减少输出信号 $V_{on}$ 和输出信号 $V_{on}$

到地的电阻值,以避免第二晶体管 $M_2$ 和第四晶体管 $M_4$ 进入线性区,即使实际制造存在偏差,但 $I_5$ 小于2×( $I_1$ - $I_2$ )值不再成立,则第二晶体管 $M_2$ 和第四晶体管 $M_4$ 不易进入线性区。然而,当第五电流源 $I_5$ 的数值被增大时,会影响第一电流源 $I_1$ 和第三电流源 $I_3$ 的性能。

[0058] 为了解决电流源不匹配的问题,以进一步提高带通滤波器性能,有效改进线性度,实现稳定的共模输出,提出了图2展示了所示的本发明配置滤波功能的集成电路的另一实施例的示意图。该实施例中,所有晶体管均采用MOS晶体管,该结构同样适用于至少部分晶体管采用三极管的结构,如所有晶体管均为三极管,或者仅共模晶体管M。为MOS管,或者仅共模晶体管M。为三极管。

[0059] 图2所示的配置滤波功能的集成电路等效为带通滤波器200。带通滤波器200进一步设置有共模晶体管 $M_c$ 和匹配输入电流源 $I_{8}$ 。共模晶体管 $M_c$ 为NMOS管,共模晶体管 $M_c$ 的栅极接收共模电压信号 $V_{cm}$ ,共模晶体管 $M_c$ 的源极/发射极(第十二电极)与第二晶体管 $M_2$ 的源极/发射极(第四电极)、第四晶体管 $M_4$ 的源极/发射极(第八电极)及第五电流源 $I_5$ 电性连接,共模晶体管 $M_c$ 的漏极/集电极(第十一电极)与匹配输入电流源 $I_8$ 相接以接收其输出电流。通过共模晶体管 $M_c$ 的设置,可以有效抑制第一晶体管 $M_1$ 和第三晶体管 $M_3$ 进入线性区。

[0060] 如前述,当第五电流源 $I_5$ 的数值被增大时,可能导致第一电流源 $I_1$ 和第三电流源 $I_3$ 不能有效工作的情况。因此,于此实施例中,匹配输入电流源 $I_8$ 作为匹配输入电流源,可通过匹配输入电流源 $I_8$ 来补偿第五电流源 $I_5$ 增加的部分,以及通过共模晶体管 $M_c$ 来钳位住输出信号 $V_{\rm on}$ 和输出信号 $V_{\rm op}$ 的直流工作点。详细而言,匹配输入电流源 $I_8$ 之电流大小设定为第五电流源 $I_5$ 减去第一电流源 $I_1$ 和第二电流源 $I_2$ 间电流差值的两倍(即 $I_8=I_5-2\times (I_1-I_2)$ ),以补偿第五电流源 $I_5$ 。当共模晶体管 $M_c$ 的临界电压为 $V_{\rm thc}$ ,第二晶体管 $M_2$ 的临界电压为 $V_{\rm th2}$ ,可通过共模信号 $V_{\rm cm}$ 来控制第二晶体管 $M_2$ 的源极电压为 $V_{\rm thc}$ 。因此,输出信号 $V_{\rm on}$ 的电压被钳位在 $V_{\rm cm}-V_{\rm thc}$ 。同理,当第四晶体管 $M_4$ 的临界电压为 $V_{\rm th4}$ ,可通过共模信号 $V_{\rm cm}-V_{\rm thc}$ 。因此,输出信号 $V_{\rm on}$ 的电压被钳位在 $V_{\rm cm}-V_{\rm thc}$ 。因此,输出信号 $V_{\rm on}$ 的电压被钳位在 $V_{\rm cm}-V_{\rm thc}$ 。因此,输出信号 $V_{\rm on}$ 的电压被钳位在 $V_{\rm cm}-V_{\rm thc}$ ,可通过共模信号 $V_{\rm cm}-V_{\rm thc}$

[0061] 基于上述实施例,当第二晶体管 $M_2$ 的栅极/基极(第二晶体管控制极)电压(即输出信号 $V_{on}$ )和其漏极电压的电压差被限定以不超过其临界电压 $V_{th2}$ ,则第二晶体管 $M_2$ 不会进入线性区。同理,第四晶体管 $M_4$ 的栅极/基极(第四晶体管控制极)电压(即输出信号 $V_{op}$ )和其漏极电压的电压差被限定以不超过其临界电压 $V_{th4}$ ,则第四晶体管 $M_4$ 不会进入线性区,由此解决了由于电流源不匹配导致输出共模变化太大的问题。

[0062] 综上所述,相较于带通滤波器100,带通滤波器200通过设置共模晶体管 $M_c$ 和匹配输入电流源 $I_8$ ,可以进一步解决由于第一电流源 $I_1$ 、第二电流源 $I_2$ 和第五电流源 $I_5$ 的不匹配所导致的输出共模变化太大的问题。

[0063] 请同时参阅图3A和图3B。图3A展示了当带通滤波器未设置有控制第二晶体管 $M_2$ 和第四晶体管 $M_4$ 有效跨导的第五电流源 $I_5$ 时的输出波形图。而图3B展示了本发明的一实施例的带通滤波器100的输出波形图,该带通滤波器设置有第五电流源 $I_5$ 。其中,图3A和图3B的输出波形图的纵轴单位为电压值 (mV),横轴单位为时间 (ms)。从此二图中可看出,具备第五电流源 $I_5$ 设置的带通滤波器100的输出信号 $V_{\rm on}$ 及输出信号 $V_{\rm op}$ ,相较于无第五电流源 $I_5$ 设置时的输出信号 $V_{\rm on}$ 及输出信号 $V_{\rm on}$ ,具有更高的线性度。

[0064] 接着,请同时参阅图4A和图4B。图4A展示了当带通滤波器未设置有控制第二晶体

管 $M_2$ 和第四晶体管 $M_4$ 有效跨导的第五电流源 $I_5$ 时的功率谱密度图。而图4B展示了本发明的改进实施例的带通滤波器100的功率谱密度图,该带通滤波器设置有第五电流源 $I_5$ 。其中,图4A和图4B的功率谱密度图的纵轴单位为分贝(dB),横轴单位为频率(kHz)。于图4A中,可看出当带通滤波器100未设置有第五电流源 $I_5$ 时,其三次谐波抑制大致上为一34.1dB。而于图4B中,可看出当带通滤波器100设置有第五电流源 $I_5$ 时,其三次谐波抑制大致上为一39.6dB。明显地,带通滤波器100的三次谐波抑制效果可达到显着的提升。

[0065] 请同时参阅图5A和图5B。图5A展示了图1所展示的带通滤波器100输出的蒙特卡洛分析图,而图5B展示了图2所展示的带通滤波器200输出的蒙特卡洛分析图。其中,图5A和图5B蒙特卡洛分析图的纵轴单位为抽样数量(sample),横轴单位为电压值(V)。于图5A中,可看出带通滤波器100输出的共模信号变化较大。而相较于带通滤波器100,带通滤波器200通过设置共模晶体管M。和匹配输入电流源I<sub>8</sub>的控制,输出共模信号变化大的问题得以进一步解决(如图5B所示)。

[0066] 综合以上,本发明所教示配置滤波功能的集成电路设计,能够有效地改进线性度,实现具备高线性度的新型电容式带通滤波器。此外,本发明提出了解决电流源不匹配的新型稳定输出共模的电路,在仅增加两个器件(电流源I<sub>8</sub>和晶体管M<sub>c</sub>)的情况下,有效提高了输出共模信号的稳定性,具有较低的功耗以及较小面积的优异特性。

[0067] 除此之外,本发明的另一些实施例可进行N型晶体管和P型晶体管的转换,例如,第一晶体管 $M_1$ 为NMOS/NPN管,第二晶体管 $M_2$ 为PMOS/PNP管,如此,其余元件,电流源、电源和地的连接也相应地发生变化,这些都是电路设计领域常用的变换。但不仅限于此,晶体管 $M_1$ 与 $M_2$ 可以为同为N型或P型,只要 $M_2$ 的漏极/集电极接 $M_1$ 的源极/发射极, $M_2$ 的栅极/基极接 $M_1$ 的漏极/集电极极,形成负反馈即可。

[0068] 综上所述,本发明能够有效地改进线性度,实现具备高线性度的有源跨导电容式带通滤波器。虽然本发明已以较佳实施例揭露如上,但该较佳实施例并非用以限制本发明,该领域的普通技术人员,在不脱离本发明的精神和范围内,可以对前述实施例所记载的技术方案进行修改与润饰,或者对其中部分技术特征进行等同替换,而这些修改或替换均应包括在本发明的保护范围之内。本发明的保护范围以权利要求为准。

100

图1

200

图2

图3A

图3B

图4A

图4B

图5A

图5B