# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*H01L 31/0352* (2006.01) *H01L 31/0216* (2014.01)

**H01L 31/0392** (2006.01) **H01L 31/18** (2006.01)

(21) 출원번호 10-2014-0152753

(22) 출원일자 **2014년11월05일** 심사청구일자 **2014년11월05일**

(43) 공개일자

(71) 출원인

(11) 공개번호

#### 성균관대학교산학협력단

경기도 수원시 장안구 서부로 2066, 성균관대학교 내 (천천동)

10-2016-0053548

2016년05월13일

(72) 발명자

#### 박일흥

경기도 수원시 장안구 서부로 2066, 제2공학관 502호 (천천동, 성균관대학교자연과학캠퍼스)

#### 이직

경기도 수원시 장안구 서부로 2066, 제2공학관 506호 (천천동, 성균관대학교자연과학캠퍼스) (뒷면에 계속)

(74) 대리인

특허법인엠에이피에스

전체 청구항 수 : 총 12 항

#### (54) 발명의 명칭 확산 방지충을 이용한 실리콘 광증배 소자 및 그 제조 방법

#### (57) 요 약

본 발명은 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법에 있어서, 중간층에 단위 마이크로 픽셀을 구분하는 트렌치를 형성하는 단계, 마이크로 픽셀의 영역에 PN접합층을 형성하는 단계, PN접합층과 트렌치의 측벽사이에 확산 방지층을 형성하는 단계, 실리콘 광증배 소자의 상부면에 절연층을 형성하는 단계, 절연층의 상부면에 폴리실리콘 저항층을 형성하는 단계, 및 폴리실리콘 저항층과 PN접합층을 연결하는 금속 전극을 형성하는 단계를 포함한다.

#### 대 표 도 - 도3b

(72) 발명자

이혜영

충청북도 청주시 흥덕구 오송읍 오송가락로 235, 110동 301호 (청원오송휴먼시아1단지) 전진아

서울특별시 송파구 올림픽로35길 104, 25동 1006호 (신천동, 장미아파트)

이 발명을 지원한 국가연구개발사업

과제고유번호 UD110112FD 부처명 방위사업청

연구관리전문기관 국방과학연구소 연구사업명 국방 특화연구실 사업 연구과제명 차세대 광센서 특화연구실

기 여 율 1/1

주관기관 성균관대학교 산학협력단 연구기간 2014.06.01 ~ 2016.12.31

## 명 세 서

#### 청구범위

#### 청구항 1

확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법에 있어서,

중간층에 단위 마이크로 픽셀을 구분하는 트렌치를 형성하는 단계;

상기 마이크로 픽셀의 영역에 PN접합층을 형성하는 단계;

상기 PN접합층과 상기 트렌치의 측벽 사이에 확산 방지층을 형성하는 단계;

상기 실리콘 광증배 소자의 상부면에 절연층을 형성하는 단계;

상기 절연층의 상부면에 폴리실리콘 저항층을 형성하는 단계; 및

상기 폴리실리콘 저항층과 상기 PN접합층을 연결하는 금속 전극을 형성하는 단계를 포함하는 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 청구항 2

제 1 항에 있어서,

상기 확산 방지층을 형성하는 단계는

상기 트렌치의 측벽과 상기 PN접합층 사이에 질소 이온을 주입한 후 열처리하여 실리콘 질화물 $(Si_3N_4)$ 을 형성시키는 것인 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 청구항 3

제 1 항에 있어서,

상기 확산 방지층은

상기 PN접합층의 불순물이 상기 트렌치의 측벽까지 확산되는 것을 방지하여, 상기 트렌치의 측벽 영역에서 PN 항복전압(breakdown voltage)이 감소되는 것을 방지하는 것인 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

## 청구항 4

확산 방지층을 이용한 실리콘 광증배 소자에 있어서,

기판;

상기 기판 위의 중간층;

상기 중간층에 형성되며 단위 마이크로 픽셀의 영역을 구분하는 트렌치;

상기 중간층에 형성된 PN 접합층;

상기 PN접합층과 상기 트렌치의 측벽 사이에 형성된 확산 방지층;

상기 실리콘 광증배 소자의 상부면에 형성된 절연층;

상기 절연층의 상부면에 형성된 폴리실리콘 저항층;

상기 폴리실리콘 저항층과 상기 PN접합층을 연결하는 금속 전극을 포함하는 확산 방지층을 이용한 실리콘 광증배 소자.

#### 청구항 5

제 4 항에 있어서,

상기 확산 방지층은

상기 트렌치의 측벽과 상기 PN접합층 사이에 질소 이온을 주입한 후 열처리하여 형성된 실리콘 질화물 $(Si_{\vartheta}N_{4})$ 인 文인 확산 방지층을 이용한 실리콘 광증배 소자.

#### 청구항 6

제 4 항에 있어서,

상기 확산 방지층은

상기 PN접합층의 불순물이 상기 트렌치의 측벽까지 확산되는 것을 방지하여, 상기 트렌치의 측벽 영역에서 PN 항복전압(breakdown voltage)이 감소되는 것을 방지하는 것인 확산 방지층을 이용한 실리콘 광증배 소자.

#### 청구항 7

확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법에 있어서,

중간층에 단위 마이크로 픽셀을 구분하는 트렌치를 형성하는 단계;

상기 트렌치의 측벽에 인접하도록 확산 방지층을 형성하는 단계;

상기 마이크로 픽셀의 영역에 포함된 확산 방지층들 사이에 PN접합층을 형성하는 단계;

상기 실리콘 광증배 소자의 상부면에 절연층을 형성하는 단계;

상기 절연층의 상부면에 폴리실리콘 저항층을 형성하는 단계; 및

상기 폴리실리콘 저항층과 상기 PN접합층을 연결하는 금속 전극을 형성하는 단계를 포함하는 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 청구항 8

제 7 항에 있어서,

상기 확산 방지층을 형성하는 단계는

상기 트렌치의 측벽과 상기 PN접합층 사이에 질소 이온을 주입한 후 열처리하여 실리콘 질화물 $(Si_3N_4)$ 을 형성시키는 것인 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 청구항 9

제 7 항에 있어서,

상기 확산 방지층은

상기 PN접합층의 불순물이 상기 트렌치의 측벽까지 확산되는 것을 방지하여, 상기 트렌치의 측벽 영역에서 PN 항복전압(breakdown voltage)이 감소되는 것을 방지하는 것인 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 청구항 10

확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법에 있어서,

중간층의 마이크로 픽셀로 설정된 영역에 PN접합층을 형성하는 단계;

상기 PN접합층이 형성된 중간층을 단위 마이크로 픽셀로 구분하는 트렌치를 형성하는 단계;

상기 PN접합층과 상기 트렌치의 측벽 사이에 확산 방지층을 형성하는 단계;

상기 실리콘 광증배 소자의 상부면에 절연층을 형성하는 단계;

상기 절연층의 상부면에 폴리실리콘 저항층을 형성하는 단계; 및

상기 폴리실리콘 저항층과 상기 PN접합층을 연결하는 금속 전극을 형성하는 단계를 포함하는 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 청구항 11

제 10 항에 있어서,

상기 확산 방지층을 형성하는 단계는

상기 트렌치의 측벽과 상기 PN접합층 사이에 질소 이온을 주입한 후 열처리하여 실리콘 질화물(Si<sub>3</sub>N<sub>4</sub>)을 형성시키는 것인 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 청구항 12

제 10 항에 있어서,

상기 확산 방지층은

상기 PN접합층의 불순물이 상기 트렌치의 측벽까지 확산되는 것을 방지하여, 상기 트렌치의 측벽 영역에서 PN 항복전압(breakdown voltage)이 감소되는 것을 방지하는 것인 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법.

#### 발명의 설명

#### 기 술 분 야

[0001] 본 발명은 확산 방지층을 이용한 실리콘 광증배 소자(Silicon PhotoMultiplier device: SiPM) 및 제조하는 방법에 관한 것이다.

#### 배경기술

- [0002] 실리콘 광증배 소자(Silicon Photomultiplier; SiPM)는 100만배로 신호를 증폭시킬 수 있어, 단일 광자의 측정 이 가능하고, 초소형으로 제작이 가능하며, 동작전압이 낮고(일반적으로 25~100V), 자기장에 영향을 받지 않는 특징을 가지고 있다.

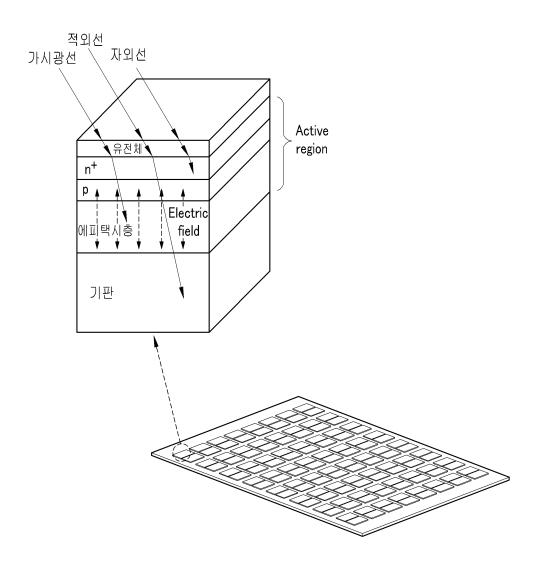

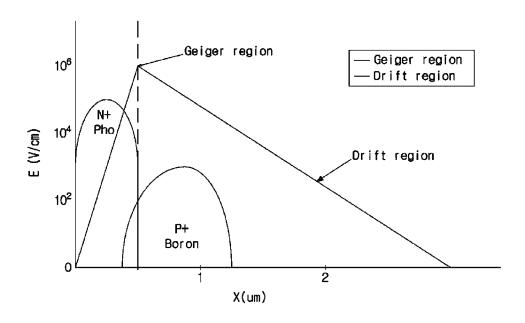

- [0003] 도 1은 일반적인 실리콘 광증배 소자 및 그에 포함된 어느 하나의 마이크로 픽셀을 나타낸 도면이고, 도 2는 도 1의 마이크로 픽셀에 있어서, 제 1 및 제 2 접합층 및 에피텍시층 각각의 도핑농도에 대응하여, 동작전압 인가에 따른 활성영역의 전기장 분포를 나타낸 도면이다.

- [0004] 실리콘 광증배 소자는 다수의 마이크로 픽셀(Micro-pixel)을 포함하여 이루어진다. 각 마이크로 픽셀의 크기는 25~100년 1㎡의 면적당 마이크로 픽셀 100~1000개가 집적된다. 각 마이크로 픽셀은 p+ 전도성 타입의 기판위에 5년 이하의 두께로 형성된 p- 전도성 타입의 에피텍시층(Epitaxial Layer)과, 에피텍시층 내에 순차적으로 p 이온과 n+ 이온을 주입하여 형성된 PN 접합층(PN-Junction Layer)을 포함한다.

- [0005] 마이크로 픽셀의 간단한 동작 원리는 다음과 같다. PN 접합층에서는 n형에서 p형 방향으로 매우 강한 전기장이 형성됨에 따라 얇은 공핍 영역(Depletion Region)이 형성된다. 이때, 마이크로 픽셀로 입사되는 빛(광자)에 의해 생성된 전자-정공 짝(Electron-Hole Pair)이 형성되어 있는 전기장에 의해 가속된다. 이렇게 가속된 전자-정공 짝은 전자사태 방전(Avalanche Breakdown)을 야기시키고, 전자사태 방전에 의해 신호가 증폭된다. 각 마이크로 픽셀은 도 2에 도시된 가이거 영역(Geiger region)에서 동작하며, 센서내의 모든 마이크로 픽셀들의 신호는 하나의 출력으로 합쳐진다. 도 2는 일반적인 실리콘 광증배 소자에서 에피텍시층 내 전기장의 분포를 나타내는 도면이다.

- [0006] 이러한 종래 실리콘 광증배 소자는 각 마이크로 픽셀을 광학적으로 서로 분리하기 위하여, 마이크로 픽셀 사이에 배치되는 트랜치 구조 또는 가드링을 포함한다. 즉, 트랜치 구조 또는 가드링은 마이크로 픽셀 간에 서로 미치는 영향을 감소시키기 위한 구성이다.

- [0007] 한편, 한국등록특허 제10-1113364호(발명의 명칭: 실리콘 광전자 증배관 및 상기 실리콘 광전자 증배관을 위한 셀)는 종래 실리콘 광증배 소자의 구조를 개시하면서 이방성 에칭에 의해 마이크로 픽셀 사이에 형성되는 오목 부 형상의 분리 요소에 대한 기술을 설명하고 있다.

[0008] 한편, 종래에는 실리콘 광증배 소자의 제조시, 마이크로 픽셀의 집적도를 향상시키기 위하여, 패턴의 선 폭이 줄어들고 있다. 선 폭이 줄어 들수록 PN접합층의 불순물이 후속 열처리 공정에서 트렌치로 확산됨에 따라 트렌치의 상부 및 모서리 부분에서 PN접합의 평면 영역보다 큰 전계값(전기장)을 형성하여 PN의 항복전압(breakdown voltage)을 감소시키는 문제가 있었다.

#### 발명의 내용

#### 해결하려는 과제

[0009] 본 발명의 일부 실시예는 실리콘 광증배 소자의 제조시 발생할 수 있는 PN접합층의 불순물의 확산으로 인한 PN 항복전압(breakdown voltage)이 감소되는 것을 방지하는 제조 방법을 제안하는 것을 목적으로 한다.

#### 과제의 해결 수단

- [0010] 상술한 기술적 과제를 달성하기 위한 기술적 수단으로서, 본 발명의 제 1 측면에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법은 중간층에 단위 마이크로 픽셀을 구분하는 트렌치를 형성하는 단계, 마이크로 픽셀의 영역에 PN접합층을 형성하는 단계, PN접합층과 트렌치의 측벽 사이에 확산 방지층을 형성하는 단계, 실리콘 광증배 소자의 상부면에 절연층을 형성하는 단계, 절연층의 상부면에 폴리실리콘 저항층을 형성하는 단계, 및 폴리실리콘 저항층과 PN접합층을 연결하는 금속 전극을 형성하는 단계를 포함한다.

- [0011] 또한, 본 발명의 제 2 측면에 따른 확산 방지층을 이용한 실리콘 광증배 소자는 기판, 기판 위의 중간층, 중간 층에 형성되며 단위 마이크로 픽셀 영역을 구분하는 트렌치, 중간층에 형성된 PN 접합층, PN접합층과 트렌치의 측벽 사이에 형성된 확산 방지층, 실리콘 광증배 소자의 상부면에 형성된 절연층, 절연층의 상부면에 형성된 폴리실리콘 저항층, 폴리실리콘 저항층과 PN접합층을 연결하는 금속전극을 포함한다.

- [0012] 또한, 본 발명의 제 3 측면에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법은 중간층에 PN접합층을 형성하는 단계, PN접합층이 형성된 중간층을 단위 마이크로 픽셀로 구분하는 트렌치를 형성하는 단계, PN접합층과 트렌치의 측벽 사이에 확산 방지층을 형성하는 단계, 실리콘 광증배 소자의 상부면에 절연층을 형성하는 단계, 절연층의 상부면에 폴리실리콘 저항층을 형성하는 단계, 및 폴리실리콘 저항층과 PN접합층을 연결하는 금속 전극을 형성하는 단계를 포함한다.

## 발명의 효과

[0013] 전술한 본 발명의 과제 해결 수단에 의하면, PN접합층과 트렌치의 측벽 사이에 확산 방지층을 형성하여, PN접합층의 불순물이 트렌치까지 확산되는 것을 방지하고, 이로 인해 트렌치의 측벽에서 PN 항복전압(breakdown voltage)이 감소되는 것을 방지하여 소자의 성능이 향상되는 효과가 있다.

#### 도면의 간단한 설명

[0014] 도 1은 일반적인 실리콘 광증배 소자 및 그에 포함된 어느 하나의 마이크로 픽셀을 나타낸 도면이다.

도 2는 도 1의 마이크로 픽셀에 있어서, 제 1 및 제 2 접합층 및 에피텍시층 각각의 도핑농도에 대응하여, 동작 전압 인가에 따른 활성영역의 전기장 분포를 나타낸 도면이다.

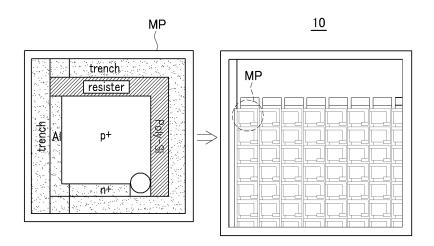

도 3a는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 평면을 도시한 도면이다.

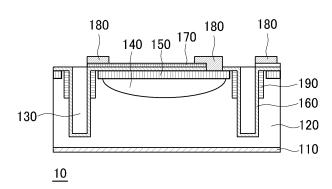

도 3b는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 단면을 도시한 단면도이다.

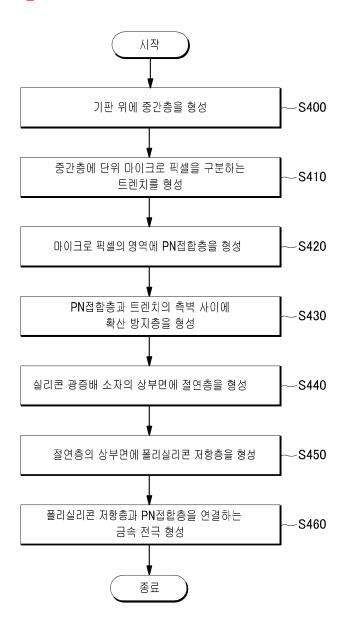

도 4는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제작 순서도이다.

도 5는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제작 공정도이다.

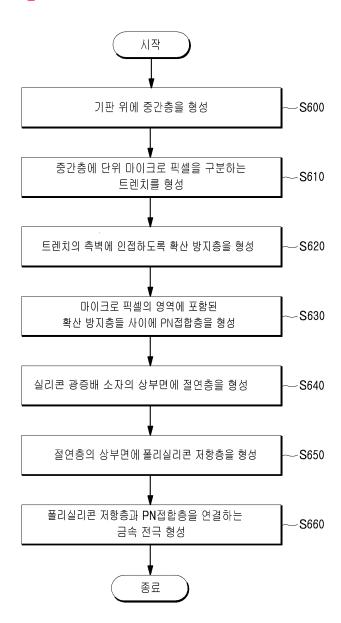

도 6은 본 발명의 다른 실시예에 따른 실리콘 광증배 소자의 제작 순서도이다.

도 7은 본 발명의 일 실시예에 따른 확산 방지층의 공정과정을 설명하기 위한 도면이다.

도 8은 본 발명의 다른 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제작 순서도이다.

#### 발명을 실시하기 위한 구체적인 내용

[0015] 아래에서는 첨부한 도면을 참조하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할

수 있도록 본 발명의 실시예를 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다. 그리고 도면에서 본 발명을 명확하게 설명하기 위해서 설명과 관계없는 부분은 생략하였으며, 명세서 전체를 통하여 유사한 부분에 대해서는 유사한 도면 부호를 붙였다.

- [0016] 명세서 전체에서, 어떤 부분이 다른 부분과 "연결"되어 있다고 할 때, 이는 "직접적으로 연결"되어 있는 경우뿐 아니라, 그 중간에 다른 소자를 사이에 두고 "전기적으로 연결"되어 있는 경우도 포함한다. 또한 어떤 부분이 어떤 구성요소를 "포함"한다고 할 때, 이는 특별히 반대되는 기재가 없는 한 다른 구성요소를 제외하는 것이 아니라 다른 구성요소를 더 포함할 수 있는 것을 의미한다.

- [0017] 이하, 도면을 참조하여 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자 및 제조 방법에 대하여 자세히 설명한다.

- [0018] 도 3a는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 평면을 도시한 도면이다.

- [0019] 먼저, 도 3a에 도시된 바와 같이, 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자(10)의 기판은 p 전도성 타입 또는 n 전도성 타입으로 도핑되고, 실리콘 기판일 수 있다. 참고로, 실리콘 광증배 소자(10)의 단위 마이크로 픽셀 영역(Micro pixel, MP)은 마이크로 픽셀을 둘러싼 트렌치에 의하여 구분될 수 있다. 즉, 좌우 측면에 배치된 트렌치와 전후방에 배치된 트렌치가 마이크로 픽셀 영역을 둘러싸도록 할 수 있다.

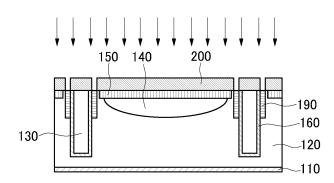

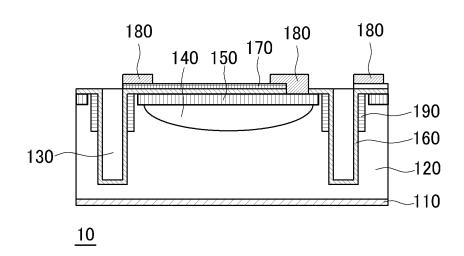

- [0020] 다음으로, 도 3b는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 단면을 도시한 단면도이다.

- [0021] 도 3b에 도시된 바와 같이, 본 발명의 일 실시예에 따른 실리콘 광증배 소자(10)는 기판(110), 중간층(120), 트 렌치(130), P형 반도체층(140), N 형 반도체층(150), 절연층(160), 폴리실리콘 저항층(170), 금속 전극(180), 및 확산 방지층(190)을 포함한다.

- [0022] 기판(110)의 상부에 중간층(120)이 형성될 수 있다. 또한, 기판(110)은 p 전도성 타입 또는 n 전도성 타입으로 도핑되고, 실리콘 기판일 수 있다. 이때, 기판의 도핑 농도는  $10^{16} \sim 10^{20}$  cm<sup>-3</sup>의 고농도이거나, 자연적으로 발생하는 암전류(Dark Current)를 감소시키기 위해  $10^{12} \sim 10^{16}$  cm<sup>-3</sup>의 저농도일 수도 있다.

- [0023] 중간층(120)은 기판(110)의 상부와 절연층(160)의 중간에 형성된다. 이때, 중간층(120)은 에피텍시(epitaxy)공 정을 이용하여 형성시킬 수 있다. 또한, 트렌치(130)와 PN접합층은 중간층(120)상에 형성될 수 있다.

- [0024] 또한, 중간층(120)은 기판(110)과 동일한 전도성 타입으로 도핑된다. 즉, 기판(110)이 p 전도성 타입이면 중간 층(120)도 p 전도성 타입이다. 중간층(120)은 1014~1018cm-3과 같이 기판(110)과 다른 도핑 농도로 형성시킬 수 있고, 기판(110)에 자연적으로 발생하는 암전류(Dark Current)를 감소시키기 위해 10<sup>12</sup>~10<sup>16</sup>cm<sup>-3</sup>과 같이 기판 (110)과 동일한 도핑 농도로 형성시킬 수도 있다.

- [0025] 트렌치(130)는 중간층(120)에 형성될 수 있다. 또한, 트렌치(130)를 통하여 실리콘 광증배 소자(10)를 단위 마이크로 픽셀 영역으로 구분할 수 있다.

- [0026] 참고로, P형 반도체충(140) 및 N형 반도체충(150)에 의해 중간충(120) 내에는 PN 접합층이 성장되고, PN 접합이 일어나 공핍 영역이 형성된다. 이러한 공핍 영역에서 발생되는 전자사태 방전은 마이크로 픽셀로 입사되는 빛의 증폭과 매우 밀접한 관계를 가진다. 즉, 2차 광자가 생성될 수 있고, 생성된 2차 광자에 의해 마이크로 픽셀의 광검출 효율에 악영향을 미치는 크로스토크 현상이 일어날 수 있다. 마이크로 픽셀로 입사되는 빛이 증폭되기 위해서는, 입사광이 PN 접합층까지 효율적으로 전달되어야 한다.

- [0027] 절연층(160)은 실리콘 광증배 소자(10) 내의 다중 픽셀을 격리시킬 수 있다. 또한, 절연층(160)은 트렌치(13 0)가 형성될 때, 트렌치(130)를 산화물로 채우기 전에 중간층(120)과 트렌치영역 사이에 형성되어 함께 트렌치(130)를 이루기도 하며, PN접합층이 형성된 후, 트렌치(130)를 제외한 영역 상에 절연층(160)이 형성되어 다중 픽셀을 격리시킬 수 있다.

- [0028] 한편, 절연층(160)을 통해서, 빛(광자)가 입사하면 빛에 의해 생성된 전자-정공 쌍(electron-hole pair)이 내부 자기장에 의해 가속화 됨에 따라 충돌 이온화(impact ionization)에 의해 캐리어 수가 기하급수적으로 증가하면 서 신호가 증폭되어 나타날 수 있다. 또한, 빛(광자)은 폴리실리콘 저항층(170)을 통해서 입사될 수도 있다.

- [0029] 또한, 폴리실리콘 저항층(170)은 절연층(160)의 상부면에 형성될 수 있다. 이때, 폴리실리콘 저항층(170)은 Quenching 저항으로 실리콘 광증배 소자(10)의 마이크로 픽셀 내에 입사된 광에 의해 전자 사태(avalanche

breakdown)가 발생되면 일정량의 전류가 흐른 후 전류를 차단함으로써 실리콘 광증배 소자(10) 내의 모든 마이크로 픽셀에서 출력되는 전류의 양을 동일하게 만들고, 마이크로 픽셀 내의 잔류 전류를 종식시킴으로써 마이크로 픽셀을 수십 나노 초 내에 동작 상태로 만들 수 있다.

- [0030] 또한, 실리콘 광증배 소자(10)내에 폴리실리콘 저항층(170)과 PN접합층을 연결하는 금속 전극(180)이 형성될 수 있으며, 금속 전극(180)은 PN접합층과 폴리실리콘 저항층(170)을 전기적으로 연결할 수 있다.

- [0031] 한편, 확산 방지층(190)은 PN영역의 불순물 주입 후 후속의 열처리 공정에서, 불순물이 트렌치(130)까지 확산되는 것을 방지한다. 종전의 구성에는 불순물이 트렌치(130)까지 확산되면, 트렌치(130)상부 및 모서리 부분의 거칠고 뾰족한 표면에서 PN접합의 평면 영역보다 큰 전계값을 갖게 되어, 센서의 PN 항복전압(breakdown voltage)이 감소되는 문제가 발생할 수 있었다.

- [0032] 그러나, 본 발명의 일 실시예에 따른 확산 방지층(190)은 불순물이 트렌치(130)까지 확산되는 것을 방지하며, 이로 인하여 센서의 PN 항복전압(breakdown voltage)이 감소되는 것을 방지할 수 있다.

- [0033] 이때, 확산 방지층(190)은 트렌치(130)의 측벽과 PN접합층 사이에 질소 이온을 주입한 이후 열처리를 함으로써 형성된 실리콘 질화물(Si3N4)일 수 있다.

- [0034] 다음은 도 4를 참조하여, 실리콘 광증배 소자의 제작 방법에 대해서 자세히 설명하고자 한다.

- [0035] 도 4는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제작 순서도이다.

- [0036] 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법은 기판(110) 위에 중간층 (120)을 형성하고(S400), 중간층(120)에 단위 마이크로 픽셀을 구분하는 트렌치(130)를 형성하고(S410), 마이크로 픽셀의 영역에 PN접합층을 형성하고(S420), PN접합층과 트렌치(130)의 측벽 사이에 확산 방지층(190)을 형성하고(S430), 실리콘 광증배 소자(10)의 상부면에 절연층(160)을 형성하고(S440), 절연층(160)의 상부면에 폴리실리콘 저항층(170)을 형성하고(S450), 폴리실리콘 저항층(170)과 PN접합층을 연결하는 금속 전극(180)을 형성하다(S460).

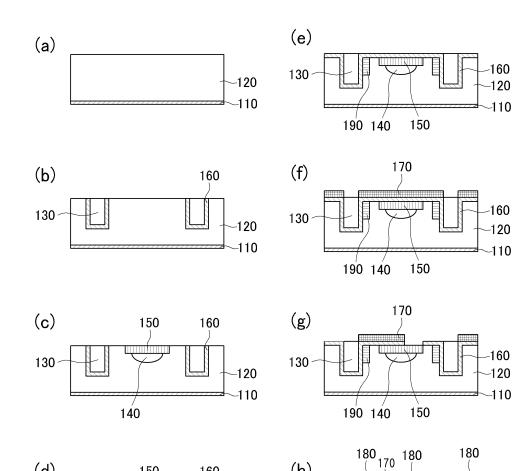

- [0037] 도 5를 참조하여 좀더 자세히 설명하면, 도 5는 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증 배 소자의 제작 공정도이다.

- [0038] 먼저, 도 5의 (a)를 살펴보면, 기판(10) 위에 중간층(120)을 형성한다(S400).

- [0039] 예를 들어, 기판(110)은 p 전도성 타입 또는 n 전도성 타입으로 도핑된 것으로,  $10^{16} \sim 10^{20} \, \mathrm{cm}^{-3}$ 의 고농도로 도핑된 것이거나, 기판(110)에 자연적으로 발생하는 암전류(Dark Current)를 감소시키기 위해  $10^{12} \sim 10^{16} \, \mathrm{cm}^{-3}$ 의 저농도 도핑을 할 수도 있다.

- [0040] 다음으로, 도 5 의 (b)에 도시된 바와 같이, 앞선 단계 S400에서 중간층(120)이 형성된 소자 내에 단위 마이크로 픽셀을 구분하는 트렌치(130)를 형성한다(S410).

- [0041] 이때, 트렌치(130)의 내부를 산화물(0xide)로 채움으로 단위 마이크로 픽셀을 구분하는 트렌치(130)를 형성시킬 수 있다.

- [0042] 한편, 실리콘 광증배 소자(10)는 복수의 마이크로 픽셀의 영역을 포함하며, 단위 마이크로 픽셀 영역은 마이크로 픽셀을 둘러싼 트렌치(130)에 의하여 구분될 수 있다.

- [0043] 또한, 트렌치(130)는 픽셀 격리를 위한 절연충(160)을 함께 형성하여 만들 수도 있다. 이때 사용되는 절연체로 는 이산화규소나 질화규소 등이 사용될 수 있다.

- [0044] 다음으로, 도 5의 (c)에 도시된 바와 같이, 앞선 단계 S410에서 형성된 소자 위에 P형 반도체층(140)과 N형 반도체층(150)을 형성하여, 단위 마이크로 픽셀의 영역에 PN접합층을 형성한다(S420).

- [0045] 즉, PN접합층은 중간층(120)영역에서 형성될 수 있다. 이때의 PN접합층은 이온 주입 공정을 이용하여 형성될 수 있다. 그리고, PN 접합으로 인하여 공핍 영역이 형성된다.

- [0046] 다음으로, 도 5의 (d)에 도시된 바와 같이, 앞선 단계 S420에서 형성된 PN접합층과 트렌치(130)의 측벽 사이에 확산 방지층(190)을 형성한다(S430).

- [0047] 이때의 확산 방지층(190)은 PN영역에 불순물을 주입 후 후속의 열처리 공정에서 불순물이 트렌치(130)까지 확산

되는 것을 방지할 수 있다.

- [0048] 또한, 확산 방지층(190)은 질소(Nitrogen)를 이온 주입하여 형성될 수 있다. 이후, 열처리 공정을 통해 실리 콘과 결합하여 실리콘 질화물(Si<sub>3</sub>N<sub>4</sub>)을 형성시킬 수 있다. 보다 자세한 방법은 후술하는 도 6을 예를 들어 설명 하도록 한다.

- [0049] 다음으로, 도 5의 (e)에 도시된 바와 같이, 앞선 단계 S430에서 형성된 실리콘 광증배 소자(10)의 상부면에 절 연층(160)을 형성한다(S440).

- [0050] 이때의 절연층(160)은 픽셀을 격리시키기 위한 절연체로서 이산화규소나 질화규소 등으로 이루어질 수 있으며, 절연층(160)을 통해 PN 접합층으로 광자가 입사되면 전자-정공 쌍이 발생하여 내부 전자기장에 의하여 가속화되면서 충돌 이온화에 의해 전기적 항복이 일어날 수 있다.

- [0051] 다음으로, 도 5의 (f)에 도시된 바와 같이, 앞선 단계 S440에서 형성된 절연층(160)의 상부면에 폴리실리콘 저항층(170)을 형성할 수 있다(S450).

- [0052] 한편, 실시예에 따라, 절연충(160)의 상부면에 폴리실리콘 저항충(170)을 형성 후, 폴리실리콘 저항충(170)의 상부에 절연충(160)을 추가로 충진하며 형성할 수 있다. 절연충(160)의 중착에 따라 각 마이크로 픽셀에 입사되는 빛 중 반사되는 빛을 줄여 감도를 향상시킬 수 있다.

- [0053] 다음으로, 도 5의 (g)에 도시된 바와 같이, 앞선 단계 S450에서 형성된 폴리실리콘 저항층(170)과 PN접합층을 연결하는 금속 전극(180)을 형성한다(S460).

- [0054] 이때, 금속 전극(180)을 형성하는 단계는 절연충(160)을 통과하여, 폴리실리콘 저항충(170), PN접합충, 및 금속 전극(180)을 서로 전기적으로 연결하는 컨텍홀을 형성하는 단계를 포함할 수 있다.

- [0055] 컨택홀 형성을 위하여 폴리실리콘 저항층(170) 및 절연층(160)의 상부면에 포토레지스트를 적층하고, 마스크를 이용하여 특정 부분을 노광한 후, 의도하는 컨택홀의 형상대로 패턴을 현상하고, 습식 식각 또는 건식 식각을 통해 폴리실리콘 저항층(170)과 절연층(160)을 식각하는 공정을 수행할 수 있다.

- [0056] 즉, 컨텍홀은 폴리실리콘 저항층(170) 및 절연층(160)을 식각하여 PN접합층의 일부를 노출시킴으로써 형성시킬수 있다. 이때, 형성된 컨텍홀 상에 금속 전극(180)이 배치됨으로 폴리실리콘 저항층(170)과 PN접합층이 전기적으로 연결 될 수 있다.

- [0057] 한편, 실시예에 따라, 마이크로 픽셀의 영역에 PN접합층을 형성하는 단계(S420)이전에, 확산 방지층(190)을 먼저 형성할 수도 있다(S430).

- [0058] 도 6을 참조하면, 도 6은 본 발명의 다른 실시예에 따른 실리콘 광증배 소자의 제작 순서도이다.

- [0059] 도 6을 참조하면, 본 발명의 일 실시예에 따른 확산 방지층을 이용한 실리콘 광증배 소자의 제조 방법은 기판 (110) 위에 중간층(120)을 형성하고(S600), 중간층(120)에 단위 마이크로 픽셀을 구분하는 트렌치(130)를 형성하고(S610), 트렌치(130)의 측벽에 인접하도록 확산 방지층(190)을 형성하고(S620), 마이크로 픽셀의 영역에 포함된 확산 방지층(190)들 사이에 PN접합층을 형성하고(S630), 실리콘 광증배 소자(10)의 상부면에 절연층(160)을 형성하고(S640), 절연층(160)의 상부면에 폴리실리콘 저항층(170)을 형성하고(S650), 폴리실리콘 저항층(170)과 PN접합층을 연결하는 금속 전극(180)을 형성한다(S660).

- [0060] 한편, 도 7은 본 발명의 일 실시예에 따른 확산 방지층의 공정과정을 설명하기 위한 도면이다.

- [0061] 도 7을 참조하면, 확산 방지층(190)은 PN영역의 불순물이 트렌치(130)의 측벽까지 확산되는 것을 방지하며, 이로 인해, 트렌치(130) 측벽 영역에서 PN 항복전압(breakdown voltage)이 감소되는 것을 방지할 수 있다.

- [0062] 확산 방지층(190)의 형성을 위하여 PN접합층의 상부면에 포토레지스트(200)를 적층하고, 마스크를 이용하여 특정 부분을 노광한 후, 패턴을 현상한다. 이때의 특정 부분은 PN접합층과 트렌치(130) 측벽의 사이인데, PN접합층과는 떨어져 있고, 트렌치(130) 측벽의 절연층(160)과는 맞닿을 수 있다. 이 후, 질소 이온을 주입한 후, 열처리 공정을 하면 주입된 질소는 중간층(120)내의 실리콘과 결합하여 실리콘 질화물(Si3N4)이 형성되고, 불필요한 포토레지스트(200)는 아세톤(acetone)과 같은 유기용매로 제거하거나, 건식 또는 습식 식각하는 공정을 수행할 수 있다.

- [0063] 한편, 실시예에 따라, 중간층(120)에 단위 마이크로 픽셀을 구분하는 트렌치(130)를 형성하기 전에, 먼저 중간 층(120)에 PN접합층을 형성 후, 중간층(120)에 단위 마이크로 픽셀을 구분하는 트렌치(130)를 형성할 수 있다.

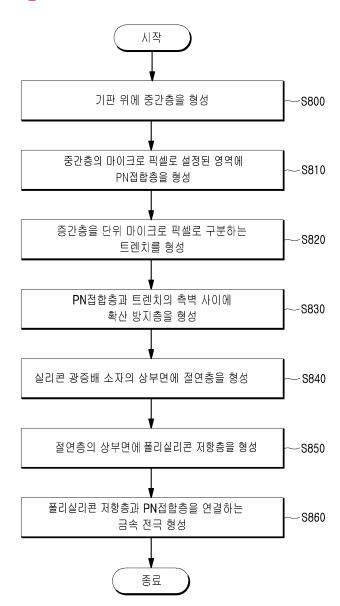

- [0064] 다음으로, 도 8은 본 발명의 다른 실시예에 따른 실리콘 광증배 소자의 제작 순서도이다.

- [0065] 도 8을 참조하면, 본 발명의 다른 실시예에 따른 실리콘 광증배 소자의 제조 방법은 기판(110) 위에 중간층 (120)을 형성하고(S800), 중간층(120)의 마이크로 픽셀로 설정된 영역에 PN접합층을 형성하고(S810), PN접합층이 형성된 중간층을 단위 마이크로 픽셀로 구분하는 트렌치(130)를 형성하고(S820), PN접합층과 트렌치(130)의 측벽 사이에 확산 방지층(190)을 형성하고(S830), 실리콘 광증배 소자(10)의 상부면에 절연층(160)을 형성하고 (S840), 절연층(160)의 상부면에 폴리실리콘 저항층(170)을 형성하고(S850), 폴리실리콘 저항층(170)과 PN접합층을 연결하는 금속 전극(180)을 형성한다(S860).

- [0066] 전술한 본 발명의 설명은 예시를 위한 것이며, 본 발명이 속하는 기술분야의 통상의 지식을 가진 자는 본 발명의 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 쉽게 변형이 가능하다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다. 예를 들어, 단일형으로 설명되어 있는 각 구성 요소는 분산되어 실시될 수도 있으며, 마찬가지로 분산된 것으로 설명되어 있는 구성 요소들도 결합된 형태로 실시될 수 있다.

- [0067] 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 균등 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

## 부호의 설명

[0068] 10: 실리콘 광증배 소자

110: 기판

120: 중간층

130: 트렌치

140: P형 반도체층

150: N형 반도체층

160: 절연층

170: 폴리실리콘 저항층

180: 금속 전극

190: 확산 방지층

200: 포토레지스트

## 도면3a

## 도면3b

160

120

~110

# 도면5

(d)

130

150

190 140

160

120

-110

(h)

130

190 140

150