(19) **日本国特許庁(JP)**

# (12) 特許公報(**B2)**

(11)特許番号

特許第4082507号 (P4082507)

(45) 発行日 平成20年4月30日 (2008.4.30)

(24) 登録日 平成20年2月22日(2008.2.22)

(51) Int.Cl. F 1

**HO3L 7/089 (2006.01)** HO3L 7/08 D **HO3L 7/083 (2006.01)** HO3L 7/08 E

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2003-277931 (P2003-277931) (22) 出願日 平成15年7月22日 (2003.7.22)

(65) 公開番号 特開2005-45562 (P2005-45562A)

(43) 公開日 平成17年2月17日 (2005. 2. 17) 審査請求日 平成17年8月10日 (2005. 8. 10) ||(73)特許権者 000005049 ||シャープ株式会社

ンヤーノ休式芸任

大阪府大阪市阿倍野区長池町22番22号

||(74)代理人 100078282

弁理士 山本 秀策

(74)代理人 100062409

弁理士 安村 高明

(74)代理人 100107489

弁理士 大塩 竹志

(72)発明者 アルベルト アダン

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

審査官 甲斐 哲雄

最終頁に続く

(54) 【発明の名称】位相同期回路

### (57)【特許請求の範囲】

## 【請求項1】

基準クロック信号REFとクロック信号CLKとを受け取り、<u>該</u>基準クロック信号REFの位相と<u>該</u>クロック信号CLKの位相とを比較することにより、<u>該</u>基準クロック信号REFと<u>該</u>クロック信号CLKとの位相差 に応じた位相差信号を出力する位相比較器と

前記位相差信号に応じた出力電流Ⅰ。を出力するチャージポンプ回路と、

前記出力電流Ⅰ。を出力電圧に変換するループフィルタと、

前記出力電圧I。に応じた周波数 f。を有する信号をクロック信号 CLK 'として出力する電圧制御発振器と、

<u>前記</u>クロック信号 C L K 'の周波数 f 。を N ( N は任意の自然数)で除算することによって得られる周波数 f 。 / N を有する信号をクロック信号 C L K として前記位相比較器に供給する 1 / N 分周器と

を備えた位相同期回路であって、

前記位相比較器と前記チャージポンプ回路とは、 $I_0$  特性において、 $K_{p,2} > K_{p,1}$  を満たすように構成されており、

前記位相比較器は、前記位相差信号としてUP信号とDN信号とを前記チャージポンプ

# 回路に出力し、

前記位相比較器は、

前記位相差 に相当する遅延時間  $T_p$  と、該遅延時間  $T_p$  が小さくなるにつれて該遅延時間  $T_p$  よりも大きくなるか等しいように可変の遅延時間  $T_p$  とを決定する手段と、

前記基準クロック信号REFの位相より前記クロック信号CLKの位相が遅れている場合には、前記位相差 に相当する遅延時間Tpと前記可変の遅延時間Tdとの和に等しいパルス幅を有するUP信号を生成する手段と、

前記基準クロック信号REFの位相より前記クロック信号CLKの位相が進んでいる場合には、前記位相差 に相当する遅延時間Tpと前記可変の遅延時間Tgとの和に等しいパルス幅を有するDN信号を生成する手段と

を含む、位相同期回路。

#### 【請求項2】

前記UP信号を生成する手段は、

前記基準クロック信号REFを受け取り、<u>該</u>基準クロック信号REFの立ち上がりエッジに応答して<u>前記</u>UP信号を立ち上げ、リセット信号Rに応答して<u>前記</u>UP信号を立ち下げる第1のフリップフロップを含み、

前記DN信号を生成する手段は、

前記クロック信号 CLKを受け取り、<u>該</u>クロック信号 CLKの立ち上がりエッジに応答して<u>前記</u> DN信号を立ち上げ、リセット信号 Rに応答して<u>前記</u> DN信号を立ち下げる第 2のフリップフロップを含み、

前記可変の遅延時間  $T_d$ を決定する手段は、前記第1のフリップフロップと前記第2のフリップフロップとに入力されるリセット信号Rの遅延時間を可変に調整可能な可変遅延回路を含む、請求項1に記載の位相同期回路。

#### 【請求項3】

前記可変遅延回路は、

前記リセット信号を遅延させるように動作する可変抵抗と、

前記 UP信号のパルス幅と<u>前記</u> DN信号のパルス幅とに応じて前記可変抵抗の値を制御する可変抵抗制御部と

を含む、請求項2に記載の位相同期回路。

# 【請求項4】

前記可変抵抗は、<u>前記UP信号および前記DN信号のそれぞれが入力される一対の</u>MOSトランジスタを含み、

前記可変抵抗制御部は、前記各MOSトランジスタのチャンネル抵抗の値を制御することにより、前記可変抵抗の値を制御する、請求項3に記載の位相同期回路。

## 【請求項5】

前記可変抵抗制御部は、前記 U P 信号および前記 D N 信号がそれぞれ入力される N O R ゲートと、該 N O R ゲートの出力が与えられる第 1 インバータと、該第 1 インバータの出力が与えられる第 2 インバータとを備え、該第 1 インバータおよび該第 2 インバータの出力が前記各 M O S トランジスタのゲートに与えられる請求項 4 に記載の位相同期回路。

### 【請求項6】

前記MOSトランジスタのゲートは電圧 $V_X$ によって制御され、電圧 $V_X$ は、

#### 【数1】

$V_X = \begin{cases} V_{X0} & \text{ただし}, (UP + DN) \leq V_{X0} \text{ の場合} \\ \\ V_{X0} + NOT(\overline{UP + DN}) \text{ ただし}, (UP + DN) > V_{X0} \text{ の場合} \end{cases}$

10

20

30

## によって表され、

ここで、UPは前記UP信号の電圧値を示し、DNは前記DN信号の電圧値を示し、Vx。は前記第2インバータの論理が反転する電圧(アナログ値)を示し、Vx。と比較される(UP+DN)は前記UP信号の電圧値(デジタル値)と前記DN信号の電圧値(デジタル値)とをアナログ値として加算したものを示し、NOTバー(UP+DN)は前記NORゲートの論理演算を示すアナログ値である、請求項5に記載の位相同期回路。

## 【発明の詳細な説明】

### 【技術分野】

[0001]

本発明は、位相同期回路に関する。特に、本発明は、通信デバイス中の周波数シンセサイザーとして好適に使用される位相同期回路に関する。

#### 【背景技術】

## [0002]

従来、2つのクロック信号を同期させる回路として位相同期回路(Phase Loc ked Loop;PLL)が知られている。

### [0003]

非特許文献1は、通信デバイスに好適に使用される代表的な位相同期回路を記載している。

[0004]

特許文献 2 は、非リニアな I 。 - 特性を実現する位相同期回路を記載している。

#### [0005]

特許文献 3 は、リニアな I 。 - 特性を実現する位相同期回路を記載している。

[0006]

特許文献4は、UP信号のパルス幅とDN信号のパルス幅とを制御可能な位相同期回路を記載している。

【非特許文献1】S.Lo et al., "A 1.8V/3.5mA 1.1GHz/300MHz CMOS Dual PLL Frequency Synthesizer IC for RF Communications", Proc.IEEE 1998 Custom Integrated Circuits Conference

【特許文献1】特開平8-307258号公報

【特許文献2】特開平6-85664号公報

【特許文献3】特開2000-349626号公報

【発明の開示】

【発明が解決しようとする課題】

# [0007]

しかし、いずれの従来技術においても、ロック状態における位相ノイズを低減すること は考慮されていなかった。

### [00008]

本発明は、上記課題に鑑みてなされたものであり、ロック状態における位相ノイズを低減することが可能な位相同期回路を提供することを目的とする。

【課題を解決するための手段】

# [0009]

本発明の位相同期回路は、基準クロック信号REFとクロック信号CLKとを受け取り、<u>該</u>基準クロック信号REFの位相と<u>該</u>クロック信号CLKの位相とを比較することにより、<u>該</u>基準クロック信号REFと<u>該</u>クロック信号CLKとの位相差 に応じた位相差信号を出力する位相比較器と、前記位相差信号に応じた出力電流 I。を出力するチャージポンプ回路と、<u>前記</u>出力電流 I。を出力電圧に変換するループフィルタと、前記出力電圧 I。に応じた周波数 f。を有する信号をクロック信号CLK,として出力する電圧制御発振

10

20

30

40

20

30

40

器と、前記クロック信号CLK'の周波数f。をN(Nは任意の自然数)で除算すること によって得られる周波数 f。 / Nを有する信号をクロック信号 CLKとして前記位相比較 器に供給する1/N分周器とを備えた位相同期回路であって、前記位相比較器と前記チャ ージポンプ回路とは、 $I_0$  - 特性において、 $K_{p,2} > K_{p,1}$  を満たすように構成され 。の場合における傾き  $K_p$  を示し、傾き  $K_p$  は、  $K_p$  = d I 。 / d によって定義されており、。は、所定の位相誤差を示す定数であり、前記位相比較器 は、前記位相差信号としてUP信号とDN信号とを前記チャージポンプ回路に出力し、前 記位相比較器は、前記位相差 に相当する遅延時間Tっと、該遅延時間Tっが小さくな るにつれて該遅延時間Tっよりも大きくなるか等しいように可変の遅延時間Tっとを決定 する手段と、前記基準クロック信号REFの位相より前記クロック信号CLKの位相が遅 れている場合には、前記位相差 に相当する遅延時間T。と前記可変の遅延時間T。と の和に等しいパルス幅を有するUP信号を生成する手段と、前記基準クロック信号REF の位相より前記クロック信号 С L K の位相が進んでいる場合には、前記位相差 に相当 する遅延時間T。と前記可変の遅延時間T。との和に等しいパルス幅を有するDN信号を 生成する手段とを含み、これにより上記目的が達成される。

#### [0010]

前記UP信号を生成する手段は、前記基準クロック信号REFを受け取り、該基準クロック信号REFの立ち上がリエッジに応答して前記UP信号を立ち上げ、リセット信号R に応答して前記UP信号を立ち下げる第1のフリップフロップを含み、前記DN信号を生成する手段は、前記クロック信号CLKを受け取り、該クロック信号CLKの立ち上がリエッジに応答して前記DN信号を立ち上げ、リセット信号Rに応答して前記DN信号を立ち下げる第2のフリップフロップを含み、前記可変の遅延時間Tdを決定する手段は、前記第1のフリップフロップと前記第2のフリップフロップとに入力されるリセット信号Rの遅延時間を可変に調整可能な可変遅延回路を含んでいてもよい。

## [0011]

前記可変遅延回路は、前記リセット信号を遅延させるように動作する可変抵抗と、前記 U P信号のパルス幅と前記 D N 信号のパルス幅とに応じて前記可変抵抗の値を制御する可 変抵抗制御部とを含んでいてもよい。

#### [0012]

前記可変抵抗は、前記UP信号および前記DN信号のそれぞれが入力される一対のMO Sトランジスタを含み、前記可変抵抗制御部は、前記各MOSトランジスタのチャンネル 抵抗の値を制御することにより、前記可変抵抗の値を制御されてもよい。

### [0013]

前記可変抵抗制御部は、前記UP信号および前記DN信号がそれぞれ入力されるNOR ゲートと、該NORゲートの出力が与えられる第1インバータと、該第1インバータの出 力が与えられる第2インバータとを備え、該第1インバータおよび該第2インバータの出 力が前記各MOSトランジスタのゲートに与えられてもよい。

# [0014]

前記MOSトランジスタのゲートは電圧Vxによって制御され、電圧Vxは、

### 【数2】

$$V_X = \begin{cases} V_{X0} & \text{ただし}, (UP + DN) \leq V_{X0} \text{ の場合} \\ \\ V_{X0} + NOT(\overline{UP + DN}) \text{ ただし}, (UP + DN) > V_{X0} \text{ の場合} \end{cases}$$

# によって表されてもよく、

10

ここで、UPは前記UP信号の電圧値を示し、DNは前記DN信号の電圧値を示し、Vx。は前記第 2 インバータの論理が反転する電圧(アナログ値)を示し、Vxのと比較される(UP+DN)は前記UP信号の電圧値(デジタル値)と前記DN信号の電圧値(デジタル値)とをアナログ値として加算したものを示し、NOTバー(UP+DN)は前記NORゲートの論理演算を示すアナログ値である。

## 【発明の効果】

## [0016]

本発明によれば、ロック状態における位相ノイズを低減することが可能な位相同期回路 を提供することができる。

20

【発明を実施するための最良の形態】

#### [0017]

以下、図面を参照しながら本発明の実施の形態を説明する。

#### [0018]

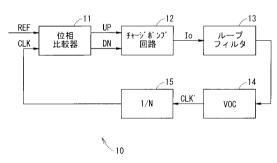

図1は、本発明の実施の形態の位相同期回路10の構成の一例を示す。

# [0019]

位相同期回路10は、基準クロック信号REFの位相とクロック信号CLKの位相とを一致させるように動作する。基準クロック信号REFの位相とクロック信号CLKの位相とが一致すると同期が確定する。一般に、同期が確定した状態を位相同期回路10がロックした状態という。

30

## [0020]

位相同期回路10は、位相比較器11と、チャージポンプ回路12と、ループフィルタ 13と、電圧制御発振器(Voltage Controlled Oscilator ;以下、VCOという)14と、1/N分周器15とを含む。

# [0021]

位相比較器 1 1 は、基準クロック信号 R E F とクロック信号 C L K とを受け取り、基準クロック信号 R E F の位相とクロック信号 C L K の位相とを比較することにより、基準クロック信号 R E F とクロック信号 C L K との位相差 に応じた位相差信号をチャージポンプ回路 1 2 に出力する。

#### [0022]

40

位相比較器11は、基準クロック信号REFの位相よりクロック信号CLKの位相が遅れている場合には位相差信号としてUP信号を出力し、基準クロック信号REFの位相よりクロック信号CLKの位相が進んでいる場合には位相差信号としてDN信号を出力する。UP信号のパルス幅とDN信号のパルス幅とは、位相差に応じて決定される。

#### [0023]

チャージポンプ回路 1 2 は、位相差信号(UP信号、DN信号)に応じた出力電流  $I_o$ をループフィルタ 1 3 に出力する。

### [0024]

ループフィルタ13は、チャージポンプ回路12から出力された出力電流I。を出力電圧に変換する。このような変換は、例えば、出力電流I。を積分し、低域通過フィルタで

20

30

40

不要な高周波成分や雑音を除去することによって行われる。

#### [0025]

VCO14は、ループフィルタ13から出力された出力電圧に応じた周波数 f。を有する信号をクロック信号 CLK'として出力する。

# [0026]

1/N分周器 1.5 は、クロック信号 CLK の周波数 f 。を N ( N は任意の自然数)で除算することによって得られる周波数 f 。 /N を有する信号をクロック信号 CLK として位相比較器 1.1 に供給する。

## [0027]

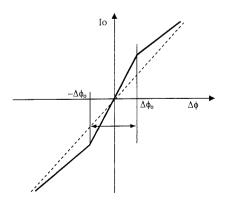

図 2 は、本発明の位相同期回路 1 0 における位相比較器 - チャージポンプ回路特性(I。 - 特性)の一例を示す。図 2 において、I。 - 特性は、実線で示されている。縦軸 I。はチャージポンプ回路 1 2 から出力される出力電流を示す。横軸 は、位相比較器 1 1 によって検出される位相差を示す。

## [0028]

図 2 に示される  $I_0$  - 特性は、 | 。の場合における傾き  $K_p$  が、 | | 。の場合における傾き  $K_p$  より大きいことによって特徴づけられる。ここで、傾き  $K_p$  は、  $K_p$  = d  $I_o$  / d によって定義される。 。は、所定の位相誤差を示す定数である。

# [0029]

#### [0030]

傾き  $K_{p,1}$ 、  $K_{p,2}$  の値と、傾きが  $K_{p,2}$  となる の範囲(すなわち、 - 。。)とは、同期が不安定になったり、寄生振動により誤ってロックがはずれてしまわないように適切に設計される。

### [0031]

位相同期回路10がロック状態にある場合(すなわち、 0の場合)には、傾き  $K_p$ が大きいことはループゲインが高いことと等価であるから、バンド幅が広いことに対応する。従って、 0の場合における傾き  $K_p$ が大きいと、ロック状態におけるノイズ伝達係数が低減されることになる。その結果、ロック状態における位相ノイズが低減されることになる。位相同期回路10による位相ノイズの低減効果については、後述する。

# [0032]

なお、図 2 に示される例では、 $K_{p,1}$ 、 $K_{p,2}$  は定数である。しかし、本発明はこれに限定されない。 $K_{p,1}$ 、 $K_{p,2}$  の少なくとも一方が変数(例えば、 の関数)であってもよい。 $K_{p,1}$ 、 $K_{p,2}$ が定数であるか変数であるかによらず、任意の に対して $K_{p,2}$  という関係が成り立つ限り、そのような  $I_{p,1}$  。 特性を有する任意の位相同期回路は本発明の範囲に含まれるというべきである。

### [0033]

図 2 に示される I。 - 特性は、例えば、位相比較器 1 1 が、図 3 に示されるパルス幅を有する U P 信号、 D N 信号を生成し、生成された U P 信号、 D N 信号をチャージポンプ 1 2 に出力することによって実現され得る。

#### [0034]

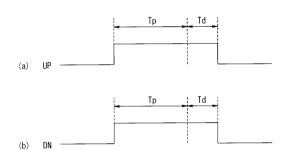

図3は、位相比較器11によって生成されるUP信号、DN信号の波形の一例を示す。

#### [ 0 0 3 5 ]

基準クロック信号 R E F の位相よりクロック信号 C L K の位相が遅れている場合には、位相比較器 1 1 は、位相差 に相当する遅延時間 T  $_p$  と可変の遅延時間 T  $_d$  との和に等しいパルス幅を有する U P 信号を生成する(図 3 ( a ))。基準クロック信号 R E F の位相よりクロック信号 C L K の位相が進んでいる場合には、位相比較器 1 1 は、位相差に相当する遅延時間 T  $_p$  と可変の遅延時間 T  $_d$  との和に等しいパルス幅を有する D N 信号を生成する(図 3 ( b ))。ここで、位相比較器 1 1 は、位相差 に相当する遅延時間

Tpが小さくなるにつれて可変の遅延時間Tdが大きくなるか等しくなるように可変の遅延時間Tdを決定する。可変の遅延時間Tdは、例えば、位相差 に相当する遅延時間Tbに反比例するように決定される。

### [0036]

このように可変の遅延時間  $T_d$ を決定することにより、位相差が 0に近づくにつれて(すなわち、位相同期回路 1 0 がロック状態に近づくにつれて)、可変の遅延時間  $T_d$  は大きくなるか等しくなる。これにより、=0 の近傍領域における傾き  $K_p$  をその近傍領域以外の領域における傾き  $K_p$  よりも大きくすることができる。=0 の近傍領域では、可変の遅延時間  $T_d$  に相当する分だけ出力電流  $T_o$  が増加することになるからである。

[0037]

図3に示されるUP信号は、例えば、基準クロック信号REFの立ち上がりエッジに応答してUP信号を立ち上げ、位相差に相当する遅延時間  $T_p$ の経過後、可変の遅延時間  $T_d$  に相当する分だけUP信号の立ち下りタイミングを遅延させることによって生成され得る。

[0038]

図3に示されるDN信号は、例えば、クロック信号CLKの立ち上がりエッジに応答してDN信号を立ち上げ、位相差 に相当する遅延時間T<sub>p</sub>の経過後、可変の遅延時間T<sub>d</sub>に相当する分だけDN信号の立ち下りタイミングを遅延させることによって生成され得る。

[0039]

なお、図 3 に示される例では、位相比較器 1 1 によって生成されるUP信号、DN信号のパルス幅を調整することにより、 $K_{p2} > K_{p1}$  という関係を満たすことを説明した。しかし、本発明は、これに限定されない。 $K_{p2} > K_{p1}$  という関係を満たすように構成された位相比較器 1 1 とチャージポンプ回路 1 2 とを含む限り、任意の位相同期回路 1 0 は本発明の範囲に含まれるというべきである。

[0040]

以下、本発明の位相同期回路のインプリメンテーションの一例として、CMOS技術を用いてインプリメントされた位相同期回路の構成を説明する。しかし、本発明はこれに限定されない。本発明の位相同期回路は、半導体集積回路に関する任意のプロセスを用いてインプリメントされ得る。

[0041]

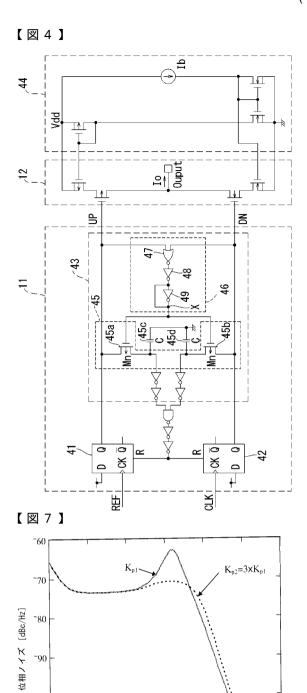

図 4 は、図 3 に示される位相比較器 1 1、チャージポンプ回路 1 2 の具体的な回路構成の例を示す。図 4 に示される回路構成は、図 2 に示される位相比較器 - チャージポンプ回路特性( $I_0$  - 特性)を実現する。

[0042]

位相比較器 1 1 は、フリップフロップ 4 1 と、フリップフロップ 4 2 と、可変遅延回路 4 3 とを含む。フリップフロップ 4 1 、 4 2 は、例えば、 D タイプのフリップフロップである。

[0043]

フリップフロップ41は、基準クロック信号REFを受け取り、基準クロック信号REFの立ち上がリエッジに応答してUP信号を立ち上げ、リセット信号Rに応答してUP信号を立ち下げる。

[0044]

フリップフロップ 4 2 は、クロック信号 C L K を受け取り、クロック信号 C L K の立ち上がりエッジに応答して D N 信号を立ち上げ、リセット信号 R に応答して D N 信号を立ち下げる。

[0045]

可変遅延回路43は、リセット信号Rの遅延時間(リセットパス遅延)を可変に調整可能なように構成されている。リセット信号Rは、フリップフロップ41、42のリセット

10

20

30

40

端子に入力される。

# [0046]

可変遅延回路43は、リセット信号Rを遅延させるように動作する可変抵抗45と、UP信号のパルス幅とDN信号のパルス幅とに応じて可変抵抗45の値を制御する可変抵抗制御部46とを含む。

## [0047]

リセット信号Rの遅延は、例えば、RC回路によって実現され得る。図4に示される例では、RC回路は、NMOSトランジスタMn(45a、45b)とキャパシタC(45c、45d)とによって実現されている。可変抵抗制御部46は、NMOSトランジスタMn(45a、45b)のゲート電圧を制御することにより、NMOSトランジスタMn(45a、45b)のチャンネル抵抗の値を可変に制御する。この場合、NMOSトランジスタMn(45a、45b)のチャンネル抵抗が可変抵抗45として作用する。

#### [0048]

図4に示される例では、可変抵抗制御部46は、論理ゲート47、48と、インバータ 49とを含む。

### [0049]

UP信号とDN信号とは、論理ゲート47、48を用いてセンシングされる。論理ゲート48の出力は、ノードXに接続されている。ノードXの電圧 $V_X$ により、PMOSトランジスタMn(45a、45b)のゲートが制御される。ノードXの平均電圧は、UP信号のパルス幅またはDN信号のパルス幅が大きくなるにつれて増加する。

#### [0050]

ノード X の電圧  $V_X$  は、例えば、(数3)によって表される。

[0051]

#### 【数3】

$$V_X = \begin{cases} V_{X0} & \text{ただし}, (UP + DN) \leq V_{X0} \text{ の場合} \\ \\ V_{X0} + NOT\overline{(UP + DN)} \text{ ただし}, (UP + DN) > V_{X0} \text{ の場合} \end{cases}$$

30

(数 3 )において、U P は U P 信号の電圧値を示し、D N は D N 信号の電圧値を示す。 V  $_{\times}$   $_{0}$  と比較される(U P + D N)は、U P 信号の電圧値(デジタル値)とD N 信号の電圧値(デジタル値)とをアナログ値として加算したものを示す(V  $_{\times}$  、 V  $_{\times}$   $_{0}$  がアナログ信号を示すため)。N O T  $\underline{\mathit{I}'-}$  (U P + D N)は N O R  $\underline{\mathit{V}'-}$  トの 論理演算を  $\underline{\mathit{r}}$   $\underline$

# [0052]

インバータ49は、 $V_x$ がゼロとならないようにノードX上の基準電圧 $V_x$ 。を設定するために使用される。インバータ49を使用することにより、 $V_x$ 。 $< V_x < V_d$  。 とすることができる。ここで、 $V_x$ 。は、インバータ49の<u>論理が反転する電圧(アナログ値</u>)を示し、 $V_d$  。は、バイアス回路44から供給される電源電圧を示す。

#### [0053]

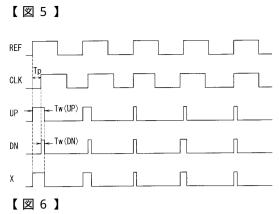

図 5 は、位相同期回路 1 0 における主要な信号の波形の例を示す。図 5 において、R E F は基準クロック信号の波形を示し、C L K はクロック信号の波形を示し、U P はU P 信号の波形を示し、D N は D N 信号の波形を示し、X は J ード X 上の電圧 V  $_{X}$  の波形を示す

50

40

10

20

30

40

50

[0054]

図5は、基準クロック信号REFの位相よりクロック信号CLKの位相が遅延時間Tpに相当する位相差 だけ遅れている場合を示している。この場合、位相比較器11は、基準クロック信号REFの立ち上がりエッジに応答してUP信号がローレベルからハイレベルに変化し、かつ、リセット信号Rに応答してUP信号がハイレベルからローレベルに変化するようにUP信号を生成し、クロック信号CKLの立ち上がりエッジに応答してDN信号がローレベルからハイレベルに変化し、かつ、リセット信号Rに応答してDN信号がハイレベルからローレベルに変化するようにDN信号を生成する。

[0055]

図 5 に示される例では、U P 信号のパルス幅 T  $_w$  (U P ) は、遅延時間 T  $_p$  と D N 信号のパルス幅 T  $_w$  (D N ) との和として決定される(すなわち、 T  $_w$  (U P ) = T  $_p$  + T  $_w$  (D N ) )。

[0056]

基準クロック信号 R E F の位相とクロック信号 C L K の位相とが一致すると、位相同期回路 1 0 はロック状態になる。ロック状態では、U P 信号とD N 信号とは一致し、U P 信号のパルス幅 T  $_w$  (DN)とは、最小のパルス幅  $_w$  に等しくなる(すなわち、T  $_w$  (U P) = T  $_w$  (DN) =  $_w$ )。

[0057]

図 5 に示される例では、D N 信号のパルス幅  $_w$  ( D N ) は、最小のパルス幅  $_w$  と可変のパルス幅  $_d$   $_n$  との和として決定される(すなわち、 T  $_w$  ( D N ) =  $_w$  +  $_d$   $_n$  )。ここで、  $_d$   $_n$  は、U P 信号のパルス幅 T  $_w$  ( U P ) に依存して可変である。

[0058]

可変のパルス幅 dnは、(数4)によって表される。

[0059]

【数4】

$$\delta_{dn} = k \times C \times R_{MOS}, \qquad R_{MOS} \cong \frac{1}{\beta_{MOS} \times (V_X - V_{th})}$$

ここで、

k:比例定数、

C: コンデンサ45 c、45 dの容量

RMOS:可変抵抗45の抵抗値

MOS: MOSトランジスタ45 a、45 bのコンダクタンスパラメータ(定数)

**V** <sub>x</sub> : ノード X の電圧

V<sub>+h</sub>: MOSトランジスタ45a、45bのしきい値電圧

なお、基準クロック信号REFの位相よりクロック信号CLKの位相が遅延時間Tpに相当する位相差 だけ進んでいる場合にも、位相比較器11は、基準クロック信号REFの位相よりクロック信号CLKの位相が遅延時間Tpに相当する位相差 だけ遅れている場合と同様にしてUP信号とDN信号とを生成する。すなわち、位相比較器11は、基準クロック信号REFの立ち上がリエッジに応答してUP信号がローレベルからハイレベルに変化し、かつ、リセット信号Rに応答してUP信号がハイレベルからローレベルに変化するようにUP信号を生成し、クロック信号CKLの立ち上がリエッジに応答してDN信号がローレベルからハイレベルに変化し、かつ、リセット信号Rに応答してDN信号がハイレベルからローレベルに変化するようにDN信号を生成する。

[0060]

この場合、 D N 信号のパルス幅 T  $_w$  ( D N ) は、遅延時間 T  $_p$  と U P 信号のパルス幅 T  $_w$  ( U P ) との和として決定される(すなわち、 T  $_w$  ( D N ) = T  $_p$  + T  $_w$  ( U P ) )。 U P 信号のパルス幅 T  $_w$  ( U P ) は、最小のパルス幅  $_w$  と可変のパルス幅  $_d$   $_n$  との和として決定される(すなわち、 T  $_w$  ( U P ) =  $_w$  +  $_d$   $_n$  )。

20

30

50

[0061]

このように、本実施の形態では、位相比較器11から出力される位相差信号(UP信号、DN信号)のタイミングを調整することによって 0の場合における大きな傾きKpを実現する。このアプローチによれば、ロック状態でのチャージポンプ電流を増加させる必要がないため、電力消費の増加がない。従って、位相同期回路10は、低消費電力が要求されるシステム(例えば、携帯バッテリで動作するシステム)に好適に使用され得る

[0062]

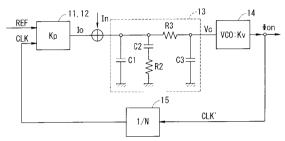

図6は、位相同期回路10のモデルを示す。このモデルを用いて、位相ノイズが低減されることを説明する。

[0063]

図 6 に示されるモデルでは、位相比較器 1 1 およびチャージポンプ回路 1 2 の全ノイズは、チャージポンプ回路 1 2 の出力での電流ノイズジェネレータ  $1_n$  によって表されるものと仮定している。位相比較器 1 1 およびチャージポンプ回路 1 2 の組み合わせによるゲインを  $K_n$  (すなわち、 $K_n$  = d  $I_n$  / d ) とする。

[0064]

電流ノイズジェネレータ  $1_n$  から V C O 1 4 の出力までの伝達関数は、(数 5 )によって表される。

[0065]

【数5】

$F(s) \cdot \frac{K_{\nu}}{}$

$$\frac{\Phi_{on}}{I_n} = \frac{F(s) \cdot \frac{K_v}{s}}{1 + \frac{K_p F(s) K_v}{N \cdot s}}$$

ここで、

。。:VCO14の出力上のノイズ

In:入力ノイズ

F ( s ) / s : ループフィルタ 1 3 の伝達関数

K : V C O 1 4 のゲイン

$K_p = d I_o / d$

N:分周比

(数5)において 0(s=j)とすると、(数5)は(数6)に示されるように 変形される。

[0066]

【数6】

$$\frac{\Phi_{on}}{I_n} \cong \frac{N}{K_p}$$

(数 6 ) から、 0 の場合における傾き  $K_p$  が大きいことは、ロック状態における位相ノイズの低減に有効であることがわかる。

[0067]

図 7 は、位相同期回路 1 0 による位相ノイズの低減効果を示す。図 7 では、  $K_{p,2}=3 \times K_{p,1}$  の場合を示す。図 7 から、ループバンドのエッジの位相ノイズが低減されることがわかる。

### 【図面の簡単な説明】

- [0068]

- 【図1】本発明の実施の形態の位相同期回路10の構成の一例を示す図

- 【図2】本発明の位相同期回路10における位相比較器-チャージポンプ回路特性(I。 特性)の一例を示す図

- 【図3】位相比較器11によって生成されるUP信号、DN信号の波形の一例を示す図

- 【図4】図3に示される位相比較器11、チャージポンプ回路12の具体的な回路構成の例を示す図

【図3】

- 【図5】位相同期回路10における主要な信号の波形の例を示す図

- 【図6】位相同期回路10のモデルを示す図

- 【図7】位相同期回路10による位相ノイズの低減効果を示す図

## 【符号の説明】

- [0069]

- 10 位相同期回路

- 11 位相比較器

- 12 チャージポンプ回路

- 13 ループフィルタ

- 14 V C O

- 15 1/N分周器

# 【図1】

# 【図2】

$10^{6}$

$10^4$

周波数 [GHz]

$10^5$

$10^7$

-100

-110

-120

10

# フロントページの続き

(56)参考文献 特開2001-077687(JP,A)

特開2001-230668(JP,A)

特開2000-059212(JP,A)

(58)調査した分野(Int.CI., DB名)

H03L 7/06-7/23