# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.5(45) 공고일자1990년07월30일HO3M 1/38(11) 공고번호90-005464

(21) 출원번호 특1987-0700503 (65) 공개번호 특1988-0700550 (22) 출원일자 1987년06월13일 (43) 공개일자 1988년03월15일 (86) 국제출원번호 PCT/US 86/001882 (87) 국제공개번호 W0 87/02530 (86) 국제출원일자 1986년09월15일 (87) 국제공개일자 1987년04월23일

(30) 우선권주장 787831 1985년10월15일 미국(US)

(71) 출원인 휴우즈 에어크라프트 캄파니 에이. 더블유. 카람벨라스

미합중국 90045-0066 캘리포니아주 로스앤젤리스 휴우즈 테라스 7200

(72) 발명자 뉴콤, 러셀 알.

미합중국 92633 캘리포니아주 플러톤 케일 울티모 2206

블랙, 윌리엄 씨.

미합중국 52403 아이오워주 씨더 래피드즈 컨트리 클럽 파크웨이 2131

(74) 대리인 장수길, 이세진, 최종왕

#### 심사관: 이택수 (책자공보 제1967호)

# (54) 언트림된 12비트 단조 전 용량성 아날로그/디지탈 변환기

#### 요약

내용 없음.

#### 대표도

### 도1

### 명세서

[발명의 명칭]

언트림된 12비트 단조 전 용량성 아날로그/디지탈 변환기

[도면의 간단한 설명]

이하, 첨부 도면을 참조하여 본 발명의 장점 및 특징에 대해서 상세히 기술하겠다.

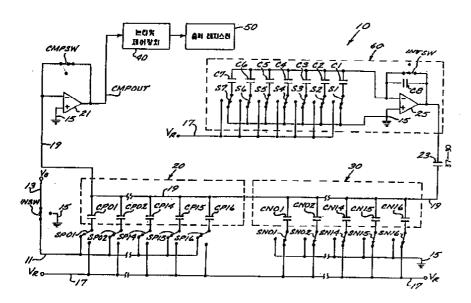

제1도는 기술한 아날로그/디지탈(A/D)변환기의 개략도이다.

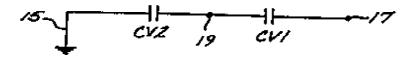

제2도는 제1도의 A/D 변환기의 캐패시터 그룹의 개략도이다.

제3도는 제1도의 A/D 변환기의 병렬 캐패시터의 가능한 스위치 상태를 도시한 상태도이다.

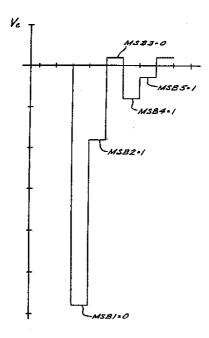

제4도는 최상위 비트를 결정하기 위해 병렬 캐패시터의 선택적 스위칭에 응답하여 변할 때, 제1도의 A/D 변환기의 샘플 전압을 특정한 아날로그 입력 전압에 대해 도시한 그래프이다.

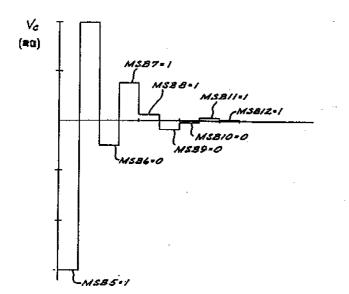

제5도는 최하위 비트를 결정하기 위한 이진 가중 캐패시터의 스위칭에 응답하여 변할 때, 제1도의 A/D 변환기의 샘플 전압을 제4도의 예에 대해 도시한 그래프이다.

[발명의 상세한 설명]

[발명의 배경]

본 발명은 주로 전 용량성(all capacifive) 아날로그/디지탈(A/D) 변환기에 관한 것으로, 특히 거의 동일한 값의 선택적으로 스위치된 병렬 캐패시터들을 사용하는 전 용량성 A/D 변환기에 관한 것이다.

A/D 변환기는 아날로그 변환기에 의해 제공된 것과 같은 아날로그 신호들이 디지털적으로 처리되는 시스템내에 사용된다. 특정한 A/D 변환기의 분해능(resolution)은 출력 비트수에 따라 증가하고, 이 분해능은 특정한 응용의 요구된 동적 범위에 따라 변하게 된다.

지금까지, 정확한 고 분해능 A/D 변환기가 요구되어 왔지만, 이러한 요구를 충족시키기 위한 시도들은 만족스러운 것이 아니었다. 이진 가중(binary weighted)소자들을 사용하는 공지된 A/D 변환기 기술로는, 분해능을 증가시키면서 단조성(monotonicity)을 유지하기란 점점 더 어려워진다. 특히, 비

트수가 증가할 때, 정합 회로 수자들의 필요조건은 더욱 엄격하게 된다. 이진 가중 소자 사용의 일 례는 1978.12.12자 그레이(Gray)등에게 허여된 미합중국 특허 제4,129,863호에 기술되어 있는데, 이특허는 이진 가중 캐패시터를 사용한다.

모놀리드식(monolithic)집적 회로로, 오정합을 감소시키기 위해 정밀 비율 소자들의 크기를 증가시 킴으로써 엄격한 정합 필요조건이 어드레스될 수 있다. 그러나, 소자 크기를 증가시키면 생산률이 감소된다.

엄격한 정합 필요조건을 충족시키기 위한 다른 해결 방법은 정밀 박막 정밀 저항기 및 온-칩 레이저 트리밍(on-chip laser timming)을 사용하는 것이다. 그러나, 레이저 트리밍은 더욱 복잡해지는 것외에, 저항기의 온도 트랙킹 특성에 악영향을 미칠 수 있다.

정합 필요조건을 처리하기 위한 특정한 해결 방법은 LEEE Journal of solid State Physics, 1979년 12월 제 sc-14권, 920-926페이지에 포토우히(Fotouhi) 등이 쓴 'MOS/LSI 내의 고 분해능 A/D 변환 (High-Resolution A/D conversion in MOS/LSI)'이란 명칭의 논문내에 기술되어 있다. 이 논문내에 기술된 기술은 8비트 비율 정밀 회로 소자들을 요구하면서 12비트 단조성을 달성하기 위해 등가 확산 저항기 스트링(string)과 이진 비율 캐패시터 어레이를 결합시킨다. 그러나, 저항기들의 정합은 통상적을 캐패시터들의 정합보다 더욱 복잡하다. 이와 유사한 기술이 1980.4.29자 호지스(Hodges)등에게 허여된 미합중국 특허 제4,200,863호에 기술되어 있다.

다른 특정한 해결 방법은 1982년도 IEEE 국제 고상 회로 회의, Digest of Technical Papers, 80-81페이지에 맥글린취(McGlinchey)가 쓴 '모놀리드식 12b 3us ADC'란 명칭의 논문내에 기술되어 있다. 이 논문내에 기술된 기술은 최상위 비트용으로 병령 등가 전류원을 사용한다. 그러나, 이러한 기술은 능동 소자를 사용하기 때문에 더욱 복잡하다.

또 다른 공지된 해결방법은 최상위 비트용으로 병렬 등가 저항기들을 사용하는 것이다. 그러나, 저항기들을 정합시키는 것은 통상적으로 정합시키는 것보다 더욱 어렵다.

#### [발명의 요약]

그러므로, 본 발명의 한가지 장점은 소자 정합 필요조건을 감소시킨 고 분해능 A/D 변환기를 제공하는 것이다.

다른 장점은 고 분해능을 달성하기 위해 레이저 트리밍을 필요로 하지 않는 고 분해능 A/D 변환기를 제공하는 것이다.

또 다른 장점은 거의 동일한 값의 선택적으로 스위치된 병렬 용량성 소자를 사용하는 고 분해능 A/D 변환기를 제공하는 것이다.

다른 장점은 상부 N개의 비트들이 코드를 빠뜨리지 않도록 2<sup>M→</sup>의 한 파트(part)의 캐패시터 정합 필요 조건을 갖고 있는 거의 동일한 값의 선택적으로 스위치된 병렬 용량성 소자로 처리되는 고 분해능 M-비트 A/D 변환기를 제공하는 것이다.

또 다른 장점은 전 용량성 소자들을 사용하고 소자 정합 필요 조건이 감소된 고 분해능 A/D 변환기를 제공하는 것이다.

상술한 장점들 및 그외의 다른 장점과 특징들은 N개의 최상위 비트(MSB)를 결정하기 위해 사용되는 거의 동일한 값의 2 개의 스위치된 캐패시터를 갖고 있는 A/D 변환기를 포함하는 본 발명내에서 제공된다. 각각의 스위치된 캐패시터의 한 단자는 공통 노드에 결합되고, 다른 단자는 접지 또는 정 (+)기준 전압에 선택적으로 스위치될 수 있다. 변환 싸이클의 개시시에, 2 1대의 캐패시터의 제1그룹의 스위칭가능 단자는 접지에 접속되고, 2 1대의 캐패시터의 제2그룹의 스위치가능 단자는 정 기준전압에 접속된다. 공통 노드는 샘플된 아날로그 입력전압을 나타내는 전위로 충전된다. 공통 노드전압의 초기 극성에 따라서, 제1 또는 제2캐패시터 그룹들 중 1개의 그룹이 캐패시터를 선택적으로 스위칭하기 위해 선택된다. 선택된 캐패시터 그룹의 캐패시터들은 공통 노드 전위가 점점 더 가깝게되게 하기에 적합한 순차로 스위치된다. MSB 디지털 출력들은 소정의 스위칭 전 및 후속 스위칭 후에 초기 상태에서의 공통 노드 전위의 각각의 극성에 의해 정해진다.

또한, 본 발명은 (1) 거의 동일한 값의 2<sup>™</sup> 개의 캐패시터의 제1단자들을 공통 노드에 결합시키고 이러한 캐패시터의 각각의 제2단자들을 제1기준 전압 노드 또는 전압 노드에 스위치 가능하게 결합시키는 수단, (2) 샘플된 아날로그 입력 전압을 나타내는 공통 노드 상의 전압을 제공하도록 아날로그 입력 전압을 샘플링하는 수단, (3) 공통 노드와 제1기준 전압 노드 사이에 제1캐패시턴스를 제공하고 공통 노드와 제2기준 전압 노드 사이에 제2캐패시턴스를 제공하도록 캐패시터의 각각의 제2단자들의 접속 상태를 제어하는 수단, 및 (4) 제1기준 전압을 향해 공통 노드의 전압을 증가적으로 구동시키고 제1 및 제2캐패시턴스의 각각의 연속 상태에 따라 출력 비트를 제공하도록 제1 및 제2캐패시턴스의 각각의 연속 상태에 따라 출력 비트를 제공하도록 제1 및 제2캐패시턴스를 순차적으로 변화시키는 수단을 포함하는 아날로그 신호를 디지털 신호로 변환시키기 위한 방법을 포함한다.

### [상세한 설명]

다음의 상세한 설명 및 도면들 중 몇 개의 도면내에서, 동일한 소자들에는 동일한 참조번호를 붙였다.

제1도를 참조하면, 입력스위치(INSW)에 접속되는 입력 라인(11)을 포함하는 (부호비트를 포함하는) 12-비트 출력을 제공하기 위한 A/D 변환기(10)이 도시되어 있다. 입력 스위치(INSW)는 아날로그 입력 노드(13)과 접지 기준 노드(15) 사이에서 선택적으로 스위치될 수 있다. 변환된 아날로그 입력 전압(V4)는 아날로그 입력 노드(13)에서 나타난다. 변환 전의 초기 상태내에서, 스위치(INSW)는 아

날로그 입력 노드(13)에 결합되므로, 입력 라인(11)은 아날로그 입력 전압( $V_A$ )에 결합된다. 입력 스위치(INSW)가 초기 상태로부터 접지 기준 노드(15)로 스위치되면, 아날로그 입력 전압( $V_A$ )는 효율적으로 샘플된다.

또한, A/D 변환기(10)은 12-비트 출력의 5개의 최상위 비트(MSB)를 결정할 때 사용되는 제1캐패시터 그룹(20) 및 제2캐패시터 그룹(30)을 포함한다. 이 캐패시터들은 거의 동일한 값(C)로 되어 있고, 2 개의 그룹의 캐패시터들의 총수는  $2^{^{N}}$ 개[여기서, N은 캐패시터 그룹(20,30)에 의해 정해질 MSB의 수 이다)이다. 각각의 캐패시터 그룹은  $2^{^{N}}$ 개의 캐패시터의 1/2, 즉  $2^{^{N-1}}$ 개의 캐패시터를 포함한다. 기술한 예내에서, 부호비트를 포함하는 5개의 MSB(MSB1 내지 MSB5로서 식별됨)는 총 32개의 캐패시터를 포함하는 캐패시터 그룹(20,30)에 의해 정해진다.

제1캐패시터 그룹(20)은 공통 노드(19)에 접속되는 16개의 캐패시터(CP01 내지 CP16)를 포함한다. 또한, 캐패시터(CP01 내지 CP16)은 입력 라인(11)과 기준 전압( $V_R$ )에 있는 정 기준 노드(17) 사이에서 선택적으로 스위치될 수 있는 각각의 스위치(SP01 내지 SP16)에 각각 결합된다. 변환전의 초기상태에서, 스위치(SP01 내지 SP16)은 입력 라인(11)에 결합되므로, 캐패시터(CP01 내지 CP16)은 입력 라인(11)에 각각 결합된다.

제2캐패시터 그룹(30)은 공통 노드(19)에 접속되는 16개의 캐패시터(CN01 내지 CN16)을 포함한다. 또한, 캐패시터(CN01 내지 CN16)은 접지 기준 노드(15)와 정 기준 노드(17) 사이에서 선택적으로 스 위치될 수 있는 각각의 스위치(CN01 내지 CN16)에 각각 결합된다. 변환전의 초기 상태에서, 스위치 (SN01 내지 SN16)은 정 기준 노드(17)에 결합되므로, 캐패시터(CN01 내지 CN16)은 정 기준 노드(17)에 각각 결합된다.

공통 노드(19)는 비-반전 입력이 접지 기준 노드(15)에 접속되어 있는 전압비교기(21)의 반전 입력에 접속된다. 또한, 비교기(21)의 반전 입력은 개방 위치와 CMPOUT 신호를 제공하는 비교기(21)의 출력 사이에서 선택적으로 스위치될 수 있는 스위치(CMPSW)에 접속된다. 변환전의 초기 상태에서, 스위치(CMPSW)는 공통 노드(19)를 접지시키도록 비교기(21)의 출력에 스위치된다.

비교기(21)의 CMPOUT 출력은 필요한 논리 및 제어 기능을 A/D 변환기(10)에 제공하고 A/D 변환기의 디지털 출력은 출력 레지스터(50)에 연속적으로 제공하는 논리 및 제어 장치(40)에 결합된다.

또한, A/D 변환기(10)은 7개의 최하위 비트(LSB)를 결정하기 위해 사용되는 표준 연속 근사 형태의 디지털/아날로그(D/A) 변환기(60)을 포함한다. D/A 변환기(60)은 캐패시터 그룹(20,30)내의 각각의 캐패시터와 거의 동일한 값으로 되어 있는 캐패시터(23)을 통해 공통 노드(19)에 결합된다. D/A 변환기(60)은 연산 증폭기(25)의 반전 입력에 공통 접속되는 7개의 이진 가중 캐패시터(C1 내지 D7)아 포함한다. 연산 증폭기(25)의 비-반전 입력은 접지 기준 노드(15)에 접속된다. 또한, 캐패시터(C1 내지 C7)은 접지 기준 노드(15) 또는 정 기준 노드(17)에 선택적으로 스위치될 수 있는 스위치(S1 내지 S7)에 결합된다. 변환전의 초기 상태내에서, 스위치(S1 내지 C7)은 접지 기준 노드(15)에 스위치되므로, 캐패시터(C1 내지 C7)은 접지에 결합된다.

캐패시터(C1 내지 C7)은 이진 가중되는데, 캐패시터(C1)은 베이스 값(CAP)을 갖고, 캐패시터(C2)는 값(2CAP)을 가지며, 캐패시터(C3)은 값(4CAP)을 갖고, …등으로 하여 캐패시터(C7)은 값 (64CAP)을 갖는다.

연산 증폭기(25)의 출력은 캐패시터(C8)을 통해 반전 입력에 결합된다. 캐패시터(C8)은 값(128CAP)을 갖는데, 여기서 CAP은 캐패시터(C1)의 값이다. 스위치(INTSW)는 캐패시터(C8)과 병렬이고, 개방위치와 폐쇄 위치 사이에서 스위치될 수 있다. 초기 상태내에서, 스위치(INTSW)는 폐쇄 위치내에 있으므로, 연산 증폭기(25)의 출력과 반전 입력 사이에 쇼트 회로를 제공한다. 스위치(INTSW)가 폐쇄되면, 연산 증폭기(25)의 출력은 접지 전압에 있다.

동작시에, A/D 변환기(10)의 상술한 스위치 소자들은 변환될 아날로그 입력 신호( $V_A$ )가 아날로그 입력 노드(13)에 있을 때 초기 상태내에 있도록 논리 및 제어 장치(40)에 의해 제어된다. 다음 표 I은 스위치들의 초기 상태를 요약한 것이다.

| 스위치   | 위치                        |

|-------|---------------------------|

| INTSW | मं अ                      |

| CMPSW | 폐쇄                        |

| INSW  | $\mathbf{v}_{A}$          |

| SPXX  | $V_{A}$                   |

| SNXX  | $\mathbf{v}_{\mathbf{k}}$ |

| SX    | 접지                        |

캐패시터 그룹(20,30)에 관련된 스위치들의 영향을 더욱 용이하게 이해하기 위해서, 캐패시터 그룹 (20,30)에 의해 제공된 캐패시턴스를 개략적으로 도시한 제2도를 참조하겠다. CV1은 공통 노드(19)와 정 기준 노드(17) 사이의 캐패시턴스를 나타내고, CV2는 공통 노드(19)와 접지 기준노드(15) 사이의 캐패시턴스를 나타낸다. 초기 위치내의 캐패시터 그룹(20,30)에 관련된 스위치에 있어서, CV1은 캐패시터(CN01 내지 CN16)에 의해 제공된 캐패시턴스에 대응하고, CV2는 캐패시터(CP01 내지

CP16)에 의해 제공된 캐패시턴스에 대응한다. 캐패시턴스(CV1 및 CV2)의 값들은 스위치(SN01 내지 SN16) 및 스위치(SP01 내지 SP16)에 의해 제어된다.

참조하기 위해, 각각의 캐패시터 그룹의 각각 캐패시터는 관련된 스위치가 초기 상태내에 있을 때 '제거' 또는 '아웃'되는 것으로 고찰될 수 있다. 캐패시터는 관련된 스위치가 비-초기 또는 교호위치내에 있을 때 '추가' 또는 '인'되는 것으로 고찰될 수 있다. 그러므로, 캐패시터 그룹(20)의 캐패시터들은 다른 캐패시터 그룹(30)의 캐패시터들에 관련하여 병렬로 추가 또는 제거되고, 이 반대로도 된다. 이렇게 될 때, 캐패시턴스(CV1 및 CV2)의 값의 변화는 동일하고 반대이다.

본 명세서내에서 더욱 상세하게 기술한 바와 같이, 소정의 변환 싸이클 동안, 캐패시터 그룹(20,30)들 중 단지 1개의 캐패시터 그룹의 캐패시터들은 접지 기준 전압을 향해 공통 노드 전압을 순차적으로 구동시키기 위해 선택적으로 추가 또는 제거된다. 그러나, 상술한 바와 같이, 이러한 스위칭은 캐패시턴스(CV1과 CV2)를 변화시킨다. 출력 비트는 캐패시터 그룹(20,30)들 중 1개의 캐패시터 그룹에 관련된 스위치들에 의해 제어될 때 캐패시턴스(CV1 및 CV2)의 각각의 연속 상태에 따라 결정된다.

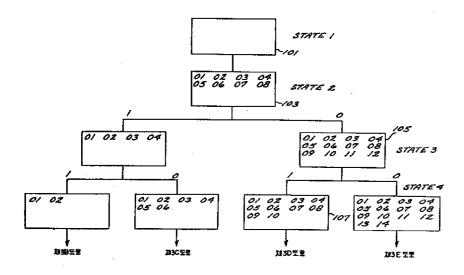

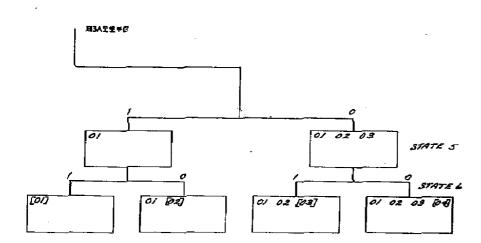

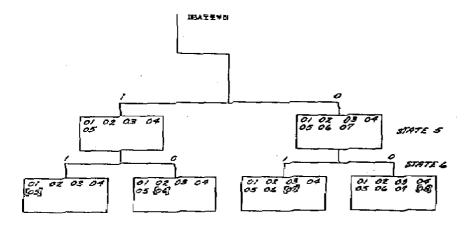

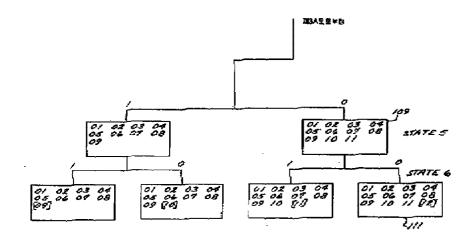

적합한 캐패시터 그룹에 관련된 스위치들이 5개의 MSB들 중 1개의 MSB를 결정하기 위해 제 위치내에 있을 때, 캐패시터 그룹(20,30)은 제1최상위 비트(MSB1)을 결정하기 위한 STATE1, 제2최상위 비트(MSB2)를 결정하기 위한 STATE2, 등 내에 있다고 고찰된다.

변환 싸이클의 개시시에, 스위치(INTSW)는 개방되고, 스위치(CMPSW)는 후속적으로 개방된다. 이때, 입력 스위치(INSW)는 아날로그 입력 전압( $V_A$ )를 효율적으로 샘플 및 보유하기 위해 접지되도록 스위치된다. 입력 스위치(INSW)를 접지에 스위칭시키기 전에, 공통 노드(19)는 스위치(CMPSW)가 초기에 폐쇄되어 있는 결과로서 접지 전위에 있다.

접지로의 입력 스위치(INSW)의 스위칭은 입력 라인(11)상의 전압이 전지 기준 전압에 있도록 샘플된 아날로그 입력 전압( $V_A$ )와 동일한 크기만큼 변하게 한다. 공통 노드(19)의 전압( $V_C$ )는 샘플된 아날로 그 입력 전압( $V_A$ )의 크기의 1/2과 동일한 크기만큼 변하는데, 그 이유는 캐패시터 그룹(20,30)이 50% 분압기로서 작용하기 때문이다. 공통 노드 전압( $V_C$ )의 변화는 샘플된 아날로그 입력 전압( $V_C$ )가 +일 때 -방향이고, 샘플된 아날로그 입력 전압이 -일 때 +방향이다. 공통 노드 전압( $V_A$ )가 초기에 접지 기준 전압에 있기 때문에, 정 샘플 아날로그 입력 전압( $V_A$ )는 -인 공통 노드 전압( $V_C$ )를 발생시키게 되고, 부 샘플 아날로그 입력 전압( $V_A$ )은 +인 공통 노드 전압( $V_C$ )를 발생시키게 된다.

그러므로, 접지로의 INSW의 스위칭은 효율적으로 샘플전압이 공통 노드(19)상에 나타나게 하는데, 이러한 샘플 전압은 -1/2VA이다.

입력 아날로그 전압  $V_A$ 의 샘플링에 따라, 5개의 최상위 비트(MSB1 내지 MSB5)는 공통 노드 전압( $V_C$ )가 캐패시턴스(CV1 및 CV2)의 값들을 순차적으로 변화시킴으로써 접지 기준 전압을 향해 증가적으로 구동되는 연속적 근사에 의해 연속적으로 결정된다. 제2도에 관련하여 기술한 바와 같이, 캐패시턴 스(CV1 및 CV2)의 값들은 캐패시터 그룹(20,30)에 관련된 스위치들의 스위칭에 따라 동일한 반대 방향으로 변한다. 상세하게 말하자면, 캐패시턴스(CV1 및 CV2)의 값들은 캐패시터 그룹(20,30)들 중 1개의 캐패시터 그룹의 캐패시터들을 이진 가중 그룹내에서 추가 또는 제거함으로써 변화된다. 이러한 제거 및 추가를 달성하기 위한 스위칭은 특히 다음과 같이 변환 싸이클을 제어하는 논리 및 제어장치(40)에 의해 제어된다.

입력 아날로그 전압( $V_A$ )를 샘플할 때, STATE1 중의 공통 노드 전압( $V_C$ )의 극성은 캐패시터들이 순차적으로 추가 또는 제거되는 캐패시터 그룹은 결정하고 MSB1을 정하기 위해 사용된다. 공통 노드 전압( $V_C$ )의 극성은 전압 캐패시터(21)의 CMPOUT 출력으로 표시된다. COMPUT은  $V_C$ 가-일 때 하이(high)상태이고,  $V_C$ 가 +일 때 로우(low) 상태이다.

상세하게 말하자면, 제1캐패시터 그룹(20)의 캐패시터들은 공통 노드 전압( $V_c$ )가 초기에 정 샘플 아날로그 입력 전압( $V_A$ )에 따라 -일 때 변환중에 스위치된다. 제2캐패시터 그룹(30)의 캐패시터들은  $V_c$ 가 초기에 부 샘플 입력 아날로그 전압( $V_A$ )에 따라 +일 때 변환중에 스위치된다.

MSB1에 관해서는, 공통 노드 전압(Vc)가 +이면, MSB1은 1이다. Vc가 -1이면, MSB1은 0이다. 전압 비교기(21)의 CMPOUT 출력은 MSB1의 보수(Complement)이므로, MSB1용 비교기(21)에 의해 제공된 출력은 MSB1용으로 적합한 값을 출력 레지스터(50)에 이송하는 논리 및 제어 장치(40)에 의해 보수된다.

MSB2 내지 MSB5를 결정하기 위해, 논리 및 제어 장치(40)은 특히 캐패시턴스가 비교기(21)의 CMPOUT 출력 및 MSB1'로서 식별된 MSB1의 부정값 상의 익스클루시브 OR 연산의 결과에 기초를 두고 추가 또 는 제거되는지의 여부를 제어한다. 이러한 연산은 다음과 같이 정의된다.

# A = CMPOUT @MSB1'

(식 1)

익스클루시브 OR 결과 A가 O(로우상태)이면, 캐패시터는 초기 위치로부터 관련 스위치들을 스위칭시 킴으로써 추가되어야 한다. 익스클루시브 OR 결과 A가 1(하이상태)이면, 캐패시터는 교화 위치로부 터 관련 스위치를 스위칭시킴으로써 제거되어야 한다.

특정한 캐패시터들이 추가되든지 또는 제거되는지의 결정은 다음 법칙에 기초를 두고 있다. 캐패시 턴스는 소정의 경우에 가장 최근에 제거된 캐패시턴스로부터 추가된다. 그렇지 않으면, 캐패시턴스 는 이미 추가 또는 제거되지 않은 캐패시턴스로부터 추가된다. 캐패시턴스는 가장 최근에 추가된 캐 패시턴스로부터 제거된다.

또한, MSB1의 경우에는 캐패시터들이 초기 상태로부터 전혀 스위치되지 않는다. MSB2의 경우에는 선택된 캐패시터 그룹의 캐패시터들의 1/2이 스위치된다. MSB3의 경우에는 선택된 캐패시터 그룹의 캐패시터들의 1/4이 스위치된다. MSB4의 경우에는, 선택된 그룹 캐패시터들의 1/8이 스위치되고, MSB5의 경우에는 이러한 그룹의 1/16이 스위치된다. 그러므로, N개의 MSB를 결정하기 위해, 각각의 캐패시터 그룹은 2<sup>N-1</sup>개의 캐패시터를 갖고, 각각 스위치되는 서브그룹은 다음의 캐패시터 수를 갖는다.

$K_1 = 0$

l=1인 경우 (식 2)

$K_t = (2^{N-1}) * (2^{t-1})^{-1}$

I→2인 경우 (싀 3)

여기서,  $K_1$ 는 I(이때, I는 1 내지 N이다)번째 MSB를 결정하기 위해 스위치되어야 하는 캐패시터 수를 나타낸다. 식 3은 다음과 같이 간략화될 수 있다.

$K_1 = 2^{N-1}$

I≥2인 경우 (식 4)

기술한 다른 방식으로, SMB2의 경우에는 선택된 캐패시터 그룹의 캐패시터들의 1/2이 스위치되고, 후속 MSB의 경우에는 스위치된 캐패시터 수는 즉시 선행하는 MSB의 경우에 스위치된 캐패시터 수의 1/2이다.

익스클로시브 OR 결과 A의 함수로서 캐패시턴스를 순차적으로 추가 및 제거함으로써, 공통 노드 전  $CO(V_C)$ 는 접지 기준 전위를 향해 증가적으로 구동된다. 각각의 캐패시턴스 추가 또는 제거에 따라, 공통 노드 전압의 극성은 최상위 비트들 중 1개의 최상위 비트에 출력 비트에 제공하기 위해 사용된다.

상술한 바와 같이, MSB1의 경우에 CMPOUT는 보수되어 출력 레지스터(50)에 제공된다. MSB2 내지 MSB5의 경우에, CMPOUT의 값은 출력 레지스터(50)에 직접 제공된다. 다음에 더욱 상세하게 기술한 바와 같이, MSB6 내지 MSB12로서 식별된 7개의 최하위 비트의 경우에, CMPOUT은 보수되어 출력 레지스터(50)에 제공된다.

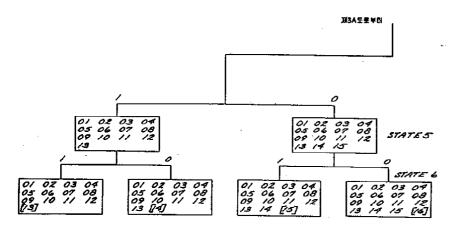

상술한 캐패시터들의 순차 스위칭은 초기 상태로부터 스위치되는 선택된 캐패시터 그룹의 캐패시터 들을 도시한 제3도에 상태도로 예시화된다. 제3도는 선택된 그룹의 캐패시터들만을 식별하는데, 그 이유는 다른 캐패시터 그룹의 캐패시터들이 초기 상태를 유지하기 때문이다. 예를 들어, 다음과 같 은 것을 포함하는 블록은 선택된 그룹의 캐패시터(01 내지 14)가 교호 상태로 스위치되는 것을 나타 낸다.

01 02 03 04 05 06 07 08 09 10 11 12 13 14

제3도의 블록들내의 숫자들은 선택된 캐패시터 그룹(20,30)의 캐패시터들에 대한 참조 명칭의 숫자 부분에 대응한다.

제3도의 상태도를 통해 트레이스된 특정한 경로는 각각의 STATE에서의 익스클루시브 OR 연산의 결과 A에 따라 변한다. 제3도의 상이한 브랜취는 브랜취가 즉시 선행하는 STATE에 대한 식 1의 익스클루 시브 OR 연산의 결과 A에 따라 뒤따를 것이라는 것을 표시하도록 1 또는 0으로 식별된다.

제3도 및 제4도와 함께 기술한 일례는 도움이 될 수 있다. 샘플된 아날로그 입력 전압  $V_A$ 가  $0.725V_R$  [이때,  $V_R$ 은 기준 노드(17)의 전위이다]이라고 가정한다. 스위치(INSW)가 접지에 스위치된 후, 캐패시터 그룹(20,30)으 SSTATE 1내에 있고, 공통 노드 전압  $V_C$ 는 부이다. 그러므로, MSB1은 0이고, 부정 MSB1은 1이며, 제1캐패시터 그룹(20)(CP01 내지 CP16)은 선택된 캐패시터 그룹이라고 결정된다. 식 1의 익스클루시브 0R 결과 A는 0이고, 스위치되지 않은 캐패시터들의 1/2(즉, CP01 내지 CP08)은 블록(103)내에 도시한 바와 같이 초기 위치로부터 관련 스위치를 스위칭시킴으로써 추가된다. 이것은 캐패시터 그룹(20,30)을 STATE2내에 배치시킨다. 공통 노드 전압( $V_C$ )는 -이므로, MSB2는 1이다.

STATE2내에서, 식 1의 익스클루시브 OR 결과 A는 O이고, 나머지 스위치되지 않은 캐패시터들의 1,2, 즉 CP09 내지 CP12는 블록(105)내에 도시한 바와 같이 초기 위치로부터 관련 스위치를 스위칭시킴으로써 추가된다. 이것을 캐패시터 그룹(20,30)을 STATE3내에 배치시킨다. 공통 노드 전압  $V_C$ 는 +이므로, MSB3은 O이다.

STATE3내에서, 식 1의 익스클루시브 OR 결과 A는 1이고, 이미 추가된 캐패시터들의 1/2, 즉 CP11 및 CP12는 블록(107)내에 도시한 바와 같이 초기 위치로 다시 관련 스위치들을 스위칭시킴으로써 제거된다. 공통 노드 전압  $V_{\rm C}$ 는 -이므로, MSB4는 1이다. 이것은 캐패시터 그룹(20,30)을 STATE4내에 배치시킨다.

STATE4내에서, 식 1의 익스클루시브 OR 결과 A는 O이고, 이미 제거된 캐패시터들의 1/2, 즉 CP11은 블록(109)내에 도시한 바와 같이 교호 위치로 관련 스위치(SP11)을 스위칭시킴으로써 추가도니다. 이것은 캐패시터 그룹(20,30)을 STATE5내에 배치시킨다. 공통 노드 전압 V<sub>c</sub>는, MSB5는 1이다.

그러므로, MSB1 내지 MSB5는 특정한 예의 경우에 접지 기준 전압을 향해 공통 노드 전압( $V_c$ )을 증가적으로 구동시킴으로써 결정되었다. 일반적으로, 정 아날로그 입력 전압( $V_A$ )의 경우에, 제1캐패시터 그룹(20)내의 캐패시턴스는 공통 노드 전압( $V_c$ )가 -일 때 추가되고(즉, 선택된 스위치들은 교호 위

치로 스위치된다). 캐패시턴스는 공통 노드 전압  $V_c$ 가 +일 때 제거된다(즉, 선택된 스위치들은 초기위치로 스위치된다). 부 아날로그 입력 전압( $V_A$ )의 경우에, 제2캐패시터 그룹(30)내의 캐패시턴스는 공통 노드 전압  $V_c$ 가 +일 때 추가되고(즉, 선택된 스위치들은 교호 위치로 스위치된다). 캐패시턴스는 공통 노드 전압( $V_c$ )가 -일 때 제거된다(즉, 선택된 스위치들은 초기 위치로 스위치된다).

MSB1(부호 비트) 내지 MSB5가 결정된 후, 공통 노드(19)상의 잔류 전압( $V_c$ )는 7개의 최하위 비트를 결정하기 위해 D/A 변환기(20)에 사용된다. 그러나, 표준 형태 D/A 변환기(60)은 단극성이므로, 공통 노드 전압( $V_c$ )는 7개의 최하위 비트를 제공하기 위해 사용될 수 있기전에 정으로 되어야 한다. 이것은 다음과 같이 달성된다.

만약 있다면, MSB5를 결정하기 위한 STATE6은 달성하는데 필요한 스위칭은 실제로 2가지 연산에 기초를 두고 있다. 첫째, 식 1의 익스클루시브 OR 결과 A는 캐패시터가 제거될 것인지의 여부를 결정하기 위해서만 사용된다. 결과 A가 0이면, 변화가 없다. 결과 A가 1이면, 캐패시터는 제거된다. 최종 MSB 즉, MSB5를 결정하기 위해, 식 1은 이전의 MSB를 결정하기 위한 것과 상이하게 사용된다. 차이는 MSB5의 경우에 0인 결과 A가 아무런 변화를 요구하지 않는다는 것이다.

제2연산은 다음 기술에 기초를 두고 있다. 공통 노드 전압( $V_c$ )의 극성이 STATE6이 식 1을 참조하여 결정된 경우에 STATE1내에 있을때와 동일하게 된다는 것이 결정되었다. 즉, 공통 노드 전압( $V_c$ )다 STATE1 내에서 부이면(즉,  $V_A$ 가 정이고 MSB1이 0이면),  $V_c$ 는 STATE6이 식 1을 참조하여 결정된 경우에 약간 -로 된다. 공통 노드 전압( $V_c$ )가 STATE 1내에서 정이면(즉,  $V_A$ 가 부이고 MSB1이 1이면),  $V_c$ 는 STATE6이 식 1을 참조하여 결정된 경우에 약간 +로 된다. 따라서, STATE6을 결정하기 위한 제2연산은  $V_A$ 가 정인 경우(즉, MSB1이 0인 경우)에 부수 캐패시터를 추가시킨다.  $V_A$ 가 -이면(즉, MSB1이 1 이면), 부수 캐패시터가 전혀 추가되지 않는다.

제3도 내에서, 부수 캐패시터는 V<sub>A</sub>가 +인 경우(MSB1이 0인 경우에만 추가된다는 것을 나타내기 위해 괄호로 도시되어 있다. 부수 캐패시터를 추가시키기 위한 논리는 MSB1 값을 용이하게 사용할 수 있다. 간단히 말하면, STATE6은 식 1의 익스클루시브 OR 결과 A(0=무변화, 1=제거) 및 MSB1(0=추가, 1=무변화)을 참조하여 결정된다.

상술한 예내에서, STAYE5내에서 익스클루시브 OR 결과 A는 O인데, 이것은 무변화를 나타낸다. 그러나, 아날로그 입력 전압( $V_A$ )는 +이고, 결과적으로 공통 노드 전압( $V_C$ )는 STATE1내에서 -였고, MSB1은 O이다. 그러므로, 캐패시터(CP12)는 블록(111)내에 도시한 바와 같이 관련 스위치(SP12)를 교호 위치로 스위칭시킴으로써 추가된다. 이것은 7개의 들이 D/A 변환기(60)에 의해 결정될 수 있도록 STATE6 내에 캐패시터 그룹을 효율적으로 배치시킨다.

캐패시터 그룹(20,30)이 STATE6내의 배치된 후, 스위치 INTSW는 MSB6 내지 MSB12로 식별되는 7개의 최하위 비트를 결정하기 위해 개방된다. 공지된 기술에 따라, MSB6 내지 MSB12는 접지 전압을 향해 공통 노드 전압( $V_c$ )를 구동시키기 위해 캐패시터(C7 내지 C1)을 순차적으로 스위칭함으로써 연속적으로 결정된다. 상술한 바와 같이, 전압 비교기(C1)의 CMPOUT 출력은 MSB6 내지 MSB12의 경우에 논리 및 제어 장치(C40)에 의해 보수된다.

상술한 예의 경우에, 제5도는 MSB6 내지 MSB12가 결정될 때의 공통 노드 전압( $V_c$ )의 파형을 확대 도시한 것이다. 스위치(S7)은  $V_R$ 에 접속되고, 공통 노드 전압( $V_c$ )는 -로 된다. 그러므로, MSB6은 0이다.

스위치(S7)은 접지로 다시 스위치되고, 스위치(S6)은  $V_R$ 에 접속된다. 공통 노드 전압( $V_C$ )는 +로 되므로, MSB7은 1이다. 스위치(S6)을 계속  $V_R$ 에 접속되고, 스위치(S5)는  $V_R$ 에 접속된다. 공통 노드 전압 ( $V_C$ )는 +로 유지되므로, MSB8은 1이다.

스위치(S6 및 S5)는 계속  $V_R$ 에 접속되고, 스위치(S4)는  $V_R$ 로 스위치된다. 공통 노드 전압( $V_C$ )는 -로 되므로, MSB9는 0이다.

공통 노드 전압( $V_c$ )가 -이기 때문에, 스위치(S4)는 접지로 다시 스위치되고, 스위치(S3)은  $V_R$ 로 스위치되며, 스위치(S6 및 S5)는 계속  $V_R$ 에 접속된다. 공통 노드 전압( $V_c$ )는 -로 유지되므로, MSB10은 0이다.

스위치(S3)은 접지로 다시 스위칭되고, 스위치(S2)는  $V_R$ 로 스위치되며, 스위치(S6 및 S5)는 계속  $V_R$ 에 접속된다. 공통 노드 전압( $V_C$ )는 +로 되므로, MSB11은 1이다.

스위치(S6,S5 및 S2)는 계속  $V_R$ 에 접속되고, 스위치(S1)은  $V_R$ 로 스위치된다. 공통 노드 전압( $V_C$ )는 +로 유지되므로, MSB12는 1이다.

상술한 설명으로부터, 7개의 최하위 비트(즉, MSB6 내지 MSB12)에 관해서는, 공통 노드 전압( $V_c$ )가 -일 때 캐패시턴스가 제거되지만, 공통 노드 전압( $V_c$ )가 +일 때 캐패시턴가 추가된다.

지금까지, 본 발명의 특수한 실시예에 관하여 기술하였지만, 본 분야에 숙련된 기술자들은 다음의 특허 청구의 범위에 의해 정해진 바와 같이 본 발명의 범위 및 원리를 벗어나지 않고서 본 발명을 여러 가지 형태로 변형 및 변경시킬 수 있다.

#### (57) 청구의 범위

### 청구항 1

아날로그 입력 전압 $(V_A)$ 를 나타내는 샘플 전압과 제1기준 전압 사이에 초기에 결합되고 제1기준 전압과 샘플 전압 사이의 제1개패시턴스(CV1)를 공동으로 제거하는 거의 동일한 캐패시턴스의 다수의 제1용량성 조자(CP01,CP02,CP15,CP10)을 갖고 있는 제1가변 용량성 장치(20), 제1용량성 조자(CP01,CP02,CP15,CP10)과 값이 거의 동일하고 샘플 전압과 제1기준 전압에 관련하여 +인 제2기준 전압 $(V_R)$  사이에 초기에 결합되며 샘플 전압과 제2기준 전압 사이의 제2캐패시턴스(CV2)를 공동으로 제공하는 다수의 제2용량성 소자(CN01,CN02,CN15,CN10)을 갖고 있는 제2가변 용량성 장치(30), 및 샘플 전압의 극성의 함수로서 동일하지만 반대 방향으로 제1 및 제2캐패시턴스(CV1) 및 (CV2)를 순차적으로 변화시킴으로써 제1기준 전압을 향해 샘플 전압 $(V_A)$ 를 증가적으로 구동시키고 제1 및 제2캐패시턴스에 각각의 연속 상태에 따라 출력 비트를 제공하기 위해 샘플 전압 $(V_A)$ 에 응답하는 논리 및 제어 장치(40)으로 구성되는 것을 특징으로 하는 아날로그 입력 전압을 변환시키기 위한 아날로그/디지탈 변환기.

#### 청구항 2

제1항에 있어서, 제1가변 용량성 장치(20)이 각각의 제1용량성 소자(CP01,CP02,CP15,CP10)을 제1기준 전압( $V_R$ )로부터 제2기준 전압으로 선택적으로 스위칭시키기 위해 논리 및 제어 장치(40,50)에 응답하는 제1스위칭 장치(SP01,SP02,SP15,SP10)을 포함하고, 제2가변 용량성 장치(30)이 각각의 제2용량성 소자(CN01,CN02,CN15,CN10)을 제2기준 전압으로부터 제1기준 전압으로 선택적으로 스위칭시키기 위해 논리 및 제어 장치(40)에 응답하는 제2스위칭 장치(SN01,SN02,SN15,SN10)을 포함하는 것을 특징으로 하는 아날로그/디지탈 변환기.

#### 청구항 ?

제2항에 있어서, 제1기준 전압이 접지 전압이고, 제2기준 전압이 정(+) 전압( $V_R$ )인 것을 특징으로 하는 아날로그/디지탈 변환기.

#### 청구항 4

제3항에 있어서, 제1용량성 소자들중 선택된 소자들이 아날로그 입력 전압(V₄)가 +일 때 스위치되고, 제2용량성 소자들중 선택된 소자들이 아날로그 입력 전압(V₄)가 -일 때 스위치되는 것 을 특징으로 하는 아날로그/디지탈 변화기.

# 청구항 5

아날로그 입력 전압( $V_A$ )를 나타내는 샘플 전압에 결합된 각각의 제1단자를 갖고 있고 제1기준 전압 또는 제2기준 전압( $V_B$ )에 접속하기 위해 각각 스위치가능한 각각의 제2단자를 갖고 있는 거의 동일한 값(C)의  $2^N$  [여기서, N은 용량성 장치(20,30)으로 결정될 최상위 비트수이다]개의 캐패시터를 갖고 있는 용량성 장치(20,30), 샘플 전압( $V_A$ )와 제1기준 전압 사이의 제1캐패시턴스를 제공하고 샘플 전압과 제2기준 전압( $V_B$ ) 사이의 제2캐패시턴스를 제공하도록 각각의 제2단자들의 접속을 제어하기위한 스위칭 장치(20,30) 장기(20,30) 위해 제1 및 제2캐패시턴스(20,30)을 순차적으로 변화시키도록 스위칭 장치를 제어하고 제1 및 제2캐패시턴스(20,30)의 각각의 연속 상태에 따라 출력 비트를 제공하기 위해 샘플 전압(20,30)에 응답하는 제어 장치(20,30)의 각각의 연속 상태에 따라 출력 비트를 제공하기 위해 샘플 전압(20,30)에 응답하는 제어 장치(20,30)으로 구성되는 것을 특징으로 하는 아날로그입력 전압(20,30)의 변환시키기 위한 아날로그/디지탈 변환기(20,30)이.

### 청구항 6

제5항에 있어서, 스위칭 장치(SP01,SP02,SP14,SP15,SP16)이 변환 싸이클의 개시시에 제1그룹의  $2^{N-1}$ 개의 캐패시터(20)을 제1기준 전압에 접속시키고 제2그룹의  $2^{N-1}$ 개의 캐패시터(30)을 제2기준 전압  $(V_R)$ 에 접속시키는 것을 특징으로 하는 아날로그/디지탈 변환기.

# 청구항 7

제6항에 있어서, 소정의 변환 싸이클 동안, 제1 또는 제2그룹의 2<sup>N-1</sup>개의 캐패시터들 중 한 그룹으로 부터 캐패시터들만이 선택적으로 스위치되는 것을 특징으로 하는 아날로그/디지탈 변환기.

#### 청구항 8

제7항에 있어서, 선택적으로 스위치된 캐패시터들이 만약 있다면 초기 상태로부터 스위치될 캐패시터들이 가장 최근에 초기 상태로 다시 스위치된 캐패시터들로부터 선택되는 순차로 스위치되고, 초기 상태로 다시 스위치될 캐패시터들의 초기 상태로부터 가장 최근에 스위치된 캐패시터들로부터 선택되는 것을 특징으로 하는 아날로그/디지탈 변환기.

#### 청구항 9

제8항에 있어서, 선택적으로 스위치된 캐패시터들이 2<sup>N-1</sup>(여기서, I는 I번째 최상위 비트이고 2 내지

N과 동일하다)개의 캐패시터를 갖고 있는 서브 그룹의 순차로 스위치되는 것을 특징으로 하는 아날로그/디지탈 변환기.

#### 청구항 10

아날로그 입력 신호를 N개의 최상위 비트를 갖고 있는 디지털 신호로 변환시키기 위한 방법에 있어서, 거의 동일한 값의  $2^N$ 개의 캐패시터의 제1단자를 공통 노드(19)에 결합시키고 이러한 캐패시터의 가각의 제2단자를 제1기준 전압 노드 또는 제2기준 전압 노드( $V_R$ )에 스위치가능하게 결합시키는 수단, 샘플된 아날로그 입력 전압( $V_A$ )를 나타내는 공통 노드(19)상의 전압을 제공하기 위해 아날로그입력 전압( $V_A$ )를 샘플링하는 수단, 공통 노드(19)와 제1기준 전압 노드 사이에 제1캐패시턴스를 제공하고 공통 노드(19)와 제2기준 전압 노드(17) 사이에 제2캐패시턴스를 제공하기 위해 캐패시터들의 각각의 제2단자들의 접속을 제어하는 수단, 및 제1기준 전압을 향해 공통 노드(19)의 전압을 증가적으로 구동시키고 제1 및 제2캐패시턴스(20,30)의 각각의 연속 상태에 따라 출력 비트를 제공하기 위해 제1 및 제2캐패시턴스(20,30)의 순차적으로 변화시키는 수단을 포함하는 것을 특징으로 하는 방법.

#### 청구항 11

제10항에 있어서, 제어 수단이 변환 싸이클의 개시시에 제1그룹의 2<sup>N-1</sup> 개의 캐패시터(20)을 제1기준 전압 노드에 접속시키고 제2그룹의 2<sup>N-1</sup> 캐패시터(30)을 제2기준 전압 노드(17)에 접속시키는 수단을 포함하는 것을 특징으로 하는 방법.

#### 청구항 12

제11항에 있어서, 제1 및 제2캐패시턴스(20,30)을 순차적으로 변환시키는 수단이 소정의 변환 싸이 클 동안에 제1 및 제2그룹(20,30)들 중 한 그룹의 캐패시터들을 선택적으로 스위칭하는 수단을 포함하는 것을 특징으로 하는 방법.

#### 청구항 13

제12항에 있어서, 캐패시터들을 선택적으로 스위칭하는 수단이, 소정의 경우에 초기 상태로부터 스위치될 캐패시터들을 가장 최근에 초기 상태로 다시 스위치된 캐패시터들로부터 선택하고, 초기 상태로 다시 스위치될 캐패시터들로부터 선택하는 수단을 포함하는 것을 특징으로 하는 방법.

#### 청구항 14

제13항에 있어서, 캐패시터들을 선택적으로 스위칭하는 수단 2<sup>N-1</sup> (여기서, I는 I번째 최상위 비트를 나타내고 2 내지 N과 동일하다)개의 캐패시터들을 갖고 있는 서브 그룹의 순서로 캐패시터들을 스위 칭하는 수단을 포함하는 것을 특징으로 하는 방법.

# 도면

# 도면2

# 도면3A

도면30

도면3E

# 도면4