## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5042881号 (P5042881)

最終頁に続く

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月20日(2012.7.20)

| (51) Int.Cl. | F I                           |                     |        |

|--------------|-------------------------------|---------------------|--------|

| HO2M 3/28    | ( <b>2006.01)</b> HO2M        | 3/28 Q              |        |

| HO2M 3/325   | <b>(2006.01)</b> HO2M         | 3/28 L              |        |

| HO2M 3/338   | <b>(2006.01)</b> HO2M         | 3/325 A             |        |

| HO1L 33/00   | <b>(2010.01)</b> HO2M         | 3/338 Z             |        |

| HO5B 37/02   | <b>(2006.01)</b> HO1L         | 33/00 J             |        |

|              |                               | 請求項の数 4 (全 17 頁) 晶  | 最終頁に続く |

| (21) 出願番号    | 特願2008-42193 (P2008-42193)    | (73) 特許権者 000005821 |        |

| (22) 出願日     | 平成20年2月22日 (2008.2.22)        | パナソニック株式会社          |        |

| (65) 公開番号    | 特開2009-100641 (P2009-100641A) | 大阪府門真市大字門真1006      | 番地     |

| (43) 公開日     | 平成21年5月7日(2009.5.7)           | (74) 代理人 100067828  |        |

| 審査請求日        | 平成22年10月22日 (2010.10.22)      | 弁理士 小谷 悦司           |        |

| (31) 優先権主張番号 | 特願2007-248245 (P2007-248245)  | (74)代理人 100115381   |        |

| (32) 優先日     | 平成19年9月25日 (2007.9.25)        | 弁理士 小谷 昌崇           |        |

| (33) 優先権主張国  | 日本国(JP)                       | (74)代理人 100097054   |        |

|              |                               | 弁理士 麻野 義夫           |        |

|              |                               | (74) 代理人 100133798  |        |

|              |                               | 弁理士 江川 勝            |        |

(74)代理人 100143373

弁理士 大西 裕人

(54) 【発明の名称】スイッチング電源装置

### (57)【特許請求の範囲】

# 【請求項1】

直流入力電源の両端子間に第1および第2のスイッチング素子から成る直列回路が接続され、前記第1および第2のスイッチング素子の接続点と前記直流入力電源の一方の端子との間に、インダクタ、コンデンサおよびトランスの1次巻線から成る直列回路が接続され、前記第1および第2のスイッチング素子のスイッチングにより得られたトランスの2次側誘起電流をダイオードおよび平滑コンデンサによって整流・平滑化して出力し、第1および第2の制御回路が前記トランスの第1および第2の補助巻線に誘起された電圧で前記第1および第2のスイッチング素子をそれぞれON/OFFすることでスイッチングを継続するようにした電圧帰還型の自励式複合共振直列コンバータから成るスイッチング電源装置において、

前記第1および第2の制御回路は、前記第1および第2のスイッチング素子をそれぞれOFFさせるための第3および第4のスイッチング素子と、前記第1および第2の補助巻線に生じる誘起電圧をピークホールドするピークホールド回路と、前記誘起電圧が前記ピークホールド回路によるホールド電圧より予め定めるレベル以上低下したときに前記第3および第4のスイッチング素子をONして前記第1および第2のスイッチング素子をそれぞれOFFさせる第1の比較器とを備えて構成され、

前記第1および第2の補助巻線の少なくとも一方に誘起された電圧が対応する前記第1 および第2のスイッチング素子<u>の少なくとも一方</u>を順バイアスする方向に発生した時点を 起点として三角波を発生する三角波発生回路と、可変の基準電圧を発生する基準電圧源と

、<u>前記第1および第2のスイッチング素子の少なくとも一方をOFFさせるための第5のスイッチング素子と、</u>前記三角波の電圧と基準電圧とを比較し、前記三角波の電圧が基準電圧より高くなる<u>と前</u>記第<u>5</u>のスイッチング素子をONさせる第2の比較器とを備えて構成される出力調整回路を含むことを特徴とするスイッチング電源装置。

### 【請求項2】

2次側負荷電流または電圧を検出する負荷検出回路と、

前記負荷検出回路の検出結果を 1 次側へフィードバックし、前記基準電圧源の基準電圧を変化するフィードバック回路とをさらに備えることを特徴とする請求項 1 記載のスイッチング電源装置。

#### 【請求項3】

前記<u>平滑コンデンサの端子間に接続される</u>負荷<u>が</u>、LEDであることを特徴とする請求項1または2記載のスイッチング電源装置。

#### 【請求項4】

前記基準電圧源は、調光器を備え、調光量に応じて前記基準電圧を変化することを特徴とする請求項3記載のスイッチング電源装置。

【発明の詳細な説明】

### 【技術分野】

#### [0001]

本発明は、入力電源側と絶縁された直流安定化電圧・電流を出力するスイッチング電源装置に関し、特にスイッチング素子の損失低減、および小型・低コスト化を図るものに関する。

# 【背景技術】

# [0002]

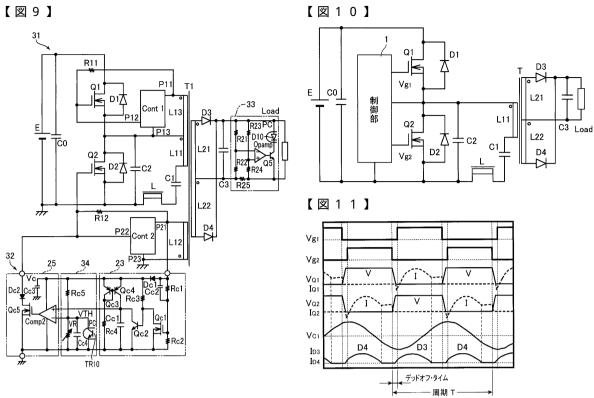

従来、上述のような小型高効率のスイッチング電源として、複合共振型の直列コンバータ回路が知られ、特許文献1など多くの公知技術が示されている。図10にその従来技術による主回路構成を、図11に主な部位の波形を示す。

#### [0003]

このスイッチング電源装置では、直流入力電源Eの両端子間に、スイッチング素子Q1とQ2(以下、パワーMOSFETで記述)との直列回路が接続されるとともに、コンデンサC0が接続される。そして、前記パワーMOSFETQ1,Q2の接続点と前記直流入力電源Eの一端との間に、インダクタLと出力トランスTの1次巻線L11とコンデンサC1との直列共振回路を形成し、前記パワーMOSFETQ1またはQ2の何れかと並列にコンデンサC2が接続される(図10では、直流入力電源Eの一端は低圧側に、コンデンサC2はパワーMOSFETQ2に並列に接続した例を示している)。また、パワーMOSFETQ1,Q2には、それぞれ逆並列にダイオードD1,D2が接続される(パワーMOSFETQ1,Q2のボデイダイオードで兼用される場合が多い)。

# [0004]

さらに前記出力トランスTの出力巻線に中間タップを設けて2分割(L21,L22)し、それらの出力を整流するダイオードD3,D4で全波整流回路を形成し、前記中間タップとの間に平滑コンデンサC3および直流負荷Loadが接続される。前記のパワーMOSFETQ1,Q2は、ブロックで示した制御部1によって、複合共振条件を加味して予め設定された周波数で交互にON/OFFされる。したがって、制御部1には、高周波発振機能、2つのパワーMOSFETQ1,Q2を交互に駆動する機能、および2つのパワーMOSFETQ1,Q2を交互に駆動する機能、および2つのパワーMOSFETQ1,Q2を共にOFFするデットタイム期間を設定する機能、必要に応じて入出力電圧や電流、電力を制御する為のフィードフォワードやフィードバック制御機能ならびに出力可変機能などが備えられる。

### [0005]

図11を参照して、Vg1,Vg2は制御部1によって予め設定されたパワーMOSFETQ1,Q2の駆動信号を示す。交互にON/OFFさせるとともに、両方共にOFFするデットタイム期間が設定されている。VQ1,IQ1およびVQ2,IQ2は、パワ

10

20

30

40

ーMOSFETQ1,Q2のドレイン・ソース間電圧およびドレイン電流を示す。駆動信 号Vg1がHighの時、パワーMOSFETQ1にはドレイン電流IQ1が流れ、Lo wの時は略直流入力電源 E に等しい電圧 V Q 1 が印加される(パワーMOSFETQ 2 の 場合も同様)。なお、デットタイム期間においては、コンデンサC2とインダクタLおよ び出カトランスTの励磁インダクタンスとによる効果から、ドレイン・ソース間電圧VQ 1 , VO2は任意の傾斜を持った立上がり、立下り波形となる。また、ドレイン電流IO 1,IQ2は、略インダクタLとコンデンサC1とで設定される直列共振電流波形となり 、これらの合成電流がインダクタLと出力トランスTの1次巻線L11とコンデンサC1 との直列共振回路の電流となる。VC1はコンデンサC1の電圧波形を表しており、前記 の直列共振回路の電流より位相の遅れた波形となる。ID3,ID4は出力整流のダイオ ードD3,D4の電流波形を示すもので、前記のパワーMOSFETQ1,Q2の駆動周 波数と、インダクタLおよびコンデンサC1の直列共振周波数との関係を、「共振周波数 > 駆動周波数」の条件を満足させることによって、ダイオードD3,D4の一方の電流が 流れ終わった後に他方の電流が流れ始めるように設定が可能で、両方のダイオード電流が 流れない期間は出力側へ電力が伝達されない。すなわち、前記ダイオードD3,D4の電 流が流れない期間では、出力トランスTの2次側は無負荷と考えられ、1次側の直列共振 回路にトランスTの1次側励磁インダクタンスLが直列に挿入されて直列共振条件が切り 替わる結果、ドレイン電流IQ1およびIQ2の波形にも変曲点が見られる。

### [0006]

このような複合共振型直列コンバータでは、 Z V S (ゼロ電圧スイッチング)、すなわちスイッチング素子Q 1 , Q 2 の印加電圧が低下した後に電流が流れ始めるような条件設定が可能とされ、スイッチング損失が極めて少ないこと、および 2 次側整流ダイオード D 3 , D 4 のリカバリ損失を回避できることから、高効率で高周波化が可能となる。また、スイッチング時の電圧・電流波形が安定しているとともに、 2 次側整流ダイオード D 3 , D 4 のリンギングも抑制できることから、雑音面でも優れている。

### [0007]

上述の従来技術は、このような数々の特徴を有しながらも、周波数を予め発振器で設定し、2つのスイッチング素子Q1,Q2を駆動する所謂他励式のスイッチング電源装置であり、その場合、高電位側のスイッチング素子Q1,Q2へのレベルシフタが必要で、その周波数追従性や損失の観点から、高周波化に対する技術課題を有し、またコスト面での課題などから、たとえば特許文献2~4で示すような自励式の検討もなされている。

# [0008]

図12は、電流帰還型の自励式複合共振直列コンバータの公知例を示す電気回路図であり、前記特許文献2に示されたものである。主回路構成は概ね図10と同様であるが、入力電源は商用電源を全波整流にて用いるとともに、出力トランスT02の2次側は整流ブリッジDBによる全波整流回路としている。スイッチング素子TR1,TR2はバイポーラトランジスタで構成し、その駆動は電流帰還トランスT01の2次巻線LB1およびLB2を利用し、逆バイアス手段によるデットタイムの確保や駆動条件の改善がなされている。

### [0009]

一方、図13は、電圧帰還型の自励式複合共振直列コンバータの公知例を示す電気回路図であり、前記特許文献3に示されたものである。スイッチング素子であるバイポーラトランジスタTR1,TR2への帰還信号を出力トランスPITに帰還巻線NB2を設けて得るものとし、負荷変動対策や出力安定化の為のフィードバック制御を付加している。

#### [0010]

これら図12および図13で示す自励式複合共振直列コンバータの従来例は、駆動回路の簡易化の可能性を示唆するものであるが、図10を基に説明した他励式複合共振直列コンバータの数々の特徴を同様に実現するのは、下記の点から難しいと考えられる。先ず、駆動周波数を決定するのは帰還回路の時定数や遅延要素であり、負荷変動など外部要因の変動に対して、前記ZVSなど最適なスイッチング条件の維持が難しいと思われる。次に

10

20

30

40

、スイッチング素子としてバイポーラトランジスタが想定され、高周波化には適しないと 思われる。

# [0011]

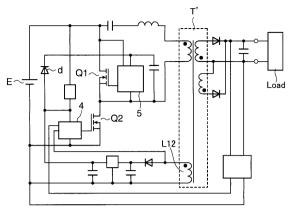

そこで、図14はパワーMOSFETを用いた電圧帰還型の自励他励式複合共振直列コンバータの公知例を示すブロック図であり、前記特許文献4に示されたものである。この従来技術では、スイッチング素子としてパワーMOSFETQ1,Q2を使用し、出力トランスT'の補助巻線L12から主制御回路4および副制御回路5の電源を確保するとともに、この巻線電圧を信号源として、負荷Loadへの供給電圧が一定になるように主制御回路4は低圧側のパワーMOSFETQ2のON/OFFを制御し、副制御回路5は高圧側のパワーMOSFETQ1の端子間電圧が基準電圧より低下したときにONさせ、該高圧側パワーMOSFETQ1のZVSを維持するものである。

【特許文献1】特許第2734296号公報

【特許文献2】特許第3371595号公報

【特許文献3】特開2002-262568号公報

【特許文献 4 】特開 2 0 0 6 - 1 2 9 5 4 8 号公報

【発明の開示】

【発明が解決しようとする課題】

#### [0012]

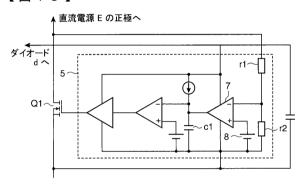

上述の従来技術では、副制御回路 5 には、図15 に示すような具体例が示され、前記パワーMOSFETQ1のドレイン・ソース間電圧を抵抗<u>r1</u>と<u>r2</u>とで分圧し、コンパレータ7にて基準電圧 8 と比較して、積分回路のコンデンサ c 1 の充放電によってパワーMOSFETQ1をONさせている。このような構成では、高圧側のパワーMOSFETQ1のドレイン・ソース間電圧を直接判別しながらONのタイミングを決定するので、前記 Z V S が実現される可能性はあるが、下記のような課題を有すると考えられる。先ず、パワーMOSFETQ1のドレイン・ソース間電圧を分圧する必要があり、前記抵抗<u>r1</u>, <u>r2</u>による損失が懸念される。一方、これらの抵抗<u>r1</u>, <u>r2</u>を高抵抗で構成する場合は、コンパレータ7の入力容量による遅延時間が想定され、高周波化が難しいと思われる。次に、駆動制御回路 4 ,5 が複雑化し、他励方式に対する優位性が認められない。

# [0013]

本発明の目的は、電圧帰還型の自励式複合共振直列コンバータにおいて、本来の特徴である低損失・低雑音化を維持しながら、他励式に比べて大幅な回路の簡素化、低コスト化を実現することができるスイッチング電源装置を提供することである。

【課題を解決するための手段】

# [0014]

本発明のスイッチング電源装置は、直流入力電源の両端子間に第1および第2のスイッ チング素子から成る直列回路が接続され、前記第1および第2のスイッチング素子の接続 点と前記直流入力電源の一方の端子との間に、インダクタ、コンデンサおよびトランスの 1次巻線から成る直列回路が接続され、前記第1および第2のスイッチング素子のスイッ チングにより得られたトランスの2次側誘起電流をダイオードおよび平滑コンデンサによ って整流・平滑化して出力し、第1および第2の制御回路が前記トランスの第1および第 2の補助巻線に誘起された電圧で前記第1および第2のスイッチング素子をそれぞれON / OFFすることでスイッチングを継続するようにした電圧帰還型の自励式複合共振直列 コンバータから成るスイッチング電源装置において、前記第1および第2の制御回路は、 前記第1および第2のスイッチング素子をそれぞれOFFさせるための第3および第4の スイッチング素子と、前記第1および第2の補助巻線に生じる誘起電圧をピークホールド するピークホールド回路と、前記誘起電圧が前記ピークホールド回路によるホールド電圧 より予め定めるレベル以上低下したときに前記第3および第4のスイッチング素子をON して前記第1および第2のスイッチング素子をそれぞれOFFさせる第1の比較器とを備 えて構成され、前記第1および第2の補助巻線の少なくとも一方に誘起された電圧が対応 する前記第1および第2のスイッチング素子の少なくとも一方を順バイアスする方向に発 10

20

30

40

生した時点を起点として三角波を発生する三角波発生回路と、可変の基準電圧を発生する 基準電圧源と、前記第1および第2のスイッチング素子の少なくとも一方をOFFさせる ための第5のスイッチング素子と、前記三角波の電圧と基準電圧とを比較し、前記三角波 の電圧が基準電圧より高くなると前記第5のスイッチング素子をONさせる第2の比較器 とを備えて構成される出力調整回路を含むことを特徴とする。

#### [0015]

上記の構成によれば、直流入力電源の両端子間に第1および第2のスイッチング素子から成る直列回路が接続され、前記第1および第2のスイッチング素子の接続点と前記直流入力電源の一方の端子との間に、インダクタ、コンデンサおよびトランスの1次巻線から成る直列回路が接続され、第1および第2の補助巻線の誘起電圧を前記スイッチング素子のON/OFF駆動に用いる電圧帰還型の自励式複合共振直列コンバータから成るスイッチング電源装置において、その補助巻線の誘起電圧からスイッチング素子のON/OFF駆動を行う第1および第2の制御回路を、前記第1および第2のスイッチング素子をそれでれOFFさせるための第3および第4のスイッチング素子と、前記誘起電圧が前記ピークホールド回路によるホールド電圧より予め定めるレベル以上低下したときに前記第3および第4のスイッチング素子をONして前記第1および第2のスイッチング素子をそれぞれOFFさせる第1の比較器とを備えて構成する。

### [0016]

したがって、前記第1および第2の制御回路は、2次側平滑コンデンサの充電完了によって2次側誘起電流が流れなくなったことを、前記第1および第2の補助巻線の内、一方の電圧低下から検知して前記第1および第2のスイッチング素子の内のONしていた側をOFF駆動するとともに、他方の電圧上昇を検知して前記第1および第2のスイッチング素子の内のOFFしていた側をONさせることで前記スイッチングを継続させる。こうして、電圧帰還型の自励式複合共振直列コンバータにおいて、適切なスイッチング条件(ZVS動作)を簡易な構成で実現でき、本来の特徴である低損失・低雑音化を維持しながら、他励式に比べて大幅な回路の簡素化、低コスト化を実現することができる。また、より高周波化し、小型・高効率化にも適応できる。

# [0017]

さらに、前記第1および第2の補助巻線の少なくとも一方に誘起された電圧が対応する前記第1および第2のスイッチング素子を順バイアスする方向に発生した時点を起点として三角波を発生する三角波発生回路と、可変の基準電圧を発生する基準電圧源と、前記第1および第2のスイッチング素子の少なくとも一方をOFFさせるための第5のスイッチング素子と、前記三角波の電圧と基準電圧とを比較し、前記三角波の電圧が基準電圧より高くなると前記第5のスイッチング素子をONさせる第2の比較器とを備えて構成される出力調整回路をさらに設ける。

# [0018]

したがって、簡単な構成で、出力の可変機能或いは出力安定化の機能を付加することができる。

### [0019]

また、本発明のスイッチング電源装置は、2次側負荷電流または電圧を検出する負荷検出回路と、前記負荷検出回路の検出結果を1次側へフィードバックし、前記基準電圧源の基準電圧を変化するフィードバック回路とをさらに備えることを特徴とする。

# [0020]

上記の構成によれば、2次側の負荷電流または出力電圧が定電流または定電圧となるようにフィードバック制御を行うことができる。

#### [0021]

さらにまた、本発明のスイッチング電源装置では、前記<u>平滑コンデンサの端子間に接続</u>される負荷が、LEDであることを特徴とする。

# [0022]

10

20

30

上記の構成によれば、LEDの順方向電圧以上の電圧が印加されるまでは電流が流れず、起動時はいわゆる無負荷状態にあるため、電圧帰還型の自励式複合共振直列コンバータの起動性を改善するとともに、LED負荷着脱時などに発生するLEDへのラッシュ電流を抑制する効果がある。

# [0023]

好ましくは、前記基準電圧源は、調光器を備え、調光量に応じて前記基準電圧を変化することを特徴とする。

### 【発明の効果】

## [0024]

本発明のスイッチング電源装置は、以上のように、補助巻線の誘起電圧をスイッチング 素子のON/OFF駆動に用いる電圧帰還型の自励式複合共振直列コンバータから成るス イッチング電源装置において、第1および第2の補助巻線の誘起電圧からスイッチング素 子のON/OFF駆動を行う第1および第2の制御回路を、第1および第2のスイッチン グ素子をそれぞれOFFさせるための第3および第4のスイッチング素子と、前記第1お よび第2の補助巻線に生じる誘起電圧をピークホールドするピークホールド回路と、前記 誘起電圧が前記ピークホールド回路によるホールド電圧より予め定めるレベル以上低下し たときに前記第3および第4のスイッチング素子をONして前記第1および第2のスイッ チング素子をそれぞれOFFさせる第1の比較器とを備えて構成するとともに、前記第1 および第2の補助巻線の少なくとも一方に誘起された電圧が対応する前記第1および第2 のスイッチング素子を順バイアスする方向に発生した時点を起点として三角波を発生する 三角波発生回路と、可変の基準電圧を発生する基準電圧源と、前記第1および第2のスイ ッチング素子の少なくとも一方をOFFさせるための第5のスイッチング素子と、前記三 角波の電圧と基準電圧とを比較し、前記三角波の電圧が基準電圧より高くなると前記第5 のスイッチング素子をONさせる第2の比較器とを備えて構成される出力調整回路をさら に設ける。

### [0025]

それゆえ、前記第1および第2の制御回路は、2次側平滑コンデンサの充電完了によって2次側誘起電流が流れなくなったことを、前記第1および第2の補助巻線の内、一方の電圧低下から検知して前記第1および第2のスイッチング素子の内のONしていた側をOFF駆動するとともに、他方の電圧上昇で検知して前記第1および第2のスイッチング素子の内のOFFしていた側をONさせることで前記スイッチングを継続させる。こうして、電圧帰還型の自励式複合共振直列コンバータにおいて、適切なスイッチング条件を簡易な構成で実現でき、本来の特徴である低損失・低雑音化を維持しながら、他励式に比べて大幅な回路の簡素化、低コスト化を実現することができる。また、より高周波化し、小型・高効率化にも適応できる。さらに、簡単な構成で、出力の可変機能或いは出力安定化の機能を付加することができる。

# [0026]

また、本発明のスイッチング電源装置は、以上のように、2次側負荷電流または電圧を検出する負荷検出回路と、前記負荷検出回路の検出結果を1次側へフィードバックし、前記基準電圧源の基準電圧を変化するフィードバック回路とをさらに備える。

# [0027]

それゆえ、 2次側の負荷電流または出力電圧が定電流または定電圧となるようにフィードバック制御を行うことができる。

# [0028]

さらにまた、本発明のスイッチング電源装置は、以上のように<u>、負</u>荷をLEDとする。

# [0029]

それゆえ、LEDの順方向電圧以上の電圧が印加されるまでは電流が流れず、起動時はいわゆる無負荷状態にあるため、電圧帰還型の自励式複合共振直列コンバータの起動性を改善するとともに、LED負荷着脱時などに発生するLEDへのラッシュ電流を抑制する効果がある。

10

20

30

40

#### 【発明を実施するための最良の形態】

## [0030]

# 「実施の形態1]

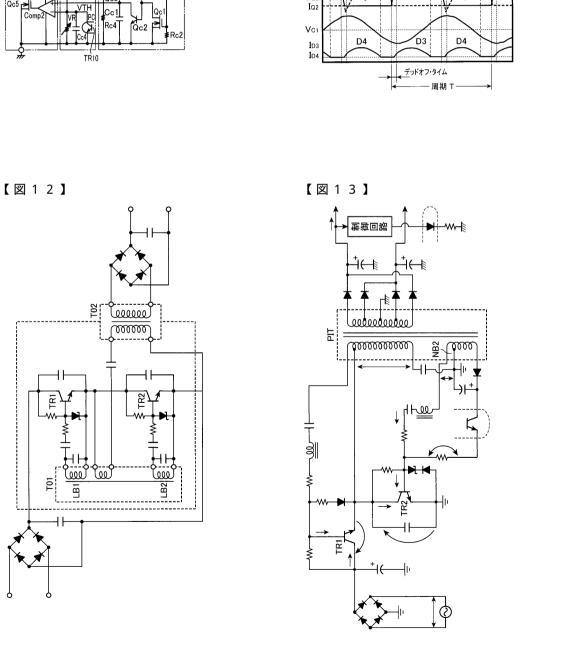

図1は、本発明の前提構成となるスイッチング電源装置11の電気的構成を示すブロック図である。このスイッチング電源装置11は、改良された電圧帰還型の自励式複合共振直列コンバータであり、本来の特徴であるスイッチング素子Q1,Q2の低損失・低雑音化を維持しながら、他励式に比べて大幅な回路の簡素化、低コスト化を図り、さらに動作の高周波化を可能とするものである。

# [0031]

図1において、直流入力電源Eの両端子間に、第1および第2の前記スイッチング素子Q1とQ2(以下、パワーMOSFETで記述)との直列回路が接続されるとともに、コンデンサC0が接続される。そして、前記パワーMOSFETQ1,Q2の接続点と前記直流入力電源Eの一端との間に、インダクタLと出力トランスT1の1次巻線L11とコンデンサC1との直列共振回路を形成し、前記パワーMOSFETQ1,Q2の何れかと並列にコンデンサC2が接続される(図1では、直流入力電源Eの一端は低圧側に、コンデンサC2はパワーMOSFETQ2に並列に接続した例を示している)。また、パワーMOSFETQ1,Q2には、それぞれ逆並列にダイオードD1,D2が接続される。なお、コンデンサC2は、パワーMOSFETQ1,Q2の接合容量で代用される場合もあり、ダイオードD1,D2も、前記パワーMOSFETQ1,Q2のボデイダイオードで兼用される場合もある。

#### [0032]

さらに前記出力トランスT1の出力巻線に中間タップを設けて2分割(L21,L22)し、それらの出力を整流するダイオードD3,D4で全波整流回路を形成し、前記中間タップとの間に平滑コンデンサC3および直流負荷Loadが接続される。また、前記出力トランスT1に補助巻線L12を設け、1次の主巻線L11と逆極性側をゲート抵抗R12を介してパワーMOSFETQ2のゲートに接続し、補助巻線L12に生じる電圧でパワーMOSFETQ2を駆動できるように構成する。高圧側のパワーMOSFETQ1のゲート駆動についても同様に、出力トランスT1に第2の補助巻線L13を設け、1次の主巻線L11と同一極性側をゲート抵抗R11を介して前記パワーMOSFETQ1のゲートに接続し、第2の補助巻線L13に生じる電圧でパワーMOSFETQ1を駆動できるように構成する。こうして、2つの補助巻線L13,L12からの帰還電圧によって、パワーMOSFETQ1,Q2が交互にON/OFFして自励発振する。

#### [0033]

ここで、注目すべきは、本構成では、各パワーMOSFETQ1,Q2には、そのOFFタイミングを設定するための制御回路Cont1,Cont2が設けられることである。なお、これらの制御回路Cont1,Cont2は同一構成であり、図面の簡略化のために、図1では制御回路Cont2についてのみ、具体的構成を示している。これらの制御回路Cont1,Cont2は、前記パワーMOSFETQ1,Q2のゲート・ソース間を短絡し、該パワーMOSFETQ1,Q2をOFFさせるための第3および第4のスイッチング素子であるスイッチ素子SW1と、ダイオードD5とコンデンサC4とで構成したピークホールド回路と、前記ダイオードD5の逆電圧を検出し、前記スイッチ素子SW1をONさせるための第1の比較器Comp1と、次のサイクルに備えてコンデンサC4の電荷を放電するための遅延回路2およびスイッチSW2とを備えて構成される。これらの制御回路Cont1,Cont2は、以下のような自励動作を行う。

# [0034]

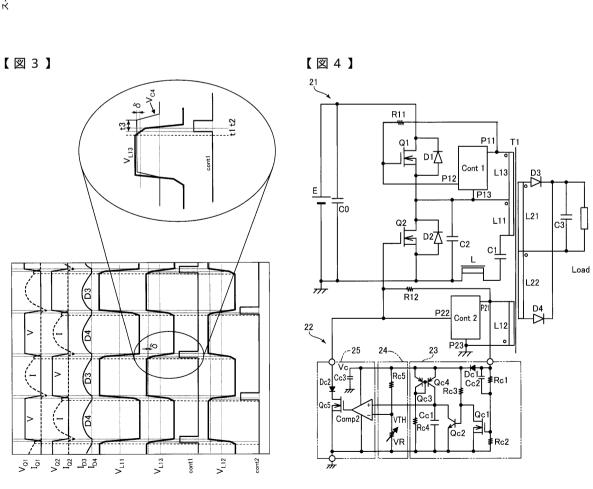

図2および図3に基づいて回路動作を説明する。図中VQ1,VQ2はパワーMOSFETQ1,Q2のドレイン・ソース間電圧、IQ1,IQ2はパワーMOSFETQ1,Q2のドレイン電流、VC1はコンデンサC1の電圧、ID3,ID4は出力整流ダイオードD3,D4のダイオード電流、VL11は出力トランスT1の1次巻線L11の電圧、VL12,VL13は出力トランスT1の補助巻線L12,L13の電圧、cont1

10

20

30

40

10

20

30

40

50

,cont2は制御回路Cont1,Cont2内で前記スイッチ素子SW1を駆動するための信号をそれぞれ表している。ただし、図2は、図1で示す本実施の形態の自励式複合共振直列コンバータの動作波形図ではなく、前述の図10で示す他励式複合共振直列コンバータの図11で示す動作波形図に、前記巻線L11,L1<u>3</u>の電圧VL11,VL13を詳しく示すものである。

# [0035]

図2を参照して、出力トランスT1の1次巻線L11に印加される電圧波形は、VL11のような波形となり、その相似した波形が補助巻線L12,L13に発生する。電流帰還の場合は正弦波状の共振電流が帰還されるのに対して、出力トランスT1からの電圧帰還においては前記VL11のような矩形波の電圧が帰還されるので、パワーMOSFETQ1,Q2の駆動に適することが理解される。しかしながら、VL11には2次側ダイオードD3,D4の電流ID3,ID4が途切れる区間に対応して、参照符号Pで示すような段差が存在する。本構成はこの段差Pに着目したものであり、スイッチング素子Q1,Q2をOFFさせるタイミングをこの段差Pの発生時とすることによって、下記の効果を狙ったものである。

#### [0036]

すなわち、段差Pの発生までの期間はインダクタLとコンデンサC1との直列共振周波数に依存し、安定した動作周波数設計が可能である。また、段差Pの発生は、出力側のダイオード電流ID3,ID4が途切れた結果であり、まさに他励式において理想とされるスイッチングOFFの動作ポイントで、出力ダイオードD3,D4のリカバリを抑制するとともに、スイッチング素子Q1,Q2のZVS動作が可能である。さらにまた、段差Pを検出する検出手段として用いる整流平滑回路によって、適度のデットオフタイムが生成可能で、ZVS動作実現に利用できる。これらの効果を以下に詳しく説明する。

#### [0037]

図3は、本構成に係る電圧帰還型の自励式複合共振直列コンバータの動作波形図である。図3を参照して、VL1<u>2</u>は補助巻線L1<u>2</u>に生じる帰還電圧波形を示し、VC4はピークホールド用のコンデンサC4の電圧を示しており、帰還電圧VL1<u>2</u>が正の間にコンデンサC4はダイオードD5のON電圧だけ低い電圧まで充電・保持される。VL1<u>2</u>に段差が発生した瞬間、VC4>VL1<u>2</u>の状態が発生してダイオードD5に逆電圧が印加される。時刻t1において、比較器Comp1でこの逆電圧をある閾値 で検出し、該比較器Comp1の出力でパワーMOSFETQ<u>2</u>のゲート・ソース間に接続されたスイッチ素子SW1をONさせることで、前記パワーMOSFETQ<u>2</u>がOFFする。その後、次のONサイクルに備えて遅延回路12で時間t3だけ遅延した後、コンデンサC4の電荷をスイッチ素子SW2によって放電させる結果、VC4はゼロにリセットされる。

# [0038]

こうして、補助巻線電圧VL1<u>2</u>に段差が発生した時点(前記時刻t1)でパワーMOSFETQ<u>2</u>のゲート・ソース間に設けたスイッチ素子SW1をONさせて該パワーMOSFETQ<u>2</u>をOFFさせる結果、補助巻線電圧VL1<u>2</u>は、時刻t2から速やかに低下し、適度なデットオフタイムを経て補助巻線L1<u>3</u>の電圧VL1<u>3</u>が立上がり、ゲート抵抗R11を介してパワーMOSFETQ1をONさせ、インダクタLとコンデンサC1との共振周波数で決まる一定期間後に段差を生じて、同様な動作を繰返すことによって、自励式であっても、パワーMOSFETQ1のドレイン・ソース間電圧VQ1、ドレイン電流IQ1およびパワーMOSFETQ2のドレイン・ソース間電圧VQ2、ドレイン電流 IQ2、ならびにダイオード電流ID3,ID4は、前記図11で示す他励式と極めて近似した波形が得られることが理解される。これによって、前述のように、スイッチング素 子Q1,Q2の低損失・低雑音化を維持しながら、他励式に比べて大幅な回路の簡素化、低コスト化を図り、さらに動作の高周波化(たとえば500kHz)を可能とすることができる。

## [0039]

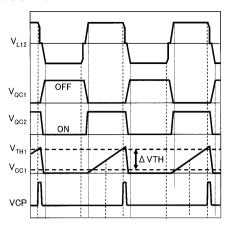

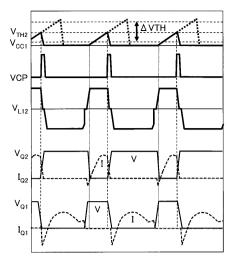

図4は、本発明の実施の第1の形態のスイッチング電源装置21の電気的構成を示すブ

10

20

30

40

50

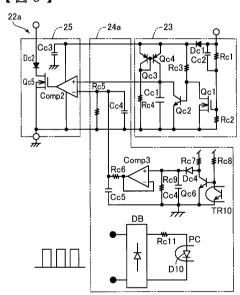

ロック図である。このスイッチング電源装置 2 1 において、前述のスイッチング電源装置 1 1 に対応する部分には同一の参照符号を付して示し、その説明を省略する。注目すべき は、本発明では、前記第 1 および第 2 の補助巻線 L 1 3 , L 1 2 の少なくとも一方(図 4 の例では低圧側のスイッチング素子 Q 2 に対応する第 2 の補助巻線 L 1 2 のみ)に関して、出力調整回路 2 2 が設けられていることである。図 5 および図 6 は、このスイッチング電源装置 2 1 の動作を説明するための波形図である。

#### [0040]

前記出力調整回路22は、補助巻線L12に誘起された電圧が、対応するスイッチング素子Q2を順バイアスする方向に発生した時点を起点として三角波を発生する三角波発生回路23と、可変の基準電圧VTHを発生する基準電圧源24と、前記三角波の電圧と基準電圧VTHとを比較し、前記三角波の電圧が基準電圧VTHより高くなると対応する前記スイッチング素子Q2のゲート・ソース間を短絡する比較回路25とを備えて構成される。この出力調整回路22内では、出力トランスT1の補助巻線L12の非グランド側端子からダイオードDc1およびコンデンサCc3によって制御用電源Vcを作成している

#### [0041]

前記三角波発生回路23において、出力トランスT1の補助巻線L12の非グランド側端子から抵抗Rc1,Rc2で分圧回路を形成し、その接続点をFETQc1のゲート端子に接続する。この抵抗Rc1に並列のコンデンサCc2は極性反転時のスピードアップ用である。したがって、図5で示すように、補助巻線L12の電圧VL12がパワーMOSFETQ2のゲートを順バイアスする方向に発生しているとき、参照符号VQC1で示すように(ドレイン・ソース間電圧)前記FETQc1はONとなり、その反転回路を形成するトランジスタQc2は参照符号VQC2で示すようにOFFとなっている。

#### [0042]

一方、前記制御用電源VcからトランジスタQc3,Qc4をミラー構成として、ダイオード構造のトランジスタQc3に接続される抵抗Rc4に基準電流を流し、反対のトランジスタQc4に接続されるコンデンサCc1を充電する回路を設けるとともに、そのコンデンサCc1の端子間に放電回路として前記トランジスタQc2を接続する。したがって、補助巻線L12の電圧VL12がパワーMOSFETQ2のゲートを逆バイアスする方向に発生しているとき、すなわち前記トランジスタQc2がONしているときは、カレントミラー回路による充電は行われず、補助巻線L12の電圧VL12がパワーMOSFETQ2のゲートを順バイアスする方向に発生する、すなわち前記トランジスタQc2がOFFしたときには、充電が行われ、コンデンサCc1の端子電圧は、参照符号VCC1で示すように、三角波状に上昇する。

# [0043]

そして、このコンデンサC c 1 の電位が、前記制御電源 V c を、前記基準電圧源 2 4 の抵抗 R c 5 と可変抵抗 V R とで分圧した値(前記基準電圧) V T H を超えたとき、参照符号 V C P で示すように、比較回路 2 5 内の第 2 の比較器 c o m p 2 の出力はハイレベルとなり、その出力側のFETQ c 5 を O N させ、前記パワーMOSFETQ 2 のゲート・ソース間を短絡して該パワーMOSFETQ 2 をターンOFFさせる。前記可変抵抗 V R の抵抗値を変化して比較器 C o m p 2 の基準電圧 V T H を V T H の範囲で変化することで、パワーMOSFETQ 2 のターンOFFのタイミングを、図 5 で示す(V T H = V T H 1)前記制御回路 C o n t 2 のハイレベルタイミング(フルデューティ)以降から、図 6 で示す(V T H = V T H 2)ように速めることができる。これによって、簡単な構成で、パワーMOSFETQ 2 のON幅を変化させ、出力調整を行うことができる。

# [0044]

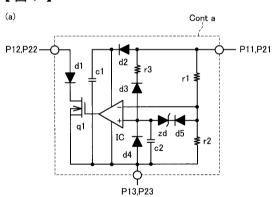

図7は、前記図1および図4の制御回路Cont1,Cont2の具体的な他の構成例である制御回路Conta,Contbの回路図である。図7(a)で示す制御回路Contaでは、端子P11-P13;P21-P23間に入力される電圧帰還信号を、抵抗r1,r2で分圧し、その分圧された電圧をコンパレータICの-端子へ供給している。

またこの分圧電圧で、ダイオードd5およびツエナーダイオードzdを介してコンデンサ c2を充電するとともに、その充電電圧を前記コンパレータICの+端子に供給している。このような構成によって、帰還電圧が所定値以下に低下した場合、前記分圧点の電位も低下し、-端子の電位が+端子の電位以下となってコンパレータICの出力がハイレベルとなり、これによってMOSFETq1がONし、端子P12-P13; P22-P23間を短絡、すなわちパワーMOSFETQ1,Q2をOFFさせることができる。図中、ダイオードd2とコンデンサc1とは、コンパレータICの電源を形成し、またダイオードd3,d4および抵抗r3は、コンデンサc2の電荷を引き抜く回路を形成している。このようなダイオードd5およびツエナーダイオードzdによって、前記コンパレータICの閾値設定の自由度が高くなっている。

[0045]

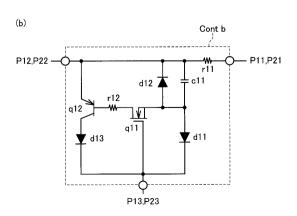

また、図7(b)で示す制御回路Contbでは、前記端子P11-P13;P21-P23間に入力される電圧帰還信号を、抵抗 r 11とダイオード d 11とを介してコンデンサ c 11に蓄積 U、前記帰還電圧がMOSFET q 11のゲートスレシホールド電圧以上に低下した場合に前記MOSFET q 11をONさせて、該コンデンサ c 11の電荷を放出させるとともに、その放電電流で p n p 型のバイポーラトランジスタから成るスイッチ素子 q 12をONさせ、端子P12-P13;P22-P23間を短絡、すなわちパワーMOSFETQ1,Q2をOFFさせている。なお、各端子P11~P13;P21~P23の対応関係は、図1および図4に示す。

[0046]

「実施の形態21

図8は、本発明の実施の第2の形態のスイッチング電源装置における出力調整回路22 aの構成を示すブロック図である。本実施の形態では、この出力調整回路22a以外の構成は、前述のスイッチング電源装置21と同一であり、省略している。またこの出力調整回路22aにおいて、前述の出力調整回路22とは、基準電圧源24aの構成が異なるだけである。具体的には、前記基準電圧源24では、可変抵抗VRを用いているのに対して、本実施の形態では、外部の調光器DBを用いることである。

[0047]

前記調光器 D B に対応した照明負荷の内、前記負荷 L o a d には、L E D が好ましい。それは、L E D の順方向電圧 V f 以上の電圧(直列構成の場合はその n 倍)が印加されるまでは電流が流れず、起動時はいわゆる無負荷状態にあるため、電圧帰還型の自励式複合共振直列コンバータの起動性を改善するとともに、L E D 負荷着脱時などに発生する L E D へのラッシュ電流を抑制する効果があるためである。

[0048]

前記基準電圧源 2 4 a では、前記調光器 D B からは調光量に応じたデューティの P W M 信号が出力され、その P W M 信号で抵抗 R c 1 1 を介してフォトカプラ P C のフォトダイオード D 1 0 が点灯駆動される。一方、抵抗 R c 8 でバイアスされているフォトトランジスタ T R 1 0 は、前記 P W M 信号に応じて O N / O F F し、それをトランジスタ Q c 6 および抵抗 R c 7 から成る反転回路で反転した後、ダイオード D c 4 、コンデンサ C c 4 および抵抗 R c 9 によって平滑化する。そのコンデンサ C c 4 の充電電圧が、インピーダンス変換器 C o m p 3 を介してインピーダンス変換され、抵抗 R c 6 を介してコンデンサ C c 5 に前記 P W M 信号のパルス幅(デューティ)に応じた直流電圧が作成される。この直流電圧を前記基準電圧 V T H として用いる。

[0049]

このように構成することで、外部からのPWM信号によってコンバータの出力を可変、 すなわち調光を行うことができる。

[0050]

[実施の形態3]

図9は、本発明の実施の第3の形態のスイッチング電源装置31の電気的構成を示すブロック図である。このスイッチング電源装置31は、前述のスイッチング電源装置21に

10

20

30

40

類似し、対応する部分には同一の参照符号を付して示し、その説明を省略する。注目すべきは、このスイッチング電源装置31では、2次側に負荷電流検出回路33が設けられ、 その検出結果を1次側へフィードバックすることである。

## [0051]

詳しくは、前記負荷電流検出回路33では、抵抗R21,R22の直列回路および抵抗R23,R24の直列回路が出力の平滑コンデンサC3と並列に接続され、2つの直列回路間に電流検知抵抗R25が設けられる。前記電流検知抵抗R25による電圧降下が前記抵抗R21,R22;R23,R24の接続点間から取出され、エラーアンプOpampによって増幅される。一方、前記平滑コンデンサC3と並列に、フォトカプラPCの発光ダイオードD10とトランジスタQ5との直列回路が設けられており、前記エラーアンプOpampの出力がトランジスタQ5のベースに与えられ、負荷電流による電流検知抵抗R25の電圧降下が大きくなる程、発光ダイオードD10の輝度が大きくなる。

#### [0052]

これに対して、1次側では、基準電圧源34において、前記可変抵抗VRと並列に、コンデンサCc4および前記フォトカプラPCのフォトトランジスタTR10が設けられており、前記発光ダイオードD10の輝度が大きくなる、すなわち負荷が大きい程、コンデンサCc4の端子電圧、すなわち前記基準電圧VTHが低くなり、デューティが大きくなる。こうして、電流検知抵抗R25の電圧降下が一定値になるようにフィードバック制御が行われ、フォトカプラPCはフィードバック回路を構成する。なお、フィードバックするのは、2次側の上述のような負荷電流に限らず、出力電圧や出力電力などの他のパラメータ、或いは前記負荷電流、出力電圧および出力電力の内任意の2つ以上の組合わせが用いられてもよい。

### [0053]

以上の説明において入力電源を直流電源Eとして説明したが、商用電源を整流・平滑化して用いてもよい。また出力トランスT1の2次側はセンタータップを設けて整流回路を構成する例で説明したが、整流ブリッジによる方法でも動作などは同じである。さらに、複合共振回路を形成するキャパシタC2については、第1および第2のスイッチング素子Q1,Q2の少なくとも一方に設けるものとするが、動作周波数が高い場合は、パワーMOSFETQ1,Q2の寄生容量(Crss)で代用することが可能である。

# 【図面の簡単な説明】

[0054]

- 【図1】本発明の前提構成となるスイッチング電源装置の電気的構成を示すブロック図で ある。

- 【図2】図10で示す従来の他励式複合共振直列コンバータの動作波形を詳しく示す図である

- 【図3】図1で示す構成に係る電圧帰還型の自励式複合共振直列コンバータの動作波形図である。

- 【図4】本発明の実施の第1の形態のスイッチング電源装置の電気的構成を示すブロック図である。

- 【図5】図4で示す本発明の実施の第1の形態に係る電圧帰還型の自励式複合共振直列コンバータの動作波形図である。

- 【図 6 】図 4 で示す本発明の実施の第 1 の形態に係る電圧帰還型の自励式複合共振直列コンバータの動作波形図である。

- 【図7】図1および図4で示すコンバータの具体的な回路例を示す図である。

- 【図8】本発明の実施の第2の形態のスイッチング電源装置における出力調整回路の構成を示すブロック図である。

- 【図9】本発明の実施の第3の形態のスイッチング電源装置の電気的構成を示すブロック図である。

- 【図10】他励式複合共振直列コンバータの基本構成を示す回路図である。

- 【図11】図10の動作波形図である。

20

10

30

50

- 【図12】従来の自励(電流帰還)式複合共振直列コンバータの例を示す回路図である。

- 【図13】従来の自励(電圧帰還)式複合共振直列コンバータの例を示す回路図である。

- 【図14】従来の自励(電圧帰還)式複合共振直列コンバータの他の例を示す回路図であ

- 【図15】図14で示すコンバータの制御回路の具体例を示すブロック図である。

### 【符号の説明】

#### [0055]

- 11,21,31 スイッチング電源装置

- 1 2 遅延回路

- 22,22a,32 出力調整回路

- 三角波発生回路

- 24,24a,34 基準電圧源

- 2 5 比較回路

- 3 3 負荷電流検出回路

- C 0 , C 1 , C 2 , C 4 コンデンサ

- 平滑コンデンサ C 3

- Comp1,Comp2 比較器

- Comp3 インピーダンス変換器

- Cont1, Cont2, Conta, Contb 制御回路

- D 1 , D 2 , D 3 , D 4 , D 5 ダイオード

直流入力電源 Е

インダクタ L

Load 直流負荷

- Opamp エラーアンプ

- PC フォトカプラ

- Q 1 , Q 2 スイッチング素子 (パワーMOSFET)

- R 2 5 電流検知抵抗

- SW1 スイッチ素子

- SW2 スイッチ

- T1 出力トランス

10

20

【図1】 【図2】 ខ 富大。 22 4本 P21 L12 E :  $V_{L11}$ C4 g <u>v</u> <u>a</u> M t1 t2 8 ╗ スイッチング電源装置

【図5】

【図6】

【図7】

【図8】

# 【図14】

【図15】

# フロントページの続き

(51) Int.CI.

H 0 5 B 37/02

(72)発明者 西野 博之

大阪府門真市大字門真1048番地 松下電工株式会社内

FΙ

(72)発明者 塩濱 英二

大阪府門真市大字門真1048番地 松下電工株式会社内

審査官 永田 和彦

(56)参考文献 特許第2734296(JP,B2)

特許第3371595(JP,B2)

特開2002-262568(JP,A)

特開2006-129548(JP,A)

特開平10-98877(JP,A)

特開2005-318719(JP,A)

特開平3-135366(JP,A)

特開平8-289542(JP,A)

(58)調査した分野(Int.CI., DB名)

H02M 3/00-3/44,

H05B 37/00-37/04,

H01L 33/00