(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第4213153号 (P4213153)

(45) 発行日 平成21年1月21日(2009.1.21)

(24) 登録日 平成20年11月7日(2008.11.7)

(51) Int.Cl. F I

GO9F 9/30 (2006, 01) GO9F 9/30 338 G02F 1/1368 (2006, 01) GO2F 1/1368 G02F 1/13 (2006.01) GO2F 1/13101

平成17年11月1日(2005.11.1)

請求項の数 7 (全 17 頁)

(21) 出願番号 特願2005-318600 (P2005-318600) (22) 出願日 平成17年11月1日 (2005.11.1) (65) 公開番号 特開2007-4106 (P2007-4106A) (43) 公開日 平成19年1月11日 (2007.1.11)

(31) 優先権主張番号 94120905

審査請求日

(32) 優先日 平成17年6月23日 (2005. 6. 23)

(33) 優先権主張国 台湾 (TW)

||(73)特許権者 501358079

友達光電股▲ふん▼有限公司

AU Optronics Corpor

ation

台湾新竹市科学工業園區力行二路1号

No. 1, Lt-Hsin Rd, II, Science-Based Industrial Park, Hsinchu,

Taiwan, R. O. C.

||(74)代理人 100064584

弁理士 江原 省吾

|(74)代理人 100093997

弁理士 田中 秀佳

|(74)代理人 100101616

弁理士 白石 吉之

最終頁に続く

(54) 【発明の名称】アクティブ・マトリクス基板と画素ユニットの修正方法

## (57)【特許請求の範囲】

### 【請求項1】

基板と、基板上に配置した複数の走査線と、基板上に配置した複数のデータ線と、複数の画素ユニットを有するアクティブ・マトリクス基板であって、

各画素ユニットが、走査線の一つとデータ線の一つに電気的に接続され、

前記画素ユニットの少なくとも一部がさらに、走査線の一つとデータ線の一つに電気的に接続した複数の能動素子と、能動素子の一つに電気的に接続した画素電極とを有し、

複数の能動素子が各々、画素電極に電気的に接続した第一能動素子と、画素電極から電 気的に分離した第二能動素子とを有し、

第一能動素子が第一TFTであり、

前記第一TFTが、走査線に電気的に接続した第一ゲート電極と、第一チャネル層と、 データ線に電気的に接続した第一ソース電極と、画素電極に電気的に接続した第一ドレイン電極とを有し、

第二能動素子が第二TFTであり、

前記第二TFTが、走査線に電気的に接続した第二ゲート電極と、第二チャネル層と、 データ線に電気的に接続した第二ソース電極と、画素電極から電気的に分離した第二ドレ イン電極とを有し、

第二TFTが、走査線上に配置されており、

第二ドレイン電極が走査線に沿って両方向に延び、各々の端部が、データ線の両側で隣 り合う二つの画素電極の下側まで延びていることを特徴とするアクティブ・マトリクス基

板。

#### 【請求項2】

基板と、基板上に配置した複数の走査線と、基板上に配置した複数のデータ線と、複数 の画素ユニットを有するアクティブ・マトリクス基板であって、

各画素ユニットが、走査線の一つとデータ線の一つに電気的に接続され、

前記画素ユニットの少なくとも一部がさらに、走査線の一つとデータ線の一つに電気的 に接続した複数の能動素子と、能動素子の一つに電気的に接続した画素電極とを有し、

複数の能動素子が各々、画素電極に電気的に接続した第一能動素子と、画素電極から電 気的に分離した第二能動素子とを有し、

第一能動素子が第一TFTであり、

前記第一TFTが、走査線に電気的に接続した第一ゲート電極と、第一チャネル層と、 データ線に電気的に接続した第一ソース電極と、画素電極に電気的に接続した第一ドレイ ン電極とを有し、

第二能動素子が第二TFTであり、

前記第二TFTが、走査線に電気的に接続した第二ゲート電極と、第二チャネル層と、 データ線に電気的に接続した第二ソース電極と、画素電極から電気的に分離した第二ドレ イン電極とを有し、

第二TFTが、走査線上に配置されており、

第二ドレイン電極が走査線の両側方へ向かって延び、各々の端部が、走査線の両側で隣 り合う二つの画素電極の下側まで延びていることを特徴とするアクティブ・マトリクス基 板。

#### 【請求項3】

第二チャネル層が、走査線とデータ線の交差部に配置され、走査線とデータ線の間に挟 持されている請求項1又は2に記載のアクティブ・マトリクス基板。

#### 【請求項4】

第二ドレイン電極が、走査線の上側から走査線の片側に沿って、画素電極の下側まで延 びている請求項1又は2に記載のアクティブ・マトリクス基板。

#### 【請求項5】

請求項1又は2に記載のアクティブ・マトリクス基板の画素ユニットを修正するための 方法であって、

走査線およびデータ線と第一能動素子の接続を切断し、走査線およびデータ線から第一 能動素子を分離し、

第二能動素子を画素電極と電気的に接続することを特徴とするアクティブ・マトリクス 基板の修正方法。

#### 【請求項6】

走査線およびデータ線と第一能動素子の接続の切断が、レーザ切断プロセスを有する請 求項5載の方法。

#### 【請求項7】

画素電極と第二能動素子の電気的に接続が、レーザ溶接プロセスまたはレーザ化学気相 成プロセスを有する請求項5記載の方法。

【発明の詳細な説明】

## 【技術分野】

# [0001]

この発明は、アクティブ・マトリクス基板とその修正方法に関し、特に、冗長的能動素 子を備えたアクティブ・マトリクス基板とその修正方法に関する。

#### 【背景技術】

## [00002]

表示技術は、陰極線管(CRT)を用いた最初の白黒TV以来、継続的かつ急速に発展 している。しかし、CRT表示装置は、分厚さ、重量、高電磁波、および相対的に画質が 低いという欠点を有する。従って、他の新型平板表示技術が次第に発展しており、とりわ 10

20

30

40

け空間利用率のよさ、低消費電力、低電磁波および携帯性のよさといった利点を備えた液晶表示装置(LCD)が最も成熟し、一般的な技術となっている。LCDは、携帯電話、デジタルカメラ、デジタル・ビデオカメラ、携帯情報端末、ノートブックPCおよび液晶TVの分野で広く用いられている。

## [0003]

LCD技術は成熟の傾向にあるが、LCDパネル製造プロセス中に、いくつかの欠陥が生じることは避けられず、LCDパネルの表示画像のために、やや視覚的不快感を引き起こすことがある。そして、このようなLCDパネルをそのまま廃棄すると、製造コストが実質的に上昇することになる。一般に、製造プロセス技術を改善することだけでは欠陥率0を達成することは非常に難しく、LCDパネルの欠陥修正技術がますます重要になっている。既存の技術では、LCDパネル欠陥修正にレーザ切断またはレーザ溶接がしばしば採用されている。例としてTFT-LCDを挙げると、レーザ切断またはレーザ溶接プロセスは、通常TFTアレイを製造した後に処理を行う。残念ながら、既存の画素構造設計のいくつかの欠点のために、全ての欠陥を素早く修正することはできず、そのいくつかは修正することさえできない。

#### [0004]

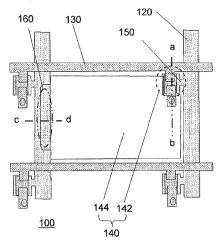

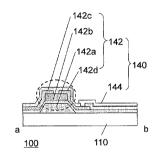

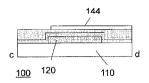

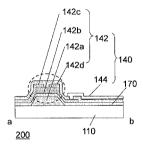

図1Aは既存のTFTアレイ基板の平面図であり、図1B、1Cは各々ラインa-b、およびラインc-dにおける図1Aの断面図である。図1A~1Cを共に参照すると、既存のTFTアレイ基板100は基板110、複数の走査線120、複数のデータ線130および複数の画素ユニット140を有し、走査線120、データ線130および画素ユニット140は全て基板110上に配置する。

#### [ 0 0 0 5 ]

画素ユニット 1 4 0 は、対応する走査線 1 2 0 とデータ線 1 3 0 に電気的に接続する。各画素ユニット 1 4 0 は、TFT 1 4 2 と、例えばインジウム錫酸化物(ITO)電極等の画素電極 1 4 4 を有する。従来の技術では、TFT 1 4 2 は、ゲート電極 1 4 2 a、アモルファス・シリコンのチャネル層 1 4 2 b、ソース電極 1 4 2 c およびドレイン電極 1 4 2 d を有する。ゲート電極 1 4 2 a は、走査線 1 2 0 と接続する。ゲート電極 1 4 2 a と走査線 1 2 0 は、第一金属層に属している。ソース電極 1 4 2 c は、データ線 1 3 0 と接続する。そしてデータ線 1 3 0、ソース電極 1 4 2 c およびドレイン電極 1 4 2 d は、第二金属層に属している。画素電極 1 4 4 は、ドレイン電極 1 4 2 d と電気的に接続する

# [0006]

しかし、欠陥のあるTFT142は、画素ユニット140の通常の動作を妨げることがある。このような欠陥は、TFT基板100とカラーフィルタ基板を組み合わせて液晶を充填した後のLCDパネル上の輝点欠陥に対応する。このようなLCDパネル上の輝点欠陥を避け、このような輝点欠陥を暗点に修正するために、レーザ修正プロセスが必要とされる。図1A~1Cを参照すると、既存の修正方法では、レーザ溶接プロセスによって隣接する走査線120と画素電極144を溶接することで、修正した画素ユニット140を暗点にする。

#### [0007]

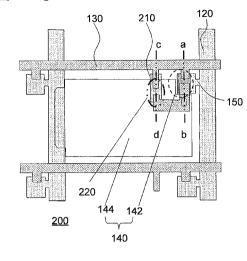

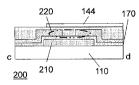

図2 A は別の既存のTFTアレイ基板の平面図であり、図2 B、2 C は各々ラインa-b およびライン c - d における図2 A の断面図である。図2 A ~ 2 C を共に参照すると、既存のTFT基板200は基板110、複数の走査線120、複数のデータ線130、複数の画素ユニット140、複数の修正ライン210、複数の修正構造220を有し、走査線120、データ線130、画素ユニット140、修正ライン210および修正構造220は基板110上に配置する。

#### [0008]

基板 1 1 0、走査線 1 2 0、データ線 1 3 0 および画素ユニット 1 4 0 は、TFTアレイ基板 1 0 0 上に配置した前述のものと同様である。修正構造 2 2 0 の端子の一つはデータ線 1 3 0 と接続し、修正構造 2 2 0 の他の端子はドレイン電極 1 4 2 d と接続する。修

10

20

30

40

正構造 2 2 0 は、第二金属層に属している。各修正ライン 2 1 0 は修正構造 2 2 0 の一つの下に配置し、修正ライン 2 1 0 は第一金属層に属している。ゲート絶縁層 1 7 0 は、修正ライン 2 1 0 と修正構造 2 2 0 の間に配置する。

#### [0009]

図2A~2Cを再び参照すると、欠陥のあるTFT142は、画素ユニット140の通常動作を妨げることがある。このような欠陥は、TFT基板100とカラーフィルタ基板を組み合わせて液晶を充填した後のLCDパネル上の輝点に対応する。このようなLCDパネル上の輝点欠陥を避けるために、レーザ切断プロセスを通常用いて、ゲート電極142aと走査線120の間の接続150を切断し、次にレーザ溶接プロセスで修正ライン210と修正構造220の二つの端子の間で溶接を行う。しかし、修正した画素ユニットは、輝点欠陥または暗点欠陥である。大型LCDパネルに補償フィルムを取り付け、視野角を向上させると、このような修正した画素ユニットは光漏れによって、所定の視野角で再び輝点欠陥を引き起こすことがある。

#### 【発明の開示】

【発明が解決しようとする課題】

# [0010]

以上の観点から、この発明は冗長的能動素子を備えたアクティブ・マトリクス基板を提供し、LCDパネル上の輝点欠陥を効率的に防ぐことを対象とする。

#### 【課題を解決するための手段】

#### [0011]

以上の観点から、この発明は画素ユニットの修正方法を提供することを対象とし、それによって修正された画素ユニットは通常動作可能で、LCDパネルの歩留まりを改善できる。

#### [0012]

以上のまたは他の目的に従って、この発明は、基板、複数の走査線、複数のデータ線および複数の画素ユニットを含むアクティブ・マトリクス基板を提供する。走査線、データ線、画素ユニットは全て、基板上に配置する。各画素ユニットは対応する走査線およびデータ線と電気的に接続し、画素ユニットの少なくとも一部は複数の能動ユニットと画素電極を有する。いくつかの能動ユニットを備えた画素ユニットにおいて、能動素子は対応する走査線およびデータ線と電気的に接続し、画素電極は能動素子の一つと電気的に接続する。

## [0013]

この発明の一実施例のアクティブ・マトリクス基板によると、能動素子は第一能動素子と第二能動素子を有する。第一能動素子は画素電極と電気的に接続し、第二能動素子は画素電極から電気的に分離する。

#### [0014]

この発明の一実施例のアクティブ・マトリクス基板によると、第一能動素子は第一ゲート電極、第一チャネル層、第一ソース電極および第一ドレイン電極を含む第一TFTであってもよい。さらに、前記第一ゲート電極は走査線と電気的に接続し、第一ソース電極はデータ線と電気的に接続し、第一ドレイン電極は画素電極と電気的に接続する。

# [0015]

この発明の一実施例のアクティブ・マトリクス基板によると、第二能動素子は第二ゲート電極、第二チャネル層、第二ソース電極および第二ドレイン電極を含む第二TFTであってもよい。さらに、前記第二ゲート電極は走査線と電気的に接続し、第二ソース電極はデータ線と電気的に接続し、第二ドレイン電極は画素電極から電気的に分離する。

# [0016]

この発明の一実施例のアクティブ・マトリクス基板によると、第二TFTは走査線上に配置する。

#### [0017]

この発明の一実施例のアクティブ・マトリクス基板によると、第二チャネル層は走査線

20

10

30

40

とデータ線の交差部に配置し、第二チャネル層は走査線とデータ線の間に挟持する。

#### [0018]

この発明の一実施例のアクティブ・マトリクス基板によると、第二ドレイン電極は走査線の上側から走査線の片側に沿って、画素電極の下側まで延びることができる。

#### [0019]

この発明の一実施例のアクティブ・マトリクス基板によると、第二ドレイン電極は走査線の上側から走査線の両側に沿って、画素電極の下側まで延びることができる。

#### [0020]

この発明は、前記アクティブ・マトリクス基板の画素ユニットを修正するための修正方法を提供する。修正方法は、次のステップを有する。まず、走査線およびデータ線と第一能動素子の接続を切断し、第一能動素子が走査線およびデータ線から電気的に分離されるようにする。それから、第二能動素子を画素電極と電気的に接続する。

#### [0021]

この発明の一実施例の修正方法によると、走査線およびデータ線と第一能動素子の接続の切断方法は、レーザ切断プロセスであってもよい。

#### [0022]

この発明の一実施例の修正方法によると、第二能動素子を画素電極と電気的に接続する ための方法は、レーザ溶接プロセスまたはレーザ化学気相成プロセス(レーザCVDプロ セス)であってもよい。

## 【発明の効果】

#### [0023]

この発明のアクティブ・マトリクス基板によると、各画素ユニットは複数の能動素子を有し、前記能動素子の一つは画素電極と電気的に接続する。画素電極と電気的に接続した能動素子が動作し損なうと、別の能動素子(例えば、冗長的な能動素子)を用いて、画素電極と電気的に接続し、元々画素ユニットを正常動作させていた能動素子の代わりとなり、LCDパネル上の輝点欠陥を避けることができる。

## 【発明を実施するための最良の形態】

#### [0024]

## (実施例1)

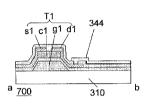

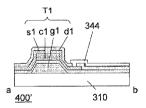

## [0025]

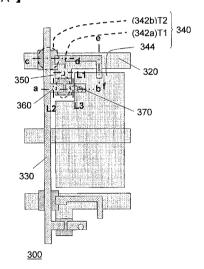

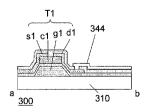

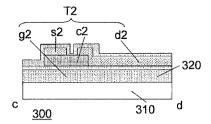

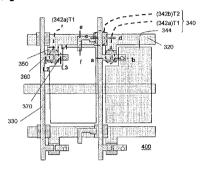

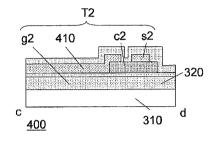

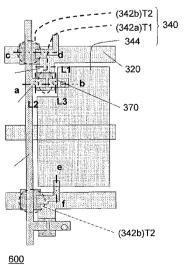

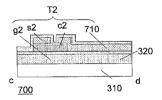

図3 A は、この発明の第一実施例によるアクティブ・マトリクス基板の平面図である。 図3 B、3 C、3 D は各々ライン a - b、ライン c - d、ライン e - f における図3 A の 断面図である。図3 A ~ 3 D を共に参照すると、アクティブ・マトリクス基板3 0 0 は基 板3 1 0、複数の走査線3 2 0、複数のデータ線3 3 0、複数の画素ユニット3 4 0 を有 する。走査線3 2 0、データ線3 3 0、画素ユニットは全て基板3 1 0 上に配置する。

# [0026]

基板 3 1 0 は、ガラス基板、石英基板または他の透明基板であってもよい。走査線は、アルミニウム合金または他の導電性材料からなる導線であってもよい。データ線 3 3 0 は、クロム、アルミニウム合金または他の導電性材料からなる導線であってもよい。詳細には、走査線 3 2 0 の延伸方向はデータ線 3 3 0 の延伸方向と直交し、基板 3 1 0 上の複数の画素領域(図示せず)を規定でき、画素ユニット 3 4 0 は画素領域に配置する。

#### [0027]

図3 Aから分かるように、画素ユニット3 4 0 は、対応する走査線3 2 0 とデータ線3 3 0 に各々電気的に接続する。各画素ユニット3 4 0 は、第一能動素子3 4 2 a、第二能動素子3 4 2 b および画素電極3 4 4 を有する。第一能動素子3 4 2 a と第二能動素子3 4 2 b は各々走査線3 2 0 とデータ線3 3 0 に電気的に接続し、画素電極3 4 4 は能動素子3 4 2 a の一つに電気的に接続する。当然のことながら、実施例では、発明を例示として、ここでは二つの能動素子を用いているが、この発明のよる画素ユニット3 4 0 は必要であれば三つ以上の能動素子を導入できる。さらに、画素電極3 4 4 は、透過型電極、反射型電極または半透過型電極であってもよい。上記のように、画素電極3 4 4 の材料はイ

10

20

30

40

ンジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、金属または他の導電性材料であってもよい。

#### [0028]

この実施例によると、第一能動素子342aは第一TFT T1であり、第二能動素子342bは第二TFT T2である。第一TFT T1は画素電極344と電気的に接続し、第二TFT T2は画素電極344から電気的に分離する。当然のことながら、この発明において画素ユニット340に三つ以上の能動素子を導入する場合、一つのみを画素電極344と電気的に接続し、他(つまり冗長的能動素子)は画素電極344から電気的に分離する。

## [0029]

をらに、第一TFT T1は第一ゲート電極g1、第一チャネル層c1、第一ソース電極s1および第一ドレイン電極d1を有する。第一ゲート電極g1は走査線320と電気的に接続し、ゲート電極g1の材料は走査線320と同様である。第一チャネル層c1の材料は、アモルファス・シリコン、多結晶シリコンまたは単結晶シリコンであってもよい。第一ソース電極s1はデータ線330と電気的に接続し、第一ソース電極s1の材料はデータ線330と同様である。同様に、第二TFT T2は、第二ゲート電極g2、第二チャネル層c2、第二ソース電極s2および第二ドレイン電極d2の材料は、TFT T1で説明したものと同様である。さらによび第二ドレイン電極d2の材料は、TFT T1で説明したものと同様である。さらに、第二ゲート電極は走査線320と電気的に接続し、第二ソース電極s2はデータ線330と電気的に接続し、第二ドレイン電極d2は画素電極344から電気的に分離する。

# [0030]

当然のことながら、この実施例の第二TFT T2は走査線320上に配置し、第二TFT T2の第二チャネル層 c 2は走査線320とデータ線330の交差部に配置して、第二チャネル層 c 2が走査線320とデータ線330の間に挟持されるようにする。さらに、この実施例の第二ドレイン電極 d 2は走査線320の上側から、走査線320の片側に沿って画素電極344の下側まで延びている。

### [0031]

第一TFT T1が損傷し、画素ユニット340の異常動作を引き起こした場合、アクティブ・マトリクス基板300とカラーフィルタ基板を組み合わせて液晶を充填した後、LCDパネル上に輝点欠陥が発生する。画素ユニット340の修正には、レーザ修正プロセスが必要とされる。再び図3A~3Dを参照すると、修正プロセスの第一ステップは、例えば、レーザ切断プロセスによって、第一TFT T1と走査線320の間の接続350、第一TFT T1とデータ線330の間の接続360、および第一TFT T1と走査線320の間の接続370の少なくとも一つを切断することである。第一TFT T1と走査線320から電気的に分離される。第一TFT T1とデータ線330の間を続360を切断ラインL2に沿って切断すると、第一TFT T1はデータ線330から電気的に分離される。第一TFT T1と画素電極344の間の接続370を切断ラインL3に沿って切断すると、第一TFT T1は画素電極344から電気的に分離される。の実施例によると、接続350、360、370の切断方法はレーザ切断プロセスであってもよい。

# [0032]

接続350、360、370を切断後、レーザ溶接プロセスによって画素電極344と第二ドレイン電極d2を溶接することで、第二TFT T2を画素電極344と電気的に接続する。この発明の別の実施例では、第二TFT T2は、レーザで第二ドレイン電極d2上の保護層を燃焼し、レーザCVDプロセスで薄い金属層を形成することで、画素電極344と電気的に接続される。このように修正した画素ユニットは、LCDパネル上に輝点欠陥を引き起こすことはない。

10

20

30

#### (実施例2)

## [0033]

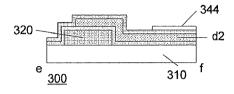

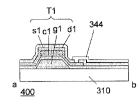

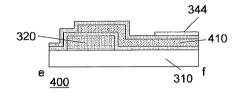

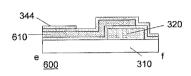

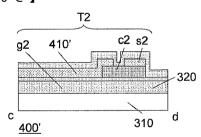

図4Aは、この発明の第二実施例によるアクティブ・マトリクス基板の平面図であり、図3Aの修正形態である。図4B、4C、4Dは各々、ラインa- b、ラインc- d、ラインe- fにおける図4Aの断面図である。図4A~4Dを共に参照すると、この実施例のアクティブ・マトリクス基板400は、走査線320の上側から走査線320の片側に沿って、隣の画素電極344の下側まで延びている隣の画素ユニット340内に、この実施例のアクティブ・マトリクス基板400の第二ドレイン電極410を配置している以外は、第一実施例のアクティブ・マトリクス基板300と同様である。

# [0034]

図4A~4Dを参照すると、隣の画素ユニット340の第一TFT T1(図4Aの左側に示した第一TFT T1)が損傷した場合、レーザ切断プロセスを行って、第一TFT T1と走査線320の間の接続350、第一TFT T1とデータ線330の間の接続360、および第一TFT T1と画素電極344の間の接続350を切断ラインL1に沿って切断すると、第一TFT T1と走査線320の間の接続350を切断ラインL1に沿って切断すると、第一TFT T1は走査線320から電気的に分離される。第一TFT T1とデータ線330の間の接続360を切断ラインL2に沿って切断すると、第一TFT T1とデータ線330から電気的に分離される。第一TFT T1と画素電極344の間の接続370を切断ラインL3に沿って切断すると、第一TFT T1は画素電極344から電気的に分離される。この実施例によると、接続350、360、370の切断方法は、レーザ切断プロセスであってもよい。

#### [0035]

当然のことながら、第二TFT T2の第二ドレイン電極410は隣の画素ユニット340内に配置し、走査線320の上側から、隣の画素ユニット340に向かって、画素電極344の下側まで延びているので、第二TFT T2は図4Aの左側に示した画素電極344と電気的に接続する必要がある。第二TFT T2の第二ドレイン電極を図4Aの左側に示した画素電極344と電気的に接続する方法は、レーザ溶接プロセスであってもよい。第二TFT T2の第二ドレイン電極を図4Aの左側に示した画素電極344と電気的に接続する別の方法では、レーザで第二TFT T2の第二ドレイン電極410上の保護層を燃焼し、次にレーザCVDプロセスで薄い金属層を形成することもできる。

# (実施例3)

[0036]

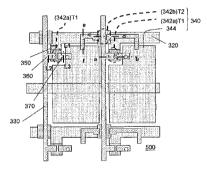

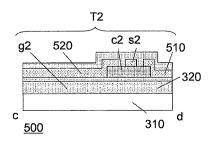

図5Aは、この発明の第三実施例によるアクティブ・マトリクス基板の平面図であり、図3Aの修正形態である。図5B、5C、5Dは各々、ラインa-b、ラインc-d、ラインe-fにおける図5Aの断面図である。図5A~5Dを共に参照すると、この実施例のアクティブ・マトリクス基板500は、偶数データ線330と走査線320の交差部のみに、この実施例のアクティブ・マトリクス基板500の第二TFT T2を形成する以外は、第一実施例のアクティブ・マトリクス基板300と同様である。従って、二つの隣の画素ユニット340は、共有型の第二TFT T2を有する。さらに、この実施例の第二TFT T2は、二つの第二ドレイン電極510、520は、データ線30に隣接する画素ユニット340に配置し、各々走査線320の上側から、走査線320の片側に向かって、画素電極344の下側まで延びている。

# [0037]

図5Aは、一対の画素ユニット340を示している。右側の画素ユニット340の第一 TFT T1が損傷した場合、右側の画素ユニット340を修正するために、第二ドレイン電極510を用いることができる。修正方法は、第一実施例の方法と同様である。左側の画素ユニット340の第一TFT T1が損傷した場合、左側の画素ユニット340を修正するために、第二ドレイン電極520を用いることができる。修正方法は、第二実施例の方法と同様である。 10

20

30

#### (実施例4)

## [0038]

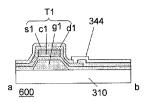

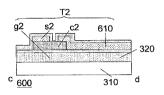

図6Aは、この発明の第四実施例によるアクティブ・マトリクス基板の平面図であり、図3Aの修正形態である。図6B、6C、6Dは各々、ラインa-b、ラインc-d、ラインe-fにおける図6Aの断面図である。図6A~6Dを共に参照すると、この実施例のアクティブ・マトリクス基板600は、第二ドレイン電極610が、走査線320の上側から、走査線320の片側に向かって、画素電極の下側まで延びている以外は、第一実施例のアクティブ・マトリクス基板300と同様である。延伸方向は、第一実施例の延伸方向とは逆である。

### [0039]

この実施例による修正方法は、第一実施例の方法と同様である。図6A~6Dを参照すると、第一TFT T1が損傷した場合、第一TFT T1と走査線320の間の接続350、第一TFT T1とデータ線330の間の接続360、および第一TFT T1と画素電極344の間の接続370の少なくとも一つをレーザ切断プロセスで切断する。接続350、360、370の切断方法は、レーザ切断プロセスであってもよい。当然のことながら、第二TFT T2の第二ドレイン電極610は走査線320の上側から、画素電極344と電気的に接続する必要がある。図6Aの下側で第二TFT T2の第二ドレイン電極610を画素電極344と電気的に接続する方法は、レーザ溶接プロセスであってもよい。図6Aの下側で第二TFT T2の第二ドレイン電極610を画素電極344と電気的に接続する方法は、レーザ溶接プロセスであってもよい。図6Aの下側で第二TFT T2の第二ドレイン電極610を画素電極344と電気的に接続する別の方法では、レーザによって図6Aの下側で、第二TFT T2の第二ドレイン電極610上の保護層を燃焼し、次にレーザCVDプロセスで薄い金属層を形成できる。

#### (実施例5)

#### [0040]

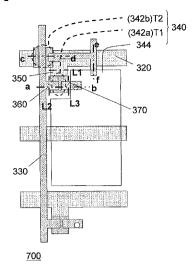

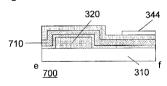

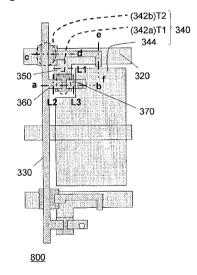

図7Aは、この発明の第五実施例によるアクティブ・マトリクス基板の平面図であり、図3Aの修正形態である。図7B、7C、7Dは各々、ラインa-b、ラインc-d、ラインe-fにおける図7Aの断面図である。図7A~7Dを共に参照すると、この実施例のアクティブ・マトリクス基板700は、第一実施例のアクティブ・マトリクス基板300によると、各画素ユニット340が第二TFT T2を有する。しかし、この発明のアクティブ・マトリクスス基板700によると、第二TFT T2は奇数の走査線320とデータ線330の交差部のみに形成する。従って、互いに上下に隣接する画素ユニット340の各対が、共有型の第二TFT T2を有する。に、この実施例の第二TFT T2の第二ドレイン電極710は、走査線320の上側から、奇数または偶数の走査線320の両側に沿って、画素電極344の下側まで延びで交差部のみ、または偶数の走査線320とデータ線330の交差部にのみ形成するが、第二TFT T2が形成されない走査線320とデータ線330の交差部に、第二チャネル層 ことも形成することもできる。

# [0041]

図7A~7Dを再び参照すると、互いに上下に隣接する一対の画素ユニットの第一TFT T1の一つが損傷した場合、第一TFT T1と走査線320の間の接続350、第一TFT T1とデータ線330の間の接続360、および第一TFT T1と画素電極344の間の接続370の少なくとも一つをレーザ切断プロセスで切断する。次に、第二TFT T2の第二ドレイン電極710を画素電極344と電気的に接続するために、レーザ溶接法を用いる。第二TFT T2の第二ドレイン電極710を画素電極344と電気的に接続する方法は、レーザ溶接プロセスまたはレーザCVDプロセスを行うことで実現することもできる。互いに上下に隣接する一対のこのような画素ユニットは共有型の第二TFT T2を有し、第二TFT T2の第二ドレイン電極710は走査線320の上

10

20

30

40

側から、走査線320の両側に向かって、画素電極344の下側まで延びているので、互いに隣接する一対の画素ユニットの任意の第一TFT T1が損傷した場合、共有型の第二TFT T2が損傷した第一TFT T1の代わりとなることができる。

#### (実施例6)

#### [0042]

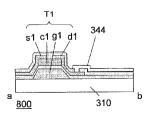

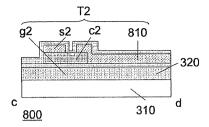

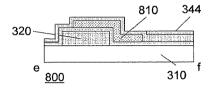

図8Aは、この発明の第六実施例によるアクティブ・マトリクス基板の平面図であり、図3Aの修正形態である。図8B、8C、8Dは各々、ラインa・b、ラインc・d、ラインe・fにおける図8Aの断面図である。図8A~8Dを共に参照すると、この実施例のアクティブ・マトリクス基板800は、第一実施例のアクティブ・マトリクス基板300と同様である。主な違いは、第二ドレイン電極810が走査線320の上側から、走査線320の片側に向かって、画素電極344の下側に到達することなく延びていることである。

#### [0043]

図8A~8Dを再び参照すると、第一TFT T1が損傷した場合、第一TFT T1と走査線320の間の接続350、第一TFT T1とデータ線330の間の接続360、および第一TFT T1と画素電極344の間の接続370の少なくとも一つをレーザ切断プロセスで切断する。次に、第二TFT T2を画素電極344と電気的に接続する。しかし、この発明によると、第二ドレイン電極810は画素電極344の下側までは延びていないので、レーザで第二ドレイン電極810上の保護層を燃焼した後、レーザCVDプロセスを行って薄い金属層を形成し、第二ドレイン電極810を画素電極344と電気的に接続しなければならない。言い換えると、この実施例では、画素ユニット340を修正するには、レーザCVDプロセスを用いるしかない。

#### (実施例7)

#### [0044]

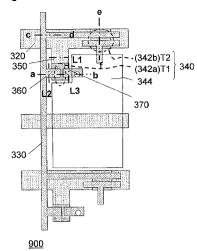

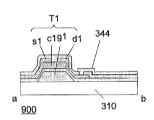

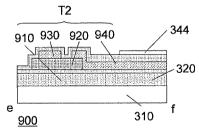

図9Aは、この発明の第七実施例によるアクティブ・マトリクス基板の平面図であり、図3Aの修正形態である。図9B、9C、9Dは各々、ラインa-b、ラインc-d、ラインe-fにおける図9Aの断面図である。図9A~9Dを共に参照すると、この実施例のアクティブ・マトリクス基板900は、第一実施例のアクティブ・マトリクス基板300と同様である。第二TFT T2は走査線320上に配置し、第二ソース電極930はデータ線330と電気的に接続する。第二チャネル層920は走査線320とデータ線330の交差部から所定の距離だけ離して配置し、走査線320、第二ソース電極930および第二ドレイン電極940の間に挟持する。第二ドレイン電極940は、走査線320の上側から走査線320の片側に向かって、画素電極344の下側まで延びている。

#### [0045]

図9A~9Dを再び参照すると、第一TFT T1が損傷した場合、第一TFT T1と走査線320の間の接続350、第一TFT T1とデータ線330の間の接続360、および第一TFT T1と画素電極344の間の接続370の少なくとも一つをレーザ切断プロセスで切断する。次にレーザ溶接法を用いて、レーザで第二ドレイン電極940を画素電極344と溶接することで、第二TFT T2を画素電極344と電気的に接続する。第二TFT T2を画素電極344と電気的に接続する別の方法では、レーザで第二ドレイン電極940上の保護層を燃焼し、次にレーザCVDプロセスで薄い金属層を形成する。

### (実施例8)

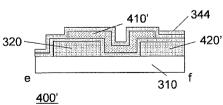

# [0046]

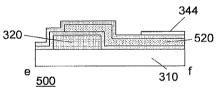

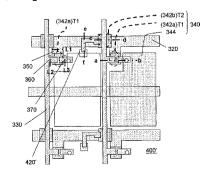

図10Aは、この発明の第八実施例によるアクティブ・マトリクス基板の平面図であり、図3Aの修正形態である。図10B、10C、10Dは各々、ラインa-b、ラインc-d、ラインe- f における図10Aの断面図である。図10A~10Dを共に参照すると、この実施例のアクティブ・マトリクス基板400'は、第二実施例のアクティブ・マトリクス基板400'は、アクティブ・マトリクス基板400'が第二ドレイン電極410'と画素電極344の下に配置した修正ライン420'を有する

10

20

30

ことである。修正ライン420 'は第一金属層に属し、誘電体層(ゲート絶縁層)によっ て第二ドレイン電極410から電気的に分離される。

#### [0047]

図 1 0 A ~ 1 0 D を参照すると、隣の画素ユニット 3 4 0 の第一TFT T 1 (図 1 0 Aの左側の第一TFT T1)が損傷した場合、レーザ切断プロセスを用いて、第一TF T T1と走査線320の間の接続350、第一TFT T1とデータ線330の間の接 続360、および第一TFT T1と画素電極344の間の接続370の少なくとも一つ を切断する。次に、レーザを用いて、修正ライン420′、第二ドレイン電極410′お よび画素電極344が重なっている領域を燃焼し、第二ドレイン電極410′、画素電極 3 4 4 および修正ライン 4 2 0 ′を溶接する。こうして、第二TFT T 2 は、図 1 0 A の左側の画素電極344と電気的に接続する。その結果、画素ユニット340が修正され る。

【産業上の利用可能性】

## [0048]

つまり、アクティブ・マトリクス基板およびその画素ユニット修正方法は、少なくとも 次の利点を有する。

- 1.画素ユニットがTFTを一つしか持たない既存のTFTアレイ基板と比べて、この 発明によって提供されるアクティブ・マトリクス基板は冗長的な能動素子を有する。画素 電極と電気的に接続した能動素子が損傷した場合、元の能動素子の代わりに他の能動素子 (冗長的な能動素子)を用いて、画素ユニットが通常動作を再開できるようにする。その 結果、LCDパネル上の輝点欠陥の問題が避けられ、LCDパネルの修正率が適宜改善さ れる。

- 2.修正した画素ユニットが完全な明または暗しか表示しない別の既存のTFTアレイ 基板と比べて、この発明によるアクティブ・マトリクス基板の画素ユニットは修正後、通 常の機能を再開できる。

- 3.この発明によるアクティブ・マトリクス基板の製造およびその画素修正方法は、そ れらの既存のプロセスと互換性がある。二つの遮光パターンが修正形態では必要とされる が、追加の製造装置は必要とされない。

# [0049]

当然のことながら、ここでは例示のために、この発明の具体的な実施形態および例を説 明しており、この発明の範囲内で様々な等価な修正形態が可能であるが、当業者には明ら かなように、この発明の上記の好ましい実施例の修正および調整を行い、特定の要件に適 合させることができる。この開示内容は、その範囲を限定することなく、この発明を典型 的に示すことを意図している。好ましい実施例で開示した発明に組み込んだ全ての修正形 態は、添付の請求項の範囲または請求項に権利が与えられる等価なものの範囲内にあると 解釈される。

【図面の簡単な説明】

#### [0050]

添付の図面は、この発明をさらに理解するために含められ、この明細書に組み込まれ、 その一部を構成する。図面はこの発明の実施例を示し、その内容と共にこの発明の原理を 説明するのに役立つ。

【図1A】既存のTFTアレイ基板の平面図である。

【図1B】ラインa-bにおける図1Aの断面図である。

【図1C】ラインc‐dにおける図1Aの断面図である。

【図2A】別の既存のTFTアレイ基板の平面図である。

【図2B】ラインa-bにおける図2Aの断面図である。

【図2C】ラインc-dにおける図2Aの断面図である。

【図3A】この発明の第一実施例によるアクティブ・マトリクス基板の平面図である。

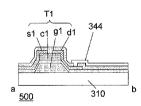

【図3B】ラインa-bにおける図3Aの断面図である。

【図3C】ラインc‐dにおける図3Aの断面図である。

10

20

30

40

50

```

【図3D】ラインe-fにおける図3Aの断面図である。

【図4A】この発明の第二実施例によるアクティブ・マトリクス基板の平面図である。

【図4B】ラインa-bにおける図4Aの断面図である。

【図4C】ラインc‐dにおける図4Aの断面図である。

【図4D】ラインe-fにおける図4Aの断面図である。

【図5A】この発明の第三実施例によるアクティブ・マトリクス基板の平面図である。

【図5B】ラインa-bにおける図5Aの断面図である。

【図5C】ラインc-dにおける図5Aの断面図である。

【図5D】ラインe-fにおける図5Aの断面図である。

10

【図6A】この発明の第四実施例によるアクティブ・マトリクス基板の平面図である。

【図6B】ラインa-bにおける図6Aの断面図である。

【図6C】ラインc-dにおける図6Aの断面図である。

【図6D】ラインe-fにおける図6Aの断面図である。

【図7A】この発明の第五実施例によるアクティブ・マトリクス基板の平面図である。

【図7B】ラインa-bにおける図7Aの断面図である。

【図7C】ラインc-dにおける図7Aの断面図である。

【図70】ラインe-fにおける図7Aの断面図である。

【図8A】この発明の第六実施例によるアクティブ・マトリクス基板の平面図である。

【図8B】ラインa-bにおける図8Aの断面図である。

20

【図8C】ライン c - d における図8Aの断面図である。

【図80】ラインe-fにおける図8Aの断面図である。

【図9A】この発明の第七実施例によるアクティブ・マトリクス基板の平面図である。

【図9B】ラインa-bにおける図9Aの断面図である。

【図9C】ライン c-dにおける図9Aの断面図である。

【図9D】ラインe‐fにおける図9Aの断面図である。

【図10A】この発明の第八実施例によるアクティブ・マトリクス基板の平面図である。

【図10B】ラインa-bにおける図10Aの断面図である。

【図10C】ラインc-dにおける図10Aの断面図である。

【図10D】ラインe‐ f における図10Aの断面図である。

30

【符号の説明】

[0051]

100 TFTアレイ基板

1 1 0 基板

120 走査線

130 データ線

140 画素ユニット

1 4 2 a

ゲート電極

1 4 2 b

チャネル層

1 4 2 c

ソース電極

40

1 4 2 d

ドレイン電極

1 4 4 画素電極

150 接続

170 ゲート絶縁層

200 TFT基板

2 1 0 修正ライン

2 2 0 修正構造

300 アクティブ・マトリクス基板

3 1 0 基板

3 2 0 走査線

```

330 データ線

- 3 4 0 画素ユニット

- 3 4 2 a 第一能動素子

- 3 4 2 b 第二能動素子

- 3 4 4 画素電極

- 3 5 0 接続

- 3 6 0 接続

- 3 7 0 接続

- 400 アクティブ・マトリクス基板

- アクティブ・マトリクス基板 4 0 0 '

- 4 1 0 第二ドレイン電極

- 4 2 0 ' 修正ライン

- 500 アクティブ・マトリクス基板

- 6 1 0 第二ドレイン電極

- 700 アクティブ・マトリクス基板

- 7 1 0 第二ドレイン電極

- 800 アクティブ・マトリクス基板

- 900 アクティブ・マトリクス基板

- 920 第二チャネル層

- 9 3 0 第二ソース電極

- 9 4 0 第二ドレイン電極

- 第一チャネル層 c 1

- c 2 第二チャネル層

- d 1 第一ドレイン電極

- d 2 第二ドレイン電極

- g 1 第一ゲート電極

- g 2 第二ゲート電極

- L 1 切断ライン

- L 2 切断ライン

- L 3 切断ライン

- s 1 第一ソース電極

- s 2 第二ソース電極

10

20

- 5 1 0 第二ドレイン電極

- 520 第二ドレイン電極

- 600 アクティブ・マトリクス基板

- 8 1 0 第二ドレイン電極

【図1A】

【図1B】

【図1C】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図3D】

【図4A】

【図4B】

【図4C】

【図4D】

【図5A】

【図5D】

【図5B】

【図 6 A】

【図5C】

【図6B】

【図 6 C】

【図6D】

【図7A】

【図7B】

【図7C】

【図7D】

【図8A】

【図8B】

# 【図8C】

# 【図8D】

# 【図9A】

# 【図9B】

# 【図9C】

# 【図9D】

# 【図10A】

# 【図10B】

# 【図10C】

# 【図10D】

# フロントページの続き

(74)代理人 100107423

弁理士 城村 邦彦

(74)代理人 100120949

弁理士 熊野 剛

(74)代理人 100121186

弁理士 山根 広昭

(72)発明者 來漢中

台湾桃園懸中 歴 市内 歴 成功路122巷63弄20號

## 審査官 佐竹 政彦

(56)参考文献 特開平02-193114(JP,A)

特開平07-104311(JP,A)

特開平07-199221(JP,A)

特開平03-230125 (JP,A)

特開平04-32225(JP,A)

特開平02-262125 (JP,A)

実開平02-044723(JP,U)

(58)調査した分野(Int.CI., DB名)

G09F 9/00-9/30

G02F 1/1368