# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.<sup>6</sup> HO4N 5/04 (45) 공고일자 1996년01월03일

(11) 공고번호 특1996-0000102

(21) 출원번호

특1985-0003099

(65) 공개번호

특1985-0008593

(22) 출원일자

1985년05월07일

(43) 공개일자

1985년12월18일

(30) 우선권주장 607595 1984년05월07일 미국(US)

(71) 출원인 알 씨 에이 라이센싱 코포레이션 글렌 에이취. 브르스틀

미합중국, 뉴져지, 프린스턴, 피. 오. 박스 2023, 투인디펜스 웨이

(72) 발명자 챨스 마틴 와인

미합중국, 뉴져지, 프린스턴, 해밀톤 애비뉴 144

(74) 대리인 이병호

### 심사관 : 이헌수 (책자공보 제4264호)

#### (54) 동기장치

### 요약

내용 없음.

#### 叫丑도

### 도1

### 명세서

[발명의 명칭]

동기장치

[도면의 간단한 설명]

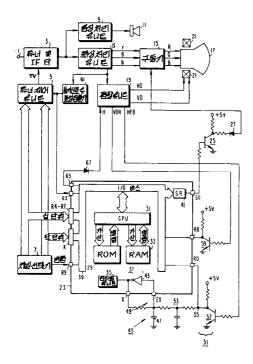

제1도는 수상기 화면상에 채널 번호를 표시하기 위해 본 발명에 따라 수평 및 수직 레이트 신호로 동작을 동기시키기 위한 장치와 마이크로프로세서를 사용한 텔레비젼 수상기의 부분 블럭도 및 부분 개략도.

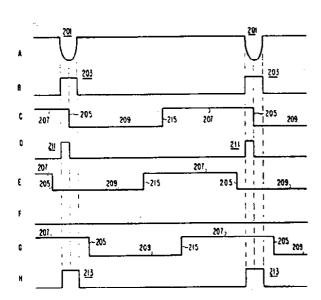

제2도는 제1도에 도시된 동기 장치의 동작을 이해하는데 유용한 파형도.

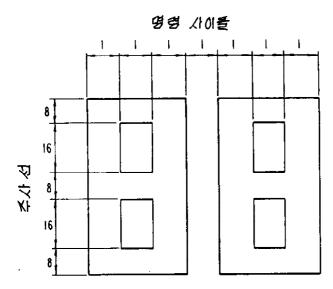

제3도는 제1도에 도시된 온-스크린 채널 번호 표시 장치로 형성되는 포맷 채널 번호의 도시도.

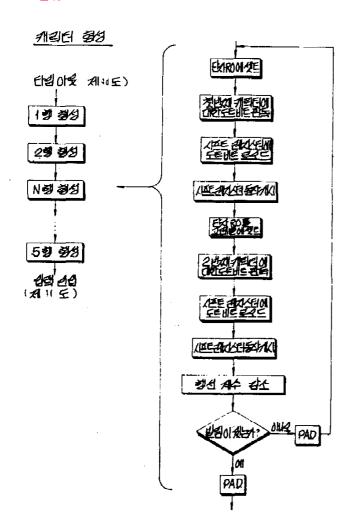

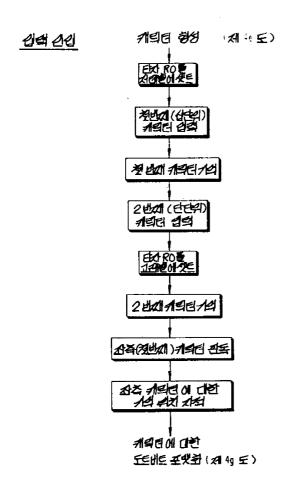

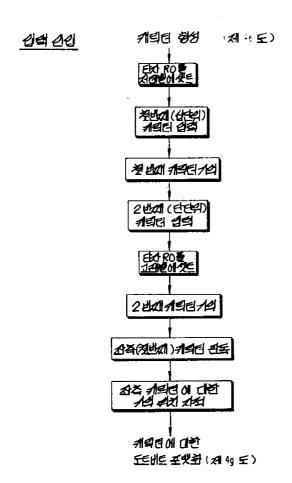

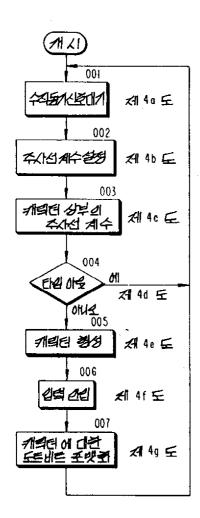

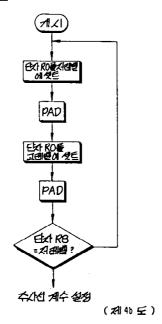

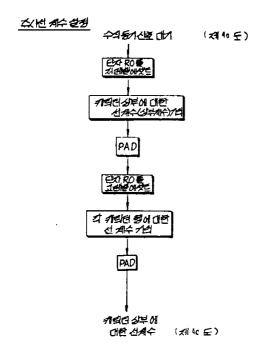

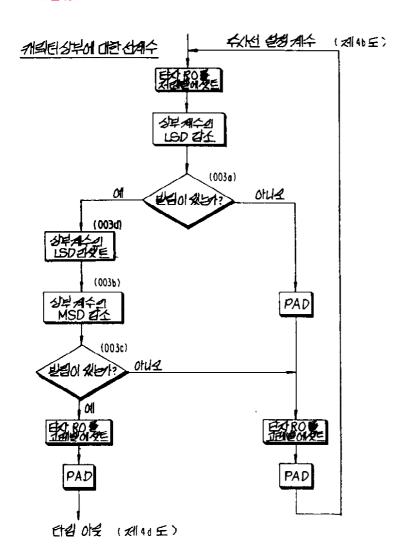

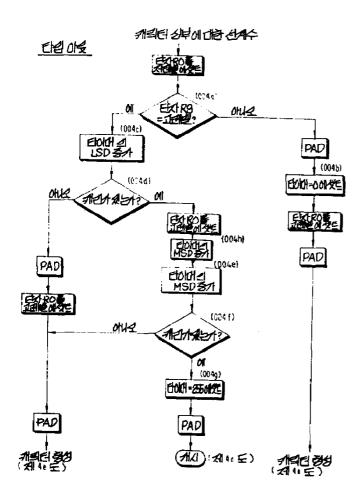

제4도 및 제4a도 내지 제4g도는 온-스크린 채널 번호 표시를 행하기 위해 제1도에 도시된 마이크로 프로세서를 제어하는 프로그램의 순서도.

\* 도면의 주요부분에 대한 부호의 설명

3 : 튜너 및 IF단

5 : 튜너 제어 유니트

7 : 채널 선택기

9 : 음성 처리 유니트

13 : 화상 처리 유니트 15 : 구동기

19 : 편향 유니트23 : 마이크로프로세서31 : CPU35 : 타이밍 유니트

61 : 동기 신호 유효성 검출기

### [발명의 상세한 설명]

본 발명은 텔레비젼 동기 신호와 같은 기준 신호로 마이크로프로세서 또는 마이크로컴퓨터와 같은 계산 시스템(computing system)의 동작을 동기시키기 위한 장치에 관한 것이다.

마이크로프로세서 또는 마이크로컴퓨터(상기 용어는 통상 상호 변경할 수 있음)가 텔레비젼 신호의 처리를 실시간 동안 수행하기 위해서는 그 동작을 비디오 신호의 동기 성분에 동기시키는 것이 바람 직하다. 상기 목적을 행하기 위한 방법 및 장치는 1984년 8월 7일 부여된 R. A. Wargo의 발명의 명 청이 "Method and Apparatus for Operating a Microprocessor in synchronism with a Video Signal "인 미합중국 특허 제 4,464,679 호에 기술되어 있다. 상술한 장치는 위상 동기 루프를 포함하는데, 상기 루프는 마이크로프로세서를 사용한 집적 회로의 외부에 있는 전압 제어형 발진기 (Voltage Controlled Oscillator : 이하 VCO라 함)의 주파수를 수평 레이트 신호 (horizontal rate signal)의 주파수로 동기시킨다. VCO의 출력신호는 마이크로프로세서에 의해 제어되는 게이트를 통해 마이크로프로세서의 클럭 입력에 공급된다. 마이크로프로세서에 의해 수신된 클럭 신호는 마이크로프로세서의 동작을 제어하는 프로그램의 명령 발생 시기를 결정한다. 마이크로프로세서는 주기적으로 합성 비디오 신호를 샘플링시킬 명령을 실행하고 동기성분의 위치를 결정하며, 샘플링 명령이 동기 성분과 동상으로 발생될 때까지 클럭 펄스를 제거하기 위해 게이트를 작동시키도록 프로그램된다.

본 발명은 동기 신호로 마이크로프로세서와 같은 계산 시스템의 동작을 동기시키기 위한 매우 간단한 장치에 관한 것으로, 상기 장치는 마이크로프로세서가 설치되는 직접 회로 외부에 비교적 적은수의 부품을 사용하여 구현될 수 있다.

본 발명의 일 양상에 따르면, 계산 장치의 명령 실행은 기준 신호로 동기된다. 상기 계산 장치는 클 럭 신호에 동기적으로 관련된 명령 사이클로 명령을 실행한다. 제어 신호에 응답하여 클럭 신호의 위상 및 주파수를 제어할 수 있는 장치에 의해 클럭 신호가 발생된다. 계산 장치는 설정된 수의 명 령 사이클이 발생할 때마다 비교 신호를 발생한다. 비교 장치는 비교 신호의 위상 및 주파수를 신호 원으로부터의 기준 신호의 위상 및 주파수와 비교하고, 응답으로 제어 신호를 발생한다.

본 발명에 다른 양상에 따르면, 캐릭터(characters)가 마이크로프로세서에 의해 텔레비젼 시스템의화상표시 장치상에 표시된다. 마이크로프로세서는 집적 회로로 구현되어 클럭 신호와 시간 관계의명령 사이클로 명령을 실행한다. 제어 신호에 응답하여 클럭 신호의 위상 및 주파수를 제어할 수 있는 장치에 의해 클럭 신호가 발생한다. 동기 장치는 신호원으로부터의 텔레비젼 동기 신호 및 클럭신호에 응답하여 제어 신호를 발생하므로 명령 사이클이 텔레비젼 동기 신호로 동기된다. 마이크로 프로세서는 신호원으로부터의 캐릭터에 대응하는 데이타 신호로부터의 명령 사이클에 비례하는 레이트(rate)로 캐릭터 펄스를 발생시킨다. 상기 장치는 캐릭터 펄스를 화상 표시 장치에 제공하여 상기캐릭터를 표시한다.

특히, 본 발명의 일양상에 따르면, 계산 시스템용 클럭 신호를 발생시키는 클럭 신호 발생 장치는 보통 동일한 집적 회로내에 포함된 인버터와 같은 증폭 장치를 포함하는데, 상기 집적 회로로 계산 시스템이 구현된다. 또한, 상기 클럭 신호 발생 장치는 집적 회로 외부에 주파수 결정 회로를 포함하는데, 주파수 결정 회로는 단자를 통해 증폭 장치에 결합된다. 클럭 신호는 계산 시스템의 명령사이클의 타이밍을 결정함에 의해, 계산 시스템의 동작을 제어하는 명령의 발생 타이밍을 결정한다. 상기 계산 시스템은 설정된 수의 명령 사이클이 발생될 때마다 비교 신호를 발생하도록 프로그램된다. 설정된 수의 명령 사이클이 클럭 신호의 주파수와 연관되어 선택되므로, 비교 신호의 주파수가계산 시스템의 동작이 동기되도록 하는 동기 신호의 주파수와 통상 동일하게 된다. 비교 장치는 동기 신호의 위상 및 주파수를 비교 신호와 위상 및 주파수와 비교하여 클럭 신호 발생 장치의 주파수및 위상을 제어하도록 클럭 신호 발생 장치에 공급되는 제어 신호를 발생시킨다.

본 발명의 다른 양상에 따르면, 상술한 본 발명의 장치는 추가 캐릭터 발생 장치를 필요로 하지않는 텔레비젼 시스템용 온-스크린 캐릭터 표시를 발생하는데 특히 적합하다.

이하, 본 발명의 상기 및 다른 특징이 첨부된 도면을 참조하여 상세히 기술될 것이다.

제1도의 텔레비젼 수상기에 있어서, 무선 주파수(Radio Frequency ; 이하 RF라함) 입력단(1)에서 수신된 RF 텔레비젼 신호는 튜너 및 중간 주파수(Immediate Frequency ; 이하 IF라함)단(3)에 공급되고, 상기 튜너 및 IF단은 선택된 채널에 대응하는 RF 신호를 선택하고 헤테로다인 처리하여 대응 IF 신호를 발생시킨다. 상기 튜너 및 IF단(3)의 튜너는 전압제어형 튜너로서, 채널 선택기(7)에 의해결정된 선택 채널에 부합하여, 튜너 제어 유니트(5)에 의해 발생되는 동조 전압(tuning voltage : TV)의 크기에 응답하여 제어된다.

IF 신호의 음성 성분은 음성 처리 유니트(9)에 공급되며, 상기 유니트(9)는 음성을 복조하여 스피커 (11)에 적용하기에 적절한 베이스밴드 오디오 신호를 발생시키기 위해 처리한다. IF 신호의 화상 성분은 화상처리 유니트(13)에 공급되며, 상기 유니트(13)는 화상을 복조하여 저레벨의 적, 녹 및 청(r,g 및 b)의 색신호를 발생시키기 위해 처리한다. 상기 저레벨 색신호는 구동 유니트내의 각각의 구동기(15)에 의해 증폭되며, 그결과의 신호(R,G 및 B)는 화상 표시 장치 예를들어, 화상관(17)의각 전자총에 공급되며 상기 각 전자총은 응답으로 대응 전자빔을 발생시킨다.

화상 처리 유니트(13)에 의해 발생된 수평 및 수직 동기성분을 포함하는 합성 동기 신호는 수평 및 수직 편향 신호(HD 및 VD)를 발생하는 편향 유니트(19)에 공급된다. 편향 신호가 화상관(17)과 연관된 편향 코일(21)에 공급되어 래스터에 전자빔을 편향시킨다.

편향 신호의 발생과 관련하여 발생된 수직 레이트로 구동(vertical rate drive; VDR) 펄스(이하 수직 레이트 신호라함) 및 수평 레이트 귀선 또는 "플라이백" (Horizontal rate retrace or flyback: HFB) 펄스는(이는 텔레비젼 동기 신호중 하나로, 클럭 신호의 위상 및 주파수를 제어하는데 기준이 되는 신호로도 사용되므로, 이하 텔레비젼 동기신호 또는 기준 신호라고도함) 후술하는 바와같이마이크로프로세서의 동작을 동기시키기 위해 사용된다.

지금까지 설명한 텔레비젼 수상기의 부분은 통상의 것으로, 튜너 제어 유니트(5) 및 채널 선택기 (7)를 제외하고는, 미합중국 인디애나, 인디애나폴리스 소재의 알 씨 에이 코포레이션에 의해 제작된 CTC-115형의 RCA 칼라 텔레비젼 샤시를 사용한 텔레비젼 수상기의 대응부분과 동일한 방법으로형성될 수도 있고, C-4, 파일 1981, CTC-115 샤시에 대한 RCA 서비스 데이타북에 기술되어 있다. CTC-115 샤시에 있어서, 튜너 제어 유니트는 다수의 병렬 접속된 분압기(potentiometers)를 포함하며, 상기 분압기는 공급 전압에 결합되며, 각 분압기의 와이퍼는 적절한 동조 전압의 크기를 대응

채널에 제공하도록 조정되고, 채널 선택기(7)는 동조 분압기의 한 와이퍼를 튜너(3)에 선택적으로 결합시키기 위한 회전 동조 장치를 가지므로 요구된 채널을 선택할 수 있다. 그러나, 본 발명의 장치에서 채널 선택기(7)는 계산기형 키보드를 포함하는데, 사용자는 상기 키보드를 사용하여 십단위디지트 및 단단위 디지트를 순차적으로 인입함에 의해, 선택된 채널에 대응하는 2-디지트 채널 번호를 인입시킬 수 있고, 튜너 제어 유니트(5)는 채널 선택기(7)에 의해 발생된 채널 번호의 십단위 및단단위 디지트를 나타내는 BCD(binary coded decimal) 신호를 선택된 채널에 대응하는 동조 전압 크기로 변환시키기 위해 위상 동조 루프와 같은 변환기를 포함한다. 상기 형태의 장치는 1982년 11월 30일자로 C. M. Wine에게 부여된 미합중국 특허 제 4,361, 907 호에 기술되어 있으며, 상기 장치를 사용하는데 적절한 위상 동기 루프의 상세한 설명은 1982년 11월 2일자로 M. P. French에게 부여된 미합중국 특허 제 4,357,632 호에 기술되어 있다.

제1도에 도시된 수상기는 화상관(17)의 스크린상에 선택된 채널의 채널 번호를 표시하기 위한 장치도 포함한다. 특히 채널 선택기(7)에 의해 발생된 채널 번호의 십단위 및 단단위 디지트를 나타내는 BCD 신호는 계산 장치 예를들어, 마이크로프로세서 (23)의 4단자의 R4-R7 및 K의 각 그룹에 제공된다. 예로서, 마이크로프로세서(23)는 일본국 도오꾜도에 소재하는 후지츠 리미티드로부터 시판되고있는 8841형의 집적 회로로 구성할 수 있으며, 제1도에 표시된 단자는 비록 다른 마이크로프로세서가 사용될 수 있을지라도 상기 집적 회로에 대응한다. 마이크로프로세서(23)는 단자(S0)에서 채널 번호의 수평 슬라이스(slices)를 나타내는 캐릭터 신호(character signal)를 발생하여, 대응하는 수평 주사 기간 동안 표시된다. 캐릭터 신호는 NPN 스위칭 트랜지스터 (25)에 공급되는데, 상기 트랜지스터(25)는 적절한 극성과 크기의 대응 신호를 제공하여 구동 유니트의 구동기(15)를 도통시켜,그에 따라 백색 채널 번호가 표시되게 한다. 특히, RCA CTC-115 샤시에 사용하기 위해서, 스위칭 트랜지스터(25)는 단자(S0)에서 발생되는 정방향 진행 펄스에 응답하여, 구동기를 "온"상태로 턴하기위한 부방향 진행 펄스를 제공한다. 단자(S0)의 정방향 진행 펄스가 존재하지 않을 때에는 공급 전압(예를들어, +5볼트)에 매우 근접한 정의 전압이 트랜지스터(25)의 콜렉터 전국에 발생될 것이다. 다이오드(27)는 상기 정의 전압이 구동기에 도달하지 못하게 하여, 구동기의 동작에 악영향을 끼치는 것을 막는다. 스크린 상에 채널 번호를 적절하게 위치시키기 위해, 마이크로프로세서(23)의 동작은 편향 유니트(19)에 의해 발생된 수평 및 수직 레이트 신호와 동기되어야 한다. 상기가 구현되는 방법은 이하 상세히 기술될 것이다.

마이크로프로세서(23)는 판독 전용 메모리(ROM ; 29)에 기억된 프로그램의 명령에 따라 동작한다. 중앙 제어 장치(CPU ; 31)는 ROM(29)의 메모리 위치를 어드레싱하여 명령을 판독하며, 그후 이들 명령을 실행한다. 즉, 데이타를 처리한다. RAM(33)은 일시적으로 데이타를 기억하는데 사용된다. 어떤명령은 명령에 따라 하나 이상의 명령 사이클을 요구한다. 명령 사이클은 클럭 신호 발진기(37)에 의해 발생하는 클럭 신호의 클럭 펼스에 응답하여 타이밍 유니트에 의해 발생되는 타이밍 펄스와 적절한 시간 관계로 발생한다. 이하, 상세히 설명하는 바와같이, 상기 클럭 신호의 위상 및 주파수를 제어함에 의해서, 마이크로프로세서(23)의 동작은 편향 유니트(19)에 의해 발생되는 수평 레이트 신호와 동기된다. 입력/출력(1/0) 버스(39)는 데이타를 CPU (31)와 집적 회로의 단자간에 연결하며, 집적회로로 마이크로프로세서(23)가 구현된다. 직렬 쉬프트 레지스터(SR : 41)는 1/0 버스(39)를 통해 CPU(31)에서부터 병렬 형태로 데이타를 수신하며, 상기 데이타 수신에 따라 인에이블될 때 명령사이클의 레이트로 데이타를 단자(SO)에 공급한다. 후자는 이하 상세히 기술되는 바와같이 온-스크린 채널 번호의 형성에 사용된다.

클럭 신호 발진기(37)는 마이크로프로세서(23)가 설치된 집적 회로내에 포함된 논리 "인버터 "형태의 반전 증폭기 즉, 인버터(43)를 포함한다. 인버터(43)는 집적 회로의 각 단자(EX 및 X)에 접속된입력 및 출력을 가진다. 클럭 신호 발진기(37)를 완성하기 위해, 캐패시터(47) 및 가변 저항(49)을 포함하는 주파수 결정 회로(45)는 단자(EX 및 X)를 통해 인버터(43)의 입력과 출력간의 궤환 경로에접속된다. 이러한 클럭 신호 발생 장치(45,37)가 공통적으로 사용된다.

캐패시터(47) 및 저항(49) 값이 선택되어 설정된 수의 명령 사이클이 수평 레이트로 발생된다. 예로 서 만약 클로 신호가 후지츠 8841 마이크로프로세서용의 최대 클럭 주파수인 2MHz의 공칭 주파수 (nominal frequency)를 가지면, 명령 사이클은 3마이크로 세컨드의 지속 시간을 가진다. 따라서, 20 개의 명령 사이클은 미합중국에서 사용되는 NTSC 시스템의 63 마이크로세컨드 수평 기간에 근접한 60 마이크로 세컨드마다 발생한다. 수평 방향으로 최고의 해상도를 갖는 온-스크린 캐릭터를 제공하 기 위해서는 가능한 가장 높은 클럭 주파수를 사용하는 것이 바람직하다.

설정된 수의 명령 사이클의 각 그룹에 대해서, 마이크로프로세서(23)가 단자(R0)에서 비교 펄스를 발생하도록 마이크로프로세서(23)는 프로그램된다. 즉 마이크로프로세서의 명령이 배치된다. 단자 (R0)에 발생된 비교 펄스의 주파수 및 위상은 위상 및 주파수 비교 장치 예를들어, 비교기(51)에서 편향 유니트(19)에 의해 발생된 수평 레이트 신호의 위상 및 주파수와 비교된다. 비교 펄스와 수평 레이트 신호간의 위상 및 주파수 편차를 나타내는 비교 장치 예를들어, 비교기(51 ; 동기 검출 회로 라고도 함)에 의해 발생된 오차신호는 저역 통과 필터(53)에 의해 필터되어 제어 신호를 발생한다. 제어 신호는 단자(EX)를 통해 인버터(43)의 입력에 공급되며, 인버터(43)의 바이어스를 변경시킴에 의해 클럭 신호의 위상 및 주파수가 조정되고 그것에 의해 비교 신호가 수평 레이트 신호와 정렬될 때까지 마이크로프로세서의 명령 사이클의 타이밍이 조정된다. 결과적으로 명령 사이클이 수평레이 트 신호와 시간 관계로 발생되므로 마이크로프로세서(23)의 동작은 수평 레이트 신호로 동기된다. 본질적으로, 본 발명의 장치에 있어서, 설정된 수의 명령 사이클의 선택은 위상 동기 루프에서 분주 기의 분주 계수를 선택하는 것과 동일하므로 주파수 분배기에 의해 주파수가 분배되는 제어형 발진 기의 출력 신호의 위상 및 주파수는 기준 신호와 비교될 수 있다.

따라서, 마이크로프로세서(23)의 프로그램의 명령은 비디오 신호를 샘플링하거나 수평 주사선의 예 상되는 위치에서 캐릭터를 발생하는 바와 같은 주어진 동작을 이행할 수 있도록 배열될 수 있다. 이 러한 캐릭터 발생 동작은 이하 더욱 상세하게 설명하기로 한다.

특히, 동기 장치에 관해서, 비교기(51)는 다음과 같이 구성되는 "배선된 (wired)" AND 게이트로

구성된 동기 검출기(coincidence detector)이다. 출력 단자 (RO)는 회로점(55)에 접속된다. 제2도의 파형(A)에 있어서, 수평 플라이백(HFB) 펄스는 수평 레이트로 발생되는 부방향 진행 펄스(201) 즉, 수평 레이트 신호이다. 수평 플라이백 펄스는 NPN 스위칭 트랜지스터(57)의 베이스에 결합된다. 트랜지스터(57)의 콜렉터는 회로점(55)에 접속된다.

프로그램 제어하에서, 이하 상세하게 설명되는 바와같이, 마이크로프로세서 (23)는 단자(R0)를 구동 시킬 수 있으므로 해서 회로점(55)을 저레벨로 구동시킨다. 회로점(55)은 트랜지스터(57)가 수평 플 라이백 신호(HFB signal)의 정 레벨에 응답하여 도통될 때 저레벨로 또한 구동된다. 회로점(55)은 마이크로프로세서(23) 또는 트랜지스터(57)의 어느것에 의해서도 저레벨로 구동되지 않을 때 고 레 벨에 있게 된다. 만일 단자(R0)가 마이크로프로세서(23)에 의해 저레벨로 구동되지 않는다고 가정하 면, 수평 플라이백 펄스의 지속 기간과 사실상 동일한 지속 기간을 갖는 정방향 진행 펄스(203)가 제2도의 파형(B)으로 표시된 바와같이 각각 부방향 진행 수평 플라이백 펄스에 응답하여 회로점(55)에서 발생된다.

단자(RO)에서 발생된 비교 신호는 제2도의 파형(C)으로 예시되어 있고, 고레벨부(207)로부터 저레벨부(209)로의 천이부(205)를 갖는다. 비교기(51)에 의해 발생된 클럭 신호 발진기(37)의 제어 신호는 클럭 신호의 위상 및 주파수를 제어하여 천이부(205)를 정방향 진행 수평 레이트 펄스(203)의 각 중앙에 정렬 배치되게 한다. 이경우, 사실상 파형(B)의 펄스(203) 폭의 1/2과 동일한 폭의 정방향 진행 펄스를 갖는 파형(D)로 표시되는 신호가 회로점(55)에 발생된다. 제어 신호로서 저역 통과필터(53)에 의해 발생되는 파형(D)으로 표시되는 신호의 평균 레벨은 클럭 신호의 정확한 위상 및 주파수에 대응한다.

만약, 파형(F)으로 표시된 바와같이, 천이부(205)가 정방향 진행 수평 레이트 펄스(203)에 앞서 발생된다면, 파형(F)에 의해 도시된 바와같이 회로점(55)에서 저레벨이 발생될 것이다. 회로점(55)에서 발생되는 저레벨에 응답하여, 각각의 정방향 진행 수평 레이트 펄스(203)의 지속 기간 동안에 천이부(205)가 나타날 때까지 클럭 신호의 위상 및 주파수가 조정된다. 이는 비교적 좁은 펄스를 노드(55)에서 발생시킨다. 그후, 좁은 펄스로 인한 비교적 낮은 평균 레벨에 응답하여, 좁은 펄스의 폭이 파형(D)의 펄스(211)폭으로 증가할 때까지 클럭 신호의 위상 및 주파수가 조정된다.

만약 천이부(205)가 파형(G)으로 표시된 바와같이 정방향 전체 수평 레이트 펄스(203)보다 늦게 발생하면, 펄스(211)보다 넓은 정방향 진행 펄스(213)는 파형(H)으로 표시된 바와같이 회로점(55)에 발생될 것이다. 상기 비교적 넓은 펄스로 인한 비교적 높은 평균 레벨에 응답하여, 넓은 펄스의 폭이 파형(D)의 펄스(211) 폭으로 감소될 때까지 클럭 신호의 위상 및 주파수가 조정된다.

따라서, 고레벨부(207)로부터 저레벨부(209)로의 다른 부방향 진행 천이부 (205)는 최종 부방향 진행 천이부 이후에 설정된수, 예로서, 20개의 명령 사이클을 발생시킬 수 있으므로, 비교 신호는 부방향 진행 천이부(205)들간의 중간 시점에 대응하는 명령 사이클의 수, 예로서, 10개의 명령 사이클에서 저레벨부(209)로부터 고레벨 (207)로의 정방향 진행 천이부(215)를 갖는다. 정방향 진행 천이부(215)가 비교하기 위해 사용되지 않으므로, 그들의 타이밍은 정밀하지 않으며 발생된 각각의 부방향 진행 천이부(205)로부터의 명령 사이클 수는 프로그래밍의 호환성을 허용하기 위해 가변될 수도있다.

제3도는 예로서, 채널 번호 88의 포맷이 도시되어 있다. 채널 번호는 설정된 수, 예로서 40개의 주사선에 대응하는 간격만큼 스크린의 상촉 연부로부터 위치되고, 설정된 수, 예로서, 4개의 명령 사이클에 대응하는 간격만큼 스크린의 좌촉 연부로부터 위치된다. 주어진 예에 대하여, 캐릭터는 스크린의 상부 좌측 모서리에 위치될 것이다. 각 캐릭터는 5개의 수평 행(row) 및 3개의 수직 열 (column)을 포함한다(실제로, 캐릭터간의 간격은 좌측 캐릭터의 4번째 수직 열로 고려된다). 행은 표시된 바와같이 설정된 수의 수평 주사선으로 구성된다. 열(column)은 각각 전자빔이 한 명령 사이클내에서 횡단하는 거리에 대응하는 폭을 갖는다. 행의 각 수평 주사선에서, 캐릭터의 일부분인 "도트"라 불리우는 부분이 존재하는 각각의 열에 대해, 명령 사이클의 지속 기간에 대응하는 지속 기간을 가진 정방향 진행 펄스를 단자(SO)에서 발생시키는 명령을 실행함에 의해 채널 번호의 슬라이스가 형성된다.

온-스크린 채널 번호의 형성은 마이크로프로세서(23)의 ROM(29)에 기억된 프로그램의 순서도를 참조하여 더욱 상세히 설명하기로 한다. 제4도는 프로그램 전체 시퀀스를 나타낸다. 제4a도 내지 제4g도는 제4도에 표시된 프로그램의 여러 부분의 상세한 순서도를 나타낸다. 다음의 설명에서, 괄호 안에 표시된 번호는 대응하는 순서도의 부분과 동일하다.

각각의 순서도를 참조하기 전에, 도움을 주기 위해 동기 동작의 상세 사항에 관련된 몇가지 일반적인 사항을 설명할 것이다. 예로서, 다음을 설명하는 동안 제4c도가 참조된다. 순차적으로 실행되는 프로그램의 각 세그먼트는 수평 주사 기간에 대응하는 설정 수, 예로서, 20개의 명령 사이클을 가지며, 단자(RO)의 전압을 저레벨로 설정함에 따라 개시된다(즉, 비교신호의 발생으로 개시된다). 만약세그먼트내에 명령 사이클이 충분하지 않으면, 적정수의 무연산(no-operation ; 보통, NOP라함)명령이 실행된다. 이부분은 PAD 기능 블럭으로 표시되는데 이것은 만약 세그먼트가 여러번 반복되더라도(즉, 판단에 의해 프로그램의 다음 세그먼트로 진행하는 것보다 동일한 세그먼트의 개시점에 되돌아 가게됨) 만찬가지이다. 세그먼트의 각 경로에 있어서, 단자(RO)의 전압은 저레벨로 셋트된 후대략 10번째 명령 사이클에서 고레벨로 셋트된다. PAD 동작은 상기의 목적으로도 역시 사용된다.

제4도에 있어서, 스크린의 상부로부터 설정된 수의 주사선에 채널 번호를 위치시키기 위해서, 수직소인기간(vertical trace interval ; 垂直掃引期間)의 개시는 정해져야만 한다(001). 특히, 제4a도에 관하여, 상기 목적을 위해 마이크로프로세서(23)는 단자(R8)의 레벨을 반복적으로 샘플링하여 수직 소인기간의 개시를 정한다. 제1도에 도시된 바와 같이, 수직 구동 신호(vertical drive signal ; VDR)는 NPN스위칭 트랜지스터(59)의 베이스에 결합된다. 트랜지스터(59)의 콜렉터는 단자(R8)에 접속된다. 수직 소인기간의 개시시에, 수직 구동 신호는 저레벨에서 고레벨로 천이되고, 이에 대응해서 단자(R8)의 신호가 고레벨에서 저레벨로 천이된다.

제4도에 일반적으로 도시된 바와 같이, 마이크로프로세서(23)가 단자(R8)의 저레벨을 감지했을때, (실제로 RAM(33)의 기억 위치인) 계수기가 초기화되어 캐릭터의 상부 및 각 행에 대해 주사선 수를 계수한다. 상기 목적을 위해 상세한 순서도는 제4b도에 도시된다.

제4도에 도시된 바와 같이, 주사선 계수가 초기화된 후, 마이크로프로세서(23)는 캐릭터의 상부행을 형성하는 시기를 결정하기 위해 수평 주사선의 계수를 시작한다. 단자(RO)에서의 비교 신호의 발생을 야기시키는 명령을 상술한 바와 같이 수평귀선 신호로 동기된다. 따라서, 수평 귀선으로부터 캐릭터의 상부를 형성하는 선까지의 수평선에 대한 계수화는 단자(RO)의 전압이 저레벨로 셋트될 때마다 한번씩 계수기의 계수를 감소시키는 것에 의해 행해진다. 상기 계수화는 설정된 수의 주사선이계수될 때까지 계속된다.(설정된 수는 캐릭터의 상부에 실제대응하지 않지만, 캐릭터의 형성전에일 어나는 동작중에 횡단된 주사선의 수에 대한 계산을 위해 보다 높은 수직 위치에 대응한다.). 제4도도에 도시된 바와 같이, 후지츠 MB8841마이크로프로세서가 4비트 마이크로프로세서이므로(이것은 최대계수 16이 RAM(33)의 단일 기억 위치를 사용하여 제조될 수 있고, 설정된 수의 주사선은 16보다큼을 의미함), 최하위 또는 단단위 디지트(least significant or units digit: 이하 LSD라함)와 최상위 또는 십단위 디지트(most significant or tens digit: 이하 MSD라함)에 대해 RAM(33)의 두개의 기억 위치가 사용된다. "빌림(borrow)"이 발생되는 지점(003a)으로 LSD가 감소된 후, LSD는 리셋트(003d)되고 MSD는 감소된다(003b). 빌림이 발생되는 지점으로 (0036) MSD가 감소될 때, 전체 프로그램의 다음 세그먼트인 타임 아웃(004)이 시작된다.

제4도에 도시된 바와 같이, 설정된 수의 주사선이 계수된 후(003), 타임 아웃 부분이 유입되어 (004), 채널 번호의 표시 여부 또는 채널 번호 표시의 계속 여부를 판단한다. 특히, 제1도에 도시된 구조물에 있어서, 정방향 진행 변환 펄스는 선택된 채널이 변환될 때마다 채널 선택된(7)에 의해 발생된다. 변환 펄스는 마이크로프로세서의 단자(R9)에 공급된다. 제46도에 있어서, 프로그램의 타임아웃 부분을 단자(R9)의 레벨을 감지하도록 하여(004a), 만일 고레벨에 있으면 채널 변호가 표시되게 한다. 만약, 단자(R9)의 레벨이 저레벨이고 설정된 시간, 예로서, 4초가 경과되지 않았다면, 채널 변호가 계속적으로 표시된다. 만일 단자(R9)의 레벨이 저레벨이고 설정된 시간이 경과되면, 채널 변호는 표시되지 않고 프로그램은 개시(시작)로 복귀한다. 특히, 경과된 시간 계수기 또는 타이머는 RAM(33)의 기억 위치를 포함하는데, 상기 기억 위치의 내용은 설정된 계수에 도달할 때까지 증가한다. 4초의 표시 시간을 제공하기 위해, LSD 및 MSD부분을 갖는 8비트 타이머를 요구하는 256의 설정된 계수가 사용된다. 단자(R9)가 고레벨로 되게 초기에 결정될 때 상기 타이머는 0의 계수로 셋트된다. 단자(R9)의 전압이 더이상(프로그램이 캐릭터를 표시한 후에 시작으로 복귀하는 각각의 필드에서 고레벨에 있지 않을때, 타이머의 LSD는 일회 증가하고 그이후 캐릭터가 표시되게 되고 프로그램은 후술하는 바와 같이 초기 상태로 복귀한다. 이러한 처리는 캐리가 발생될 때까지(004d) 계속된다. 캐리가 각각의 필드에서 LSD에 대해 발생되어진 후, 타이머의 LSD는 리셋트되고(004h) 타이머의 MSD는 일회증가되고(004e) 그후 캐릭터가 표시되게 되고 프로그램은 초기 상태로 복귀한다.

이러한 처리는 MSD에 대한 캐리가 발생될 때까지(004f) 계속된다. 설정된 시간이 경과되었음을 나타 내는(즉, 60Hz의 필드 레이드에서 계수 256이 대략 4초에 대응하는), MSD에 대하서 캐리가 발생된 후, 캐릭터의 표시되지 않으며 프로그램은 초기 상태(개시)로 복귀한다. 후자의 경우, 프로그램이 초기 상태로 복귀하기 전에, 타이머는 계수255로 셋트되므로(004g), 캐리는 다음 필드 동안 발생될 것이며 따라서 캐릭터는 표시되지 않을 것이다.

제4d도에 도시된 전체 프로그램의 다음 부분에서 캐릭터가 형성된다(005). 각 캐릭터의 각 행에 대한 도트 패턴은 ROM(29)에 기억된 프로그램에 의해 결정된다. 후술되는 바와 같이, 채널 번호가 입력될 때 채널 번호의 두 디지트의 각행에 대한 도트 패턴은 마이크로프로세서(23)의 RAM(33)의 각메모리 위치에 기억된다. 각 도트는 각 비트로 표시된다. 제4e도에 도시된 바와 같이, 특정 행의 각주사선에서 도트 비트는 행에 대한 기억 위치를 판독하여 쉬프트 레지스터(Shift Register; SR; 41)에 병렬 형태로 결합된다. 그후 쉬프트 레지스터(41)가 인에이블되고 각각의 도트 비트를 명령사이클 레이트에서 일련 형태로 단자(SO)에 결합시킨다. 상기 처리는 캐릭터 표시가 완료될 때까지각 행및 각 행의 각 선에 대해 반복된다.

제4도에 표시된 바와 같이, 캐릭터가 형성된 후 채널 번호 BCD신호 십단위 및 단단위 디지트가 인입되어 기억된다(006). 특히, 제4f도를 참조하면 십단위 및 단단위 디지트가 차례로 입력되어 기억된다. 단단위 디지트가 최종적으로 기억되고 십단위 디지트가 처음에 형성되어지므로 십단위 디지트에대한 기억 위치는 프로그램의 캐릭터 포맷부의 대비로 식별되거나 지정받게 된다.

제4도에 표시된 프로그램의 포맷화부분(007)에 있어서, 인입된 캐릭터의 각 행에 대한 도트 비트가 포맷되므로, 캐릭터가 상기에 표시된 바와 같이 형성될 수 있다. 이후 프로그램은 초기상태(개시)로 복귀한다. 특히 제4g도를 참조하면, 좌측캐릭터(즉, 십단위 디지트)가 포맷된 다음 우측 캐릭터(즉, 단단위 디지트)가 포맷된다. 인입된 특정 캐릭터가 일단 식별되면, 상술한 바와 같이 상기 각 행은 프로그램된 코드에 따라 포맷되고, 캐릭터가 형성되는 동안 재호출하기 위해 대응 기억위치에 기억

선택한 채널에 대해 적절히 동조된 RF 신호가 없을때, 편향 유니트(19)에 의해 발생된 동기신호에 마이크로프로세서(23)의 동작을 동기시키기 위해 마이크로프로세서(23)를 인에이블시켜 온-스크린 캐릭터 표시를 발생하더라도, 화상 처리 유니트(13)에 의해 제공된 합성 동기신호는 적합한 수평 및 수직 동기성분보다는 잡음성분을 포함게 된다. 이러한 상태하에서 편향유니트(19)가 잡음성분에 응답하기 때문에, 캐릭터은 왜곡될 것이다(즉, 수평 연부(horizontal edge)에서 찌그러진다).

특히, 편향 유니트(19)는 위상 동기루프를 포함하는데, 상기 위상 동기루프는 수평 레이트의 몇배가 되는 주파수를 갖는 발진기를 합성 동기신호의 수평 동기성분에 따라 동기시킨다. 발진기의 출력신호는 수평 및 수직 평향신호가 적당한 계수에서 발생되는 수평 및 수직 구동신호를 생성하는 계수장치에 공급된다. 보통, 계수장치는 수직 동기성분에 응답하여 리셋트되어 수직 구동신호를 발생시킨다. 그러나, 수직 구동신호가 없거나 적당한 상태를 나타내지 않으면, 계수장치는 수직 구동신호를 발생시키기 위하여 일필드의 가시부(the visible protion)에서 수평 주사선의 수, 예로서 525에 대

응하는 설정된 계수로 리셋트될 것이다. 이러한 계수장치는 편향신호의 발생이 비교적 잡음에 무관하게 하기 위한 것이다. 이러한 계수장치는 1975년 4월 15일자로 A.R.Balaban에게 부여된 미합중국특허 제3,878,335호와 1981년 2월 17일자로 R.E.Fernsler 및 D.H.Willis에게 부여된 미합중국특허 제4,251,833호에 상세히 기재되어 있다.

상술한 편항 유니트가 잡음에 대한 편향신호의 민감도를 효과적으로 감소시킨다하더라도 적절히 동조된 RF 신호가 없는 상태에서 위상 동기 루프는 발진기의 주파수를 초기에 변형하기 위하여 잡음성분에 응답할 것이며 이에 의해, 표시된 채널번호가 왜곡되는 것으로 알려져 있다.

RF 신호가 아직 적당히 동조되지 않을시에 동조 동작 동안 새로이 선택된 채널의 채널번호의 표시를 제공하는 것이 바람직한 것과 마찬가지로 제1도에 도시된 장치는 적당히 동조된 RF 신호가 없을때 안정한 수평 레이트 동기신호를 화상처리 유니트(13)로부터 제공된 신호로 대처하기 위한 장치를 포함한다. 이러한 목적을 위하여, 동기신호(sync)의 유효성 검출기(61)의 출력신호는 전술한 프랑스특허에서 설명한 방법으로 적당한 동조된 RF 신호를 얻을 때까지 튜너 및 IF단(3)의 국부발진기의 주파수를 점증적으로 변화시키기 위해 튜너 제어유니트(5)에 접속되며, 마이크로프로세서(23)의 단자(63)에 결합된다. 동기신호 유효성 검출길(61)의 화상처리 유니트에 의해 제공된 합성 동기신호를 평가하여 합성동기신호가 정확한 특성을 나타낼때 고레벨을 제공하고 합성동기신호가 정확한 특성을 나타내지 않을때 저레벨을 제공한다. 프로그램내의 편리한 지점에서, 예를 들어, 제4도에 표시된 (004)인 타임아웃부분 바로 다음에서 단자(63)의 레벨을 검사한다. 상기 레벨이 정확한 합성동기신호를 나타내는 고레벨이면, 프로그램은 상술한 바와 같이 계속되는데, 즉, 부분(005-007)이 수행된다. 그러나, 상기 레벨이 부정확한 합성동기신호를 나타내는 저레벨이면, 프로그램의 보조경로는 부분(001-007)을 포함하는 경로로 대체된다. 보조경로는 실질적으로 단자(R0)가 저레벨로 셋트된 지점에서 정방향 진행펄스가 단자(65)에서 발생되는 부분을 제외하고 부분(001-007)을 포함하는 부분 자심성상 동일하다. 단자(R0)가 일반적으로 수평레이트에서 저레벨로 셋트될때, 단자(65)에서 발생된다(클럭신호발진기(37)의 주파수는 공칭 주파수에서 약간 변경됨을 주의). 단자(65)에서 발생된다(클럭신호발진기(37)의 주파수는 공칭 주파수에서 약간 변경됨을 주의). 단자(65)에서 발생된 신호는 다이오드(67)를 통해 편향 유니트(19)의 위상 동기 루프의수평동기입력신호(H) 즉, 텔레비젼 동기신호(HFB)와 대체되는 대체동기신호(H)로 제공되며 이에 의해 편향유니트(19)이 발진기가 공칭 주파수에서 안정하게 발진하게 된다.

프로그램의 보조부분동안 단자(65)에서 발생된 정방향 펄스는 하나의 명령사이클에서 단자(65)를 고 레벨로 셋트함에 의해 형성된 후, 다음 명령사이클에서 저레벨로 셋트된다. 그러나, 동기시키기 위 해 마이크로프로세서에 대한 동기신호가 수신되지 않으므로, 먼저 단자(RO)를 저레벨로 셋트할 필요 가 없고 다음에 10개의 명령 사이클후에 고레벨에 셋트할 필요가 없어 동기화가 이루어진다. 대신에, 단자(65)를 고레벨로 셋트한 후 저레벨로 셋트하는 명령은 단자(RO)를 고벨레로 셋트한후 저레벨로 셋트하는 명령으로 대체된다. 따라서, 동일한 설정된 수, 예로서, 20개의 명령사이클이 프 로그램의 각 부분에서 사용될 것이다.

상술한 실시예에 대한 다른 변경이 있을수 있다. 예를 들어, 검은 테두리를 채널번호에 제공하여 좀더 잘 보이게 할 수도 있다. 게다가, 문자나 심볼을 포함하는 다른 캐릭터가 동일한 방법으로 형성될 수도 있다. 또한, 캐릭터 발생장치가 화상관을 포함하는 텔레비젼 수상기에 합체되는 것으로 기술되어 있으나, 화상관을 포함할 뿐만 아니라 텔레비젼 수상기나 모니터에 연관된 화상관 수단에 의해 화상을 표시하는 신호를 발생하기도 하는 비디오 카셋트 레코더와 같은 텔레비젼 부속물에도 함께 사용될 수 있다. 이경우에, 부속물에 합체된 상술된 바와 같이 캐릭터 발생장치에 의해 발생된 캐릭터 신호는 부속물에 의해 예를 들어, 결합된 신호를 비사용 채널의 RF 반송파로 변조함에 의해발생된 텔레비젼 신호와 함께 텔레비젼수상기나 모니터에 인가될 수 있다. 상술된 등기 구조체는 수평선의 주어진 지점에서 비디오 신호를 샘플링하는 온-스크린 캐릭터 표시를 형성하기 위한 것과는다른 목적을 위하여 쓰일수도 있다. 상기 및 다른 변경은 다음의 청구범위에 의해 규정된 본 발명의 범주내에 속하는 것으로 간주된다.

### (57) 청구의 범위

### 청구항 1

클럭신호와 동기적으로 관련된 레이트(rate)로 발생하는 명령 사이클에 대해 시간관계로(in timed relationship) 실행되는 기억프로그램 명령에 응답하여 동작하는 계산장치와, 상기 클럭신호를 발생하며 제어신호에 응답해서 상기 클럭신호의 위상 및 주파수를 제어하는 클럭신호 발생장치(45,37)와, 기준 주파수를 갖는 기준 주파수 신호원을 포함하는 동기장치에 있어서, 상기

계산장치는 설정된 수의 명령 사이클이 발생될 때마다 비교신호를 발생하도록 프로그램되며, 상기 비교신호의 위상 및 주파수와 기준신호(HFB)의 위상 및 주파수를 비교하고 이에 응답하여 상기 제어 신호를 발생하는 비교장치(51,53)를 포함하는 것을 특징으로 하는 동기장치.

#### 청구항 2

제1항에 있어서, 상기 계산장치는 집적회로로 구현된 마이크로프로세서(23)를 포함하는 것을 특징으로 하는 동기장치.

### 청구항 3

선 주사기간동안 선에 주사되는 화상 표시장치(17)상의 화상을 형성하기 위한 텔레비젼의 시스템내에서 집적회로로 구현되고 클럭신호와 시간관계로 발생하는 명령 사이클에 대해 시간관계로 실행되는 프로그램된 명령에 응답하여 동작하는 마이크로프로세서(23)와, 상기 클럭신호를 발생하며 제어신호에 응답해서 상기 클럭신호의 위상 및 주파수를 제어하는 클럭신호 발생장치(45,37)와, 상기 선주사기간이 발생하는 레이트를 갖춘 기준 주파수 신호를 규정하는 텔레비젼 동기신호원을 포함하는 동기장치에 있어서, 상기 클럭신호 및 상기 텔레비젼 동기신호(HFB)에 응답하여 상기 클럭신호 및 상기 명령 사이클을 상기 텔리비젼 동기신호와 동기시키기 위해 상기 제어신호를 발생하는 동기수단

(23,51,57,45,37)과, 캐릭터에 대응하는 데이타 신호원(7, 29)과, 상기 캐릭터 슬라이스를 표시하기 위해 상기 캐릭터 펄스를 상기 펄스에 응답하는 상기 화상 표시장치(17)로 공급하는 결합수단 (41,25,15)을 더 포함하고, 상기 마이크로프로세서 (23)가 상기 선 주사기간동안 상기 명령 사이클 의 레이트에 비례하는 레이트로 캐릭터 펄스를 발생시키도록 프로그램되는 것을 특징으로 하는 동기 장치.

#### 청구항 4

제3항에 있어서, 상기 동기수단(23,51,57,45,37)은 설정된 수의 명령 사이클이 발생한 때마다 상기 비교신호를 발생시키도록 프로그램된 상기 마이크로프로세서(23)에 의해 발생된 비교신호의 위상 및 주파수와 상기 텔레비젼 동기신호(HFB)의 위상 및 주파수를 비교하여 상기 제어신호를 발생하는 비교장치(51,53)를 포함하고, 상기 텔레비젼 동기신호(HFB)가 부적절할 경우를 검출하기 위한 검출수단(61)을 더 포함하며, 상기 마이크로프로세서(23)가 부적절한 텔레비젼 동기신호(VDR)의 검출에 응답하도록 프로그램되어 상기 설정된 수의 명령 사이클이 발생될 때마다 발생된 펄스를 포함하는 대체 동기신호(H)를 제공하는 것을 특징으로 하는 동기장치.

#### 청구항 5

제1항에 있어서, 상기 클럭신호의 주파수가 공칭주파수이며, 상기 기준 주파수의 정수배이고, 상기 설정된 수의 명령 사이클이 선택되므로 상기 비교신호의 주파수가 공칭적으로 상기 기준 주파수와 동일한 것을 특징으로 하는 동기장치.

#### 청구항 6

제1항에 있어서, 상기 비교신호의 발생(제2도의 C)은 제1레벨(207)에서 제2레벨(209)로의 제1천이 (205)에 의해 표시되며, 상기 비교신호의 종류는 상기 제2레벨(209)에서 상기 제1레벨(207)로의 제2천이(215)에 의해 표시되고 상기 제2천이는 상기 제1천이 후 발생된 상기 설정된 수의 명령 사이클의 1/2과 거의 동일한 수의 명령 사이클을 발생하는 것을 특징으로 하는 동기장치.

#### 청구항 7

제2항에 있어서, 상기 클럭신호 발생장치(45,37)는 집적회로의 각 단자에 접속된 입력(EX) 및 출력(X)을 갖는 상기 집적회로내에 포함된 증폭장치(43)와, 상기 단자를 통해 상기 증폭장치(43)의 상기입력(EX) 및 출력(X)간의 궤환회로에 접속된 상기 집적회로 외부의 주파수 결정신호(45)를 포함하고, 상기 비교장치(51,53)는 상기 비교신호와 상기 기준신호(HFB)가 일치할 때 회로점에서 펄스를 발생하는 동기검출회로 (51)와 상기 회로점 및 상기 단자중 한단자간에 결합된 필터수단(53)을 포함하는 것을 특징으로 하는 동기장치.

#### 청구항 8

제2항에 있어서, 텔리비젼 수직 레이트신호(VDR)원(19)을 더 포함하고, 상기 마이크로프로세서(23)가 상기 수직 레이트신호(VDR)에 응답하도록 프로그램되어 상기 수직 레이트신호(VDR)의 발생후 상기 비교신호가 발생되는 횟수를 계수하는 것을 특징으로 하는 동기장치.

#### 청구항 9

제1항에 있어서, 캐릭터에 대응하는 데이타 신호원을 더 포함하고, 상기 계산장치가 상기 데이타신호에 응답하여 상기 비교신호의 대응계수에서 상기 캐릭터의 슬라이스에 대한 상기 명령 사이클의레이트에 비례하는 레이트로 캐릭터 펄스를 발생하는 것을 특징으로 하는 동기장치.

### 청구항 10

제3항에 있어서, 상기 클럭신호의 주파수가 공칭주파수이며 상기 기준 주파수의 정수배이고, 상기 설정된 수의 명령 사이클이 선택되므로 상기 비교신호의 주파수가 공칭적으로 상기 기준 주파수와 동일한 것을 특징으로 하는 동기장치.

### 청구항 11

제4항에 있어서, 상기 비교신호의 발생(제2도의 C)은 제1레벨(207)에서 제2레벨(209)로의 제1천이 (205)에 의해 표시되며, 상기 비교신호의 종료는 상기 제2레벨 (209)에서 상기 제1레벨(207)로의 제2천이(215)에 의해 표시되고, 상기 제2천이는 상기 제1천이 후 발생된 상기 설정된 수의 명령 사이클의 1/2과 거의 동일한 수의 명령 사이클을 발생시키는 것을 특징으로 하는 동기장치.

### 청구항 12

제4항에 있어서, 상기 클럭신호 발생장치(45,37)는 집적회로의 각 단자에 접속된 입력(EX) 및 출력(X)을 갖는 상기 집적회로내에 포함된 증폭장치(43)와, 상기 단자를 통해 상기 증폭장치(43)의 상기입력(EX) 및 출력(X)간의 궤환회로에 접속된 상기 집적회로 외부의 주파수 결정신호(45)를 포함하고, 상기 비교장치(51,53)는 상기 비교신호와 상기 기준신호(HFB)가 일치할 때 회로점에서 펄스를 발생하는 동기검출회로(51)와 상기 회로점 및 상기 단자중 한단자간에 결합된 필터수단(53)을 포함하는 것을 특징으로 하는 동기장치.

### 청구항 13

제3항에 있어서, 텔리비젼 수직 레이트신호(VDR)원(19)을 더 포함하고, 상기 마이크로프로세서(23)가 상기 수직 레이트신호(VDR)에 응답하도록 프로그램되어 상기 수직 레이트신호(VDR)의 발생후 상기 비교신호가 발생되는 횟수를 계수하는 것을 특징으로 하는 동기장치.

# 도면

# 도면1

# 도면2

### 도면3

# 도면4

### 도면4a

# 42181611

# 도면4b

### 도면4c

# *도면4d*

### 도면4e