# (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5040387号 (P5040387)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月20日(2012.7.20)

| (51) Int.Cl. | F I                           |                         |

|--------------|-------------------------------|-------------------------|

| HO1L 21/8234 | <b>4 (2006.01)</b> HO1L       | 27/06 1 O 2 A           |

| HO1L 27/06   | ( <b>2006.01)</b> HO1L        | , 27/04 H               |

| HO1L 27/04   | <b>(2006.01)</b> HO1L         | 29/78 3 O 1 D           |

| HO1L 21/822  | <b>(2006.01)</b> HO1L         | . 29/78 6 1 6 V         |

| HO1L 29/78   | ( <b>2006.01)</b> HO1L        | 29/78 6 1 3 Z           |

|              |                               | 請求項の数 8 (全 15 頁) 最終頁に続く |

| (21) 出願番号    | 特願2007-73320 (P2007-73320)    | (73) 特許権者 000004260     |

| (22) 出願日     | 平成19年3月20日 (2007.3.20)        | 株式会社デンソー                |

| (65) 公開番号    | 特開2008-235592 (P2008-235592A) | 愛知県刈谷市昭和町1丁目1番地         |

| (43) 公開日     | 平成20年10月2日 (2008.10.2)        | (74) 代理人 100106149      |

| 審査請求日        | 平成21年8月25日 (2009.8.25)        | 弁理士 矢作 和行               |

|              |                               | (74) 代理人 100121991      |

|              |                               | 弁理士 野々部 泰平              |

|              |                               | (72) 発明者 赤木 望           |

|              |                               | 愛知県刈谷市昭和町1丁目1番地 株式会     |

|              |                               | 社デンソー内                  |

|              |                               | (72) 発明者 高橋 茂樹          |

|              |                               | 愛知県刈谷市昭和町1丁目1番地 株式会     |

|              |                               | 社デンソー内                  |

|              |                               |                         |

|              |                               | 最終頁に続く                  |

# (54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

# 【請求項1】

半導体基板の表層部に、横型MOSトランジスタが形成されてなる半導体装置であって

前記横型MOSトランジスタのゲート駆動信号ラインに、前記横型MOSトランジスタのドレインと逆の導電型の多結晶シリコン抵抗体が挿入配置され、

絶縁膜を介して、前記横型MOSトランジスタのドレイン電圧が前記多結晶シリコン抵抗体に印加される半導体装置であり、

前記絶縁膜が、前記横型MOSトランジスタのドレインのドリフト領域上に形成され、 前記多結晶シリコン抵抗体が、前記絶縁膜上に配置されてなることを特徴とする半導体 装置。

# 【請求項2】

前記絶縁膜が、LOCOS酸化膜であることを特徴とする請求項1に記載の半導体装置

# 【請求項3】

前記多結晶シリコン抵抗体が、前記半導体基板における前記横型MOSトランジスタの 形成領域の外周部に配置されてなることを特徴とする請求項2に記載の半導体装置。

## 【請求項4】

半導体基板の表層部に、横型MOSトランジスタが形成されてなる半導体装置であって

20

10

.

前記横型MOSトランジスタのゲート駆動信号ラインに、前記横型MOSトランジスタのドレインと逆の導電型の多結晶シリコン抵抗体が挿入配置され、

絶縁膜を介して、前記横型MOSトランジスタのドレイン電圧が前記多結晶シリコン抵抗体に印加される半導体装置であり、

\_\_前記絶縁膜が、前記横型MOSトランジスタのドレインのドリフト領域に形成されたトレンチの側壁絶縁膜であり、

<u>前記多結晶シリコン抵抗体が、前記側壁絶縁膜を介して前記トレンチ内に埋め込まれた</u> 多結晶シリコンであることを特徴とする半導体装置。

# 【請求項5】

前記多結晶シリコン抵抗体と前記横型MOSトランジスタの多結晶シリコンからなるゲート電極が、配線により接続されてなることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

#### 【請求項6】

前記多結晶シリコン抵抗体と前記横型MOSトランジスタの多結晶シリコンからなるゲート電極が、一体的に形成されてなることを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

## 【請求項7】

前記多結晶シリコン抵抗体と前記ゲート電極が、異なる導電型であり、

前記多結晶シリコン抵抗体の一部と前記ゲート電極に当接して、シリサイド層または金属層が形成されてなることを特徴とする請求項6に記載の半導体装置。

#### 【請求項8】

前記多結晶シリコン抵抗体と前記ゲート電極が、同じ導電型であることを特徴とする請求項6に記載の半導体装置。

【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明は、半導体基板の表層部に横型MOSトランジスタ(LDMOS, Lateral Diffused Metal Oxide Semiconductor)が形成されてなる半導体装置に関する。

#### 【背景技術】

# [0002]

半導体基板の表層部に横型MOSトランジスタ素子が形成されてなる半導体装置および その製造方法が、例えば、特開2001-352707号公報(特許文献1)に開示され ている。

### [0003]

図11は、特許文献1に開示ざれた半導体装置で、半導体装置80の模式的な断面図である。図11に示す半導体装置80は、p型シリコン基板2、絶縁層3、n型層1からなるSOI基板に形成されている。半導体装置80においては、n+型ドレイン領域5を囲むように、n型層1よりも高濃度に形成され、n+型ドレイン領域5に近づくほど高濃度となるn型領域(ドリフト領域)6が配置されている。さらに、n+型ソース領域8に隣接配置されるp+型コンタクト領域9が、n+型ソース領域8の下部まで入り込むように形成されている。尚、図11において、符号4はLOCOS酸化膜、符号11はゲート電極である。

# [0004]

図11に示す半導体装置80は、n型層1の表層部にソースとドレインが配置され、キャリアが半導体基板の横方向に流れる、横型MOSトランジスタ素子(LDMOSと略記)が形成された半導体装置となっている。LDMOSは、他のトランジスタ素子に較べて高速スイッチングが可能であることから、例えばトランジスタ素子を高速でオン・オフさせるスイッチング回路やスイッチング電源に利用される。

# [0005]

一般的に、DC-DCコンバータやインバータ等のスイッチング回路では、回路の動作

10

20

30

40

周波数を高周波化するほど、付属するインダクタンスやキャパシタンスが小さくなって、小型化することができる。このため、できるだけ高いスイッチング速度のトランジスタ素子が必要であり、LDMOSは上記用途に好適である。一方、LDMOSに限らず、一般的にトランジスタ素子を高速でスイッチングすると、その急激な電圧変化(dV/dt)でドレイン電圧のオーバーシュート(サージ電圧)が生じ、発生ノイズ(リンギング)が増大すると共にスイッチング損失も増大してしまう。

#### [0006]

スイッチング回路に適用するトランジスタ素子の上記課題を解決する半導体装置が、特開2004-6598号公報(特許文献2)に開示されている。

#### [0007]

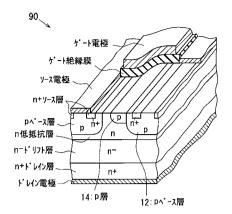

図12は、特許文献2に開示ざれた半導体装置で、半導体装置90の模式的な斜視図において、要部を部分的に断面で示した図である。図12に示す半導体装置90は、半導体基板の両側にソースとドレインが配置され、キャリアが半導体基板の縦方向に流れる、縦型MOSトランジスタ素子(VDMOS(Vertical Diffused Metal Oxide Semiconductor)と略記)が形成された半導体装置である。図12の半導体装置90は、pベース層12に隣接する位置に、ドレインと反対極性のp導電型の不純物を低濃度に含むp層14を設けることを特徴としている。

### [00008]

図12の半導体装置90では、p層14の形成により、ドレイン電圧が高くなるほどゲート・ドレイン間容量を増大させることができ、これによってドレインでのサージ電圧の発生を抑制している。しかしながら、p層14の形成はVDMOS構造を有する半導体装置90において有効なものであり、LDMOS構造を有する半導体装置に同様のp層14を形成すると、キャリア流路への影響が大きくてLDMOSの設計が困難となる。また、半導体装置90ではキャリアが低不純物濃度のp層14を流れるために、オン抵抗が高くなってしまう。さらに、p層14の形成のみではゲート・ドレイン間容量の増加が不十分で、サージ電圧の抑制効果も不十分である。

【特許文献1】特開2001-352707号公報

【特許文献 2 】特開 2 0 0 4 - 6 5 9 8 号公報

【発明の開示】

【発明が解決しようとする課題】

#### [0009]

そこで、上記スイッチング回路に適用するトランジスタ素子の問題を回避するため、MOSトランジスタの新規な駆動回路が発明された。

### [0010]

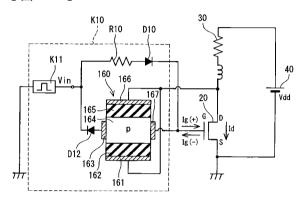

図13は、上記MOSトランジスタの新規な駆動回路を用いたスイッチング回路の一例で、破線で囲った部分が、電界効果型のトランジスタ20(n型MOSトランジスタ)を駆動するための駆動回路K10である。図13に示すトランジスタ20の駆動回路K10は、トランジスタ20のゲート入力抵抗として、MOS構造を有するMOS型抵抗体160を備えている。

## [0011]

図13のスイッチング回路において、トランジスタ20は、負荷30とグランドの間に接続されている。トランジスタ20と負荷30の間には、配線の寄生インダクタンスが接続されている。駆動回路 K10は、矩形波の駆動電圧 Vinをトランジスタ20のゲート電極 Gに供給し、その駆動電圧 Vinに基づいてトランジスタ20のオン・オフを切替える。駆動回路 K10は、トランジスタ20のオン・オフを切替えることによって、電圧供給源40の直流電圧 Vddを負荷30に供給する状態と供給しない状態を切替える。

#### [0012]

駆動回路 K 1 0 は、駆動電圧生成回路 K 1 1 と、固定抵抗体 R 1 0 と、第 1 ダイオード D 1 0 と、第 2 ダイオード D 1 2 と、 M O S 型抵抗体 1 6 0 を備えている。固定抵抗体 R 1 0 と第 1 ダイオード D 1 0 は直列に接続されており、 M O S 型抵抗体 1 6 0 と第 2 ダイ

10

20

30

40

10

20

30

40

50

オード D 1 2 は直列に接続されている。固定抵抗体 R 1 0 と第 1 ダイオード D 1 0 の組と M O S 型抵抗体 1 6 0 と第 2 ダイオード D 1 2 の組は、駆動電圧生成回路 K 1 1 とトランジスタ 2 0 の間で並列回路を構成している。第 1 ダイオード D 1 0 のアノードは駆動電圧 生成回路 K 1 1 側に接続しており、カソードはトランジスタ 2 0 側に接続している。第 2 ダイオード D 1 2 のアノードはトランジスタ 2 0 側に接続しており、カソードは駆動電圧 生成回路 K 1 1 側に接続している。

#### [0013]

MOS型抵抗体160は、酸化シリコンの第1絶縁体領域162と、p型の不純物を含む単結晶シリコンのp型半導体領域164と、酸化シリコンの第2絶縁体領域165を備えている。第1絶縁体領域162と第2絶縁体領域165は、p型半導体領域164によって隔てられている。第1電極161は、第1絶縁体領域162を介してp型半導体領域164に対向している。第2電極166は、第2絶縁体領域165を介してp型半導体領域164に対向している。第1電極161と第2電極166は、トランジスタ20のドレイン電極Dに電気的に接続している。p型半導体領域164の一端は、第3電極167を介してトランジスタのゲート電極Gに電気的に接続している。p型半導体領域164の他端は、第4電極163を介して駆動電圧生成回路K11に電気的に接続している。

#### [0014]

MOS型抵抗体160は、電界効果によってp型半導体領域64内に伸縮する空乏層の幅を調整することができ、MOS型抵抗体160の抵抗値Rは、印加される電圧Vに応じてほぼ連続的に増加する。このため、MOS型抵抗体160の抵抗値Rは、ドレイン・ソース間電圧Vdsが小さいときに小さく調整され、ドレイン・ソース間電圧Vdsが大きいときに大きく調整される。すなわち、ゲート入力抵抗であるMOS型抵抗体160の抵抗値Rをドレイン電圧が高くなるほど増大させ、スイッチングの初期は高速でスイッチングし、電圧のオーバーシュートが問題になるスイッチング後期でスイッチング速度を低減する。これによって、ドレインでのサージ電圧の発生を、顕著に抑制することができる。

# [0015]

尚、上記MOSトランジスタの駆動回路の発明については、すでに特許出願(出願番号2006-204770)がなされている。

# [0016]

本発明は、駆動回路に上記MOS型抵抗体が組み込まれてなり、ドレイン電圧のオーバーシュートを低減してノイズとスイッチング損失の増大を抑制することが可能な半導体装置であって、特に、高速スイッチングが可能な横型MOSトランジスタを用いた、小型で安価な半導体装置を提供することを目的としている。

# 【課題を解決するための手段】

# [0017]

請求項1に記載の半導体装置は、半導体基板の表層部に、横型MOSトランジスタが形成されてなる半導体装置であって、前記横型MOSトランジスタのゲート駆動信号ラインに、前記横型MOSトランジスタのドレインと逆の導電型の多結晶シリコン抵抗体が挿入配置され、絶縁膜を介して、前記横型MOSトランジスタのドレイン電圧が前記多結晶シリコン抵抗体に印加される半導体装置であり、前記絶縁膜が、前記横型MOSトランジスタのドレインのドリフト領域上に形成され、前記多結晶シリコン抵抗体が、前記絶縁膜上に配置されてなることを特徴としている。

# [0018]

上記半導体装置は、横型MOSトランジスタが形成されてなる半導体装置である。半導体基板の一方の表層部にソースとドレインが配置され、キャリアが半導体基板の横方向に流れる横型MOSトランジスタは、他のトランジスタ素子に較べて高速スイッチングが可能であり、スイッチング回路やスイッチング電源への利用に適している。

#### [0019]

スイッチング回路では、一般的に、高速のトランジスタ素子を用いて回路の動作周波数を上げるほど、回路全体を小型化することができるが、スイッチングによる電圧変化(d

V / d t ) がより急激になるため、ドレイン電圧のオーバーシュート(サージ電圧、ノイズ)が増大してしまう。

# [0020]

しかしながら、上記半導体装置においては、横型MOSトランジスタのゲート駆動信号ラインにドレインと逆の導電型の多結晶シリコン抵抗体が挿入配置されており、該多結晶シリコン抵抗体には、絶縁膜を介して、スイッチング時に電位変動するドレイン電圧が印加される。該多結晶シリコン抵抗体は、不純物濃度を低く設定することでMOS構造を有するMOS型抵抗体として機能し、ドレインと逆の導電型であるため、ドレイン電圧が上昇すると該多結晶シリコン抵抗体内に空乏層が広がって、抵抗値が増大する。従って、該横型MOSトランジスタは、スイッチングの初期においてはゲート入力抵抗である該多結晶シリコン抵抗体の抵抗値が小さいため高速でスイッチングし、スイッチングの後期では該多結晶シリコン抵抗体の抵抗値が大きくなってスイッチング速度が低減する。これにより、ドレイン電圧のオーバーシュート(サージ電圧)を低減してノイズ(リンギング)を抑制すると共に、スイッチング損失の増大も防止することができる。

### [0021]

また、上記多結晶シリコン抵抗体は、多結晶シリコンからなり安価であると共に、半導体基板の種々の場所に形成することができる。このため、上記半導体装置は、小型化が可能である。

# [0022]

以上のようにして、上記半導体装置は、高速スイッチングが可能な横型MOSトランジスタが形成されてなる半導体装置であって、ドレイン電圧のオーバーシュート(サージ電圧)を低減してノイズとスイッチング損失の増大を抑制した、小型且つ低コストで製造できる半導体装置とすることができる。

#### [0023]

また、上記半導体装置は、<u>前</u>記絶縁膜が、前記横型MOSトランジスタのドレインのドリフト領域上に形成され、前記多結晶シリコン抵抗体が、前記絶縁膜上に配置されてなる構成とすることができる。この場合、請求項<u>2</u>に記載のように、前記絶縁膜が、LOCOS酸化膜であってもよい。

# [0024]

上記半導体装置では、横型MOSトランジスタのドレインのドリフト領域上に形成された絶縁膜(LOCOS酸化膜)を介して、ドリフト領域のドレイン電圧がドレインと逆の導電型の多結晶シリコン抵抗体に直接印加されることとなる。従って、上記半導体装置は、該多結晶シリコン抵抗体を配置することによってチップ面積が増大することはなく、構造も簡単であり、安価に製造することができる。

# [0025]

また、横型MOSトランジスタの形成領域の外周部にドレインのドリフト領域を延長し、請求項3に記載のように、前記多結晶シリコン抵抗体が、前記半導体基板における前記横型MOSトランジスタの形成領域の外周部におけるLOCOS酸化膜上に配置されてなる構成としてもよい。

## [0026]

横型MOSトランジスタをパワー素子として用いる場合、横型MOSトランジスタは、小さいセルが多数並列に並んだ構成となる。従って、チップ面積に余裕がある場合には、多結晶シリコン抵抗体を上記のように横型MOSトランジスタの形成領域の外周部に配置することで、横型MOSトランジスタの形成領域におけるセル構造を変えることなくパターン設計を単純化すると共に、該多結晶シリコン抵抗体の配置の自由度を高めることができる。

#### [0028]

また、<u>請</u>求項<u>4</u>に記載の<u>半導体装置は</u>、前記絶縁膜が、前記横型MOSトランジスタのドレインのドリフト領域に形成されたトレンチの側壁絶縁膜であり、前記多結晶シリコン抵抗体が、前記側壁絶縁膜を介して前記トレンチ内に埋め込まれた多結晶シリコンである

10

20

30

40

<u>ことを特徴としている</u>。当該半導体装置においては、多結晶シリコン抵抗体がトレンチ内に配置されるため、これによっても該多結晶シリコン抵抗体の配置に伴うチップ面積の増大を抑制することができる。

#### [0029]

例えば請求項<u>5</u>に記載のように、上記半導体装置においては、前記多結晶シリコン抵抗体と前記横型MOSトランジスタの多結晶シリコンからなるゲート電極が、配線により接続されてなる構成とすることができる。

## [0030]

一方、請求項<u>6</u>に記載のように、前記多結晶シリコン抵抗体と前記横型MOSトランジスタの多結晶シリコンからなるゲート電極が、一体的に形成されてなる構造であってもよい。この場合には、多結晶シリコン抵抗体とゲート電極を接続する配線が不要となるため、多結晶シリコン抵抗体の形成による配線効率の低下を抑制することができる。

#### [0031]

尚、請求項<u>7</u>に記載のように、横型MOSトランジスタの閾値電圧制御のために、前記多結晶シリコン抵抗体と前記ゲート電極を、異なる導電型とする場合には、前記多結晶シリコン抵抗体の一部と前記ゲート電極に当接して、シリサイド層または金属層が形成されてなることが好ましい。これによって、多結晶シリコン抵抗体の一部とゲート電極がシリサイド層または金属層により短絡されるため、異なる導電型であっても簡単な構造で多結晶シリコン抵抗体とゲート電極を接続することができる。

# [0032]

一方、請求項<u>8</u>に記載のように、前記多結晶シリコン抵抗体と前記ゲート電極が、同じ 導電型である場合には、多結晶シリコン抵抗体とゲート電極を接続するための特別な構造 が必要ないため、構造を簡略化でき、製造コストが低減される。

【発明を実施するための最良の形態】

#### [0033]

以下、本発明を実施するための最良の形態を、図に基づいて説明する。

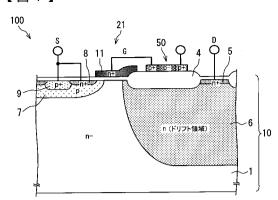

#### [0034]

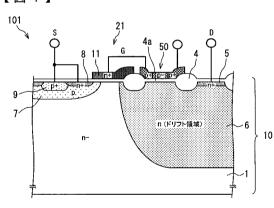

図1は、本発明の半導体装置の一例で、半導体装置100の模式的な断面図である。尚、図1の半導体装置100において、図11に示した半導体装置80と同様の部分については同じ符号を付して、その説明は省略する。

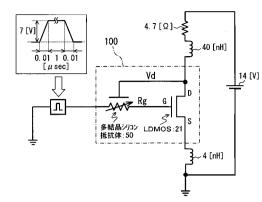

# [0035]

また、図 2 は、図 1 の半導体装置 1 0 0 を等価回路で示したスイッチング回路の回路図で、一点鎖線で囲った部分が図 1 の半導体装置 1 0 0 に相当する。尚、図 2 のスイッチング回路において、図 1 3 に示したスイッチング回路と同様の部分については同じ符号を付して、その説明は省略する。また、図 2 の回路図においては、簡略化して図を見やすくするため、図 1 3 の回路図に描かれている固定抵抗体 R 1 0 と第 1 ダイオード D 1 0 、および第 2 ダイオード D 1 2 の図示を省略している。

## [0036]

図1に示すように、半導体装置100は、半導体基板10の表層部に、横型MOSトランジスタ(以下、LDMOSと略記)21が形成されてなる半導体装置である。半導体装置100では、図1と図2に示すように、LDMOS21のゲート駆動信号ラインに、LDMOS21のドレイン(N型)と逆の導電型(P型)の多結晶シリコン抵抗体50が挿入配置されている。この多結晶シリコン抵抗体50は、LDMOS21のドレイン(D)のドリフト領域6上に形成されたLOCOS酸化膜4からなる絶縁膜上に配置されている。このため、LOCOS酸化膜4を介して、LDMOS21のドリフト領域6のドレイン電圧Vdが多結晶シリコン抵抗体50に印加される構成となっている。

#### [0037]

図1に示す半導体装置100は、図12に示した半導体装置90と異なり、LDMOS 21が形成されてなる半導体装置である。半導体基板10の一方の表層部にソース(S) とドレイン(D)が配置され、キャリアが半導体基板10の横方向に流れるLDMOS2

10

20

30

40

1 は、他のトランジスタ素子に較べて高速スイッチングが可能であり、スイッチング回路 やスイッチング電源への利用に適している。

#### [0038]

スイッチング回路では、一般的に、高速のトランジスタ素子(LDMOS21)を用いて回路の動作周波数を上げるほど、回路全体を小型化することができるが、スイッチングによる電圧変化(dV/dt)がより急激になるため、ドレイン電圧のオーバーシュート(サージ電圧、ノイズ)が増大してしまう。

# [0039]

しかしながら、図1の半導体装置100においては、LDMOS21のゲート駆動信号ラインにドレイン(D)と逆の導電型(P型)の多結晶シリコン抵抗体50がゲート取動信号抵抗Rgとして挿入配置されている。該多結晶シリコン抵抗体50には、LOCOS酸化膜4からなる絶縁膜を介して、スイッチング時に電位変動するドレイン電圧Vdが印加下に低く設定(p-)することで、図13で説明したMOS構造を有するMOS型抵抗体として機能する。該多結晶シリコン抵抗体50の導電型はドレイン(D)と逆の導電型リコン抵抗体50の導電型はドレイン(D)と逆の導電型リコン抵抗体50内に空乏層が広がってドレイン電圧Vdが上昇すると、該多結晶シリコン抵抗体50内に空乏層が広がって抵抗値が増大する。従って、LDMOS21は、スイッチングの初期においてはゲート入力抵抗Rgである多結晶シリコン抵抗体50の抵抗値が大きくなってスイッチングし、スイッチングの後期では多結晶シリコン抵抗体50の抵抗値が大きくなってスイッチング速度が低減する。これにより、ドレイン電圧Vdのオーバーシュート(サージ電圧)を低減してノイズ(リンギング)を抑制すると共に、スイッチング損失の増大も防止することができる。

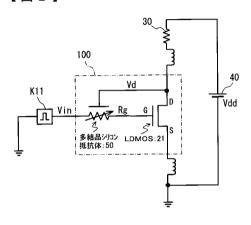

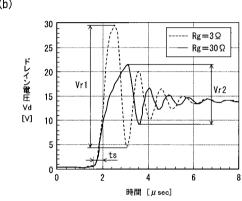

#### [0040]

図3は、上記多結晶シリコン抵抗体50による効果をシミュレーションにより見積もった結果で、図3(a)はシミュレーションの各設定パラメータを示す図であり、図3(b)は、シミュレーションにより得られたLDMOS21のゲート入力抵抗Rgをそれぞれ3,30とした場合のドレイン電圧Vdの立ち上り特性を示す図である。

#### [0041]

図3(b)に示すように、ゲート入力抵抗Rgをスイッチング途中において3 から30 に変更することで、図中にtsで示した区間の立ち上り速度がほとんど変わらずに、ドレイン電圧Vdのオーバーシュートおよびリンギングを図中のVr1からVr2に大きく低減することができる。

#### [0042]

図1に示す半導体装置100の多結晶シリコン抵抗体50は、多結晶シリコンからなり安価であると共に、後述するように半導体基板10の種々の場所に形成することができる。このため、図1の半導体装置100は、例えば図13に示した単結晶シリコンからなるMOS型抵抗体160を半導体基板の別位置や外部素子として独立して設ける場合に較べて、小型化が可能である。特に、図1の半導体装置100では、LDMOS21のドレイン(D)のドリフト領域6上に形成されたLOCOS酸化膜4を介して、ドリフト領域6のドレイン電圧Vdがドレイン(D)と逆の導電型の多結晶シリコン抵抗体50に直接印加されている。従って、図1の半導体装置100は、多結晶シリコン抵抗体50を配置することによってチップ面積が増大することはなく、構造も簡単であり、これによっても小型化が図れ、安価に製造することができる。

# [0043]

以上のようにして、図1に示す半導体装置100は、高速スイッチングが可能なLDMOS21が形成されてなる半導体装置であって、ドレイン電圧Vdのオーバーシュート(サージ電圧)を低減してノイズとスイッチング損失の増大を抑制した、小型且つ低コストで製造できる半導体装置とすることができる。

# [0044]

次に、図1の半導体装置100の変形例である種々の半導体装置を説明する。

10

20

30

#### [0045]

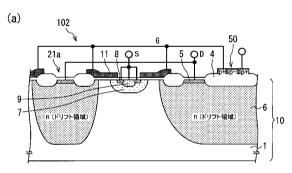

図4は、本発明における別の半導体装置の例で、半導体装置101の模式的な断面図である。尚、図4の半導体装置101において、図1の半導体装置100と同様の部分については、同じ符号を付した。

## [0046]

図4に示す半導体装置101では、多結晶シリコン抵抗体50が、LOCOS酸化膜4上ではなく、LDMOS21のドレイン(D)のドリフト領域6上に形成されたより薄い 絶縁膜4a上に配置されている。図4の半導体装置101では、図1の半導体装置100に較べて、多結晶シリコン抵抗体50の抵抗値のドレイン電圧Vdに対する依存性がより 大きくなり、低電圧で動作するLDMOS21に対して特に効果的である。

[0047]

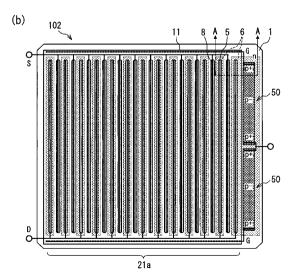

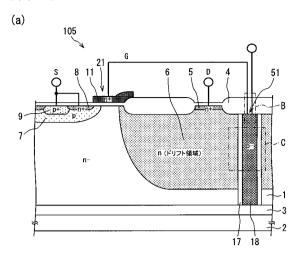

図5も別の半導体装置の例で、図5(a)は、半導体装置102の模式的な断面図である。また、図5(b)は、半導体装置102のチップ全体を示した模式的な平面図で、一点鎖線A-Aでの断面が、図5(a)に相当する。尚、図5の半導体装置102においても、図1の半導体装置100と同様の部分については、同じ符号を付した。

[0048]

半導体装置102は、図5(b)に示すように、LDMOS21aの形成領域の外周部にドレイン(D)のドリフト領域6を延長し、多結晶シリコン抵抗体50が、半導体基板(チップ)10におけるLDMOS21aの形成領域の外周部におけるLOCOS酸化膜4上に配置された構成となっている。

[0049]

LDMOSをパワー素子として用いる場合、LDMOSは、小さいセルが多数並列に並んだ構成となる。従って、チップ面積に余裕がある場合には、図5(b)に示す半導体装置102のように、多結晶シリコン抵抗体50をLDMOS21aの形成領域の外周部に配置することで、LDMOS21aの形成領域におけるセル構造を変えることなくパターン設計を単純化すると共に、該多結晶シリコン抵抗体50の配置の自由度を高めることができる。

[0050]

上記した半導体装置100~102では、いずれも、多結晶シリコン抵抗体50がLDMOS21,21aのドレイン(D)のドリフト領域6上に形成された絶縁膜(LOCOS酸化膜4、絶縁膜4a)上に配置され、該絶縁膜を介して、多結晶シリコン抵抗体50にドレイン電圧Vdが印加される構成となっていた。

[0051]

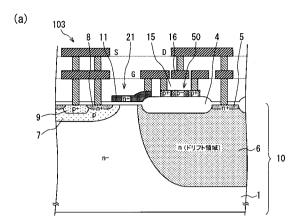

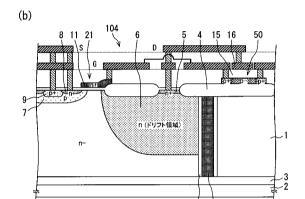

図6(a),(b)は、ドレイン電圧Vdを多結晶シリコン抵抗体50に印加する別の構成を有した半導体装置の例で、それぞれ、半導体装置103,104の模式的な断面図である。尚、図6(a),(b)の半導体装置103,104においては、それぞれ、図1の半導体装置100および図11の半導体装置80と同様の部分について、同じ符号を付した。

[0052]

図6(a),(b)に示す半導体装置103,104では、どちらも、多結晶シリコン抵抗体50の上方において、半導体基板上に形成された層間絶縁膜15を間に挟んで、LDMOS21のドレイン(D)に接続する配線層16が配置されている。従って、半導体装置103,104では、多結晶シリコン抵抗体50の上方にある層間絶縁膜15と配線層16を介して、ドレイン(D)と逆の導電型の多結晶シリコン抵抗体50にドレイン電圧Vdを印加する構成となっている。尚、図6(a)の半導体装置103における多結晶シリコン抵抗体50は、LDMOS21のドリフト領域6上に形成されたLOCOS酸化膜4上に配置されているため、LOCOS酸化膜4を介してもドレイン電圧Vdが印加される。このように、図6(a)の半導体装置103では多結晶シリコン抵抗体50の両側からドレイン電圧Vdが印加されるため、図1の半導体装置100に較べて、より大きなドレイン電圧Vd依存性を付与することができる。

10

20

30

40

10

20

30

40

50

#### [0053]

一方、図6(b)の半導体装置104は、p型シリコン基板2、絶縁層3、n型層1からなるSOI(Silicon On Insulator)構造の半導体基板に形成されており、LDMOS21は、側壁酸化膜17を介して内部に多結晶シリコン18が埋め込まれた絶縁層3に達する絶縁分離トレンチにより、周囲から絶縁分離されている。半導体装置104の多結晶シリコン抵抗体50は、絶縁分離トレンチの外側のLOCOS酸化膜4上に配置されているため、層間絶縁膜15とLDMOS21のドレイン(D)に接続する配線層16を介してのみ、ドレイン電圧Vdが印加される構成となっている。

# [0054]

図 6 ( a ) , ( b ) に示す半導体装置 1 0 3 , 1 0 4 は、いずれも構造が簡単であり、 安価に製造することが可能である。

#### [0055]

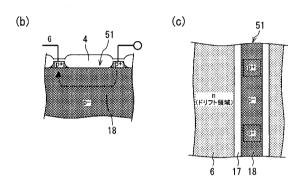

図7は、別構成の多結晶シリコン抵抗体を有する半導体装置の例で、図7(a)は、半導体装置105の模式的な断面図である。また、図7(b)は、図7(a)の一点鎖線Bで囲った部分を拡大した模式的な断面図であり、図7(c)は、図7(a)の二点鎖線Cで囲った部分を拡大した模式的な上面図である。尚、図7の半導体装置105においても、図11の半導体装置80と同様の部分について、同じ符号を付した。

# [0056]

図7に示す半導体装置105では、側壁絶縁膜17を介してトレンチ内に埋め込まれた低濃度(p-)の多結晶シリコン18が、図1~図6に示した半導体装置100~104における多結晶シリコン抵抗体50と同様の機能有する、多結晶シリコン抵抗体51となっている。すなわち、半導体装置105においては、横型MOSトランジスタ21のゲート駆動信号ラインに、横型MOSトランジスタ21のドレイン(D)と逆の導電型の多結晶シリコン抵抗体18が挿入配置された構成となっており、側壁絶縁膜17からなる絶縁膜を介して、横型MOSトランジスタ21のドリフト領域6のドレイン電圧Vdが、トレンチ内に埋め込まれた多結晶シリコン18からなる多結晶シリコン抵抗体51に印加される。従って、図7に示す半導体装置105についても、ドレイン電圧Vdのオーバーシュート(サージ電圧)を低減してノイズとスイッチング損失の増大を抑制した半導体装置とすることができる。

# [0057]

また、図7の半導体装置105においては、多結晶シリコン抵抗体51がトレンチ内に配置されるため、この場合にも、多結晶シリコン抵抗体51の配置に伴うチップ面積の増大を抑制することができる。

# [0058]

以上の図1~図7に示した半導体装置100~105においては、多結晶シリコン抵抗体50,51とLDMOS21の多結晶シリコンからなるゲート電極11が、配線により接続されてなる構成となっている。一方、多結晶シリコン抵抗体50,51とLDMOS21のゲート電極11は同じ多結晶シリコンからなるため、多結晶シリコン抵抗体とLDMOSのゲート電極が、一体的に形成されてなる構造であってもよい。

#### [0059]

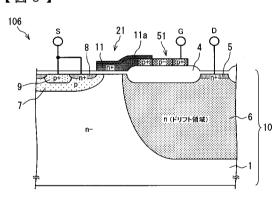

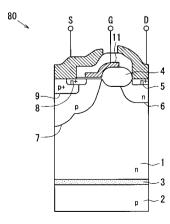

図8~図10は、いずれも上記多結晶シリコン抵抗体とLDMOSのゲート電極が一体的に形成されてなる半導体装置の例で、それぞれ、半導体装置106~108の模式的な断面図である。

# [0060]

図8に示す半導体装置106では、LDMOS21の閾値電圧制御のために、多結晶シリコン抵抗体51とゲート電極11を、異なる導電型としている。一体形成されたゲート電極11と多結晶シリコン抵抗体51における導電型と不純物濃度の異なる各領域は、イオン注入により不純物を打ち分けて形成する。半導体装置106のように多結晶シリコン抵抗体51をゲート電極11と異なる導電型とする場合には、図8に示すように、多結晶シリコン抵抗体51の一部とゲート電極11に当接して、シリサイド層(または金属)1

1 a が形成されてなることが好ましい。これによって、多結晶シリコン抵抗体 5 1 の一部とゲート電極 1 1 がシリサイド層(または金属層) 1 1 a により短絡されるため、異なる 導電型であっても簡単な構造で多結晶シリコン抵抗体 5 1 とゲート電極 1 1 を接続することができる。

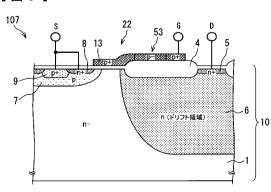

# [0061]

一方、図9に示す半導体装置 1 0  $\underline{7}$  では、多結晶シリコン抵抗体 5 3 と L D M O S 2 2 のゲート電極 1 3 が、同じ導電型 ( P 型 ) である。この場合には、 L D M O S 2 2 の閾値電圧は上昇するものの、多結晶シリコン抵抗体 5 3 とゲート電極 1 3 を接続するための特別な構造が必要ないため、構造を簡略化でき、製造コストが低減される。

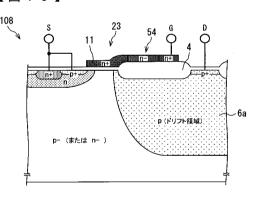

#### [0062]

図10の半導体装置10<u>8</u>では、LDMOS23のゲート電極11と多結晶シリコン抵抗体54を、同じN導電型の多結晶シリコンで一体的に形成している。図10に示す半導体装置10<u>7</u>の導電型を逆転した半導体装置となっており、図9の半導体装置10<u>7</u>のLDMOS22がNチャネルであるのに対し、図10の半導体装置10<u>7</u>のLDMOS22がNチャネルであるのに対し、図10の半導体装置10<u>8</u>のLDMOS23はPチャネルである。図10の半導体装置10<u>8</u>は、P導電型のドリフト領域6a内に形成されたLOCOS酸化膜4上にN導電型の多結晶シリコン抵抗体54が配置され、LOCOS酸化膜4を介して、LDMOS23のドリフト領域6aのドレイン電圧Vdが多結晶シリコン抵抗体54に印加される構成となっている。図10の半導体装置10<u>8</u>においても、多結晶シリコン抵抗体54の導電型がドレイン(D)と逆の導電型となっているため、先に説明したように、ドレイン電圧Vdのオーバーシュート(サージ電圧)を低減してノイズ(リンギング)を抑制すると共に、スイッチング損失の増大も防止することができる。

## [0063]

図8~図10に示した半導体装置106~108は、いずれも、多結晶シリコン抵抗体51,53,54とゲート電極11,13を接続する配線が不要となるため、多結晶シリコン抵抗体51,53,54の形成による配線効率の低下を抑制することができる。

#### [0064]

以上のようにして、図1~図10で例示した本願発明の半導体装置は、高速スイッチングが可能な横型MOSトランジスタが形成されてなる半導体装置であって、ドレイン電圧のオーバーシュート(サージ電圧)を低減してノイズとスイッチング損失の増大を抑制した、小型且つ低コストで製造できる半導体装置となっている。

【図面の簡単な説明】

#### [0065]

- 【図1】本発明の半導体装置の一例で、半導体装置100の模式的な断面図である。

- 【図2】図1の半導体装置100を等価回路で示したスイッチング回路の回路図で、一点鎖線で囲った部分が図1の半導体装置100に相当する。

- 【図3】多結晶シリコン抵抗体50による効果をシミュレーションにより見積もった結果で、(a)はシミュレーションの各設定パラメータを示す図であり、(b)は、LDMOS21のゲート入力抵抗Rgをそれぞれ3 ,30 とした場合のドレイン電圧Vdの立ち上り特性を示す図である。

- 【図4】本発明における別の半導体装置の例で、半導体装置101の模式的な断面図である。

- 【図5】別の半導体装置の例で、(a)は、半導体装置102の模式的な断面図である。また、(b)は、半導体装置102のチップ全体を示した模式的な平面図で、一点鎖線A-Aでの断面が、(a)に相当する。

- 【図6】(a),(b)は、ドレイン電圧 V d を多結晶シリコン抵抗体 5 0 に印加する別の構成を有した半導体装置の例で、それぞれ、半導体装置 1 0 3 , 1 0 4 の模式的な断面図である。

- 【図7】別構成の多結晶シリコン抵抗体を有する半導体装置の例で、(a)は、半導体装置105の模式的な断面図である。また、(b)は、(a)の一点鎖線Bで囲った部分を

10

20

30

40

拡大した模式的な断面図であり、(c)は、(a)の二点鎖線Cで囲った部分を拡大した 模式的な上面図である。

- 【図8】多結晶シリコン抵抗体とLDMOSのゲート電極が一体的に形成されてなる半導体装置の例で、半導体装置106の模式的な断面図である。

- 【図9】多結晶シリコン抵抗体とLDMOSのゲート電極が一体的に形成されてなる半導体装置の例で、半導体装置107の模式的な断面図である。

- 【図10】多結晶シリコン抵抗体とLDMOSのゲート電極が一体的に形成されてなる半導体装置の例で、半導体装置108の模式的な断面図である。

- 【図11】特許文献1に開示ざれた半導体装置で、半導体装置80の模式的な断面図である。

- 【図12】特許文献2に開示ざれた半導体装置で、半導体装置90の模式的な斜視図において、要部を部分的に断面で示した図である。

- 【図13】MOSトランジスタの新規な駆動回路を用いたスイッチング回路の一例で、破線で囲った部分が、電界効果型のトランジスタ20(n型MOSトランジスタ)を駆動するための駆動回路K10である。

## 【符号の説明】

- [0066]

- 80,90,100~108 半導体装置

- 10 半導体基板

- 21,21a,23 横型MOSトランジスタ(LDMOS)

- 11,13 ゲート電極

- 11a シリサイド層

- 6,6a ドリフト領域

- 50,51,53,54 多結晶シリコン抵抗体

- 4 LOCOS酸化膜

- 4 a 絶縁膜

- 15 層間絶縁膜

- 16 配線層

- 17 側壁酸化膜

- 18 多結晶シリコン

20

10

# 【図1】

# 【図3】

(a)

【図2】

(b)

【図4】

【図5】

# 【図6】

# 【図7】

【図8】

【図10】

【図9】

【図11】

# 【図12】

# 【図13】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L

21/336

(2006.01)

H 0 1 L

27/08

1 0 2 B

H 0 1 L

29/786

(2006.01)

H 0 1 L

27/04

P

H 0 1 L 27/088 (2006.01)

(72)発明者 中野 敬志

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 樋口 安史

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 藤井 哲夫

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 服部 佳晋

愛知県愛知郡長久手町大字長湫字横道41番地の1 株式会社豊田中央研究所内

(72)発明者 桑原 誠

愛知県愛知郡長久手町大字長湫字横道41番地の1 株式会社豊田中央研究所内

# 審査官 宇多川 勉

(56)参考文献 特開平11-234104(JP,A)

特開平07-066405(JP,A)

特開平02-128475(JP,A)

特開平05-235722(JP,A)

特開2008-054280(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/8234

H01L 21/336

H01L 21/822

H01L 27/04

H01L 27/06

H01L 27/088

H01L 29/78

H01L 29/786