# (19)**日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号 特許第7170724号 (P7170724)

(45)発行日 令和4年11月14日(2022.11.14)

(24)登録日 令和4年11月4日(2022.11.4)

| (51)国際特許分類 |       | FΙ        |         |       |       |  |

|------------|-------|-----------|---------|-------|-------|--|

| G 1 1 C    | 16/26 | (2006.01) | G 1 1 C | 16/26 | 1 3 0 |  |

| G 1 1 C    | 16/04 | (2006.01) | G 1 1 C | 16/04 | 1 8 0 |  |

| G 1 1 C    | 16/24 | (2006.01) | G 1 1 C | 16/24 | 1 1 0 |  |

請求項の数 20 (全30頁)

| (04)山岡辛口     | #± MT 2020 F20F24 (D2020 F20F24) | /フつ\#±=/r+午-#× | 540400005           |

|--------------|----------------------------------|----------------|---------------------|

| (21)出願番号     | 特願2020-526521(P2020-526521)      | (73)特許権者       | 518109985           |

| (86)(22)出願日  | 平成30年11月16日(2018.11.16)          |                | サンライズ メモリー コーポレイション |

| (65)公表番号     | 特表2021-503683(P2021-503683       |                | アメリカ合衆国カリフォルニア州945  |

|              | A)                               |                | 38・フレモント・レイクビュー ブー  |

| (43)公表日      | 令和3年2月12日(2021.2.12)             |                | ルバード 46831          |

| (86)国際出願番号   | PCT/US2018/061495                | (74)代理人        | 110001379           |

| (87)国際公開番号   | WO2019/099811                    |                | 特許業務法人 大島特許事務所      |

| (87)国際公開日    | 令和1年5月23日(2019.5.23)             | (72)発明者        | チェルニア、ラウル エイドリアン    |

| 審査請求日        | 令和3年8月20日(2021.8.20)             |                | アメリカ合衆国カリフォルニア州950  |

| (31)優先権主張番号  | 62/588,109                       |                | 54・サンタ クララ・アグニュー ロー |

| (32)優先日      | 平成29年11月17日(2017.11.17)          |                | F 889               |

| (33)優先権主張国・均 | 也域又は機関                           | 審査官            | 後藤 彰                |

|              | 米国(US)                           |                |                     |

| (31)優先権主張番号  | 16/193,292                       |                |                     |

| (32)優先日      | 平成30年11月16日(2018.11.16)          |                |                     |

|              | 最終頁に続く                           |                | 最終頁に続く              |

### (54) 【発明の名称】 フローティングソースメモリ構造体の検出方法

## (57)【特許請求の範囲】

#### 【請求項1】

共通ソース線と共通ビット線を共有し、かつ、薄膜ストレージトランジスタのゲート電極として機能する導体であるワード線に関連付けられた前記薄膜ストレージトランジスタのメモリストリングにおいて、予め第1の電圧範囲または第2の電圧範囲のいずれかの範囲内のしきい値電圧を有するよう構成された選択された前記薄膜ストレージトランジスタの1つを読み出す方法であって、

容量結合技術を用いて前記共通ソース線と前記共通ビット線との間に電圧差を生じさせるステップと、

選択された前記薄膜ストレージトランジスタ<u>の前記しきい値電圧が前記第1の電圧範囲または前記第2の電圧範囲であるか否かに応じて</u>導電状態または非導電状態にするように選択される読み出し電圧を<u>選</u>択された前記薄膜ストレージトランジスタの前記ゲート電極に印加するステップと、

選択された前記薄膜ストレージトランジスタの電流を検出することにより、選択された前記薄膜ストレージトランジスタが導電状態であるか非導電状態であるかを決定するステップとを含む方法。

### 【請求項2】

前記容量結合技術が、前記共通ビット線および前記共通ソース線を所定の電圧に初期化するステップと、

前記共通ソース線と前記共通ソース線の周辺にある前記導体との間の電位を変化させる

ことにより、前記電圧差を生じさせるステップとを含む、請求項1に記載の方法。

### 【請求項3】

前記共通ソース線の周辺の前記導体は、前記メモリストリング内の、選択された前記薄 膜ストレージトランジスタ以外の薄膜ストレージトランジスタに関連付けられたワード線 を構成する、請求項2に記載の方法。

#### 【請求項4】

前記所定の電圧が、電源電圧と他の基準電圧との範囲内にある、請求項2に記載の方法。

### 【請求項5】

前記共通ソース線は、前記共通ビット線および前記共通ソース線を前記所定の電圧に初 期化するための電流経路が有効である場合を除き、前記電源電圧または前記基準電圧のソ - スから電気的に絶縁されている、請求項4に記載の方法。

#### 【請求項6】

前記読み出し電圧を印加する前に、前記電流経路を無効にするステップを含む、請求項 5に記載の方法。

#### 【請求項7】

前記共通ソース線は、前記共通ビット線を前記共通ソース線に電気的に接続する選択装 置または回路によって、前記所定の電圧に初期化されるステップを含む、請求項3に記載 の方法。

### 【請求項8】

前記所定の電圧は、実質的に電源電圧または他の基準電圧である、請求項2に記載の方 法。

#### 【請求項9】

選択された前記薄膜ストレージトランジスタの前記電流を検出した後、前記しきい値電 圧が前記第1の電圧範囲にあるか前記第2の電圧範囲にあるかを決定するステップをさら に含む、請求項1に記載の方法。

#### 【請求項10】

前記共通ビット線上の前記電圧が判別レベルを超えるか否かを決定するステップをさら に含む、請求項8に記載の方法。

## 【請求項11】

前記判別レベルが、前記電源電圧以下のPMOSしきい値電圧である、請求項10に記 載の方法。

# 【請求項12】

前記読み出し電圧が前記ワード線に印加された後の所定時間内に、前記共通ビット線上 の電圧が判別レベルを超えるか否かを決定するステップをさらに含む、請求項8に記載の 方法。

## 【請求項13】

検出された前記電流は、前記共通ソース線に流入または流出する電流を検出することに より推測されるステップを含む、請求項1に記載の方法。

## 【請求項14】

(i)前記メモリストリングである第1のメモリストリングが前記第1のメモリストリ ングと実質的に同じように構成された薄膜ストレージトランジスタの第2のメモリストリ ングと関連付けられるステップと、

( ii) 前記第2のメモリストリングの前記共通ソース線が、前記第1のメモリストリ ングの前記共通ソース線と電気的に結合されるステップと、

( iii) 前記第1のメモリストリングの前記共通ビット線が、前記第2のメモリスト リングの前記共通ビット線から電気的に絶縁されるステップとを含む、請求項1に記載の 方法。

# 【請求項15】

前記電圧差は、少なくとも部分的には、前記第2のメモリストリング内の前記薄膜スト レージトランジスタに関連付けられた前記ワード線上の電位を変化させることによって生 10

20

30

じる、請求項14に記載の方法。

#### 【請求項16】

前記電流がオペアンプで検出されるステップを含む、請求項1に記載の方法。

#### 【請求項17】

前記電流が差動アンプで検出されるステップを含む、請求項1に記載の方法。

#### 【請求項18】

前記電流が所定のレベルに達する前、かつ、前記共通ビット線上の電圧が判別点を超えたことを検出した後に、前記電流を検出するステップを含む、請求項1に記載の方法。

#### 【請求項19】

所定の電圧が実質的に電源電圧からNMOSトランジスタしきい値電圧を差し引いた電圧である、請求項1に記載の方法。

#### 【請求項20】

選択装置が、前記電流を検出する前に、検出回路の入力端子を一方向導通モードの前記 共通ビット線に接続するステップを含む、請求項19に記載の方法。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、NOR型メモリストリングとして構成された、メモリセルの3次元の不揮発性メモリ構造体に関する。より詳細には、本発明は、各メモリセルが、直接アクセス可能なドレイン電極と、直接アクセス可能ではないフローティングソース電極との間に接続されている、メモリセルの構造からのデータの読み出しに関する。

### 【背景技術】

# [0002]

不揮発性メモリセル群は、多くの場合、外部からアクセス可能な2つの電気ノード(「電極」)間で直列(NAND)または並列(NOR)に接続される。ダイナミックランダムアクセスメモリ(DRAM)セルとは対照的に、不揮発性メモリセルは、データ取得のためにアクセスした後、または電源を切った後も、保存された情報を保持する。典型的な不揮発性メモリセルでは、データは、例えば、ファウラーノルドハイムトンネリングによって作成される絶縁された電荷トラップ層に注入された電荷の形で記憶される。記憶された情報は、通常、測定可能な電流の流れまたは測定可能な電圧レベルの変化のいずれかに基づく非破壊的な方法を用いて取得される。測定結果は、一般的に「センスアンプ」によってデジタル情報として提供される。電流の流れを利用する方法は「電流検出法(電流センシング)」、電圧を変化させる方法は「電圧検出法(電圧センシング)」と呼ばれる。このような観点から、センスアンプとして、電流検出法の場合はデジタル電流計、電圧検出の場合はデジタル電圧計が用いられる。

## [0003]

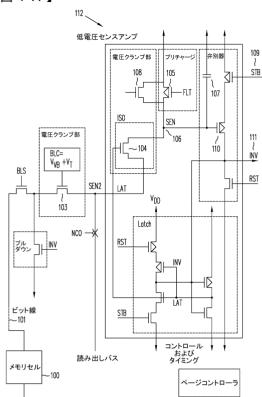

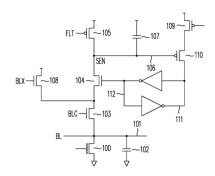

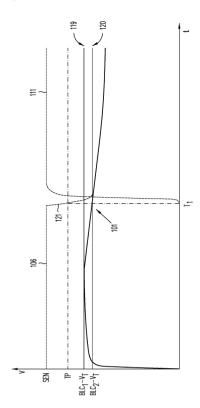

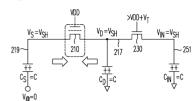

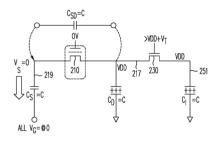

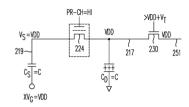

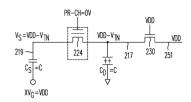

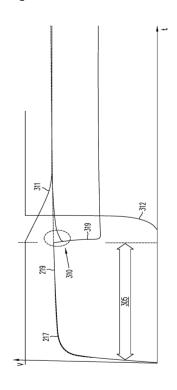

図1Aは、米国特許第7,046,568号明細書に記載されている電流検出および電圧検出のいずれも可能なセンスアンプ回路を示す。図1Bは、図1Aのセンスアンプ回路をもとに、電流検出モードで動作する簡略化したセンスアンプ回路を示す図である。図1Aおよび図1Bに示すように、メモリセル100は、寄生容量(図1Bの寄生ビット線コンデンサ102に代表される)の負荷が大きいビット線(BL)101とグランド基準との間に接続されている。NMOSトランジスタ103、104は、メモリセル100を時間に依存しないドレイン電圧にバイアスするようにカスコード構成で接続されており、これにより、ノード106における電位(信号SEN)に依存せず、メモリセル100内の電流を一定に保つことができる。

## [0004]

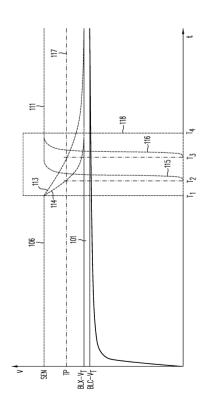

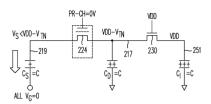

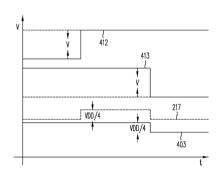

図1Cは、図1Bの電流検出動作における各種信号の電圧波形を示す図である。図1Bおよび図1Cに示すように、ノード106は、レベルセンシティブ型であるPMOS初期化トランジスタ110が非導電状態となるように、PMOS初期化トランジスタ105によって電源電圧VDDに初期化され、ビット線101は電圧BLC・V<sub>T</sub>に保持される。

10

20

30

40

ここで、電圧 B L C は N M O S トランジスタ 1 0 3 のゲート電極の電圧であり  $V_T$  は N M O S トランジスタ 1 0 3 のしきい値電圧である。コンデンサ 1 0 7 は J ード 1 0 6 と電源電圧 V D D との間に接続されており、寄生ビット線コンデンサ 1 0 2 に対して相対的に小さい容量を有する専用コンデンサ (すなわち、寄生コンデンサではなく、明示的に提供されるコンデンサ)であってもよい。時刻  $T_1$ において、P M O S 初期化トランジスタ 1 0 5 はオフになり、メモリセル 1 0 0 は、その導電状態に応じて、コンデンサ 1 0 7 を放電してもよいし、放電しなくてもよい。メモリセル 1 0 0 が導電状態でない場合、J ード 1 0 6 は電荷を失うことなく、電源電圧 V D D のままであるため、P M O S 初期化トランジスタ 1 1 0 は非導電状態である。この場合、結合されたインバータの一方の出力電極 1 1 は、グランド基準のままである。しかし、メモリセル 1 0 0 が導電状態であれば、J ード 1 0 6 上の電圧は低下する。時刻  $T_2$ で、J ード 1 0 6 の電圧が「トリップポイント」(T P)レベル 1 1 7 を下回ると、P M O S 初期化トランジスタ 1 1 0 が導通し、出力電極 1 1 1 を駆動して電源電圧 V D D を供給する。

## [0005]

コンデンサ107は、ノイズフィルタとしての役割と、セル電流評価装置としての役割 (時間積分による)の2つの役割を果たす。メモリセル内の一定の電流は、図1Cに示されるように、異なるセル電流は、ノード106の電圧が異なる波形113、114を有する結果となり、波形114によって示されるより急な勾配は、より高い放電電流に対応する。出力電極111の電圧は、ノード106上の電圧がTPレベル117を越えると、波形115および116(それぞれ波形113および114に対応する)で示されるように、論理状態が変化する。TPレベル117は、PMOS初期化トランジスタ110のしきい値電圧に対応する。

### [0006]

図1Bにおいて、追加のトランジスタ108は、そのゲート電極にNMOSトランジスタ103の電圧BLCよりも高い電圧BLXを有し、そのドレイン電極に電源電圧VDDを供給する。トランジスタ108は、NMOSトランジスタ103のドレイン電極の電圧を維持する。これは、ノード106の電圧が低下すると、NMOSトランジスタ103のドレイン電極がビット線101の電圧BLC・VTよりも高い電圧BLX・VTに保持されるため、ビット線101の電圧をBLC・VTで一定に保つことができるからである。T1とT4の間の期間にまたがる放電時間窓118は、電源電圧VDDとTPレベル117との間のノード106における放電直線性を提供するように、電流検出動作に先立って較正される。TPレベル117以下では、全体的な回路応答により、直線性が失われる場合がある。回路応答には、PMOS初期化トランジスタ110が導電状態となり、NMOSトランジスタ103のドレイン電極の電圧が精度に影響を与えずにBLX・VTに保持されることが含まれる。この図1Bおよび図1Cの動作は、電流検出動作の一種に過ぎないことを示している。あるいは、セル電流をミラーリングして既知の基準と比較することにより、セル電流を評価することもできる。

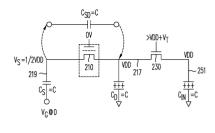

# [0007]

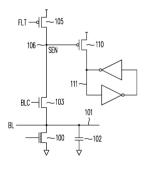

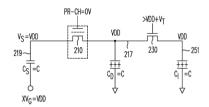

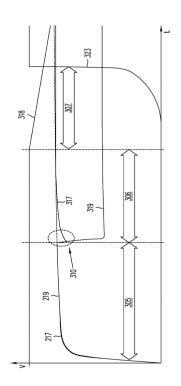

図1Dは、図1Aのセンスアンプ回路をベースに、電圧検出モードで動作する簡略化されたセンスアンプ回路を示す図である。図1Eは、図1Dの電圧検出動作における各種信号の電圧波形を示す図である。図1Dに示すように、NMOSトランジスタ103は、そのゲート電極が電圧BLC1にある状態で、ビット線101(寄生ビット線コンデンサ102によって示される容量性ノード)をグランドから電圧BLC1・VT(図1Eの波形119によって示されるように)までプリチャージする。そして、NMOSトランジスタ103のゲート電極の電圧を電圧BLC2・VT(波形120で示される)まで下げることにより、ビット線101をノード106から切り離す。時刻T1において、読み出し電圧がメモリセル100に印加される。符号化された状態に応じて、メモリセル100を活性化すると、ビット線101を放電してもよいし、放電しなくてもよい。ビット線101における放電率は、寄生ビット線コンデンサ102が上述したコンデンサ107よりも数桁大きい可能性があるため、上述した「電流検出」動作と比較して著しく低い(例えば、数

10

20

30

40

桁)可能性がある。電流検出とは異なり、電圧検出動作では、専用のコンデンサ 107 を必要としない。図1 Eに示すように、ビット線 101 の電圧が 101 の電圧が 101 と 1

[00008]

メモリセル100のソース電極が接地されていない場合には、メモリセル100がグランドへのアクティブプルダウンとして機能することができなくなるため、電流検出方法および電圧検出方法のいずれも使用することができない。センスアンプの容量性入力端子に中間回路を介して判別点を横切ることを強制できるようなグランドへの電流の流れはない。

【発明の概要】 【発明が解決しようとする課題】

[0009]

本発明の一実施形態は、メモリセルのストリング群から選択されたメモリセルより記憶された情報を取得する方法である。その実施形態では、ストリング内のすべてのメモリセルは共通のビット線を共有し、一部のメモリセルは共通のソース線に関連付けられ、他のメモリセルはそれぞれ他の共通のソース線に関連付けられている。メモリストリング内の各メモリセルは、異なるワード線に関連付けられている。この方法は、(a)メモリセルの共通ビット線および関連する共通ソース線を、電源電圧とグランドとの間の所定の電圧で初期化するステップと、(b)共通ビット線、関連する共通ソース線、またはその両方を所定の電圧から偏位させることによって、関連する共通ソース線と共通ビット線との間の電圧分離を行うステップと、(c)関連するワード線上で、メモリセルを、メモリセルに記憶された情報に対応する導電状態に置くための読み出し電圧を提供するステップと、および(d)電流検出回路を使用し、関連するワード線上での読み出し電圧の結果として関連する共通ソース線への電荷の流れを検出することに基づいて、導電状態を決定するステップとを含む。

【図面の簡単な説明】

[0010]

本発明は、添付の図面と併せて、以下の詳細な説明を検討するとよりよく理解される。

[0011]

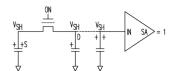

【図1A】電流検出動作と電圧検出動作の両方が可能なセンスアンプ回路を示す図である。

【図1B】図1Aのセンスアンプ回路をベースに、電流検出モードで動作する簡略化されたセンスアンプ回路を示す図である。

【図1C】図1Bの電流検出動作における各種信号の電圧波形を示す図である。

【図1D】図1Aのセンスアンプ回路をベースに、電圧検出モードで動作する簡略化されたセンスアンプ回路を示す図である。

【図1E】図1Dの電圧検出動作における各種信号の電圧波形を示す図である。

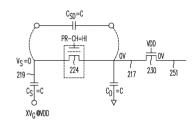

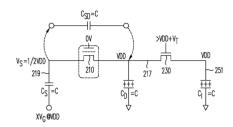

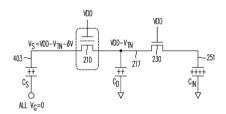

【図2A】本発明の一実施形態による電荷検出の原理を示す図である。

【図2B】本発明の一実施形態によるメモリセルの導電状態を評価するために電荷検出の原理の適用を示す図である。

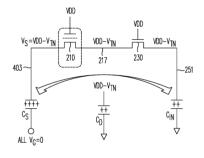

【図3A】本発明の一実施形態による、センスアンプ回路を使用して非導電状態のメモリセル上の電荷共有の評価を示す図である。

【図3B】本発明の一実施形態による、センスアンプ回路を使用して導電状態にあるメモリセルの電荷共有の評価を示す図である。

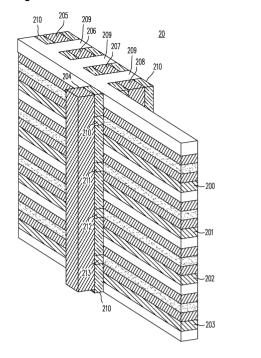

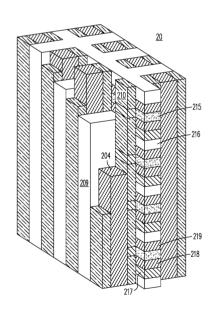

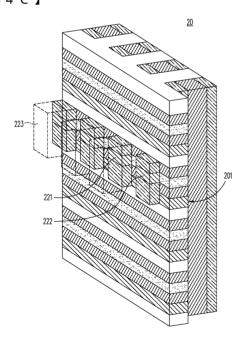

【図4A】本発明の一実施形態による3次元不揮発性メモリ構造体20を異なる観点から示す図である。

【図4B】本発明の一実施形態による3次元不揮発性メモリ構造体20を異なる観点から示す図である。

【図4C】本発明の一実施形態による3次元不揮発性メモリ構造体20を異なる観点から 示す図である。 10

20

30

40

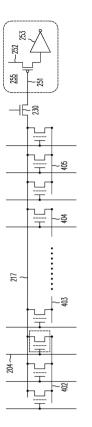

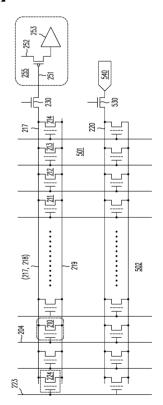

【図5】本発明の一実施形態による、センスアンプ255を共有する2つのアクティブストリップによって形成されたNORストリング501および501内のメモリセルの概略回路を示す図である。

【図6】本発明の一実施形態による寄生コンデンサが示されたNORストリング501を示す図である。

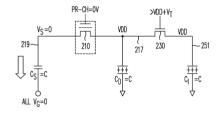

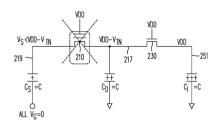

【図7A】NMOS選択トランジスタ(ストリング選択トランジスタ) 2 3 0 によってセンスアンプ 2 5 5 に直結されたNORストリング 5 0 1 のメモリセルの導電状態を決定するための条件を準備するプリチャージセル 2 2 4 を示す図である。

【図7B】本発明の一実施形態による、「プログラム済」(すなわち、非導電状態)メモリセルおよび「消去済」(すなわち、導電状態)メモリセルの読み出しをそれぞれ示す図である。

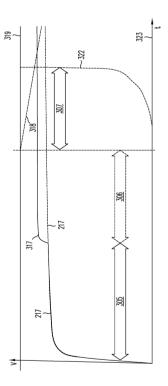

【図7C】本発明の一実施形態による、「プログラム済」(すなわち、非導電状態)メモリセルおよび「消去済」(すなわち、導電状態)メモリセルの読み出しをそれぞれ示す図である。

【図7D】本発明の一実施形態による、ドレイン電極217とソース電極219との間の寄生容量を考慮した、図7Bおよび図7Cの読み出しメモリセル210を示す図である。

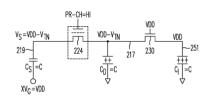

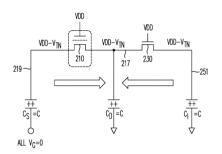

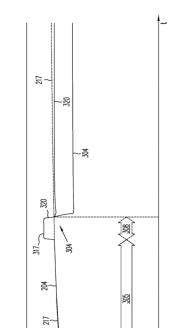

【図8A】本発明の一実施形態による、電源電圧VDDに設定したワード線に結合したソース電極219を有するNORストリング501内のメモリセルの導電状態を決定するための条件を準備するプリチャージセル(トランジスタ)224を示す図である。

【図8B】本発明の一実施形態による、結合したワード線電圧を変化させる技術を使用して、「プログラム済」(すなわち、非導電状態)メモリセル210の読み出しを示す図である。

【図8C】本発明の一実施形態による、結合したワード線電圧を変化させる技術を使用して、「プログラム済」(すなわち、非導電状態)メモリセル210の読み出しを示す図である。

【図9】フローティングノード301を入力電極(ノード300)および接地にそれぞれ 結合するコンデンサC0およびC1を示す図である。

【図10A】図9のモデルのさらなる改良を示す図である。

【 図 1 0 B 】 図 1 0 A のモデルのノード 3 0 1 、 3 0 2 および 3 0 3 における例示的な波形を示す図である。

【図11A】図10A~図10Bのモデルにおける動作原理を使用した直接接続データ検出のための別の方法を示す図である。

【図11B】図10A~図10Bのモデルにおける動作原理を使用した直接接続データ検出のための別の方法を示す図である。

【図11C】図10A~図10Bのモデルにおける動作原理を使用した直接接続データ検出のための別の方法を示す図である。

【図12A】ドレイン電極217とセンスアンプの入力電極251との間の「ダイオード類似」接続を使用したストレージトランジスタ(メモリセル)210のデータ検出を示す図である。

【図12B】ドレイン電極217とセンスアンプの入力電極251との間の「ダイオード類似」接続を使用したストレージトランジスタ(メモリセル)210のデータ検出を示す図である。

【図12C】ドレイン電極217とセンスアンプの入力電極251との間の「ダイオード類似」接続を使用したストレージトランジスタ(メモリセル)210のデータ検出を示す図である。

【図12D】ドレイン電極217とセンスアンプの入力電極251との間の「ダイオード類似」接続を使用したストレージトランジスタ(メモリセル)210のデータ検出を示す図である。

【図12E】ドレイン電極217とセンスアンプの入力電極251との間の「ダイオード類似」接続を使用したストレージトランジスタ(メモリセル)210のデータ検出を示す

10

20

30

40

図である。

【図13A】図12Aから図12Eの方法による非導電状態の(すなわち、プログラム済)メモリセル上の動作を示す図である。

【図13B】図12Aから図12Eの方法による非導電状態の(すなわち、プログラム済)メモリセル上の動作を示す図である。

【図13C】図12Aから図12Eの方法による非導電状態の(すなわち、プログラム済)メモリセル上の動作を示す図である。

【図14】ロングメモリストリングにおけるサブスレッショルドリーク効果を緩和するために、共通のソース線をセグメント(例えば、ソースセグメント402、403、404 および405)に分割することを示す図である。

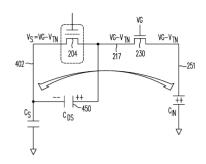

【図15A】上述の図12A~図12Eに示したダイオード類似接続に基づいて適切なセグメントサイズを決定するための方法を示す図である。

【図15B】上述の図12A~図12Eに示したダイオード類似接続に基づいて適切なセグメントサイズを決定するための方法を示す図である。

【図15C】ドレイン 接地容量を無視した場合のドレイン ソース容量(すなわち、コンデンサ450)を考慮した場合を示す図である。

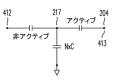

【図16A】ドレイン電極217が、(i)アクティブソースセグメントに関連するワード線を表すノード412および(ii)非アクティブソースセグメントのすべてに関連するワード線を表すノード413に容量結合されているモデルを示す図である。

【図16B】ソース電極が2つのセグメントに分割されている場合について、ドレイン電極217がアクティブセグメントおよび非アクティブセグメントにそれぞれ結合された図16Aのモデルの一部を示す図である。

【図16C】ソース電極が2つのセグメントに分割されている場合について、ドレイン電極217がアクティブセグメントおよび非アクティブセグメントにそれぞれ結合された図16Aのモデルの一部を示す図である。

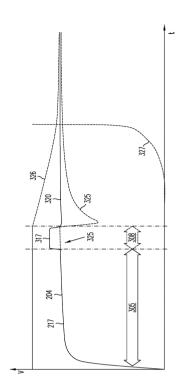

【図16D】図16A~図16Cのモデルにおけるソースセグメント412、413、ドレイン電極217および部分ドレイン電極403における電圧波形を示す図である。

【図17】ドレイン電極217からソース電極219を分離した後、ドレイン電極217 に電圧の「昇圧(ステップアップ)」ステップを設けた場合の効果を示す図である。

【図18】ドレイン電極217からソース電極219を分離した後、ドレイン電極217 において、図17の昇圧電圧ではなく、正パルスを印加した場合の効果を示す図である。

【図19】ソース電極の分割を利用して、様々なワード線ベースの容量結合ステップが実行されるセンシングシーケンス中のドレイン電極、分割されたソース電極およびセンスアンプの入力電極における信号の波形を示す図である。

【図20】垂直に隣接する2つのNORストリング501、502の間の寄生容量を使用した、フローティング共通ソース線の1つに結合された電圧ステップまたはパルスの誘導を示す図である。

【発明を実施するための形態】

#### [0012]

絶縁系では、システム内部にトラップされた電荷は、検出動作の下で保存される。例えば、グランドノードに接続されていないメモリセルでは、電圧検出時にメモリセル内の電荷を 「 0 」に放電することができず、また、電流検出時に一定の電流を供給して測定することができない。本発明は、このようなメモリセルの電荷共有の原理に基づく「電荷検出」方法を提供するものである。

### [0013]

本発明の電荷検出方法は、例えば、2016年7月26日に出願された「Multi-Gate NOR Flash Thin-film Transistor Strings Arranged in Stacked Horizontal Active Strips with-Vertical Control Gates」なる標題の米国特許出願第15/220,375号明細書(非仮出願I)および、2017年8月26日

10

20

30

40

に出願された「Capacitive - Coupled Non - Volatile Thin - Film Transistor Strings in Three - Dimensional Arrays」なる標題の米国特許出願第15/248,420号明細書(非仮出願II)に開示されているNORストリング内のメモリセルの検出に適用可能であってもよい。これらの各実施例において、本発明の方法は、メモリセルのフローティングドレイン電極を介してアクセスされるメモリセルのフローティングソース電極とセンスアンプのフローティング入力電極との間の電荷共有動作の結果を評価するために使用されてもよい。メモリセルの導電状態は、メモリセルのソース電極とセンスアンプの入力電極との間の電圧バランスの判定結果から決定される。メモリセルの導電状態が非導電状態の場合、ノード間の電位は等しくならない。そうでなければ、メモリセルの導電状態が導通状態である場合、ノード間の電位は等しくなる。

#### [0014]

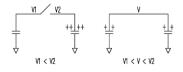

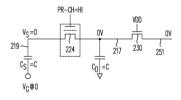

図 2 Aに示すように、 2 つの異なる電圧  $V_1$  および  $V_2$  に初期化された 2 つのコンデンサは、フローティングプレートが接続されていない限り、そのフローティングプレート上の電圧を保持する。これらのコンデンサの容量と電圧に応じて、これらのコンデンサはまた、 2 つの異なる量の電荷を蓄積する。しかし、接続した場合、 2 つのコンデンサに保持されている電荷量は、それぞれの接続前の電荷量の合計のままであるが、それぞれのプレート間の電圧は  $V_1$  と  $V_2$  の間の電圧に等しくなる。

### [0015]

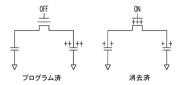

図2 B は、本発明の一実施形態による、メモリセルの導電状態を評価するために電荷検出の原理の適用を説明する図である。図2 B に示すように、非導電状態(「プログラム済」)では、メモリセルのゲート電極に読み出し電圧を印加すると、そのドレイン電極とソース電極に異なる電圧が維持される。一方、導電状態(「消去済」)では、ゲート電極に読み出し電圧を印加することで、ドレイン電極とソース電極の電圧が等しくなり、蓄積された電荷量が再配分される。

## [0016]

本発明の方法の下での電荷共有は、図3Aおよび3Bに図示されているように、メモリ セルのノードの1つをセンスアンプ回路に接続することによって評価されてもよい。図3 A に示すように、ソース電極 S とドレイン電極 D を有するメモリセルは、メモリセルのド レイン電極 D を介してセンスアンプSAの入力電極INに接続されている。3つの容量性 ノードであるS、D、INは、それぞれ電圧V $_{S}$ 、V $_{D}$ 、V $_{I}$  $_{N}$ で、例えば電圧V $_{S}$ が電圧 VェNよりも低い状態で電源ノードによって初期化される。これらの容量性ノードは、充 電され、その後、それぞれの電源ノードから分離される。例えば、ソース電極Sは、電圧 源に直接接続することはできないが、ドレイン電極Dに結合された導電状態のセルを介し て充電することができる。図3Aに示すように、容量性ノードであるS、D、INの電圧 は、メモリセルが非導通状態(「オフ」または「プログラム済」)にある場合、無期限に (寄生リークを無視して)維持されてもよい。反対に、メモリセルが導通状態(「オン」 または「消去済」)にある場合、図3Bに示すように、センスアンプのソース電極S、ド レイン電極D、および入力電極INは、共通の共通電圧VSHに収束する。ソース電極S の初期電圧Vsは、センスアンプの入力電極INの電圧VTNよりも低いため、共通電圧V  $_{SH}$ は $V_{S}$ と $V_{IN}$ の中間にある(つまり $V_{SH}$  <  $V_{SH}$  <  $V_{IN}$  ) 。そして、センスアンプ 回路は、アナログ電圧の小振幅が判別値を超えるとVェNからVSHへのアナログ電圧の小 振幅をフルCMOSデジタル電圧振幅に変換する。

#### [0017]

図4A~図4Cは、本発明の一実施形態による3次元不揮発性メモリ構造体20の様々な態様を示す(3次元不揮発性メモリ構造体20は、例えば、上記の非仮出願Iおよび非仮出願IIに開示されているように、NORストリングの配列を提供する)。図4Aに示されるように、メモリ構造体20は、アクティブストリップの堆積を含む。図4Aでは、参照符号200、201、202および203の隣接する各対の間に、半導体および誘電体材料の細長い層から形成されたアクティブストリップがある。堆積されたアクティブス

10

20

30

40

20

30

40

50

トリップのいずれかの側には、図4Aで参照符号204、205、206、207および208によって示される垂直なローカルワード線が提供され、各ワード線は、誘電体材料の垂直な列(例えば、誘電体列209)によって、堆積が同じ側の別のワード線から分離されている。各ローカルワード線と各アクティブストリップとの重なり部分(例えば、211、212または213)は、メモリセルまたはストレージトランジスタが形成される位置である。

#### [0018]

記憶材料の特殊な層、例えば電荷トラッピング層210は、電荷を捕獲することを可能 にする。蓄積情報は、電荷の有無などの電荷の捕獲量を1ビット単位のセルケースで表し 、電荷の量の異なる電荷を複数ビット単位のセルケースでそれぞれ異なる蓄積値を表して いる。図4Bに示すように、各アクティブストリップは、半導体層215と誘電体層21 6とを含み、半導体層215は、導電性半導体層218と219との間に設けられている 。導電性半導体層218および219は、例えば、N<sup>+</sup>ポリシリコンであってもよい。図 4 B では、抵抗を低減するために、導電性半導体層 2 1 8 に隣接する追加の導電性層 2 1 7 ( 例えば、金属 ) を設けてもよい。この例では、導電性層 ( 金属層 ) 2 1 7 とその隣接 する導電性半導体層218の組み合わせは、関連するメモリセルに共通ドレイン電極を提 供し、導電性半導体層219は、関連するメモリセルに共通ソース電極を提供する。各共 通ドレイン電極は、3次元不揮発性メモリ構造体20の外部の1以上の回路に電気的に接 続され、共通ソース電極は、3次元不揮発性メモリ構造体20の外部の回路から絶縁され ている。半導体層215は、メモリセルのためのフローティング基板を提供する。半導体 層  $2 \ 1 \ 5$  は、例えば、 $P^{-}$ ポリシリコン層であってもよい。同じアクティブストリップ内 の2つ以上のメモリセル(例えば、図4Cのメモリセル221、222および223)は 、共通のドレイン電極を共有している。同様に、同じアクティブストリップ内の2つ以上 のメモリセル(例えば、図4Cのメモリセル221、222および223)は、共通ソー ス電極を共有する。同じアクティブストリップに沿ったメモリセルは、1以上のNORス トリングを形成する。

### [0019]

電荷トラッピング層 2 1 0 は、浅い P ポリシリコン基板層(半導体層) 2 1 5 の表面で、導電性半導体層 2 1 8 と 2 1 9 (両方とも N <sup>+</sup>型ポリシリコン)間の伝導を可能にする(「チャネル形成」)正電荷を蓄積することができる。しかし、電荷トラッピング層 2 1 0 における負の電荷の蓄積は、チャネルの形成を妨げ、それによって導電性半導体層 2 1 8 および 2 1 9 を分離した状態に保つ。

## [0020]

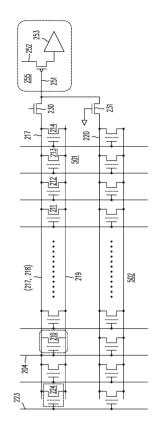

図5は、本発明の一実施形態による、センスアンプ255を共有する2つのアクティブストリップ内の2つのNORストリング501、502内のメモリセルの概略回路を示す。図5に示すように、NORストリング501のビット線または共通ドレイン電極217(図4Bでは金属層217およびN<sup>+</sup>ポリシリコン層(導電性半導体層)218を表す)は、NMOS選択トランジスタ230によってセンスアンプ255に接続されている。NORストリング502の共通ドレイン電極220は、そのゲート電極が接地される(すなわち、非選択される)ように、図5に示されているNMOS選択トランジスタ231によってセンスアンプから絶縁されている。メモリセル、例えばメモリセル210、211、212、213、214は、共通ドレイン電極217と共通ソース電極219との間にNOR構成で並列に接続され、NORストリング501を形成する。NORストリング内の各メモリセルは、その関連ワード線によって個別に選択され、活性化されてもよい。例えば、NORストリング501において、ワード線204は、メモリセル210を選択して活性化する。メモリセル210の導電状態を決定するために、NORストリング501における導通を防止する。

#### [0021]

図5において、ワード線223は、図示されたNORストリング501、502の各々

において、その関連するメモリセル(例えば、メモリセル224)を活性化するために提供された結果、共通ドレイン電極と共通ソース電極との間の電圧を等しくする。ワード線223に関連付けられたメモリセル(「プリチャージセル」)は、典型的には「消去済」の導電状態にあり、各関連付けられたNORストリングのドレイン電極およびソース電極上の電圧を意図的に等しくする「プリチャージ段階」の間、一時的に活性化される。

### [0022]

図6は、本発明の一実施形態による、寄生コンデンサが明示的に示されているNORストリング501を示す。図6に示すように、寄生コンデンサ250は、ドレイン電極217とソース電極219との間に存在する寄生容量を表している。また、図6には、(a)ドレイン電極217とNORストリング501に関連付けられたワード線(例えばワード線204)との間に存在する寄生容量を表す寄生コンデンサ241~248と、(b)ソース電極219とNORストリング501に関連付けられたワード線(例えばワード線204)との間に存在する寄生容量を表す寄生コンデンサ261~268とが示されている。図6において、寄生コンデンサ240は、ワード線が接地されている場合のワード線とレイン電極217との間の寄生容量(例えば、寄生コンデンサ241~248)の全ての和を表している。同様に、寄生コンデンサ260は、ワード線が接地されている場合のワード線とソース電極219との間のすべての寄生容量(例えば、寄生コンデンサ261~268)の和を表す。寄生コンデンサ225は、センスアンプ255の入力電極とグランドとの間の寄生容量を表す。

#### [0023]

NORストリング501に沿ったメモリセルは、電気的に絶縁された電荷トラップ層において、もしくはそこから電荷を捕獲または除去することにより、情報を記憶および消去する。電荷は、トンネリング(例えば、ファウラーノルドハイムトンネリング)または別の好適なプロセスを介して、電荷トラップ層に注入されるか、または電荷トラップ層から除去される。電荷は、NORストリングに電力が供給されていない期間中であっても、電荷トラップ層内に長時間存在していてもよい。センスアンプ255は、制御された条件下でメモリセルの導電状態を検出することによって間接的に決定されるので、電荷トラップ層に取り込まれた電荷の量を顕著に変化させることなく、関連するNORストリング内のメモリセルの導電状態を決定する。

### [0024]

本発明のNORストリング(例えば、NORストリング501)のメモリセルは、その共通ソース電極がNORストリングの外部の回路から直接アクセスできない点で、従来の不揮発性NOR型メモリセルと大きく異なる。従って、メモリセルの導電状態を判定するための従来の電流検出方法や電圧検出方法は適用できない。例えば、従来の「電流検出法」では、導電状態のメモリセルの電流を比較的一定にする必要があり、従来はドレイン電極の電圧を実質的に一定に保ち、ソース電極を接地することで実現してきた。本発明のNORストリングでは、メモリセルの電荷共有を伝導により可能にすると、ソース電極の電圧とメモリセルの電流が連続的に変化するため、一定のメモリセル電流を満たすことができない。同様に、本発明のNORストリングでは、導電状態のメモリセルではメモリセルのドレイン電極の電圧をグランドの状態にすることができないため、「電圧検出」の方法は機能しない。

#### [0025]

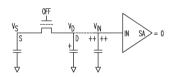

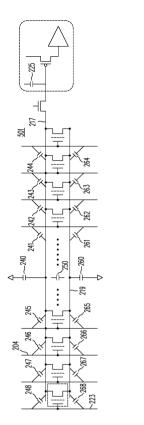

図7Aは、活性化されたNMOS選択トランジスタ230によってセンスアンプ255に直接接続されたNORストリング501のメモリセルの読み出し(すなわち、導電状態の決定)のための条件を準備するプリチャージセル224を示す。この構成では、外部回路からアクセス可能なドレイン電極217がグランドに初期化され、NORストリング501に関連付けられた全てのワード線も接地される。その後、プリチャージセル224が活性化されてソース電極219とドレイン電極217とが接続され、これにより、センスアンプ255の入力電極もNMOS選択トランジスタ230を介してグランドに放電される。プリチャージセル224のゲート電極は、後にオフ状態(すなわち、0ボルト)に設

10

20

30

40

定され、これにより、ソース電極 2 1 9 をドレイン電極 2 1 7 から分離する。そして、N M O S 選択トランジスタ 2 3 0 のゲート電極に少なくとも( V D D + V  $_T$  )である電圧を提供することにより、センスアンプ 2 5 5 の入力電極およびドレイン電極 2 1 7 へ電源電圧 V D D がもたらされるが、ここで V V は N M O S 選択トランジスタ V 2 3 0 のしきい値電圧である。この時点で、N O R ストリング 5 0 1 内の任意のメモリセル(例えば、メモリセル V 2 1 0 )を読み出しのために選択してもよい。

#### [0026]

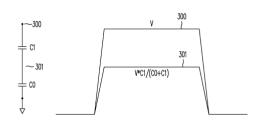

図7 B および7 C は、本発明の一実施形態による、「プログラム済」(すなわち、非導 電状態)メモリセルおよび「消去済」(すなわち、導電状態)メモリセルの読み出しをそ れぞれ示している。図7Bに示すように、読み出されるメモリセル(すなわち、メモリセ ル210)のワード線上に読み出し電圧が印加されると、メモリセル210が非導電状態 であるか、または「プログラム済」であるので、ドレイン電極217とソース電極219 との間に電荷の共有は起こらない。あるいは、図7Cに示すように、メモリセル210が 「消去済」になると、メモリセル210は導通し、それにより、メモリセル210のソー ス電極およびドレイン電極とセンスアンプ255の入力電極との間で電荷を共有すること が可能になる。例えば、メモリセル210のドレインおよびソース電極の接地に対する静 電容量とセンスアンプ255の入力電極のグランドに対する静電容量とが等しい場合、電 荷共有から生じる最終的な電圧はVsн=2/3VDDである。適切に設計されたセンス アンプでは、理想的には、その入力電極の電圧スイングは、センスアンプの出力状態の変 化を確実に提供するのに十分な1/3VDD(この場合のように)である。図7Bおよび 7 C の例は、ソース電極 2 1 9 とドレイン電極 2 1 7 との間の寄生容量を考慮していない 。図7Dは、本発明の一実施形態による、ドレイン電極217とソース電極219との間 の寄生容量を考慮した、図7Bおよび7Cの読み出しメモリセル210の例を示す。

#### [0027]

ソース電極219とドレイン電極217との間の寄生容量Cが他のノードの寄生容量のそれぞれと等しい場合、NMOS選択トランジスタ230の活性化によりドレイン電極217を電源電圧VDDにして、フローティングソース電極219を電圧1/2VDDにしてもよい。その場合、読み出し動作中の電荷共有により、共通電圧VSH=5/6VDDとなり、図7Cに示した場合の1/3VDDに比べて、センスアンプ255の入力電極の電圧スイングを1/6VDDに低減することができる。また、センスアンプ255の入力電極の電圧スイングを1/6VDDに低減することができる。また、センスアンプ255の入力電極251における寄生容量が、ドレイン電極217及びソース電極219における寄生容量に対して無視できるほど小さい場合には、センスアンプ255の入力電極251における電圧スイングは1/4VDDに改善される。この2つのケースの間では、「直接接続」アプローチでは十分なマージンが得られない可能性がある。また、NMOS選択トランジスタ230のゲート電極を電源電圧VDD以上にするためのバイアスをかけるには、内部でチャージポンプを必要とするため、消費電力が増大し、アクセス信号が遅くなる。

#### [0028]

センスアンプ255の入力電極251の電圧を電荷共有交換の判別レベルを越えて変化させるために、NORストリング501の共通ソース電極219は、十分なプルダウンウェイト(すなわち、少なくともドレイン電極217とセンスアンプ255の入力電極251の合計容量に匹敵する寄生容量)を提供しなければならない。ソース電極219とドレイン電極217の容量が等しいと仮定すると(単純化するために、センスアンプ255の入力電極251における寄生容量を無視する)、ソース電極219とドレイン電極217との間の電圧分離は、トリップポイント電圧スイングの少なくとも2倍であることが望ましい。

#### [0029]

ソース電極 2 1 9 がセンスアンプ 2 5 5 の入力電極 2 5 1 に接続された結果、ドレイン電極 2 1 7 が上昇した電圧にされた後に、ソース電極 2 1 9 とドレイン電極 2 1 7 との間に十分な電圧分離を提供する 1 つの方法は、ワード線を使用してソース電極 2 1 9 の電圧を引き下げるようにすることである。図 8 A は、本発明の一実施形態に従って、ソース電

10

20

30

40

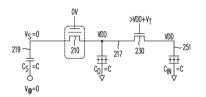

極219が、電源電圧VDDに設定された所定数のワード線に結合された状態で、NORストリング501内のメモリセルの導電状態を決定するための条件を準備するプリチャージセル224を示している。図7Aと同様に、図8Aの構成では、ドレイン電極217はグランドに初期化されている。ただし、図7Aの構成とは異なり、ソース電極219に結合された所定数のワード線は、電源電圧VDDに設定されている。次いで、プリチャージセル224は、ソース電極219およびドレイン電極217の電圧を等しくするために活性化され、それによってセンスアンプ255の入力電極251もまた、NMOS選択トランジスタ230を介してグランドに放電される。そして、プリチャージセル224のゲート電極は、ソース電極219とドレイン電極217とを分離するために、負論理状態(例えば、0ボルト)に設定される。

# [0030]

図8 B および8 C は、本発明の一実施形態による、結合されたワード線電圧の変化を使用する技術を使用して、「プログラム済」(すなわち、非導電状態)メモリセル2 1 0 の読み出しを示している。図8 B に示すように、ソース電極2 1 9 がドレイン電極2 1 7 から分離された後(図8 A と併せて上述したように)、NMOS選択トランジスタ2 3 0 のゲート電極の電圧は、電源電圧 V D D + のそのしきい値電圧 V T よりも大きくなるように上昇し、その結果、センスアンプ2 5 5 のドレイン電極2 1 7 および入力電極2 5 1 の両方が電源電圧 V D D まで引き上げられる。ドレイン電極2 1 7 とソース電極2 1 9 との間に寄生容量があるため、図7 D と併せて上述したように、ソース電極2 1 9 を電圧1 / 2 V D D まで同時に引き上げてもよい。その後電源電圧 V D D に設定されたソース電極2 1 9 に結合されたワード線は、図8 C に示されるように、接地される。これらのワード線の接地は、十分な数のワード線がこのステップダウン(降圧)技術に関与している場合には、ソース電極2 1 9 をグランド(すなわち、0 V)に戻すか、またはそれよりも低い値にする。

# [0031]

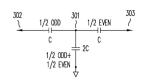

本発明は、半導体層への実質上均一な容量性結合を使用して、様々な形状および振幅のワード線信号を作り出すことにより、フローティングノード301を入力電極(設定するためのアプローチを提供する。図9は、フローティングノード301を入力電極(でこれを例示的に示す。フローティングノード301は、例えば、共通のソース電極(例えば、図8Bのソース電極219)として機能するフローティング半導体層を表してもよい。コンデンサC1は、フローティングノード301のある数の接地されたワード線への結合を表してもよく、ノード300は、作成された波形を受信するワード線の残りの部分を表してもよい。図9に示すように、ノード300で受信されたパルスは、ノード300で受信されたパルスの振幅の分数CR(「結合比」)である電圧の変化をフローティングノード301で誘導する。具体的には、結合比CRは、CR=C1/(C0+C1)で与えられる。

# [0032]

図10Aは、図9のモデルをさらに改良したものである。全てのODDワード線の半分の電圧がノード302の電圧で表される場合を考える。この電圧は、寄生容量 C によってフローティングノード301(例えば、図8Aのソース電極219)にされる。グランドに設定されているすべてのODDワード線の残りの半分もまた、フローティングノード301に同じ寄生容量 C によって比較的高い精度で結合されている。同様に、ノード303で表される全EVENワード線の半分の電圧は、フローティングノード301にも寄生容量 C にされており、残りのEVENワード線の電圧はグランドに設定されている。接地されたODDおよびEVENワード線の寄生容量は、接地された寄生容量結合フローティングノード301の総寄生容量を2Cにする。各ノード302、303のそれ自体は、フローティングノード301に対する結合比が1/4である。したがって、図10Bでは、ノード302におけるVDD振幅の昇圧信号は、フローティングノード301における対応する1/4のVDD振幅の初期値以上の昇圧をもたらす。初期状態では、ノード303

10

20

30

40

VDDで安定している(したがって、「ACグランド」として機能する)。ノード303のVDDからグランドへの降圧は、1/4VDDの振幅の降圧としてフローティングノード301になされ、フローティングノード301をノード302によって誘発される電圧の昇圧の前の初期値に戻す。結合された信号の振幅および形状は、所定の入力信号に適切な数のワード線を設定し、DCまたはACグランドに適切な数のワード線を設定することによって制御することができる。

#### [0033]

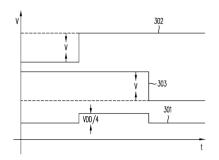

図10Aおよび図10Bによって示される原理は、直接接続データ検出の別の方法を提供する。はじめに、図11Aを参照すると、ドレイン電極217およびソース電極219は、所定数のローカルワード線を電源電圧VDDに設定した後、プリチャージセル(トランジスタ)224をオンすることにより、HIGH(すなわち、電源電圧VDD時)に初期化される(そのゲート電極が、そのしきい値電圧と電源電圧VDDの和よりも大き電で圧VDDに設定する)。次に、プリチャージセル(トランジスタ)224をオフにしてに設定されているストリング選択トランジスタ230は、ドレイン電極217を電で、ドレイン電極217をソース電極219から絶縁する(図11B)(このデータ検出をではレイン電極217をソース電極219から絶縁する(図11B)(このデータ検出を準備するためのシーケンスは、ドレイン電極217およびソース電極219が0Vに初期化されている図8A、8Bおよび8Cによって示されるものとは異なる)。さらに、図11Cに示すように、ソース電極219は、電源電圧VDDにあったワード線をグランドに降圧することにより、都合の良い電圧になされる。この方法は、図8A~図8Cに関連して上述したLOW初期化セットアップ手順の別の手段を提供する。

### [0034]

あるいは、センスアンプ255のドレイン電極217とセンスアンプ255の入力電極 251は、図12Aに図示されているような「ダイオード類似」接続を介して、高バイア ス(すなわち、電源電圧VDD)で所定の数のワード線と接続されてもよい。図12Aに 示すように、プリチャージセル(トランジスタ)224が導通状態にある時は、ストリン グ選択トランジスタ230のゲート電極の電圧が電源電圧VDDに設定されているため、 ソース電極 2 1 9 およびドレイン電極 2 1 7 、およびそれらの寄生容量の両方が電圧 V D D-VTN(すなわち、電源電圧VDDからストリング選択トランジスタ230のしきい 値電圧を差し引いた電圧)にもたらされる。この方法では、上述した図11A~図11C の方法とは異なり、ストリング選択トランジスタ230のゲート電極に電源電圧VDDよ りも大きな電圧を必要としないため、電圧の発生および管理の課題が簡素化される。この 方法では、ドレイン電極217およびソース電極219は、センスアンプ255のトリッ プポイントVDD-VTP以下の電圧VDD-VTNに初期化される。この例では、ストリ ング選択トランジスタ230のゲート端子の電圧は電源電圧VDDであるが、電源電圧V DDとグランドとの間のソース電極 2 1 9 およびドレイン電極 2 1 7 におけるプリチャー ジ電圧を達成するために、電源電圧VDDよりも低い電圧がストリング選択トランジスタ 2 3 0 のゲート端子で使用されてもよい。この高度な一方向性のタイプの接続では、電源 電圧VDDとグランドとの間の電圧は、ドレイン電極217上で非常に長い時間にわたっ て実質的に維持されることがある。

## [0035]

次に、プリチャージセル(トランジスタ) 2 2 4 をオフにすることにより、ソース電極 2 1 9 を分離する(図 1 2 B)。上述のように、高バイアスのソース電極 2 1 9 は、結合 されたワード線の一部または全部を電源電圧 V D D D からグランドに降圧することによって 結合されることがある。この動作に関連するワード線の数に応じて、図 1 2 C に示される ように、任意の所望のソース電極の電圧 V s を設定することができる。メモリセル 2 1 0 がプログラム済状態(すなわち、非導電状態)にある場合、そのゲート電極に印加された 読み出し電圧(例えば、電源電圧 V D D D のままであるように、ドレイン電極 2 1 7 およびソース電極 2 1 9 の電圧の変化を もたらさないであろう(図 1 2 D)。この場合、センスアンプ 2 5 5 の出力電極では論理 状態の変化は生じない。この場合、センスアンプ 2 5 5 の出力値は、L O W ( すなわち、

10

20

30

40

グランド時)となるように設計されていてもよい。しかしながら、メモリセル 2 1 0 が消去済状態(すなわち、導電状態)にある場合、そのゲート電極に読み出し電圧を設定すると、ソース電極 2 1 9、ドレイン電極 2 1 7 およびセンスアンプ 2 5 5 の入力電極 2 5 1 (図 1 2 E) の間で電荷共有が発生し、センスアンプ 2 5 5 の入力電極 2 5 1 で電圧スイングが生じる。後述する特定の条件の下では、電荷共有から生じる最終的な電圧は VDD - VTN またはそれ以下になることがある。先に指摘したように VDD - VTN 電圧レベルはセンスアンプのトリップポイント VDD - VTP 以下であるため、センスアンプ 2 5 5 の出力電極はロジック VTD 1 (すなわち電源電圧 VDD ) にトリップする。

#### [0036]

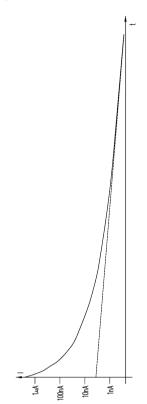

図12A~図12Eの方法による非導電状態の(すなわち、プログラム済)メモリセル のための検出動作を、図13A~図13Cの信号波形に関してさらに説明する。図13A に示すように、ダイオード類似接続では、初期等化ステップ(図12A~図12C)が時 間間隔305にわたって実行され、その間、ドレイン電極217およびソース電極219 の両方が電圧VDD-VTNに可能な限り近づけられる。そして、プリチャージセル(ト ランジスタ)224をオフにすると、ソース電極219はドレイン電極217から分離さ れ、ドレイン電極217はセンスアンプ255の入力電極251に接続されたままとなる 。現在フローティングしているソース電極219は、その後、初期化ステップにおいて高 電圧に保持された所定数の結合ワード線をグランド電圧にすることにより、ダウン結合さ れる。図13Aに示すように、ソース電極219における電圧波形は、波形319によっ て、この降圧ステップを示している。ドレイン電極217もワード線での電圧降圧により 結合されているが、グリッチ310は、ドレイン電極217がセンスアンプ255の入力 電極251に接続されていることにより妨害が低減されていることを示している。しかし 、グリッチ310のタイミングでセンスアンプ255の入力電極251がデータ評価のた めに解放されると、グリッチ310の影響と波形311で示されるセンスアンプ255の 入力電極251のリーク電流は、読み出されるメモリセルが非導電状態であるにもかかわ らず、センスアンプの出力状態のスプリアス変化(波形312)を引き起こす可能性があ る(すなわち、読み出される動作中に電荷共有がない)。

### [0037]

センスアンプ255における誤った出力論理状態の変化を回避するために、グリッチ310後のドレイン電極217が電圧  $VDD-V_{TN}$ に戻るように回復時間が必要である。この回復時間は、図13Bに図示されている。図13Bに示すように、回復時間間隔306の終了時に、センスアンプ255の入力電極251がメモリセルの検出を可能にするために解放されると、時間間隔307が経過した後(非導通またはプログラム済メモリセルが読み出される場合)になって初めて、センスアンプ255の入力電極251(波形318)のリーク電流によって、センスアンプ255の出力状態のフリップが引き起こされる。この場合、センスアンプの出力状態のスプリアス変化のトリガは、ドレイン電極217における充電電流である。(ただし、出力状態の変化は、やはり疑似信号であることに注意)。図13Cは、さらに $VDD-V_{TH}$ まで充電されたコンデンサの電流が減少していく様子を対数で示し、検出遅延の重要性を示している。図13Cに示すように、充電電流は、ある程度の時間が経過すると、線形に見えるように漸近的に減少する。

#### [0038]

図13Cの充電電流は対数目盛で示されているため、このほぼ直線的な減少は、ドレイン電極217の電圧が電圧VDD・VTHに向かって漸近的に増加し、等間隔で一定の電圧利得が得られることを意味する。回復時間間隔が不足すると、センスアンプの出力状態が早くトリップしすぎてしまう(図13A)。回復時間間隔が長く、充電電流が小さいほど、疑似出力状態変化は時間的にさらに押し出される。言い換えれば、スプリアス信号は、遅かれ早かれ発生する。スプリアス信号が早く発生する場合は、グリッチ310に起因する(図13A)。また、十分な回復時間間隔が許容されている場合は、スプリアス信号は遅く発生する(図13B)。

# [0039]

10

20

30

20

30

40

50

図13Aおよび図13Bは、回復時間間隔が、ドレイン電極217のダウン結合のグリッチ310によって引き起こされる疑似信号の機会を減少させることができるが、データ検出は、選択されていないメモリセル内の高い累積サブスレッショルドリーク電流に対して依然として脆弱である可能性があることを示している。ソース電極219が切り離されてデータ検出を開始した直後に電流のリークが始まるので、長い回復時間間隔を取ったとしても、リーク電流による誤った出力状態変化が引き起こされる。このように、メモリセルのリーク電流が大きい場合には、回復時間間隔は偽似トリガを防止できない可能性がある。

#### [0040]

以下の図14~図19は、図13Aおよび13Bによって示されるように、図12A~図12Eの方法の欠点を克服する改良を示す。ある点までは、メモリストリング内のビット線を選択して駆動する回路は、より長いメモリストリングでスケールアップする必要がないため、より長いメモリストリングをチップ面積の優位性として提供することができる。しかし、メモリストリングが長くなると、共通ソース電極とドレイン電極の充放電に長い時間が必要となり、また、単にメモリセルの数が多いために、より大きなサブスレッショルドリーク電流が必要となる。図13Aおよび図13Bの例では、メモリセルのリーク電流が大きいほど、疑似検出信号が早く現れる。この影響を緩和するために、導電層であるソース電極をセグメントに分割してもよい。図14は、ソース層(例えば、図12Aのソース電極219)をソースセグメント402、403、404および405に分割したものである。共通ソース層をセグメント化することは、2017年6月20日に出願された「3 DimensionalNOR Strings with SegmentedShared Source Regions」なる標題の米国仮特許出願第62/522,665号明細書に開示されている。

#### [0041]

ソースのセグメント化はリーク電流を減少させるが、ソース電極のプルダウン強度も低下させる。このように、適切なセグメントの大きさは、センスアンプ255の入力電極251の入力容量に対するセグメントの総容量の比率に依存する。図15Aおよび15Bは、上述の図12A~図12Eに示されたダイオード接続アプローチに基づいて適切なセグメントサイズを決定するための方法を例示する。図15Aに示すように、全ての結合ワード線を降圧した後、ソースセグメント403は電圧Vs=VDD・VTHN・ Vでフローティング状態となり、ドレイン電極217はゲート電極が電源電圧VDDに設定されたストリング選択トランジスタ230によりVDD・VTNに充電され、次に、センスアンプの入力電極251を電源電圧VDDから切断することにより、全てのノードをフローティングする。メモリセル210がプログラム済であるか消去済であるかにかかわらず、電荷は保存される。導通状態(すなわち、消去済状態)では、センスアンプのソースセグメント403、ドレイン電極217、および入力電極251上の電圧は、3つの容量の合計に対する総電荷の比率によって決定される共通値に向かって収束する。この最終値は、ノードが接続されている順序に依存しない。

### [0042]

次に、どの程度のセグメント化が許容されるかを判断する一つの方法について説明する。同電位の2つのノード間には電流が流れないため、導電路が存在しても、3つのコンデンサ(すなわち、ソース電極219、ドレイン電極217、センスアンプ255の入力電極251の寄生容量)は、理論的には全て同じ電圧「VDD-VTN」を保持していてもよい。図15Bは、ドレイン電極217が電圧VDD-VTNに充電され、ソースセグメント403とセンスアンプ255の入力電極251が電荷共有後に個別に同じ電圧VDD-VTNに到達する場合の一例を示している。すなわち、消去済のメモリセル204では、たまたま、センスアンプ255の入力電極251(すなわち、寄生容量 $C_{IN}$ )とソースセグメント403との間で共有される電荷量Q(すなわち、寄生容量 $C_{S}$ )がQ= V\* $C_{S}$ = $V_{TN}$ \* $C_{IN}$ であるとき、ドレイン電極217の電圧は変化しないが、ここで、Vは電荷共有前のドレイン電極217とソースセグメント403との間の電圧差であり

、 V<sub>TN</sub>は電荷共有前のドレイン電極 2 1 7 とセンスアンプ 2 5 5 の入力電極 2 5 1 との間の電圧差である。

### [0043]

したがって、 V=VTN\*CIN/CS、ここで、 Vがドレイン電極とソース電極と の間の初期電圧分離である場合、ドレイン電極217は、メモリセル204がプログラム 済か消去済かにかかわらず、その電圧を変化させず、センスアンプ255の入力電極25 1は、1)メモリセル204がプログラム済である場合(すなわち、非導通)には、変化 しないままであるか、または、2)メモリセル204が消去済である場合(すなわち、導 通している場合)にはVTNの電圧スイングを有するかのいずれかである。識別条件を定 義するために、メモリセルが導通しているときに、センスアンプが少なくともVTP(セ ンスアンプのトリップポイント)の入力電圧スイングを発生させるために、ドレイン電極 2 1 7 とソースセグメント 4 0 3 との間の初期電圧分離 Vは、 V> V T P \* C T N / C 5の関係を満たさなければならない。ソース層をセグメント化することは、アクセス時間 やリーク削減などの利点があるが、 V\*Cs=Vтр\*Стыの関係が満たされた後は、 それ以上のセグメント化は発生しない。上記の関係は、所与のセグメントサイズについて 、ドレイン電極217とソースセグメント403との間の電圧分離は、センスアンプの入 力電極における静電容量に関連しているが、ドレイン層の長さには依存しないことを示し ている。

### [0044]

図15Cは、ドレイン対グランド容量が無視される場合(すなわち、ドレイン対グランド容量は、 $C_{DS}$ またはソース対グランド容量( $C_{S}$ )のいずれかに対して無視できるものとみなされる場合)に、ドレイン対ソース容量(すなわち、コンデンサ450に代表される $C_{DS}$ )が考慮される場合を示している。読み出し電圧がメモリセル204上に配置される前に、電圧 $V_{DS}$ 0はソースセグメント402およびドレイン電極217を横断して維持される。ドレイン電極217における電圧 $V_{G}$ - $V_{TN}$ は、メモリセル204が非導電状態である場合、ストリング選択トランジスタ230のゲートにおける電圧 $V_{G}$ によって提供される「ダイオード類似」接続のために、非常に長い期間維持することができる。メモリセル204が導通しているとき、容量性ノード間の電荷共有が起こり、センスアンプ255の入力電極251における電圧が、ソース電極403における電圧を犠牲にして減少する結果となる。ドレイン電極217の電圧を $V_{G}$ - $V_{TN}$ で一定にしても $V_{DS}$ 0\* $C_{S}$ > $V_{TP}$ \* $C_{IN}$ であれば、センスアンプ255の入力電極251に少なくとも $V_{TP}$ のスイングを誘発することができる。

## [0045]

本発明者は、ダイオード類似の接続アプローチとセグメント化されたソース電極とを組み合わせることにより、検出が高速化されることを認めている。上述の図13Cと関連して論じたように、電圧VDD・VTNまで充電されたドレイン電極に対して、ソースセグメント上の電圧を V変化させるためにワード線結合を使用することは、ドレイン電極で望ましくない結合を誘発する可能性がある。しかしながら、そのような結合を防止することは、図13Aのグリッチ310を回避し、それ故に必要な回復時間間隔を提供しなければならないことを避けることができる。ドレイン電極の電圧に影響を与えることなくソースセグメントをダウン結合する方法が、それに応じて次に提示される。

#### [0046]

上述したメモリ構造体では、ドレイン電極217における電圧は、外部回路への接続によって初期化することができるが、共通フローティングソース電極219における電圧は、所望により、ドレイン電極217との均等化およびその後のローカルワード線からの容量結合によってのみ設定することができる。ドレイン電極217およびソース電極219は、連続的なソース層として提供されるか、またはソースセグメントとして提供されるかにかかわらず、ドレイン電極217およびソース電極219の両方において電圧変化を誘導するために使用されよいかなりの数のローカルワード線に結合される。メモリセル210を読み取る際には、上述したように、ソース電極219をドレイン電極217からの電

10

20

30

40

圧分離を介して活性化またはロードする必要がある。ソース電極 2 1 9 がソースセグメントである場合、他のすべてのソースセグメントは非アクティブのままであるべきであり、すなわち、各ソースセグメントとドレイン電極 2 1 7 との間には、リーク電流を低減するために電圧分離が存在してはならない。ワード線信号の結合を行う場合には、ドレイン電極 2 1 7 が妨害される可能性があるため、ドレイン回復時間間隔が必要となる。

# [0047]

ワード線の信号は、ドレイン層またはビット線に沿って任意の場所に適用された場合、 完全なドレイン層とワード線に関連付けられたソースセグメント(「アクティブソースセ グメント」)には印加されるが、他のソースセグメント(「非アクティブソースセグメン ト」)には印加されない。図16Aは、ドレイン電極217が、(i)アクティブソース セグメントに結合されたワード線を表すノード412、および(ii)非アクティブソー スセグメントに結合されたワード線を表すノード413に容量的に結合されたモデルを示 す。ソース層が2つのソースセグメントにセグメント化されている場合については、図1 6 B および図16C は、それぞれ、アクティブセグメントおよび非アクティブセグメント に結合されたドレイン電極217のための図16Aのモデルの一部を示している。非アク ティブソースセグメント412およびアクティブソースセグメント413による個々の容 量結合を示すために、ドレイン電極217への誘導電圧は、それぞれノード402および 403の電圧の和よって表される。図16A~図16Cのモデルにおける非アクティブソ ースセグメント412およびアクティブソースセグメント413、ドレイン電極217お よび部分ドレイン電極403における電圧波形をそれぞれ図16Dに示す。図16Dに示 すように、非アクティブソースセグメント412に関連付けられたワード線における昇圧 ワード線信号は、非アクティブソースセグメント412と共通ドレイン電極217の両方 に印加され、アクティブソースセグメント413に印加されない。その後、降圧ワード線 信号は、関連するアクティブソースセグメント413と共通ドレイン電極217の両方に 印加され、非アクティブソースセグメント412に印加されない。降圧信号では、共通ド レイン電極217の電圧は、初期値(すなわち、非アクティブソースセグメント412に おける昇圧前の値)に戻る。従って、ソース層がセグメント化され、ドレイン層がダイオ ード疑似接続(すなわち一方向性)でセンスアンプに接続されている限り、ドレイン電極 とソース電極に独立した電圧を誘導する技術を提供することができる。

#### [0048]

ダイオード疑似接続アプローチでは、センスアンプ255から見たドレイン層充電電流は、時間とともに漸近的に減少する(図13C参照)。スプリアス検出信号を回避するためには、上述したように回復時間間隔が必要である長いセットアップ時間を避けるための1つの方法は、正の「昇圧」ドレイン電圧を提供することであり、これはダイオード接続に逆バイアスをかけ、それによってセンスアンプ255の入力電極251からドレイン電極217への一方向の電流の流れを防ぐことができる。このような電圧上昇は、関連ワード線で実行される昇圧信号を介して容易に達成でき、正確に制御することができる。

# [0049]

図17は、ドレイン電極217からソース電極219を分離した後、ドレイン電極217に昇圧電圧を印加した場合の効果を説明するための図である。図17に示すように、ドレイン電極217とソース電極219が等化される時間間隔305の後、ドレイン電極217の電圧は、波形317で示される正の昇圧電圧で昇圧される。その結果、ストリング選択トランジスタ230を介したドレイン充電電流が実質的に停止する。昇圧電圧がなければ、ドレイン電極217は、回復時間間隔306にわたって(線分217の点線部分によって示される)連続的に充電し、その後、点線の波形318によって示されるように、リーク電流が発生する。その場合、時間間隔307の後、センスアンプの出力状態(波形322で示される)にスプリアス遷移が発生する可能性がある。しかし、波形317の昇圧電圧では、センスアンプ255の入力電極251(波形319)の電圧が高いままであるため、センスアンプの出力状態323の疑似遷移が引き起されることを防止することができる。

10

20

30

40

### [0050]

図18は、ドレイン電極217からアクティブソースセグメントを分離した後の、図17の昇圧電圧ではなく、ドレイン電極217における正のパルスの効果を示す図である。図18に示すように、時間間隔305の終了時の昇圧電圧に続く所定の時間間隔308の後、ワード線信号は、ドレイン電極217における電圧を波形320によって示される電圧レベルにダウン結合させる(すなわち、ドレイン電極217における電圧を電圧パルスの前の値に実質的に戻す)。時間間隔305の満了時には、ソース電極219はドレイン電極217から電気的に絶縁される。このときのソース電極219の電圧は、電圧レベル304で示されている。ストリング選択トランジスタ230のドレイン連結を横切る逆バイアスのため、時間間隔308の終了時に電圧が降圧されることによってドレイン電極217に望ましくないグリッチが誘発されることはない。ドレイン電極217での電圧降圧は、アクティブソースセグメントによる電圧降圧と同時に行われ、アクティブソースセグメントによる電圧降圧と同時に行われ、アクティブソースセグメントでの電圧を電圧レベル304にする。

#### [0051]

時間間隔308にわたるドレイン電極217における電圧パルスは、対応するワード線結合信号における電圧パルスによって達成されてもよい。従って、ワード線の電圧パルスが同じ電圧レベルから始まり、同じ電圧レベルに戻る限り、ドレイン電極217における誘起電圧パルスも同じ電圧レベルから始まり、同じ電圧レベルに戻るであろう。また、誘起パルスの振幅は、ドレイン電極217と対応するワード線との間の容量間の結合比に依存する。このように、関係しているワード線の数によってパルス振幅を制御することができる。異なる形状のパルス(例えば、波形で表した304および320の形状)は、すべての信号がドレイン電極を結合させる一方で、アクティブソースセグメントにおけるワード線信号のみがドレイン電極およびアクティブソースセグメントの両方を結合させるように、非アクティブソースセグメントに隣接するワード線に区分的信号を適用することによって作成することができる。

## [0052]

一方向接続のダイオード疑似接続のため、時間間隔308を過ぎないと検出は行われないが、時間間隔305の満了時の昇圧電圧の直後にセンスアンプの入力電極が解放され、 検出が可能になる場合がある。

#### [0053]

ソース電極 2 1 9 のみをダウン結合させ、ドレイン電極 2 1 7 をダウン結合させないデータ検出の方法は、ドレイン電極 2 1 7 での望ましくないグリッチを防止するため、回復時間間隔の負荷を回避する。また、関連するワード線の数を調整することにより、ドレイン電極 2 1 7 の電圧を微調整してもよい(例えば、開始時よりも若干高い電圧が生じるようにする)。ドレイン電極 2 1 7 におけるわずかに高い最終電圧は、小さな「昇圧」電圧に相当し、ドレイン充電電流を防止する。また、ソース電極 2 1 9 の電圧の(ドレイン電極 2 1 7 の電圧との相対的な)降圧は、アクティブソースセグメントに関連するワード線のみを関与させることが好ましく、それによってリーク電流を低減する。

### [0054]

ドレイン電圧パルスのもう一つの利点は、ソース / ドレイン分離が、リーク電流と潜在的なメモリセル伝導に同期することである。これは、ソース電極とドレイン電極の電圧分離の前にメモリセルを読み出す(すなわちオンにする)ことができ、これにより、より長いワード線 R C 遅延を打ち消すことができる。

### [0055]

図19は、ソース層におけるセグメント化を利用した、様々なワード線ベースの容量性結合ステップが実行される検出シーケンスの間のセンスアンプ255のドレイン電極217、セグメント化されたソース電極、および入力電極251における信号の波形を示す図である。図19に示すように、ドレイン電極217およびアクティブソースセグメントは、図12A~図12Cに図示されるような技法を用いて、アクティブソースセグメントのワード線のある数を電源電圧VDDに設定することによって、初めに両方とも電圧VDD

10

20

30

40

- V T N にもたらされる。次に、アクティブソースセグメントはドレイン電極 2 1 7 から 分離され、さらに、非アクティブソースセグメントに関連付けられた同じ数のワード線を 電源電圧VDDに上昇させ、それにより、アクティブソースセグメント(波形325)に おいて対応する電圧上昇なしにドレイン電極217において昇圧電圧(波形317)を提 供する。ドレイン電極217はすべてのソースセグメントに共通であるので、任意のソー スセグメントに沿った任意のワード線は、ドレイン電極217において電圧昇圧または電 圧降圧を誘発するために使用されてもよい。実際のところ、ドレイン電極217の電圧が 上昇すると、アクティブソースセグメントも同様にアップ結合するが、マイナスの影響は ない。最小遅延の後、アクティブソースセグメントに関連付けられたワード線は、電源電 圧VDDからグランドにリセットされ、ドレイン電極217を昇圧電圧の前の電圧に戻し (すなわち、波形320によって示される電圧レベルに戻る)、同時に、アクティブソー スセグメントには、アクティブソースセグメントとドレイン電極217との間の所望の電 圧分離を達成するための降圧電圧が提供される。アクティブソースセグメント上の電圧は 、波形325によって提供される。下方に移動するアクティブソースセグメントに関連付 けられたワード線の数は、昇圧電圧を生成するために上方に移動する非アクティブソース セグメントに関連付けられたワード線の数と等しいため、ドレイン電極217は、昇圧電 圧を生成する前の電圧レベルに戻る。しかし、アクティブソースセグメントは、アクティ ブソースセグメントに関連付けられたワード線の関連している数に応じてダウン結合する 。すべての非アクティブソースセグメントは、非アクティブソースセグメントからのリー ク電流を防止するために、好ましくはドレイン電極217に接続された状態に保たれる。

[0056]

電圧パルスの間は検出が可能であるが、センスアンプ255のドレイン電極207と入力電極251との間に電流が流れないように、ストリング選択トランジスタ230の逆バイアス連結により、センスアンプ255の出力状態は変化しない。また、パルスの立下リエッジの前には、ドレイン電極217とソース電極219との間の電圧分離のためのワード線が既に選択されている。アクティブソースセグメントに関連するワード線が低いレベルになると、データ検出が開始され、電圧分離とメモリセル電流があれば基本的に完全に同期して、早期リーク電流を発生させずに電荷を共有できるようになる。

[0057]

図20は、垂直に隣接する2つのNORストリング501、502の間の寄生容量を使用して、フローティング共通ソース線の1つに結合された電圧ステップまたはパルスの誘導を示す。図20において、NORストリング501のフローティング共通ソース線219は、垂直に隣接するNORストリング502の共通ビット線220に近接している。共通ビット線220は選択トランジスタ530を介して電気的にアクセス可能であるので、選択トランジスタ530を介して信号540を共通ビット線220上に印加することにより、結合されたステップまたはパルス信号をフローティング共通ソース線219上に誘導することができる。

[0058]

上記の詳細な説明は、本発明の特定の実施形態を例示するために提供されるものであり、限定することを意図したものではない。本発明の範囲内での多数の変形および修正が可能である。本発明は、以下の特許請求の範囲に記載されている。

10

20

30

【図面】

# 【図1B】

10

20

【図1C】

# 【図1D】

30

# 【図1E】

# 【図2A】

10

20

# 【図2B】

# 【図3A】

30

【図3B】

【図4A】

30

10

【図4B】

【図4C】

【図5】

【図6】

20

30

【図7A】

【図7B】

# 【図7C】

# 【図7D】

# 【図8A】

# 【図8B】

# 【図8C】

# 【図9】

30

10

20

# 【図10A】

# 【図10B】

10

# 【図11A】

# 【図11B】

20

# 【図11C】

# 【図12A】

30

# 【図12B】

# 【図12C】

# 【図12D】

# 【図12E】

20

10

# 【図13A】

# 【図13B】

30

【図13C】

【図14】

20

30

【図15A】

【図15B】

# 【図15C】

# 【図16A】

10

# 【図16B】

# 【図16C】

20

# 【図16D】

# 【図17】

30

【図18】

【図19】

10

【図20】

30

# フロントページの続き

# (33)優先権主張国・地域又は機関

米国(US)

(56)参考文献 特開平07-057482(JP,A)

特開2008-021781(JP,A)

米国特許出願公開第2017/0148517(US,A1)

特表2019-504479(JP,A)

(58)調査した分野 (Int.Cl., DB名)

G 1 1 C 1 6 / 2 6 G 1 1 C 1 6 / 0 4 G 1 1 C 1 6 / 2 4