# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

G11C 7/22 (2015.01) G11C 7/10 (2015.01)

(21) 출원번호

10-2014-0174449

(22) 출원일자

2014년12월05일

심사청구일자 없음

(11) 공개번호 10-2016-0069093 (43) 공개일자 2016년06월16일

(71) 출원인

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

이현배

경기 이천시 대월면 경충대로2050번길 70-50, 60 4동 1004호 (현대6차아파트)

(74) 대리인

김성남

전체 청구항 수 : 총 15 항

# (54) 발명의 명칭 클릭 데이터 리커버리 회로 및 이를 이용하는 시스템

# (57) 요 약

클럭 데이터 리커버리 회로는 위상 검출부, 필터링부, 위상 정보 합산부 및 위상 보간기를 포함한다. 상기 위상 검출부는 클럭 신호와 데이터를 비교하여 얼리 위상 감지 신호 및 레이트 위상 감지 신호를 생성한다. 상기 필터링부는 상기 얼리 위상 감지 신호의 생성 횟수와 상기 레이트 위상 감지 신호의 생성 횟수에 따라 업 신호 및 다운 신호를 생성한다. 상기 위상 정보 합산부는 상기 클럭 신호의 주기마다 상기 필터링부의 출력을 수신하고, 상기 클럭 신호의 주기의 n 배 (n은 2이상의 정수)에 해당하는 합산 시간 동안 상기 필터링부로부터 수신된 상기업 신호 및 상기 다운 신호의 개수를 합산하여 제 1 및 제 2 위상 제어 신호를 생성한다. 상기 위상 보간기는 상기 제 1 및 제 2 위상 제어 신호에 응답하여 상기 클럭 신호의 위상을 조절한다.

## 대 표 도 - 도2

2

# 명세서

# 청구범위

#### 청구항 1

클럭 신호와 데이터를 비교하여 얼리 위상 감지 신호 및 레이트 위상 감지 신호를 생성하는 위상 검출부;

상기 얼리 위상 감지 신호의 생성 횟수와 상기 레이트 위상 감지 신호의 생성 횟수에 따라 업 신호 및 다운 신호를 생성하는 필터링부;

상기 클럭 신호의 주기마다 상기 필터링부의 출력을 수신하고, 상기 클럭 신호의 주기의 n 배 (n은 2이상의 정수)에 해당하는 합산 시간 동안 상기 필터링부로부터 수신된 상기 업 신호 및 상기 다운 신호의 개수를 합산하여 제 1 및 제 2 위상 제어 신호를 생성하는 위상 정보 합산부; 및

상기 제 1 및 제 2 위상 제어 신호에 응답하여 상기 클럭 신호의 위상을 조절하는 위상 보간기를 포함하는 클럭 데이터 리커버리 회로.

# 청구항 2

제 1 항에 있어서,

상기 위상 검출부는 상기 클럭 신호의 분주 클럭 신호의 라이징 에지에서 상기 데이터의 레벨을 캐치하고, 캐치된 결과를 연산하여 상기 얼리 위상 감지 신호 및 상기 레이트 위상 감지 신호를 생성하는 클럭 데이터 리커버리 회로.

## 청구항 3

제 1 항에 있어서,

상기 필터링부는 상기 얼리 위상 감지 신호의 생성 횟수와 상기 레이트 위상 감지 신호의 생성 횟수의 차이가 소정 개수에 도달했을 때, 상기 업 신호 및 상기 다운 신호 중 하나를 생성하는 클럭 데이터 리커버리 회로.

## 청구항 4

제 1 항에 있어서,

상기 필터링부는 무빙 에버리지 필터인 클럭 데이터 리커버리 회로.

# 청구항 5

제 1 항에 있어서,

상기 위상 정보 합산부는 상기 합산 시간 동안 상기 필터링부로부터 출력된 상기 업 신호의 개수를 합산하여 상기 제 1 위상 제어 신호를 출력하는 업 신호 합산기; 및

상기 합산 시간 동안 상기 필터링부로부터 출력된 상기 다운 신호의 개수를 합산하여 상기 제 2 위상 제어 신호를 출력하는 다운 신호 합산기를 포함하는 클럭 데이터 리커버리 회로.

#### 청구항 6

제 5 항에 있어서,

상기 업 신호 합산기는 상기 클럭 신호의 주기마다 상기 업 신호의 출력 여부를 감지하고, 상기 합산 시간 동안 합산된 상기 업 신호의 개수를 복수 비트의 이진 코드로 출력하는 클럭 데이터 리커버리 회로.

# 청구항 7

제 5 항에 있어서,

상기 다운 신호 합산기는 상기 클럭 신호의 주기마다 상기 다운 신호의 출력 여부를 감지하고, 상기 합산 시간

동안 합산된 상기 다운 신호의 개수를 복수 비트의 이진 코드로 출력하는 클럭 데이터 리커버리 회로.

#### 청구항 8

제 1 클럭 신호와 데이터를 비교하여 얼리 위상 감지 신호 및 레이트 위상 감지 신호를 생성하는 위상 검출부;

상기 얼리 위상 감지 신호의 생성 횟수와 상기 레이트 위상 감지 신호의 생성 횟수에 따라 업 신호 및 다운 신호를 생성하는 필터링부;

상기 제 1 클럭 신호에 동기하여 상기 업 신호 및 상기 다운 신호의 생성 횟수를 합산하고, 합산된 결과를 제 2 클럭 신호에 동기하여 제 1 및 제 2 위상 제어 신호로서 출력하는 위상 정보 합산부; 및

상기 제 2 클럭 신호에 동기하여 업데이트될 때 상기 제 1 및 제 2 위상 제어 신호에 기초하여 상기 제 1 클럭 신호의 위상을 보정하는 위상 보간기를 포함하는 클럭 데이터 리커버리 회로.

# 청구항 9

제 8 항에 있어서,

상기 제 2 클럭 신호의 주기는 상기 제 1 클럭 신호의 주기의 n 배(n은 2 이상의 정수)인 클럭 데이터 리커버리 회로.

#### 청구항 10

제 8 항에 있어서,

상기 위상 검출부는 상기 제 1 클럭 신호의 분주 클럭 신호의 라이징 에지에서 상기 데이터의 레벨을 캐치하고, 캐치된 결과를 연산하여 상기 얼리 위상 감지 신호 및 상기 레이트 위상 감지 신호를 생성하는 클럭 데이터 리 커버리 회로.

#### 청구항 11

제 8 항에 있어서,

상기 필터링부는 상기 얼리 위상 감지 신호의 생성 횟수와 상기 레이트 위상 감지 신호의 생성 횟수의 차이가 소정 개수에 도달했을 때, 상기 업 신호 및 상기 다운 신호 중 하나를 생성하는 클럭 데이터 리커버리 회로.

# 청구항 12

제 8 항에 있어서,

상기 필터링부는 무빙 에버리지 필터인 클럭 데이터 리커버리 회로.

#### 청구항 13

제 8 항에 있어서,

상기 위상 정보 합산부는 상기 제 2 클럭 신호의 주기에 대응하는 시간 동안 상기 필터링부로부터 출력된 상기 업 신호의 개수를 합산하여 출력하는 업 신호 합산기; 및

상기 제 2 클럭 신호의 주기에 대응하는 시간 동안 상기 필터링부로부터 출력된 상기 다운 신호의 개수를 합산하여 출력하는 다운 신호 합산기를 포함하는 클럭 데이터 리커버리 회로.

#### 청구항 14

제 13 항에 있어서,

상기 업 신호 합산기는 상기 제 1 클럭 신호의 주기마다 상기 업 신호의 출력 여부를 감지하고, 상기 제 2 클럭 신호의 주기에 대응하는 동안 합산된 상기 업 신호의 개수를 복수 비트의 이진 코드로 출력하는 클럭 데이터 리 커버리 회로.

# 청구항 15

제 13 항에 있어서,

상기 다운 신호 합산기는 상기 제 1 클럭 신호의 주기마다 상기 다운 신호의 출력 여부를 감지하고, 상기 제 2 클럭 신호의 주기에 대응하는 시간 동안 합산된 상기 다운 신호의 개수를 복수 비트의 이진 코드로 출력하는 클럭 데이터 리커버리 회로.

# 발명의 설명

# 기술분야

[0001] 본 발명은 반도체 장치에 관한 것으로서, 더 상세하게는 클럭 데이터 리커버리 회로 및 이를 이용하는 시스템에 관한 것이다.

# 배경기술

- [0002] 일반적으로 적은 개수의 데이터 버스를 통해 직렬 데이터 통신을 하는 시스템은 클릭 데이터 리커버리 방식을 사용한다. 상기 클릭 데이터 리커버리 방식은 직렬 데이터로부터 기준이 되는 클릭 신호를 생성하고, 생성된 클릭 신호를 데이터를 수신하기 위한 스트로브 신호로 사용한다. 따라서, 전송 장치는 상기 클릭 신호와 관련된 정보를 갖는 데이터를 전송할 수 있고, 수신 장치는 상기 데이터로부터 클릭 신호를 생성한 후 생성된 클릭 신호에 동기하여 상기 전송 장치로부터 전송된 데이터를 수신할 수 있다.

- [0003] 노이즈와 지터 등에 의해 신호 왜곡을 최소화하고 데이터 유효 윈도우를 증가시키기 위해, 상기 수신 장치는 데이터로부터 생성된 클럭 신호의 위상과 데이터의 천이 시점을 비교하여 상기 클럭의 신호의 위상을 조절할 수있다.

# 발명의 내용

# 해결하려는 과제

[0004] 본 발명의 실시예는 클럭 신호의 위상 정보 획득은 짧은 주기로 수행되고, 상기 클럭 신호의 위상의 조절은 보다 긴 주기로 수행될 수 있는 클럭 데이터 리커버리 회로를 제공할 수 있다.

# 과제의 해결 수단

- [0005] 본 발명의 실시예에 따른 클럭 데이터 리커버리 회로는 클럭 신호와 데이터를 비교하여 얼리 위상 감지 신호 및 데이트 위상 감지 신호를 생성하는 위상 검출부; 상기 얼리 위상 감지 신호의 생성 횟수와 상기 레이트 위상 감지 신호의 생성 횟수에 따라 업 신호 및 다운 신호를 생성하는 필터링부; 상기 클럭 신호의 주기마다 상기 필터 링부의 출력을 수신하고, 상기 클럭 신호의 주기의 n 배 (n은 2이상의 정수)에 해당하는 합산 시간 동안 상기 필터링부로부터 수신된 상기 업 신호 및 상기 다운 신호의 개수를 합산하여 제 1 및 제 2 위상 제어 신호를 생성하는 위상 정보 합산부; 및 상기 제 1 및 제 2 위상 제어 신호에 응답하여 상기 클럭 신호의 위상을 조절하는 위상 보간기를 포함할 수 있다.

- [0006] 본 발명의 실시예에 따른 클럭 데이터 리커버리 회로는 제 1 클럭 신호와 데이터를 비교하여 얼리 위상 감지 신호 및 레이트 위상 감지 신호를 생성하는 위상 검출부; 상기 얼리 위상 감지 신호의 생성 횟수와 상기 레이트 위상 감지 신호의 생성 횟수에 따라 업 신호 및 다운 신호를 생성하는 필터링부; 상기 제 1 클럭 신호에 동기하여 상기 업 신호 및 상기 다운 신호의 생성 횟수를 합산하고, 합산된 결과를 제 2 클럭 신호에 동기하여 제 1 및 제 2 위상 제어 신호로서 출력하는 위상 정보 합산부; 및 상기 제 2 클럭 신호에 동기하여 업데이트될 때 상기 제 1 및 제 2 위상 제어 신호에 기초하여 상기 제 1 클럭 신호의 위상을 보정하는 위상 보간기를 포함할 수 있다.

#### 발명의 효과

[0007] 본 발명의 실시예는 수신되는 데이터의 신호 무결성을 향상시키면서 시스템의 전력 소모를 감소시킬 수 있다.

#### 도면의 간단한 설명

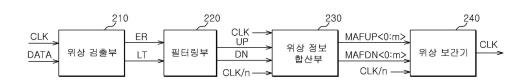

[0008] 도 1은 본 발명의 실시예에 따른 시스템의 구성을 보여주는 도면,

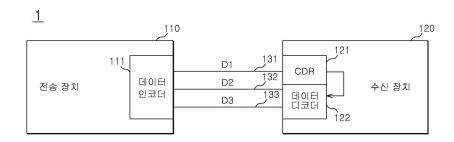

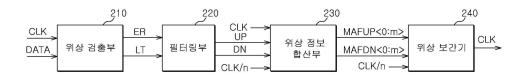

도 2는 본 발명의 실시예에 따른 클럭 데이터 리커버리 회로의 구성을 보여주는 도면,

도 3a 내지 3d는 도 2에 도시된 위상 검출부의 동작을 보여주는 타이밍도 및 테이블,

도 4는 도 2에 도시된 위상 정보 합산부의 개략적인 구성을 보여주는 블록도,

도 5는 도 4에 도시된 업 신호 합산기의 구성을 보여주는 도면,

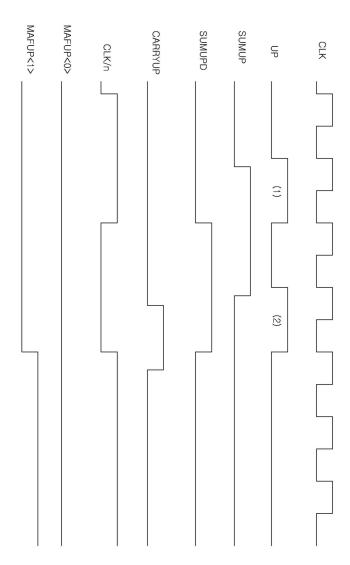

도 6은 도 5에 도시된 업 신호 합산기의 동작을 보여주는 타이밍도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0009] 도 1에서, 본 발명의 실시예에 따른 시스템(1)의 구성을 보여주는 도면이다. 도 1에서, 상기 시스템(1)은 전송 장치(110) 및 수신 장치(120)를 포함할 수 있다. 상기 전송 장치(110)는 데이터를 전송하는 쪽을 대표하는 구성 요소일 수 있고, 상기 수신 장치(120)는 상기 전송 장치(110)로부터 전송된 데이터를 수신하는 쪽을 대표하는 구성요소일 수 있다. 예를 들어, 상기 시스템(1)은 마스터 장치와 슬레이브 장치를 포함할 수 있고, 마스터 장치로부터 상기 슬레이브 장치로 데이터가 전송될 때, 상기 마스터 장치는 상기 전송 장치(110)일 수 있고, 상기 슬레이브 장치는 상기 수신 장치(120)일 수 있다. 반대로, 상기 슬레이브 장치로부터 상기 마스터 장치로 데이터가 전송될 때, 상기 마스터 장치는 상기 수신 장치(120)일 수 있고, 상기 슬레이브 장치는 상기 전송 장치(110)일 수 있다.

- [0010] 상기 시스템(1)을 구성하는 상기 전송 장치(110) 및 상기 수신 장치(120)는 적은 개수의 데이터 버스를 사용하는 직렬 데이터 전송 방식으로 통신할 수 있다. 도 1에서, 상기 전송 장치(110)는 데이터 인코더(111)를 포함할수 있다. 상기 수신 장치(120)는 클럭 데이터 리커버리 회로(121, CDR) 및 데이터 디코더(122)를 포함할수 있다. 상기 전송 장치(110)는 복수의 데이터 버스(131, 132, 133)를 통해 상기 수신 장치(120)와 연결될수 있다. 도 1에서, 상기 데이터 버스(131, 132, 133)의 개수는 3개인 것으로 예시하였으나, 이에 한정하려는 의도는 아니다. 상기 전송 장치(110)는 상기 데이터 인코더(111)를 통해 적어도 4비트 이상의 내부 데이터를 인코딩하여복수 그룹의 3비트의 데이터(D1, D2, D3)로 변환할수 있다. 상기 복수 그룹의 3비트 데이터(D1, D2, D3)는 상기 데이터 버스(131, 132, 133)를 통해 순차적으로 직렬 전송될수 있다. 상기 데이터(D1, D2, D3)는 상기 데이터 버스(131, 132, 133)를 통해 전송되는 데이터를 지칭할수 있고, 상기 내부 데이터는 상기 전송 장치(110) 또는 상기 수신 장치(120) 내부에서 사용되는 데이터를 지칭할수 있다. 예를 들어, 상기 데이터 인코더(111)는 16비트의 내부 데이터를 인코딩하여 7개 그룹의 3비트 데이터(D1, D2, D3)로 변환할수 있고, 상기 7개 그룹의 3비트 데이터(D1, D2, D3)는 상기 3개의 데이터 버스(131, 132, 133)를 통해 직렬 전송될수 있다.

- [0011] 상기 수신 장치(120)의 클럭 데이터 리커버리 회로(121, CDR)는 상기 데이터 버스(131, 132, 133)를 통해 전송된 데이터로부터 클럭 신호(CLK)를 생성할 수 있다. 상기 클럭 신호(CLK)는 스트로브 신호로 사용될 수 있고, 상기 수신 장치(120)는 상기 클럭 신호(CLK)에 동기하여 상기 데이터 버스(131, 132, 133)를 통해 전송된 데이터(D1, D2, D3)를 수신할 수 있다. 상기 데이터 디코더(122)는 상기 데이터 버스(131, 132, 133)를 통해 전송된 복수 그룹의 3비트 데이터(D1, D2, D3)를 적어도 4비트 이상의 내부 데이터로 변환할 수 있다. 예를 들어, 상기 데이터 디코더(122)는 3비트씩 7회에 걸쳐 순차적으로 전송된 21비트의 데이터(D1, D2, D3)를 디코딩하여 16비트의 내부 데이터로 변환할 수 있다.

- [0012] 상기 데이터 인코더(111) 및 상기 데이터 디코더(122)는 상기 내부 데이터를 상기 데이터(D1, D2, D3)로 변환하 거나 상기 데이터(D1, D2, D3)를 상기 내부 데이터로 변환하기 위한 변환 테이블을 포함할 수 있다. 상기 3개의 데이터 버스(131, 132, 133)를 통해 전송되는 3비트의 데이터(D1, D2, D3)는 3개의 상태(phase, state 또는 level)를 갖는 데이터일 수 있다.

- [0013] 상기 클럭 데이터 리커버리 회로(121)는 상기 데이터(D1, D2, D3)로부터 클럭 신호(CLK)를 생성할 수 있고, 상기 클럭 신호(CLK)와 상기 데이터(D1, D2, D3)를 비교하여 상기 클럭 신호(CLK)의 위상을 조절할 수 있다.

- [0014] 도 2는 본 발명의 실시예에 따른 클럭 데이터 리커버리 회로(2)의 구성을 보여주는 도면이다. 도 2에서, 상기 클럭 데이터 리커버리 회로(2)는 위상 검출부(210), 필터링부(220), 위상 정보 합산부(230) 및 위상 보간기 (240)를 포함할 수 있다. 상기 위상 검출부(210)는 클럭 신호(CLK) 및 데이터(DATA)를 수신하고, 상기 클럭 신호(CLK)의 주기마다 상기 클럭 신호(CLK)와 상기 데이터(DATA)를 비교할 수 있다. 예를 들어, 상기 위상 검출부 (210)는 상기 클럭 신호(CLK)의 에지가 상기 데이터(DATA)의 천이 시점에 비해 앞서있는지 뒤져있는지 여부를 검출할 수 있다. 상기 위상 검출부(210)는 상기 클럭 신호(CLK)와 상기 데이터(DATA)를 비교하여 얼리 위상 감지 신호(ER) 및 레이트 위상 감지 신호(LT)를 생성할 수 있다. 예를 들어, 상기 위상 검출부(210)는 상기 데이

터(DATA)의 천이 시점에 비해 상기 클럭 신호(CLK)의 에지가 앞서 있으면 상기 얼리 위상 감지 신호(ER)를 생성할 수 있고, 상기 데이터(DATA)의 천이 시점에 비해 상기 클럭 신호(CLK)의 에지가 뒤져 있으면 상기 레이트 위상 감지 신호(LT)를 생성할 수 있다. 상기 위상 검출부(210)의 구체적인 동작에 대해서는 후술하기로 한다.

- [0015] 상기 필터링부(220)는 상기 위상 검출부(210)로부터 상기 얼리 위상 감지 신호(ER) 및 상기 레이트 위상 감지 신호(LT)를 수신하고, 업 신호(UP) 및 다운 신호(DN)를 생성할 수 있다. 상기 필터링부(220)는 상기 얼리 위상 감지 신호의(ER) 생성 횟수와 상기 레이트 위상 감지 신호(LT)의 생성 횟수에 따라 상기 업 신호(UP) 및 상기 다운 신호(DN)를 생성할 수 있다. 상기 필터링부(220)는 상기 얼리 위상 감지 신호(ER)의 생성 횟수와 상기 레이트 위상 감지 신호(LT)의 생성 횟수의 차이가 소정 개수에 도달했을 때, 상기 업 신호(UP) 및 상기 다운 신호(DN) 중 하나를 생성할 수 있다. 상시 소정 개수는 상기 필터링부(220)의 필터 길이(filter depth)에 대응할 수 있다. 예를 들어, 상기 필터 길이가 3이라면, 상기 필터링부(220)는 상기 얼리 위상 감지 신호(ER)가 상기 레이트 위상 감지 신호(LT)보다 3회 더 많이 생성되었을 때 상기 다운 신호(DN)를 생성할 수 있다. 또한, 상기 필터링부(220)는 상기 레이트 위상 감지 신호(LT)가 상기 얼리 위상 감지 신호(ER)보다 3회 더 많이 생성되었을 때 상기 업 신호(UP)를 생성할 수 있다. 일 실시예에서, 상기 필터링부(220)는 무빙 에버리지 필터(moving average filter)를 포함할 수 있다.

- [0016] 상기 위상 정보 합산부(230)는 상기 클럭 신호(CLK)의 주기마다 상기 필터링부(220)의 출력 신호를 수신하고, 상기 클럭 신호(CLK)의 주기의 n 배에 대응하는 시간 동안 상기 필터링부(220)로부터 수신된 업 신호(UP) 및 다운 신호(DN)의 개수를 합산할 수 있다. 상기 n은 2이상의 모든 정수일 수 있다. 일 실시예에서, 상기 n은 상기 필터링부(220)의 필터 길이에 대응하는 수일 수 있으나, 이에 한정하려는 것은 아니다. 상기 클럭 신호(CLK)의 주기의 n 배에 대응하는 시간은 합산 시간일 수 있다. 상기 위상 정보 합산부(230)는 상기 합산 시간 동안 수신된 상기 업 신호(UP) 및 상기 다운 신호(DN)의 개수를 합산하여 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)를 생성할 수 있다. 예를 들어, 상기 위상 정보 합산부(230)는 합산된 업 신호(UP)의 개수에 따라 상기 제 1 위상 제어 신호(MAFUP<0:m>)의 논리 값을 변화시킬 수 있고, 합산된 다운 신호(DN)의 개수에 따라 상기 제 2 위상 제어 신호(MAFUP<0:m>)는 상기 클럭 신호(CLK)의 위상을 지연시키는 정보를 갖는 신호일 수 있고, 상기 제 2 위상 제어 신호(MAFUP<0:m>)는 상기 클럭 신호(CLK)의 위상을 앞당기는 정보를 갖는 신호일 수 있다.

- [0017] 상기 위상 정보 합산부(230)는 상기 클럭 신호(CLK)에 동기하여 상기 필터링부(220)로부터 출력되는 업 신호 (UP) 또는 다운 신호(DN)를 수신할 수 있고, 상기 클럭 신호(CLK)의 주기의 n 배의 주기를 갖는 클럭 신호 (CLK/n)에 동기하여 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)를 출력할 수 있다. 이하에서, 상기 클럭 신호(CLK)는 제 1 클럭 신호의 명칭과 함께 서술될 수 있고, 상기 클럭 신호의 주기의 n 배의 주기를 갖는 클럭 신호(CLK/n)는 제 2 클럭 신호의 명칭으로 함께 서술될 수 있다. 즉, 상기 제 2 클럭 신호(CLK/n)는 상기 제 1 클럭 신호(CLK/b보다 n 배 낮은 주파수를 가질 수 있다.

- [0018] 상기 위상 보간기(240)는 상기 위상 정보 합산부(230)로부터 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)를 수신할 수 있다. 상기 위상 보간기(240)는 상기 제 1 및 제 2 위상 정보 신호(MAFUP<0:m>, MAFDN<0:m>)에 기초하여 상기 클럭 신호(CLK)의 위상을 조절할 수 있다. 상기 위상 보간기(240)는 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)를 수신하는 시점을 동기시키기 위해 상기 제 2 클럭 신호(CLK/n)를 수신할 수 있다. 따라서, 상기 위상 보간기(220)는 상기 제 2 클럭 신호(CLK/n)에 동기하여 업데이트 될 수 있고, 상기 제 2 클럭 신호(CLK/n)의 주기마다 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)에 기초하여 상기 클럭 신호(CLK/n)의 위상을 조절할 수 있다.

- [0019] 도시되지는 않았지만, 상기 위상 보간기(240)는 다수의 단위 지연 셀을 포함할 수 있고, 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)에 따라 턴온되는 단위 지연 셀의 개수를 조절하여 상기 클릭 신호(CLK)의 위상을 조절할 수 있다. 상기 위상 보간기(240)는 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)에 따라 1개의 단위 지연 셀을 턴온 시키거나 턴오프 시킬 수 있고, 2 이상의 단위 지연 셀을 한번에 턴온 시키거나 2 이상의 단위 지연 셀을 한번에 턴오프시킬 수 있다. 즉, 상기 위상 보간기(240)는 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)에 기초하여 상기 클릭 신호(CLK)의 위상 조절량을 변화시킬수 있다.

- [0020] 상기 위상 검출부(210)는 상기 클럭 신호(CLK)의 주기마다 상기 얼리 위상 감지 신호(ER) 및 상기 레이트 위상 감지 신호(LT)를 생성할 수 있다. 상기 필터링부(220)는 상기 클럭 신호(CLK)의 주기마다 생성되는 상기 얼리 및 레이트 위상 감지 신호(ER, LT)의 생성 횟수를 연산한다. 상기 얼리 및 레이트 위상 감지 신호(ER, LT)가 교

대로 반복하여 생성되면, 상기 얼리 및 레이트 위상 감지 신호(ER, LT)의 생성 횟수 차이가 필터 길이에 도달하는 때를 특정할 수 없다. 따라서, 상기 필터링부(220) 이후에 연결되는 구성요소들은 상기 클럭 신호(CLK)의 주기마다 상기 필터링부(220)로부터 업 신호(UP)가 생성되는지 또는 다운 신호(DN)가 생성되는지 여부를 확인해야만 한다. 이 때, 상기 위상 정보 합산부(230)는 상기 클럭 신호(CLK)에 동기하여 상기 필터링부(220)에서 생성된 상기 업 신호(UP) 및 다운 신호(DN)를 수신하고, 상기 제 2 클럭 신호(CLK/n)의 주기에 대응하는 시간 동안수신된 업 신호(UP)와 다운 신호(DN)의 개수를 합산하며, 상기 제 2 클럭 신호(CLK/n)에 동기하여 상기 합산된결과를 상기 제 1 및 제 2 위상 제어 신호(MAFUP<0:m>, MAFDN<0:m>)로서 제공할 수 있다. 따라서, 상기 위상 보간기(240)는 상기 제 2 클럭 신호(CLK/n)의 주기마다 업데이트될 수 있고, 위상 보간기(240)에서 소모되는 전력은 감소될 수 있다. 만약, 상기 위상 정보 합산부(230)가 존재하지 않는다면, 상기 위상 보간기(240)는 상기 클럭 신호(CLK)의 주기마다 상기 업 신호(UP) 및 다운 신호(DN)를 수신해야 하고, 이에 따라 업데이트 주기가 빨라져 큰 전력을 소모할 수밖에 없을 것이다. 또한, 상기 위상 정보 합산부(230)는 상기 필터링부(220)가 무빙에버리지 필터임에도 불구하고 로우 패스 필터로서의 기능을 충실하게 수행할 수 있도록 한다.

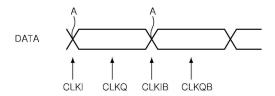

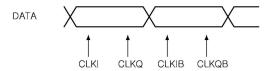

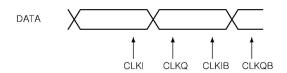

- [0021] 도 3a 내지 3d는 도 2에 도시된 위상 검출부(210)의 동작을 보여주는 도면이다. 상기 위상 검출부(210)는 상기 클럭 신호(CLK) 및 데이터(DATA)를 비교하여 상기 얼리 위상 감지 신호(ER) 및 상기 레이트 위상 감지 신호(L T)를 생성할 수 있다. 상기 위상 검출부(210)는 상기 클럭 신호(CLK)의 1주기 동안 상기 클럭 신호(CLK)의 0도, 90도, 180 및 270도에 해당하는 위상에서 상기 데이터(DATA)의 레벨을 캐치할 수 있다. 이를 위해, 상기 위상 검출부(210)는 상기 클럭 신호(CLK)를 분주한 분주 클럭 신호를 이용할 수 있고, 상기 분주 클럭 신호의 라이징에지에서 상기 데이터(DATA)의 레벨을 캐치할 수 있다. 상기 분주 클럭 신호는 상기 위상 보간기(240)에서 생성될 수 있고, 상기 위상 검출부(210)에서 분주될 수도 있다. 도 3a 내지 도 3c에서, 상기 분주 클럭 신호(CLK)에는 상기 클럭 신호(CLK)와 동일한 위상을 가질 수 있고, 상기 분주 클럭 신호(CLK)에 비해 90도 지연된 위상을 가질 수 있으며, 상기 분주 클럭 신호(CLK)에 비해 270도 지연된 위상을 가질 수 있다.

- [0022] 도 3a는 클럭 신호(CLK)의 위상 조절이 필요 없는 경우, 즉, 락킹 상태(Locking state)를 도시한다. 락킹 상태 에서, 상기 분주 클럭 신호(CLKI, CLKIB)의 라이징 에지는 상기 데이터(DATA)의 천이 시점(A)에 위치될 수 있다. 상기 분주 클럭 신호(CLKQ, CLKQB)의 라이징 에지는 상기 데이터(DATA)의 유효 구간의 중앙 부분에 위치 될 수 있다. 상기 위상 검출부(210)는 상기 분주 클럭 신호(CLKI, CLKQ, CLKIB, CLKQB)의 라이징 에지에서 캐치 된 데이터(DATA)의 레벨을 연산하여 상기 얼리 위상 감지 신호(ER) 및 상기 레이트 위상 감지 신호(LT)를 생성 할 수 있다. 상기 위상 검출부(210)는 상기 분주 클럭 신호(CLKI)에 의해 캐치된 데이터의 레벨과 상기 분주 클 럭 신호(CLKQ)에 의해 캐치된 데이터의 레벨을 XOR 연산하고, 상기 분주 클럭 신호(CLKQ)에 의해 캐치된 데이터 의 레벨과 상기 분주 클럭 신호(CLKIB)에 의해 캐치된 데이터의 레벨을 XOR 연산할 수 있다. 상기 위상 검출부 (210)는 상기 XOR 연산 결과에 기초하여 상기 얼리 위상 감지 신호(ER) 및 상기 레이트 위상 감지 신호(LT)를 생성할 수 있다. 도 3b에 도시된 표와 같이, 상기 위상 검출부(210)는 상기 분주 클릭 신호(CLKI, CLKQ)에 의해 캐치된 데이터의 레벨(I, Q)이 동일하여 XOR 연산된 결과가 0이고 상기 분주 클럭 신호(CLKQ, CLKIB)에 의해 캐 치된 데이터의 레벨(Q, IB)이 상이하여 XOR 연산된 결과가 1인 경우, 상기 클럭 신호(CLK)의 에지의 위상이 상 기 데이터(DATA)의 천이 시점보다 늦다고 판단하고(Late), 상기 레이트 위상 감지 신호(LT)를 생성할 수 있다. 반대로, 상기 위상 검출부(210)는 상기 분주 클럭 신호(CLKI, CLKQ)에 의해 캐치된 데이터의 레벨(I, Q)이 상이 하여 XOR 연산 결과가 1이고, 상기 분주 클럭 신호(CLKQ, CLKIB)에 의해 캐치된 데이터의 레벨(Q, IB)이 동일하 여 XOR 연산 결과가 0인 경우, 상기 클럭 신호(CLK)의 에지의 위상이 상기 데이터(DATA)의 천이 시점보다 앞선 다고 판단하고, 상기 얼리 위상 감지 신호(ER)를 생성할 수 있다. 상기 2가지 경우에 해당하지 않는 경우, 상기 위상 검출부(210)는 상기 얼리 위상 감지 신호(ER) 및 상기 레이트 위상 감지 신호(LT) 모두를 생성하지 않을 수 있다.

- [0023] 도 3c는 상기 클럭 신호(CLK)의 에지의 위상이 상기 데이터(DATA)의 천이 시점보다 늦은 경우를 보여준다. 상기 데이터(DATA)가 토글한다면, 상기 분주 클럭 신호(CLKI. CLKQ)에 의해 캐치된 데이터의 레벨(I, Q)은 동일하고, 상기 분주 클럭 신호(CLKQ, CLKIB)에 의해 캐치된 데이터의 레벨(Q, IB)은 상이할 것이다. 따라서, 도 3c의 경우 상기 위상 검출부(210)는 레이트 위상 감지 신호(LT)를 생성할 수 있다. 도 3d는 상기 클럭 신호(CLK)의 위상이 상기 데이터(DATA)의 천이 시점보다 빠른 경우를 보여준다. 상기 분주 클럭 신호(CLKI, CLKQ)에 의해 캐치된 데이터의 레벨(I, Q)은 상이하고, 상기 분주 클럭 신호(CLKQ, CLKIB)에 의해 캐치된 데이터의 레벨(Q, IB)은 동일할 것이다. 따라서, 도 3d의 경우 상기 위상 검출부(210)는 얼리 위상 감지 신호(ER)를 생성할 수 있다.

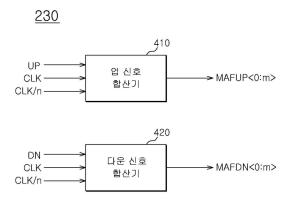

- [0024] 도 4는 도 2에 도시된 위상 정보 합산부(230)의 구성을 개략적으로 보여주는 블록도이다. 도 4에서, 상기 위상 정보 합산부(230)는 업 신호 합산기(410) 및 다운 신호 합산기(420)를 포함할 수 있다. 상기 업 신호 합산기(410)는 상기 필터링부(220)에서 출력되는 업 신호(UP), 상기 클럭 신호(CLK) 및 상기 제 2 클럭 신호(CLK/n)를 수신하여 상기 제 1 위상 제어신호(MAFUP<0:m>)를 생성할 수 있다. 상기 업 신호 합산기(410)는 상기 합산 시간 동안 입력되는 업 신호(UP)의 개수를 합산하여 출력할 수 있다. 상기 업 신호 합산기(410)는 상기 클럭 신호(CLK)의 주기마다 상기 업 신호(UP)를 수신할 수 있고, 상기 제 2 클럭 신호(CLK/n)의 주기마다 합산된 업 신호(UP)의 개수에 대응하는 정보를 상기 제 1 위상 제어 신호(MAFUP<0:m>)로서 출력할 수 있다. 상기 업 신호 합산기(410)는 상기 합산 시간 동안 합산된 상기 업 신호(UP)의 개수를 복수 비트의 이진 코드로 출력할 수 있다.

- [0025] 상기 다운 신호 합산기(420)는 상기 필터링부(220)에서 출력되는 다운 신호(DN), 상기 클럭 신호(CLK) 및 상기 제 2 클럭 신호(CLK/n)를 수신하여 상기 제 2 위상 제어 신호(MAFDN<0:m>)를 생성할 수 있다. 상기 다운 신호 합산기(420)는 상기 합산 시간 동안 입력되는 다운 신호(DN)의 개수를 합산하여 출력할 수 있다. 상기 다운 신호 합산기(420)는 상기 클럭 신호(CLK)의 주기마다 상기 다운 신호(DN)를 수신할 수 있고, 상기 제 2 클럭 신호 (CLK/n)의 주기마다 합산된 다운 신호(DN)의 개수에 대응하는 정보를 상기 제 2 위상 제어 신호(MAFDN<0:m>)로 서 출력할 수 있다. 상기 다운 신호 합산기(DN)는 상기 합산 시간 동안 합산된 상기 다운 신호(DN)의 개수를 복수 비트의 이진 코드로 출력할 수 있다.

- [0026] 도 5는 도 4에 도시된 업 신호 합산기(410)의 구성을 보여주는 도면이다. 도 5에서, 상기 업 신호 합산기(410)는 XOR 게이트(501), AND 게이트(503), 제 1 내지 제 3 플립플롭(511, 513, 515)을 포함할 수 있다. 상기 XOR 게이트(501)는 상기 업 신호(UP)와 상기 제 1 플립플롭(511)의 출력을 수신하여 섬 신호(SUMUP)를 생성할 수 있다. 상기 AND 게이트(503)는 상기 업 신호(UP)와 상기 제 1 플립플롭(511)의 출력을 수신하여 캐리 신호(CARRYUP)를 생성할 수 있다. 상기 제 1 플립플롭(511)은 상기 섬 신호(SUMUP)와 상기 클릭 신호(CLK)를 수신하여 상기 지연 섬 신호(SUMUP)를 생성할 수 있다. 상기 제 2 플립플롭(513)은 상기 섬 신호(SUMUP)와 상기 제 2 클릭 신호(CLK/4)를 수신하여 상기 제 1 위상 제어 신호의 최하위 비트(MAFUP<O>)를 생성할 수 있다. 상기 제 3 플립플롭(515)은 상기 캐리 신호(CARRYUP)와 상기 제 2 클릭 신호(CLK/4)를 수신하여 상기 제 1 위상 제어 신호의 최상위 비트(MAFUP<1>)를 생성할 수 있다. 도 5에서, n은 4이고, 상기 업 신호 합산기(410)는 상기 합산 시간 동안 2개의 업 신호(UP)를 합산할 수 있는 구성을 도시하였으나, 상기 업 신호 합산기(410)는 위와 같은 방식을 이용하여 더 많은 수의 업 신호(UP)를 합산할 수 있는 구성을 갖도록 수정되거나 다른 구성요소가 추가될수 있을 것이다. 상기 다운 신호 합산기(420)는 업 신호(UP) 대신에 다운 신호(DN)를 수신하는 것에서 차이가 있을 뿐이고, 상기 업 신호 합산기(410)와 실질적으로 동일한 구성을 가질 수 있다.

- [0027] 도 6은 도 5에 도시된 업 신호 합산기(410)의 동작을 보여주는 타이밍도이다. 상기 합산 시간, 즉, 상기 제 2 클릭 신호(CLK/n)의 주기 동안 2개의 업 신호(UP)가 입력된다고 가정하자. 첫 번째 업 신호(UP(1))가 입력되면, 상기 XOR 게이트(501)는 하이 레벨의 섬 신호(SUMUP)를 출력하고, 상기 AND 게이트(503)는 로우 레벨의 캐리 신호(CARRYUP)를 출력할 수 있다. 상기 섬 신호(SUMUP)는 상기 제 1 플립플롭(511)에 의해 상기 클릭 신호(CLK)의 주기만큼 지연되어 상기 지연 섬 신호(SUMUP)로 출력될 수 있다. 두 번째 업 신호(UP(2))가 입력되면, 상기 XOR 게이트(501)는 로우 레벨의 섬 신호(SUMUP)를 출력하고, 상기 AND 게이트(503)는 하이 레벨의 캐리 신호(CARRYUP)를 출력할 수 있다. 상기 제 2 플립플롭(513)은 상기 제 2 클릭 신호(CLK/n)에 응답하여 상기 로우 레벨의 섬 신호(SUMUP)를 상기 제 1 위상 제어 신호의 최하위 비트(MAFUP<0>)로 출력하고, 상기 제 3 플립플롭(515)은 상기 제 2 클릭 신호(CLK/n)에 응답하여 하이 레벨의 캐리 신호(CARRYUP)를 상기 제 1 위상 제어 신호의 최상위 비트(MAFUP<0) > )로 출력할 수 있다. 따라서, 상기 제 1 위상 제어 신호(MAFUP<0) > )는 1,0의 논리 값을 가질 수 있고, 상기 합산 시간 동안 상기 업 신호(UP)가 2회 생성되었다는 정보를 가질 수 있다.

- [0028] 상기 필터링부(220)는 상기 위상 검출부(210)로부터 출력되는 얼리 위상 감지 신호(ER)와 레이트 위상 감지 신호(LT)를 상기 클럭 주기(CLK)마다 수신하여 연산하므로, 상대적으로 짧은 주기로 위상 정보를 획득할 수 있다. 상기 위상 정보 합산부(230)는 상기 위상 검출부(210) 및 상기 필터링부(220)가 짧은 주기로 위상 정보를 획득하더라도, 상대적으로 긴 주기 동안 획득된 위상 정보를 합산할 수 있다. 상기 위상 보간기(240)는 상대적으로 긴 주기마다 합산된 위상 정보에 따라 업데이트될 수 있다. 따라서, 상기 클럭 데이터 리커버리 회로(2) 및 이를 이용하는 시스템(1)에서 소모되는 전력을 효율적으로 감소시킬 수 있다.

- [0029] 본 발명이 속하는 기술분야의 당업자는 본 발명이 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있으므로, 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적인 것이아닌 것으로서 이해해야만 한다. 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 등가개념으로부터 도출되는 모든 변경 또는 변형된 형태가

본 발명의 범위에 포함되는 것으로 해석되어야 한다.

# 도면

# 도면1

# 도면2

<u>2</u>

# 도면3a

# 도면3b

| I ⊕ Q | Q⊕IB |       |

|-------|------|-------|

| 0     | 1    | Late  |

| 1     | 0    | Early |

| 0     | 0    | Х     |

| 1     | 1    | Х     |

# 도면3c

# 도면3d

# 도면4

# 도면5

# 410 UP 501 SUMUP CLK/4 CLK/4 MAFUP<0> CLK/4 CLK/4 MAFUP<1> CLK/4

# 도면6