## (11) Número de Publicação: PT 2430555 E

(51) Classificação Internacional: **G06F 13/16** (2013.01) **G06F 12/10** (2013.01)

## (12) FASCÍCULO DE PATENTE DE INVENÇÃO

(22) Data de pedido: 2010.11.08 (73) Titular(es): **INTERNATIONAL BUSINESS MACHINES** (30) Prioridade(s): 2010.06.23 US 821170 **CORPORATION NEW ORCHARD PLACE ARMONK, NY 10504 US** (43) Data de publicação do pedido: 2012.03.21 (72) Inventor(es): DAVID CRADDOCK US (45) Data e BPI da concessão: 2013.08.28 THOMAS GREGG US 189/2013 **DAN GREINER** US **ERIC NORMAN LAIS** US (74) Mandatário: LUÍS MANUEL DE ALMADA DA SILVA CARVALHO **RUA VÍCTOR CORDON, 14 1249-103 LISBOA** PT

## (54) Epígrafe: TRADUÇÃO DE ENDEREÇOS DE ENTRADA/SAÍDA PARA ENDEREÇOS DE MEMÓRIA

#### (57) Resumo:

UM ENDEREÇO FORNECIDO NUM PEDIDO EMITIDO POR UM ADAPTADOR É CONVERTIDO NUM ENDEREÇO DIRETAMENTE UTILIZÁVEL NO ACESSO À MEMÓRIA DE SISTEMA. O ENDEREÇO INCLUI UMA PLURALIDADE DE BITS, EM QUE A PLURALIDADE DE BITS INCLUI UMA PRIMEIRA PORÇÃO DE BITS E UMA SEGUNDA PORÇÃO DE BITS. A SEGUNDA PORÇÃO DE BITS É UTILIZADA PARA INDEXAR EM UM OU MAIS NÍVEIS DE TABELAS DE TRADUÇÃO DE ENDEREÇOS PARA REALIZAR A TRADUÇÃO, AO PASSO QUE A PRIMEIRA PORÇÃO DE BITS É IGNORADA PARA A CONVERSÃO. A PRIMEIRA PORÇÃO DE BITS É UTILIZADA PARA A VALIDAÇÃO DO ENDEREÇO.

## **RESUMO**

# "TRADUÇÃO DE ENDEREÇOS DE ENTRADA/SAÍDA PARA ENDEREÇOS DE MEMÓRIA"

Um endereço fornecido num pedido emitido por um adaptador é convertido num endereço diretamente utilizável no acesso à memória de sistema. O endereço inclui uma pluralidade de bits, em que a pluralidade de bits inclui uma primeira porção de bits e uma segunda porção de bits. A segunda porção de bits é utilizada para indexar em um ou mais níveis de tabelas de tradução de endereços para realizar a tradução, ao passo que a primeira porção de bits é ignorada para a conversão. A primeira porção de bits é utilizada para a validação do endereço.

## **DESCRIÇÃO**

## "TRADUÇÃO DE ENDEREÇOS DE ENTRADA/SAÍDA PARA ENDEREÇOS DE MEMÓRIA"

#### ANTECEDENTES

Esta invenção refere-se, em geral, à tradução de endereços num ambiente informático, e em particular, à tradução de um endereço de entrada/saída para um endereço de memória utilizável no acesso à memória de sistema do ambiente.

A memória de sistema é acessível através de pedidos de leitura e de escrita. Estes pedidos podem ser provenientes de vários componentes de um ambiente informático, incluindo unidades centrais de processamento, assim como adaptadores. Cada pedido inclui um endereço que irá ser utilizado para aceder à memória de sistema. Este endereco, no entanto, normalmente não tem uma correspondência um-para-um com uma localização física na memória de sistema. Portanto, a tradução de endereços é realizada.

A tradução de endereços é utilizada para traduzir um endereço que é fornecido de uma forma não diretamente utilizável no acesso à memória de sistema para uma outra forma que pode ser utilizada diretamente no acesso a uma

localização física na memória de sistema. Por exemplo, um endereço virtual incluído num pedido fornecido por uma unidade central de processamento é traduzido para um endereço real ou absoluto na memória de sistema. Como exemplo adicional, um endereço de Interconexão de Componentes Periféricos (Peripheral Component Interconnect - PCI), fornecido num pedido proveniente de um adaptador pode ser traduzido para um endereço absoluto na memória de sistema.

2008/0168208 Publicação dos EUA No. Al. publicada em 10 de julho de 2008, Gregg, "I/O Adapter LPAR Isolation In a Hypertransport Environment With Assigned Memory Space Indexing A TVT Via Unit IDs" descreve um sistema e método de processamento de dados para isolamento de uma pluralidade de adaptadores de I/O no sistema. O sistema de processamento de dados compreende também um conjunto de processadores, uma ponte anfitriã bridge), e um barramento (bus) de sistema que liga o conjunto de processadores e a host bridge. Cada um dos adaptadores de I/O tem um ID respetivo e envia comandos para a host bridge que incluem um ou mais dos IDs dos adaptadores de I/O. Na forma de realização preferida, estes são de Unidade (Unit. IDs)definidos IDs IDs HyperTransport, e os comandos emitidos pelos Adaptadores de I/O incluem um campo de *Unit ID* que contém um ou mais dos Unit IDs dos Adaptadores de I/O. Cada um dos Unit IDs é utilizado para indexar um TVT para identificar espaços de memória de sistema únicos e independentes.

Publicação dos EUA No. 2009/0182966 Al, publicada em 16 de julho de 2009, Greiner et al., "Dynamic Address Translation with Frame Management" divulga uma função de gestão de tabela definida para uma arquitetura de máquina de um sistema informático. Numa realização, uma instrução de gestão de tabela é obtida, a qual identifica um primeiro e um segundo registo geral. O primeiro registo geral contém um campo de gestão de tabela com um campo da chave com bits de proteção de acesso e uma indicação de tamanho de bloco. Se a indicação de tamanho de bloco indicar um bloco grande então um endereço do operando de um bloco grande de dados é obtido a partir do segundo registo geral. O bloco grande de dados tem uma pluralidade de blocos pequenos cada um dos quais está associado com uma chave correspondente de armazenamento tendo uma pluralidade de bits de proteção de acesso da chave de armazenamento. Se a indicação de tamanho de bloco indicar um bloco grande, os bits de proteção de acesso da chave de armazenamento de cada chave de armazenamento correspondente de cada bloco pequeno dentro do bloco grande são definidos com os bits de proteção de acesso do campo da chave.

US 6 658 521 divulga método e aparelho para tradução de endereços sobre o *bus* PCI sobre uma rede *infiniband*.

US 2008/0114906 Al divulga acessos de sistema especiais mapeados na memória, controlados eficientemente.

#### BREVE SUMÁRIO

As deficiências da técnica anterior são ultrapassadas e vantagens adicionais são proporcionadas através do fornecimento de um método tal como reivindicado na reivindicação 1, e produto de programa de computador e sistema correspondentes.

Características e vantagens adicionais são realizadas através das técnicas da presente invenção. Outras formas de realização e aspetos da invenção são aqui descritos em pormenor e são considerados parte da invenção reivindicada.

### DESCRIÇÃO RESUMIDA DAS DIVERSAS VISTAS DOS DESENHOS

Um ou mais aspetos da presente invenção são particularmente salientados e distintamente reivindicados como exemplos nas reivindicações na conclusão da especificação. O anterior e outros objetivos, características e vantagens da invenção são evidentes a partir da seguinte descrição detalhada tomada em conjunto com os desenhos acompanhantes nos quais:

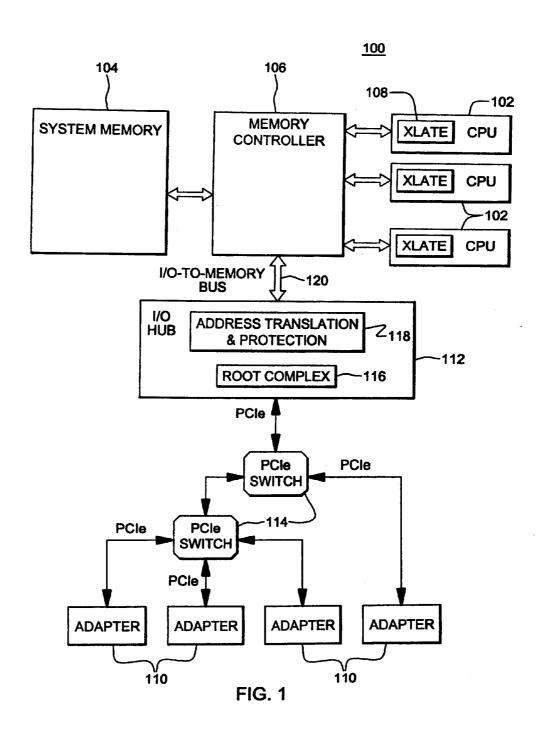

A FIG. 1 representa uma forma de realização de um ambiente informático para incorporar e utilizar um ou mais aspetos da presente invenção;

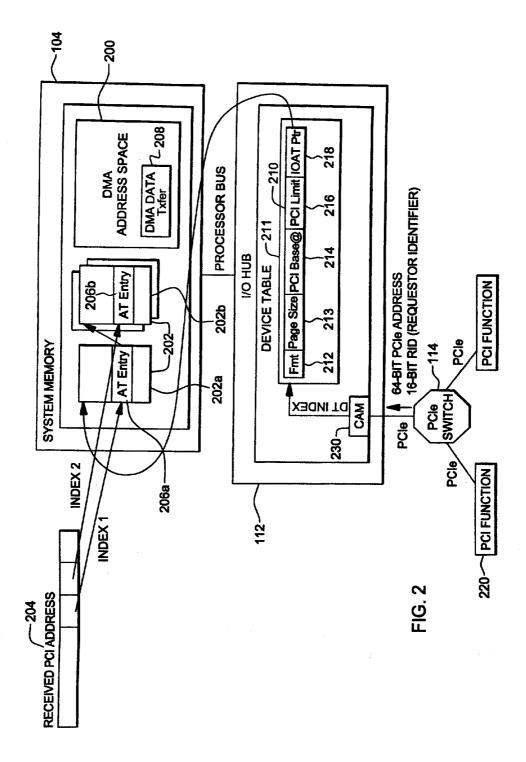

A FIG. 2 representa uma forma de realização de

detalhes adicionais sobre a memória de sistema e o *hub* de I/O do sistema da FIG. 1, de acordo com um aspeto da presente invenção;

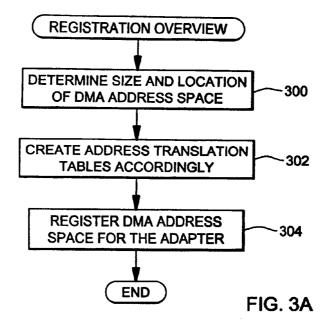

A FIG. 3A representa uma forma de realização de uma vista geral da lógica para registar um espaço de endereçamento DMA (Acesso Direto de Memória - Direct Memory Access) para um adaptador, de acordo com um aspeto da presente invenção;

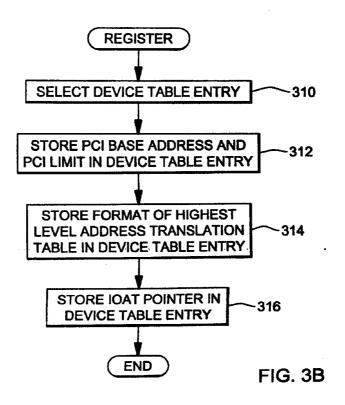

A FIG. 3B representa uma forma de realização de vários detalhes do registo do espaço de endereçamento DMA para o adaptador, de acordo com um aspeto da presente invenção;

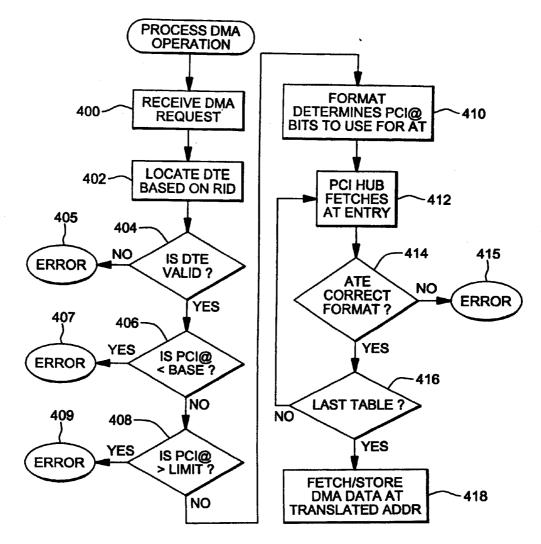

A FIG. 4 representa uma forma de realização da lógica para processar uma operação DMA, de acordo com um aspeto da presente invenção;

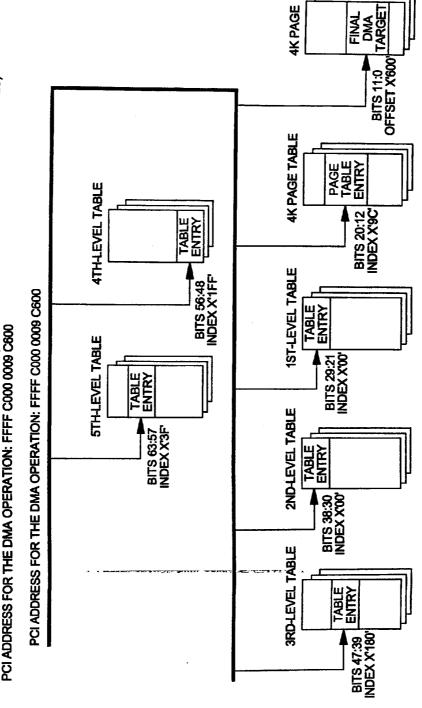

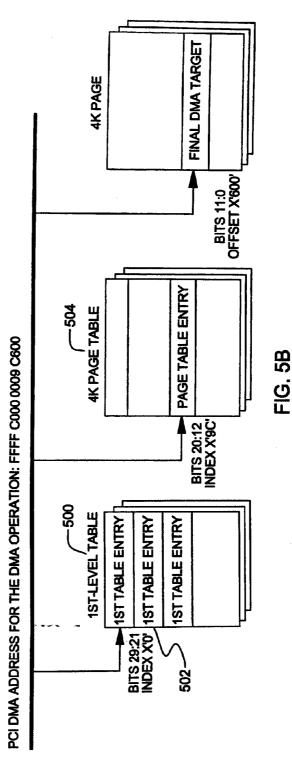

A FIG. 5A representa um exemplo dos níveis de tradução empregues quando um endereço inteiro é utilizado para indexar em tabelas de tradução de endereços para traduzir o endereço e para aceder à página;

A FIG. 5B representa um exemplo de níveis de tradução empregues quando uma parte do endereço é ignorada durante a indexação nas tabelas de tradução de endereços, de acordo com um aspeto da presente invenção;

A FIG. 5C representa exemplos de vários formatos compatíveis com CPU DAT utilizáveis de acordo com um ou mais aspetos da presente invenção;

A FIG. 5D representa exemplos de vários formatos estendidos de tradução de endereços de I/O utilizáveis de acordo com um ou mais aspetos da presente invenção;

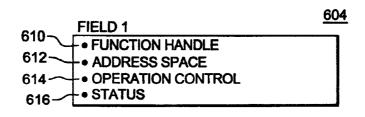

A FIG. 6A representa uma forma de realização de uma instrução de Modificar Controlos de Função PCI utilizada de acordo com um aspeto da presente invenção;

A FIG. 6B representa uma forma de realização de um campo utilizado pela instrução de Modificar Controlos de Função PCI da FIG. 6A, de acordo com um aspeto da presente invenção;

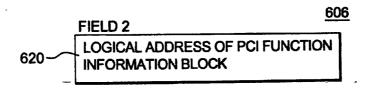

A FIG. 6C representa uma forma de realização de um outro campo utilizado pela instrução de Modificar Controlos de Função PCI da FIG. 6A, de acordo com um aspeto da presente invenção;

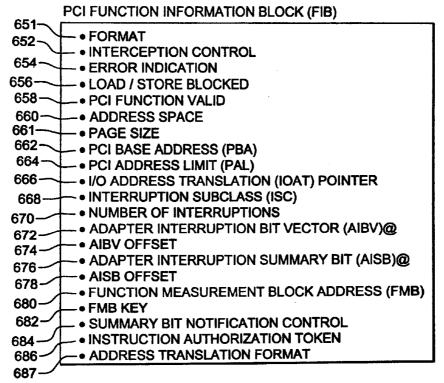

A FIG. 6D representa uma forma de realização dos conteúdos de um bloco de informação de função (Function Information Block - FIB) utilizado de acordo com um aspeto da presente invenção;

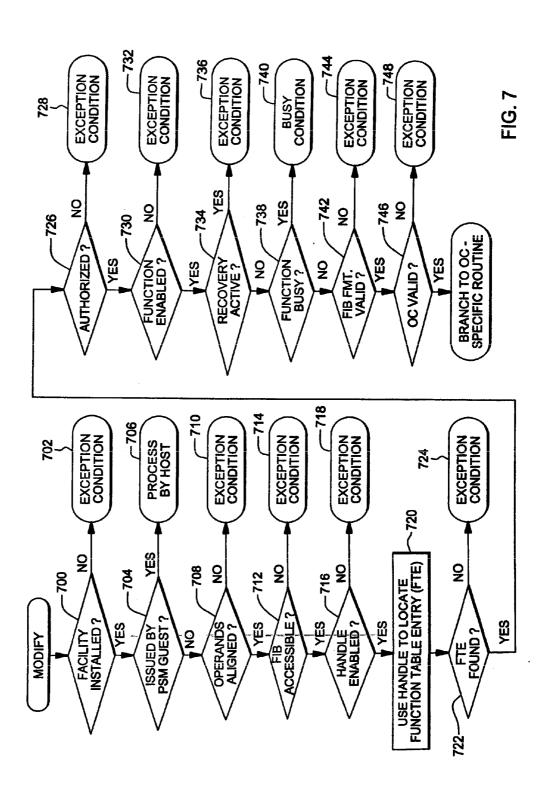

A FIG. 7 representa uma forma de realização de uma visão geral da lógica da instrução Modificar Controlos

de Função PCI, de acordo com um aspeto da presente invenção;

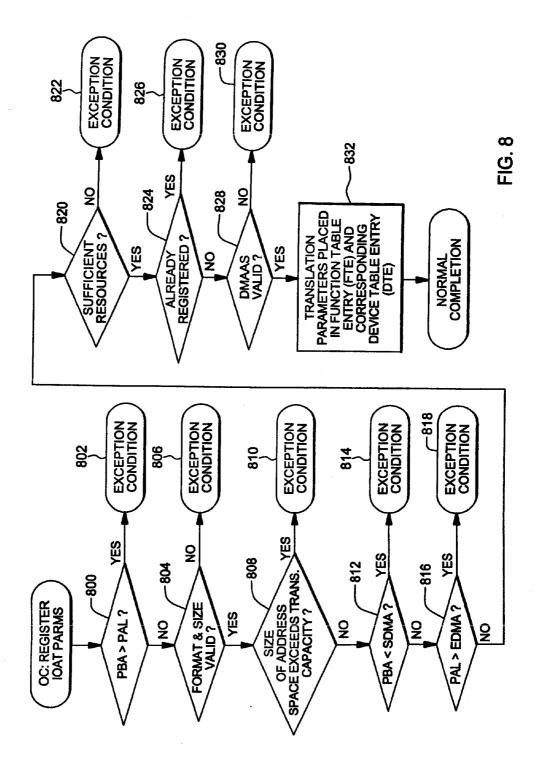

A FIG. 8 representa uma forma de realização da lógica associada a uma operação de registo de parâmetros de tradução de endereços de I/O que pode ser especificada por meio da instrução Modificar Controlos de Função PCI, de acordo com um aspeto da presente invenção;

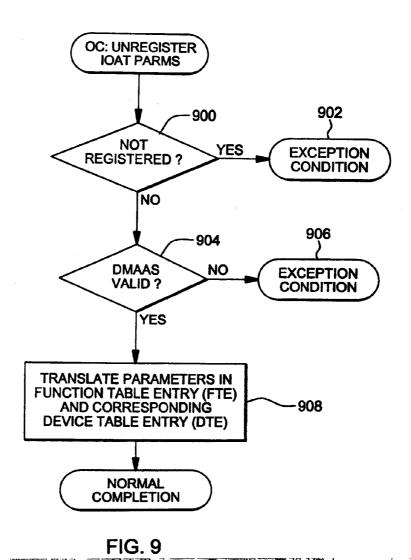

A FIG. 9 representa uma forma de realização da lógica associada a uma operação de cancelamento do registo de parâmetros de tradução de endereços de I/O que pode ser especificada pela instrução Modificar Controlos de Função PCI, de acordo com um aspeto da presente invenção;

A FIG. 10 representa uma forma de realização de um produto de programa de computador que incorpora um ou mais aspetos da presente invenção;

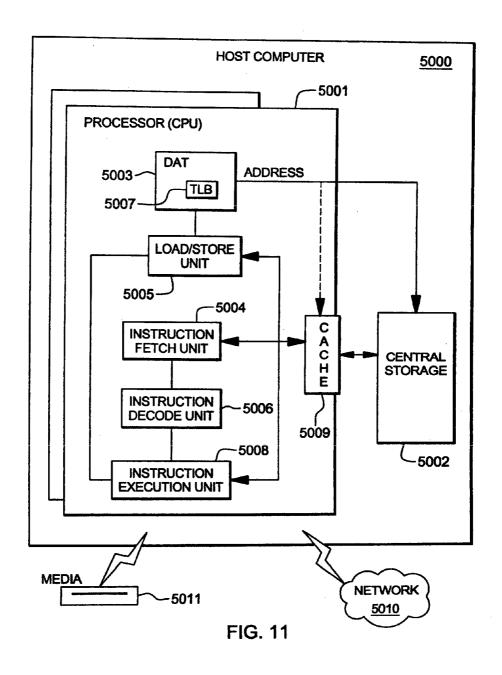

A FIG. 11 representa uma forma de realização de um sistema informático anfitrião (host) para incorporar e utilizar um ou mais aspetos da presente invenção;

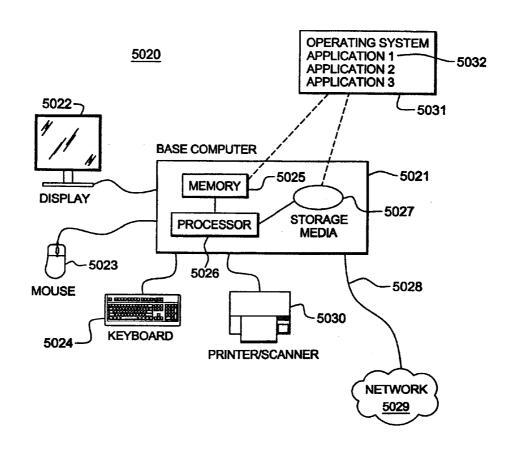

A FIG. 12 representa um exemplo adicional de um sistema informático para incorporar e utilizar um ou mais aspetos da presente invenção;

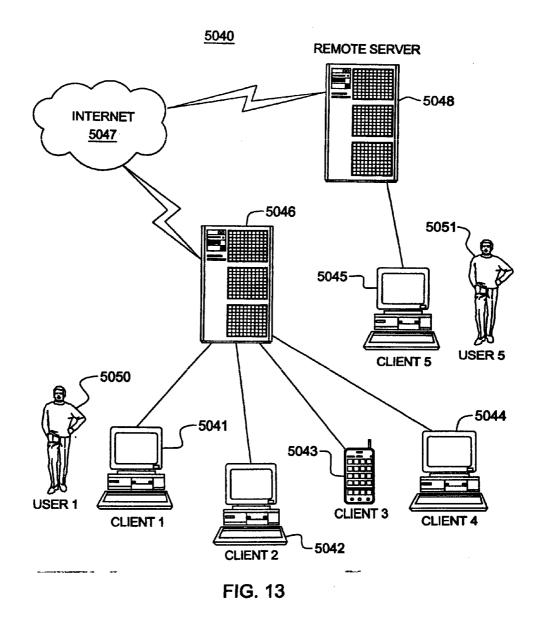

A FIG. 13 representa um outro exemplo de um sistema informático compreendendo uma rede de computadores

para incorporar e utilizar um ou mais aspetos da presente invenção;

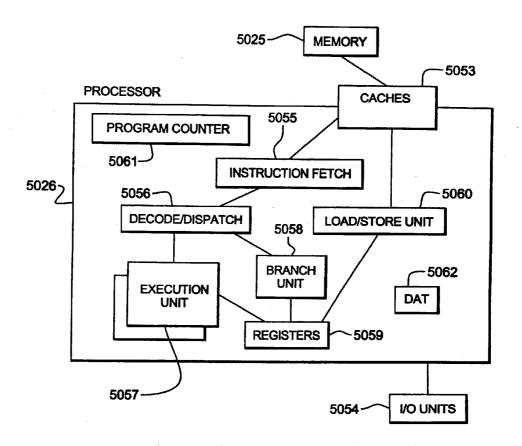

A FIG. 14 representa uma forma de realização de vários elementos de um sistema informático para incorporar e utilizar um ou mais aspetos da presente invenção;

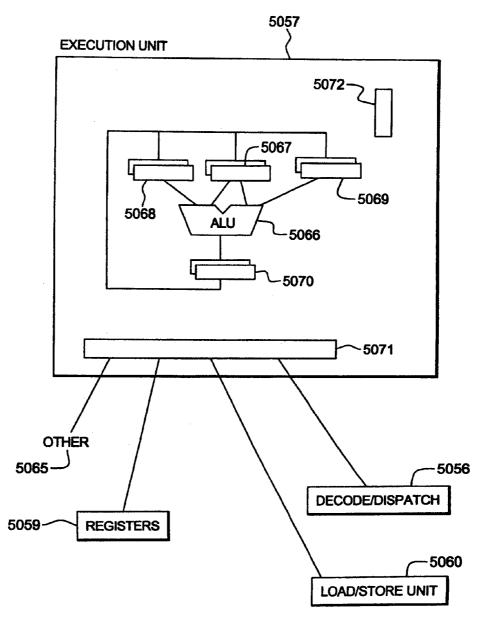

A FIG. 15A representa uma forma de realização da unidade de execução do sistema informático da FIG. 14 para incorporar e utilizar um ou mais aspetos da presente invenção;

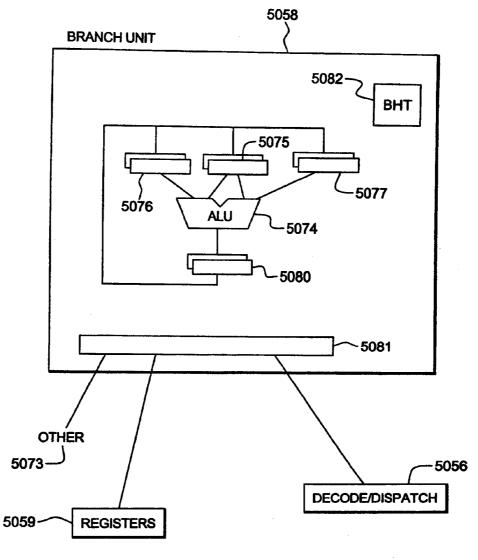

A FIG. 15B representa uma forma de realização da unidade de ramificação do sistema informático da FIG. 14 para incorporar e utilizar um ou mais aspetos da presente invenção;

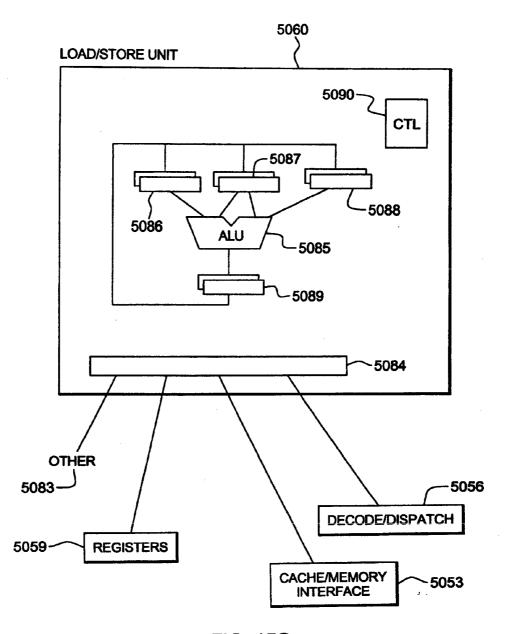

A FIG. 15C representa uma forma de realização da unidade de carga/armazenamento do sistema informático da FIG. 14 para incorporar e utilizar um ou mais aspetos da presente invenção; e

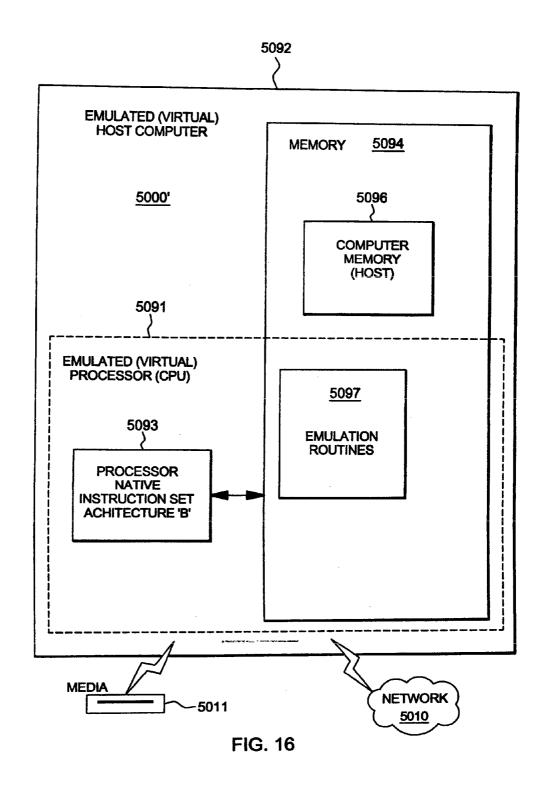

A FIG. 16 representa uma forma de realização de um sistema informático *host* emulado para incorporar e utilizar um ou mais aspetos da presente invenção.

## DESCRIÇÃO DETALHADA

De acordo com um aspeto da presente invenção, é

fornecida uma capacidade para traduzir endereços num ambiente informático. Num exemplo, os endereços a serem traduzidos são endereços fornecidos por um adaptador (aqui referido como endereços de entrada/saída (Input/Output - I/O), que irão ser traduzidos para endereços utilizáveis no acesso à memória de sistema. Para realizar a tradução de endereços, um número de níveis de tradução de endereços é utilizado, e o número de níveis baseia-se, por exemplo, no tamanho do espaço de endereçamento de memória atribuído ao adaptador, um tamanho de uma ou mais tabelas de tradução de endereços utilizadas na tradução, e/ou um tamanho da página (ou outra unidade de memória), a ser acedida.

O endereço a ser traduzido inclui uma pluralidade de bits, e numa forma de realização, apenas uma porção dos referidos bits é utilizada para indexar nas tabelas de tradução de endereços para obter o endereço traduzido. Os outros bits são ignorados para tradução. Por exemplo, o endereço inclui bits de ordem superior e bits de ordem inferior (de acordo com tamanho do 0 espaço endereçamento atribuído). Neste exemplo, os bits de ordem são utilizados para inferior indexar nas tabelas tradução de endereços, incluindo a tabela de páginas, e para indexar na própria página. Os bits de ordem superior (independentemente do valor, ou seja, zero ou diferente de zero) são ignorados para tradução e não são utilizados para indexar nas tabelas de tradução de endereços. Isto reduz o número de níveis de tabelas de tradução utilizados para traduzir os endereços. (A indicação de bits de ordem inferior e de ordem superior é independente da forma como os bits são numerados).

Num exemplo, a tradução é realizada, proporcionando ao mesmo tempo proteção adequada para um servidor da classe enterprise, tal como um servidor System  $z^{\circ}$ . Como exemplo, um endereço completo (por exemplo, a totalidade do endereço de 64 bits) é utilizado no acesso à memória, no entanto, apenas uma porção do endereço é utilizada para tradução. Uma outra porção do endereço, que é ignorada para tradução, é utilizada para validação (por exemplo, uma verificação de intervalo), juntamente com pelo menos uma porção do endereço utilizada para tradução. Ao ser utilizada apenas uma porção do endereço para tradução, as pesquisas de tradução de endereços são minimizadas. Isto é conseguido através da realização de um número de níveis de tradução, com base por exemplo no tamanho do espaço de endereçamento DMA registado para acesso pelo adaptador, em vez do tamanho do próprio endereço.

Uma forma de realização de um ambiente informático para incorporar e utilizar um ou mais aspetos da presente invenção é descrito com referência à FIG. 1. Num exemplo, um ambiente informático 100 é um servidor System z® proposto pela International Business Machines Corporation. O System z® é baseado na z/Architecture® proposta pela International Business Machines Corporation. Detalhes sobre a z/Architecture® são descritos numa publicação da IBM® intitulada, "z/Architecture Principles

of Operation" Publicação IBM No. SA22-7832-07, fevereiro de 2009. IBM®, System z® e z/Architecture® são marcas comerciais registadas da International Business Machines Corporation, Armonk, Nova Iorque. Outros nomes aqui utilizados podem ser marcas registadas, marcas comerciais ou nomes de produtos da International Business Machines Corporation ou de outras empresas.

Num exemplo, o ambiente informático 100 inclui uma ou mais unidades centrais de processamento (CPUs) 102 acopladas a uma memória de sistema 104 (também conhecida como memória principal) por meio de um controlador de memória 106. Para aceder à memória de sistema 104, uma unidade central de processamento 102 emite um pedido de leitura ou de escrita que inclui um endereço utilizado para aceder à memória de sistema. O endereço incluído no pedido normalmente não é utilizável diretamente para aceder à memória de sistema, e portanto é traduzido para um endereço que pode ser utilizado diretamente no acesso à memória de sistema. O endereço é traduzido através de um mecanismo de tradução (XLATE) 108. Por exemplo, o endereço é traduzido a partir de um endereço virtual para um endereço real ou absoluta utilizando, por exemplo, tradução de endereço dinâmica (Dynamic Address Translation - DAT).

O pedido, incluindo o endereço traduzido, é recebido pelo controlador de memória 106. Num exemplo, o controlador de memória 106 é constituído por *hardware* e é utilizado para arbitrar o acesso à memória de sistema e

para manter a consistência da memória. Esta arbitragem é realizada para pedidos recebidos a partir dos CPUs 102, bem como para pedidos recebidos a partir de um ou mais adaptadores 110. Tal como as unidades centrais de processamento, os adaptadores emitem pedidos para a memória de sistema 104 para obter acesso à memória de sistema.

Num exemplo, o adaptador 110 é um adaptador de Interconexão de Componentes Periféricos (Peripheral Component Interconnect - PCI) ou PCI Express (PCIe), que inclui uma ou mais funções PCI. Uma função PCI emite um pedido que requer acesso à memória de sistema. O pedido é encaminhado para um concentrador (hub) de entrada/saída 112 (por exemplo, um hub PCI) através de um ou mais comutadores (switches) (por exemplo, switches PCIe) 114. Num exemplo, o hub de entrada/saída é constituído por hardware, incluindo uma ou mais máquinas de estado.

Tal como aqui utilizado, o termo adaptador inclui qualquer tipo de adaptador (por exemplo, um adaptador de armazenamento, adaptador de rede, adaptador de processamento, adaptador PCI, adaptador criptográfico, outro tipo de adaptadores de entrada/saída, etc.). Numa forma de realização, um adaptador inclui uma função de adaptador. No entanto, em outras formas de realização, um adaptador pode incluir uma pluralidade de funções de adaptador. Um ou mais aspetos da presente invenção são aplicáveis se um adaptador incluir uma função de adaptador ou uma pluralidade de funções de adaptador. Além disso, nos exemplos aqui apresentados, o adaptador é utilizado de forma intercambiável com função de adaptador (por exemplo, função PCI), a menos que seja indicado de forma diferente.

O hub de entrada/saída inclui, por exemplo, um complexo de raíz 116 que recebe o pedido de um comutador (switch). O pedido inclui um endereço de entrada/saída a ser traduzido e, por conseguinte, o complexo de raíz fornece o endereço para uma unidade de tradução de endereços e de proteção 118. Esta unidade é, por exemplo, uma unidade de hardware que traduz o endereço de I/O para um endereço diretamente utilizável para aceder à memória de sistema 104, tal como descrito em maior detalhe abaixo.

O pedido iniciado a partir do adaptador, incluindo o endereço traduzido, é fornecido ao controlador de memória 106 através de, por exemplo, um bus de I/O-paramemória 120. O controlador de memória realiza a sua arbitragem e encaminha o pedido com o endereço traduzido para a memória de sistema no momento apropriado.

Detalhes adicionais relativos à memória de sistema e ao hub de entrada/saída são descritos com referência à FIG. 2. Nesta forma de realização, o controlador de memória não é mostrado. No entanto, o hub de I/O pode ser acoplado à memória de sistema diretamente ou através de um controlador de memória. Num exemplo, a memória de sistema 104 inclui um ou mais espaços de endereçamento 200. Um espaço de endereçamento é uma porção

particular de memória de sistema que foi atribuída a um determinado componente do ambiente informático, tal como um adaptador específico. Num exemplo, o espaço de endereçamento é acessível por acesso direto à memória (Direct Memory Access - DMA), iniciado pelo adaptador, e portanto, o espaço de endereçamento é referido nos exemplos aqui como um espaço de endereçamento DMA. No entanto, noutros exemplos, o acesso direto à memória não é utilizado para aceder ao espaço de endereçamento.

Além disso, num exemplo, a memória de sistema 104 inclui tabelas de tradução de endereços 202 utilizadas para traduzir um endereço a partir de um que não é diretamente utilizável para aceder à memória de sistema para um endereço que é diretamente utilizável. Numa forma de realização, existe uma ou mais tabelas de tradução de endereços atribuídas a um espaço de endereçamento DMA, e essas uma ou mais tabelas de tradução de endereços são configuradas com base, por exemplo, no tamanho do espaço de endereçamento para o qual estão atribuídas, no tamanho das próprias tabelas de endereços de tradução, e/ou no tamanho da página (ou outra unidade de memória).

Num exemplo, existe uma hierarquia de tabelas de tradução de endereços. Por exemplo, tal como mostrado na FIG. 2, existe uma tabela de primeiro nível 202a (por exemplo, uma tabela de segmentos) apontada por um apontador IOAT 218 (descrito abaixo), e uma segunda tabela de nível inferior 202b (por exemplo, uma tabela de páginas) apontada

por uma entrada 206a da tabela de primeiro nível. Um ou mais bits de um endereço recebido 204 são utilizados para na tabela 202a para localizar uma determinada entrada 206a, o que indica uma determinada tabela de nível inferior 202b. Em seguida, um ou mais bits do endereço 204 são utilizados para localizar uma determinada entrada 206b nessa tabela. Neste exemplo, essa entrada fornece endereço utilizado para localizar a página correta e bits adicionais no endereço 204 são utilizados para localizar uma determinada localização 208 na página para realizar uma transferência de dados. Ou seja, o endereço na entrada 206b e os bits selecionados do endereço PCI 204 recebido são utilizados para fornecer o endereço diretamente utilizável para aceder à memória de sistema. Por exemplo, o endereço diretamente utilizável é formado а partir de concatenação de bits de ordem superior do endereço na entrada 206b (por exemplo, os bits 63:12, num exemplo de página com 4k) e os bits de ordem inferior selecionados a partir do endereço PCI recebido (por exemplo, bits 11:0 para uma página com 4k).

Num exemplo, é um sistema operativo que atribui um espaço de endereçamento DMA a um determinado adaptador. Esta atribuição é realizada através de um processo de registo, o que provoca uma inicialização (através de, por exemplo, software de confiança), de uma entrada de tabela 210 de um dispositivo para esse adaptador. A entrada de tabela do dispositivo está localizada numa tabela de dispositivo 211 localizada no hub de I/O 112. Por exemplo,

a tabela de dispositivo 211 está localizada dentro da unidade de tradução de endereços e de proteção do *hub* de I/O.

Num exemplo, a entrada de tabela do dispositivo 210 inclui um número de campos, tais como os seguintes:

Formato 212: Este campo inclui uma pluralidade de bits para indicar várias informações, incluindo, por exemplo, o formato de tradução de endereços (incluindo o nível) de uma tabela de nível superior das tabelas de tradução de endereços (por exemplo, no exemplo acima, a tabela de primeiro nível);

Tamanho da Página 213: Este campo indica o tamanho de uma página (ou outra unidade de memória) a ser acedida;

Endereço base PCI 214 e limite PCI 216: Estes valores fornecem um intervalo utilizado para definir um espaço de endereçamento DMA e verificar se um endereço recebido (por exemplo, um endereço PCI) é válido; e

Apontador IOAT (Input/Output Address Translation - Tradução de Endereços de Entrada/Saída) 218: Este campo inclui um apontador para o nível mais elevado da tabela de tradução de endereços utilizada para o espaço de endereçamento DMA.

Noutras formas de realização, a DTE pode incluir mais, menos ou diferente informação.

Numa forma de realização, a entrada de tabela de dispositivo a ser utilizada numa tradução específica está localizada utilizando um identificador solicitante (Requestor Identifier - RID), localizado num pedido emitido por uma função PCI 220 associada com um adaptador (e/ou por uma porção do endereço). O id do solicitante (por exemplo, um valor de 16 bits especificando, por exemplo, um número de bus, número de dispositivo e número de função) está incluído no pedido, bem como o endereço de I/O exemplo, um endereço PCIe de 64 bits) a ser utilizado para aceder à memória de sistema. O pedido, incluindo o RID e o endereço de I/O, são fornecidos para, por exemplo, uma conteúdo endereçável (Contents Addressable memória de Memory - CAM) 230 através de, por exemplo, um comutador (switch) 114, que é utilizado para proporcionar um valor de índice. Por exemplo, a CAM inclui múltiplas entradas, com cada entrada correspondente a um índice de tabela de dispositivo. Cada entrada CAM inclui o valor de um RID. Se, por exemplo, o RID recebido corresponde ao valor contido numa entrada na CAM, o índice da tabela de dispositivo correspondente é utilizado para localizar a entrada de tabela de dispositivo. Isto é, a saída da CAM é utilizada para indexar na tabela de dispositivo 211 para localizar a entrada de tabela de dispositivo 210. Se não existe correspondência, o pacote recebido é descartado, realização de acesso à memória de sistema. (Noutras formas de realização, uma CAM ou outra pesquisa não é necessária e o RID é utilizado como índice.)

Subsequentemente, os campos dentro da entrada de tabela de dispositivo são utilizados para garantir a validade do endereço e a configuração das tabelas de tradução de endereços. Por exemplo, o endereço de entrada no pedido é verificado pelo hardware do hub de I/O (por exemplo, a unidade de tradução de endereços e de proteção) para garantir que está dentro dos limites definidos pelo endereço base PCI 214 e pelo limite PCI 216 armazenados na entrada de tabela de dispositivo localizados utilizando o RID do pedido que forneceu o endereço. Isto assegura que o endereço está dentro do intervalo previamente registado e para o qual as tabelas de tradução de endereços estão validamente configuradas.

De acordo com um aspeto da presente invenção, numa forma de realização, para traduzir um endereço de I/O (isto é, um endereço fornecido por um adaptador ou outro componente de um subsistema de I/O) para um endereço de memória de sistema (isto é, um endereço diretamente utilizável para aceder à memória de sistema), inicialmente, um processo de registo é realizado. Este processo de registo regista um determinado espaço de endereçamento com um solicitante específico, tal como um adaptador ou função de adaptador específico. Um exemplo de uma vista geral deste processo de registo é descrito com referência à FIG. 3A.

Inicialmente, um sistema operativo em execução dentro de uma das unidades centrais de processamento acopladas à memória de sistema determina o tamanho e localização do espaço de endereçamento a que o adaptador deve aceder, ETAPA 300. Num exemplo, o tamanho do espaço de endereçamento é determinado pelo endereço base PCI e limite PCI definidos pelo sistema operativo. O sistema operativo a base e o limite utilizando determina um 011 critérios. Por exemplo, se o sistema operativo deseja que endereços PCI mapeiem diretamente para endereços virtuais de CPU, então a base e o limite são definidos como tal. Num outro exemplo, se é desejado um isolamento adaptadores e/ou imagens do adicional entre sistema operativo, então os endereços a serem utilizados são selecionados para fornecer espaços de endereçamento não disjuntos. A localização sobrepostos e também especificada pelo sistema operativo, e baseia-se, por exemplo, nas características do adaptador.

A partir daí, uma ou mais tabelas de tradução de endereços são criadas para cobrir esse espaço de endereçamento DMA, ETAPA 302. Como exemplos, as tabelas podem ser compatíveis com as tabelas de tradução de endereços de CPU ou um formato único pode ser fornecido que é suportado pelo hub de entrada/saída. Num exemplo, a criação inclui a construção das tabelas e a colocação dos endereços apropriados dentro das entradas das tabelas. Como exemplo, uma das tabelas de tradução é uma tabela de página com 4k tendo 512 entradas de 64 bits, e cada entrada inclui

um endereço de página de 4k compatível com o espaço de endereçamento atribuído.

Em seguida, o espaço de endereçamento DMA é registado para o adaptador, ETAPA 304, tal como descrito em maior detalhe com referência à FIG. 3B. Neste exemplo, é assumido que existe uma função PCI por adaptador, e portanto, um ID de solicitante por adaptador. Esta lógica é realizada, por exemplo, por uma unidade central de processamento ligada à memória de sistema, que responde a um pedido do sistema operativo.

Inicialmente, numa forma de realização, uma entrada de tabela de dispositivo disponível é selecionada por forma a corresponder ao ID do solicitante do adaptador, ETAPA 310. Isto é, o ID do solicitante irá ser utilizado para localizar uma entrada de tabela de dispositivo.

Além disso, o endereço base PCI e o limite PCI são armazenados na entrada de tabela de dispositivo, ETAPA 312. Além disso, o formato da tabela de tradução de endereços de nível mais elevado é também armazenado na entrada de tabela de dispositivo (por exemplo, o campo de formato), ETAPA 314, bem como o apontador de tradução de endereços de entrada/saída (Input/Output Address Translation - IOAT) utilizado para apontar para a tabela de tradução de endereços de nível mais elevado, ETAPA 316. Isto conclui o processo de registo.

Responsivo para realizar o registo, um espaço de endereçamento DMA e as tabelas de tradução de endereços correspondentes estão prontos para utilização, assim como uma entrada de tabela de dispositivo. Os detalhes sobre o processamento de um pedido emitido por um solicitante, tal como um adaptador, para aceder à memória de sistema são descritos com referência à FIG. 4. O processamento descrito abaixo é realizado pelo hub de I/O. Num exemplo, é a unidade de tradução de endereços e de proteção que realiza a lógica. Numa forma de realização, inicialmente, um pedido de DMA é recebido no hub de entrada/saída, ETAPA 400. Por exemplo, uma função PCI emite um pedido que é encaminhado para o hub PCI via, por exemplo, um switch PCI. Utilizando o ID solicitante no pedido, a entrada de tabela dispositivo apropriada é localizada, ETAPA 402. disso, é feita uma determinação sobre se a entrada de tabela de dispositivo é válida, PESQUISA 404. Num exemplo, a validade é determinada pela verificação de um bit de validade na própria entrada. Este bit é definido, por exemplo, em resposta à execução de um pedido de função de ativação pelo sistema operativo. Se ativado, o bit é definido como, por exemplo, um (ou seja, válido); caso contrário, ele permanece como zero (ou seja, inválido). Num outro exemplo, o bit pode ser definido quando o processo de registo está completo. Se entrada na tabela а dispositivo é inválida, é apresentado um erro, ETAPA 405. Caso contrário, uma determinação adicional é feita sobre se o endereço PCI fornecido no pedido é menor do que o endereço base PCI armazenado na entrada de tabela de dispositivo, PESQUISA 406. Se for, então o endereço está fora de um intervalo válido e é fornecido um erro, ETAPA 407. No entanto, se o endereço PCI é maior ou igual do que o endereço base, então uma é feita outra determinação sobre se o endereço PCI é maior do que o valor limite PCI na entrada de tabela de dispositivo, PESQUISA 408. Se o endereço PCI é maior do que o limite, então mais uma vez, é apresentado um erro uma vez que o endereço está fora do intervalo válido, ETAPA 409. No entanto, se o endereço está dentro de um intervalo válido, então o processamento continua.

Num exemplo, o formato fornecido na entrada da tabela do dispositivo é utilizado para determinar os bits de endereço PCI no endereço a ser utilizado para a tradução de endereços, ETAPA 410. Por exemplo, se o formato indica que a tabela de nível superior é uma tabela de primeiro nível com páginas de 4k, então os bits 29:21 do endereço são utilizados para indexar na tabela de primeiro nível; os bits 20:12 são utilizados para indexar na tabela de página; e os bits 11:0 são utilizados para indexar na página de 4k. Os bits utilizados dependem de quantos bits são necessários para indexar na página ou tabela de tamanho determinado. Por exemplo, para uma página de 4k com endereçamento de nível de byte, 12 bits são utilizados para endereçar 4096 bytes; e para uma tabela de página de 4k com 512 entradas, de 8 bytes cada, 9 bits são utilizados para endereçar 512 entradas, etc.

Em seguida, o hub PCI pesquisa a entrada da tabela de tradução de endereços apropriada, ETAPA 412. Por exemplo, inicialmente, a tabela de tradução de nível mais elevado é localizada utilizando o apontador IOAT da entrada de tabela de dispositivo. Então, os bits do endereço (aqueles após os bits de ordem superior utilizados para validade e não tradução; por exemplo, os bits 29:21 no exemplo acima) são utilizados para localizar a entrada específica dentro dessa tabela.

Uma determinação é então feita com base, por exemplo, no formato fornecido na entrada de tabela de dispositivo, sobre se a entrada de tradução de endereços localizada tem um formato correto, PESQUISA 414. Por exemplo, o formato na entrada de tabela de dispositivo é comparado com um formato indicado na entrada de tradução de endereços. Se for igual, então o formato na entrada de tabela de dispositivo é válido. Se não, é fornecido um erro, ETAPA 415; caso contrário, o processamento continua com a determinação sobre se esta é a última tabela a ser processada, PESQUISA 416. Ou seja, uma determinação é feita sobre se existem outras tabelas de tradução de endereços necessárias para obter o endereço real ou absoluto, ou se a entrada da tabela de nível mais baixo foi localizada. Esta determinação é feita com base no formato e tamanho fornecidos das tabelas que já foram processadas. Se não for a última tabela, então o processamento continua com a ETAPA 412. Caso contrário, o hub de I/O continua o processamento para permitir uma pesquisa ou armazenamento dos dados no endereço traduzido, ETAPA 418. Num exemplo, o hub de I/O encaminha o endereço traduzido para o controlador de memória, o qual utiliza o endereço para pesquisar ou armazenar dados na localização DMA designada pelo endereço traduzido.

Conforme descrito acima, de acordo com um aspeto da presente invenção, o número de níveis de tradução e, portanto, o número de pesquisas necessárias para realizar a tradução são reduzidos. Isto é conseguido, por exemplo, ignorando os bits de ordem superior de um endereço durante a tradução e utilizando apenas os bits de ordem inferior para atravessar as tabelas de tradução, que se baseiam, por exemplo, no tamanho do espaço de endereçamento DMA atribuído ao adaptador. A utilização de um endereço parcial versus o endereço completo é mostrada adicionalmente nos exemplos seguintes.

Com referência inicialmente à FIG. 5A, é representado um exemplo em que o endereço inteiro é utilizado na tradução de endereços/acesso à memória. Com esta técnica anterior, são necessários seis níveis de tabelas de tradução, incluindo a tabela de página. O início da tabela de nível mais elevado (por exemplo, a tabela de nível 5, neste exemplo) é apontado por um apontador IOAT, e então os bits do endereço PCI são utilizados para localizar uma entrada na tabela. Cada entrada da tabela de tradução aponta para o início de uma tabela de tradução de nível inferior ou para uma página (por exemplo, uma entrada na

tabela de nível 5 aponta para o início de uma tabela de nível 4, etc.).

Neste exemplo, o espaço de endereçamento DMA (DMAAS) tem 6M em tamanho, e cada tabela tem 4k bytes com um máximo de 512 entradas de 8 bytes (com exceção da tabela de nível 5, que tem 128 entradas baseadas no tamanho do endereço). O endereço tem, por exemplo, 64 bits: FFFF C000 0009 C600. O início da tabela de nível 5 é apontado pelo IOAT e os bits 63:57 do endereço PCI são apontador utilizados para indexar na tabela de nível 5 para localizar o início da tabela de nível 4; os bits 56:48 do endereço PCI são utilizados para indexar na tabela de nível 4 para localizar o início da tabela de nível 3; os bits 47:39 são utilizados para indexar na tabela de nível 3 para localizar o início da tabela de nível 2; os bits 38:30 são utilizados para indexar na tabela de nível 2 para localizar o início da tabela de nível 1; os bits 29:21 são utilizados para indexar na tabela de nível 1 para localizar o início da tabela de página; os bits 20:12 são utilizados para indexar na tabela de página para localizar o início da página; e os bits 11:0 são utilizados para localizar a entrada na página de 4k. Assim, neste exemplo, todos os bits de endereço são utilizados para tradução/acesso.

Isto está em contraste com o exemplo na FIG. 5B, na qual o espaço de endereçamento é do mesmo tamanho (por exemplo 6M) e o endereço é a mesmo, mas a técnica de tradução ignora alguns dos *bits* de endereço durante a

tradução. Neste exemplo, os bits 63:30 do endereço são ignorados para tradução. O apontador IOAT aponta para o início da tabela de nível 1 e os bits 29:21 do endereço PCI são utilizados para indexar na tabela de nível 1 para localizar o início da tabela de página; os bits 20:12 são utilizados para indexar na tabela de página apropriada para localizar o início da página; e os bits 11:0 são utilizados para indexar na página de 4k.

Tal como mostrado, a tabela de nível 1 500 inclui três entradas 502, cada uma fornecendo um endereço a uma das três tabelas de página 504. O número de tabelas de página necessárias, e portanto, o número de tabelas de outros níveis, depende, por exemplo, do tamanho do espaço de endereçamento DMA, do tamanho das tabelas de tradução, e/ou do tamanho das páginas. Neste exemplo, o espaço de endereçamento DMA tem 6M, e cada tabela de página tem 4k, tendo até 512 entradas. Portanto, cada tabela de página pode mapear até 2M de memória (4k x 512 entradas). Assim, três tabelas de página são necessárias para o espaço de endereçamento de 6M. A tabela de nível 1 é capaz de armazenar as três entradas, uma para cada tabela de página, e assim, não são necessários mais níveis de tabelas de tradução de endereços, neste exemplo.

Numa outra forma de realização, podem existir diferentes formatos de tabelas de tradução de endereços utilizados para tradução de endereços, e podem existir variações entre os formatos. Assim, existem variações nos

bits utilizados para indexar numa determinada tabela ou página. Alguns destes exemplos são descritos com referência às FIGs. 5C e 5D.

Por exemplo, um formato é um formato compatível com CPU DAT no qual as tabelas de tradução são compatíveis com as tabelas de tradução utilizadas para traduções CPU DAT. Podem existir vários formatos compatíveis com CPU DAT, exemplos dos quais são descritos com referência à FIG. 5C. Tal como mostrado, um formato compatível com CPU DAT é um formato compatível com CPU DAT com uma página de 4k 550, e outro é um formato compatível com CPU DAT com uma página de 1M 552, como exemplos. O número de bits mostrados são o número de bits de endereço utilizados para indexar nessa página ou tabela (ou de outro modo localizar uma entrada na referida página ou tabela). Por exemplo, 12 bits 554 de um endereço PCI são utilizados como um deslocamento de byte numa página de 4k 556, 8 bits 558 são utilizados como um índice para uma tabela de página 560, 11 bits 562 são utilizados como um índice para uma tabela de segmento 564, etc. Localizado sob a tabela de tradução de endereços designada está o tamanho máximo do espaço de endereçamento suportado por essa tabela de tradução de endereços. Por exemplo, a tabela de página 560 suporta um espaço de endereçamento DMA de 1M; a tabela de segmento 564 suporta um espaço de endereçamento DMA de 2G, etc. Nesta figura, bem como na FIG. 5D, K = kilobytes, M = megabytes, G =gigabytes, T = terabytes, P = petabytes e E = exabytes.

Tal como representado, à medida que o tamanho da página aumenta, o número de níveis das tabelas de tradução diminui.Por exemplo, para a página de 4k 556, é necessária uma tabela de página, mas não é necessária para a página de 1M. Outros exemplos e variações são possíveis.

Outro formato de tradução de endereços é um formato de tradução de endereços estendido de I/O em que as tabelas de tradução de endereços estendidas são utilizadas. Vários exemplos de formatos de tradução de endereços estendidos de I/O estão representados na FIG. 5D. Por exemplo, os seguintes formatos são mostrados: uma tabela de tradução de endereços de 4k com páginas de 4k 570; tabelas de tradução de endereços de 1M com páginas de 4k 572; e tabelas de tradução de endereços de 1M com páginas de 1M 574. Tal como acontece com os formatos compatíveis com CPU DAT, o número de bits listados são os bits utilizados para localizar uma entrada na tabela específica. Por exemplo, no número de referência 576, os 12 bits são um deslocamento na página de 4k. Do mesmo modo, no número de referência 578, os 9 bits são utilizados para indexar numa tabela de página de I/O. Esta tabela de página de I/O permite um espaço de endereçamento DMA que tenha um tamanho de 2M. Existem muitos outros exemplos.

Numa implementação específica, para realizar o registo de um espaço de endereçamento DMA para o adaptador, uma instrução referida como uma instrução Modificar Controlos de Função PCI (Modify PCI Function Controls -

MPFC), é utilizada. Por exemplo, o sistema operativo determina qual o formato de tradução de endereços que pretende utilizar, constrói as tabelas de tradução de endereços para esse formato, e em seguida emite a instrução MPFC com esse formato incluído como um operando da instrução. Num exemplo, o formato e outros operandos da instrução são incluídos num bloco de informação de função (descrito abaixo), que é um operando da instrução. O bloco de informação de função é depois utilizado para atualizar a DTE e, numa forma de realização, opcionalmente, uma entrada de tabela de função (Function Table Entry - FTE) que inclui parâmetros operacionais do adaptador.

Uma forma de realização dos detalhes relacionados com esta instrução, e em particular o processo de registo, é descrita com referência às FIGs. 6A-9. Com referência à FIG. 6A, uma instrução Modificar Controlos de Função PCI 600 inclui, por exemplo, um código de operação 602 indicando a instrução Modificar Controlos de Função PCI; um primeiro campo 604 especificando uma localização onde várias informações estão incluídas em relação à função de adaptador para a qual os parâmetros operacionais estão a ser estabelecidos; e um segundo campo 606 especificando uma localização a partir da qual um bloco de informação de função PCI (Function Information Block - FIB) é pesquisado. Os conteúdos das localizações designadas por Campos 1 e 2 encontram-se adicionalmente descritos abaixo.

Numa forma de realização, o Campo 1 designa um

registo geral que inclui uma variedade de informação. Tal como mostrado na FIG. 6B, os conteúdos do registo incluem, por exemplo, um manípulo (handle) de função 610 que identifica a handle da função de adaptador em nome da qual a instrução de modificar está a ser realizada; um espaço de endereçamento 612 designando um espaço de endereçamento na memória de sistema associado com a função de adaptador designada pela handle da função; um controlo de operação 614 que especifica a operação a ser realizada para a função de adaptador; e estado 616 que fornece o estado relacionado com a instrução quando a instrução termina com um código predefinido.

Numa forma de realização, a handle da função inclui, por exemplo, um indicador de ativação indicando se a handle foi ativada, um número de função que identifica uma função de adaptador (este é um identificador estático e pode ser utilizado para indexar numa tabela de função); e um número de instância especificando a instância específica desta handle de função. Existe uma handle de função para cada função de adaptador, e é utilizada para localizar uma entrada de tabela de função (Function Table Entry - FTE) dentro da tabela de função. Cada entrada de tabela de parâmetros operacionais função inclui e/ou outras informações associadas com a sua função de adaptador. Como exemplo, uma entrada de tabela de função inclui:

Número de Instância: Este campo indica uma instância específica da *handle* de função de adaptador

associada com a entrada de tabela de função;

Índice 1...n da Entrada de Tabela de Dispositivo Table Entry - DTE): Podem existir um ou mais índices de tabela de dispositivo, e cada índice é um índice para uma tabela de dispositivo para localizar uma entrada de tabela de dispositivo (DTE). Existem uma ou mais entradas de tabela de dispositivo por cada função de adaptador, e cada entrada inclui informação associada à sua função de adaptador, incluindo informação utilizada para processar os pedidos da função de adaptador (por exemplo, pedidos de DMA, pedidos de MSI) e informação referente a pedidos relacionados com a função de adaptador (por exemplo, instruções PCI). Cada entrada de tabela dispositivo está associada com um espaço de endereçamento na memória de sistema atribuída à função de adaptador. Uma função de adaptador pode ter um ou mais espaços de endereçamento dentro da memória de sistema atribuída à função de adaptador.

Indicador de Ocupado (Busy): Este campo indica se a função de adaptador está ocupada;

Indicador de Estado de Erro Permanente: Este campo indica se a função de adaptador está em num estado de erro permanente;

Indicador de Recuperação Iniciada: Este campo indica se a recuperação foi iniciada para a função de

adaptador;

Indicador de Permissão: Este campo indica se o sistema operativo que tenta controlar a função de adaptador tem autorização para fazê-lo;

Indicador de Ativação: Este campo indica se a função de adaptador está ativada (por exemplo, l = ativada, 0 = desativada);

Identificador do Solicitante (Requestor Identifier - RID): Este é um identificador da função de adaptador, e inclui, por exemplo, um número de bus, um número de dispositivo e um número de função.

Num exemplo, este campo é utilizado para acessos de um espaço de configuração da função de adaptador. (Memória de um adaptador pode ser definida como espaços de endereçamento, incluindo, por exemplo, um espaço de configuração, um espaço de I/O e/ou um ou mais espaços de memória.). Num exemplo, o espaço de configuração pode ser acedido através da especificação do espaço de configuração numa instrução emitida pelo sistema operativo (ou outra configuração) para a função de adaptador. Especificado na instrução está um deslocamento no espaço de configuração e uma handle de função utilizada para localizar a entrada de tabela de função apropriada que inclui o RID. O firmware recebe a instrução e determina se é para um espaço de configuração. Portanto, utiliza o RID para gerar um pedido

para o hub de I/O, e o hub de I/O cria uma pedido para aceder ao adaptador. A localização da função de adaptador é baseada no RID, e o deslocamento especifica um deslocamento no espaço de configuração da função de adaptador.

Tal como aqui utilizado, o firmware inclui, por exemplo, o microcódigo, milicódigo e/ou macrocódigo do processador. Inclui, por exemplo, as instruções ao nível do hardware e/ou as estruturas de dados utilizadas na implementação de código de máquina de nível mais elevado. Numa forma de realização, inclui, por exemplo, código proprietário que normalmente é fornecido como microcódigo que inclui software de confiança ou microcódigo específico do hardware subjacente e controla o acesso do sistema operativo ao hardware do sistema.

Registo de Endereço Base (Base Address Register -(1 para n): Este campo inclui uma pluralidade de números inteiros sem sinal, designados como BAR<sub>0</sub> - BAR<sub>n</sub>, que estão associados com a função de adaptador especificada originalmente, e cujos valores são também armazenados nos registos de endereço base associados com a função de adaptador. Cada BAR especifica o endereço inicial de um espaço de memória ou espaço de I/O dentro da função de adaptador, e indica também 0 tipo de espaço de endereçamento, ou seja, se se trata de um espaço de memória de 64 ou 32 bits, ou de um espaço de I/O de 32 bits, como exemplos;

Num exemplo, é utilizado para acessos ao espaço de memória e/ou ao espaço de I/O da função de adaptador. Por exemplo, um deslocamento fornecido numa instrução para aceder à função de adaptador é adicionado ao valor no registo de endereço base associado ao espaço de endereçamento designado na instrução para obter o endereço a ser utilizado para aceder à função de adaptador. O identificador de espaço de endereçamento fornecido na instrução identifica o espaço de endereçamento dentro da função de adaptador a ser acedido e o BAR correspondente a ser utilizado;

Tamanho l...n: Este campo inclui uma pluralidade de números inteiros sem sinal, designados como  $SIZE_0$  -  $SIZE_n$ . O valor de um campo SIZE (tamanho), quando diferente de zero, representa o tamanho de cada espaço de endereçamento com cada entrada correspondendo a um BAR previamente descrito.

Detalhes adicionais relacionados com BAR e SIZE estão descritos abaixo.

- 1. Quando um BAR não é implementado para uma função de adaptador, o campo BAR e o seu campo de tamanho correspondente são ambos armazenados como zeros.

- 2. Quando um campo BAR representa ou um espaço de endereçamento de I/O ou um espaço de endereçamento de memória de  $32\ bits$ , o campo de tamanho correspondente é

diferente de zero e representa o tamanho do espaço de endereçamento.

- 3. Quando um campo BAR representa um espaço de endereçamento de memória de 64 bits,

- a. o campo  $BAR_{\text{n}}$  representa os bits menos significativos do endereço.

- $\mbox{b.} \quad \mbox{O pr\'oximo campo BAR}_{n+1} \mbox{ consecutivo representa} \\ \mbox{os } \mbox{\it bits} \mbox{ mais significativos do endereço.}$

- c. O campo  $\text{SIZE}_n$  correspondente é diferente de zero e representa o tamanho do espaço de endereçamento.

- d. O campo  $SIZE_{n+1}$  correspondente não é significativo e é armazenado como zero.

Informação de Encaminhamento Interno: Esta informação é utilizada para realizar encaminhamento específico ao adaptador. Inclui, por exemplo, nó, chip do processador, e informação de endereçamento do hub, como exemplos.

Indicação de Estado: Proporciona uma indicação de, por exemplo, se as operações de carga/armazenamento estão bloqueadas ou se o adaptador está no estado de erro, bem como outras indicações.

Num exemplo, o indicador de ocupado, o indicador

de estado de erro permanente, e o indicador de recuperação iniciada são definidos com base em monitorização realizada pelo firmware. Além disso, o indicador de permissão é definido, por exemplo, com base na política; e a informação de BAR é baseada em informação de configuração descoberta durante um varrimento de bus pelo processador (por exemplo, firmware do processador). Outros campos podem ser definidos com base na configuração, inicialização e/ou eventos. Noutras formas de realização, a entrada de tabela de função pode incluir mais, menos ou diferente informação. A informação incluída pode depender das operações suportadas ou ativadas para a função de adaptador.

Com referência à FIG. 6C, num exemplo, o Campo 2 designa um endereço lógico 620 de um bloco de informação de função (Function Information Block - FIB) PCI, que inclui informação sobre a função de adaptador associada. O bloco de informação de função é utilizado para atualizar uma entrada de tabela de dispositivo e/ou entrada de tabela de função (ou outra localização) associada com a função de adaptador. A informação é armazenada no FIB durante a inicialização e/ou configuração do adaptador, e/ou responsiva a eventos específicos.

Detalhes adicionais sobre um bloco de informação de função (Function Information Block - FIB) são descritos com referência à FIG. 6D. Numa forma de realização, um bloco de informação de função 650 inclui os seguintes campos:

Formato 651: Este campo especifica o formato do FIB.

Controlo de Interceção 652: Este campo é utilizado para indicar se a execução *guest* de instruções específicas por um *guest* de modo paginável resulta em interceção da instrução;

Indicação de Erro 654: Este campo inclui a indicação de estado de erro para interrupções de acesso direto à memória e de adaptador. Quando o bit é definido (por exemplo, 1), um ou mais erros foram detetados durante a realização de interrupção de acesso direto à memória ou de adaptador para a função de adaptador;

Bloqueio de Carga/Armazenamento 656: Este campo indica se as operações de carga/armazenamento estão bloqueadas;

Função PCI Válida 658: Este campo inclui um controlo de ativação para a função de adaptador. Quando o bit está definido (por exemplo, 1), a função de adaptador é considerada ativada para operações de I/O;

Espaço de Endereçamento Registado 660: Este campo inclui um controlo de ativação de acesso direto à memória para uma função de adaptador. Quando o campo está definido (por exemplo, 1) o acesso direto à memória está ativado;

Tamanho de Página 661: Este campo indica o tamanho da página ou outra unidade de memória a ser acedida por um acesso à memória DMA;

Endereço Base PCI (*PCI Base Address* - PBA) 662: Este campo é um endereço base para um espaço de endereçamento na memória de sistema atribuído para a função de adaptador. Representa o menor endereço virtual que é permitido a uma função de adaptador utilizar para acesso direto à memória ao espaço de endereçamento DMA especificado;

Limite de Endereço PCI (*PCI Address Limit* - PAL) 664: Este campo representa o maior endereço virtual a que é permitido aceder uma função de adaptador dentro do espaço de endereçamento DMA especificado;

Apontador de Tradução de Endereço de Entrada/Saída (Input/Output Address Translation Pointer - IOAT) 666: O apontador de tradução de endereço de entrada/saída designa a primeira de quaisquer tabelas de tradução utilizadas por uma tradução de endereço virtual PCI, ou pode designar diretamente o endereço absoluto de uma estrutura de armazenamento que é o resultado da tradução;

Subclasse de Interrupção (Interrupt Subclass - ISC) 668: Este campo inclui a subclasse de interrupção utilizada para apresentar interrupções de adaptador para a

função de adaptador;

Número de Interrupções (Number of Interruptions - NOI) 670: Este campo indica o número de códigos de interrupção distintos aceites para uma função de adaptador. Este campo também define o tamanho, em bits, do vetor de bit de interrupção do adaptador designado por um endereço de vetor de bit de interrupção do adaptador e pelos campos de deslocamento do vetor de bit de interrupção do adaptador;

Endereço de Vetor de *Bit* de Interrupção do Adaptador (*Adapter Interruption Bit Vector Address* - AIBV) 672: Este campo especifica um endereço do vetor de *bit* de interrupção do adaptador para a função de adaptador. Este vetor é utilizado no processamento de interrupção;

Deslocamento de Vetor de *Bit* de Interrupção do Adaptador 674: Este campo especifica o deslocamento do primeiro *bit* do vetor de *bit* de interrupção do adaptador para a função de adaptador;

Endereço de *Bit* de Resumo de Interrupção do Adaptador (*Adapter Interruption Summary Bit Address* - AISB) 676: Este campo fornece um endereço que designa o *bit* de sumarização de interrupção do adaptador, que é opcionalmente utilizado no processamento de interrupção;

Deslocamento de Bit de Sumarização de Interrupção

do Adaptador 678: Este campo fornece o deslocamento no vetor de *bit* de resumo de interrupção do adaptador;

Endereço de Bloco de Medição de Função (Function Measurement Block - FMB) 680: Este campo fornece um endereço de um bloco de medição de função utilizado para recolher medições relacionadas com a função de adaptador;

Chave de Bloco de Medição de Função 682: Este campo inclui uma chave de acesso para aceder ao bloco de medição de função;

Controlo de Notificação de *Bit* de Resumo 684: Este campo indica se há um vetor de *bit* de resumo a ser utilizado;

Token de Autorização de Instrução 686: Este campo é utilizado para determinar se um modo de guest de armazenamento paginável está autorizado a executar instruções PCI sem intervenção do host.

Num exemplo, na z/Architecture®, um guest paginável é interpretativamente executado através da execução da instrução Iniciar Execução Interpretativa (Start Interpretive Execution - SIE), no nível 2 de interpretação. Por exemplo, o hipervisor de partição lógica (Logical Partition Hypervisor - LPAR) executa a instrução SIE para iniciar a partição lógica na memória física, fixa. Se z/VM® é o sistema operativo nessa partição lógica, emite

a instrução SIE para executar as suas máquinas clientes (virtuais) no seu armazenamento V = V (virtual). Portanto, o hipervisor LPAR utiliza SIE de nível 1, e o hipervisor  $z/VM^{\$}$  utiliza SIE de nível 2 SIE; e

Formato de Tradução de Endereço 687: Este campo indica um formato selecionado para tradução de endereço da tabela de tradução de nível mais elevado a ser utilizado na tradução (por exemplo, uma indicação de tabela de nível mais elevado (por exemplo, tabela de segmento, região terceira, etc.)).

O bloco de informação de função designado na instrução Modificar Controlos de Função PCI é utilizado para modificar entrada de tabela de dispositivo uma selecionada, uma entrada de tabela de função e/ou outros controlos de firmware associados com a função de adaptador designada na instrução. Ao modificar a entrada de tabela de dispositivo, a entrada de tabela de função e/ou outros controlos de firmware, determinados serviços são fornecidos adaptador. Estes serviços incluem, por ao exemplo, adaptador; traduções de interrupções de endereços; reinicialização de estado de erro; reinicialização de bloqueio de carga/armazenamento; definição de parâmetros de medição de função; e definição de controlo de interceção.

Uma forma de realização da lógica associada com a instrução Modificar Controlos de Função PCI é descrita com referência à FIG. 7. Num exemplo, a instrução é emitida por

um sistema operativo (ou outra configuração) e executada pelo processador (por exemplo, firmware) que executa o sistema operativo. Nos exemplos aqui contidos, a instrução e funções de adaptador são baseadas em PCI. Contudo, noutros exemplos, pode ser utilizada uma arquitetura de adaptador e instruções correspondentes diferente.

Num exemplo, o sistema operativo fornece os seguintes operandos à instrução (por exemplo, em um ou mais registos designados pela instrução): a handle da função PCI, o identificador de espaço de endereçamento DMA, um controlo de operação; e um endereço do bloco de informação de função.

Com referência à FIG. 7, numa primeira fase, é feita uma determinação sobre se a componente permitindo uma instrução Modificar Controlos de Função PCI está instalada, PESQUISA 700. Esta determinação é feita, por exemplo, através da verificação de um indicador armazenado, por exemplo, num bloco de controlo. Se a componente não estiver instalada, é fornecida uma condição de exceção, ETAPA 702. Caso contrário, é feita uma determinação sobre se a instrução foi emitida por um modo guest de armazenamento paginável (ou por outro guest), PESQUISA 704. Se sim, o sistema operativo host irá emular a operação para esse guest, ETAPA 706.

Caso contrário, é feita uma determinação sobre se um ou mais dos operandos estão alinhados, PESQUISA 708. Por

exemplo, é feita uma determinação sobre se o endereço do bloco de informação de função está num limite de palavra dupla. Num exemplo, isto é opcional. Se os operandos não estão alinhados, então é fornecida uma condição de exceção, ETAPA 710. Caso contrário, é feita uma determinação sobre se o bloco de informação de função está acessível, PESQUISA 712. Se não, então é fornecida uma condição de exceção, ETAPA 714. Caso contrário, é feita uma determinação sobre se a handle fornecida nos operandos da instrução Modificar Controlos de Função PCI está ativada, PESQUISA 716. Num exemplo, esta determinação é feita através da verificação de um indicador de ativação na handle. Se a handle não estiver ativada, então é fornecida uma condição de exceção, ETAPA 718.

Se a handle estiver ativada, a handle é utilizada para localizar uma entrada de tabela de função, ETAPA 720. Isto é, pelo menos uma porção da handle é utilizada como um índice para a tabela de função para localizar a entrada de tabela de função correspondente à função de adaptador para a qual os parâmetros operacionais devem ser estabelecidos.

É feita uma determinação sobre se a entrada de tabela de função foi encontrada, PESQUISA 722. Se não, então é fornecida uma condição de exceção, ETAPA 724. Caso contrário, se a configuração que emite a instrução é um guest, PESQUISA 726, então é fornecida uma condição de exceção (por exemplo, a interceção do host), ETAPA 728. Esta pesquisa pode ser ignorada se a configuração não é um

guest ou outras autorizações podem ser verificadas, se designado.

É então feita uma determinação sobre se a função está ativada, PESQUISA 730. Num exemplo, essa determinação é feita através da verificação de um indicador de ativação na entrada de tabela da função. Se não estiver ativada, é fornecida uma condição de exceção, ETAPA 732.

Se a função estiver ativada, então é feita uma determinação sobre se a recuperação está ativa, PESQUISA 734. Se a recuperação estiver ativa conforme determinado por um indicador de recuperação na entrada de tabela de função, então é fornecida uma condição de exceção, ETAPA 736. No entanto, se a recuperação não estiver ativa, é feita uma nova determinação sobre se a função está ocupada, PESQUISA 738. Esta determinação é feita através da verificação do indicador de ocupado na entrada de tabela de função. Se a função estiver ocupada, então é fornecida uma condição de ocupado, ETAPA 740. Com a condição de ocupado, a instrução pode ser repetida, em vez de descartada.

Se a função não estiver ocupada, então é feita uma nova determinação sobre se o formato de bloco de informação de função é válido, PESQUISA 742. Por exemplo, o campo de formato do FIB é verificado para determinar se este formato é suportado pelo sistema. Se for inválido, então é fornecida uma condição de exceção, ETAPA 744. Se o formato de bloco de informação de função for válido, então

é feita uma nova determinação sobre se o controlo de operação especificado nos operandos da instrução é válido, PESQUISA 746. Ou seja, é o controlo da operação um dos controlos de operação especificados para esta instrução. Se for inválido, então é fornecida uma condição de exceção, ETAPA 748. No entanto, se o controlo de operação é válido, então o processamento continua com o controlo de operação específico sendo especificado.

Um controlo de operação que pode ser especificado é uma operação de registo de parâmetros de tradução de endereços de I/O utilizada no controlo de traduções de endereços para um adaptador. Com esta operação, parâmetros de função PCI relevantes para a tradução de endereços de I/O são definidos na DTE, FTE e/ou outra localização a partir dos parâmetros apropriados do FIB, que é um operando para a instrução. Estes parâmetros incluem, por exemplo, o endereço base PCI, o limite de endereço PCI (aka, limite PCI ou limite); o formato de tradução de endereços; o tamanho da página; e o apontador de tradução de endereços de I/O, que são operandos para esta operação. Existem também operandos implícitos, incluindo um endereço DMA inicial (Starting DMA Address - SDMA) e um endereço DMA final (Ending DMA Address - EDMA), que estão armazenados numa localização acessível ao processador que executa a instrução.

Uma forma de realização da lógica para estabelecer os parâmetros operacionais para tradução de

endereços de I/O é descrita com referência à FIG. Inicialmente, é feita uma determinação sobre se o endereço base PCI no FIB é maior do que o limite PCI no FIB, PESQUISA 800. Se a comparação do endereço base e o limite indicam que o endereço base é maior do que o limite, então uma condição de exceção é reconhecida, ETAPA 802. entanto, se o endereço base é menor ou igual ao limite, então uma nova determinação é feita sobre se o formato de tradução de endereços e o tamanho de página são válidos, PESQUISA 804. Se forem inválidos, então é fornecida uma condição de exceção, ETAPA 806. No entanto, se forem válidos, então uma nova determinação é feita sobre se o tamanho do espaço de endereçamento (com base no endereço base e no limite) excede a capacidade de tradução, PESQUISA 808. Num exemplo, o tamanho do espaço de endereçamento é comparado com a capacidade máxima possível de tradução de endereços com base no formato da tabela de nível superior. Por exemplo, se a tabela de nível superior é uma tabela de segmento compatível com DAT, a capacidade máxima tradução é de 2 Gbytes.

Se o tamanho do espaço de endereçamento exceder a capacidade de tradução, então é fornecida uma condição de exceção, ETAPA 810. Caso contrário, uma nova determinação é feita sobre se o endereço base é menor do que o endereço DMA inicial, PESQUISA 812. Se assim for, então é fornecida uma condição de exceção, ETAPA 814. Caso contrário, uma outra determinação é feita sobre se o limite de endereços é superior ao último endereço DMA, PESQUISA 816. Se o for,

então é fornecida uma condição de exceção, ETAPA 818. Num exemplo, o endereço DMA inicial e o endereço DMA final são baseados numa política global do sistema.

A partir daí, é feita uma determinação sobre se estão disponíveis recursos suficientes, se necessários, para realizar uma tradução de endereços de I/O, PESQUISA 820. Se não, então é fornecida uma condição ETAPA 822. Caso contrário, exceção, uma determinação é feita sobre se os parâmetros de tradução de endereços de I/O já foram registados na FTE e DTE, PESQUISA 824. Isto é determinado através da verificação dos valores dos parâmetros na FTE/DTE. Por exemplo, se os valores da FTE/DTE são zero ou outro valor definido, então o registo não foi realizado. Para localizar a FTE, o identificador fornecido na instrução é utilizado e, para localizar a DTE, um índice dispositivo na FTE é utilizada.

Se a função de adaptador já foi registada para a tradução de endereços, então é fornecida uma condição de exceção, ETAPA 826. Se não, então é feita uma determinação sobre se o espaço de endereçamento DMA que foi especificado é válido (ou seja, se é um espaço de endereçamento para o qual uma DTE foi ativada), PESQUISA 828. Se não, então é fornecida uma condição de exceção, ETAPA 830. Se todas as verificações forem bem sucedidas, os parâmetros de tradução são colocados na entrada de tabela de dispositivo, e opcionalmente na entrada de tabela de função correspondente (ou outra localização designada), ETAPA 832. Por exemplo,

os parâmetros de função PCI relevantes para a tradução de endereços de I/O são copiados a partir do bloco de informação de função e colocados na DTE/FTE. Estes parâmetros incluem, por exemplo, o endereço base PCI, o limite de endereço PCI, o formato de tradução, o tamanho da página, e o apontador de tradução de endereços de I/O. Esta operação permite acessos DMA ao espaço de endereçamento DMA especificado. Permite tradução de endereços de I/O para a função de adaptador.

controlo operação Outro de que pode ser especificado pela instrução Modificar Controlos de Função PCI é uma operação de cancelar registo de parâmetros de tradução de endereços de I/O, a exemplo do que é descrito com referência à FIG. 9. Com esta operação, os parâmetros de função relevantes para tradução de endereços de I/O são reinicializados para zeros. Esta operação desativa os acessos DMA ao espaço de endereçamento DMA especificado e provoca uma limpeza das entradas de buffer de tradução (translation lookaside buffer - TLB) de I/O para esse espaço de endereçamento DMA. Desativa a tradução de endereços.

Com referência à FIG. 9, numa forma de realização, é feita uma determinação sobre se os parâmetros de tradução de endereços de I/O não são registados, PESQUISA 900. Num exemplo, esta determinação é feita através da verificação dos valores dos parâmetros apropriados na FTE ou DTE. Se esses campos são zero ou

algum valor especificado, não são registados. Portanto, é fornecida uma condição de exceção, ETAPA 902. Se eles são registados, então é feita uma determinação sobre se o espaço de endereçamento DMA é válido, PESQUISA 904. Se for inválido, então é fornecida uma condição de exceção, ETAPA 906. Se o espaço de endereçamento DMA é válido, então os parâmetros de tradução na entrada de tabela de dispositivo, e opcionalmente na entrada de tabela de função correspondente são apagados, ETAPA 908.

Descrito em detalhe acima está um mecanismo eficiente para traduzir um endereço de entrada/saída fornecido por um adaptador para um endereço de memória de sistema. Num exemplo, o endereço PCI completo (por exemplo, a totalidade do endereço de 64 bits) é utilizado no acesso entanto, as pesquisas de tradução memória, no endereços são minimizadas utilizando apenas uma porção do endereço para tradução. Embora o uso do endereço completo forneça proteção adicional, a utilização de, por exemplo, apenas os bits de ordem mais baixa para tradução permite uma tradução mais eficiente por meio de menos níveis de pesquisa de tradução. Isto permite uma maior flexibilidade do sistema operativo na utilização de endereços que podem coexistir ou serem os mesmos que os endereços virtuais do sistema operativo. Além disso, permite que as tabelas de tradução de endereços de CPU possam ser partilhadas por adaptadores, permitindo ao mesmo tempo que o I/O reduza o número de tabelas que necessitam de ser digitalizadas. Além disso, é fornecida proteção adicional ao ser permitido que

diferentes adaptadores e/ou sistemas operativos utilizem intervalos de espaço de endereçamento disjuntos. Nas formas realização aqui descritas, OS adaptadores adaptadores PCI. PCI, tal como é aqui utilizado, refere-se a todos os adaptadores implementados de acordo com uma especificação baseada em PCI, tal como definido pelo Grupo de Interesse Especial em Conexão Componente Periférica (Peripheral Component Interconnect Special Interest Group -PCI-SIG), incluindo, mas não estando limitado a, PCI ou Num exemplo particular, a Conexão Componente PCIe. Periférica Expresso (Peripheral Component Interconnect Express - PCIe) é uma norma de interconexão do nível define componente que um protocolo de comunicação bidirecional para transações entre adaptadores e sistemas de host de I/O. As comunicações PCIe são encapsuladas em pacotes de acordo com a norma PCIe para a transmissão num bus PCIe. As transações provenientes de adaptadores de I/O e terminando em sistemas host são referidas como transações upbound. As transações provenientes de sistemas host e terminando em adaptadores de I/O são chamadas de transações downbound. Α topologia PCIe baseia-se emligações unidirecionais ponto-a-ponto que são emparelhadas exemplo, uma ligação upbound, uma ligação downbound) para formar o bus PCIe. A norma PCIe é mantida e publicada pelo PCI-SIG.

Como será valorizado por um perito na técnica, os aspetos da presente invenção podem ser incorporados como um sistema, método ou produto de programa de computador.

Assim, aspetos da presente invenção podem assumir o contorno de uma forma de realização totalmente de hardware, uma forma de realização totalmente de software (incluindo firmware, software residente, microcódigo, etc) ou uma forma de realização combinando aspetos de software e de hardware que podem todos ser geralmente aqui referidos como um "circuito", "módulo" ou "sistema". Além disso, os aspetos da presente invenção podem assumir o contorno de um produto de programa de computador incorporado num ou mais suportes legíveis por computador, tendo código de programa legível por computador incorporado nele.

Qualquer combinação de um mais ou legíveis por computador pode ser utilizada. O suporte legível por computador pode ser um suporte de armazenamento legível por computador. Um suporte de armazenamento legível por computador pode ser, por exemplo, mas não estando limitado, a um sistema eletrónico, magnético, eletromagnético, de infravermelhos ou de semicondutores, aparelho, ou dispositivo, ou qualquer combinação adequada destes materiais. Exemplos mais específicos (uma lista não exaustiva) suporte de armazenamento do legível computador incluem o seguinte: uma conexão elétrica com um ou mais fios, uma disquete de computador portátil, um disco rígido, uma memória de acesso aleatório (Random Access Memory - RAM), uma memória só de leitura (Read-Only Memory - ROM), uma memória só de leitura programável apagável (Erasable Programmable Read-Only Memory - EPROM ou memória Flash), uma fibra ótica, uma memória só de leitura em disco

compacto portátil (Compact Disc Read-Only Memory - CD-ROM), um dispositivo de armazenamento ótico, um dispositivo de armazenamento magnético, ou qualquer combinação adequada destes materiais. No contexto deste documento, um suporte de armazenamento legível por computador pode ser um qualquer suporte material que possa conter ou armazenar um programa para utilização ou ligação com um sistema, aparelho ou dispositivo de execução de instruções.

Com referência agora à FIG. 10, num exemplo, um produto de programa de computador 1000 inclui, por exemplo, um ou mais suportes de armazenamento legíveis por computador 1002 para armazenar suportes ou lógica de código de programa legível por computador 1004 sobre os mesmos para proporcionar e facilitar um ou mais aspetos da presente invenção.

- O código do programa incorporado num suporte legível por computador pode ser transmitido através de um suporte adequado, incluindo, mas não estando limitado a um suporte sem fios, com fios, um cabo de fibra ótica, RF, etc, ou qualquer combinação adequada destes materiais.

- O código de programa de computador para a realização de operações para aspetos da presente invenção pode ser escrito em qualquer combinação de uma ou mais linguagens de programação, incluindo uma linguagem de programação orientada a objetos, como Java, Smalltalk, C++ ou semelhante, e linguagens de programação processuais

convencionais, tais como a linguagem de programação "C", assembler ou linguagens de programação similares. O código de programa pode executar-se inteiramente no computador do utilizador, em parte no computador do utilizador, como um pacote de software independente, parcialmente no computador do utilizador e parcialmente num computador remoto ou inteiramente no computador ou servidor remoto. Neste último cenário, o computador remoto pode ser conectado ao computador do utilizador através de qualquer tipo de rede, incluindo uma rede de área localização (Local Area Network - LAN), uma rede de área ampla (Wide Area Network - WAN), ou ou a conexão pode ser feita para um computador externo (para exemplo, através da Internet utilizando um Provedor de Serviços de Internet).

presente invenção 0s aspetos da descritos com referência ilustrações de fluxogramas e/ou diagramas de blocos de métodos, aparelhos (sistemas) e produtos de programas de computador de acordo com formas de realização da invenção. Será compreendido que cada bloco das ilustrações de fluxogramas e/ou diagramas de blocos, e combinações de blocos nas ilustrações de fluxogramas e/ou diagramas de blocos, podem ser implementados por instruções de programa de computador. Estas instruções de programa de computador podem ser fornecidas a um processador de um computador de uso geral, um computador com um objetivo específico, ou qualquer outro aparelho de processamento de dados programável para produzir uma máquina, de tal modo que as instruções que se executam por meio do processador do computador ou outro aparelho de processamento de dados programável, criar suportes para implementar as funções/ações especificadas no bloco ou blocos de fluxograma e/ou bloco de diagrama.

Estas instruções de programa de computador podem também ser armazenadas num suporte legível por computador que pode controlar um computador, outro aparelho de processamento de dados programável, ou outros dispositivos para funcionar de uma forma específica, de tal modo que as instruções armazenadas no suporte legível pelo computador produzam um artigo de fabrico incluindo instruções que implementem a função/ação especificada no blocos ou blocos de fluxograma e/ou bloco de diagrama.

As instruções do programa de computador podem também ser carregadas num computador, outro aparelho de processamento de dados programável, ou outros dispositivos para provocar uma série de etapas operacionais a serem executadas no computador, outro aparelho programável ou outros dispositivos para produzir um processo implementado por computador de tal modo que as instruções que se executam no computador ou outro aparelho programável proporcionam processos para implementação das funções/ações especificados no blocos ou blocos de fluxograma e/ou bloco de diagrama.

Os fluxogramas e diagramas de blocos nas figuras ilustram a arquitetura, funcionalidade e operação de

possíveis implementações de sistemas, métodos e produtos de programas de computador de acordo com várias formas de realização da presente invenção. A este respeito, nos fluxogramas ou diagramas de blocos representar um módulo, segmento, ou porção de código, o qual compreende uma ou mais instruções executáveis para a implementação da(s) função(ões) lógica(s) especificada(s). Também deve ser notado que, em algumas implementações alternativas, as funções destacadas no bloco podem ocorrer fora da ordem destacada nas figuras. Por exemplo, dois blocos mostrados sucessão podem, em na verdade, ser executados substancialmente de forma concorrente, ou os blocos podem por vezes ser executados na ordem inversa, dependendo da funcionalidade envolvida. Também deve ser notado que cada bloco dos diagramas de blocos e/ou ilustração de fluxograma, e combinações de blocos nos diagramas de blocos e/ou ilustração de fluxograma, podem ser implementados por sistemas baseados em hardware para fins específicos que desempenham as funções ou ações especificadas, ou combinações de hardware e instruções de computador para fins específicos.

- 55 -

Para além do referido, um ou mais aspetos da presente invenção pode ser fornecido, oferecido, implementado, gerido, mantido, etc. por um provedor de serviços que proponha gestão de ambientes de cliente. Por exemplo, o provedor de serviços pode criar, manter, suportar, etc. código de computador e/ou uma infraestrutura informática que realiza um ou mais aspetos da presente

invenção para um ou mais clientes. Em comutação, o provedor de serviços pode receber o pagamento do cliente no âmbito de um contrato de subscrição e/ou taxação, como exemplos. Adicionalmente ou alternativamente, o provedor de serviços pode receber o pagamento com a venda de conteúdos publicitários a uma ou mais entidades terceiras.

Num aspeto da presente invenção, uma aplicação pode ser implementada para a realização de um ou mais aspetos da presente invenção. Como um exemplo, a implementação de uma aplicação compreende o fornecimento de uma infraestrutura informática operável para realizar um ou mais aspetos da presente invenção.

Como um aspeto adicional da presente invenção, uma infraestrutura informática pode ser implementada compreendendo a integração de código legível por computador num sistema informático, em que o código em combinação com o sistema informático é capaz de realizar um ou mais aspetos da presente invenção.