# (10) **DE 10 2008 059 646 B4** 2010.12.30

(12)

# **Patentschrift**

(21) Aktenzeichen: 10 2008 059 646.9

(22) Anmeldetag: 28.11.2008(43) Offenlegungstag: 02.06.2010

(45) Veröffentlichungstag

der Patenterteilung: 30.12.2010

(51) Int Cl.8: **H01L 21/336** (2006.01) **H01L 29/78** (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

#### (73) Patentinhaber:

Advanced Micro Devices, Inc., Sunnyvale, Calif., US; AMD Fab 36 Limited Liability Company & Co. KG, 01109 Dresden, DE

## (74) Vertreter:

Grünecker, Kinkeldey, Stockmair & Schwanhäusser, 80802 München

(72) Erfinder:

Mulfinger, Robert, 01097 Dresden, DE; Wei, Andy, 01097 Dresden, DE; Hoentschel, Jan, 01309 Dresden, DE; Waite, Andrew, 01129 Dresden, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

WO 2007/0 38 575 A2

(54) Bezeichnung: Verfahren zur Herstellung eines Halbleiterbauelements als Mehr-Gatetransistor mit Stegen mit einer Länge, die durch die Gateelektrode definiert ist und Halbleiterbauelement

## (57) Hauptanspruch: Verfahren mit:

Bilden einer Öffnung (260a) in einem Maskenmaterial (260), das über einer Halbleiterschicht (202) eines Mehr-Gatetransistors (250) gebildet ist, wobei die Öffnung (260a) laterale Abmessungen aufweist, die einer Gateelektrodenstruktur (220) des Mehr-Gatetransistors (250) entsprechen;

Strukturieren der Halbleiterschicht (202) innerhalb der Öffnung (260a), so dass Stege (210a, ..., 210e) aus der Halbleiterschicht (202) innerhalb der Öffnung (260a) gebildet werden; und

Bilden der Gateelektrodenstruktur (220) innerhalb der Öffnung (260a) in Anwesenheit der Stege (210a, ..., 210e), wobei Bilden der Öffnung (260a) umfasst: Bilden einer Platzhalterstruktur (240) über der Halbleiterschicht (202), laterales Einbetten der Platzhalterstruktur (240) in das Maskenmaterial (260) und Entfernen der Platzhalterstruktur (240) selektiv zu dem Maskenmaterial (260).

### **Beschreibung**

Gebiet der vorliegenden Offenbarung

**[0001]** Im Allgemeinen betrifft die vorliegende Offenbarung die Herstellung modernster integrierter Schaltungen mit Transistorelementen, die eine Doppelgate-(FinFET) oder eine Trippel-Gatearchitektur besitzen.

Beschreibung des Stands der Technik

[0002] Die Herstellung moderner integrierter Schaltungen, etwa von CPU's, Speicherbauelementen, ASIC's (anwendungsspezifische integrierte Schaltungen) und dergleichen, erfordert die Herstellung einer großen Anzahl an Schaltungselementen auf einer vorgegebenen Chipfläche gemäß einem spezifizierten Schaltungsaufbau, wobei Feldeffekttransistoren eine wichtige Art von Schaltungselementen repräsentieren, die im Wesentlichen das Leistungsverhalten integrierter Schaltungen bestimmt. Im Allgemeinen werden eine Vielzahl von Prozesstechnologien eingesetzt, wobei für viele Arten komplexer Schaltungen mit Feldeffekttransistoren die MOS-Technologie aktuell eine der vielversprechendsten Lösungen auf Grund der guten Eigenschaften im Hinblick auf die Arbeitsgeschwindigkeit und/oder Leistungsaufnahme und/oder Kosteneffizienz ist. Während der Herstellung komplexer integrierter Schaltungen unter Anwendung von beispielsweise der MOS-Technologie werden Millionen Transistoren, beispielsweise n-Kanaltransistoren und/oder p-Kanaltransistoren, auf einem Substrat hergestellt, das eine kristalline Halbleiterschicht aufweist. Ein Feldeffekttransistor enthält, unabhängig davon, ob ein n-Kanaltransistor oder ein p-Kanaltransistor betrachtet wird, sogenannte pn-Übergänge, die durch eine Grenzfläche stark dotierter Gebiete, die als Drain- und Sourcegebiete bezeichnet werden, mit einem leicht dotierten oder nicht dotierten Gebiet gebildet, etwa ein Kanalgebiet, das benachbart zu den stark dotierten Gebieten angeordnet ist. In einem Feldeffekttransistor wird die Leitfähigkeit des Kanalgebiets, d. h. der Durchlassstrom des leitenden Kanals, durch eine Gateelektrode gesteuert, die benachbart zu dem Kanalgebiet ausgebildet und davon durch eine dünne isolierende Schicht getrennt ist. Die Leitfähigkeit des Kanalgebiets beim Aufbau eines leitenden Kanals beim Anlegen einer geeigneten Steuerspannung an die Gateelektrode hängt von der Dotierstoffkonzentration, der Beweglichkeit der Ladungsträger und - für eine planare Transistorarchitektur - von einem Abstand zwischen dem Sourcegebiet und dem Draingebiet ab, der auch als Kanallänge bezeichnet wird.

[0003] Gegenwärtig basiert der überwiegende Teil integrierter Schaltungen auf Silizium auf Grund der im Wesentlichen unbegrenzten Verfügbarkeit, den gut verstandenen Eigenschaften des Siliziums und

zugehöriger Materialien und Prozesse und auf Grund der Erfahrung, die über die letzten 50 Jahre gewonnen wurde. Daher bleibt Silizium mit hoher Wahrscheinlichkeit das Material der Wahl für künftige Schaltungsgenerationen, die für die Massenherstellung gedacht sind. Ein Grund für die Wichtigkeit für die Herstellung bei der Herstellung von Halbleiterbauelementen sind die guten Eigenschaften einer Silizium/Siliziumdioxidgrenzfläche, die eine zuverlässige elektrische Isolation unterschiedlicher Gebiete voneinander ermöglicht. Die Silizium/Siliziumdioxidgrenzfläche ist bei hohen Temperaturen stabil und ermöglicht somit das Ausführen nachfolgender Hochtemperaturprozesse, wie sie beispielsweise für Ausheizprozesse erforderlich sind, um Dotierstoffe zu aktivieren und Kristallschäden auszuheilen, ohne die elektrischen Eigenschaften der Grenzfläche zu beeinträchtigen.

[0004] Aus den zuvor genannten Gründen wird Siliziumdioxid vorzugsweise als eine Gateisolationsbasisschicht in Feldeffekttransistoren verwendet, die die Gateelektrode, die häufig aus Polysilizium oder anderen metallenthaltenden Materialien aufgebaut ist, von dem Siliziumkanalgebiet trennt. Beim stetigen Verbessern des Bauteilleistungsverhaltens von Feldeffekttransistoren wird die Länge des Kanalgebiets verringert, um die Schaltgeschwindigkeit und den Durchlassstrom zu verbessern. Da das Transistorverhalten durch die der Gateelektrode zugeführten Spannung zur Invertierung der Oberfläche des Kanalgebiets zu einer ausreichend hohen Ladungsdichte gesteuert wird, um damit den gewünschten Durchlassstrom für eine vorgegebene Versorgungsspannung zu erreichen, ist ein gewisses Maß an kapazitiver Kopplung aufrecht zu erhalten, die durch den Kondensator hervorgerufen wird, der durch die Gateelektrode, das Kanalgebiet und das dazwischen angeordnete Siliziumdioxid gebildet ist. Es zeigt sich, dass das Verringern der Kanallänge für eine planare Transistorkonfiguration eine höhere kapazitive Kopplung erfordert, um das sogenannte Kurzkanalverhalten während des Transistorbetriebs zu vermeiden. Das Kurzkanalverhalten wird zu einem erhöhten Leckstrom und zu einer Abhängigkeit der Schwellwertspannung von der Kanallänge. Sehr kleine Transistorbauelemente mit einer relativ geringen Versorgungsspannung und damit mit einer geringeren Schwellwertspannung weisen einen exponentiellen Anstieg des Leckstromes auf, wobei auch eine höhere kapazitive Kopplung der Gateelektrode an das Kanalgebiet erforderlich ist. Somit muss die Dicke der Siliziumdioxidschicht entsprechend verringert werden, um die erforderliche Kapazität zwischen dem Gate und dem Kanalgebiet zu erzeugen. Z. B. erfordert eine Kanallänge von ungefähr 0,08 µm ein aus Siliziumdioxid hergestelltes Gatedielektrikum, das eine Dicke von ungefähr 1,2 nm besitzt. Obwohl die Verwendung von Hochgeschwindigkeitstransistorelementen mit einem äußerst kurzen Kanal typischerweise auf Hochgeschwindigkeitsanwendungen beschränkt ist, wohingegen Transistorelemente mit einem längeren Kanal für weniger kritische Anwendungen eingesetzt werden, etwa Speichertransistorelemente, hat dennoch der relativ hohe Leckstrom, der durch das direkte Tunneln von Ladungsträgern durch eine sehr dünne Siliziumdioxidgateisolationsschicht hervorgerufen wird, Werte bei einer Oxiddicke im Bereich von 1 bis 2 nm erreicht, die nicht mehr mit den Anforderungen für Schaltungen verträglich sind.

[0005] Daher wurde das Ersetzen von Siliziumdioxid als Material für Gateisolationsschichten vorgeschlagen, insbesondere für äußerst dünne Siliziumdioxidgateschichten. Mögliche alternative Materialien sind solche, die eine deutlich höhere Permittivität aufweisen, so dass eine physikalisch größere Dicke einer entsprechend hergestellten Gateisolationsschicht eine kapazitive Kopplung ergibt, die mit einer äußerst dünnen Siliziumdioxidschicht erreicht wurde. Es wurde daher vorgeschlagen, Siliziumdioxid durch Materialien mit hoher Permittivität zu ersetzen, etwa Tantaloxid ( $\text{Ta}_2\text{O}_5$ ) mit einem  $\epsilon$  von ungefähr 25, Strontiumtitanoxid ( $\text{SrTiO}_3$ ) mit einem  $\epsilon$  von ungefähr 150, Hafniumoxid ( $\text{HfO}_2$ ), HfSiO, Zirkonoxid ( $\text{ZrO}_2$ ), und dergleichen.

[0006] Obwohl merkliche Vorteile im Hinblick auf das Leistungsverhalten und die Steuerbarkeit modernster planarer Transistorarchitekturen auf der Grundlage der oben angegebenen Strategien erreicht werden können, wurden im Hinblick auf eine weitere Größenreduzierung neuer Transistorkonfigurationen vorgeschlagen, in denen eine "dreidimensionale" Architektur vorgeschlagen wird, um eine gewünschte Kanalbreite zu erhalten, während gleichzeitig eine ausgeprägte Steuerbarkeit des Stromflusses durch das Kanalgebiet beibehalten wird. Zu diesem Zweck wurden sogenannte FinFET's vorgeschlagen, in denen ein dünner Grad oder ein Steg aus Silizium in einer dünnen aktiven Schicht eines SOI-(Silizium-auf-Isolator-)Substrats ausgebildet ist, wobei an beiden Seitenwänden ein Gatedielektrikumsmaterial und ein Gateelektrodenmaterial vorgesehen sind, wodurch ein Doppelgatetransistor realisiert wird, dessen Kanalgebiet vollständig verarmt ist. Typischerweise liegt in anspruchsvollen Anwendungen die Breite der Siliziumstege in der Größenordnung von 10 nm und deren Höhe liegt in der Größenordnung von 30 nm. In einer modifizierten Version der grundlegenden Doppelgatetransistorarchitektur wird auch ein Gatedielektrikumsmaterial und eine Gateelektrode auf einer oberen Fläche des Stegs hergestellt, wodurch eine Tri-Gatetransistorarchitektur realisiert wird.

**[0007]** Somit bieten FinFET-Transistorarchitekturen, die im Weiteren als Mehr-Gatetransistoren bezeichnet werden, Vorteile im Hinblick auf die Verbesserung der effektiven Ankopplung der Gateelektrode

an die diversen Kanalgebiete, ohne dass eine zugehörige Verringerung der Dicke des Gatedielektrikumsmaterials erforderlich ist. Durch das Bereitstellen dieser nicht-planaren Transistorarchitektur kann auch die effektive Kanalbreite vergrößert werden, so dass für vorgegebene Transistorgesamtabmessungen ein höherer Durchlassstrom erreichbar ist. Aus diesem Grunde werden große Anstrengungen unternommen, um ein höheres Transistorleistungsverhalten auf der Grundlage nicht-ebener oder planarer Transistorarchitekturen zu erreichen, wobei jedoch aufwendige Fertigungsprozesse konventioneller Weise eingesetzt werden, etwa selektive epitaktische Aufwachstechniken, die zu einem deutlich geringeren Gesamtdurchsatz führen, da entsprechende epitaktische Aufwachsprozesse typischerweise auf der Basis einzelner Substrate ausgeführt werden. Mit Bezug zu den Fig. 1a bis Fig. 1g wird nunmehr ein typischer konventioneller Prozessablauf zur Herstellung eines Mehr-Gatetransistors detaillierter beschrieben, um die grundlegende Struktur und die beteiligten Prozesstechnologien deutlicher zu machen.

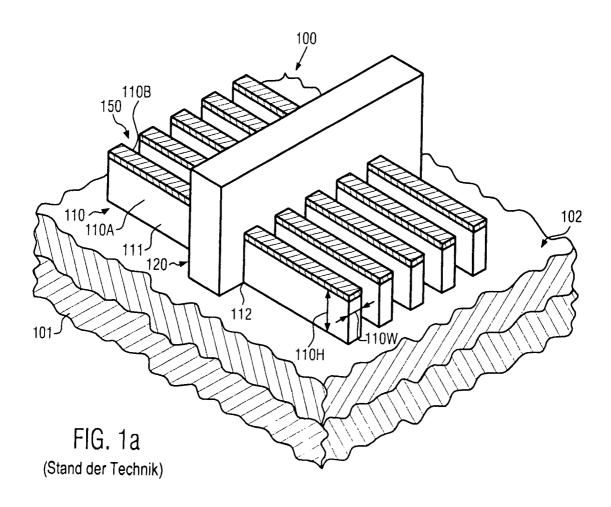

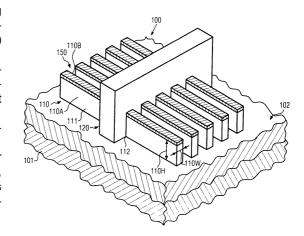

[0008] Fig. 1a zeigt schematisch eine perspektivische Ansicht eines Transistorelements 100, das als FinFET-Transistor oder Mehr-Gatetransistor bezeichnet werden kann. Wie gezeigt, umfasst der Transistor 100 ein Substrat 101, über welchem eine Basisschicht 102, etwa eine Siliziumschicht und dergleichen gebildet ist. Des weiteren sind mehrere Stege 110 über der Schicht 102 gebildet und sind aus einem beliebigen geeigneten Halbleitermaterial, etwa Silizium, Silizium/Germanium, und dergleichen aufgebaut. Wie nachfolgend detaillierter erläutert ist, können die Stege 110 auf der Grundlage eines epitaktisch aufgewachsenen Halbleitermaterials hergestellt werden, das auf der Basisschicht 102 abgeschieden wird, während in anderen Fällen komplexe Prozesstechnologien angewendet werden, um eine SOI-(Silizium-auf-Isolator-)Konfiguration stellen, wobei die Basisschicht 102 ein isolierendes Material, etwa Siliziumdioxid und dergleichen, repräsentiert. Eine Gateelektrodenstruktur 120 ist über einem zentralen Bereich der Stege 110 ausgebildet, wobei die Gateelektrodenstruktur 120 ein geeignetes Gatedielektrikumsmaterial, etwa Siliziumdioxid, aufweist in Verbindung mit einem geeigneten Elektrodenmaterial, d. h., typischerweise einem Polysiliziummaterial. Somit repräsentiert jeder der Stege 110 in Verbindung mit der gemeinsamen Gateelektrodenstruktur 120 eine einzelne Transistorzelle des Bauelements 100. In dem gezeigten Beispiel besitzen die Stege darauf ausgebildet eine Deckschicht 112, die sich auch durch die Gateelektrodenstruktur 120 erstrecken kann, wenn eine obere Fläche der Stege 110 nicht als ein Kanalgebiet dienen soll. Andererseits repräsentieren entsprechende Seitenwandflächen 110a, 110b der Stege 110 zugehörige Kanalgebiete, deren Leitfähigkeit durch die Gateelektrode 120 gesteuert wird. Es sollte beachtet werden, dass die Stege 110 eine geeignete Dotierstoffkonzentration aufweisen, um damit entsprechende Drain- und Sourcebereiche in jedem Steg 110 zu bilden, während in anderen Strategien entsprechende Drain- und Sourcegebiete in einer späteren Phase hergestellt werden, nachdem die Endbereiche der Stege 110 durch Aufwachsen eines weiteren Halbleitermaterials zur Füllung des Zwischenraums zwischen den einzelnen Stegen 110 verbunden sind.

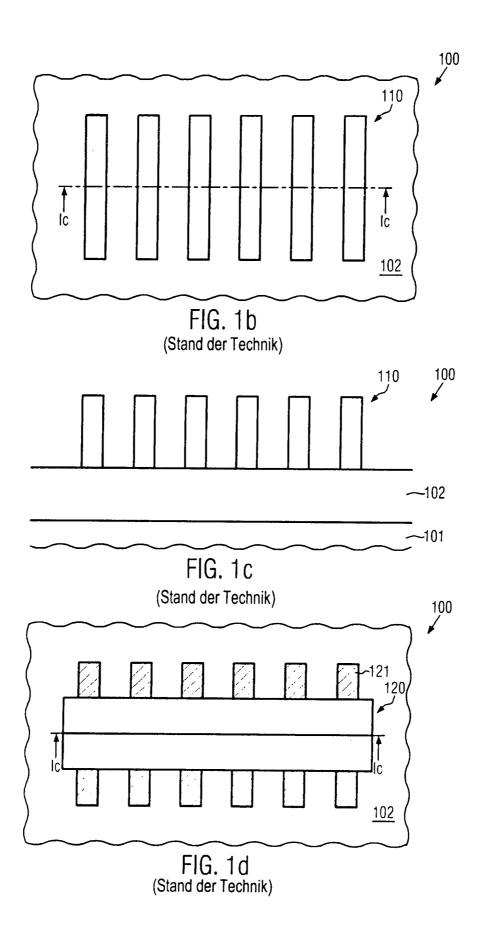

[0009] Fig. 1b zeigt schematisch eine Draufsicht des Bauelements 100 in einer frühen Fertigungsphase. Wie gezeigt, sind die Stege 110 mit lateralen Abmessungen gemäß den gesamten Entwurfsregeln für das Bauelement 100 hergestellt.

[0010] Fig. 1c zeigt schematisch eine Querschnittsansicht des Bauelements 100 aus Fig. 1b entlang der Linie Ic. Wie gezeigt, erstrecken sich die Stege 110 bis hinab zu der Basisschicht 102, was auf der Grundlage aufwendiger Lithographie- und Ätztechniken bewerkstelligt werden kann, in denen ein Halbleitermaterial, etwa ein Siliziummaterial und dergleichen, geätzt wird. Typischerweise wird das Halbleitermaterial der Stege 110 auf der Grundlage epitaktischer Aufwachstechniken hergestellt, was zu einem geringeren Durchsatz führt, da diese Abscheidetechnik für gewöhnlich auf der Grundlage von Prozessanlagen ausgeführt wird, die der Reihe nach einzelne Substrate bearbeiten. Es sollte beachtet werden, dass abhängig von der gesamten Prozessstrategie ein Deckmaterial, etwa die Deckschicht 112 (siehe Fig. 1a) vor dem Strukturieren der Stege 110 vorgesehen werden kann, wenn die obere Fläche der Stege 110 nicht als ein Kanalgebiet zu nutzen ist. Vor oder nach dem Strukturieren der Stege 110 wird ein grundlegendes Dotierstoffprofil erzeugt, um etwa die grundlegende Leitfähigkeitsart der Stege und dergleichen zu definieren. Dies kann durch Implantationstechniken und/oder durch Einbau einer gewünschten Dotierstoffsorte während des epitaktischen Aufwachsprozesses zur Herstellung des Materials für die Stege 110 bewerkstelligt werden. Als nächstes wird die Gateelektrodenstruktur 120 (siehe Fig. 1a) gebildet, beispielsweise durch Bilden eines geeigneten Gatedielektrikumsmaterials, etwa Silizium Siliziumdioxid, was durch anspruchsvolle Oxidationstechniken und dergleichen bewerkstelligt werden kann, woran sich das Abscheiden des Gateelektrodenmaterials, etwa von Polysilizium, anschließt. Nach dem Einebnen des Elektrodenmaterials, das auch geeignete Materialien zur Herstellung einer Hartmaske, zum Einstellen der gesamten optischen Eigenschaften auf der Grundlage eines ARC(antireflektierendes Beschichtungs-)Materials und dergleichen enthalten kann, wird das Elektrodenmaterial strukturiert, indem eine durch Lithographie erzeugte Lackmaske verwendet wird und eine geeignete Ätzsequenz ausgeführt wird, wobei ein hohes Maß an Ätzselektivität zwischen dem Gateelektrodenmaterial und dem Gatedielektrikumsmaterial die Integrität der Endbereiche der Stege **110** gewährleistet. Beispielsweise sind gut etablierte Prozesstechniken zum Ätzen von Polysiliziummaterial selektiv zu Siliziumdioxid verfügbar.

[0011] Fig. 1d zeigt schematisch eine Draufsicht des Bauelements 100 nach der zuvor beschriebenen Prozesssequenz und nach dem Entfernen von Lackmaterialien und anderen nicht mehr benötigten Materialien, die zum Strukturieren der Gateelektrodenstruktur 120 verwendet wurden. Wie gezeigt, besitzt die Gateelektrodenstruktur 120 geeignete laterale Abmessungen, um einen zentralen Bereich der Stege 110 abzudecken, wodurch entsprechende Kanallängen für jeden Steg 110 definiert werden. Des weiteren sind die Stege 110 von einem Gatedielektrikumsmaterial 121, etwa Siliziumdioxid und dergleichen, bedeckt, wie dies auch zuvor erläutert ist.

[0012] Fig. 1e zeigt schematisch eine Querschnittsansicht entlang der Linie Ic, wie sie in Fig. 1d gezeigt ist. Wie dargestellt, enthält die Gateelektrodenstruktur 120 ein Gateelektrodenmaterial 122, das zwischen den Raumbereichen benachbarter Stege 110 gebildet ist, die durch das Gatedielektrikumsmaterial 121 bedeckt sind. In dem gezeigten Beispiel sei angenommen, dass jeder Oberflächenbereich, d. h. beide Seitenwände 110a, 110b und eine obere Fläche 110t als eigentliche Kanalgebiete dienen, die durch das umgebende Gateelektrodenmaterial 122 gesteuert werden, so dass jede der Oberflächen 110a, 110b und 110t als durch eine zugeordnete Gateelektrode gesteuert erachtet werden kann. Nach dem Bilden der Gateelektrodenstruktur 120 werden Drain- und Sourcebereiche etwa durch Ionenimplantation gebildet, wozu das Abscheiden eines Abstandshaltermaterials und dessen Strukturierung bei Bedarf gehören kann, während in anderen Fällen ein Halbleitermaterial zunächst gebildet wird, um Endbereiche der Stege an beiden Seiten der Gateelektrodenstruktur 120 elektrisch miteinander zu verbinden, um damit zugehörige Drain- und Sourcebereiche zu schaffen. Zu diesem Zweck werden die Endbereiche der Stege 110, die nicht von der Gateelektrodenstruktur 120 bedeckt sind, durch Entfernen des Gatedielektrikumsmaterials 121 freigelegt, was durch gut etablierte Ätzrezepte, etwa auf der Grundlage von Flusssäure und dergleichen bewerkstelligt werden kann. Danach werden die freiliegenden Oberflächenbereiche der Stege 110 für einen nachfolgenden selektiven epitaktischen Aufwachsprozess vorbereitet, wozu gut etablierte Reinigungsprozesse und dergleichen gehören können. Wie zuvor erläutert ist, erfordert der epitaktische Aufwachsprozess aufwendige Prozessanlagen, auf Basis einzelner Substrate arbeiten, wodurch der Durchsatz des gesamten Fertigungsablaufs deutlich verringert wird.

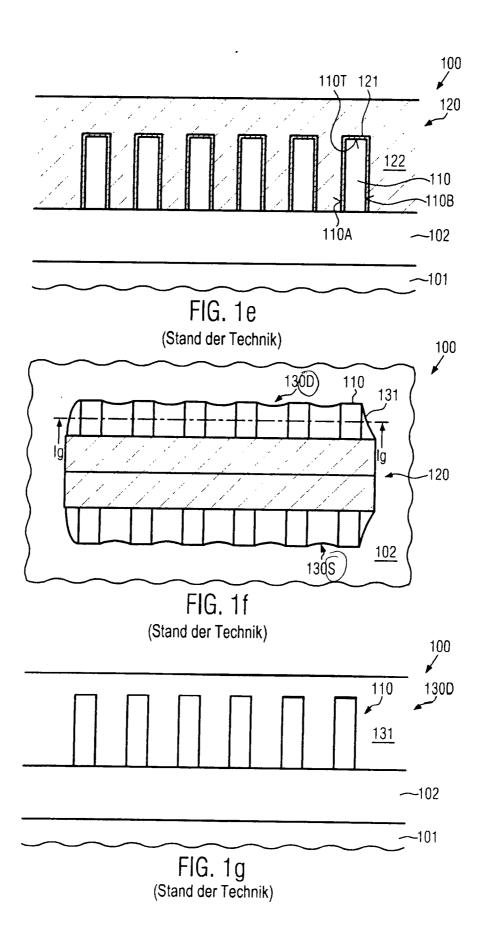

[0013] Fig. 1f zeigt schematisch eine Draufsicht

des Bauelements 100 nach dem Ende des selektiven epitaktischen Aufwachsprozesses, wodurch ein Siliziummaterial oder Silizium/Germanium-Material 131 auf beiden Seiten der Gateelektrodenstruktur 120 gebildet wurde, wodurch ein Drainbereich 130d und ein Sourcebereich 130s hergestellt werden. Wie gezeigt, können somit die Stege 110 mit einem Endbereich zu Drainbereich 130d zusammengefasst und ein weiterer Endbereich ist zum Sourcebereich 130s zusammengeschlossen.

[0014] Fig. 1g zeigt schematisch eine Querschnittsansicht durch den Drainbereich 130d, wo dargestellt ist, dass epitaktisch aufgewachsene Material 131 mit den Stegen 110 in direkten Kontakt ist, wodurch ein zusammenhängendes Drain gebildet wird, dessen Leitfähigkeit in geeigneter Weise durch Ionenimplantation und dergleichen angepasst werden kann, wobei zugehörige Abstandshalterstrukturen gebildet werden können, wie zuvor erläutert ist, um damit einen gewünschten Dotierstoffkonzentrationsgradienten in der Nähe der Gateelektrodenstruktur 120 (siehe Fig. 1f) zu schaffen.

[0015] Nach dem Erzeugen des gewünschten Dotierstoffprofils in den Drain- und Sourcebereichen 130d, 130s können weitere Prozesse ausgeführt, etwa Ausheizprozesse und dergleichen, woran sich das Abscheiden eines geeigneten dielektrischen Zwischenschichtmaterials anschließt, etwa in Form von Siliziumdioxid in Verbindung mit einem geeigneten Ätzstoppmaterial, etwa Siliziumnitrid, das dann strukturiert werden kann, um damit Kontaktöffnungen zu erhalten, die nachfolgend mit einem geeigneten leitenden Material gefüllt werden, etwa Wolfram und dergleichen.

[0016] Es sollte beachtet werden, dass mehrere aufwendige Fertigungstechniken typischerweise in ebenen Transistorkonfigurationen eingesetzt werden, um das gesamte Transistorverhalten zu verbessern. Beispielsweise wird eine geeignete Verformung in dem Kanalgebiet planerer Transistoren erzeugt und es werden auch aufwendige Gatedielektrikumsmaterialien in Verbindung mit gut leitenden Gateelektrodenmaterialien häufig eingesetzt, um die Kanalsteuerbarkeit zu erhöhen und die Signalausbreitungsverzögerung zu verringern. Obwohl die nicht-ebene Transistorkonfiguration des Bauelements 100 deutliche Vorteile im Hinblick auf das gesamte Transistorleistungsverhalten bietet, ist es dennoch äußerst wünschenswert, weitere leistungssteigernde Mechanismen einzubauen, die jedoch zusätzlich zu gesamten Komplexität beitragen. D. h., auf Grund der epitaktischen Aufwachsprozesse, die zumindest für die Bildung der Drain- und Sourcebereiche 130d, 130s erforderlich sind, möglicherweise in Verbindung mit zusätzlichen leistungssteigernden Mechanismen, ist der sich ergebende Fertigungsablauf ggf. nicht mehr mit den Erfordernissen für einen hohen Durchsatz verträglich, wodurch die zuvor beschriebenen konventionellen Prozesstechniken wenig wünschenswert in einer Fertigungsumgebung für die Massenproduktion sind.

[0017] In der WO 2007/038 575 A2 wird ein Verfahren zur Herstellung eines nicht-planeren CMOS-Transistors beschrieben, das den Schritt des Ausbildens einer Maskenschicht über Gebieten, in denen Gateelektroden ausgebildet werden sollen, und das nachfolgende Ausbilden von Öffnungen in der Maskenschicht über diesen Gebieten umfasst.

[0018] Im Hinblick auf die zuvor beschriebene Situation betrifft die vorliegende Offenbarung Bauelemente und Techniken zur Herstellung von nicht-ebenen Transistoren oder Mehr-Gatetransistoren, wobei eines oder mehrere der oben erkannten Probleme vermieden oder zumindest in der Auswirkung reduziert wird.

## Überblick über die vorliegende Offenbarung

[0019] Im Allgemeinen betrifft die vorliegende Offenbarung Halbleiterbauelemente mit Mehr-Gatetransistoren oder nicht-ebenen Transistorarchitekturen und dazugehörige Fertigungsverfahren, wobei ein insgesamt höherer Prozessdurchsatz erreicht wird, indem epitaktische Aufwachsprozesse vermieden werden, die konventioneller Weise zur Herstellung zusammenhängender Drain- und Sourcebereiche in Mehr-Gatetransistoren eingesetzt werden. Zu diesem Zweck werden die Stege des Mehr-Gatetransistors in einem räumlich beschränkten Bereich einer Halbleiterschicht hergestellt, der durch ein Maskenmaterial definiert ist, so dass ein maskierter Bereich des Halbleitermaterials als zusammenhängende Drain- und Sourcebereiche verwendet wird. In einigen anschaulichen Aspekten wird eine geeignete Platzhalterstruktur verwendet, um die Drain- und Sourcebereiche zu definieren und anschließend wird das Maskenmaterial so hergestellt, dass es die Platzhalterstruktur lateral umschließt, die nachfolgend selektiv zu dem Maskenmaterial entfernt wird, wodurch der Bereich zwischen den Drain- und Sourcebereichen freigelegt wird, in denen die Stege zu bilden sind. Folglich kann eine sehr effiziente und selbstjustierte Fertigungstechnik für das Bereitstellen der Stege in lokal beschränkter Weise erreicht werden, wobei ein epitaktischer Aufwachsprozess zur Herstellung der zusammenhängenden Drain- und Sourcegebiete vermieden wird. In noch anderen anschaulichen Ausführungsformen wird eine aufwendige Gateelektrodenstruktur nach dem Strukturieren der Stege in lokal beschränkter Weise hergestellt, indem ein dielektrisches Material mit großem ε verwendet wird, das als ein dielektrisches Material mit einer Dielektrizitätskonstanten von 10,0 und höher zu verstehen ist. in Verbindung mit einem gut leitenden Gateelektrodenmaterial. Folglich können effiziente leistungssteigernde Mechanismen eingerichtet werden, wobei dennoch ein Fertigungsprozess mit hohem Durchsatz bereitgestellt wird, indem ein epitaktischer Aufwachsprozess zur Herstellung der Drain- und Sourcebereiche des nicht-planaren Transistors vermieden wird.

[0020] Ein anschauliches hierin offenbartes Verfahren umfasst das Bilden einer Öffnung in eine Maskenmaterial, die über einer Halbleiterschicht eines Mehr-Gatetransistors gebildet ist, wobei die Öffnung laterale Abmessungen besitzt, die einer Gateelektrodenstruktur des Mehr-Gatetransistors entsprechen. Des weiteren umfasst das Verfahren das Strukturieren der Halbleiterschicht innerhalb der Öffnung, um Stege aus der Halbleiterschicht innerhalb der Öffnung zu bilden. Schließlich umfasst das Verfahren das Bilden der Gateelektrodenstruktur innerhalb der Öffnung in Anwesenheit der Stege. Das Bilden der Öffnung umfasst hierbei das Bilden einer Platzhalterstruktur über der Halbleiterschicht, laterales Einbetten der Platzhalterstruktur in das Maskenmaterial und Entfernen der Platzhalterstruktur selektiv zu dem Maskenmaterial.

[0021] Ein anschauliches hierin offenbartes Halbleiterbauelement umfasst ein zusammenhängendes Draingebiet und ein zusammenhängendes Sourcegebiet, die in einem Halbleitermaterial oder Transistors hergestellt sind. Das Bauelement umfasst ferner mehrere Stege, die sich zwischen den Drain- und Sourcegebieten erstrecken, wobei jeder Steg mit einer Endfläche einer ersten Grenzfläche mit dem Draingebiet und mit einer weiteren Endfläche eine zweite Grenzfläche mit dem Sourcegebiet bildet. Des weiteren umfasst das Halbleiterbauelement eine Gateelektrodenstruktur, die über den mehreren Stegen ausgebildet ist und eine erste Seitenwand besitzt, die auf der ersten Grenzfläche ausgebildet ist, und eine zweite Seitenwand besitzt, die zu der zweiten Grenzfläche ausgerichtet ist.

Kurze Beschreibung der Zeichnungen

**[0022]** Weitere Ausführungsformen der vorliegenden Offenbarung sind in den angefügten Patentansprüchen definiert und gehen deutlicher aus der folgenden detaillierten Beschreibung hervor, wenn diese mit Bezug zu den begleitenden Zeichnungen studiert wird, in denen:

**[0023]** Fig. 1a schematisch eine perspektivische Ansicht eines konventionellen Mehr-Gatetransistors in einer fortgeschrittenen Fertigungsphase zeigt;

**[0024]** Fig. 1b und Fig. 1c schematisch eine Draufsicht bzw. eine Querschnittsansicht des konventionellen Mehr-Gatetransistors in einer frühen Fertigungsphase zeigen;

**[0025]** Fig. 1d und Fig. 1e schematisch eine Draufsicht bzw. eine Querschnittsansicht des konventionellen Mehr-Gatetransistors nach der Herstellung einer Gateelektrodenstruktur zeigen;

**[0026]** Fig. 1f und Fig. 1g schematisch eine Draufsicht bzw. eine Querschnittsansicht des konventionellen Mehr-Gatetransistors nach dem Ausführen eines epitaktischen Aufwachsprozesses zur Bildung zusammenhängender Drain- und Sourcegebiete gemäß konventioneller Strategien zeigen;

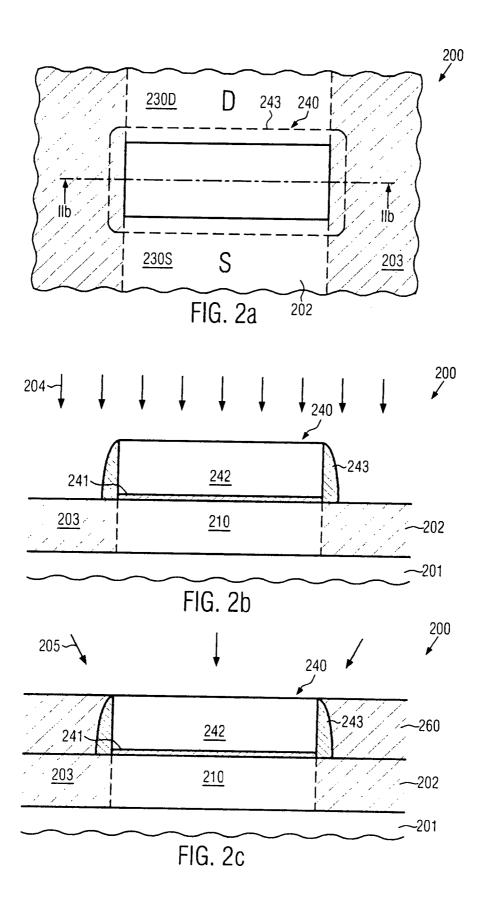

**[0027]** Fig. 2a und Fig. 2b schematisch eine Querschnittsansicht bzw. eine Draufsicht eines Halbleiterbauelements mit einem Mehr-Gatetransistor oder einem nicht-planaren Transistor in einer frühen Fertigungsphase gemäß anschaulicher Ausführungsformen zeigen;

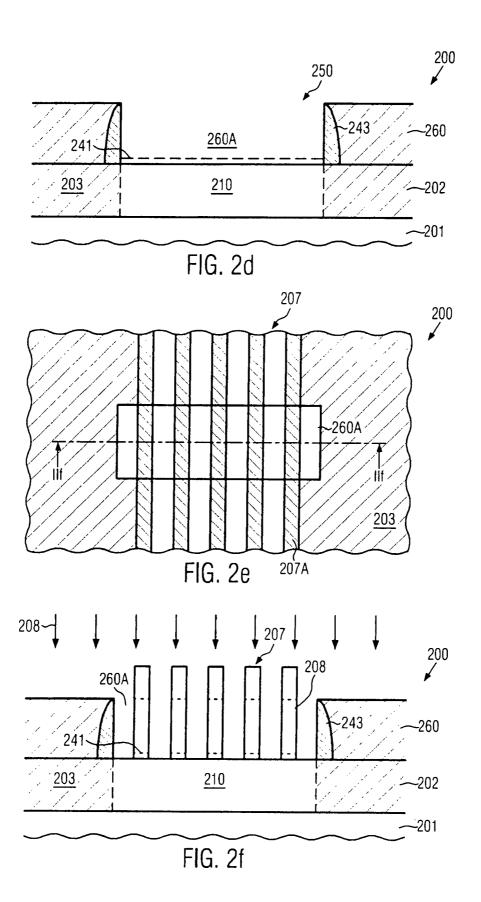

**[0028]** Fig. 2c und Fig. 2d schematisch Querschnittsansichten des Halbleiterbauelements in weiter fortgeschrittenen Fertigungsphasen zeigen, um einen räumlich beschränkten Bereich zur Herstellung von Stegen gemäß anschaulicher Ausführungsformen zu definieren;

**[0029]** Fig. 2e und Fig. 2f schematisch eine Draufsicht und eine Querschnittsansicht in einer Fertigungsphase während der Strukturierung eines freiliegenden Bereichs einer Halbleiterschicht gemäß anschaulicher Ausführungsformen zeigen;

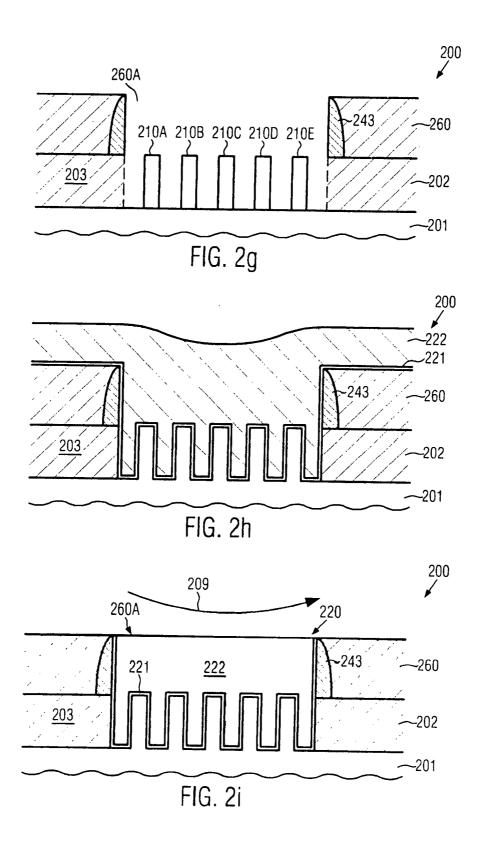

**[0030]** Fig. 2g bis Fig. 2i schematisch Querschnittsansichten eines Halbleiterbauelements während diverser Fertigungsphasen bei der Herstellung einer aufwendigen Gateelektrodenstruktur gemäß noch weiterer anschaulicher Ausführungsformen zeigen; und

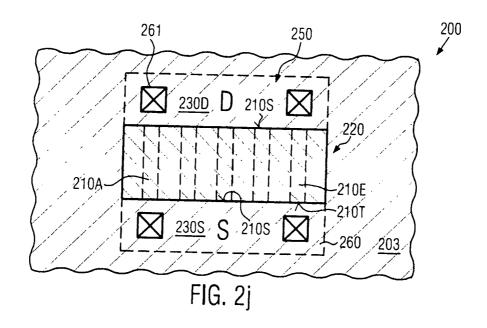

[0031] Fig. 2j schematisch eine Draufsicht des Halbleiterbauelements mit einem Mehr-Gatetransistors in einer fortgeschrittenen Fertigungsphase gemäß noch weiterer anschaulicher Ausführungsformen zeigt.

[0032] Im Allgemeinen betrifft die vorliegende Offenbarung bessere Fertigungstechniken und entsprechende Halbleiterbauelemente, in denen nicht-ebene Transistorkonfigurationen, die auch als Mehr-Gatetransistoren bezeichnet werden, so gebildet werden, dass Drain- und Sourcegebiete geschaffen werden, ohne dass epitaktisch Aufwachstechniken erforderlich sind. Zu diesem Zweck werden die Stege des Mehr-Gatetransistors auf der Grundlage eines Maskenmaterials strukturiert, das die Drain- und Sourcebereiche abdeckt, während ein Teil des Halbleitermaterials frei liegt, das als ein Kanalgebiet des Mehr-Gatetransistors verwendet wird. Nach dem Strukturieren der Transistorstege, die dem Kanalgebiet der nicht-planaren Transistorkonfiguration ent-

sprechen, wird die Gateelektrodenstruktur auf der Grundlage des Maskenmaterials hergestellt, wodurch eine selbstjustierte Technik in Bezug auf die Drain- und Sourcegebiete bereitgestellt wird. In einigen anschaulichen Ausführungsformen wird die Gateelektrodenstruktur auf der Grundlage aufwendiger Materialien, etwa ein dielektrisches Material mit großem ε für das Gateisolationsmaterial und ein metallenthaltendes Elektrodenmaterial, hergestellt, wodurch das Leistungsverhalten des Mehr-Gatetransistors weiter gesteigert wird. In einigen anschaulichen Ausführungsformen wird die Platzhalterstruktur auf der Grundlage gut etablierter Materialien hergestellt, etwa in Form von Polysilizium in Verbindung mit siliziumdioxidbasierten Materialien, wodurch ein hohes Maß an Kompatibilität mit gut etablierten Prozesstechniken erreicht wird, die auch für die Herstellung planarer Transistorelemente angewendet werden. Somit kann ein erhöhter Durchsatz des gesamten Fertigungsablaufs auf Grund des Vermeidens komplexer epitaktischer Aufwachstechniken und auf Grund der Möglichkeit der Verwendung gut etablierter Prozesstechniken erreicht werden, während gleichzeitig ein höheres Transistorleistungsverhalten durch die nicht-ebene Architektur erreicht wird, möglicherweise in Verbindung mit der komplexen Gateelektrodenstruktur. Somit kann das Leistungsverhalten von Transistorelementen durch Anwenden nicht-ebener Transistorarchitekturen weiter verbessert werden, wobei dennoch die Möglichkeit geschaffen wird, Massenherstellungstechniken einzusetzen.

[0033] Mit Bezug zu den Fig. 2a bis Fig. 2j werden nunmehr weitere anschauliche Ausführungsformen detaillierter beschrieben, wobei auch auf die Fig. 1a bis Fig. 1g bei Bedarf verwiesen wird.

[0034] Fig. 2a zeigt schematisch eine Draufsicht eines Teils eines Halbleiterbauelements 200, das ein oder mehrere Mehr-Gatetransistoren 250 in einer frühen Fertigungsphase umfasst. Es sollte beachtet werden, dass der Begriff "Mehr-Gatetransistor" so zu verstehen ist, dass dieser eine Transistorarchitektur bezeichnet, in der zwei oder mehr in eine nicht-ebene Konfiguration bildende Halbleiterflächen als ein Kanalgebiet verwendet werden. Das Bauelement 200 umfasst ein Substrat (in Fig. 2a nicht gezeigt), über welchem eine geeignete Halbleiterschicht 202 gebildet ist, die aus Silizium, Silizium/Germanium, Germanium oder einem anderen geeigneten Halbleitermaterial aufgebaut ist, das zur Herstellung des Transistorelements 250 verwendet wird. Es sollte beachtet werden, dass die Halbleiterschicht 202 einen oberen Bereich eines im Wesentlichen kristallinen Halbleitermaterials repräsentieren kann, während in anderen Fällen eine vergrabene isolierende Schicht zumindest teilweise innerhalb des Bauelements 200 vorgesehen ist, um eine SOI-(Silizium-auf-Isolator-)Konfiguration zu bilden. Des weiteren enthält das Halbleitermaterial 202 geeignet gestaltete Isolationsstrukturen 203, die entsprechende aktive Gebiete definieren, d. h. Gebiete, in denen ein oder mehrere Transistorelemente herzustellen sind, etwa der Transistor 250. Z. B. wird die Isolationsstruktur 203 in Form einer flachen Grabenisolation bereitgestellt, die sich bis hinab zu einer gewünschten Tiefe einer Halbleiterschicht 202 erstreckt oder die sich bis hinab zu einer vergrabenen isolierenden Schicht erstreckt, falls diese vorgesehen ist. In der gezeigten Fertigungsphase umfasst der Transistor 250 eine Platzhalterstruktur 240, deren laterale Abmessungen gemäß einer anschaulichen Ausführungsform im Wesentlichen den lateralen Abmessungen einer Gateelektrodenstruktur des Transistors 250 entsprechen, die noch zu bilden ist. In dem gezeigten Beispiel ist an Seitenwänden der Platzhalterstruktur 240 eine Abstandshalterstruktur 243 mit einer geeigneten Breite gebildet, wie dies zum Definieren eines geeigneten Dotierstoffprofils in zugehörigen Drain- und Sourcegebieten 230d, 230s wünschenswert ist, die in der Halbleiterschicht 202 ausgebildet sind. Beispielsweise wird die Abstandshalterstruktur 243 verwendet. um einen lateralen Abstand einer Dotierstoffkonzentration in Bezug auf die Platzhalterstruktur 240 einzustellen, die durch eine tatsächliche Gateelektrodenstruktur in einer späteren Fertigungsphase ersetzt

[0035] Fig. 2b zeigt schematisch eine Querschnittsansicht des Bauelements 200 entlang der Linie IIb aus Fig. 2a. Wie gezeigt, ist die Platzhalterstruktur 240 über einem Bereich der Halbleiterschicht 202 gebildet, der als 210 bezeichnet ist und der einen Bereich der Halbleiterschicht 202 repräsentiert, in welchem entsprechende Stege oder nicht-planare Kanalgebiete in einer späteren Fertigungsphase zu bilden sind. Die Platzhalterstruktur 240 umfasst in einer anschaulichen Ausführungsform eine Ätzstoppschicht 241, beispielsweise in Form eines geeigneten Materials, etwa Siliziumdioxid, Siliziumnitrid und dergleichen, während auf anderen Materialien, etwa dielektrische Materialien mit großem ε, beispielsweise in Form von Hafniumoxid und dergleichen, verwendet werden können. Es sollte beachtet werden, dass in einigen anschaulichen Ausführungsformen die Ätzstoppschicht **241** als ein Gatedielektrikumsmaterial in Bauteilgebieten verwendet werden kann, in denen planare Transistorelemente auf der Grundlage konventioneller Prozesstechnologien hergestellt werden. In noch anderen anschaulichen Ausführungsformen wird das Ätzstoppmaterial 241 so gewählt, dass dieses als ein Hartmaskenmaterial während der weiteren Bearbeitung dient, wenn das Halbleitergebiet 210 in individuelle Stege strukturiert wird. Ferner kann ein Platzhaltermaterial 242 in der Struktur 240 vorgesehen sein, beispielsweise in Form eines dielektrischen Materials, eines leitenden Materials, etwa Polysilizium und dergleichen. In einer anschaulichen Ausführungsform wird das Platzhaltermaterial 242 in Form eines Polysiliziummaterials vorgesehen, wodurch für

ein hohes Maß an Kompatibilität zu gut etablierten Transistorfertigungstechniken gesorgt ist. Des weiteren kann die Abstandshalterstruktur **243** bei Bedarf mit einer beliebigen geeigneten Konfiguration vorgesehen werden, etwa in Form eines oder mehrerer Abstandshalterelemente, die aus Siliziumnitrid, Siliziumdioxid und dergleichen aufgebaut sind, möglicherweise in Verbindung mit zugehörigen Ätzstoppschichten (nicht gezeigt), wobei dies von der gesamten Komplexität der Abstandshalterstruktur **243** und der verwendeten Prozessstrategie abhängt.

[0036] Das in den Fig. 2a und Fig. 2b gezeigte Halbleiterbauelement 200 kann auf der Grundlage der folgenden Prozesse hergestellt werden. Nach dem Bereitstellen des Substrats 201, auf denen die Halbleiterschicht 202 gebildet ist, werden die Isolationsstrukturen 203 hergestellt, etwa durch gut etablierte Fertigungstechniken, die ähnlich sind zu Techniken, wie sie für die Herstellung planarer Transistorelemente angewendet werden. Beispielsweise werden aufwendige Lithographie-, Ätz-, Abscheide- und Einebnungstechniken eingesetzt, um die Isolationsstrukturen 203 so zu schaffen, dass entsprechende aktive Bereiche in der Schicht 202 gebildet sind. Vor oder nach dem Herstellen der Isolationsstrukturen 203 wird ein gewünschtes grundlegendes Dotierstoffprofil in der Halbleiterschicht 202 erzeugt, beispielsweise zur Einstellung entsprechender Kanaldotierstoffkonzentrationen und auch zur Einstellung der gesamten Leitfähigkeitsart des Transistors 250. Als nächstes wird die Ätzstoppschicht 241 hergestellt, beispielsweise durch Oxidation, Abscheidung oder die Kombination davon, Oberflächenbehandlung und dergleichen. In einigen anschaulichen Ausführungsformen wird ein geeignetes Material verwendet, das den nachfolgenden Hochtemperaturprozessen wiedersteht, die während der weiteren Bearbeitung des Bauelements 200 angewendet werden. Danach wird das Material 242 abgeschieden, etwa auf der Grundlage gut etablierter CVD-(chemische Dampfabscheide-)Techniken, woran sich ein anspruchsvolles Strukturierungsschema anschließt, das auf der Basis von Lithographie- und Ätztechniken ausgeführt wird. Somit können während des entsprechenden Strukturierungsprozesses die lateralen Abmessungen der Platzhalterstruktur 240 definiert werden und entsprechen in einigen anschaulichen Ausführungsformen den lateralen Abmessungen einer Gateelektrodenstruktur des Transistors 250. Während der Strukturierung des Materials 242 kann die Schicht 241 als ein Ätzstoppmaterial dienen, wobei, wie zuvor erläutert ist, eine Vielzahl gut etablierter Ätzrezepte verfügbar sind. Als nächstes wird eine Sequenz aus Implantationsprozessen 204 ausgeführt, etwa auf der Grundlage der Abstandfshalterstruktur 243 mit einem geeigneten Aufbau, um damit eine gewünschte Dotierstoffkonzentration und ein gewünschtes Profil in den Drain- und Sourcegebieten 230d, 230s (siehe Fig. 2a) zu erzeugen. Es sollte beachtet werden,

dass in anderen anschaulichen Ausführungsformen zusätzliche Prozessschritte eingerichtet werden, beispielsweise in Bezug auf das Vorsehen weiterer leistungssteigender Mechanismen. Z. B. wird ein verformungsinduzierendes Material in die Drain- und Sourcebereiche 230d, 230s eingebaut, um eine Zugverformungskomponente oder eine kompressive Verformungskomponente entlang der Stromflussrichtung in dem Gebiet 210 hervorzurufen, wobei dies die Richtung senkrecht zur Zeichenebene der Fig. 2b ist. Zu diesem Zweck können verformungsinduzierende Halbleiterlegierungen, etwa Silizium/Germanium, Silizium/Kohlenstoff und dergleichen in eine Siliziumbasismaterialschicht eingebaut werden, um damit die gewünschte Verformungskomponente zu erhalten Anschließend wird eine Wärmebehandlung ausgeführt, um das schließlich gewünschte Gesamtdotierprofil in den Drain- und Sourcegebieten 230d, 230s zu erhalten.

[0037] Fig. 2c zeigt schematisch das Halbleiterbauelement 200 in einer weiter fortgeschrittenen Fertigungsphase. Wie gezeigt ist ein dielektrisches Material 260 so gebildet, dass dieses die Platzhalterstruktur 240 lateral umschließt. Das dielektrische Material 260, das auch als ein Maskenmaterial bezeichnet wird, bedeckt somit die Drain- und Sourcebereiche 230b, 230s (siehe Fig. 2a), während das Material 242 der Struktur 240 frei liegt. Das dielektrische Material 260 kann nach dem Ende der zuvor mit Bezug zu den Fig. 2a und Fig. 2b beschriebenen Prozesssequenz hergestellt werden, beispielsweise durch Abscheiden eines beliebigen geeigneten Materials, etwa Siliziumdioxid, Siliziumnitrid, stickstoffenthaltendes Siliziumkarbid und dergleichen. Nach dem Abscheiden des Materials 260 wird ein Einebnungsprozess ausgeführt, der einen CMP-(chemisch-mechanischer Polier-)Prozess enthalten kann, wodurch die Oberflächentopographie eingeebnet wird, wobei der Einebnungsprozess fortgesetzt werden kann, bis das Platzhaltermaterial 242 freigelegt ist. Anschließend wird das Bauelement 200 einem Ätzprozess 205 unterzogen, das so gestaltet ist, das Material 242 selektiv zu dem dielektrischen Material oder Maskenmaterial 260 und auch selektiv zu dem Ätzstoppmaterial 241 abgetragen wird, wenn ein freiliegendes Material 210 in der Ätzumgebung 205 als ungeeignet erachtet wird. Beispielsweise sind eine Vielzahl gut etablierter sehr selektiver Ätzrezepte für Polysiliziummaterial verfügbar, das effizient selektiv zur Siliziumdioxidmaterial abgetragen werden kann. Es sollte jedoch beachtet werden, dass eine beliebige andere Materialzusammensetzung für das Hartmaskenmaterial 260 und das Platzhaltermaterial 242 ausgewählt werden kann, solange das Material 242 selektiv in Bezug auf das Maskenmaterial 260 abgetragen werden kann. In einer anschaulichen Ausführungsform wird das Material 242, das in Form eines Polysiliziummaterials vorgesehen ist, effizient auf Grundlage eines nasschemischen Ätzrezepts unter Anwendung von TMAH (Tetramethylammoniumhydroxid) entfernt. TMAH wird effizient Siliziummaterial bei höheren Temperaturen im Bereich von ungefähr 50 bis 80 Grad C, wobei dennoch ein hohes Maß an Selektivität in Bezug auf Siliziumnitrid und Siliziumdioxid gegeben ist. Folglich wird das Material 242 effizient abgetragen, während gleichzeitig der Ätzprozess zuverlässig an der Schicht 242 anhält, wenn dieser in Form von Siliziumdioxidmaterial, Siliziumnitridmaterial und dergleichen vorgesehen wird.

[0038] Fig. 2d zeigt schematisch das Halbleiterbauelement 200 nach dem Entfernen des Materials 242. wodurch eine Öffnung 260a in dem Maskenmaterial 260 gebildet wird, wobei auch die Abstandshalterstruktur 240 beibehalten wird. In einer anschaulichen Ausführungsform wird auch das Ätzstoppmaterial 241 innerhalb der Öffnung 260a durch Ausführen eines weiteren Ätzprozesses, etwa eines nasschemischen Ätzprozesses unter Anwendung gut etablierter Rezepte entfernt. Z. B. kann Siliziumdioxidmaterial effizient mittels Flusssäure und dergleichen abgetragen werden. In anderen anschaulichen Ausführungsformen wird die Ätzstoppschicht 241 beibehalten und wird als ein Hartmaskenmaterial zum Strukturieren des Halbleitergebiets 210 in einer nachfolgenden Fertigungsphase verwendet. Nach dem Bilden der Öffnung 260a wird somit ein Lithographieprozess ausgeführt, um eine Lackmaske zu erzeugen, die die lateralen Abmessungen entsprechender Stege des Transistors 250 definiert. Zu diesem Zweck wird in einigen anschaulichen Ausführungsformen die Öffnung 260a mit einem geeigneten Material, etwa einem Polymermaterial, einem Lackmaterial und dergleichen aufgefüllt, das zusätzlich als ein ARC-Material dienen kann, um das Verhalten des nachfolgenden Lithographieprozesses zu verbessern.

[0039] Fig. 2e zeigt schematisch eine Draufsicht des Bauelements 200, wobei entsprechende Lackstrukturelemente 207a einer Lackmaske 207 so vorgesehen sind, dass diese sich entlang einer Kanallängsrichtung über die Öffnung 206a hinweg erstrecken, wodurch die Größe und die Lage der entsprechenden noch herzustellenden Stege definiert wird.

[0040] Fig. 2f zeigt schematisch eine Querschnittsansicht des Bauelements aus Fig. 2e. Wie gezeigt, ist die Lackmaske 207 auf einem entsprechenden Füllmaterial 208 gebildet, beispielsweise ein weiteres Lackmaterial, ein Polymermaterial und dergleichen, wie dies zuvor erläutert ist. Z. B. werden Materialien durch Aufschleudertechniken möglicherweise in Verbindung mit einem nachfolgenden Einebnungsprozess aufgebracht. Danach wird das eigentliche Lackmaterial vorgesehen und durch Lithographie strukturiert. Daraufhin wird das Füllmaterial 208 auf der Grundlage eines geeigneten Ätzrezepts strukturiert. Es sollte beachtet werden, dass andere Prozessstrategien eingesetzt werden können; beispielsweise re-

präsentiert das Füllmaterial 208 einen Teil eines Lackmaterials der Ätzmaske 207, wenn geeignete Belichtungsbedingungen innerhalb der Öffnung 260a erreicht werden. In anderen anschaulichen Ausführungsformen wird die Ätzmaske 207 zum Strukturieren der Ätzstoppschicht 241 verwendet, wodurch weniger kritische Lithographiebedingungen erhalten werden, da beispielsweise eine geringere Dicke der Lackmaske 207 anwendbar ist. Nach dem Vorsehen der Maske 207 wird das Bauelement 200 der Einwirkung einer Ätzumgebung 208 ausgesetzt, die so gestaltet ist, dass das Muster der Ätzmaske 207 oder der Hartmaske 241 in das Halbleitergebiet 210 übertragen wird. Zu diesem Zweck sind gut etablierte anisotrope Ätzrezepte verfügbar für eine Vielzahl von Materialien, etwa für Silizium, Silizium/Germanium und dergleichen. Während des Ätzprozesses 208 bedeckt das Maskenmaterial 260 zuverlässig die Drainund Sourcebereiche 230d, 230s (siehe Fig. 2a).

[0041] Fig. 2g zeigt schematisch das Halbleiterbauelement 200 nach dem Ätzprozess 208 und dem Entfernen der Ätzmaske 207, 208 oder nach dem Entfernen der Hartmaske 241. Wie gezeigt, sind somit entsprechende Stege 210a, ..., 210e aus dem Halbleitergebiet 210 (siehe Fig. 2f) hergestellt, wobei die lateralen Abmessungen der Stege 210a, ..., 210e im Wesentlichen durch die Ätzmaske 207 (siehe Fig. 2f) bestimmt sind, während eine Höhe durch eine Dicke der anfänglichen Halbleiterschicht 202 oder entsprechende Ätzparameter, etwa der Ätzzeit bei vorgegebener Abtragsrate, festgelegt ist. Andererseits ist die Ausdehnung der Stege 210a, ..., 210e entlang der Stromflussrichtung oder entlang der Kanallängsrichtung, d. h. in Fig. 2g der Richtung senkrecht zur Zeichenebene, im Wesentlichen durch die entsprechende Abmessung der Öffnung 260a bestimmt.

[0042] Fig. 2h zeigt schematisch das Halbleiterbauelement 200 in einer weiter fortgeschrittenen Fertigungsphase, in der ein Gatedielektrikumsmaterial 221 auf dem Maskenmaterial 260 und auf freiliegenden Oberflächenbereiche der Stege 210a, ..., 210e gebildet ist. In einigen anschaulichen Ausführungsformen wird das Gatedielektrikumsmaterial 221 in Form eines dielektrischen Materials mit großem ε vorgesehen, etwa in Form eines oder mehrerer der zuvor im Zusammenhang mit konventionellen planaren Transistorarchitekturen erwähnten Materialien. Des weiteren ist ein Gateelektrodenmaterial 221 so gebildet, dass es zuverlässige Öffnung 260a füllt. Z. B. wird das Gateelektrodenmaterial 222 in Form eines metallenthaltenden Materials bereitgestellt, beispielsweise in Form von Titannitrid, Wolfram, und dergleichen, um eine geeignete Austrittsarbeit in Bezug auf die Kanalgebiete zu erreichen, die durch die Stege 210a, ..., 210e bereitgestellt werden. Das Gatedielektrikumsmaterial 221 kann beispielsweise durch Oxidation, Abscheidung und dergleichen auf der Grundlage gut etablierter Prozesstechniken hergestellt werden. In ähnlicher Weise wird das Material **222** unter Anwendung verfügbarer Prozessrezepte abgeschieden, die auch bei der Herstellung planarer Transistorarchitekturen eingesetzt werden können.

[0043] Fig. 2i zeigt schematisch das Halbleiterbauelement 200 während eines Einebnungsprozesses 209, der einen CMP-Prozess und dergleichen umfasst. Während des Einebnungsprozesses 209 wird überschüssiges Material des Gateelektrodenmaterials 222 entfernt, wodurch eine Gateelektrodenstruktur 220 entsteht, die das Gateelektrodenmaterial 222 und das Gatedielektrikumsmaterial 221 aufweist. In der gezeigten Ausführungsform wird der Einebnungsprozess 209 so fortgesetzt, dass leitendes Material von oberhalb des Maskenmaterials 260 zuverlässig abgetragen wird, was beispielsweise auch zum Abtragen des Gatedielektrikumsmaterials 221 außerhalb der Öffnung 260a führen kann.

[0044] Fig. 2j zeigt schematisch eine Draufsicht des Halbleiterbauelements 200 nach der zuvor beschriebenen Prozesssequenz. Wie gezeigt, umfasst das Bauelement 200 den Mehr-Gatetransistor 250 mit der Gateelektrodenstruktur 220, deren laterale Abmessung im Wesentlichen durch die Platzhalterstruktur 240 (siehe Fig. 2a) festgelegt ist. Die Stege 210a, ..., 210e, die als gestrichelte Linien dargestellt sind, erstrecken sich zwischen den Drain- und Sourcegebieten 230d, 230s, die noch von dem Maskenmaterial 260 bedeckt sind. Wie gezeigt, besitzt auf Grund der zuvor beschriebenen Prozessstrategie jeder der Stege 210a, ..., 210e eine erste Endfläche 210s, die mit dem Draingebiet 210d verbunden ist, und besitzt auch eine zweite Endfläche 210t, die mit dem Sourceaebiet 230s verbunden ist. Des weiteren sind die Endflächen 210s zu einer ersten Seitenwand 220s der Gateelektrodenstruktur 220 ausgerichtet und in ähnlicher Weise sind die zweiten Endflächen 210t zu einer zweiten Seitenwand 220t ausgerichtet. Folglich werden die Drain- und Sourcegebiete 230d, 230s bereitgestellt, ohne dass epitakische Aufwachstechniken angewendet werden, die typischerweise in konventionellen Prozessstrategien eingesetzt werden, in die Stege 210a, ..., 210e räumlich auf den Bereich beschränkt werden, der durch die Gateelektrodenstruktur 220 bedeckt ist. In einigen anschaulichen Ausführungsformen wird die Gateelektrodenstruktur 220 auf der Grundlage aufwendiger dielektrischer Materialien mit großem ε in Verbindung mit metallenthaltenden gut leitenden Elektrodenmaterialien vorgesehen. Nach der Herstellung der Gateelektrodenstruktur **220** wird die weitere Bearbeitung fortgesetzt, indem ein weiteres dielektrisches Material bereitgestellt wird und darauf und darin eine oder mehrere Metallisierungsschichten gemäß den gesamten Prozesserfordernissen hergestellt wird. Ferner werden entsprechende Kontaktelemente 261 in dem Maskenmaterial 260 zum Vorsehen eines zusätzlichen dielektrischen Materials hergestellt, wobei ebenfalls gut etablierte Prozesstechniken eingesetzt werden können.

[0045] Es gilt also: Die vorliegende Offenbarung stellt Mehr-Gatetransistoren und entsprechende Fertigungstechniken bereit, in denen reduzierte Prozesszeiten und damit ein höherer Durchsatz erreicht werden kann, indem zumindest ein epitaktischer Aufwachsprozess im Vergleich zu konventionellen Strategien vermieden wird, wobei gleichzeitig gut etablierte Prozesstechniken eingesetzt werden können, die für Prozesstechniken zur Herstellung planarer Transistorelemente ebenfalls verfügbar sind. In einigen anschaulichen Ausführungsformen wird eine Platzhalterstruktur eingesetzt, um die Drain- und Sourcegebiete vor der Herstellung der entsprechenden Transistorstege zu definieren, die in den Halbleitermaterial in einer räumlich beschränkten Weise durch Entfernen der Platzhalterstruktur strukturiert werden. Folglich erstrecken sich die jeweiligen Stege lediglich über die Gateelektrodenstrukturen und münden in den Drain- und Sourcegebieten. Es sollte beachtet werden, dass die hierin offenbarten Prinzipien effizient auf eine beliebige Art von Mehr-Gatetransistoren angewendet werden können, beispielsweise p-Kanaltransistoren und n-Kanaltransistoren, wobei die entsprechende Prozesssequenz individuell auf die einzelne Transistorart jeweils angewendet wird, während in anderen Fällen beide Transistorarten in einer gemeinsamen Fertigungssequenz gebildet werden. D. h., die Drain- und Sourcegebiete werden auf der Grundlage gut etablierter Maskierungsschemata auf Basis entsprechender Platzhalterstrukturen erzeugt. Anschließend wird die Platzhalterstruktur in einer gemeinsamen Prozesssequenz entfernt, wie dies zuvor beschrieben ist, und die entsprechenden Stege für die unterschiedlichen Arten von Transistoren werden auf der Grundlage einer Prozesssequenz hergestellt, wie sie zuvor beschrieben ist. Daraufhin wird Gateelektrodenmaterial in unterschiedlichen Prozessschritten vorgesehen, um in geeigneter Weise die Austrittsarbeit des Gateelektrodenmaterials an die Art des betrachteten Transistors anzupassen. Zu diesem Zweck kann beispielsweise eine Transistorart maskiert werden, während das Gateelektrodenmaterial für die andere Transistorart abgeschieden wird und nach dem Entfernen von überschüssigen Material wird die Maske dann entfernt, die beispielsweise in Form eines Füllmaterials vorgesehen wird, und es wird ein weiteres Gateelektrodenmaterial abgeschieden und durch CMP und dergleichen eingeebnet.

### Patentansprüche

#### 1. Verfahren mit:

Bilden einer Öffnung (260a) in einem Maskenmaterial (260), das über einer Halbleiterschicht (202) eines Mehr-Gatetransistors (250) gebildet ist, wobei die Öffnung (260a) laterale Abmessungen aufweist, die einer Gateelektrodenstruktur (220) des Mehr-Gate-

transistors (250) entsprechen;

Strukturieren der Halbleiterschicht (202) innerhalb der Öffnung (260a), so dass Stege (210a, ..., 210e) aus der Halbleiterschicht (202) innerhalb der Öffnung (260a) gebildet werden; und

Bilden der Gateelektrodenstruktur (220) innerhalb der Öffnung (260a) in Anwesenheit der Stege (210a, ..., 210e),

wobei Bilden der Öffnung (260a) umfasst: Bilden einer Platzhalterstruktur (240) über der Halbleiterschicht (202), laterales Einbetten der Platzhalterstruktur (240) in das Maskenmaterial (260) und Entfernen der Platzhalterstruktur (240) selektiv zu dem Maskenmaterial (260).

- Verfahren nach Anspruch 1, das ferner umfasst: Bilden von Drain- und Sourcegebieten (230d, 230s) auf der Grundlage der Platzhalterstruktur (240).

- 3. Verfahren nach Anspruch 1, wobei Bilden der Gateelektrodenstruktur (220) umfasst: Bilden eines Gatedielektrikumsmaterials (221) auf den Stegen und Bilden eines Gateelektrodenmaterials in der Öffnung (260a).

- 4. Verfahren nach Anspruch 3, wobei das Gatedielektrikumsmaterial (**221**) ein dielektrisches Material mit großem  $\epsilon$  aufweist.

- 5. Verfahren nach Anspruch 3, wobei das Gateelektrodenmaterial ein metallenthaltendes Material aufweist.

- 6. Verfahren nach Anspruch 1, wobei Bilden der Platzhalterstruktur (240) umfasst: Bilden einer Ätzstoppschicht und Abscheiden eines dielektrischen Materials auf der Ätzstoppschicht.

- 7. Verfahren nach Anspruch 1, wobei die Platzhalterstruktur (**240**) Polysilizium aufweist.

- 8. Verfahren nach Anspruch 7, wobei das Polysilizium durch Ausführen eines nasschemischen Ätzprozesses entfernt wird.

- 9. Verfahren nach Anspruch 8, wobei der nasschemische Ätzprozess auf der Grundlage von TMAH (Tetramethylammoniumhydroxid) ausgeführt wird.

- 10. Verfahren nach Anspruch 1, das ferner umfasst: Bilden von Drain- und Sourcegebieten (230d, 230s) vor dem Strukturieren der Halbleiterschicht (202) innerhalb der Öffnung (260a).

- 11. Verfahren nach Anspruch 1, das ferner umfasst: Bilden von Drain- und Sourcegebieten (230d, 230s) nach dem Bilden der Gateelektrodenstruktur (220).

12. Halbleiterbauelement (200) mit: einem zusammenhängenden Draingebiet (230d) und einem zusammenhängenden Sourcegebiet (230s), die in einem Halbleitermaterial (202) eines Transistors (250) ausgebildet sind;

mehreren Stegen (210a, ..., 210e), die sich zwischen dem Draingebiet (230d) und dem Sourcegebiet (230s) erstrecken, wobei jeder der Stege (210a, ..., 210e) eine erste Endfläche, die mit dem Draingebiet (230d) verbunden ist und eine zweite Endfläche, die mit dem Sourcegebiet (230s) verbunden ist, aufweist; und

einer Gateelektrodenstruktur (220), die über den mehreren Stegen gebildet ist, wobei die Gateelektrodenstruktur (220) eine erste Seitenwand, die über der ersten Endfläche ausgerichtet ist, und eine zweite Seitenwand aufweist, die zu der zweiten Endfläche ausgerichtet ist.

- 13. Halbleiterbauelement (200) nach Anspruch 12, wobei die Gateelektrodenstruktur (220) eine Gatedielektrikumsschicht mit großem  $\epsilon$  aufweist, die zumindest an Seitenwänden der Stege (210a, ..., 210e) ausgebildet ist.

- 14. Halbleiterbauelement (**200**) nach Anspruch 13, wobei die Gateelektrodenstruktur (**220**) ein metallenthaltendes Elektrodenmaterial aufweist, das mit der Gatedielektrikumsschicht mit großem  $\epsilon$  in Kontakt ist.

Es folgen 7 Blatt Zeichnungen

# Anhängende Zeichnungen