(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4450743号 (P4450743)

(45) 発行日 平成22年4月14日(2010.4.14)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int. Cl.

GO3F 1/08 (2006.01) HO1L 21/027 (2006.01) GO3F 1/08 A HO1L 21/30 5O2P

請求項の数 6 (全 17 頁)

(21) 出願番号

特願2005-31676 (P2005-31676)

(22) 出願日

平成17年2月8日 (2005.2.8) 特開2006-220725 (P2006-220725A)

FL

(65) 公開番号 (43) 公開日

平成18年8月24日 (2006. 8. 24)

審査請求日

平成18年8月24日 (2006. 8. 24) 平成18年3月27日 (2006. 3. 27)

||(73)特許権者 308014341

富士通マイクロエレクトロニクス株式会社 東京都新宿区西新宿二丁目7番1号

|(74)代理人 100092152

弁理士 服部 毅巖

(72) 発明者 石渡 直行

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 佐藤 海

最終頁に続く

(54) 【発明の名称】フォトマスク、フォトマスクの製造方法及び半導体装置の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とが順に積層され、 所望のパターン形状の開口により、半導体チップに転写するチップ領域には回路パターン 、前記チップ領域外には非回路パターンが形成されたフォトマスクにおいて、

前記チップ領域では、前記遮光層が除去され、且つ、前記回路パターンに応じた開口がなされた前記位相シフト層が露出しており、

前記チップ領域の周囲に、前記チップ領域から15mm以内の領域において前記遮光層のみが開口され、その開口部に前記位相シフト層が露出した、前記回路パターンの位置精度を測定するための位置精度測定用モニタパターンと、前記チップ領域から15mmを超える領域において前記遮光層及び前記位相シフト層の両方が開口され、その開口部に前記透明基板が露出した、露光装置との位置合わせを行うためのフィディシャルパターンとを含む非回路パターンを有したことを特徴とするフォトマスク。

## 【請求項2】

前記チップ領域から15mm以内の範囲に存在する前記非回路パターンの前記開口部には、前記位相シフト層が露出していることを特徴とする請求項1記載のフォトマスク。

# 【請求項3】

前記位相シフト層と前記遮光層は、それぞれ選択的にエッチング可能な材料にて構成されていることを特徴とする請求項 1 記載のフォトマスク。

### 【請求項4】

前記遮光層は、クロムとクロム酸化物の積層膜で構成されていることを特徴とする請求 項1記載のフォトマスク。

## 【請求項5】

露光光の位相を変化させる機能を有するフォトマスクの製造方法において、

透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とを順に積層する工程と、

半導体チップに転写するチップ領域の回路パターン及び前記チップ領域外の、<u>前記チップ領域から15mm以内の領域に形成される、</u>前記回路パターンの位置精度を測定するための位置精度測定用モニタパターンと、<u>前記チップ領域から15mmを超える領域に形成される、</u>露光装置との位置合わせを行うためのフィディシャルパターンとを含む非回路パターンのパターン形状の開口部を前記遮光層に形成する工程と、

前記チップ領域及び、前記チップ領域外の領域のうち、前記フィディシャルパターンが 形成される領域が開口され、且つ、前記位置精度測定用モニタパターンが形成される領域 を覆うようなレジストパターンを形成し、前記レジストパターンと前記チップ領域に露出 している前記遮光層をマスクとして前記位相シフト層をエッチングする工程と、

前記チップ領域内の前記遮光層を除去する工程と、

を有することを特徴とするフォトマスクの製造方法。

#### 【請求項6】

半導体装置の製造方法において、

透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とが順に積層され、所望のパターン形状の開口により、半導体チップに転写するチップ領域には回路パターン、前記チップ領域外には非回路パターンが形成されたフォトマスクであって、前記チップ領域では前記遮光層が除去され、且つ、前記回路パターンに応じた開口がなされた前記位相シフト層が露出しており、前記チップ領域の周囲に、前記チップ領域から15mm以内の領域において前記遮光層のみが開口され、その開口部に前記位相シフト層が露出した、前記回路パターンの位置精度を測定するための位置精度測定用モニタパターンと、前記チップ領域から15mmを超える領域において前記遮光層及び前記位相シフト層の両方が開口され、その開口部に前記透明基板が露出した、露光装置との位置合わせを行うためのフィディシャルパターンとを含む非回路パターンを有したフォトマスクを用いて露光を行う露光工程を有することを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

# 【技術分野】

## [0001]

本発明はフォトマスク、フォトマスクの製造方法及び半導体装置の製造方法に関し、特に、特に露光光の位相を変化させる機能を有するフォトマスクと、その製造方法及びそのようなフォトマスクを用いた半導体装置の製造方法に関する。

# 【背景技術】

### [0002]

近年のLSI(Large Scale Integrated circuit)製造においては、非常に微細なパターンの形成が要求されている。そのため、微細回路パターンを半導体基板(以下ウェハという。)上に転写する露光工程時に、露光光の位相を変化させコントラストを上げる機能を有したフォトマスク(以下位相シフトマスクという。)が用いられるようになっている。中でもハーフトーン型と称される方式は、製造の簡便さなどから現在のデバイス製造で広く使用されている。

### [0003]

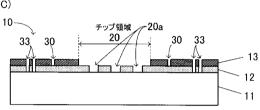

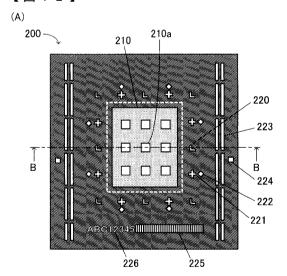

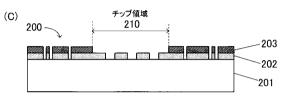

図12は、従来の代表的なハーフトーン型の位相シフトマスクの構造を示す図であり、(A)は平面図であり、(B)はB-B線での断面図である。

従来のハーフトーン型の位相シフトマスク200は、合成石英基板などの透明基板20 1上に順に形成された、半透明のハーフトーン位相シフト層(以下位相シフト層という。

) 202、遮光層203から構成される。半導体チップ(以下単にチップという。)に転

20

10

30

40

写される回路パターン 2 1 0 a が形成されるチップ領域 2 1 0 では、遮光層 2 0 3 が除去されており、形成する回路パターン 2 1 0 a に応じた開口がなされた位相シフト層 2 0 2 が露出されている。露光工程の際には、このチップ領域 2 1 0 において、透明基板 2 0 1 が露出している領域では露光光がそのまま透過され、位相シフト層 2 0 2 が露出している領域では、露光光の位相が 1 8 0 度反転される。

### [0004]

一方、チップ領域210の外側の領域は、ウェハに回路パターンを転写する際に、隣接するチップへの多重露光を防止するために、遮光層203を残すような構成となっている(例えば、特許文献1参照)。そしてこの領域にも各種のパターンが形成される。例えば、回路パターン210aの位置精度測定用のモニタパターン220、マスク描画装置で位相シフトマスク200の製造時において、重ね合わせ描画を行う際のアライメント用ターゲットパターン221、重ね合わせ描画を行う際に用いるアライメント精度測定用パターン222、露光装置(ステッパまたはスキャナ)との位置合わせ用のフィディシャルパターン222、回路パターン210aの欠陥検査におけるアライメント用のパターン(または回路パターン210aの線幅測定におけるアライメント用のパターン)224、マスク識別用のバーコードパターン225、マスク識別用のナンバリングパターン226などが形成される。

#### [00005]

次に、従来の位相シフトマスクの製造方法を説明する。

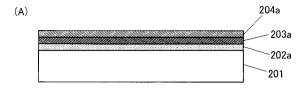

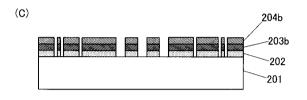

図13、図14は、従来の位相シフトマスクの製造方法の一工程を示す断面図である。 まず、透明基板201上に、位相シフト層202a、遮光層203aを積層し、更にレ ジスト層204aを形成する(図13(A))。

## [0006]

続いて、レジスト層 2 0 4 a を露光及び現像して所望のパターンのレジストパターン 2 0 4 b を形成した後に(図 1 3 ( B ) )、遮光層 2 0 3 a、位相シフト層 2 0 2 a を順次エッチングし、レジストパターン 2 0 4 b に応じた開口部を有する遮光層 2 0 3 b 及び位相シフト層 2 0 2 を形成する(図 1 3 ( C ) )。

### [0007]

そして、レジストパターン 2 0 4 b を除去した後、再度レジスト層 2 0 5 a を形成する(図 1 3 (D))。

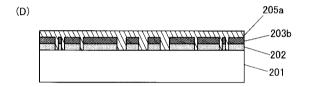

レジスト層 2 0 5 a 形成の後、チップ領域 2 1 0 を形成する領域に対し、露光及び現像を施し、レジストパターン 2 0 5 b を形成する(図 1 4 (A))。

### [00008]

ここで、チップ領域 2 1 0 に露出した遮光層 2 0 3 bをエッチングすることで、チップ領域 2 1 0 を開口した遮光層 2 0 3 が形成され(図 1 4 ( B ) )、最後にレジストパターン 2 0 5 bを除去することにより、位相シフトマスク 2 0 0 が完成する(図 1 4 ( C ) )

【特許文献 1 】特開 2 0 0 2 - 1 8 2 3 6 7 号公報(段落番号〔0 0 2 2〕~〔0 0 2 7〕,第1 図)

### 【発明の開示】

【発明が解決しようとする課題】

### [0009]

しかし、従来の位相シフトマスクを用いてウェハに回路パターンを転写する際、露光装置のブラインドによりチップ領域外に光が漏れないようにはしているものの、露光装置の照明系、レンズ、位相シフトマスクでの反射によるフレアの影響で、チップ領域外にあるパターンが、ウェハ上に転写されてしまう問題があった。

### [0010]

ハーフトーン型の位相シフトマスクにおいては、チップ領域全体がわずかながら感光しているため、そこにフレアによる影響が上乗せされると、ウェハに形成される回路パターンの異常が発生しやすくなる。

10

20

30

- -

40

#### [0011]

チップ領域外に存在するパターンは、露光装置の位置合わせ用のフィディシャル(基準)パターンを除き、モニタパターンなど位相シフトマスクの製造に必要とされるパターンであり、その性格上可能な限りチップ領域近傍に配置する必要がある(離せば離すほど保証の妥当性が低下する)。しかし、チップ領域近傍への配置は、フレアによる転写の危険性をさらに増大させてしまっていた。

### [0012]

本発明はこのような点に鑑みてなされたものであり、チップ領域外に存在するパターンのウェハ上への転写を防止可能なフォトマスクを提供することを目的とする。

また、本発明の他の目的は、上記のようなフォトマスクの製造方法を提供することである。

### [0013]

さらに、本発明では、上記のようなフォトマスクを用いた半導体装置の製造方法を提供 することを目的とする。

## 【課題を解決するための手段】

### [0014]

上記目的を達成するために、以下のようなフォトマスクが提供される。このフォトマスクは、透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とが順に積層され、所望のパターン形状の開口により、半導体チップに転写するチップ領域には回路パターン、前記チップ領域外には非回路パターンが形成されたフォトマスクであって、前記チップ領域では、前記遮光層が除去され、且つ、前記回路パターンに応じた開口がなされた前記位相シフト層が露出しており、前記チップ領域の周囲に、前記チップ領域から15mm以内の領域において前記遮光層のみが開口され、その開口部に前記位相シフト層が露出した、前記回路パターンの位置精度を測定するための位置精度測定用モニタパターンと、前記チップ領域から15mmを超える領域において前記遮光層及び前記位相シフト層の両方が開口され、その開口部に前記透明基板が露出した、露光装置との位置合わせを行うためのフィディシャルパターンとを含む非回路パターンを有する。

# [0015]

また、上記目的を達成するために、以下のような露光光の位相を変化させる機能を有するフォトマスクの製造方法が提供される。

## [0016]

このフォトマスクの製造方法は、透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とを順に積層する工程と、半導体チップに転写するチップ領域の回路パターン及び前記チップ領域外の、前記チップ領域から15mm以内の領域に形成される、前記回路パターンの位置精度を測定するための位置精度測定用モニタパターンと、前記チップ領域から15mmを超える領域に形成される、露光装置との位置合わせを行うためのフィディシャルパターンとを含む非回路パターンのパターン形状の開口部を前記遮光層に形成する工程と、前記チップ領域及び、前記チップ領域外の領域のうち、前記フィディシャルパターンが形成される領域が開口され、且つ、前記位置精度測定用モニタパターンが形成される領域を覆うようなレジストパターンを形成し、前記レジストパターンと前記チップ領域に露出している前記遮光層をマスクとして前記位相シフト層をエッチングする工程と、前記チップ領域内の前記遮光層を除去する工程と、を有する。

## [0017]

また、上記目的を達成するために、以下のような半導体装置の製造方法が提供される。この半導体装置の製造方法は、透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とが順に積層され、所望のパターン形状の開口により、半導体チップに転写するチップ領域には回路パターン、前記チップ領域外には非回路パターンが形成されたフォトマスクであって、前記チップ領域では前記遮光層が除去され、且つ、前記回路パターンに応じた開口がなされた前記位相シフト層が露出しており、前記チップ領域の周囲に、<u>前</u>記チップ領域から15mm以内の領域において前記遮光層のみが開口され、その開口部に

20

10

30

40

前記位相シフト層が露出した、前記回路パターンの位置精度を測定するための位置精度測定用モニタパターンと、前記チップ領域から15mmを超える領域において前記遮光層及び前記位相シフト層の両方が開口され、その開口部に前記透明基板が露出した、露光装置との位置合わせを行うためのフィディシャルパターンとを含む非回路パターンを有したフォトマスクを用いて露光を行う露光工程を有する。

### 【発明の効果】

## [0018]

本発明のフォトマスクは、遮光層が除去され且つチップに転写する回路パターンに応じた開口がなされた位相シフト層が露出したチップ領域の周囲に、遮光層のみが開口されその開口部に位相シフト層が露出した非回路パターンを有するので、フレアの影響でこの非回路パターンがウェハに転写されることを防止することができる。

【発明を実施するための最良の形態】

## [0019]

以下、本発明の実施の形態を図面を参照して詳細に説明する。

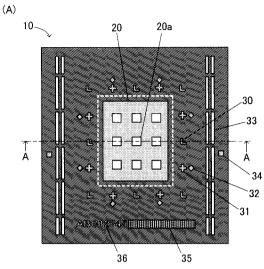

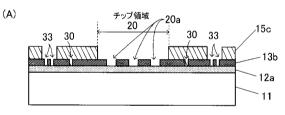

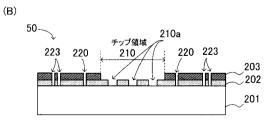

図1は、本実施の形態の位相シフトマスクの構造を示す図であり、(A)は平面図であり、(B)はA-A線での断面図である。

### [0020]

本実施の形態の位相シフトマスク 1 0 は、透明基板 1 1 上に位相シフト層 1 2 と、遮光層 1 3 とが順に積層され、所望のパターン形状に開口がなされることによってパターンが 形成された構成となっている。

#### [0021]

透明基板11は例えば、合成石英基板である。また、位相シフト層12と遮光層13とは、それぞれを選択的にエッチング可能な材料であり、例えば、位相シフト層12がMoSiONであり、遮光層13は例えば、クロムと酸化クロムの積層膜からなる。透明基板11の透過率を100%とすると、位相シフト層12は6%程度となる。

### [0022]

位相シフトマスク10に形成されるパターンのうちチップに転写する回路パターン20aが形成されるチップ領域20では遮光層13が除去されており、形成する回路パターン20aに応じた開口がなされた位相シフト層12が露出している。このチップ領域20において、透明基板11が露出している領域では露光光がそのまま透過され、位相シフト層12が露出している領域では、露光光の位相が180度反転される。

### [0023]

チップ領域20の外側の領域は、ウェハに回路パターン20aを転写する際に隣接するチップへの多重露光を防止するために、遮光層13を残すような構成となっている。そしてこの領域にも各種のパターンが形成される。例えば、回路パターン20aの位置精度測定用のモニタパターン30、マスク描画装置で、位相シフト層12と遮光層13の重ね合わせ描画を行う際のアライメント用ターゲットパターン31、重ね合わせ描画を行う際に用いるアライメント精度測定用パターン32、露光装置との位置合わせのためのフィディシャルパターン33、回路パターン20aの欠陥検査におけるアライメント用のパターン(または回路パターン20aの線幅測定装置におけるアライメント用のパターン)34、マスク識別用のバーコードパターン35、マスク識別用のナンバリングパターン36などが形成される。

# [0024]

本実施の形態の位相シフトマスク10では、これらチップ領域20の周囲に配置されるパターンの一部を、遮光層13のみが開口されその開口部に位相シフト層12が露出するように形成している。図1では、露光装置との位置合わせで露光光を透過させる必要のあるフィディシャルパターン33以外のパターンで、位相シフト層12が露出する構成としている。

# [0025]

50

40

10

20

10

20

30

40

50

モニタパターン30、アライメント用ターゲットパターン31、アライメント精度測定用パターン32は、その性質上チップ領域20の近傍に配置され、ウェハへの回路パターン20aの転写時に、フレアの影響を受けやすい。しかし、上記のように、これらのパターンの開口部の位相シフト層12を除去せずに残すことで、フレアによる影響は抑えられ、これらのパターンがウェハに転写されることを防止することができる。

### [0026]

実験結果によると、チップ領域20から15mmを超える領域ではフレアの影響は少ない。フレアの影響は、ArFエキシマレーザを光源として、高感度なレジストを用いた露光プロセスに顕著に現れるものの、露光装置内の露光光学系内で生じる多重反射現象に起因しているため、KrFレーザを光源として用いた露光装置内でも生じている。そのため、上記では、チップ領域20外にあるパターンのうち、フィディシャルパターン33を除く全てについて開口部に位相シフト層12を残すような構成としたが、15mm以内のパターンのみ位相シフト層12を残すような構成としてもよい。

## [0027]

なお、位相シフト層12を残すように構成したパターンは、遮光層13が開口されて段差が生じているので、反射光によりそのパターンを検出することができ、従来と同様に機能させることができる。

# [0028]

以下、本実施の形態の位相シフトマスクの製造方法を説明する。

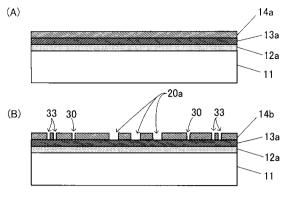

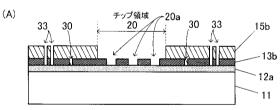

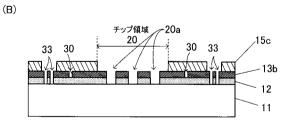

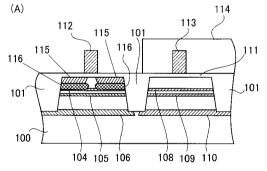

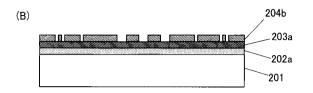

図2、図3は、本実施の形態の位相シフトマスクの製造方法における一工程を示す断面図である。

#### [0029]

まず、例えば合成石英からなる透明基板11上に、例えば、MoSiON膜からなる位相シフト層12aと、クロムと酸化クロムの積層膜からなる遮光層13aを順次積層した後、スピンコート法を用いレジスト層14aを形成する(図2(A))。

## [0030]

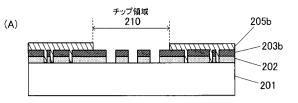

続いて、電子ビームを用いたマスク描画装置などにより、レジスト層14aを露光及び現像して、図1に示したチップ領域20内の回路パターン20a及びチップ領域20外の各種のパターン形状に開口されたレジストパターン14bを形成する(図2(B))。

# [0031]

その後、このレジストパターン 1 4 b をエッチングマスクとして遮光層 1 3 a のみを選択的に、例えばドライエッチングによりエッチングし、レジストパターン 1 4 b に応じた開口部を有する遮光層 1 3 b を形成する(図 2 ( C ))。

## [0032]

そして、残存するレジストパターン 1 4 b を除去した後、再度レジスト層 1 5 a を形成する(図 2 (D))。

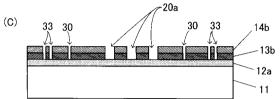

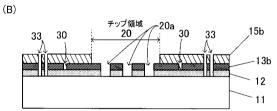

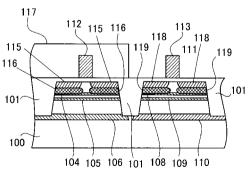

その後、レジスト層15aを露光及び現像して、レジストパターン15bを形成する。レジストパターン15bは、図1に示したチップ領域20の全面及び高い光透過率を必要とし光透過部として形成する必要があるフィディシャルパターン33の形状に開口され、モニタパターン30などチップ領域20外に存在するその他のパターンの開口部を覆うように形成する。この際にフィディシャルパターン33を形成する領域の遮光層13bは極力ダメージのないことが望ましいので、レジストパターン15bの下地に対する位置合わせは厳密に行う必要がある(図3(A))。

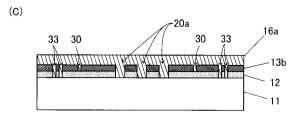

# [0033]

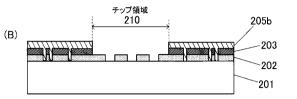

レジストパターン 1 5 bを形成した後、このレジストパターン 1 5 b及びチップ領域 2 0 内に露出している遮光層 1 3 bをエッチングマスクとして位相シフト層 1 2 aをエッチングする。これにより、チップ領域 2 0 内に形成される回路パターン 2 0 a と、チップ領域 2 0 外に形成されるフィディシャルパターン 3 3 のパターン形状に開口された位相シフト層 1 2 が形成される。フィディシャルパターン 3 3 を除いて、チップ領域 2 0 の周囲に存在する遮光層 1 3 b の開口パターンは全てレジストパターン 1 5 b で覆われているため

、その部分の位相シフト層12はエッチングされずに残っている(図3(B))。

## [0034]

続いて、残存するレジストパターン 1 5 b をエッチングマスクとして、露出しているチップ領域 2 0 の遮光層 1 3 b をエッチングする(図 3 (C))。

最後に、残存するレジストパターン 1 5 b を除去することによって、位相シフトマスク 1 0 が完成する(図 3 ( D ) )。

### [0035]

上記のような位相シフトマスク10の製造方法によれば、フィディシャルパターン33部分の遮光層13へのダメージに注意を払う必要があるが、製造工程は、従来のハーフトー型の位相シフトマスクとほぼ同様であり、手間を増やさず、コストの増加なしに、従来に比べて信頼性の高いハーフトーン型の位相シフトマスクを提供することが可能となる。

### [0036]

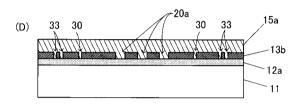

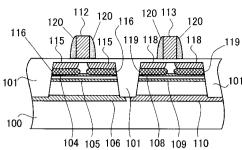

次に、ハーフトーン型の位相シフトマスク10の他の製造方法を説明する。

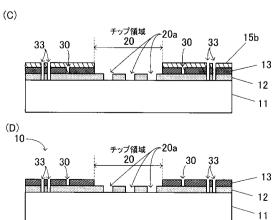

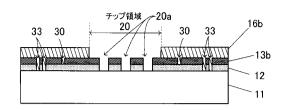

図4、図5は本実施の形態の位相シフトマスクの他の製造方法における一工程を示す断面図である。

## [0037]

図2、図3で示した構成要素と同じものについては同一符号としている。なお、始めの製造方法で説明した図2(A)~(D)の工程は、以下に示す製造方法においても同一であるので、図2(D)で示した工程の後から説明する。

## [0038]

レジスト層15aを形成した後、レジスト層15aを露光及び現像してレジストパターン15cを形成する。レジストパターン15cは、図1に示したチップ領域20外に形成するフィディシャルパターン33を含む所定の領域内を開口し、モニタパターン30などそれ以外のパターンの開口部を覆うように形成する。このレジストパターン15cは、フィディシャルパターン33の形状に合わせた開口を形成する必要がないので、下地に対しての厳密な位置合わせは不要である(図4(A))。

## [0039]

レジストパターン 1 5 c を形成した後、このレジストパターン 1 5 c 及び露出している 遮光層 1 3 b をエッチングマスクとして位相シフト層 1 2 a をエッチングし、チップ領域 2 0 内に形成される回路パターン 2 0 a と、チップ領域 2 0 外に形成されるフィディシャルパターン 3 3 のパターン形状に開口された位相シフト層 1 2 を形成する。フィディシャルパターン 3 3 を除いて、チップ領域 2 0 外に存在する遮光層 1 3 b の開口パターンは全てレジストパターン 1 5 c で覆われているため、その部分の位相シフト層 1 2 はエッチングされずに残っている(図 4 ( B ) )。

# [0040]

その後、残存するレジストパターン 1 5 c を除去した後、再度レジスト層 1 6 a を形成する(図 4 (C))。

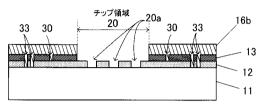

さらに、レジスト層16aを露光及び現像して、チップ領域20の全面を開口したレジストパターン16bを形成する(図5(A))。

## [0041]

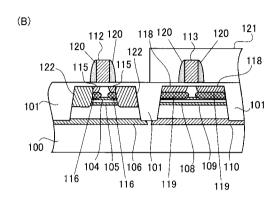

そして、このレジストパターン 1 6 b をエッチングマスクとして、露出しているチップ 領域 2 0 の遮光層 1 3 b をエッチングする(図 5 ( B ) )。

最後にレジストパターン 1 6 b を除去することにより、位相シフトマスク 1 0 が完成する(図 5 (C))。

## [0042]

上記のような製造方法によれば、1つめの製造方法に比べて重ね合わせ露光の工程が1回増えることになるが、前述したフィディシャルパターン33部の遮光層13のダメージを防止でき、信頼性の高い、高品質の位相シフトマスク10を提供することが可能となる

[0043]

10

20

30

50

次に、本実施の形態の位相シフトマスク10を、実際の半導体装置の製造に適用した例を説明する。

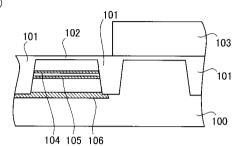

図6~図11は、半導体装置の製造工程の一工程を示す断面図である。

#### [0044]

まず、ウェハ(シリコン基板) 1 0 0 中に、例えばSTI(Shallow Trench Isolation)法により、例えば深さ 3 0 0 n mのトレンチに埋め込まれてなる素子分離膜 1 0 1 を形成する。なお、図において、左側の素子領域がN型トランジスタ形成領域であり、右側の素子領域がP型トランジスタ形成領域であるものとする(図 6 ( A ))。

## [0045]

次に、例えば熱酸化法により、素子分離膜101により画定された素子領域上に、犠牲酸化膜102を形成する。そしてフォトリソグラフィーにより、N型トランジスタ形成領域を露出しP型トランジスタ形成領域を覆うフォトレジスト膜103を形成する。さらに、フォトレジスト膜103をマスクとしてイオン注入を行い、N型トランジスタ形成領域のシリコン基板100中に、P型不純物拡散領域104、105、106を形成する(図6(B))。

### [0046]

ここで、 P 型不純物拡散領域 1 0 4 は、例えばインジウムイオン( I  $n^+$ )を、加速エネルギーを 6 0 k e V 、ドーズ量を 1 x 1  $0^{13}$  c  $m^{-2}$  としてイオン注入することにより形成する。

# [0047]

また、 P 型不純物拡散領域 1 0 5 は、例えばインジウムイオンを、加速エネルギーを 1 8 0 k e V 、ドーズ量を 3 × 1 0  $^{13}$  c m  $^{-2}$  としてイオン注入することにより形成する。 P 型不純物拡散領域 1 0 6 は、例えばボロンイオン (B  $^+$ ) を、加速エネルギーを 1 5 0 k e V 、ドーズ量を 3 × 1 0  $^{13}$  c m  $^{-2}$  としてイオン注入することにより形成する。

### [0048]

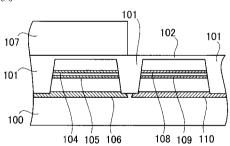

次いで、フォトリソグラフィーにより、P型トランジスタ形成領域を露出し、N型トランジスタ形成領域を覆うフォトレジスト膜107を形成する。そしてフォトレジスト膜107をマスクとしてイオン注入を行い、P型トランジスタ形成領域のシリコン基板100中に、N型不純物拡散領域108、109、110を形成する(図7(A))。

## [0049]

ここで、 N 型不純物拡散領域 1 0 8 は、例えば砒素イオン( A s  $^+$ )を、加速エネルギーを 1 0 0 k e V 、ドーズ量を 5 × 1 0  $^{12}$  c m  $^{-2}$  としてイオン注入することにより形成する。

### [0050]

また、N型不純物拡散領域 1 0 9 は、例えば砒素イオンを、加速エネルギーを 1 5 0 k e V、ドーズ量を 3 × 1 0  $^{13}$  c m  $^{-2}$  としてイオン注入することにより形成する。

N型不純物拡散領域 1 1 0 は、例えばリンイオン ( $P^+$ ) を、加速エネルギーを 3 0 0 k e V、ドーズ量を 3 × 1 0  $^{13}$  c m  $^{-2}$  としてイオン注入することにより形成する。

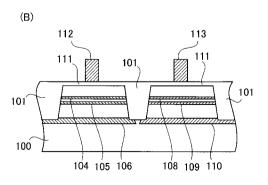

## [0051]

次に、例えば弗酸系の水溶液を用いたウェットエッチングにより、犠牲酸化膜 102 を除去する。そして、例えば熱酸化法により、犠牲酸化膜 102 を除去することにより露出する素子領域上に、例えば膜厚 1nmのシリコン酸化膜を成長し、シリコン酸化膜よりなるゲート絶縁膜 111 た形成する。そして、ゲート絶縁膜 111 上に、例えば 111 に 例えば 111 で 111 で

### [0052]

ここで、ゲート電極 1 1 2 は N 型 トランジスタのゲート電極であり、ゲート電極 1 1 3 は P 型 トランジスタのゲート電極である。

10

20

30

40

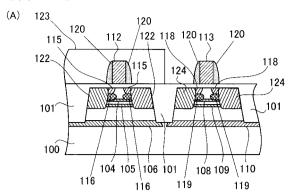

次に、フォトリソグラフィーにより、N型トランジスタ形成領域を露出し、P型トランジスタ形成領域を覆うフォトレジスト膜 1 1 4 を形成する。そしてこのフォトレジスト膜 1 1 4 及びゲート電極 1 1 2 をマスクとしてイオン注入を行い、ゲート電極 1 1 2 の両側のシリコン基板 1 0 0 中に、N型トランジスタのエクステンション領域となるN型不純物拡散領域 1 1 5 を形成する。N型不純物拡散領域 1 1 5 は、例えば砒素イオンを、加速エネルギーを 2 k e V、ドーズ量を 1 × 1 0  $^{15}$  c m  $^{-2}$  としてイオン注入することにより形成する。さらに、フォトレジスト膜 1 1 4 及びゲート電極 1 1 2 をマスクとしてイオン注入を行い、N型トランジスタ形成領域にP型ポケット領域 1 1 6 を形成する(図 8 ( A ) )

[0053]

P型ポケット領域 1 1 6 は、例えばインジウムイオンを、加速エネルギーを 5 0 k e V 、ドーズ量を 2 × 1 0  $^{13}$  c m  $^{-2}$  、基板法線に対するチルト角を 2 5 度としてイオン注入することにより形成する。

[0054]

次いで、フォトリソグラフィーにより、 P型トランジスタ形成領域を露出しN型トランジスタ形成領域を覆うフォトレジスト膜 1 1 7 を形成する。そしてこのフォトレジスト膜 1 1 7 及びゲート電極 1 1 3 をマスクとして、例えばボロンイオンを、加速エネルギーを 0 . 5 k e V、ドーズ量を 1 x 1 0  $^{15}$  c m  $^{-2}$  としてイオン注入し、 P型トランジスタのエクステンション領域となる P型不純物拡散領域 1 1 8 を形成する。 さらに、フォトレジスト膜 1 1 7 及びゲート電極 1 1 3 をマスクとしてイオン注入を行い、 P型トランジスタ形成領域に N型ポケット領域 1 1 9 を形成する(図 8 (B))。

[0055]

N型ポケット領域 1 1 9 は、例えば砒素イオンを、加速エネルギーを 5 0 k e V 、ドーズ量を 2 × 1 0  $^{13}$  c m  $^{-2}$  、基板法線に対するチルト角を 2 5 度としてイオン注入することにより形成する。

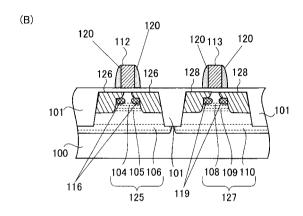

[0056]

次いで、例えばCVD法により、例えば膜厚100nmのシリコン酸化膜を堆積した後、このシリコン酸化膜をドライエッチングによりエッチバックし、ゲート電極112、1 13の側壁部分に側壁絶縁膜120を形成する(図9(A))。

[0057]

その後、フォトリソグラフィーにより、N型トランジスタ形成領域を露出しP型トランジスタ形成領域を覆うフォトレジスト膜121を形成する。そしてこのフォトレジスト膜121、ゲート電極112及び側壁絶縁膜120をマスクとしてイオン注入を行い、ゲート電極112の両側のシリコン基板100中に、N型不純物領域122を形成する(図9(B))。

[0058]

N型不純物領域 1 2 2 は、例えばリンイオンを、加速エネルギーを 2 0 k e V、ドーズ量を  $5 \times 10^{15}$  c m  $^{-2}$  としてイオン注入することにより形成する。

次いで、フォトリソグラフィーにより、P型トランジスタ形成領域を露出しN型トランジスタ形成領域を覆うフォトレジスト膜123を形成する。そしてこのフォトレジスト膜123、ゲート電極113及び側壁絶縁膜120をマスクとしてイオン注入を行い、ゲート電極113の両側のシリコン基板100中に、P型不純物領域124を形成する(図10(A))。

[0059]

P型不純物領域 1 2 4 は、例えばボロンイオンを、加速エネルギーを 5 k e V 、ドーズ量を 5 x 1 0  $^{15}$  c m  $^{-2}$  としてイオン注入することにより形成する。

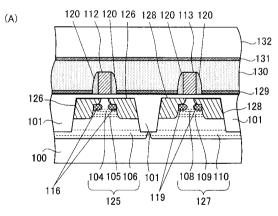

次いで、例えば1000 、3秒間の短時間熱処理を行い、注入した不純物を活性化する。これにより、N型トランジスタ形成領域には、P型不純物拡散領域104、105、106を含むP型ウェル125と、N型不純物拡散領域115、122よりなるエクステンションソース・ドレイン構造のN型ソース/ドレイン領域126とが形成される。また

10

20

30

40

、 P型トランジスタ形成領域には、 N型不純物拡散領域108、109、110を含む N型ウェル127と、 P型不純物拡散領域118、124よりなるエクステンションソース・ドレイン構造の P型ソース / ドレイン領域128とが形成される(図10(B))。

## [0060]

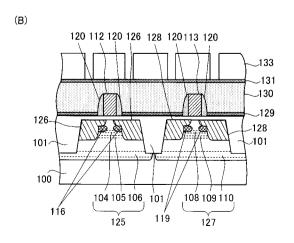

次いで、シリコン窒化膜 1 2 9 をゲート構造体及びシリコン基板 1 0 0 全面を覆うように成膜する。さらに、C V D 法により厚さ 4 0 0 n m のシリコン酸化膜よりなる層間絶縁膜 1 3 0 を成膜した後、C M P (Chemical Mechanical Polishing) 法を用いてこの層間 絶縁膜 1 3 0 を平坦化する。

## [0061]

次に、トランジスタのソース / ドレイン領域 1 2 6 、 1 2 8 を露出させ、電極を取り出すためのコンタクトホール形成を行う。このときに図 1 で示したような本実施の形態の位相シフトマスク 1 0 を適用する。そのために、層間絶縁膜 1 3 0 上に、反射防止膜 1 3 1 及びフォトレジスト膜 1 3 2 を形成する(図 1 1 ( A ) )。

# [0062]

図11(A)のような半導体装置において、ArFエキシマレーザを光源とする縮小投影露光装置により、本実施の形態の位相シフトマスク10を用いて露光を行い回路パターン20aを転写した。その際の露光条件は、開口率(NA):0.70, 値:0.70とし、露光量:470J/cm²とした。

# [0063]

次いで、現像を行い、レジストパターン133を形成する(図11(B))。

この状態の半導体装置をウェハパターン検査装置(KLA社製 KLA2350)を用いて検査したところ、デバイスパターン領域外に存在するパターンの写り込みは全く検出されず、本実施の形態の位相シフトマスク10の有効性が確認された。

### [0064]

(付記1) 透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とが順に積層され、所望のパターン形状の開口により、半導体チップに転写するチップ領域には回路パターン、前記チップ領域外には非回路パターンが形成されたフォトマスクにおいて

前記チップ領域では、前記遮光層が除去され、且つ、前記回路パターンに応じた開口がなされた前記位相シフト層が露出しており、

前記チップ領域の周囲に、前記遮光層のみが開口され、その開口部に前記位相シフト層が露出した非回路パターンを有したことを特徴とするフォトマスク。

### [0065]

(付記2) 前記非回路パターンは、前記回路パターンの位置精度測定用のモニタパターンであることを特徴とする付記1記載のフォトマスク。

(付記3) 前記非回路パターンは、前記回路パターンの欠陥検査におけるアライメント用のパターンであることを特徴とする付記1記載のフォトマスク。

## [0066]

(付記4) 前記非回路パターンは、前記回路パターンの線幅測定装置におけるアライメント用のパターンであることを特徴とする付記1記載のフォトマスク。

(付記5) 前記非回路パターンは、マスク描画装置において重ね合わせ描画を行う際のアライメント用ターゲットパターンであることを特徴とする付記1記載のフォトマスク

# [0067]

(付記6) 前記非回路パターンは、マスク描画装置において重ね合わせ描画を行う際に用いるアライメント精度測定用パターンであることを特徴とする付記1記載のフォトマスク。

## [0068]

(付記 7) 前記非回路パターンは、マスク識別用のバーコードパターンであることを 特徴とする付記 1 記載のフォトマスク。 10

20

30

40

(付記8) 前記非回路パターンは、マスク識別用のナンバリングパターンであることを特徴とする付記1記載のフォトマスク。

### [0069]

(付記9) 前記チップ領域から15mm以内の範囲に存在する前記非回路パターンの前記開口部には、前記位相シフト層が露出していることを特徴とする付記1記載のフォトマスク。

### [0070]

(付記10) 前記位相シフト層と前記遮光層は、それぞれ選択的にエッチング可能な材料にて構成されていることを特徴とする付記1記載のフォトマスク。

(付記11) 前記位相シフト層は、MoSiON膜であることを特徴とする付記1記載のフォトマスク。

### [0071]

(付記12) 前記遮光層は、クロムとクロム酸化物の積層膜で構成されていることを 特徴とする付記1記載のフォトマスク。

(付記13) 露光光の位相を変化させる機能を有するフォトマスクの製造方法において、

透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とを順に積層する工程と、

半導体チップに転写するチップ領域の回路パターン及び前記チップ領域外の非回路パターンのパターン形状の開口部を前記遮光層に形成する工程と、

前記チップ領域が開口され、且つ、前記チップ領域の周囲の前記非回路パターンの前記 開口部を覆うようなレジストパターンを形成し、前記レジストパターンと前記チップ領域 に露出している前記遮光層をマスクとして前記位相シフト層をエッチングする工程と、

前記チップ領域内の前記遮光層を除去する工程と、

を有することを特徴とするフォトマスクの製造方法。

## [0072]

(付記14) 高い光透過率を必要とする前記非回路パターンに対しては前記開口部を 覆わず前記非回路パターンに応じた前記レジストパターンを形成し、前記レジストパター ンをマスクとして前記位相シフト層をエッチングし、

前記レジストパターンをマスクとして、前記チップ領域内の前記遮光層を除去すること を特徴とする付記13記載のフォトマスクの製造方法。

# [0073]

(付記15) 前記高い光透過率を必要とする前記非回路パターンは、露光装置との位置合わせ用のフィディシャルパターンであることを特徴とする付記14記載のフォトマスクの製造方法。

## [0074]

(付記16) 前記高い光透過率を必要とする前記非回路パターンを含む所定の領域内を開口した前記レジストパターンを形成し、その開口部に露出した前記遮光層をマスクとして前記位相シフト層をエッチングすることを特徴とする付記13記載のフォトマスクの製造方法。

# [0075]

(付記17) 前記高い光透過率を必要とする前記非回路パターンは、露光装置との位置合わせ用のフィディシャルパターンであることを特徴とする付記16記載のフォトマスクの製造方法。

### [0076]

(付記18) 半導体装置の製造方法において、

透明基板上に露光光の位相をシフトさせる位相シフト層と、遮光層とが順に積層され、 所望のパターン形状の開口により、半導体チップに転写するチップ領域には回路パターン 、前記チップ領域外には非回路パターンが形成されたフォトマスクであって、前記チップ 領域では前記遮光層が除去され、前記回路パターンに応じた開口がなされた前記位相シフ

20

10

30

40

20

30

40

ト層が露出しており、前記チップ領域の周囲に、前記遮光層のみが開口され、その開口部に前記位相シフト層が露出した非回路パターンを有したフォトマスクを用いて露光を行う露光工程を有することを特徴とする半導体装置の製造方法。

【図面の簡単な説明】

[0077]

- 【図1】本実施の形態の位相シフトマスクの構造を示す図であり、(A)は平面図であり、(B)はA-A線での断面図である。

- 【図2】本実施の形態の位相シフトマスクの製造方法における一工程を示す断面図である (その1)。

- 【図3】本実施の形態の位相シフトマスクの製造方法における一工程を示す断面図である 10 (その2)。

- 【図4】本実施の形態の位相シフトマスクの他の製造方法における一工程を示す断面図である(その1)。

- 【図5】本実施の形態の位相シフトマスクの他の製造方法における一工程を示す断面図である(その2)。

- 【図6】半導体装置の製造工程の一工程を示す断面図である(その1)。

- 【図7】半導体装置の製造工程の一工程を示す断面図である(その2)。

- 【図8】半導体装置の製造工程の一工程を示す断面図である(その3)。

- 【図9】半導体装置の製造工程の一工程を示す断面図である(その4)。

- 【図10】半導体装置の製造工程の一工程を示す断面図である(その5)。

- 【図11】半導体装置の製造工程の一工程を示す断面図である(その6)。

- 【図12】従来の代表的なハーフトーン型の位相シフトマスクの構造を示す図であり、(A)は平面図であり、(B)はB-B線での断面図である。

- 【図13】従来の位相シフトマスクの製造方法の一工程を示す断面図である(その1)。

- 【図14】従来の位相シフトマスクの製造方法の一工程を示す断面図である(その2)。

## 【符号の説明】

[0078]

- 10 位相シフトマスク

- 11 透明基板

- 12 位相シフト層

- 13 遮光層

- 20 チップ領域

- 20a 回路パターン

- 30 モニタパターン

- 3 1 アライメント用ターゲットパターン

- 32 アライメント精度測定用パターン

- 33 フィディシャルパターン

- 34 欠陥検査におけるアライメント用のパターン(または線幅測定装置におけるアライメント用のパターン)

- 35 バーコードパターン

- 36 ナンバリングパターン

# 【図1】

# (B) 10 33 30 20 30 33 13 12

# 【図2】

# 【図3】

# 【図4】

# 【図5】

(A)

(B)

(C)

# 【図6】

(A) 101 101 101 100

(B)

# 【図7】

(A)

# 【図8】

(B)

# 【図9】

(A)

【図10】

【図11】

# 【図12】

# 【図13】

# 【図14】

# フロントページの続き

(56)参考文献 特開平09-050116(JP,A)

特開平09-034099(JP,A)

特開2002-182367(JP,A)

特開平11-327121(JP,A)

特開平08-334885(JP,A)

(58)調査した分野(Int.CI., DB名)

G03F 1/00-1/16

H01L 21/027