# (10) **DE 197 36 900 B4** 2006.02.16

(12)

## **Patentschrift**

(21) Aktenzeichen: 197 36 900.6(22) Anmeldetag: 25.08.1997(43) Offenlegungstag: 04.03.1999

(45) Veröffentlichungstag

der Patenterteilung: 16.02.2006

(51) Int CI.8: **H04L 25/08** (2006.01)

*H04L 25/20* (2006.01) *H03K 19/0175* (2006.01) *H03F 3/45* (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(73) Patentinhaber:

Telefonaktiebolaget LM Ericsson (publ), Stockholm, SE

(74) Vertreter:

HOFFMANN & EITLE, 81925 München

(72) Erfinder:

Hedberg, Mats, Haninge, SE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

WO 97 17 763

# (54) Bezeichnung: Leitungsempfängerschaltkreis mit großem Gleichtaktspannungsbereich für differentielle Eingangssignale

- (57) Hauptanspruch: Leitungsempfängerschaltkreis zum Empfangen von differentiellen digitalen Signalen von einer symmetrischen Übertragungsleitung, mit einem Paar von differentiellen Eingangsanschlüssen (A, B) zur Verbindung mit der Übertragungsleitung, und einem Ausgang zum Ausgeben von Datensignalen entsprechend über die Übertragungsleitung empfangenen Signalen, wobei der Leitungsempfängerschaltkreis umfaßt:

- eine erste differentielle Eingangsstufe (1) mit einem ersten Paar von differentiellen Eingängen, die geschaltet sind,

Eingangssignale von dem Paar von differentiellen Eingangsanschlüssen (A, B) zu empfangen;

- wobei die erste Eingangsstufe (1) ausgebildet ist, differentiellen Signale mit einer Gleichtaktspannung innerhalb eines ersten Gleichtaktspannungsbereiches zu empfangen und zu verarbeiten;

- eine zweite differentielle Eingangsstufe (2) mit einem zweiten Paar von differentiellen Eingängen, die geschaltet sind, Eingangssignale von dem Paar von differentiellen Eingangsanschlüssen (A, B) zu empfangen;

## **Beschreibung**

**[0001]** Die vorliegende Erfindung betrifft einen Leitungsempfängerschaltkreis zum Empfangen von differentiellen Signalen von einer symmetrischen Übertragungsleitung. Ein Leitungsempfängerschaltkreis dieser Art ist bekannt aus WO 97 17763.

#### Stand der Technik

**[0002]** Ein Leitungsempfängerschaltkreis dient dazu, Signale von einer Übertragungsleitung zu empfangen. Differentielle Signalübertragung über eine symmetrische Übertragungsleitung bedeutet, daß die zu empfangenden Signale an einem Eingang des Leitungsempfängers nicht notwendigerweise ein wohldefiniertes Potential des Leitungsempfängerschaltkreises, beispielsweise sein Massepotential, als Referenz verwenden, sondern ein Potential eines zweiten Leitungsempfängereinganges als Referenz benutzen.

[0003] Die Gleichtaktspannung auf der Übertragungsleitung, wie sie von dem Leitungsempfänger gesehen wird, kann nicht immer auf eine wohldefinierte Spannung oder ein begrenztes Spannungsintervall eingegrenzt werden. Dieses hat zahlreiche Gründe. Beispielsweise können verschiedene Systemkompontenten, die über eine symmetrische Übertragungsleitung verbunden sind, in ihren jeweiligen Massereferenzpotentialen einen Versatz aufweisen. Ein anderer Grund kann sein, daß der Leitungsempfängerschaltkreis die Entwurfsvorgabe erfüllen muß, mit einer Vielzahl von verschiedenen Signalübertragungsstandards zusammenzuarbeiten, die jeweils einen anderen Gleichtaktspannungspegel vorsehen.

[0004] In der Realität ist jedoch ein Leitungsempfängerschaltkreis nicht in der Lage, mit Gleichtaktspannungen über einen beliebig großen Bereich zu arbeiten. Wenn die Gleichtaktspannung auf der Übertragungsleitung die Grenzen des Gleichtaktspannungsbereiches des Leitungsempfängers überschreitet, wird der Empfang von Signalen von der Übertragungsleitung unzuverlässig oder unmöglich. Deshalb ist es wünschenswert, einen Leitungsempfängerschaltkreis mit einem möglichst großen Eingangsgleichttaktspannungsbereich auszustatten.

[0005] Um das zu erreichen, ist es aus WO 95 17763 bekannt, zwei Eingangsstufen parallel vorzusehen, die konstruiert sind, innerhalb verschiedener, sich teilweise überlappender Gleichtaktspannungsbereiche zu arbeiten. Wenn die Gleichtaktspannung am Eingang dieses Schaltkreises einen vorbestimmten Pegel erreicht, bei welchem der zweite Eingangsschaltkreis arbeiten kann, wird der erste Eingangsschaltkreis deaktiviert, um zu vermeiden, daß beide Eingangsstufen gleichzeitig eine folgende Stufe ansteuern, weil dieses in einer unerwünschten Abhän-

gigkeit der Gesamtsignalverzögerung von dem Eingangsgleichtaktspannungspegel resultieren kann. Der Schaltkreis gemäß diesem Dokument erzielt eine Übergabe zwischen der ersten und der zweiten Stufe in einem unteren Bereich des Gesamtgleichtaktspannungsbetriebsbereiches.

### Aufgabenstellung

[0006] Es ist die Aufgabe der vorliegenden Erfindung, einen Leitungsempfängerschaltkreis mit einem großen Gleichtaktspannungsbetriebsbereich zu sehen, so daß eine Übergabe zwischen der ersten Stufe und der zweiten Stufe in einem höheren Bereich des Gesamtgleichtaktspannungsbetriebsbereiches stattfindet.

**[0007]** Gemäß der vorliegenden Erfindung wird diese Aufgabe gelöst wie in Anspruch 1 definiert. Vorteilhafte Ausführungsbeispiele der Erfindung ergeben sich aus den abhängigen Ansprüchen.

[0008] Ein Leitungsempfängerschaltkreis gemäß der vorliegenden Erfindung erzielt einen großen Gleichtaktspannungsbetriebsbereich dadurch, daß mehr als eine Eingangsstufe vorgesehen sind, die mit der Übertragungsleitung in Verbindung stehen. Jede Eingangsstufe ist ausgebildet, in einem Gleichtaktspannungsbereich zu arbeiten, der für diese bestimmte Stufe spezifisch ist. Die Eingangsstufen sind so vorgesehen, daß sich ihre Gleichtaktspannungsbetriebsbereiche teilweise überlappen, so daß ein Gleichtaktspannungsbetriebsbereich vergrößerter erhalten wird. Die Signale, die von jeder Eingangsstufe ausgegeben werden, werden geeignet kombiniert. Die Aktivierung der zweiten Stufe wird durch Erfassen einer tatsächlichen Betriebsbedingung der ersten Stufe durchgeführt, die von dem Eingangsgleichtaktpegel abhängt. Die zweite Stufe wird nur aktiviert, wenn die erfaßte Betriebsbedingung der ersten Stufe anzeigt, daß sich der Gleichtaktspannungspegel einer Grenze des Gleichtaktbetriebsbereichs der ersten Stufe nähert.

**[0009]** Bevorzugt ist die erste Stufe ausgebildet, in einem unteren Gleichtaktbetriebsbereich zu arbeiten, und die zweite Stufe ist ausgebildet, in einem oberen Gleichtaktbetriebsbereich zu arbeiten.

[0010] Gemäß einem bevorzugten Ausführungsbeispiel schließt der Leitungsempfängerschaltkreis eine erste Eingangsstufe ein, die einen schwimmenden Stromspiegel für einen unteren Gleichtaktspannungsbereich umfaßt, sowie eine zweite Eingangsstufe, die einen Spannungsdifferenzverstärker für einen oberen Gleichtaktspannungsbereich umfaßt. Die Ausgänge der ersten Eingangsstufe und der zweiten Eingangsstufe sind geschaltet, an denselben Lastelementen zu arbeiten, um ein kombiniertes Ausgangssignal zu erhalten.

**[0011]** Bevorzugt kann die Einrichtung zum Aktivieren bzw. Deaktivieren der zweiten Eingangsstufe die zweite Eingangsstufe graduell aktivieren, sobald die Eingangsgleichtaktspannung an die Grenzen des Gleichtaktspannungsbereiches der ersten Stufe heran oder darüber hinausreicht, und hält andernfalls die zweite Eingangsstufe deaktiviert.

#### Ausführungsbeispiel

**[0012]** Im folgenden werden bevorzugte Ausführungsbeispiele der vorliegenden Erfindung unter Bezugnahme auf die begleitenden Zeichnungen beschrieben.

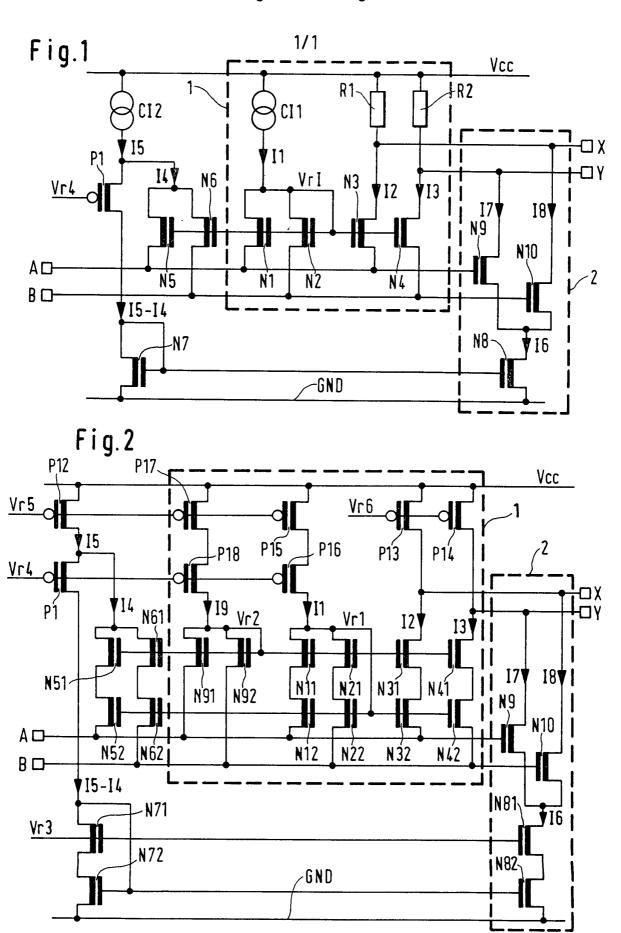

[0013] Fig. 1 zeigt ein erstes Ausführungsbeispiel eines Leitungsempfängerschaltkreises gemäß der vorliegenden Erfindung; und

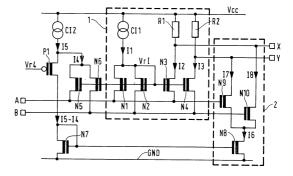

**[0014]** Fig. 2 zeigt ein zweites Ausführungsbeispiel eines Leitungsempfängerschaltkreises gemäß der vorliegenden Erfindung.

[0015] In Fig. 1 bezeichnet Bezugsziffer 1 eine erste Eingangsstufe des Leitungsempfängerschaltkreises, und 2 bezeichnet eine zweite Eingangsstufe des Leitungsempfängerschaltkreises. Vcc bezeichnet eine Spannungsversorgungsleitung zum Zuführen eines oberen Potentials, während GND eine untere Versorgungsleitung zum Zuführen eines unteren Potentials bezeichnet. A und B bezeichnen differentielle Eingangsanschlüsse des Leitungsempfängers. X und Y bezeichnen differentielle Ausgänge des Leitungsempfängerschaltkreises der Fig. 1.

[0016] Die erste Eingangsstufe 1 dieses Ausführungsbeispiels ist konstruiert, innerhalb eines unteren Eingangsgleichtaktspannungsbereiches zu arbeiten. Die zweite Eingangsstufe 2 ist konstruiert, innerhalb eines höheren Eingangsgleichtaktspannungsbereiches zu arbeiten, der den unteren Eingangsgleichtaktspannungsbereich teilweise überlappt. Der Begriff "Gleichtaktspannung" bezeichnet eine Spannungskomponente bezüglich Masse GND, die auf beiden Eingangseinschlüssen A und B vorhanden ist.

[0017] In dem in Fig. 1 gezeigten Ausführungsbeispiel umfaßt die erste Eingangsstufe 1 einen Stromspiegelschaltkreis, der aus NMOS Transistoren N1 und N3 besteht. Die Sources der Transistoren N1 und N3 sind mit dem Eingangsanschluß A verbunden. Der Drain des Transistors N1 und das Gate des Transistors N1 sind miteinander verbunden, um einen Steuerstromeingang des Stromspiegels zu bilden. Das Gate des Transistors N3 und das Gate des Transistors N1 sind miteinander verbunden. Der Drain des Transistors N3 bildet einen Spiegelstromeingang. Eine Konstantstromquelle CI1 ist zwischen die obere Versorgungsspannungsleitung Vcc und den

Drain des Transistors N1 geschaltet. Eine Lastimpedanz R1 ist zwischen Vcc und den Drain des Transistors N3 geschaltet. Der Drain des Transistors N3 stellt ein Ausgangssignal X bereit.

[0018] Die Eingangsstufe 1 umfaßt einen weiteren Stromspiegel, der aus den Transistoren N2 und N4 besteht. Die Sources der Transistoren N2 und N4 sind mit dem Eingangsanschluß B verbunden. Der Drain und das Gate des Transistors N2 und das Gate des Transistors N4 sind miteinander verbunden. Der Drain des Transistors N2 bildet einen Steuerstromeingang und ist mit der Konstantstromquelle CI1 verbunden. Eine zweite Lastimpedanz R2 ist zwischen Vcc und den Drain des Transistors N4 geschaltet, der der Spiegelstromeingang dieses Stromspiegelschaltkreises ist. Der Drain des Transistors N4 stellt ein zweites Ausgangssignal Y bereit.

[0019] In dem in Fig. 1 gezeigten Ausführungsbeispiel ist die Einrichtung zum Erfassen einer Betriebsbedingung der ersten Eingangsstufe 1, die von einer Eingangsgleichtaktspannung an den Eingängen A und B abhängt, mittels der Transistoren N5 und N6 ausgeführt. Die Source des Transistors N5 ist mit Eingangsanschluß A verbunden, und sein Gate ist mit dem Gate des Transistors N1 verbunden. Auf diese Weise bilden die Transistoren N1 und N5 einen ersten Stromspiegelschaltkreis, wobei der Drain des Transistors N5 ein Spiegelstromeingang ist. Die Source des Transistors N6 ist mit dem Eingangsanschluß B verbunden, und sein Gate ist mit dem Gate des Transistors N2 verbunden. Auf diese Weise bilden die Transistoren N2 und N6 einen zweiten Stromspiegelschaltkreis, wobei der Drain des Transistors N6 ein Spiegelstromeingang ist. Die Drains der Transistoren N5 und N6 sind miteinander verbunden, die Gates der Transistoren N1 bis N6 sind miteinander und mit den Drains der Transistoren N1 und N2 verbunden.

[0020] Im Ausführungsbeispiel der Fig. 1 umfaßt die Einrichtung zum Aktivieren der zweiten Eingangsstufe 2 eine zweite Konstantstromquelle CI2, die zwischen die obere Versorgungsleitung Vcc und die Drains der Transistoren N5 und N6 geschaltet ist. Sie umfaßt außerdem einen Transistor P1 mit einem Leitfähigkeitstyp entgegengesetzt den Transistoren N1 bis N5. Die Source des Transistors P1 ist mit den Drains der Transistoren N5 und N6 verbunden und empfängt an seinem Gate eine Referenzspannung Vr4, die bezüglich der oberen Versorgungsspannung Vcc konstant ist. Auf diese Weise wirkt P1 als Sourcefolger und sorgt für einen konstanten Spannungsabfall über der Konstantstromquelle CI2, und hält demgemäß das Potential an den Drains der Transistoren N5 und N6 auf einem definierten Pegel.

[0021] Die Einrichtung zum Aktivieren der zweiten Eingangsstufe umfaßt ferner einen Transistor N7,

dessen Drain mit dem Drain des Transistors P1 verbunden ist, und dessen Source mit der unteren Spannungsversorgungsleitung GND verbunden ist. Der Drain und das Gate des Transistors N7 sind miteinander verbunden.

[0022] Die zweite Eingangsstufe 2 dieses Ausführungsbeispiels ist ein Spannungsdifferenzverstärker, der einen Transistor N9 umfaßt, dessen Gate mit dem Eingangsanschluß A verbunden ist, und einen Transistor N10, dessen Gate mit dem Eingangsanschluß B verbunden ist. Die Sources der Transistoren N9 und N10 sind miteinander und mit dem Drain eines Transistors N8 verbunden. Die Source des Transistors N8 ist mit der unteren Spannungsversorgungsleitung GND verbunden. Das Gate des Transistors N8 ist mit dem Gate des Transistors N7 verbunden, so daß die Transistoren N7 und N8 einen Stromspiegelschaltkreis bilden. Der Drain des Transistors N9 ist mit dem Drain des Transistors N4 und mit dem Ausgangsanschluß Y verbunden. Der Drain des Transistors N10 ist mit dem Drain des Transistors N3 und mit dem Ausgangsanschluß X verbunden.

[0023] Im folgenden wird der Betrieb dieses Schalt-kreises erläutert. Zu diesem Zweck wird eine Situation betrachtet, daß ein Eingangssignal mit einer Gleichtaktspannung an die Anschlüsse A und B angelegt wird, die auf einem niedrigen Pegel beginnt, wo die erste Eingangssstufe 1 aktiv ist, und die anwächst, in einen Bereich einzutreten, wo die zweite Eingangsstufe 2 aktiv ist.

[0024] Für einen niedrigen Gleichtaktpegel an den Anschlüssen A und B wirken die Transistoren N1 und N2 als ein Stromteiler, so daß der von der Stromquelle CI1 bereitgestellte Strom I1 unter diesen Transistoren abhängig von der Spannungsdifferenz über den Anschlüssen A und B aufgeteilt wird. Weil N1 und N3 einen Stromspiegel bilden, ist der Strom I2 ein Bild des durch N1 fließenden Stroms, während der Strom I3 ein Bild des durch N2 fließenden Stromes ist. Demgemäß tritt eine Spannungsdifferenz über den Eingangsanschlüssen A und B als Ausgangssignal über den Ausgangsanschlüssen X und Y auf.

[0025] Weil außerdem die Transistoren N1 und N5 einen Stromspiegel bilden, und die Transistoren N2 und N6 einen weiteren Stromspiegel bilden, ist der Strom I4 ein Bild des Stroms I1, der von der Konstantstromquelle CI1 geliefert wird. Die Betriebsbedingung der ersten Eingangsstufe, die von der Gleichtaktspannung an den Anschlüssen A und B abhängt, ist der Strom I1. Wenn die Gleichtaktspannung anwächst, verringert sich dementsprechend der Spannungsabfall über der Konstantstromquelle CI1 und erreicht irgendwann einen Wert, bei welchem die Konstantstromquelle CI1 den Strom I1 nicht länger aufrechthalten kann. Dieses zeigt an, daß die Eingangsstufe 1 die obere Grenze ihres Gleichtaktspan-

nungsbetriebsbereiches erreicht.

[0026] Der von der zweiten Konstantstromquelle CI2 gelieferte Strom I5 teilt sich auf in den Strom I4 und in einen Strom (I5-I4) durch den Transistor P1. Weil I4 ein Bild von I1 ist, beginnt der Strom (I5-I4), anzuwachsen, wenn der Strom I1, und demgemäß der Strom I4, abzunehmen beginnt.

[0027] Der Strom I5-I4, der durch den Transistor N7 fließt, wird in den Strom I6 gespiegelt, von dem Bruchteile durch die Transistoren N9 und N10 fließen. Wenn sich die Gleichtaktspannung an den Eingängen A, B der oberen Grenze der Eingangsstufe 1 nähert, beginnt der Strom durch N7, anzuwachsen, ebenso wie der Strom I6, so daß die zweite Eingangsstufe 2 graduell aktiviert wird, während gleichzeitig die erste Eingangsstufe 1 graduell zu arbeiten aufhört. Demgemäß hängt die Aktivierung der zweiten Eingangsstufe 2 von der Betriebsbedingung der ersten Eingangsstufe 1 ab, so daß die zweite Eingangsstufe 2 die Funktion der ersten Eingangsstufe 1 mit hoher Präzision an der Obergrenze des Gleichtaktspannungsbereiches der ersten Stufe übernimmt.

**[0028]** Bevorzugt sind die von der ersten Stromquelle I1 und von der zweiten Stromquelle CI2 gelieferten Ströme gleich groß.

[0029] Dieses kann beispielsweise dadurch erreicht werden, daß die Stromquellen CI1 und CI2 eines Stromspiegelschaltkreises ausgeführt werden, wobei I1 ein Bild von I5 ist. In diesem Fall ist die Summe des Drainstroms I2 von N3 und des Drainstroms I8 durch den Transistor N10 fast vollständig unabhängig von der Gleichtaktspannung an den Eingangsanschlüssen A und B. Mutatis mutandis gilt dasselbe für die Summe von I3 und I7.

**[0030]** Fig. 2 zeigt ein zweites Ausführungsbeispiel eines Leitungsempfängerschaltkreises gemäß der vorliegenden Erfindung. In diesem Ausführungsbeispiel sind Elemente, die ähnlich oder identisch mit entsprechenden Elementen des ersten Ausführungsbeispiels der Fig. 1 sind, mit denselben Bezugsziffern bezeichnet. Betreffend die Beschreibung solcher Elemente in Fig. 2 wird auf Fig. 1 bezug genommen, um Wiederholungen zu vermeiden.

[0031] In dem in Fig. 2 gezeigten Ausführungsbeispiel umfaßt die erste Eingangsstufe 1 eine Konstantstromquelle, die aus Transistoren P15 und P16 besteht, deren Drain Source Pfade in Reihe geschaltet sind. Im Ausführungsbeispiel der Fig. 2 sind alle Stromquellen und alle Stromspiegelschaltkreise der Fig. 1 als Kaskodenschaltkreise ausgebildet. Im allgemeinen umfaßt ein Kaskodenschaltkreis eine Reihenschaltung der Drain Source Pfade von zwei Transistoren. Einer dieser Transistoren arbeitet als Sourcefolger, um die Drain Source Spannung des ande-

ren Transistors auf einem wohldefinierten Pegel zu halten. Das Gate dieses anderen Transistors dient als Steuereingang zum Steuern des Stroms durch die Reihenschaltung von Transistoren. Kaskodenschaltkreise dieser Art sind als solche allgemein bekannt.

[0032] In dem Ausführungsbeispiel der Fig. 2 bilden die Kaskode, die aus den Transistoren N11, N12 besteht, und die Kaskode, die aus den Transistoren N31, N32 besteht, einen Sromspiegel entsprechend den Transistoren N1 und N3 der Fig. 1. In gleicher Weise bildet die aus den Transistoren N21, N22 bestehende Kaskode und die aus den Transistoren N41, N42 der Fig. 2 bestehende Kaskode einen weiteren Stromspiegel entsprechend den Transistoren N2 und N4 der Fig. 1.

[0033] Die Kaskode der Transistoren N51, N52 bildet einen Stromspiegel mit der Kaskode der Transistoren N11, N12 entsprechend den Transistoren N5 und N1 in Fig. 1. Die Kaskode der Transistoren N61, N62 bildet einen Stromspiegel mit der Kaskode der Transistoren N21, N22, ähnlich den Transistoren N6 und N2 der Fig. 1.

[0034] Das Ausführungsbeispiel der Fig. 2 umfaßt Transistoren N91 und N92, die geschaltet sind, für die Sourcefolger N11, N21, N31, N41, N51 und N61 in ihren jeweiligen Kaskoden eine Referenzspannung Vr2 zu erzeugen. Die Source des Transistors N91 ist mit dem Eingangsanschluß A verbunden, während die Source des Transistors N92 mit dem Eingangsanschluß B verbunden ist. Die Drains der Transistoren N91 und N92 sind miteinander verbunden. Die Gates der Transistoren N91 und N92 sind miteinander und mit ihren Drains verbunden. Wenn ein Strom 19 in die Transistoren N91 und N92 geliefert wird, wird die Referenzspannung Vr2 bezüglich der Gleichtaktspannung an den Anschlüssen A und B erzeugt. Der Strom 19 wird von einer Konstantstromquelle erzeugt, die aus PMOS Transistoren P17 und P19 besteht. Die Source des Transistors P17 ist mit Vcc verbunden. Der Drain des Transistors P17 ist mit der Source des Transistors P18 verbunden. Der Drain des Transistors P18 ist mit den Drains und Gates der Transistoren N91 und N92 verbunden.

[0035] P12 bezeichnet einen PMOS Transistor, dessen Funktion der Konstantstromquelle Cl2 der Fig. 1 entspricht. Die Source dieses Transistors ist mit Vcc verbunden, und sein Drain ist mit der Source des Transistors P1 verbunden. Die Gates der Transistoren P12, P15 und P17 empfangen ein Referenzpotential Vr5 relativ zu Vcc. Die Gates der Transistoren P1, P16 und P18 empfangen ein Referenzpotential Vr4 relativ zu Vcc, das unterhalb des Potentials Vr5 liegt.

[0036] Die Kaskode der Transistoren N71 und N72 und die Kaskode der Transistoren N81 und N82 bil-

den einen Stromspiegelschaltkreis entsprechend den Transistoren N7 und N8 der Fig. 1. Die Gates der Transistoren N71 und N81 empfangen dasselbe Referenzpotential Vr3 relativ zur unteren Versorgungsleitung GND.

[0037] Die PMOS Transistoren P13 und P14 der Fig. 2 bilden die Lastimpedanzen R1 bzw. R2 der Fig. 1. Die Source der Transistoren P13 und P14 ist mit Vcc verbunden. Der Drain des Transistors P13 ist mit dem Drain von N31 und mit dem Drain von N10 verbunden und stellt ein Ausgangssignal X bereit. Der Drain des Transistors P14 ist mit dem Drain des Transistors N41 und mit dem Drain des Transistors N9 verbunden und stellt ein Ausgangssignal Y bereit. Das an die Gates von P13 und P14 angelegte Referenzpotential Vr6 wird relativ zu Vcc konstant gehalten und bestimmt die Lastimpedanz, die von den Transistoren P13 und P14 bereitgestellt wird.

**[0038]** Die Gates der Transistoren N51, N61, N11, N21, N31 und N41, die in ihren jeweiligen Kaskoden als Sourcefolger wirken, sind sämtlich mit den Drains der Transistoren N91 und N92 verbunden, um die Referenzspannung Vr2 zu empfangen. Die Gates der Transistoren N52, N62, N12, N22, N32 und N42, die in ihren jeweiligen Kaskoden als die Stromsteuertransistoren wirken, sind sämtlich mit den Drains der Transistoren N11 und N21 verbunden, um die Referenzspannung Vr1 zu empfangen.

[0039] Die Ausführungsbeispiele der Fig. 1 und Fig. 2 verwenden MOSFET Transistoren, um einen Leitungsempfängerschaltkreis gemäß der vorliegenden Erfindung zu realisieren. Natürlich ist eine ähnliche Konstruktion mit Bipolartransistoren oder einer Mischung aus Bipolar- und CMOS Transistoren ebenso denkbar. In den obigen Ausführungsbeispielen verwenden die erste und die zweite Eingangsstufe NMOS FETs. Eine ähnliche Konstruktion ergibt sich, wenn NMOS FETs durch PMOS FETs und umgekehrt ersetzt werden.

#### **Patentansprüche**

- 1. Leitungsempfängerschaltkreis zum Empfangen von differentiellen digitalen Signalen von einer symmetrischen Übertragungsleitung, mit einem Paar von differentiellen Eingangsanschlüssen (A, B) zur Verbindung mit der Übertragungsleitung, und einem Ausgang zum Ausgeben von Datensignalen entsprechend über die Übertragungsleitung empfangenen Signalen, wobei der Leitungsempfängerschaltkreis umfaßt:

- eine erste differentielle Eingangsstufe (1) mit einem ersten Paar von differentiellen Eingängen, die geschaltet sind, Eingangssignale von dem Paar von differentiellen Eingangsanschlüssen (A, B) zu empfangen:

- wobei die erste Eingangsstufe (1) ausgebildet ist,

- differentiellen Signale mit einer Gleichtaktspannung innerhalb eines ersten Gleichtaktspannungsbereiches zu empfangen und zu verarbeiten;

- eine zweite differentielle Eingangsstufe (2) mit einem zweiten Paar von differentiellen Eingängen, die geschaltet sind, Eingangssignale von dem Paar von differentiellen Eingangsanschlüssen (A, B) zu empfangen;

- 2. Leitungsempfängerschaltkreis nach Anspruch 1, gekennzeichnet durch

- einen ersten Stromquellenschaltkreis (CI1);

- wobei die erfasste Betriebsbedingung die Größe des Betriebsstroms (I1) ist, der von dem ersten Stromquellenschaltkreis (CI1) in die erste Eingangsstufe geliefert wird.

- 3. Leitungsempfängerschaltkreis nach Anspruch 2, dadurch gekennzeichnet, dass die Einrichtung zum Erfassen der Betriebsbedingung der ersten Eingangsstufe einen Stromspiegelschaltkreis (N1, N2, N5, N6) zum Bereitstellen eines Spiegelstroms (I4) des tatsächlich von dem ersten Stromquellenschaltkreis (CI1) in die erste Eingangsstufe gelieferten Stromes (I1) umfasst.

- 4. Leitungsempfängerschaltkreis nach Anspruch 3, dadurch gekennzeichnet, dass der Stromspiegelschaltkreis umfasst:

- einen ersten Stromspiegelschaltkreis (N1, N5), der einem ersten (A) der Eingangsanschlüsse (A, B) des Leitungsempfängerschaltkreises zugeordnet ist und einen Steuerstromeingang und einen Spiegelstromeingang aufweist; und

- einen zweiten Stromspiegelschaltkreis (N2, N6), der dem anderen (B) der Eingangsanschlüsse (A, B) des Leitungsempfängerschaltkreises zugeordnet ist und einen Steuerstromeingang und einen Spiegelstromeingang aufweist;

- wobei der Steuerstromeingang des ersten Stromspiegelschaltkreises (N1, N5) und der Steuerstromeingang des zweiten Stromspiegelschaltkreises (N2, N6) geschaltet sind, einen von dem ersten Stromquellenschaltkreis (CI1) gelieferten Strom zu teilen:

- wobei der erste und der zweite Stromspiegelschaltkreis mit den Eingangsanschlüssen (A, B) so verbunden sind, daß ein Verhältnis zwischen dem in den ersten Stromspiegelschaltkreis fließenden Steuerstrom und dem in den zweiten Stromspiegelschaltkreis fließenden Steuerstrom von einer Potentialdifferenz über den Eingangsanschlüssen (A, B) abhängt.

- 5. Leitungsempfängerschaltkreis nach Anspruch 4, dadurch gekennzeichnet, dass

- die Spiegelstromeingänge der ersten und zweiten Stromspiegelschaltkreise (N1, N5; N2, N6) miteinander verbunden sind, um den Spiegelstrom (I4) bereitzustellen; und

- die Einrichtung (CI2, N7, P1) zum Aktivieren oder

- Deaktivieren der zweiten differentiellen Eingangsstufe (2) ausgebildet ist, die zweite Eingangsstufe (2) abhängig von dem Spiegelstrom (I4) zu aktivieren.

- 6. Leitungsempfängerschaltkreis nach Anspruch 4 oder 5, dadurch gekennzeichnet, dass die Einrichtung zum Aktivieren oder Deaktivieren der zweiten differentiellen Eingangsstufe (2) umfasst:

- einen zweiten Stromquellenschaltkreis (CI2) zum Bereitstellen eines zweiten Stromes (I5);

- wobei der zweite Stromquellenschaltkreis (CI2) geschaltet ist, die Spiegelstromeingänge der ersten und zweiten Stromspiegelschaltkreise (N1, N5; N2, N6) zu speisen; und

- einen Nebenschlußschaltkreis (P1, N7) zum Aufnehmen eines Nebenschlußstroms (I5-I4), der von dem zweiten Stromquellenschaltkreis (CI2) geliefert und von den Spiegelstromeingängen nicht abgenommen wird;

- wobei die Einrichtung (CI2, N7, P1) zum Aktivieren oder Deaktivieren der zweiten differentiellen Eingangsstufe (N9, N10) ausgebildet ist, die zweite Eingangsstufe abhängig von dem Nebenschlußstrom (I5-I4) zu aktivieren.

- 7. Leitungsempfängerschaltkreis nach Anspruch 1 oder 6, dadurch gekennzeichnet, dass die zweite Eingangsstufe umfasst:

- einen Differenzverstärker, der einen ersten Transistor (N9) umfasst, der geschaltet ist, an seinem Gate ein Signal von dem ersten Eingangsanschluss (A) zu empfangen, und einen zweiten Transistor (10), der geschaltet ist, an seinem Gate ein Signal von dem zweiten Eingangsanschluss (B) zu empfangen.

- 8. Leitungsempfängerschaltkreis nach Anspruch 7, dadurch gekennzeichnet, dass die Einrichtung zum Aktivieren der zweiten Eingangsstufe umfasst

- einen dritten Stromspiegelschaltkreis (N7, N8), der geschaltet ist, an seinem Steuerstromeingang den Nebenschlußstrom (I5-I4) zu empfangen;

- wobei die ersten und zweiten Transistoren (N9, N10) des Differenzverstärkerschaltkreises mit dem Spiegelstromeingang des dritten Stromspiegels verbunden sind.

- wobei die zweite Eingangsstufe (2) ausgebildet ist, differentielle Signale mit einer Gleichtaktspannung innerhalb eines zweiten Gleichtaktspannungsbereiches zu empfangen und zu verarbeiten;

- Einrichtungen zum Kombinieren von Ausgangssignalen, die von der ersten differentiellen Eingangsstufe bereitgestellt werden und Ausgangssignalen, die von der zweiten differentiellen Eingangsstufe bereitgestellt werden;

- gekennzeichnet durch

- eine Einrichtung (N5, N6) zum Erfassen einer Betriebsbedingung der ersten Eingangsstufe (1), welche Betriebsbedingung von einer Gleichtakteingangsspannung an den Eingängen der ersten Eingangsstufe abhängt und anzeigt, wenn sich der

Gleichtaktspannungspegel einer Grenze des Gleichtaktbetriebsbereiches der ersten Stufe nähert; und – eine Einrichtung (P1, N7, N8) zum Aktivieren oder Deaktivieren der zweiten Eingangsstufe wenn die erfasste Betriebsbedingung der ersten Eingangsstufe anzeigt, dass sich der Gleichtaktspannungspegel der Grenze des Gleichtaktbetriebsbereiches der ersten Stufe nähert.

- 9. Leitungsempfängerschaltkreis nach einem der Ansprüche 6 bis 8, gekennzeichnet durch eine Einrichtung (P1) zum Halten einer Spannung an dem Ausgang der zweiten Stromquelle auf einem vorbestimmten Potential.

- 10. Leitungsempfängerschaltkreis nach Anspruch 9, dadurch gekennzeichnet, dass die Einrichtung zum Halten einer Spannung an dem Ausgang der zweiten Stromquelle auf einem vorbestimmten Potential einen Transistor (P1) umfasst, dessen Source mit der zweiten Stromquelle (Cl2) verbunden ist, derart, dass der Nebenschlußstrom durch diesen Transistor fließt.

- 11. Leitungsempfängerschaltkreis nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet, dass die Stromspiegelschaltkreise Kaskoden sind.

Es folgt ein Blatt Zeichnungen

## Anhängende Zeichnungen