(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5052025号 (P5052025)

(45) 発行日 平成24年10月17日(2012.10.17)

(2006, 01)

(24) 登録日 平成24年8月3日(2012.8.3)

(51) Int. Cl.

HO1L 29/78

FL

HO1L 29/78 652H

> 請求項の数 4 (全 26 頁)

(21) 出願番号

特願2006-92406 (P2006-92406)

(22) 出願日 (65) 公開番号 平成18年3月29日 (2006.3.29) 特開2007-266505 (P2007-266505A)

(43) 公開日

審查請求日

平成19年10月11日(2007.10.11) 平成20年8月5日(2008.8.5)

||(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 齋藤 渉

> 神奈川県川崎市幸区小向東芝町1番地 株 式会社東芝 マイクロエレクトロニクスセ

ンター内

||(72)発明者 小野 昇太郎

神奈川県川崎市幸区小向東芝町1番地 株 式会社東芝 マイクロエレクトロニクスセ

ンター内

最終頁に続く

(54) 【発明の名称】電力用半導体素子

## (57)【特許請求の範囲】

### 【請求項1】

電流を流すセル部及び前記セル部を囲む終端部からなる電力用半導体素子であって、 第1の第1導電型半導体層と、

前記セル部における前記第1の第1導電型半導体層上に形成され、前記第1の第1導電 型半導体層の表面に平行な方向のうち少なくとも一の方向に沿って交互に配列された第2 の第1導電型半導体層及び第3の第2導電型半導体層と、

前記第1の第1導電型半導体層に電気的に接続された第1の主電極と、

前記第2の第1導電型半導体層の表面及び前記第3の第2導電型半導体層の表面に選択 的に形成された第4の第2導電型半導体層と、

前記第4の第2導電型半導体層の表面に選択的に形成された第5の第1導電型半導体層 と、

前記第4の第2導電型半導体層及び前記第5の第1導電型半導体層に接続された第2の 主電極と、

前記第4の第2導電型半導体層、前記第5の第1導電型半導体層及び前記第2の第1導 電型半導体層上にゲート絶縁膜を介して形成された制御電極と、

を備え、

前記第2の第1導電型半導体層の不純物量と前記第3の第2導電型半導体層の不純物量 とは、前記第2の第1導電型半導体層及び前記第3の第2導電型半導体層によってスーパ ジャンクション構造を構成する関係にあり、前記第2の第1導電型半導体層及び前記第3

の第2導電型半導体層は、前記一の方向において、一の前記第3の第2導電型半導体層の中央から前記第2の第1導電型半導体層を経て、隣の前記第3の第2導電型半導体層の中央まで、又は、一の前記第2の第1導電型半導体層の中央から前記第3の第2導電型半導体層を経て、隣の前記第2の第1導電型半導体層の中央までを基本単位としたパターンを用いて形成されたものであり、

前記第2の第1導電型半導体層及び前記第3の第2導電型半導体層のうち少なくとも一方の半導体層であって、前記セル部の最外部に位置する半導体層以外の半導体層における前記一の方向に沿った不純物濃度プロファイルは、前記一方の半導体層の両端部を除く位置に極小値を有し、

前記セル部の最外部に位置する前記一方の半導体層の不純物濃度プロファイルは、前記 基本単位における両側部分に配置された前記一方の半導体層の不純物濃度プロファイルと 同じであり、

前記セル部の最外部に位置する前記一方の半導体層の幅は、それ以外の前記一方の半導体層の幅の半分であることを特徴とする電力用半導体素子。

### 【請求項2】

前記第2の第1導電型半導体層及び前記第3の第2導電型半導体層における前記第2の 主電極から前記第1の主電極に向かう方向に沿った不純物濃度プロファイルは、波形であることを特徴とする請求項1記載の電力用半導体素子。

#### 【請求項3】

前記終端部における前記第1の第1導電型半導体層上に形成され、その不純物濃度が前記第2の第1導電型半導体層及び前記第3の第2導電型半導体層の不純物濃度よりも低い高抵抗層をさらに備えたことを特徴とする請求項1または2に記載の電力用半導体素子。

#### 【請求項4】

上方から見て、前記セル部の外縁は前記セル部の角部において湾曲しており、前記第2の第1導電型半導体層及び前記第3の第2導電型半導体層の形状は、前記セル部の外縁に沿って整形されていることを特徴とする請求項1~3のいずれか1つに記載の電力用半導体素子。

### 【発明の詳細な説明】

## 【技術分野】

### [0001]

本発明は、電力用半導体素子に関し、より詳細には、スーパージャンクション構造を有する電力用半導体素子に関する。

### 【背景技術】

## [0002]

縦型パワーMOSFET(Metal Oxide Semiconductor Field Effect Transistor:金属酸化物半導体電界効果トランジスタ)のオン抵抗は、伝導層(ドリフト層)部分の電気抵抗に大きく依存する。そして、このドリフト層の電気抵抗を決定するドープ濃度は、ベースとドリフト層とが形成するpn接合に要求される耐圧に応じて決まる限界濃度以上には上げられない。このため、素子耐圧とオン抵抗にはトレードオフの関係が存在する。このトレードオフを改善することが低消費電力素子には重要となる。このトレードオフには素子材料により決まる限界があり、この限界を超えることが既存のパワー素子を超える低オン抵抗素子の実現への道である。

### [0003]

この問題を解決するMOSFETの一例として、ドリフト層にスーパージャンクション構造と呼ばれるpピラー層とnピラー層を埋め込んだ構造が知られている。スーパージャンクション構造はpピラー層とnピラー層に含まれるチャージ量(不純物量)を同じとすることで、擬似的にノンドープ層を作り出し、高耐圧を保持しつつ、高ドープされたnピラー層を通して電流を流すことで、材料限界を超えた低オン抵抗を実現する。耐圧を保持するためには、nピラー層とpピラー層の不純物量を精度良く制御する必要がある。

## [0004]

10

20

30

このようなドリフト層にスーパージャンクション構造が形成されたMOSFETでは、終端構造の設計も通常のパワーMOSFETと異なる。素子部と同様に終端部も高耐圧を保持しなければならないため、通常は、終端部にもスーパージャンクション構造を形成する。そして、この場合、nピラー層とpピラー層の不純物量が等しくなくなった時に、素子部(セル部)よりも大きく終端部の耐圧が低下してしまう。このため、終端部の耐圧を増加させて、耐圧低下を抑制するために、素子部よりも終端部のp/nピラー濃度を下げる構造や、ピラー層の配列周期を狭くする構造が既に考案されている(特許文献1:特開2001-298190号公報参照。)。また、終端部の耐圧を高くするために終端部を高抵抗層で形成し、スーパージャンクション構造を形成しない構造もある(特許文献2:特開2000-277726号公報参照。)。

[0005]

しかしながら、どちらの構造においても、スーパージャンクション構造が素子部と終端部との間で不連続となる。この不連続部分、すなわち、素子部のスーパージャンクション構造の最外部にあたるpピラー層もしくはnピラー層においては、不純物濃度をセル部の半分程度としなければならない。このように、場所によりピラー層の不純物濃度を変化せるためには、イオン注入のドーズ量を場所によって変化させるか、注入を2回に分けるなどスループットの低下につながる。一方、マスク幅を変化させることは、リソグラフィーのマスク幅を変化させることで容易に実現できる。しかし、リソグラフィーマスクと実際の注入用のマスクとなるレジストマスクの間には変換差が生じる。この変換差がばらつくと、不純物量がばらついたのと同じことになる。このようなことから、原理的には高耐圧が得られるはずの終端構造を実現することが困難であり、プロセス上のばらつきの影響を受け易いという欠点がある。

[0006]

【特許文献 1 】特開 2 0 0 1 - 2 9 8 1 9 0 号公報

【特許文献2】特開2000-277726号公報

【発明の開示】

【発明が解決しようとする課題】

[0007]

本発明の目的は、プロセス上のばらつきに対する耐圧の低下が小さい電力用半導体素子を提供することである。

【課題を解決するための手段】

[00008]

本発明の一態様によれば、電流を流すセル部及び前記セル部を囲む終端部からなる電力 用半導体素子であって、第1の第1導電型半導体層と、前記セル部における前記第1の第 1 導電型半導体層上に形成され、前記第1の第1導電型半導体層の表面に平行な方向のう ち少なくとも一の方向に沿って交互に配列された第2の第1導電型半導体層及び第3の第 2 導電型半導体層と、前記第1の第1導電型半導体層に電気的に接続された第1の主電極 と、前記第2の第1導電型半導体層の表面及び前記第3の第2導電型半導体層の表面に選 択的に形成された第4の第2導電型半導体層と、前記第4の第2導電型半導体層の表面に 選択的に形成された第5の第1導電型半導体層と、前記第4の第2導電型半導体層及び前 記第5の第1導電型半導体層に接続された第2の主電極と、前記第4の第2導電型半導体 層、前記第5の第1導電型半導体層及び前記第2の第1導電型半導体層上にゲート絶縁膜 を介して形成された制御電極と、を備え、前記第2の第1導電型半導体層の不純物量と前 記第3の第2導電型半導体層の不純物量とは、前記第2の第1導電型半導体層及び前記第 3 の第 2 導電型半導体層によってスーパジャンクション構造を構成する関係にあり、前記 第2の第1導電型半導体層及び前記第3の第2導電型半導体層は、前記一の方向において 一の前記第3の第2導電型半導体層の中央から前記第2の第1導電型半導体層を経て. 隣の前記第3の第2導電型半導体層の中央まで、又は、一の前記第2の第1導電型半導体 層の中央から前記第3の第2導電型半導体層を経て、隣の前記第2の第1導電型半導体層 10

20

\_\_

30

40

の中央までを基本単位としたパターンを用いて形成されたものであり、前記第2の第1導電型半導体層及び前記第3の第2導電型半導体層のうち少なくとも一方の半導体層であって、前記セル部の最外部に位置する半導体層以外の半導体層における前記一の方向に沿った不純物濃度プロファイルは、前記一方の半導体層の両端部を除く位置に極小値を有し、前記セル部の最外部に位置する前記一方の半導体層の不純物濃度プロファイルは、前記基本単位における両側部分に配置された前記一方の半導体層の不純物濃度プロファイルと同じであり、前記セル部の最外部に位置する前記一方の半導体層の幅は、それ以外の前記一方の半導体層の幅の半分であることを特徴とする電力用半導体素子が提供される。

### 【発明の効果】

#### [0010]

本発明によれば、プロセスのばらつきに対する耐圧の低下が小さい電力用半導体素子を 実現することができる。

#### 【発明を実施するための最良の形態】

## [0011]

以下、本発明の実施形態について図面を参照しながら説明する。なお、以下の実施形態では、第1導電型をn型、第2導電型をp型としている。また、図面中の同一部分には同一符号を付している。

#### [0012]

#### (第1の実施形態)

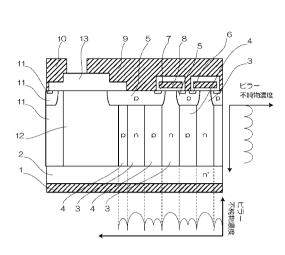

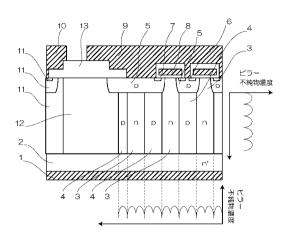

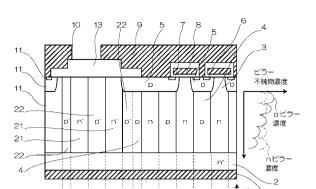

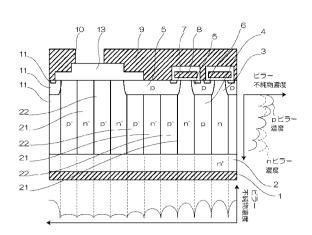

図1は本発明の第1の実施形態に係るパワーMOSFETの構成を模式的に示す断面図である。なお、図1においては、ピラー層の不純物濃度のプロファイルを示すために、横軸に位置をとり縦軸に不純物濃度をとったグラフ図を併せて記載している。後述の同様な図においても同じである。

#### [0013]

図1に示すように、本実施形態に係る電力用半導体素子は、スーパージャンクション構造を有する縦型MOSFETである。この縦型MOSFETにおいては、素子の中央部に電流を流すセル部が設けられており、素子の周辺部にセル部を囲む終端部が設けられている。セル部の外縁はその角部において湾曲している。このMOSFETの素子中央部にあたるセル部では、第1の半導体層としてn \* ドレイン層 2 が形成されており、このn \* ドレイン層 2 上に、第2の半導体層としてn ピラー層 3 と、第3の半導体層であるp ピラー層 4 とが、n \* ドレイン層 2 の表面に平行な方向に沿って交互に形成されている。n ピラー層 3 及びp ピラー層 4 はいわゆるスーパージャンクション構造を構成している。また、n \* ドレイン層 2 の下面上には、第1の主電極としてのドレイン電極 1 が形成されている

## [0014]

セル部のスーパージャンクション構造の表面の一部には、第4の半導体層としてp型ベース層 5 が選択的に且つストライプ形状に形成されており、このpベース層 5 の表面の一部には、第 5 の半導体層としてのnソース層 6 が選択的に且つストライプ形状に形成されている。また、一方のp型ベース層 5 及びその表面に形成されたnソース層 6 から、nピラー層 3 を介して、他方のpベース層 5 及びその表面に形成されたnソース層 6 に至る領域上には、膜厚が例えば約 0 . 1 μmのゲート絶縁膜 7 、例えば S i 酸化膜を介して、第1 の制御電極としてゲート電極 8 がストライプ形状に形成されている。このゲート電極 8 を挟むように、一方のp型ベース層 5 及びnソース層 6 上と、他方のpベース層 5 及びnソース層 6 上には、第 2 の主電極としてソース電極 9 がストライプ形状に形成されている

## [0015]

一方、素子終端部では、n \* ドレイン層 2 上に高抵抗層 1 2 が形成され、その表面にはフィールド絶縁膜 1 3 が形成され、フィールド絶縁膜 1 3 上にソース電極 9 が形成されることで、フィールドプレート効果により終端部での耐圧低下を抑制している。終端部にスーパージャンクション構造を形成せず、高抵抗(低不純物濃度)層とすることで空乏層が

10

20

30

40

20

30

40

50

伸び易く、セル部よりも高い終端耐圧を実現することができる。なお、図1では、フィールドプレート電極がソース電極9と一体形成されているが、ゲート電極8に接続された構造でも実施可能である。

#### [0016]

素子最外部には、高電圧印加時に空乏層がダイシングラインまで到達しないようにフィールドストップ電極 1 0 およびフィールドストップ層 1 1 が形成されている。フィールドストップ電極 1 0 は、ソース電極と同時に形成することができ、フィールドストップ層 1 1 は、n ピラー層 3 、p ベース層 5 、n ソース層 6 と同時に形成することができる。

#### [0017]

なお、一例では、最外部の p ベース層 5 とフィールドストップ層 1 1 までの距離は 1 0 乃至 1 5 0  $\mu$  m である。また、高抵抗層 1 2 の厚さ、すなわち、フィールド絶縁膜 1 3 の下面から n  $^+$  ドレイン層 2 の上面までの距離は 5 0  $\mu$  m であり、高抵抗層 1 2 及び n  $^+$  ドレイン層 2 の合計の厚さは 2 0 0 乃至 2 5 0  $\mu$  m である。また、 M O S F E T 全体の平面形状は、例えば一辺が 3 乃至 5 m m の正方形状であり、最外部の p ベース層 5 の外縁の曲率は 1 0 0 乃至 2 0 0  $\mu$  m である。

#### [0018]

そして、スーパージャンクション構造の最外部に位置する p ピラー層 4 、 すなわち、素子終端部の高抵抗層 1 2 と接する p ピラー層 4 (以下、「最外部 p ピラー層」という)の幅は、それ以外の p ピラー層 4 (以下、「セル部 p ピラー層」という)の幅の半分で示されている。これは、最外部 p ピラー層の不純物量がセル部 p ピラー層 4 の不純物量の半分であることを示している。スーパージャンクション構造は、 n ピラー層と p ピラー層の接合面から空乏層が伸びて、低い電圧にてドリフト層が完全空乏化する。そして、セル部 p ピラー層 4 はその両脇に n ピラー層が形成されているため、両方向から空乏層が伸びる。しかし、最外部 p ピラー層は、片側にしか n ピラー層 3 は無く、反対側は高抵抗層 1 2 である。このため、最外部 p ピラー層内の空乏層は、 n ピラー層 3 側からしか伸びない。よって、最外部 p ピラー層の不純物量はセル部 p ピラー層 4 の半分としなければならない。

#### [0019]

スーパージャンクション構造は、nピラー層3とpピラー層4との不純物量を等しくすることで、完全空乏化した後のドリフト層内のチャージがゼロとなり電界分布が平坦となることによって、高耐圧を実現している。このため、不純物量が等しくなくなると、完全空乏化してもドリフト層内は余剰なドナーもしくはアクセプタイオンによるチャージがドリフト層内の電界分布を傾かせる。これにより、耐圧が低下してしまう。そして、最外部pピラー層の不純物量がセル部pピラー層の不純物量の1/2でなくなると、最外部pピラー層に接するnピラー層3と不純物量が等しくなくなるため、局所的に電界が高くなり、耐圧が低下してしまう。

### [0020]

スーパージャンクション構造を形成するプロセスとして、イオン注入と埋め込み成長を繰り返すプロセスが挙げられる。本実施形態においては、nピラー層3とpピラー層4の両方の不純物をイオン注入し、高抵抗層の成長を繰り返すプロセスを用いる。このプロセスを用いると、終端部には不純物が注入されないマスクパターンとすることで、セル部にはスーパージャンクション構造を形成し、終端部には形成しない構造を形成することができる。ピラー層の不純物量はイオン注入のドーズ量とマスク開口幅で制御できる。最外ピラー層の不純物量をセル部の半分とするためには、マスク開口幅を半分とすればよい。しかし、通常、マスクとしてレジストが用いられ、レジストマスクとフォトリソグラフィーマスクの寸法変換差によるレジストの寸法ばらつきが生じ易い。このため、精度良く、最外ピラー層の不純物量をセル部の1/2にすることは困難である。

#### [0021]

そこで、本実施形態においては、nピラー層3とpピラー層4のパターンを工夫することで、このようなばらつきを抑制する。先に述べたように、低電圧時のスーパージャンクション構造内の空乏層は、pピラー層4とnピラー層3との両接合面から伸びる。伸びた

20

30

40

50

空乏層は、ピラー層の中央でつながり完全空乏化が起きる。つまり、スーパージャンクション構造の基本単位は、相互に隣接した1対のnピラー層3及びpピラー層4、すなわち、pピラー層4の端からnピラー層3の端までの間の部分ではなく、pピラー層4の中央からnピラー層3を経て、隣のpピラー層4の中央まで、もしくは、nピラー層3の中央からpピラー層4を経て、隣のnピラー層3の中央までとなる。そして、この基本単位毎にピラー層が形成されるようなパターンとすれば、局所的に寸法が異なるパターンではなくなり、寸法ばらつきは全体と同じになって、終端部との境界(最外部)のピラー層(最外部ピラー層)の不純物量が極端にばらつくことはない。

#### [0022]

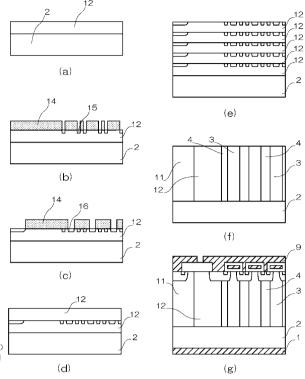

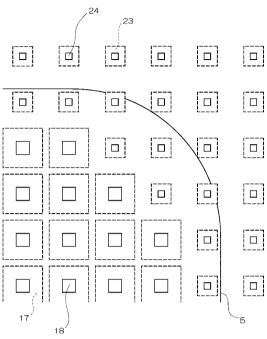

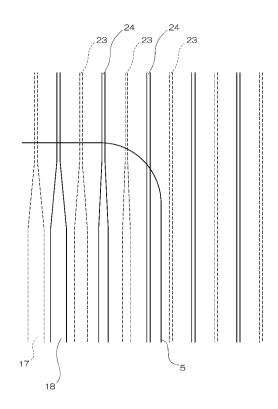

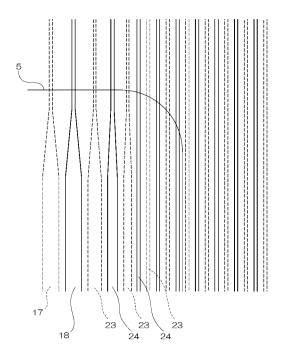

本実施形態におけるプロセスフローとレジストマスクパターンについて図 2 、 3 を用いて説明する。

図 2 ( a )乃至( g )は、第 1 の実施形態に係る縦型パワーMOSFETの製造方法を示す断面図である。

先ず、図 2 (a)に示すように、 n <sup>†</sup> ドレイン層 2 となる基板上に高抵抗層 1 2 を成長させる。次に、図 2 (b)に示すように、この基板表面に、レジスト 1 4 をマスクとして、ボロン 1 5 を注入する。次に、図 2 (c)に示すように、 n ピラー層 3 を形成するレジストマスク 1 4 を形成した後、リン 1 6 を注入する。その後、図 2 (d)に示すように、高抵抗層 1 2 で不純物ドープ層を埋め込む。そして、図 2 (a)乃至(d)に示すプロセスを複数回繰り返すことにより、図 2 (e)に示すように、 n <sup>†</sup> ドレイン層 2 上に不純物ドープ層を複数層積層する。その後、熱拡散を行うことにより、図 2 (f)に示すように、埋め込まれたドープ層がつながり、縦長の n ピラー層 3 と p ピラー層 4 が形成される。その後、図 2 (g)に示すように、MOS工程を行い、素子を完成させる。

#### [0023]

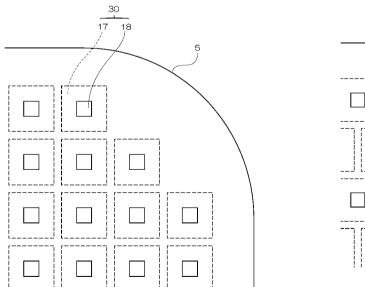

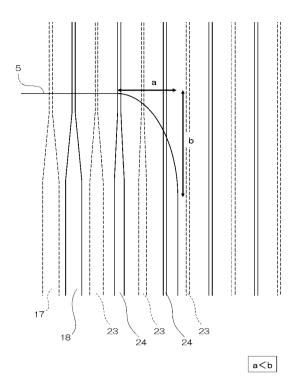

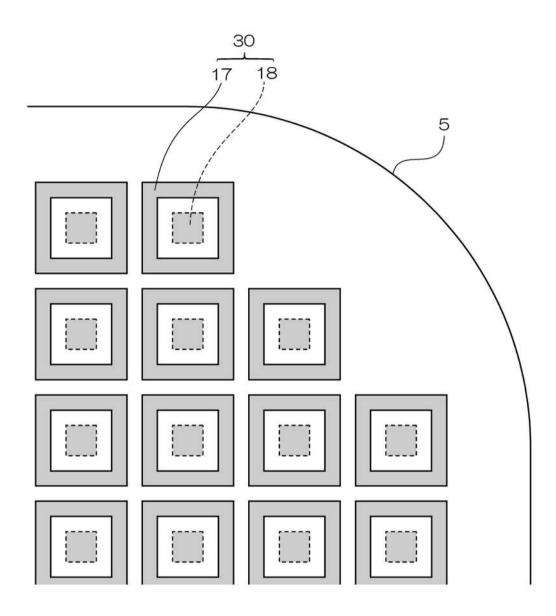

図3は、第1の実施形態に係る縦型パワーMOSFETのピラー層を形成するためのマスクパターンを示す図である。

nピラー層3とpピラー層4を形成するマスクパターンは図3のようにする。なお、図3においては、便宜上、nピラー層形成用のマスクとpピラー層形成用のマスクを重ねて示している。また、nピラー層3及びpピラー層4が形成される位置と、pベース層5が形成される位置との相対的な関係を明らかにするために、図中に最外部のpベース層5(図1参照)の外縁に相当する曲線も示している。後述する他のマスクパターン図についても同様である。

## [0024]

図3に示すパターンでは、nピラー層3を形成するためのnピラー層用開口部17の両脇を挟むように、pピラー層用開口部18が配置されている。このような配置とするったで、スーパージャンクション構造の基本単位であるpピラー層中央から隣のpピラー層中央から隣のpピラー層中央から隣のpピラー層中央がら隣のpピラー層中央がら隣のpピラー層で形成される。すなわち、図3に示す基本単位30が、本実施でに係るMOSFETのスーパージャンクション構造を形成する際の基本単位となる。pピラー層はで、この基本単位30を並列に配置する。すると、セル部pピラー層は、隣り合うpピラー層1が接続されるため、図1に示すように横方向プロファイルに谷があるようなプロファイルとなる。すなわち、nピラー層3及びpピラー層4の配列方向におけるようなプロファイルとなる。すなわち、nピラー層3及びpピラー層4の配列方向におけるば、pピラー層4の不純物濃度プロファイルは、pピラー層4の両端部以外の位置、例えば、pピラー層4の中央部に極小値を有する。このようにすると、終端部との境界でパターンを変化させなくとも、最外部ピラー層の不純物量はセル部ピラー層の不純物量の半分となる。このように、各マスク開口幅はセル部と境界部で同じであることから、開口ばらつきが生じることはない。このため、安定した高耐圧を実現することができる。

#### [0025]

このように、本実施形態によれば、セル部のスーパージャンクション構造の基本単位となる(pピラー層 / n ピラー層 / p ピラー層)構造もしくは(n ピラー層 / p ピラー層 / n ピラー層)構造を一つに形成することにより、素子部と終端部で不連続領域があっても

基本単位の配置パターンを変化させることで、理想的な濃度変化を得ることができ、終端部の高耐圧化を実現することができる。この結果、プロセス上のばらつきに対する耐圧の低下が小さいスーパージャンクション構造を有するMOSFETを得ることができ、スーパージャンクション構造の不純物濃度を上げることが可能となり、低オン抵抗化が可能となる。

### [0026]

なお、図3に示したパターンでは、pピラー層用開口部18がnピラー層用開口部17を挟み込むパターンを示したが、nピラー層用開口部17がpピラー層用開口部18を挟み込む配置でも実施可能である。この場合、nピラー層3の横方向プロファイルに谷が生じる。すなわち、各nピラー層3の不純物濃度プロファイルは、nピラー層3の両端部以外の位置に極小値を有する。

#### [0027]

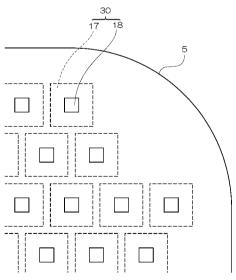

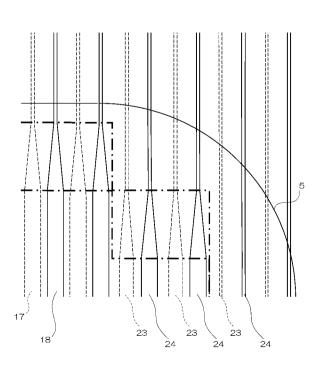

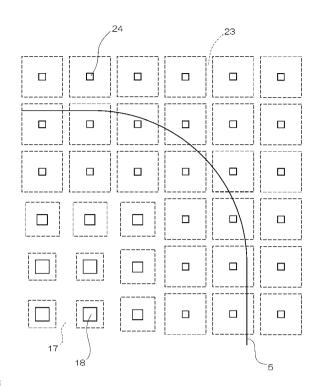

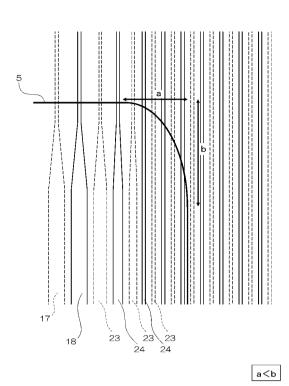

パターンの変形例を図4に示す。素子終端部のpベース層5端部は電界集中が起き易い。このため、コーナー部では、大きな曲率をつけたパターンとする必要がある。そして、コーナー部での電界集中を抑制する為には、スーパージャンクション構造をコーナーの内側に形成する必要がある。コーナー部の内側で、スーパージャンクション構造を四角形に形成すると、スーパージャンクション構造が形成されている部分の面積が減り、従って素子の有効面積が減り、オン抵抗が増加してしまう。このため、pベース層5の曲率に応じてスーパージャンクション構造も曲率をつける必要がある。

## [0028]

しかし、n ピラー層 3 とp ピラー層 4 とに独立に曲率をつけると、局所的に不純物量のバランスが崩れてしまい耐圧が低下してしまう。そこで、耐圧低下を防ぐ為に、図 4 に示すように、上方から見た n ピラー層 3 及び p ピラー層 4 の形状を最外部の p ベース層 5 の外縁の湾曲に沿って整形し、基本単位の配置を階段状に変化させることで、有効面積を減らさず、且つ、不純物量のバランスを崩さずにスーパージャンクション構造を形成することが可能である。

### [0029]

別の変形例を図5に示す。これまでの実施例は、ストライプ状にスーパージャンクション構造を形成するパターンについて示してきた。図5では、マトリクス状にpピラー層3を配置する場合のパターンを示している。すなわち、島状のpピラー層用開口部18を囲むように、環状のnピラー層用開口部17が形成されている。このようなパターンとすることで、基本単位であるnピラー層3中央から隣のnピラー層3中央まで1セットとして形成することが可能となる。マトリクス状にパターンを配置することで、素子の表面に平行な相互に直交する2方向において、同様な配置とすることが可能となる。そして、コーナー部にスーパージャンクション構造を形成しないことも可能である。

#### [0030]

別の変形例を図6に示す。図5では、環状の n ピラー層用開口部17が島状の p ピラー層用開口部18を囲むように形成されていたが、図6に示すパターンでは、大きな島状の n ピラー層用開口部17の中に、小さな島状の p ピラー層用開口部18が形成されている。このようなパターンとすると、パターンが重なっている部分は、 n 型ドーパント(リン)と p 型ドーパント(ボロン)の両方が注入されてしまうため、あらかじめ n 型ドーパントを打ち消すように p 型ドーパントを多く注入する必要がある。しかし、 n ピラー層用開口部の面積が大きくなることからパターン寸法のばらつきによる面積変化が小さくなるため、プロセスばらつきの影響を小さくすることができる。

#### [0031]

さらにまた、別の変形例を図7に示す。図7に示すようなパターンとすることで、pピラー層4が千鳥状に配置されるスーパージャンクション構造を形成することができる。これまでのパターン例で示してきたように基本単位毎にパターンを配置する為、パターン寸法を変化させなくとも自由にスーパージャンクション構造のパターンを変化させることが可能である。

10

20

30

40

20

30

40

50

#### [0032]

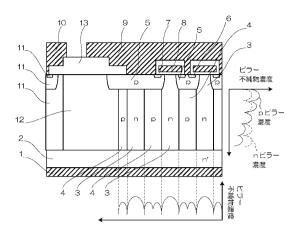

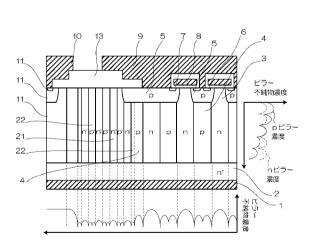

#### (第2の実施形態)

図8は本発明の第2の実施形態に係るパワーMOSFETの構成を模式的に示す断面図である。図1と同一部分の詳しい説明は省略し、ここでは異なる部分についてのみ説明する。

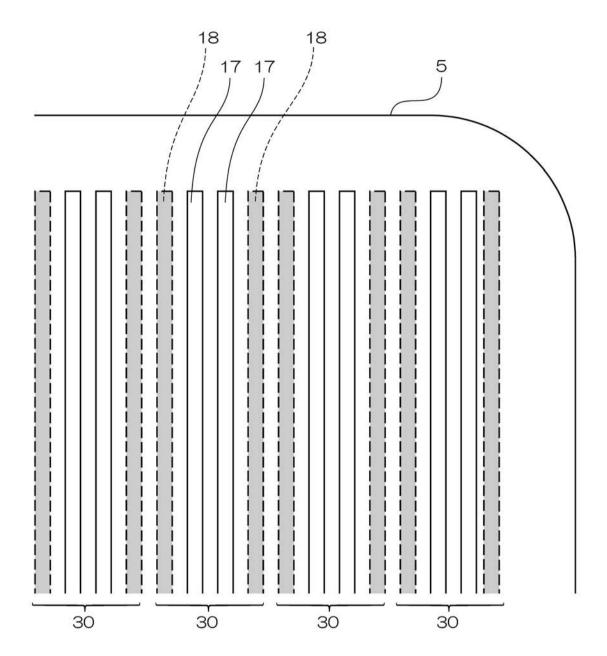

### [0033]

図に示す構造では、 n ピラー層 3 と p ピラー層 4 の横方向プロファイルに谷がある。このような構造は、図 9 に示すようなマスクパターンを用いることで形成可能である。二本のストライプ状の n ピラー層用開口部 1 7 を、二本のストライプ状の p ピラー層用開口部 1 8 で挟み込むような配置となっている。図 3 、 4 で示したパターンでは、二本の p ピラー層 4 不純物量と n ピラー層 3 不純物量を等しくするためには、マスク開口幅を 2 倍とするか、イオン注入ドーズ量を 2 倍にする必要があった。これに対して、図 9 に示すパターンでは、二本の p ピラー層用開口部 1 8 に対して、二本の n ピラー層用開口部 1 7 であるため、同一の開口幅と注入ドーズとすることができ、 n ピラー層 3 と p ピラー層 4 とのばらつき度合いを等しくすることができ、安定した耐圧が得られ易い。

#### [0034]

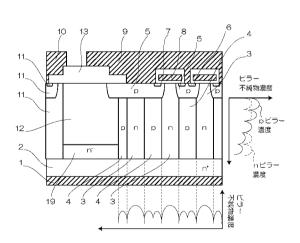

## (第3の実施形態)

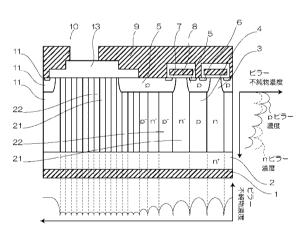

図10は本発明の第3の実施形態に係るパワーMOSFETの構造を模式的に示す断面図である。前述の実施形態と同一部分の詳しい説明は省略し、ここでは異なる部分についてのみ説明する。

#### [0035]

図に示す構造では、pピラー層 4 の縦方向プロファイルが変化している。ソース電極 9 側では、n ピラー層 3 よりも p ピラー層 4 の濃度が高く、ドレイン電極側では、p ピラー層 4 の濃度が低い。このような縦方向プロファイルとすることで安定した耐圧と高アバランシェ耐量を得ることができる。

#### [0036]

縦方向の濃度プロファイルに傾斜を付けると、 n ピラー層 3 と p ピラー層 4 との不純物量が等しくなくなった時の耐圧低下が傾斜を付けない場合よりも小さい。これにより、工程ばらつきによる耐圧低下が抑えられ、安定した耐圧が得られる。また、スーパージャンクション構造の上下端の電界が小さくなるため、高アバランシェ耐量が得られる。アバランシェ降伏が起きると、ドリフト層内に大量のキャリアが発生し、ドリフト層上下端の電界が増加する。ドリフト層上下端の電界がある程度を超えると、電界集中が止まらずに負性抵抗が発生して、素子が破壊してしまう。これによりアバランシェ耐量が決まっている。縦方向プロファイルに傾斜を付けて、予め上下端の電界を小さくしておくことで、負性抵抗が発生し難くなり、高アバランシェ耐量を得ることができる。

## [0037]

図に示す構造は、各埋め込みプロセスにおけるイオン注入ドーズを変化させることで形成することができる。スーパージャンクション構造上下端の電界を下げるためには、ソース側でpピラー層 4 が n ピラー層 3 よりも不純物量が多く、ドレイン側で少なくなっていればよい。図は、pピラー層 4 の不純物量を変化させた場合を示したが、pピラー層 4 の不純物量を一定として、 n ピラー層 3 の不純物量がドレイン側に向かって増やしても実施可能であり、pピラー層 4 と n ピラー層 3 の両方の不純物量を変化させても実施可能である。

#### [0038]

変形例を図11に示す。図に示す構造では、終端部の n <sup>+</sup> ドレイン層 2 上、すなわち、高抵抗層 1 2 の下層に、 n <sup>-</sup> 層 1 9 が形成されている。図 1 0 に示した構造では、終端部が全て高抵抗層 1 2 となっている。このため、終端部の耐圧はスーパージャンクション構造よりも高い。しかし、終端部耐圧以上の電圧が印加されて、終端部でアバランシェ降伏が起こると、終端部上下端の電界が上がり易く、負性抵抗が発生し易い。このため、終端

部のみのアバランシェ耐量は低い。そこで、図11に示すようにドレイン電極側に n 「層19を形成することで下側の電界を下げることでアバランシェ耐量を向上することができる。更に、図12に示すように終端部のソース側表面に p 「層20を形成することで、ドリフト層上部電界を下げることができるため、より高アバランシェ耐量を実現することができる。

### [0039]

n 「層19やp」層20の不純物濃度は、nピラー層3やpピラー層4の不純物濃度の1/20~1/4程度とすることが望ましい。また、図11や図12に示した構造は、埋め込み成長層の不純物濃度を変化させることで形成可能である。成長層の濃度を変化させると、同時にピラー層の不純物濃度も変化する為、イオン注入ドーズ量を変化させなくとも自動的に不純物濃度が変化する。ピラー層のドーズ量も変化させて、終端部の濃度変化よりもスーパージャンクション部の濃度変化を大きくすることも可能である。

### [0040]

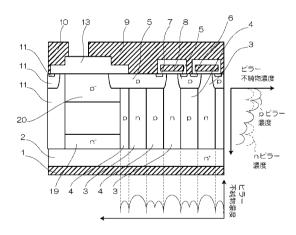

(第4の実施形態)

図13は本発明の第4の実施形態に係るパワーMOSFETの構造を模式的に示す断面図である。前述の実施形態と同一部分の詳しい説明は省略し、ここでは異なる部分についてのみ説明する。

#### [0041]

図に示す構造では、終端部に高抵抗層を形成せずに、終端部にもスーパージャンクション構造を形成している。横方向プロファイルに示しているように終端部のスーパージャンクション構造のピラー素の不純物濃度は、セル部よりも低い。これにより、セル部耐圧よりも高い終端耐圧を得ることができる。

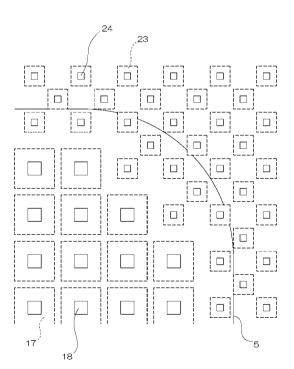

## [0042]

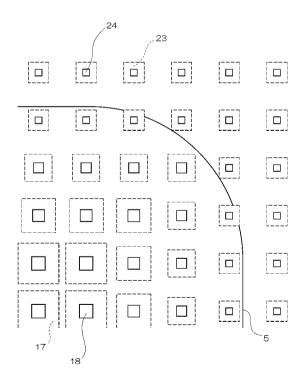

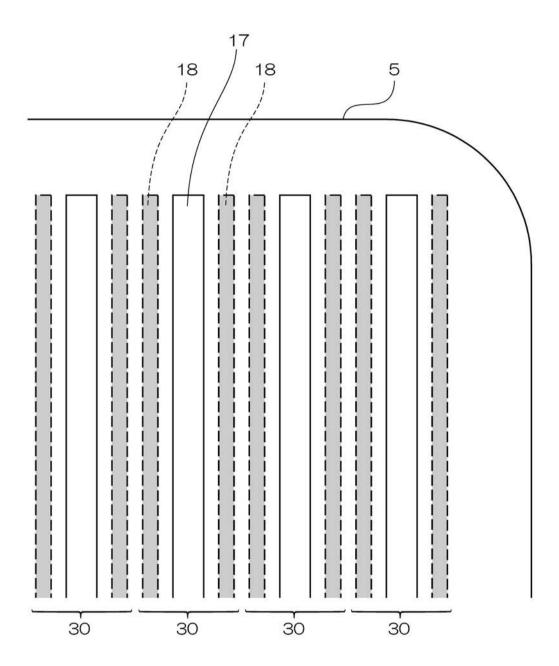

上述の各実施形態において示してきたように、スーパージャンクションの基本単位毎にパターンを配置することで、セル部と終端部のスーパージャンクション構造を同時に形成しても、それぞれのピラー層の不純物濃度を独立に制御することが可能である。図14にピラー層形成用マスクパターン例を示す。図に示すようにセル部の開口面積を広く、終端部の開口面積を狭くすることで、終端部スーパージャンクション構造のピラー層の不純物濃度を下げることが可能である。この時、nピラー層用開口部17の面積とpピラー層用開口部18の面積との比を終端部のnピラー層用開口部23の面積とpピラー層用開口部24の面積との比に等しくすることで、どちらのスーパージャンクション構造も不純物量のバランスを崩すことなく形成することができる。

#### [0043]

また、セル部のスーパージャンクション構造と終端部のスーパージャンクション構造とを同時に形成することで、セル部と同様に縦方向のピラー層の濃度プロファイルに傾斜を付けることができる。これにより、埋め込み成長層の不純物濃度を変化させなくともセル部と終端部のどちらもドリフト層上下端の電界が小さくなり、高アバランシェ耐量が実現できる。なお、図14においては、pピラー層3やp ピラー層22が格子状に配置されるマスクパターンを示したが、ストライプ状や千鳥状に配置されるパターンでも実施可能である。

## [0044]

(第5の実施形態)

図 1 5 は本発明の第 5 の実施形態に係るパワーMOSFETの構造を模式的に示す断面図である。前述の実施形態と同一部分の詳しい説明は省略し、ここでは異なる部分についてのみ説明する。

## [0045]

図に示す構造では、終端部にもスーパージャンクション構造が形成され、且つ、終端部のスーパージャンクション構造の横方向周期はセル部の横方向周期よりも狭い。終端部の横方向周期を狭くすることで、終端部のスーパージャンクション構造が空乏化しやすくなり、終端耐圧が上がる。

10

20

30

40

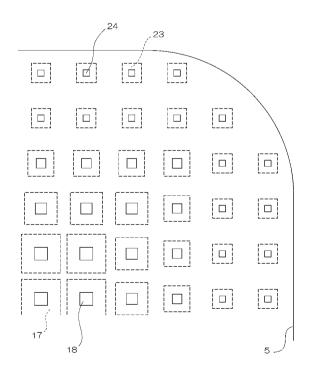

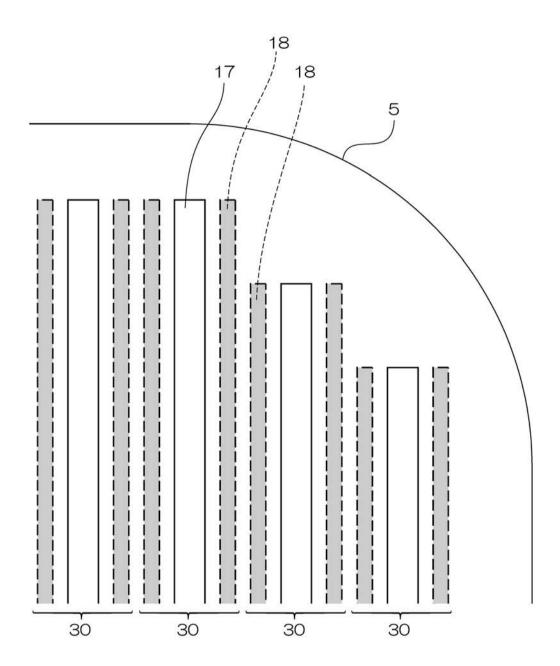

#### [0046]

上述の各実施形態において示してきたように、スーパージャンクションの基本単位毎にパターンを配置することで、セル部と終端部のスーパージャンクション構造を同時に形成しても、横方向周期も自由に変化させることができる。図16にマスクパターン例を示す。終端部のスーパージャンクション構造を形成するn ピラー層用マスク開口部23とpピラー層用マスク開口部24の面積を小さく、且つ、ピッチを狭くして配置させることで、図15に示した構造を形成することができる。図では、終端部は千鳥状に配置しているが、格子状も実施可能である。また、セル部のスーパージャンクション構造も含めてストライプ状など他のパターンでも実施可能である。

### [0047]

(第6の実施形態)

図17は本発明の第6の実施形態に係るパワーMOSFETの構造を模式的に示す断面 図である。前述の実施形態と同一部分の詳しい説明は省略し、ここでは異なる部分につい てのみ説明する。

#### [0048]

図に示す構造では、セル部及び終端部の双方にスーパージャンクション構造を形成しているが、終端部のスーパージャンクション構造のピラー層不純物濃度は、外側に向けて徐々に低減し、一定となっている。すなわち、最もセル部側(n ピラー層 3 側)に配置されたn ピラー層 2 1 の不純物濃度は、それ以外のn ピラー層 2 1 の不純物濃度よりも高く、最もセル部側(p ピラー層 4 側)に配置されたp ピラー層 2 2 の不純物濃度は、それ以外のp ピラー層 2 2 の不純物濃度は、それ以外のp ピラー層 2 2 の不純物濃度は、それ以外のp ピラー層 2 2 の不純物濃度よりも高くなっている。このように段階的にピラー層不純物濃度を変化させることで、マスクパターンが基本単位毎の配置になっていなくとも局所的な不純物濃度ばらつきが発生し難く、高耐圧を実現することができる。

#### [0049]

徐々にピラー層の不純物濃度を低下させていく場合、n ピラー層 2 1 の濃度が、隣り合う二つのp ピラー層 2 2 の平均の濃度になっていることで、n ピラー層 2 1 とp ピラー層 2 2 との不純物バランスが取れる。このため、n ピラー層 2 1 の濃度変化とp ピラー層 2 2 の濃度変化は同じ傾きで変化させることが望ましい。また、ピラー層の濃度が傾斜している領域は、ほぼ最外部のpベース層 5 の直下に位置している。最外部のpベース層 5 の幅は、例えば 2 0 乃至 5 0 μ m程度である。素子の中央部から終端部に向かって、ピラー層の濃度が低下し始める始端は、最外部のpベース層 5 の直下に位置していてもよく、それより内部に位置していてもよい。

#### [0050]

図17に示した構造は、図18に示すようなマスクパターンを用いて形成することができる。図は、ピラー層がストライプ状に形成される場合のパターン例である。横方向周期は変化させずにマスク開口幅を徐々に狭くしていくことで、ピラー濃度を徐々に低減させることができる。

#### [0051]

n ピラー層 2 1 の濃度が、隣り合う二つの p ピラー層 2 2 の平均の濃度となるように、 n ピラー層用開口部 2 3 の幅と p ピラー層用開口部 2 4 の幅は、同様な傾きで狭くしていかなければならない。例えば、 p ピラー層用開口部 2 4 の幅を、 2  $\mu$  m、 1 . 8  $\mu$  m、 1 . 6  $\mu$  m、 1 . 4  $\mu$  mと変化させる場合、その間に配置される n ピラー用開口部 2 3 の幅は、 1 . 9  $\mu$  m、 1 . 5  $\mu$  mとしなければならない。そして、不純物量バランスを崩さないために、 p ピラー層用開口部 2 4 の幅を変化させ始めたら、 n ピラー層用開口部 2 3 の幅で変化を終えるようにすることが望ましい。

## [0052]

また、ストライプ状にピラー層を形成した場合、ストライプが延びる方向(ストライプ方向)においても徐々に開口幅を狭くしていくことで、横方向周期を変化させずにピラー層濃度を徐々に低減させることができる。ストライプ方向においても不純物量のバランスを崩さない為に、 p ・ピラー層用開口部 2 4 と n ・ピラー用開口部 2 3 の幅は、同様に狭

10

20

30

40

20

30

40

50

くしなければならない。このように2次元的に寸法を変化させることで、各埋め込みドープ層同士の位置合わせずれが生じても耐圧低下が起き難くなる。ストライプ方向の開口幅を変化させる長さは、位置合わせずれが無視できるような長さとして、ピラー層の配列方向(横方向)におけるピラー層間隔よりも長く、ピラー層間隔の3~8倍程度とすることが望ましい。

### [0053]

このようにマスク開口幅を連続に変化させることで、開口幅のばらつきに対する影響を小さくすることができ、高耐圧が得やすい。また、pピラー層とnピラー層の両方の濃度をイオン注入とマスク開口幅で制御するため、終端部スーパージャンクション構造の横方向周期を変えずとも終端部の耐圧を向上することができる。

## [0054]

そして、pピラー層とnピラー層の両方の濃度をイオン注入とマスク開口幅で制御する場合において、終端部のピラー層の不純物濃度を下げることは、横方向周期を縮めることよりも、プロセスばらつきによる耐圧低下を抑制するために有効である。ピラー層濃度を下げることも横方向周期を縮めることもスーパージャンクション構造を空乏化し易くして耐圧を上げることには有効である。しかし、マスク開口幅がばらついた時の影響の度合いは、周期をそのままにして開口幅を狭くした場合と、周期を縮めて開口幅をそのままとした場合とで異なる。

#### [0055]

周期をそのままにしてマスク開口幅を狭くした場合、開口幅のばらつきが寸法によらず一定だとすると、埋め込まれるドープ層の不純物量のばらつきは、セル部と終端部とで同じとなる。耐圧低下は不純物量のばらつきに比例するので、バランスしている状態で得られる最大耐圧からの低下分は、セル部と終端部とで同じになる。そして、ピラー層を低濃度化することで終端部の耐圧はセル部の耐圧よりも高くなるため、プロセスがばらついても終端部の耐圧よりもセル部の耐圧が低いという関係は変わらない。

#### [0056]

一方、周期を縮めてマスク開口幅をそのままとした場合、ピラー層一つ一つのマスク開口幅のばらつきは変わらないのでピラー層一つ一つの不純物量ばらつきはセル部も終端部も同じとなる。しかし、終端部では周期が狭くなっているため、横方向で不純物量のばらつきを平均すると周期に反比例して増大する。つまり、周期を1/2にすると、不純物量のばらつきは2倍になってしまう。このため、最大耐圧はセル部よりも終端部が高いが、プロセスばらつきが大きくなると、セル部よりも終端部の方が低い耐圧となってしまい、耐圧低下が著しい。

### [0057]

このように、本実施形態に示す周期をそのままで濃度を徐々にさせる構造と、特許文献 1 で示されるような周期を徐々に縮めて濃度をそのままという構造とでは、最大耐圧を向上させるという点では同じであるが、プロセスばらつきによる耐圧低下は本実施形態の構造の方が小さい。

### [0058]

また、図14に示した構造と同様に、セル部と終端部のスーパージャンクション構造を同時に形成することで、どちらにおいても縦方向プロファイルに傾斜を付けることが可能となり、高アバランシェ耐量を得ることができる。

### [0059]

また、セル部のコーナーは、電界集中が起き易い為、コーナー部下のスーパージャンクション構造のピラー層濃度は低いことが望ましい。そこで、図4と同様に階段状にスーパージャンクション構造を変化させることで、有効面積を減らさずにピラー層の幅を変化させることが低オン抵抗と高耐圧を両立させることに有効である。図19にパターン例を示す。図中の一点鎖線で囲んだ領域が徐々に開口幅を変化させている領域である。このように変化させている領域を階段状に配置することで、有効面積を減らさずにコーナー部スーパージャンクション構造の低濃度化を実現することができる。

#### [0060]

このように、本実施形態によれば、セル部から終端部へと素子の外側に向かうにつれて、pピラー層とnピラー層の不純物濃度を低くしていく。このとき、急激に濃度を低下させるのではなく、徐々に変化させることで、プロセスばらつきにより生じる濃度ばらつきの影響を抑制し、高耐圧を実現することができる。

#### [0061]

[0062]

特許文献1(特開2001-298190号公報)では、ピラー層濃度を一定としたまま徐々にピラー層の幅を変化させることでスーパージャンクション構造の横方向周期を変化させる構造が示されている。この構造はp型不純物をイオン注入して、n型半導体層で埋め込み結晶成長を行う工程を複数回繰り返すことで形成が可能である。この場合、nピラー層濃度はn型成長層の不純物濃度で決まる為、横方向濃度プロファイルを制御することは困難である。このため、pピラー層内に含まれる不純物量とnピラー層内に含まれる不純物量を等しくするために、pピラー層を形成するためのイオン注入時に、マスク開口幅と開口位置を同時に変化させなければならない。そして、n型成長層の不純物を打ち消すだけのp型不純物量をイオン注入する必要があるため、イオン注入のドーズ量が高くなる。このため、レジストパターンの変形やドーズ量ばらつきによる耐圧低下が起き易い。

これに対して、p型不純物及びn型不純物の両方をイオン注入し、低濃度層による埋め込み結晶成長を複数回繰り返すプロセスを用いてスーパージャンクション構造を形成する場合では、プロセスばらつきの影響を小さくすることができる。このプロセスでは、nピラー層不純物濃度もpピラー層不純物濃度と同様にイオン注入とマスク開口幅により制御させるため、横方向周期を変化させなくとも、終端部のピラー層形成用マスク開口幅のみを縮めることでピラー層濃度を低減できる。これにより、終端部のスーパージャンクション構造は、セル部のスーパージャンクション構造よりも低い電圧で完全空乏化して、高耐圧が得られる。そして、n型成長層がないことでpピラー層形成用イオン注入のドーズ量は低くなる。これにより、マスク開口幅やドーズ量がばらついても耐圧低下が起き難い。更に、本実施形態で示すように、開口幅を徐々に変化させて段階的にピラー層濃度を低減することで、プロセスばらつきの影響を受け難くすることが可能である。

### [0063]

## (第7の実施形態)

図 2 0 は本発明の第 7 の実施形態に係るパワーMOSFETの構造を模式的に示す断面図である。前述の実施形態と同一部分の詳しい説明は省略し、ここでは異なる部分についてのみ説明する。

### [0064]

図に示す構造では、終端部のスーパージャンクション構造の濃度と周期を同時に変化させている。どちらも徐々に変化させている。前述したように周期を縮めるとプロセスばらつきによる耐圧低下が起き易くなるが、周期を縮めることで最大耐圧が向上するため、セル部よりも終端部の耐圧を高くすることができ、結果的にプロセスばらつきによる耐圧低下を抑えることができる。このような構造は、図21に示すようなマスクパターンとすることで形成することができる。

## [0065]

#### (第8の実施形態)

図 2 2 は本発明の第 8 の実施形態に係るパワーMOSFETの形成するためのマスクパターンを模式的に示す平面図である。前述の実施形態と同一部分の詳しい説明は省略し、ここでは異なる部分についてのみ説明する。

## [0066]

図に示すパターン例では、 p ピラー層用開口部 1 8 及び p ピラー層用開口部 2 4 がマトリクス状に配置されており、この p ピラー層用開口部 1 8 及び p ピラー層用開口部 2 4 から離隔して、 n ピラー層用開口部 1 7 及び n ピラー層用開口部 2 3 が格子状に設けられている。

10

20

30

40

20

30

40

50

p ピラー層用開口部 1 8 及び n ピラー層用開口部 1 7 の開口幅は、素子の中央部から終端部に向かって、縦横どちらの方向においても徐々に小さくなっている。これにより、ピラー層濃度を素子の中央部から終端部に向かって徐々に低減させている。なお、図 2 2 では、p ピラー層用開口部 1 8 及び p ピラー層用開口部 2 4 をマトリクス状に配置するパターンを示したが、千鳥状に配置するパターンでも実施可能である。

#### [0067]

また、第4の実施形態で示したように、基本単位ごとにパターンを配置した場合でも、徐々に開口幅を縮めることで各埋め込み層毎の縦方向の位置合わせずれによる影響を受け難くなり、高耐圧が得られ易い。パターン例を図23に示す。なお、図23では、pピラー層用開口部18をマトリクス状に配置する例を示しているが、ストライプ状に配置する場合でも千鳥状に配置する場合でも実施可能である。更に、図24に示すように、基本単位のパターンをセル内で徐々に縮めて、終端部にスーパージャンクション構造を形成しないパターンも実施可能である。

## [0068]

(第9の実施形態)

図 2 5 は本発明の第 9 の実施形態に係るパワーMOSFETの形成するためのマスクパターンを模式的に示す平面図である。前述の実施形態と同一部分の詳しい説明は省略し、ここでは異なる部分についてのみ説明する。

#### [0069]

図25に示すパターン例は、図18と同様にストライプ状にスーパージャンクション構造を形成する場合のパターン例である。図18と異なる点は、pベース層5のコーナー部の曲率である。ストライプ状にスーパージャンクション構造を形成した場合、ストライプが延びる方向(ストライプ方向)は空乏層が伸び易く、ストライプの配列方向は空乏層が伸び難い。このため、コーナー部の中心ではなく、その方向がストライプの配列方向に近づいている部分で電界集中が起き易い。このため、コーナー部の曲率は、配列方向で長く、ストライプ方向で短いこと(図中a < b ) が望ましい。なお、図26に示すように終端部のピラー層間隔を縮めた場合でも実施可能である。

#### [0070]

以上、本発明の具体的な態様の例を第1乃至第9の実施形態により説明したが、本発明は、これらの実施形態に限定されるものではない。例えば、上述の各実施形態では、第1の導電型をn型、第2の導電型をp型として説明したが、第1の導電型をp型、第2の導電型をn型としても実施可能である。また、第1乃至第9の実施形態では、素子部の最外部をpピラー層としたが、nピラー層としても同様な設計を行うことで同等の効果を得ることができる。更に、MOSゲート部やスーパージャンクション構造の平面パターンも、スーパージャンクション構造のピラーパターンと同様にストライプ状に限らず、格子状や千鳥状に形成してもよい。

## [0071]

更にまた、終端部表面はフィールドプレート構造を用いた構造とする例を示したが、RESURF構造やガードリング構造、フローティングフィールドプレート構造なども実施可能であり、表面の構造には限定されない。更にまた、MOSゲート構造はプレナー構造である例を説明したが、トレンチ構造でも実施可能である。

#### [0072]

更にまた、pピラー層 4 とp ・ピラー層 2 2 は、n ・ドレイン層 2 に接していなくてもよい。図 2 では、高抵抗層が成長している基板表面にイオン注入を行うことでスーパージャンクション構造を形成しているため、pピラー層 4 は n ・ドレイン層 2 に接しているが、n ・ドレイン層 2 上に n 型半導体層を成長させることで、pピラー層が n ・ドレイン層 1 に接していない構造を形成することも可能である。また、n ピラー層 3 よりも濃度が低い n ・層を成長した基板表面にスーパージャンクション構造を形成してもよい。

#### [0073]

更にまた、高抵抗層12は完全な真性半導体でなくてもよく、不純物濃度がnピラー層

20

30

40

50

3 に対して充分に小さければ高耐圧を得ることができる。但し、高抵抗層 1 2 の不純物濃度は、 n ピラー層 3 の不純物濃度の 1 / 1 0 以下であることが望ましい。そして、素子外周部ではなく、素子セル側の電界が高くなるように、 n 型であることが望ましい。

#### [0074]

更にまた、上述の各実施形態においては、高抵抗層を形成する工程と、この高抵抗層に p型不純物及びn型不純物を注入する工程とを複数回繰り返して、その後不純物を拡散さ せることにより、nピラー層及びpピラー層を形成する例を示したが、本発明はこれに限 定されない。例えば、高抵抗層を形成した後、この高抵抗層に不純物を複数水準の加速電 圧により注入し、その後不純物を拡散させてもよい。これによっても、高抵抗層内に深さ 方向に分布した不純物領域を形成することができ、厚さ方向に延びるnピラー層及びpピ ラー層を形成することができる。

[0075]

更にまた、半導体としてシリコン(Si)を用いたMOSFETを説明したが、半導体としては、例えばシリコンカーバイト(SiC)や窒化ガリウム(GaN)、等の化合物 半導体やダイアモンドなどのワイドバンドギャップ半導体を用いることもできる。

[0076]

更にまた、上述の第1乃至第9の実施形態は、技術的に可能な限りにおいて、相互に組み合わせて実施してもよい。このように、上述の実施形態のうち複数の実施形態を組み合わせた態様も、本発明の範囲に含有される。また、上述の実施形態又はその組み合わせに対して、当業者が設計の変更若しくは構成要素の追加などを行ったものも、本発明の範囲に含まれる。

[0077]

更にまた、上述の各実施形態においてはスーパージャンクション構造を有する電力用半導体素子としてMOSFETを例示したが、本発明に係る電力用半導体素子はMOSFETに限定されず、本発明の構造は、スーパージャンクション構造を有する素子であれば、SBD(Schottky Barrier Diode:ショットキーバリアダイオード)、MOSFETとSBDとの混載素子、SIT(Static Induction Transistor:静電誘導トランジスタ)、IGBT(Insulated Gate Bipolar Transistor:絶縁ゲートバイポーラトランジスタ)などの素子でも適用可能である。例えば、上述の各実施形態をIGBTに適用する場合は、ドレイン電極1とn \*ドレイン層2との間に、正孔の供給源となるP層を形成すればよい。

【図面の簡単な説明】

[0078]

【図1】本発明の第1の実施形態に係るスーパージャンクション構造を有する縦型パワーMOSFETを示す断面図である。

【図2】(a)乃至(g)は、第1の実施形態に係る縦型パワーMOSFETの製造方法を示す断面図である。

【図3】第1の実施形態に係る縦型パワーMOSFETのピラー層を形成するためのマスクパターンを示す図である。

【図4】第1の実施形態の変形例に係る縦型パワーMOSFETのピラー層を形成するためのマスクパターンを示す図である。

【図5】第1の実施形態の他の変形例に係る縦型パワーMOSFETのピラー層を形成するためのマスクパターンを示す図である。

【図 6 】第 1 の実施形態の更に他の変形例に係る縦型パワーMOSFETのピラー層を形成するためのマスクパターンを示す図である。

【図7】第1の実施形態の更に他の変形例に係る縦型パワーMOSFETのピラー層を形成するためのマスクパターンを示す図である。

【図8】本発明の第2の実施形態に係るスーパージャンクション構造を有する縦型パワー MOSFETを示す断面図である。

【図9】第2の実施形態に係る縦型パワーMOSFETのピラー層を形成するためのマス

40

クパターンを示す図である。

- 【図10】本発明の第3の実施形態に係るスーパージャンクション構造を有する縦型パワ - MOSFETを示す断面図である。

- 【図11】第3の実施形態の変形例に係るスーパージャンクション構造を有する縦型パワ - MOSFETを示す断面図である。

- 【図12】第3の実施形態の他の変形例に係るスーパージャンクション構造を有する縦型 パワーMOSFETを示す断面図である。

- 【図13】本発明の第4の実施形態に係るスーパージャンクション構造を有する縦型パワ - MOSFETを示す断面図である。

- 10 【図14】第4の実施形態に係る縦型パワーMOSFETのピラー層を形成するためのマ スクパターンを示す図である。

- 【図15】本発明の第5の実施形態に係るスーパージャンクション構造を有する縦型パワ - MOSFETを示す断面図である。

- 【図16】第5の実施形態に係る縦型パワーMOSFETのピラー層を形成するためのマ スクパターンを示す図である。

- 【図17】本発明の第6の実施形態に係るスーパージャンクション構造を有する縦型パワ - MOSFETの素子構造の断面図

- 【図18】第6の実施形態に係る縦型パワーMOSFETのピラー層を形成するためのマ スクパターンを示す図である。

- 20 【図19】第6の実施形態の変形例に係る縦型パワーMOSFETのピラー層を形成する ためのマスクパターンを示す図である。

- 【 図 2 0 】 本 発 明 の 第 7 の 実 施 形 態 に 係 る ス ー パ ー ジ ャ ン ク シ ョ ン 構 造 を 有 す る 縦 型 パ ワ - MOSFETを示す断面図である。

- 【図21】第7の実施形態に係る縦型パワーMOSFETのピラー層を形成するためのマ スクパターンを示す図である。

- 【図22】本発明の第8の実施形態に係るスーパージャンクション構造を有する縦型パワ - MOSFETのピラー層を形成するためのマスクパターンを示す図である。

- 【図23】第8の実施形態の変形例に係る縦型パワーMOSFETのピラー層を形成する ためのマスクパターンを示す図である。

- 【図24】第8の実施形態の他の変形例に係る縦型パワーMOSFETのピラー層を形成 するためのマスクパターンを示す図である。

- 【図25】本発明の第9の実施形態に係るスーパージャンクション構造を有する縦型パワ - MOSFETのピラー層を形成するためのマスクパターンを示す図である。

- 【図26】第9の実施形態の変形例に係る縦型パワーMOSFETのピラー層を形成する ためのマスクパターンを示す図である。

## 【符号の説明】

## [0079]

ドレイン電極(第1の主電極)、2 n <sup>+</sup>ドレイン層(第1の半導体層)、3 n ピ ラー層(第2の半導体層)4 pピラー層(第3の半導体層)、5 pベース層(第4の 半導体層)、6 nソース層(第5の半導体層)7 Si酸化膜(ゲート絶縁膜)、8 ゲート電極(第1の制御電極)、9 ソース電極(第2の主電極)10 フィールドスト ップ電極、11 フィールドストップ層、12 高抵抗層(第6の半導体層)、13 ィールド絶縁膜、14 レジスト、15 ボロン、16 リン、17 nピラー層用開口 部、18 pピラー層用開口部、19 n 層 (第6の半導体層)、20 p 層 (第6 の半導体層)、2.1 n ピラー層(第7の半導体層)、2.2 p ピラー層(第8の半 導体層)、23 n ピラー層用開口部、24 p ピラー層用開口部、30 基本単位

## 【図1】

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層) 3:nビラー層(第2の半導体層) 4:pビラー層(第3の半導体層) 5:pベース層(第4の半導体層) 6:nソース層(第5の半導体層) 7:Si酸化膜(ゲート絶縁膜) 8:ゲート電極(第1の制御電極) 9:ソース電極(第2の主電極) 10:フィールドストップ電極 11:フィールドストップ層 12:高抵抗層(第6の半導体層) 13:フィールド絶縁膜

## 【図2】

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層)

3:nビラー暦(第2の半導体層) 4:pビラー暦(第3の半導体層) 9:ソース電極(第2の主電極) 11:フィールドストップ圏 12:高抵抗圏(第6の半導体層)

14:レジスト 15:ボロン 16:リン

【図6】

【図7】

5:pベース層(第4の半導体層) 17:nピラー層用開口部 18:pピラー層用開口部 30: 基本単位

5:pベース層(第4の半導体層) 17:nビラー層用開口部 18:pビラー層用開口部 30: 基本単位

【図8】 【図10】

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層) 11:フィールドストップ層 12:高抵抗層(第6の半導体層) 13:フィールド絶縁膜

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層) 3:nビラー暦(第2の半導体暦) 4:pビラー暦(第3の半導体暦) 5:pベース暦(第4の半導体暦) 6:nソース暦(第5の半導体暦) 7:Si酸化膜(ゲート絶縁膜) 3:nビラー層(第2の半導体層) 4:pビラー層(第3の半導体層) 5:pベース層(第4の半導体層) 6:nソース層(第5の半導体層) 7:Si酸化機(ゲート絶縁膜) 8:ゲート電優(第1の制御電極) 9:ソース電極(第2の主電極) 10:フィールドストップ電極

【図11】

【図12】

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層) 3:nビラー層(第2の半導体層) 4:pビラー層(第3の半導体層)

5:pベース層(第4の半導体層) 6:nソース層(第5の半導体層) 7:Si酸化膜(ゲート絶縁膜) 8:ゲート電極(第10制御電極) 9:ソース電極(第2の主電砲) 10:フィールドストップ電極 11:フィールドストップ層 12:高抵抗暦(第6の半導体層) 13:フィールド絶縁襲 19: n<sup>-</sup>層(第6の半導体層)

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層) 3:nビラー層(第2の半導体層) 4:pビラー層(第3の半導体層)

5:pベース層(第4の半導体層) 6:nソース層(第5の半導体層) 7:Si酸化膜(ゲート絶縁膜) 8:ゲート電極(第1の制御電種) 9:ソース電極 (第2の主電極) 10:フィールドストップ電極 11:フィールドストップ層 13:フィールド絶縁膜 19:n<sup>-</sup>層(第6の半導体層) 20:p-層(第6の半導体層)

【図14】

## 【図13】

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層)

3:nビラー暦(第2の半導体階) 4:pビラー暦(第3の半導体階) 5:pベース暦(第4の半導体階) 6:nソース暦(第5の半導体階) 7:Si酸化類(ゲート絶縁段) 8:ゲート電極(第1の制御電極) 9:ソース電極(第2の主電極) 10:フィールドストップ電極 11:フィールドストップ層 13:フィールド絶縁膜 21:n-ピラー層(第7の半導体層) 22:p-ピラー層(第8の半導体層)

5:pベース層(第4の半導体層) 17:nピラー層用開口部 18:pピラー層用開口部 23:n-ピラー層用開口部 24:p-ピラー層用開口部

## 【図15】

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層) 3:nビラー層(第2の半導体層) 4:pビラー層(第3の半導体層) 5:pベース層(第4の半導体層) 6:nソース層(第5の半導体層) 7:Si酸化膜(ゲート絶縁膜) 8:グート電極(第10制御電極) 9:ソース電極 (第2の主電極) 10:フィールドストップ電極 11:フィールドストップ層 13:フィールド総縁膜 21:n-ビラー層(第7の半導体層) 22:p-ピラー層(第8の半導体層)

## 【図16】

5:pベース層(第4の半導体層) 17:nビラー層用開口部 18:pビラー層用開口部 23:n-ピラー層用開口部 24:p-ピラー層用開口部

## 【図17】

## 【図18】

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層) 3:nビラー層(第2の半導体層) 4:pビラー層(第3の半導体層) 5:pベース層(第4の半導体層) 6:nソース層(第5の半導体層) 7:Si酸化膜(ゲート総緩膜) 8:ゲート電極(第1の制御電極) 9:ソース電極(第2の主電極) 10:フィールドストッフ電極11:フィールドストップ圏 13:フィールド発縁膜 21:n-ビラー圏(第7の半導体圏) 22:p-ビラー圏(第8の半導体圏)

5: pベース層(第4の半導体層) 17:nピラー層用限口部 18:pピラー層用限口部 23:n-ピラー層用閉口部 24:p-ピラー層用用口部

## 【図19】

## 【図20】

3:nビラー層(第2の半導体層) 4:pビラー層(第3の半導体層) 7:Si酸化膜(ゲート総縁膜) 5:pベース層(第4の半導体層) 6:nソース層(第5の半導体層) 7:Si酸化膜(ゲート総縁膜) 8:ゲート電極(第10制調電車) 9:ソース電極(第2の主電極) 10:フィールドストップ電極 11:フィールドストップ電 13:フィールド8縁膜 21:n-ビラー層(第7の半導体層) 22:p-ビラー層(第8の半導体層)

1:ドレイン電極(第1の主電極) 2:n+ドレイン層(第1の半導体層)

5:pベース暦(第4の半導体暦) 17:nビラー暦用開口部 18:pビラー暦用開口部 23:n-ビラー暦用開口部 24:p-ビラー暦用開口部

## 【図21】

5:pベース暦(第4の半導体層) 17:nビラー暦用閥口部 18:pビラー暦用閥口部 23:n-ビラー暦用開口部 24:p-ビラー暦用閥口部

## 【図22】

5:pベース層(第4の半導体層) 17:nビラー層用開口部 18:pビラー層用開口部 23:n-ビラー層用開口部 24:p-ビラー層用開口部

## 【図23】

5:pベース層(第4の半導体層) 17:nビラー層用開口部 18:pビラー層用開口部 23:n=ビラー層用開口部 24:p=ビラー層用開口部

## 【図24】

5:pベース層(第4の半導体層) 17:nビラー層用閘口部 18:pビラー層用閘口部 23:n-ビラー層用閘口部 24:p-ビラー層用閘口部

【図25】

【図26】

5:pベース層(第4の半導体層) 17:nビラー層用閘口部 18:pビラー層用閘口部 23:n-ビラー層用閘口部 24:p-ビラー層用閘口部

5:pベース層(第4の半導体層) 17:nビラー層用欄口部 18:pビラー層用欄口部 23:n-ビラー層用開口部 24:p-ビラー層用開口部

【図3】

5:pベース層(第4の半導体層) 17:nピラー層用開口部 18:pピラー層用開口部 30:基本単位

【図4】

5:pベース層(第4の半導体層) 17:nピラー層用開口部 18:pピラー層用開口部 30:基本単位

【図5】

5:pベース層(第4の半導体層) 17:nピラー層用開口部 18:pピラー層用開口部 30: 基本単位

【図9】

5:pベース層(第4の半導体層) 17:nピラー層用開口部 18:pピラー層用開口部 30:基本単位

## フロントページの続き

(72)発明者 高下 正勝

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 角 保人

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 泉沢 優

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 大田 浩史

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

#### 審査官 瀧内 健夫

(56)参考文献 特開2001-168327(JP,A)

特開2001-015752(JP,A)

特開2000-133801(JP,A)

特開2000-277726(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 29/78

H01L 21/336

H01L 29/06

H01L 29/861

H01L 21/329