## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

*G11C 7/06* (2006.01) *G11C 11/4091* (2006.01)

(21) 출원번호 **10-2013-0091682**

(22) 출원일자 **2013년08월01일** 심사청구일자 **2018년06월18일**

(65) 공개번호 **10-2015-0015809**

(43) 공개일자 **2015년02월11일**

(56) 선행기술조사문헌 US06584026 B2 US20060092738 A1 (45) 공고일자 2020년01월29일

(11) 등록번호 10-2070977

(24) 등록일자 2020년01월21일

(73) 특허권자

### 삼성전자주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

### 서영훈

경기 화성시 동탄반석로 264, 102동 1202호 (석우 동, 예당마을대우푸르지오아파트)

(74) 대리인

특허법인 고려

전체 청구항 수 : 총 13 항

심사관 : 송상용

### (54) 발명의 명칭 감지 증폭기 및 그것을 포함하는 메모리 장치

#### (57) 요 약

본 발명에 따른 감지 증폭기는 비트 라인 및 상보 비트 라인과 연결되고, 제 1 및 제 2 제어 신호에 응답하여 비트 라인의 전압 변화를 감지하고, 감지된 전압 변화를 기반으로 센싱 비트 라인 및 상보 센싱 비트 라인의 전압을 조절하는 감지 증폭부; 격리 신호에 응답하여 비트 라인과 센싱 비트 라인 사이를 스위칭하는 제 1 격리 스위치; 격리 신호에 응답하여 상보 비트 라인과 상보 센싱 비트 라인 사이를 스위칭 제 2 격리 스위치; 오프셋 제거 신호에 응답하여 방보 비트 라인과 상보 센싱 비트 라인 사이를 스위칭하는 제 1 오프셋 제거 스위치; 및 오프셋 제거 신호에 응답하여 상보 비트 라인과 센싱 비트 라인 사이를 스위칭하는 제 2 오프셋 제거 스위치를 포함한다.

#### 대 표 도

## 명 세 서

### 청구범위

### 청구항 1

센싱 비트 라인에 응답하여, 상보 센싱 비트 라인과 제1 제어 신호 라인을 연결하도록 구성된 제1 pMOS 트랜지스터;

상기 상보 센싱 비트 라인에 응답하여, 상기 센싱 비트 라인과 상기 제1 제어 신호 라인을 연결하도록 구성된 제2 pMOS 트랜지스터;

비트 라인에 응답하여, 상기 상보 센싱 비트 라인과 제2 제어 신호 라인을 연결하도록 구성된 제1 nMOS 트랜지스터;

상보 비트 라인에 응답하여 상기 센싱 비트 라인과 상기 제2 제어 신호 라인을 연결하도록 구성된 제2 nMOS 트랜지스터;

격리 신호에 응답하여, 상기 비트 라인과 상기 센싱 비트 라인을 연결하도록 구성된 제1 격리 스위치;

상기 격리 신호에 응답하여, 상기 상보 비트 라인을 상기 상보 센싱 비트 라인과 연결하도록 구성된 제2 격리 스위치;

오프셋 제거 신호에 응답하여, 상기 비트 라인과 상기 상보 센싱 비트 라인을 연결하도록 구성된 제1 오프셋 제 거 스위치; 및

상기 오프셋 제거 신호에 응답하여 상기 상보 비트 라인과 상기 센싱 비트 라인을 연결하도록 구성된 제2 오프 셋 제거 스위치를 포함하는 감지 증폭기.

### 청구항 2

제 1 항에 있어서,

프리 차지 동작 동안, 상기 제1 및 제2 격리 스위치들은 상기 격리 신호에 따라 턴-온되고, 상기 제1 및 제2 오 프셋 제거 스위치들은 상기 오프셋 제거 신호에 따라 턴-온되어, 상기 비트 라인, 상기 상보 비트 라인, 상기 센싱 비트 라인, 및 상기 상보 센싱 비트 라인을 프리 차지 전압으로 충전하는 감지 증폭기.

#### 청구항 3

제 1 항에 있어서,

오프셋 제거 동작 동안, 상기 제1 및 제2 격리 스위치들은 상기 격리 신호에 따라 턴-오프되고, 상기 제1 및 제2 오프셋 제거 스위치들은 상기 오프셋 제거 신호에 따라 턴-온되어, 상기 제1 및 제2 pMOS 트랜지스터들 및 상기 제1 및 제2 nMOS 트랜지스터들로 기인한 오프셋만큼 상기 비트라인을 충전 또는 방전시키는 감지 증폭기.

#### 청구항 4

제 3 항에 있어서,

상기 오프셋 제거 동작 동안, 상기 제1 제어 신호는 입력 전압이고, 상기 제2 제어 신호는 접지 전압인 감지 증폭기.

#### 청구항 5

제 1 항에 있어서,

전하 공유 동작 동안, 상기 제1 및 제2 격리 스위치들은 상기 격리 신호에 따라 턴-오프되고, 상기 제1 및 제2 오프셋 제거 스위치들은 상기 오프셋 제거 신호에 따라 턴-오프되어, 상기 비트 라인의 전하 및 상기 상기 비트 라인과 연결된 메모리 셀의 전하의 전하 공유를 기반으로 소정의 레벨만큼 상기 비트 라인을 충전 또는 방전시키는 감지 증폭기.

#### 청구항 6

제 5 항에 있어서,

상기 전하 공유 동작이 수행되는 동안, 등화 신호에 응답하여, 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인을 프리차지 전압으로 충전하도록 구성된 등화 회로를 더 포함하는 감지 증폭기.

### 청구항 7

제 6 항에 있어서,

상기 등화 회로는 상기 등화 신호에 응답하여 동작하는 제1 내지 제3 등화 스위치들을 포함하고,

상기 제1 및 제2 등화 스위치들은 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인 사이에 직렬로 연결되고,

상기 제3 등화 스위치는 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인 사이에 직렬로 연결되는 감지 증폭기.

#### 청구항 8

제 1 항에 있어서,

프리-센싱 동작 동안, 상기 제1 및 제2 격리 스위치들은 상기 격리 신호에 응답하여 턴-오프되고, 상기 제1 및 제2 오프셋 제거 스위치들은 상기 오프셋 제거 신호에 응답하여 턴-오프되고, 상기 제1 제어 신호는 입력 전압이고, 상기 제2 제어 신호는 접지 전압이 됨으로써, 상기 비트 라인의 전압 변화에 따라 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인을 상기 입력 전압 또는 상기 접지 전압으로 충전 또는 방전되는 감지 증폭기.

#### 청구항 9

제 1 항에 있어서,

재 저장 동작 동안, 상기 제1 및 제2 격리 스위치들은 상기 격리 신호에 따라 턴-오프되고, 상기 제1 및 제2 오프셋 제거 스위치들은 상기 오프셋 제거 신호에 따라 턴-오프됨으로써, 상기 센싱 비트 라인의 전압 레벨을 기반으로 메모리 셀에 데이터를 저장하는 감지 증폭기.

### 청구항 10

센싱 비트 라인에 응답하여 상보 센싱 비트 라인과 제1 제어 신호 라인을 연결하도록 구성된 제1 pMOS 트랜지스터;

상기 상보 센싱 비트 라인에 응답하여 상기 센싱 비트 라인 및 상기 제1 제어 신호 라인을 연결하도록 구성된 제2 pMOS 트랜지스터;

비트 라인에 응답하여 상기 상보 센싱 비트 라인과 제2 제어 신호 라인을 연결하도록 구성된 제1 nMOS 트랜지스터;

상보 비트 라인에 응답하여 상기 센싱 비트 라인 및 제3 제어 신호 라인을 연결하도록 구성된 제2 nMOS 트랜지스터;

격리 신호에 응답하여 상기 비트 라인 및 상기 센싱 비트 라인을 연결하도록 구성된 제1 격리 스위치;

상기 격리 신호에 응답하여 상기 상보 비트 라인 및 상기 상보 센싱 비트 라인을 연결하도록 구성된 제2 격리 스위치;

오프셋 제거 신호에 응답하여 상기 비트 라인 및 상기 상보 센싱 비트 라인을 연결하도록 구성된 제1 오프셋 제 거 스위치; 및

상기 오프셋 제거 신호에 응답하여 상기 상보 비트 라인 및 상기 센싱 비트 라인을 연결하도록 구성된 제2 오프 셋 제거 스위치를 포함하고,

상기 제2 제어 신호는 상기 제3 제어 신호 및 연결 저항 잡음을 포함하는 감지 증폭기.

### 청구항 11

메모리 블록들을 포함하는 메모리 셀 어레이;

상기 메모리 블록들과 연결되고, 오픈 비트 라인 구조를 갖도록 구성된 복수의 감지 증폭기들; 및

상기 메모리 셀 어레이의 에지 영역에 위치하고, 상기 복수의 감지 증폭기들 중 상기 에지 영역에 인접한 감지 증폭기들과 연결되도록 구성된 기준 전압부를 포함하고,

상기 복수의 감지 증폭기들 각각은:

비트 라인 및 상보 비트 라인과 연결되고, 제1 및 제2 제어 신호들에 응답하여 상기 비트 라인의 전압 변화를 감지하고, 상기 감지된 전압 변화를 기반으로 센싱 비트 라인 및 상보 센싱 비트 라인의 전압들을 제어하도록 구성된 감지 증폭부;

격리 신호에 응답하여, 상기 비트 라인과 상기 센싱 비트 라인을 연결하도록 구성된 제1 격리 스위치;

상기 격리 신호에 응답하여, 상기 상보 비트 라인과 상기 상보 센싱 비트 라인을 연결하도록 구성된 제2 격리스위치;

오프셋 제거 신호에 응답하여, 상기 비트 라인과 상기 상보 센싱 비트 라인을 연결하도록 구성된 제1 오프셋 제 거 스위치; 및

상기 오프셋 제거 신호에 응답하여, 상기 상보 비트 라인과 상기 센싱 비트 라인을 연결하도록 구성된 제2 오프 셋 제거 스위치를 포함하고,

상기 기준 전압부는 복수의 캐패시터들을 포함하고,

상기 에지 영역에 인접한 상기 감지 증폭기들은 상기 복수의 캐패시터들을 프리차지 전압으로 충전하도록 구성 된 메모리 장치.

#### 청구항 12

제 11 항에 있어서,

상기 오프셋 제거 동작 동안, 상기 각각의 비트 라인은 상기 감지 증폭기의 오프셋만큼 충전 또는 방전되는 메모리 장치.

### 청구항 13

제 11 항에 있어서,

프리 센싱 동작 동안, 상기 제1 제어 신호는 입력 전압으로 천이되고, 상기 제2 제어 신호는 접지 전압으로 천이되고, 상기 감지 증폭기들은, 상기 격리 신호에 따라, 각각의 비트 라인 및 각각의 센싱 비트 라인 사이의 연결 및 각각의 상보 비트 라인 및 각각의 상보 센싱 비트 라인의 연결을 차단하고, 상기 오프셋 제거 신호에 따라, 상기 각각의 비트 라인 및 상기 각각의 상보 센싱 비트 라인 사이의 연결 및 상기 각각의 상보 비트 라인 및 상기 각각의 선보 비트 라인 및 상기 각각의 선칭 비트 라인 사이의 연결을 차단하도록 구성되고,

상기 프리 센싱 동작 동안, 상기 각각의 센싱 비트 라인 및 상기 각각의 상보 센싱 비트 라인의 전압 레벨들은 상기 각각의 비트 라인의 전압 변화를 기반으로 증폭되거나 또는 감소되는 메모리 장치.

### 발명의 설명

### 기술분야

[0001] 본 발명은 반도체 메모리 장치에 관한 것으로 더욱 상세하게는 반도체 메모리의 데이터를 감지하고 증폭하는 감 지 증폭기 및 그것을 포함하는 메모리 장치에 관한 것이다.

### 배경기술

- [0002] 반도체 메모리 장치(semiconductor memory device)는 실리콘(Si, silicon), 게르마늄(Ge, Germanium), 비화 갈륨(GaAs, gallium arsenide), 인화 인듐(InP, indium phospide) 등과 같은 반도체를 이용하여 구현되는 기억 장치이다. 반도체 메모리 장치는 크게 휘발성 메모리 장치(Volatile Memory Device) 및 불휘발성 메모리 장치 (Nonvolatile Memory Device)로 구분된다.

- [0003] 휘발성 메모리 장치는 전원 공급이 차단되면 저장하고 있던 데이터가 소멸되는 메모리 장치이다. 휘발성 메모리 장치에는 SRAM (Static RAM), DRAM (Dynamic RAM), SDRAM (Synchronous DRAM) 등이 있다. 불휘발성 메모리 장치는 전원 공급이 차단되어도 저장하고 있던 데이터를 유지하는 메모리 장치이다. 불휘발성 메모리 장치에는 ROM (Read Only Memory), PROM (Programmable ROM), EPROM (Electrically Programmable ROM), EEPROM (Electrically Erasable and Programmable ROM), NAND 플래시 메모리, NOR 플래시 메모리, PRAM (Phase-change RAM), MRAM (Magnetic RAM), RRAM (Resistive RAM), FRAM (Ferroelectric RAM) 등이 있다.

- [0004] DRAM에서, 메모리 셀 어레이는 비트 라인(BL) 및 상보 비트 라인(BLB)과 연결된다. 읽기 동작(또는 리프레쉬 동작)이 수행되는 경우, 감지 증폭기는 비트 라인(BL)과 상보 비트 라인(BLB)의 전압 차를 감지하여 증폭한다. 감지 증폭기는 다양한 반도체 소자들을 포함한다. 감지 증폭기에 포함된 반도체 소자들은 공정 변이, 온도 등 (PVT, Precess Variation, Temperature)으로 인하여 소자 간 특성(예를 들어, 문턱 전압)이 서로 다를 수 있다. 이로 인하여, 감지 증폭기의 오프셋 노이즈가 발생한다. 또한, 비트 라인들 간 커플링으로 인한 커플링 노이즈도 발생한다. 상술된 오프셋 노이즈 및 커플링 노이즈로 인하여 감지 증폭기의 유효 센싱 마진(effective sensing margine)이 감소되고, 이로 인하여 DRAM 장치의 성능이 저하될 수 있다.

### 발명의 내용

### 해결하려는 과제

[0005] 본 발명의 목적은 감지 증폭기의 오프셋 제거 동작(offset cancelling operation) 및 프리-센싱 동작(presensing operation)을 기반으로 유효 센싱 마진을 증가시킬 수 있는 감지 증폭기 및 그것을 포함하는 메모리 장치을 제공하는데 있다.

### 과제의 해결 수단

- [0006] 본 발명의 실시 예에 따른 감지 증폭기는 비트 라인 및 상보 비트 라인과 연결되고, 제 1 및 제 2 제어 신호에 응답하여 상기 비트 라인의 전압 변화를 감지하고, 감지된 전압 변화를 기반으로 센싱 비트 라인 및 상보 센싱 비트 라인의 전압을 조절하는 감지 증폭부; 격리 신호에 응답하여 상기 비트 라인과 상기 센싱 비트 라인 사이를 스위칭하는 제 1 격리 스위치; 상기 격리 신호에 응답하여 상기 상보 비트 라인과 상기 상보 센싱 비트 라인 사이를 스위칭 제 2 격리 스위치; 오프셋 제거 신호에 응답하여 상기 비트 라인과 상기 상보 센싱 비트 라인 사이를 스위칭하는 제 1 오프셋 제거 스위치; 및 상기 오프셋 제거 신호에 응답하여 상기 상보 비트 라인과 상기 센싱 비트 라인 사이를 스위칭하는 제 2 오프셋 제거 스위치를 포함한다.

- [0007] 실시 예로서, 상기 감지 증폭부는 제 1 및 제 2 pMoS 트랜지스터들; 및 제 1 및 제 2 nMoS 트랜지스터들을 포함하고, 상기 제 1 pMoS 트랜지스터의 일단은 상기 상보 센싱 비트 라인과 연결되고, 상기 제 1 pMoS 트랜지스터의 타단은 상기 제 1 제어 신호와 연결되고, 상기 제 2 pMoS 트랜지스터의 일단은 상기 제 1 제어 신호와 연결되고, 상기 제 2 pMoS 트랜지스터의 일단은 상기 제 1 pMoS 트랜지스터의 제이트는 상기 센싱 비트 라인과 연결되고, 상기 제 1 pMoS 트랜지스터의 게이트는 상기 센싱 비트 라인과 연결되고, 상기 제 1 nMoS 트랜지스터의 일단은 상기 상보 센싱 비트 라인과 연결되고, 상기 제 1 nMoS 트랜지스터의 일단은 상기 상보 센싱 비트 라인과 연결되고, 상기 제 1 nMoS 트랜지스터의 일단은 상기 제 2 nMoS 트랜지스터의 일단의 일단은 상기 제 2 제어 신호와 연결되고, 상기 제 2 nMoS 트랜지스터의 일단의 일단은 상기 제 2 제어 신호와 연결되고, 상기 제 2 nMoS 트랜지스터의 게이트는 상기 제 1 nMoS 트랜지스터의 게이트는 상기 생보 비트 라인과 연결된다.

- [0008] 실시 예로서, 상기 격리 신호의 제어에 따라 상기 제 1 및 제 2 격리 스위치들이 턴-오프되고, 상기 오프셋 제거 신호에 따라 상기 제 1 및 제 2 오프셋 제거 스위치들이 턴-온되어, 오프셋 제거 동작을 수행하되, 상기 오프셋 제거 동작은 상기 비트 라인이 오프셋만큼 충전 또는 방전되는 동작을 가리키고, 상기 오프셋은 상기 제 1 및 제 2 pMOS 트랜지스터들 및 제 1 및 제 2 nMOS 트랜지스터들 간 문턱 전압 차이이다.

- [0009] 실시 예로서, 상기 오프셋 제거 동작 동안 상기 제 1 제어 신호는 입력 전압이고, 제 2 제어 신호는 접지 전압이다.

- [0010] 실시 예로서, 상기 격리 신호의 제어에 따라 상기 제 1 및 제 2 격리 스위치들이 턴-오프되고, 상기 오프셋 제거 신호에 따라 상기 제 1 및 제 2 오프셋 제거 스위치들이 턴-오프되고, 상기 비트 라인의 전하 및 상기 비트 라인과 연결된 메모리 셀의 전하의 전하 공유를 기반으로 상기 비트 라인이 소정의 레벨만큼 충전 또는 방전된다.

- [0011] 실시 예로서, 상기 감지 증폭부는 상기 전하 공유가 수행되는 동안 등화 신호에 응답하여 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인을 프리 차지 전압으로 충전 및 등화시키는 등화 회로를 더 포함한다.

- [0012] 실시 예로서, 상기 등화 회로는 상기 등화 신호에 응답하여 동작하는 제 1 내지 제 3 등화 스위치들을 포함하고, 상기 제 1 및 제 2 등화 스위치들은 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인 사이에 직렬 연결되고, 상기 제 3 등화 스위치는 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인 사이에 연결된다.

- [0013] 실시 예로서, 상기 격리 신호의 제어에 따라 상기 제 1 및 제 2 격리 스위치들은 턴-오프되고, 상기 오프셋 제 거 신호의 제어에 따라 상기 제 1 및 제 2 오프셋 제거 스위치들은 턴-오프되고, 상기 제 1 제어 신호는 입력 전압이고, 상기 제 2 제어 신호는 접지 전압으로 되어, 프리 센싱 동작을 수행하고, 상기 프리 센싱 동작은 상기 비트 라인의 전압 변화량에 따라 상기 센싱 비트 라인 및 상기 상보 센싱 비트 라인이 각각 입력 전압 또는 접지 전압으로 충전 또는 방전된다.

- [0014] 실시 예로서, 상기 프리 센싱 동작 이 후, 상기 격리 신호의 제어에 따라 상기 제 1 및 제 2 격리 스위치들이 턴-온되고, 상기 오프셋 제거 신호의 제어에 따라 상기 제 1 및 제 2 오프셋 제거 스위치들이 턴-오프되어, 재 저장 동작을 수행하고, 상기 재저장 동작은 상기 프리 센싱된 센싱 비트 라인의 전압 레벨을 기반으로 메모리 셀에 데이터를 저장하는 동작을 가리킨다.

- [0015] 본 발명의 다른 실시 예에 따른 메모리 장치는 복수의 메모리 블록들을 포함하는 메모리 셀 어레이; 상기 복수의 메모리 블록들과 연결되고, 오픈 비트 라인 구조를 갖는 복수의 감지 증폭기들; 및 상기 메모리 셀 어레이의 에지영역에 배치되고, 상기 복수의 감지 증폭기들 중 상기 에지 영역에 인접한 감지 증폭기들과 연결된 기준전 압부를 포함하고, 상기 복수의 감지 증폭기들 각각은 비트 라인 및 상보 비트 라인과 연결되고, 제 1 및 제 2 제어 신호에 응답하여 상기 비트 라인의 전압 변화를 감지하고, 감지된 전압 변화를 기반으로 센싱 비트 라인 및 상보 센싱 비트 라인과 상기 센싱 비트 라인 사이를 스위칭하는 제 1 격리 스위치; 상기 격리 신호에 응답하여 상기 비트 라인과 상기 센싱 비트 라인 사이를 스위칭 제 2 격리 스위치; 오프셋 제거 신호에 응답하여 상기 비트 라인과 상기 성보 센싱 비트 라인 사이를 스위칭하는 제 1 오프셋 제거 스위치; 및 상기 오프셋 제거 신호에 응답하여 상기 상보 센싱 비트 라인 사이를 스위칭하는 제 1 오프셋 제거 스위치; 및 상기 오프셋 제거 신호에 응답하여 상기 상보 비트 라인과 상기 센싱 비트 라인 사이를 스위칭하는 제 2 오프셋 제거 스위치를 포함한다.

### 발명의 효과

- [0016] 본 발명에 따른 감지 증폭기는 오프셋 제거 동작을 통해 감지 증폭기의 오프셋을 보상하고, 프리 센싱 동작을 통해 비트 라인 간 커플링 영향을 감소시킨다. 따라서, 감지 증폭기는 유효 센싱 마진을 향상시킬 수 있으므로, 향상된 성능을 갖는 감지 증폭기 및 그것을 포함하는 메모리 장치가 제공된다.

- [0017] 또한, 본 발명에 따른 감지 증폭기가 오픈 비트 라인 구조의 메모리 장치에 적용될 경우, 더미 어레이 대신 캐 패시터를 사용하여 센싱 동작을 수행할 수 있다. 따라서, 오픈 비트 라인 구조를 갖는 메모리 장치의 더미 어레 이가 제거되므로, 감소된 비용 및 면적을 갖는 메모리 장치가 제공된다.

#### 도면의 간단한 설명

[0018] 도 1은 본 발명의 실시 예에 따른 메모리 장치를 보여주는 블록도이다.

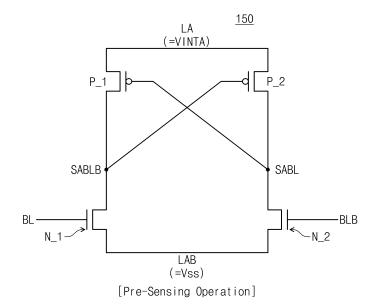

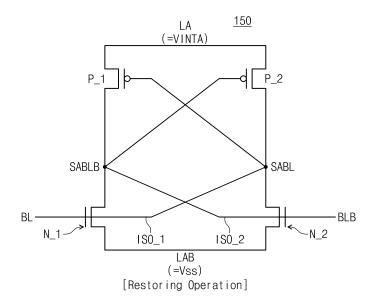

도 2 및 도 3은 는 도 1에 도시된 감지 증폭기의 감지 동작을 설명하기 위한 도면들이다.

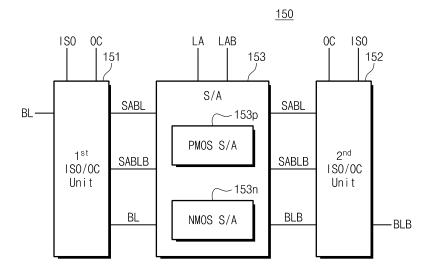

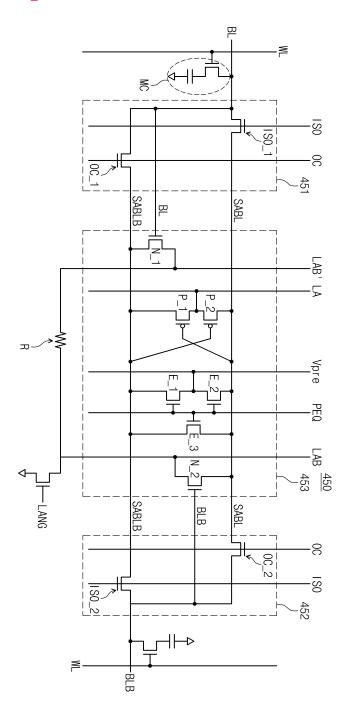

도 4는 도 1에 도시된 감지 증폭기를 상세하게 보여주는 블록도이다.

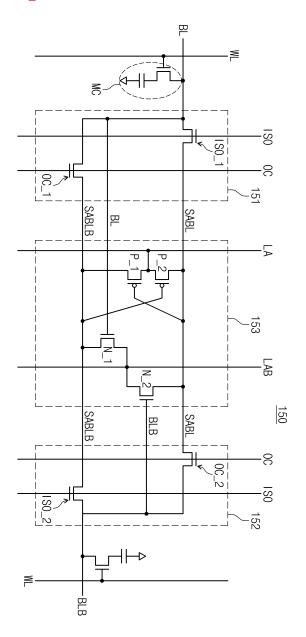

도 5는 도 4에 도시된 감지 증폭기를 더욱 상세하게 보여주는 회로도이다.

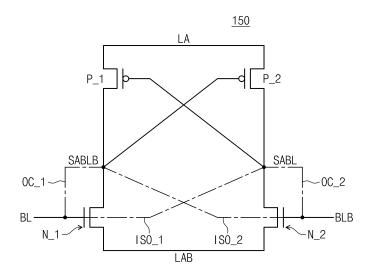

도 6은 도 5에 도시된 감지 증폭기의 등가회로를 보여주는 회로도이다.

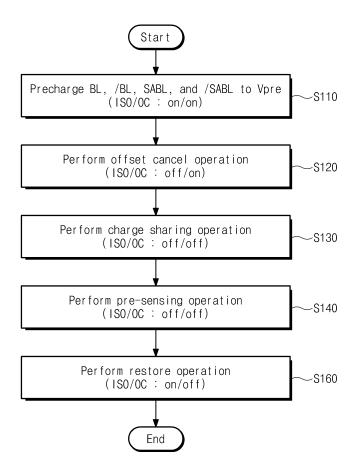

- 도 7은 도 6에 도시된 감지 증폭기의 동작을 보여주는 순서도이다.

- 도 8 내지 도 13은 도 7에 도시된 감지 증폭기의 동작을 설명하기 위한 회로도들이다.

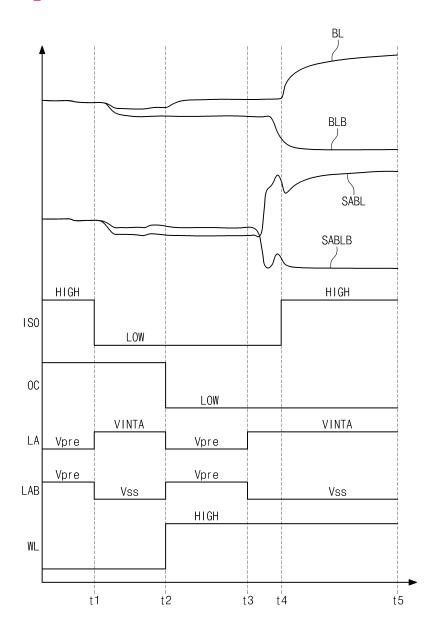

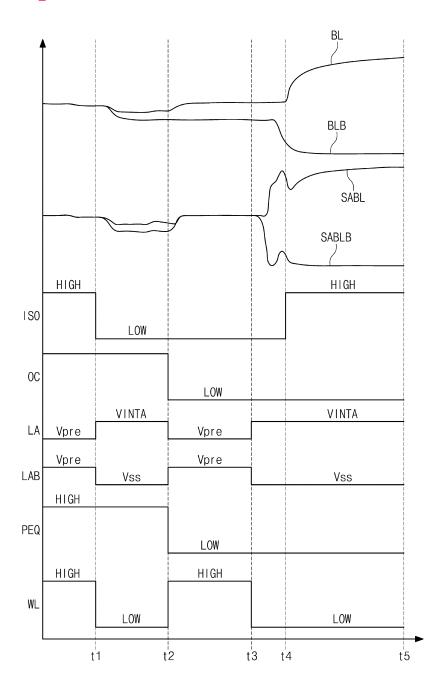

- 도 14는 도 7에 도시된 감지 증폭기의 동작을 설명하기 위한 타이밍도이다.

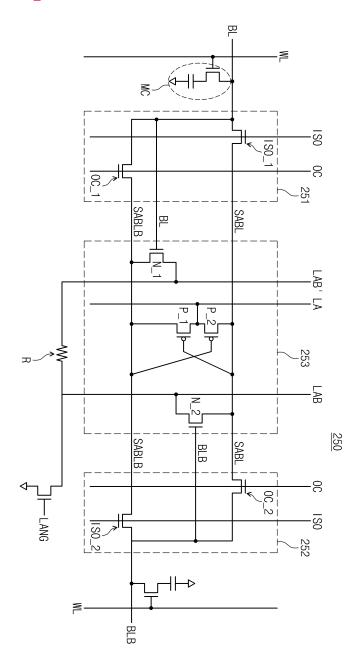

- 도 15는 본 발명의 다른 실시 예에 따른 감지 증폭기를 보여주는 회로도이다.

- 도 16은 도 15에 도시된 감지 증폭기의 등가 회로를 보여주는 회로도이다.

- 도 17은 본 발명의 또 다른 실시 예에 따른 감지 증폭기를 보여주는 블록도이다.

- 도 18은 도 17에 도시된 감지 증폭기를 상세하게 보여주는 회로도이다.

- 도 19는 도 18에 도시된 감지 증폭기의 등가 회로를 보여주는 회로도이다.

- 도 20은 도 19에 도시된 감지 증폭기의 동작을 보여주는 타이밍도이다.

- 도 21은 본 발명의 또 다른 실시 예에 따른 감지 증폭기를 보여주는 회로도이다.

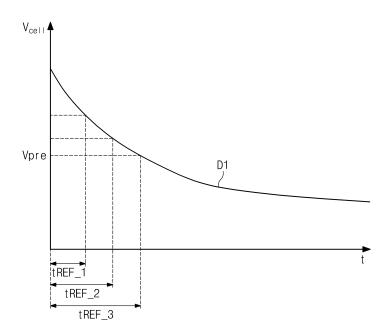

- 도 22는 본 발명에 따른 감지 증폭기의 효과를 설명하기 위한 그래프이다.

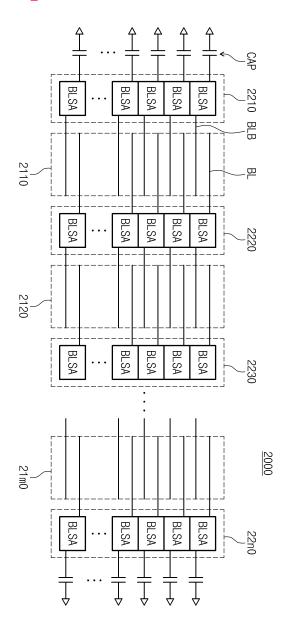

- 도 23은 본 발명에 따른 감지 증폭기 적용된 메모리 장치를 예시적으로 보여주는 블록도이다.

- 도 24는 본 발명에 따른 감지 증폭기 적용된 메모리 장치를 예시적으로 보여주는 블록도이다.

- 도 25는 본 발명에 따른 메모리 장치가 적용된 메모리 모듈을 예시적으로 보여주는 도면이다.

- 도 26은 본 발명에 따른 메모리 장치가 적용된 메모리 시스템을 예시적으로 보여주는 블록도이다.

- 도 27은 도 26의 메모리 시스템이 적용된 컴퓨팅 시스템을 예시적으로 보여주는 블록도이다.

- 도 28은 본 발명에 따른 메모리 장치가 적용된 사용자 시스템을 예시적으로 보여주는 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0019] 이하에서, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세하게 설명하기 위하여 본 발명의 실시 예들을 첨부된 도면들을 참조하여 설명하기로 한다.

- [0020] 본 발명의 실시 예에 따른 감지 증폭기는 프리-차지(pre-charge), 오프셋 제거(offset cancellation), 전하 공유(charge share), 프리-센싱(pre-sensing), 및 재저장(restore) 동작를 기반으로 동작한다. 이 때, 감지 증폭기는 오프셋 제거 동작을 통해 센스 앰프에 포함된 소자들의 오프셋을 보상할 수 있다. 또한, 센스 앰프는 프리센싱 동작을 통해 비트 라인들 간 커플링 영향을 줄일 수 있다. 이에 따라, 감지 증폭기는 유효 센싱 마진을 증가시킬 수 있다. 따라서, 향상된 성능을 갖는 센스 앰프 및 그것이 포함된 메모리 장치가 제공된다.

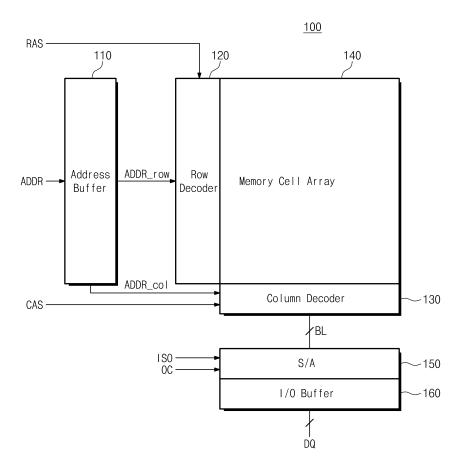

- [0021] 도 1은 본 발명의 실시 예에 따른 메모리 장치를 보여주는 블록도이다. 도 1을 참조하면, 메모리 장치(100)는 반도체 소자를 기반으로 하는 저장 장치일 수 있다. 예시적으로, 메모리 장치(100)는 DRAM(Dynamic Random Access Memory), SDRAM(Synchronous DRAM), SRAM(Static RAM), DDR SDRAM(Double Date Rate SDRAM), DDR2 SDRAM, DDR3 SDRAM, PRAM(Phase-change RAM), MRAM(Magnetic RAM), RRAM(Resistive RAM) 등과 같은 랜덤 액세스 메모리(RAM, Random Access Memory) 장치로 제공될 수 있다. 메모리 장치(100)는 외부 장치(예를 들어, 메모리 컨트롤러)로부터 수신된 어드레스(ADDR) 및 제어 신호들(RAS, CAS)에 응답하여, 데이터 라인들(DQ)을 통해 데이터를 출력할 수 있다. 메모리 장치(100)는 어드레스 버퍼(110), 로우 디코더(120), 컬럼 디코더(130), 메모리 셀 어레이(140), 감지 증폭기(150), 및 입출력 버퍼(160)를 포함한다.

- [0022] 어드레스 버퍼(110)는 외부 장치(예를 들어, 메모리 컨트롤러)로부터 어드레스(ADDR)를 수신한다. 어드레스 (ADDR)는 메모리 셀 어레이(140)의 행을 가리키는 로우 어드레스(ADDR\_row) 및 메모리 셀 어레이(140)의 열을 가리키는 컬럼 어드레스(ADDR\_col)를 포함한다. 어드레스 버퍼(110)는 로우 어드레스(ADDR\_row)를 로우 디코더 (120)로 전송할 수 있다. 어드레스 버퍼(110)는 컬럼 어드레스(ADDR\_col)를 컬럼 디코더(130)로 전송할 수 있다.

- [0023] 로우 디코더(120)는 메모리 셀 어레이(140)와 연결된 복수의 워드라인들 중 어느 하나를 선택할 수 있다. 예를 들어, 로우 디코더(120)는 어드레스 버퍼(110)로부터 로우 어드레스(ADDR\_row)을 수신할 수 있다. 로우 디코더(120)는 복수의 워드라인들 중 수신된 로우 어드레스(ADDR\_row)에 대응되는 어느 하나의 워드라인을 선택할 수

있다. 로우 디코더(120)는 제어 신호(RAS)에 응답하여, 선택된 워드라인을 활성화시킬 수 있다.

- [0024] 컬럼 디코더(130)는 메모리 셀 어레이(140)와 연결된 복수의 비트 라인들(BL) 중 어느 하나를 선택할 수 있다. 예를 들어, 컬럼 디코더(130)는 어드레스 버퍼(110)로부터 컬럼 어드레스(ADDR\_col)을 수신할 수 있다. 컬럼 디코더(130)는 복수의 비트 라인들(BL) 중 수신된 컬럼 어드레스(ADDR\_col)에 대응되는 어느 하나의 비트 라인을 선택할 수 있다. 컬럼 디코더(130)는 제어 신호(CAS)에 응답하여, 선택된 비트 라인을 활성화할 수 있다.

- [0025] 메모리 셀 어레이(140)는 복수의 메모리 셀들을 포함한다. 복수의 메모리 셀들 각각은 복수의 워드라인들 및 복수의 비트 라인들이 교차하는 지점에 위치할 수 있다. 복수의 메모리 셀들은 복수의 워드라인들 및 복수의 비트 라인들과 연결된다. 복수의 메모리 셀들 각각은 매트릭스 형태로 제공될 수 있다. 복수의 워드라인들은 메모리 셀 어레이(140)의 메모리 셀들의 행들과 연결될 수 있다. 복수의 비트 라인들은 메모리 셀 어레이(140)의 메모리 셀들의 열들과 연결될 수 있다.

- [0026] 감지 증폭기(150)는 메모리 셀 어레이(140)와 연결된 복수의 비트 라인들과 연결된다. 감지 증폭기(150)는 복수의 비트 라인들 중 활성화된 비트 라인의 전압 변화를 감지하고, 이를 증폭하여 출력한다. 입출력 버퍼(160)는 감지 증폭기(150)로부터 증폭된 전압을 기반으로 데이터 라인들(DQ)을 통해 데이터를 외부 장치로 출력할 수 있다.

- [0027] 본 발명의 실시 예에 따른 감지 증폭기(150)는 제어 로직(미도시) 또는 외부 장치(예를 들어, 메모리 컨트롤러)로부터 격리 신호(ISO) 및 오프셋 제거 신호(OC)를 수신할 수 있다. 감지 증폭기(150)는 수신된 격리 신호(ISO) 및 오프셋 제거 신호(OC)에 따라 오프셋 제거 동작 및 프리-센싱 동작을 수행한다. 예시적으로, 오프셋은 감지 증폭기(150)에 포함된 소자들 간 특성(예를 들어, 문턱 전압)의 차이를 가리킨다.

- [0028] 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 감지 증폭기(150)에 포함된 복수의 스위치들을 제어할 수 있다. 예를 들어, 격리 신호(ISO)의 제어에 따라 동작하는 스위치들이 턴-오프이고, 오프셋 제거 신호(OC)에 따라 동작하는 스위치들이 턴-온인 경우, 감지 증폭기(150)는 오프셋 제거 동작을 수행한다. 격리 신호(ISO)의 제어에 따라 동작하는 스위치들 및 오프셋 제어 신호(OC)의 제어에 따라 동작하는 스위치들이 턴-오프인 경우, 감지 증폭기(150)는 프리-센싱 동작을 수행할 수 있다.

- [0029] 감지 증폭기(150)는 오프셋 제거 동작 및 프리-센싱 동작을 통해 감지 증폭기(150)의 오프셋을 제거하고, 비트라인들(BL) 간 커플링을 감소시킬 수 있다. 이에 따라, 비트라인 전압의 센싱 마진이 증가함으로써, 향상된 성능을 갖는 감지 증폭기 및 그것이 포함된 메모리 장치가 제공된다. 감지 증폭기(150)의 구성 및 동작은 이하의도면들을 참조하여 더욱 상세하게 설명된다.

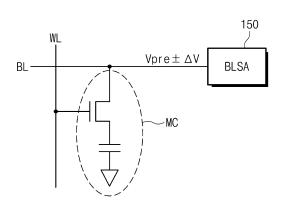

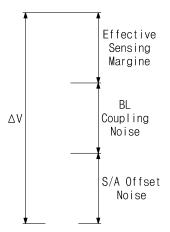

- [0030] 도 2 및 도 3은 도 1에 도시된 감지 증폭기의 비트 라인 전압 감지 동작을 설명하기 위한 도면들이다. 간결한 설명을 위하여, 감지 증폭기(150), 비트 라인(BL), 워드라인(WL), 및 메모리 셀(MC) 이외의 구성은 생략된다. 또한, 이하에서 설명되는 본 발명의 기술적 사상은 메모리 장치(100)의 리프레쉬 동작을 기반으로 설명된다. 그러나, 본 발명의 범위가 이에 한정되는 것은 아니며, 본 발명의 기술적 사상은 메모리 장치(100)의 읽기 동작에도 적용될 수 있다.

- [0031] 도 1 내지 도 3을 참조하면, 메모리 셀(MC)에 포함된 캐패시터의 전하량을 기반으로 메모리 장치(100)는 리프레쉬 동작을 수행할 수 있다. 이 때, 메모리 셀(MC)과 연결된 비트 라인(BL)은 프리차지 전압(Vpre)으로 프리차지된다. 이 후, 워드라인(WL)이 활성화됨에 따라, 프리차지 전압(Vpre)으로 충전된 비트 라인(BL)의 전하 및 메모리 셀(MC)의 캐패시터의 전하 간 전하 공유(charge sharing)가 발생된다. 전하 공유에 의해 비트 라인의 전압(VBL)은 전압 변화량(△V)만큼 감소 또는 증가할 것이다.

- [0032] 감지 증폭기(150)는 전압 변화량(△V)을 감지하고, 이를 증폭할 수 있다. 이 때, 비트 라인 커플링 잡음(BL coupling noise), 감지 증폭기 오프셋 잡음(S/A offset noise) 등으로 인하여, 감지 증폭기(150)의 유효 센싱 마진(effective sensing margine)은 도 3에 도시된 바와 같을 것이다. 즉, 전압 변화량(△V)이 일정 수준 이하 인 경우, 감지 증폭기(150)는 비트 라인(BL)의 전압 변화량(△V)을 감지하지 못할 것이다.

- [0033] 본 발명에 따른 감지 증폭기(150)는 격리 신호(ISO) 및 오프셋 제거 신호(OC)에 응답하여, 오프셋 제거 동작 및 프리-센싱 동작을 수행함으로써, 비트 라인 커플링 잡음(BL coupling noise), 및 감지 증폭기 오프셋 잡음(S/A offset noise)을 감소시킬 수 있다.

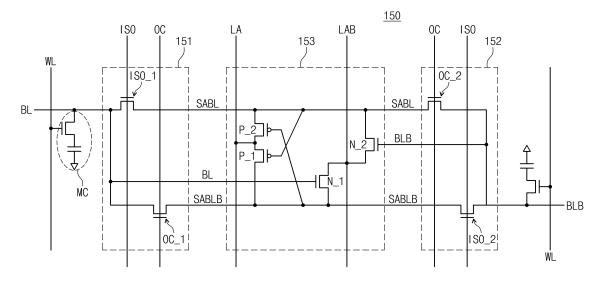

- [0034] 도 4는 본 발명의 실시 예에 따른 감지 증폭기를 보여주는 블록도이다. 간결한 설명을 위하여, 본 발명에 따른 감지 증폭기(150)의 구성 및 동작을 설명하는데 불필요한 구성요소들은 생략된다. 그러나, 본 발명의 범위가 이

에 한정되는 것은 아니며, 본 발명에 따른 프리차징 회로(Precharging circuit), 등화 회로(equalizing circuit) 등과 같은 구성 요소들을 더 포함할 수 있다.

- [0035] 도 4를 참조하면, 감지 증폭기(150)는 제 1 및 제 2 격리/오프셋 제거부들(151, 152; ISO/OC units; isolation/offset cancelation units), 및 감지 증폭부(153)를 포함할 수 있다. 제 1 격리/오프셋 제거부(15 1)는 비트 라인(BL), 센싱 비트 라인(SABL), 및 상보 센싱 비트 라인(SABLB)과 연결된다. 제 2 격리/오프셋 제거부(152)는 상보 비트 라인(BLB), 센싱 비트 라인(SABL), 및 상보 센싱 비트 라인(SABLB)과 연결된다. 제 1 및 제 2 격리/오프셋 제거부(151)는 격리 신호(ISO) 및 오프셋 제거 신호(OC)를 수신하고, 수신된 격리 신호(ISO) 및 오프셋 제거 신호(OC)를 기반으로 동작한다.

- [0036] 예를 들어, 제 1 격리/오프셋 제거부(151)는 격리 신호(ISO)에 응답하여, 비트 라인(BL) 및 센싱 비트 라인 (SABL) 간 연결을 차단할 수 있다. 제 1 격리/오프셋 제거부(151)는 오프셋 제거 신호(OC)에 응답하여, 비트 라인(BL) 및 상보 센싱 비트 라인(SABLB) 간 연결을 차단할 수 있다. 제 2 격리/오프셋 제거부(152)는 격리 신호 (ISO)에 응답하여, 상보 비트 라인(BLB) 및 상보 센싱 비트 라인(SABLB) 간 연결을 차단할 수 있다. 제 2 격리/오프셋 제거부(152)는 오프셋 제거 신호(OC)에 응답하여, 상보 비트 라인(BLB) 및 감지증폭 비트 라인(SABL) 간 연결을 차단할 수 있다.

- [0037] 감지 증폭부(153)는 pMOS 감지 증폭부(153p) 및 nMOS 감지 증폭부(153n)를 포함한다. 감지 증폭부(153)는 제 1 및 제 2 제어 신호들(LA, LAB)에 따라 비트 라인(BL) 및 상보 비트 라인(BLB)의 전압차를 감지하고 증폭할 수 있다. 예시적으로, nMOS 감지 증폭부(153n)는 비트 라인(BL) 및 상보 비트 라인(BLB)과 직접 연결된다. nMOS 감지 증폭부(153n)에 포함된 트랜지스터들의 게이트들은 각각 비트 라인(BL) 및 상보 비트 라인(BLB)과 연결된다.

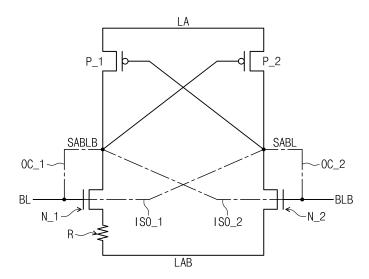

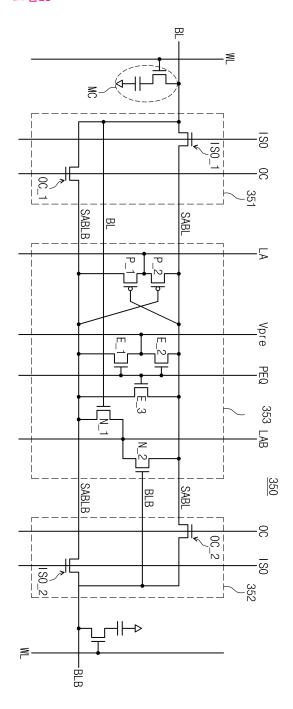

- [0038] 도 5 및 도 6은 도 4에 도시된 감지 증폭기를 상세하게 보여주는 회로도이다. 예시적으로, 도 5에 도시된 감지 증폭기(150)의 등가 회로를 보여주는 회로도이다.

- [0039] 먼저, 도 5를 참조하면, 감지 증폭기(150)는 제 1 및 제 2 격리/오프셋 제거부들(151, 152), 및 감지 증폭부 (153)를 포함한다.

- [0040] 제 1 격리/오프셋 제거부(151)는 제 1 격리 스위치(ISO\_1) 및 제 1 오프셋 제거 스위치(OC\_1)를 포함한다. 제 1 격리 스위치(ISO\_1)의 일단은 비트 라인(BL)과 연결되고, 타단은 센싱 비트 라인(SABL)과 연결된다. 제 1 격리 스위치(ISO\_1)는 격리 신호(ISO)에 따라 동작한다. 제 1 오프셋 제거 스위치(OC\_1)의 일단은 비트 라인(BL)과 연결되고, 타단은 상보 센싱 비트 라인(SABLB)과 연결된다. 제 1 오프셋 제거 스위치(OC\_1)는 오프셋 제거 신호 (OC)에 따라 동작한다.

- [0041] 제 2 격리/오프셋 제거부(152)는 제 2 격리 스위치(ISO\_2) 및 제 2 오프셋 제거 스위치(OC\_2)를 포함한다. 제 2 격리 스위치(ISO\_2)의 일단은 상보 비트 라인(BLB)과 연결되고, 타단은 상보 센싱 비트 라인(SABLB)과 연결된다. 제 2 격리 스위치(ISO\_2)는 격리 신호(ISO)에 따라 동작한다. 제 2 오프셋 제거 스위치(OC\_2)의 일단은 상보 비트 라인(BLB)과 연결되고, 타단은 센싱 비트 라인(SABL)과 연결된다. 제 2 오프셋 제거 스위치(OC\_2)는 오프셋 제거 신호(OC)에 따라 동작한다.

- [0042] 감지 증폭기(153)는 제 1 및 제 2 pMOS 트랜지스터들(P\_1, P\_2) 및 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)을 포함한다. 예시적으로, pMOS 감지 증폭부(153p, 도 4 참조)는 제 1 및 제 2 pMOS 트랜지스터들(P\_1, P\_2)을 포함할 수 있다. nMOS 감지 증폭부(153n, 도 4 참조)는 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)을 포함할 수 있다.

- [0043] 제 1 pMOS 트랜지스터(P\_1)의 일단은 상보 센싱 비트 라인(SABLB)과 연결되고, 타단은 제 1 제어 신호(LA)의 라인과 연결되고, 게이트는 센싱 비트 라인(SABL)과 연결된다. 제 2 pMOS 트랜지스터(P\_2)의 일단은 센싱 비트 라인(SABL)과 연결되고, 타단은 제 1 제어 신호(LA)연결되고, 게이트는 상보 센싱 비트 라인(SABLB)와 연결된다.

- [0044] 제 1 nMOS 트랜지스터(N\_1)의 일단은 상보 센싱 비트 라인(SABLB)과 연결되고, 타단은 제 2 제어 신호(LAB)의 라인과 연결되고, 게이트는 비트 라인(BL)과 연결된다. 제 2 nMOS 트랜지스터(N\_2)의 일단은 센싱 비트 라인(SABL)과 연결되고, 타단은 제 2 제어 신호(LAB)연결되고, 게이트는 상보 비트 라인(BLB)과 연결된다.

- [0045] 비트 라인(BL)은 메모리 셀(MC)에 포함된 구동 스위치의 일단과 연결된다. 워드 라인(WL)은 메모리 셀(MC)에 포함된 구동 스위치의 게이트와 연결된다.

- [0046] 다음으로, 도 6을 참조하면, 도 6에 도시된 감지 증폭기(150)는 도 5에 도시된 감지 증폭기(150)와 동일한 등가 회로이다. 도면의 간결성을 위해, 제 1 및 제 2 격리 스위치들(ISO\_1, ISO\_2)과 제 1 및 제 2 오프셋 제거 스위

치들(OC\_1, OC\_2)은 파선으로 도시된다. 이하에서, 도 6에 도시된 감지 증폭기(150)의 등가회로를 참조하여 감지 증폭기(150)의 동작이 설명된다.

- [0047] 도 5 및 도 6에 도시된 감지 증폭기(150)는 격리 신호(ISO), 오프셋 제거 신호(OC), 및 제 1 및 제 2 제어 신호 들(LA)에 따라 프리-차지, 오프셋 제거, 전하 공유, 프리-센싱, 및 재저장 동작들을 순차적으로 수행한다. 이하에서, 도 7 내지 도 13을 참조하여 감지 증폭기의 동작이 상세하게 설명된다.

- [0048] 도 7은 도 6에 도시된 감지 증폭기의 동작을 보여주는 순서도이다. 도 8 내지 도 13은 도 7에 도시된 감지 증폭기의 동작을 설명하기 위한 회로도들이다. 설명의 편의를 위하여, 도 7의 각 단계들은 도 8 내지 도 13을 참조하여 설명된다.

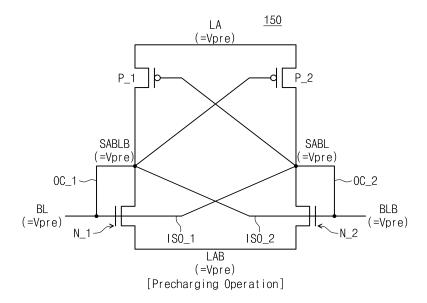

- [0049] 1. 프리-차지 동작(Pre-charging operation)

- [0050] 먼저, 도 7 및 도 8을 참조하면, 도 7의 S110 단계에서, 감지 증폭기(150)는 비트 라인(BL), 상보 비트 라인(BLB), 센싱 비트 라인(SABL), 및 상보 센싱 비트 라인(SABLB)은 프리차지 전압(Vpre)으로 프리차지한다. 예시 적으로, 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 로직 하이일 수 있다.

- [0051] 예를 들어, 도 8에 도시된 바와 같이, 격리 신호(ISO) 및 오프셋 제거 신호(OC)가 로직 하이이고, 제 1 및 제 2 격리 스위치들(ISO\_1, ISO\_2) 및 제 1 및 제 2 오프셋 제거 스위치들(OC\_1, OC\_2)은 턴-온된다. 이에 따라, 비트 라인(BL), 상보 비트 라인(BLB), 감지 증폭 비트 라인(SABLB), 상보 센싱 비트 라인(SABLB)은 하나의 노드로 연결되고, 각 라인들은 프리 차지 전압(Vpre)으로 충전된다. 예시적으로, 제 1 및 제 2 제어 신호들(LA, LAB)은 프리 차지 전압(Vpre)으로 충전될 수 있다.

- [0052] 예시적으로, 감지 증폭기(150)는 프리차지 회로(미도시)를 더 포함할 수 있다. 프리차지 회로(미도시)는 비트라인(BL), 상보 비트 라인(BLB), 감지 증폭 비트 라인(SABLB), 상보 센싱 비트 라인(SABLB)을 프리차지 전압 (Vpre)으로 충전할 수 있다.

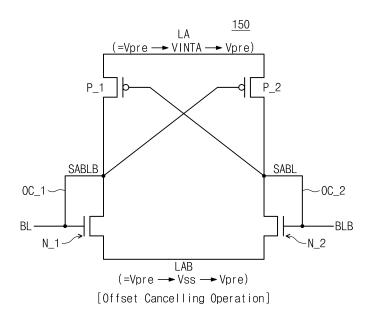

- [0053] 2. 오프셋 제거 동작(Offset cancelling operation)

- [0054] 다음으로, 도 7, 도 9, 및 도 10를 참조하면, 도 7의 S120 단계에서, 감지 증폭기(150)는 오프셋 제거 동작 (offset cancelling operation)을 수행한다. 예시적으로, 격리 신호(ISO)는 로직 로우이고, 오프셋 제거 신호 (OC)는 로직 하이일 수 있다.

- [0055] 예를 들어, 도 9에 도시된 바와 같이, 격리 신호(ISO) 및 오프셋 제어 신호(OC)에 따라 제 1 및 제 2 격리 스위치들(ISO\_1, ISO\_2)은 턴-오프되고, 제 1 및 제 2 오프셋 제거 신호들(OC\_1, OC\_2)은 턴-온될 수 있다. 이 때, 제 1 제어 신호(LA)는 프리차지 전압(Vpre)에서 입력 전압(VINTA)으로 천이되고, 제 2 제어 신호(LAB)는 프리차지 전압(Vpre)에서 접지 전압(Vss)으로 천이된다. 이 후, 제 1 제어 신호(LA)는 입력 전압(VINTA)에서 프리차지 전압(Vpre)으로 천이되고, 제 2 제어 신호(LAB)는 접지 전압(Vss)에서 프리차지 전압(Vpre)으로 천이된다. 예시적으로, 입력 전압(VINTA)는 메모리 셀 어레이(140, 도 1 참조)로 공급되는 전압일 수 있다.

- [0056] 도 9에 도시된 바와 같은 회로 구성 및 상술된 제 1 및 제 2 제어 신호들(LA, LAB)의 조절에 따라, 제 1 및 제 2 pMOS 트랜지스터들(P\_1, P\_2) 및 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)의 오프셋이 보상될 것이다. 예를 들어, 도 7에 도시된 바와 같이 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)은 다이오드로서 동작한다. 이때, 제 1 nMOS 트랜지스터(N\_1)의 문턱전압이 제 2 nMOS 트랜지스터(N\_2)의 문턱 전압보다 높은 경우, 제 1 제어 신호(LA)는 입력 전압(VINTA)이고, 제 2 제어 신호(LAB)는 접지 전압(VSS)이므로, 제 1 nMOS 트랜지스터 (N\_1)를 통해 흐르는 전류는 제 2 nMOS 트랜지스터(N\_2)를 통해 흐르는 전류보다 작을 것이다. 또한, 제 1 pMOS 트랜지스터(P\_1)를 통해 흐르는 전류보다 클 것이다. 즉, 비트 라인 및 센싱 비트 라인(BL, SABL)은 소정의 레벨만큼 상승할 것이다. 오프셋 보상 동작은 도 10을 참조하여 더욱 상세하게 설명된다.

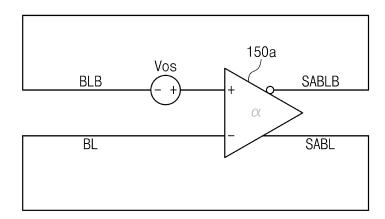

- [0057] 도 10은 도 9에 도시된 오프셋 제거 동작시의 감지 증폭기(150)가 모델링된 도면이다. 오프셋 제거 동작시의 모델링된 감지 증폭기(150)는 증폭기(150a) 및 오프셋 전압원(Vos)을 포함할 수 있다.

- [0058] 증폭기(150a)의 부출력(negative output)은 오프셋 전압원(Vos)의 음전압 단과 연결된다. 오프셋 전압원(Vos)의 양전압 입력단은 증폭기(150a)의 정입력단(positive input)과 연결된다. 증폭기(150a)의 정출력(positive

ouput)은 증폭기(150a)의 부입력단(negative input)과 연결된다. 이 때, 증폭기(150a)의 출력단들은 센싱 비트라인 및 상보 센싱 비트라인(SABL, SABLB)와 대응되고, 증폭기(150a)의 입력단들은 비트라인(BL) 및 상보 비트라인(BLB)과 대응될 것이다. 예시적으로, 오프셋 전압(Vos)은 제 1 및 제 2 pMOS 트랜지스터들(P\_1, P\_2) 및제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)의 오프셋을 가리킨다. 이 때, 도 10에 도시된 등가 회로의 동작은수학식 1과 같을 것이다.

### 수학식 1

$$V_{BL} + V_{OS} - V_{BLB} = \alpha (V_{SABL} - V_{SABLB})$$

$\therefore (V_{BL} = V_{SABLB}, V_{BLB} = V_{SABL})$

$V_{BL} - V_{BLB} = -V_{OS} \left(\frac{1}{1+\alpha}\right) \simeq -V_{OS}$

[0059]

[0060] 수학식 1을 참조하면, VBL은 비트 라인(BL)의 전압을 가리키고, Vos는 감지 증폭기(150)의 오프셋 값을 가리키고, VSABL은 성보 비트 라인(BLB)의 전압을 가리키고, VSABL은 센싱 비트 라인(SABL)의 전압을 가리키고, VSABLB는 상보 센싱 비트 라인(SABLB)를 가리키고, a는 증폭기(150a)의 전압이득을 가리킨다. 수학식 1과 같이, 비트라인(BL) 및 상보 비트 라인(BL)의 전압차는 오프셋 전압(Vos)에 근접할 것이다. 다시 말해서, 비트 라인(BL)이오프셋(Vos)만큼 전압 레벨이 보정됨으로써 감지 증폭기(150)의 오프셋이 보상될 수 있다.

[0061]

예를 들어, 도 9에 도시된 회로도를 참조하면, 공정 변이, 온도(PVT)로 인하여 제 1 nMOS 트랜지스터(N\_1)의 문턱 전압과 제 2 nMOS 트랜지스터(N\_2)의 문턱 전압이 서로 다를 수 있다. 이 때, 제 1 nMOS 트랜지스터(N\_1)의 문턱 전압이 제 2 nMOS 트랜지스터(N\_2)의 문턱 전압보다 오프셋 전압(Vos)만큼 높다고 가정한다. 이 경우, 도 9를 참조하여 설명된 동작 및 도 10의 모델링된 회로의 동작에 따라, 비트 라인(BL)은 프리차지 전압보다 오프셋 전압(Vos)만큼 상승할 것이다. 다시 말해서, 비트 라인(BL) 및 상보 비트 라인(BLB)의 전압들은 오프셋 전압(Vos)만큼의 전압 차이를 가질 것이다. 예시적으로, 비트 라인 및 상보 비트 라인(BL, BLB)의 전압은 트랜지스터들의 문턱 전압만큼 감소할 수 있다.

[0062]

따라서, 제 1 nMOS 트랜지스터(N\_1)의 게이트에 공급되는 전압과 제 2 nMOS 트랜지스터(N\_2)의 게이트에 공급되는 전압은 서로 오프셋 전압(Vos)만큼의 차이를 가지므로, 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)은 서로 동일한 전류 특성을 갖게 된다. 즉, 감지 증폭기의 오프셋 잡음(S/A offset noise)가 감소하기 때문에, 전압 변화량( $\triangle V$ , 도 3 참조)이 작아지더라도 충분한 감지 증폭기(150)의 유효 센싱 마진(effective sensing margin e)이 확보될 수 있다.

[0063]

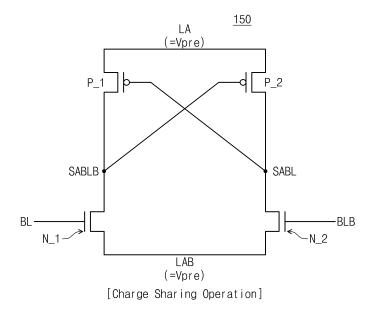

3. 전하 공유 동작(Charge sharing operation)

[0064]

다음으로, 도 7 및 도 11을 참조하면, 도 7의 S130 단계에서, 감지 증폭기(150)는 전하 공유 동작을 수행한다. 예시적으로, 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 로직 로우일 수 있다.

[0065]

예를 들어, 격리 신호(ISO) 및 오프셋 제거 신호(OC)가 로직 로우가 되어, 제 1 및 제 2 격리 스위치들(ISO\_1, ISO\_2) 및 제 1 및 제 2 오프셋 제거 스위치들(OC\_1, OC\_2)은 턴-오프되고, 감지 증폭기(150)는 도 10에 도시된 회로 구성을 가질 것이다. 이 때, 메모리 셀(MC, 도 5 참조)과 연결된 워드라인이 활성화 되고, 메모리 셀(MC)의 캐패시터에 저장된 전하와 비트 라인(BL)에 저장된 전하 사이에 전하 공유가 발생한다. 예시적으로, 메모리셀(MC)에 "데이터 1"이 저장된 경우, 전하 공유 동작시 비트 라인(BL)의 전압 레벨은 소정의 레벨만큼 증가할 것이다. 이와 반대로, 메모리 셀(MC)에 "데이터 0"이 저장된 경우, 전하 공유 동작시 비트 라인(BL)의 전압 레벨은 소정의 레벨만큼 감소할 것이다.

[0066]

4. 프리-센싱 동작(Pre-sensing operation)

[0067]

다음으로, 도 7 및 도 12를 참조하면, 도 7의 S140 단계에서, 감지 증폭기(150)는 프리-센싱 동작을 수행할 수 있다. 예시적으로, 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 로직 로우이다.

- [0068] 예를 들어, 도 7의 S130 단계 및 도 11을 참조하여 설명된 전하 공유 동작을 수행한 경우, 메모리 셀(MC)에 저장된 데이터에 따라 비트 라인(BL)의 전압은 소정의 레벨(△V)만큼 증가 또는 감소될 것이다. 이 때, 제 1 제어신호(LA)는 입력 전압(VINTA)으로 천이되고, 제 2 제어 신호(LAB)를 접지 전압(Vss)으로 천이되어, 감지 증폭기(150)는 도 12에 도시된 회로 구성을 가질 것이다. 이에 따라, 감지 증폭기(150)는 비트 라인(BL) 및 상보 비트라인(BLB)의 전압차를 기반으로 센싱 비트 라인(SABL) 및 상보 센싱 비트 라인(SABLB)의 전압들을 각각 입력 전압(Vinta)까지 충전시키거나 접지 전압(Vss)까지 방전시킬 수 있다.

- [0069] 예를 들어, 메모리 셀(MC)에 "데이터 1"이 저장된 경우, 프리-센싱 동작에서, 센싱 비트 라인(SABL)은 입력 전압(VINTA)으로 증가하고, 상보 센싱 비트 라인(SABLB)은 접지 전압(Vss)으로 감소할 것이다. 이와 반대로, 메모리 셀(MC)에 "데이터 0"이 저장된 경우, 프리 센싱 동작동안 센싱 비트 라인(SABL)은 접지 전압(Vss)으로 감소하고, 상보 센싱 비트 라인(SABLB)은 입력 전압(VINTA)으로 증가할 것이다.

- [0070] 예시적으로, 프리 센싱 동작동안, 비트 라인 및 상보 비트 라인(BL, BLB)과 센싱 비트 라인 및 상보 센싱 비트 라인(SABL, SABLB)은 제 1 및 제 2 격리/오프셋 제거부(151, 152)에 의해 차단된다. 다시 말해서, 감지 증폭기 (150)가 비트 라인 및 상보 비트 라인(BL, BLB)과 분리됨으로써, 비트 라인들 간 커플링 영향이 줄어들고, 센싱속도가 향상된다.

- [0071] 5. 재저장 동작(Restoring operation)

- [0072] 마지막으로, 도 7 및 도 13을 참조하면, 도 7의 S150 단계에서, 감지 증폭기(150)는 재저장 동작(restoring operation)을 수행할 수 있다. 예시적으로, 격리 신호(ISO)는 로직 하이이고, 오프셋 제거 신호(OC)는 로직 로우이다.

- [0073] 예를 들어, 격리 신호(ISO)는 로직 하이가 되고, 오프셋 제거 신호(OC)는 로직 로우가 되어, 제 1 및 제 2 격리 스위치들(ISO\_1, ISO\_2)은 턴-온되고, 제 1 및 제 2 오프셋 제거 신호들(OC\_1, OC\_2)은 턴-오프된다. 이 때, 도 13에 도시된 바와 같이 제 1 격리 스위치(ISO\_1)에 의해 비트 라인(BL)과 감지 증폭 비트 라인(SABL)이 연결되고, 제 2 격리 스위치(ISO\_2)에 의해 상보 비트 라인(BLB)과 상보 센싱 비트 라인(SABLB)이 연결된다. 따라서, 비트 라인(BL)은 프리 센싱된 센싱 비트 라인(SABL)의 전압 레벨로 증가 또는 감소할 것이다.

- [0074] 예시적으로, 도 7의 S150 단계 및 도 13을 참조하여, 재저장 동작이 설명되었으나, 본 발명의 범위가 이에 한정되는 것은 아니다. 예시적으로, 센싱 비트 라인 쌍(SABL, SABLB)은 데이터 라인(미도시)과 연결될 수 있다. 프리 센싱 동작 이 후, 센싱 비트 라인 및 상보 센싱 비트 라인(SABL, SABLB)은 데이터 라인과 연결되고, 데이터라인을 통해 로컬 감지 증폭기, 글로벌 감지 증폭기, 또는 입출력 회로로 출력될 수 있다.

- [0075] 상술된 본 발명의 실시 예에 따르면, 감지 증폭기(150)는 격리 신호(ISO), 오프셋 제거 신호(OC), 및 제 1 및 제 2 제어 신호들(LA, LAB)를 기반으로 프리차지, 오프셋 제거, 전하 공유, 프리 센싱, 및 재저장 동작을 수행한다. 이 때, 감지 증폭기(150)는 오프셋 제거 동작을 통해 감지 증폭기(150)의 오프셋을 보상하고, 프리 센싱 동작을 통해 비트 라인들간 커플링을 최소화하여 유효 센싱 마진을 향상시킬 수 있다. 따라서, 향상된 성능을 갖는 감지 증폭기 및 그것을 포함하는 메모리 장치가 제공된다.

- [0076] 도 14는 도 7에 도시된 감지 증폭기의 동작을 설명하기 위한 타이밍도이다. 예시적으로, 도 14의 X축은 시간을 가리키고, Y축은 신호 레벨을 가리킨다. 예시적으로, 메모리 셀(MC)은 "데이터 1"을 저장하고, 제 1 nMOS 트랜지스터(N\_1)의 문턱 전압이 제 2 nMOS 트랜지스터(N\_2)의 문턱 전압보다 오프셋 전압(Vos)만큼 높은 것으로 가정한다. 그러나 본 발명의 범위가 이에 한정되는 것은 아니다.

- [0077] 도 14를 참조하면, 감지 증폭기(150)는 프리 차지 동작, 오프셋 제거 동작, 전하 공유 동작, 프리 센싱 동작, 및 재저장 동작을 순차적으로 수행한다.

- [0078] 먼저, 제 1 구간(t0~t1)에서 감지 증폭기(150)는 프리 차지 동작을 수행한다. 이 때, 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 로직 하이이고, 비트 라인 쌍(BL, BLB) 및 센싱 비트 라인 쌍(SABL, SABLB)은 프리차지 전압 (Vpre)으로 충전된다.

- [0079] 이 후, 제 2 구간(t1~t2)에서 감지 증폭기(150)는 오프셋 제거 동작을 수행한다. 이 때, 격리 신호(ISO)는 로직로우가 된다. 제 1 제어 신호(LA)는 프리차지 전압(Vpre)에서 입력 전압(VINTA)으로 증가하고, 제 2 제어 신호(LAB)는 프리 차지 전압(Vpre)에서 접지 전압(Vss)으로 감소한다. 감지 증폭기(150)는 도 7, 도 9, 및 도 10을 참조하여 설명된 방법을 기반으로 오프셋 제거 동작을 수행할 수 있다. 오프셋 제거 동작동안, 비트 라인(BL)은

상보 비트 라인(BLB)보다 오프셋 전압(Vos)만큼 더 높을 것이다. 예시적으로, 비트 라인 쌍(BL, BLB)의 전압은 각각 감지 증폭부(153)의 트랜지스터들의 문턱 전압만큼 감소할 수 있다.

- [0080] 제 3 구간(t2~t3)에서 감지 증폭기(150)는 전하 공유 동작을 수행할 수 있다. 이 때, 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 로직 로우가 되고 워드 라인(WL)이 활성화되어, 비트 라인(BL)의 전하와 메모리 셀(MC)에 저장된 전하 간 전하 공유가 발생한다. 예를 들어, 메모리 셀(MC)에 "데이터 1"이 저장된 경우(메모리 셀(MC)의 캐 패시터의 전압이 기준값 이상인 경우), 비트 라인의 전압(VBL)은 전압 변화량(△V)만큼 상승할 것이다. 비록 도 면에 도시되지 않았지만, 메모리 셀(MC)에 "데이터 0"이 저장된 경우, 비트 라인 전압(VBL)은 전압 변화량(△V)만큼 감소할 수 있다.

- [0081] 제 4 구간(t3~t4)에서, 감지 증폭기(150)는 프리 센싱 동작을 수행할 수 있다. 이 때, 제 1 제어 신호(LA)는 입력 전압(VINTA)으로 천이되고, 제 2 입력 신호(LAB)는 접지 전압(VSS)으로 천이된다. 이에 따라, 센싱 비트 라인(SABL)은 입력 전압(VINTA)으로 증폭되고, 상보 센싱 비트 라인(SABLB)은 접지 전압(VSS)으로 감소한다.

- [0082] 제 5 구간(t4~t5)에서, 감지 증폭기(150)는 재저장 동작을 수행할 수 있다. 이 때, 격리 신호(ISO)는 로직 하이 가 되어, 제 1 및 제 2 격리 스위치들(ISO\_1, ISO\_2)은 턴-온된다. 즉, 비트라인 쌍(BL, BLB) 및 센싱 비트라인 쌍(SABL, SABLB)이 서로 연결되고, 비트라인 쌍(BL, BLB)은 각각 센싱 비트라인 쌍(SABL, SABLB)의 레벨로 충전 또는 방전될 것이다.

- [0083] 도 15는 본 발명의 다른 실시 예에 따른 감지 증폭기를 보여주는 회로도이다. 도 16은 도 15에 도시된 감지 증폭기의 등가회로를 보여주는 회로도이다. 도 15 및 도 16을 참조하면, 감지 증폭기(250)는 제 1 및 제 2 격리/오프셋 제거부(251, 252) 및 감지 증폭부(253)를 포함한다. 제 1 격리/오프셋 제거부(251)는 제 1 격리 스위치(1S0\_1) 및 제 1 오프셋 제거 스위치(0C\_1)를 포함한다. 제 2 격리/오프셋 제거부(252)는 제 1 격리 스위치(1S0\_1) 및 제 1 오프셋 제거 스위치(0C\_1)를 포함한다. 감지 증폭부(253)는 제 1 및 제 2 pMOS 트랜지스터들(P\_1, P\_2) 및 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)을 포함한다. 예시적으로, 제 1 및 제 2 격리/오프셋 제거부들 및 감지 증폭기(253)의 동작은 도 4 내지 도 13을 참조하여 설명되었으므로 이에 대한 설명은 생략된다.

- [0084] 도 15의 감지 증폭기(250)의 제 1 nMOS 트랜지스터(N\_1)는 도 5의 감지 증폭기(150)의 제 1 nMOS 트랜지스터 (N\_1)와 달리 제 3 제어 신호(LAB')를 기반으로 동작한다. 예를 들어, 감지 증폭기(250)의 제 1 nMOS 트랜지스터 터(N\_1)의 일단은 상보 센싱 비트 라인(SABLB)와 연결되고, 타단은 제 3 제어 신호(LAB') 라인과 연결된다. 이 때, 제 3 제어 신호(LAB')는 제 2 제어신호(LAB)와 동일한 제어신호일 것이다. 단, 도 16에 도시된 바와 같이 제 2 제어 신호(LAB) 및 제 3 제어신호(LAB')를 연결하는 배선 저항(R)으로 인한 신호 잡음이 발생할 수 있다.

- [0085] 이 경우, 배선 저항(R)으로 인한 신호 잡음은 오프셋 전압(Vos)에 포함될 수 있다. 예를 들어, 감지 증폭기 (250)는 도 7, 도 9, 및 도 10을 참조하여 설명된 방법을 기반으로 오프셋 제거 동작을 수행할 수 있다. 오프셋 제거 동작은 공정 변이, 온도 등으로 인한 감지 증폭기에 포함된 소자들의 특성 차이를 보상하는 동작을 가리킨다. 뿐만 아니라, 오프셋은 감지 증폭부의 배선간 저항(R) 성분에 의한 신호 잡음을 포함할 수 있다. 이 때, 배선 저항(R)으로 인한 신호 잡음은 오프셋 제거 동작시 소자들의 특성 차이와 함께 보상될 수 있다.

- [0086] 예시적으로, 도 15에 도시된 바와 같이 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)을 서로 분리하여 배치함으로 써, 감지 증폭기(250)의 레이아웃이 간결해질 수 있다.

- [0087] 상술된 본 발명의 다른 실시 예에 따르면, 감지 증폭기(250)는 프리 차지, 오프셋 제거, 전하 공유, 프리 센싱, 및 재저장 동작을 수행할 수 있다. 감지 증폭기(250)는 오프셋 제거 동작을 통해 감지 증폭기(250)의 오프셋을 보상할 수 있고, 프리 센싱을 동작을 통해 비트 라인 간 커플링 영향을 감소시킬 수 있다. 또한, 감지 증폭부 (253)에 포함된 소자들을 서로 분리하여 배치함으로써 간결한 레이아웃이 제공된다. 따라서, 향상된 성능 및 감소된 비용을 갖는 감지 증폭기 및 그것을 포함한 메모리 장치가 제공된다.

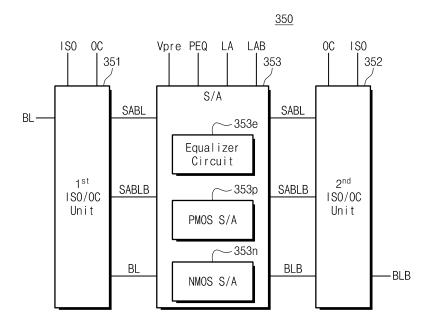

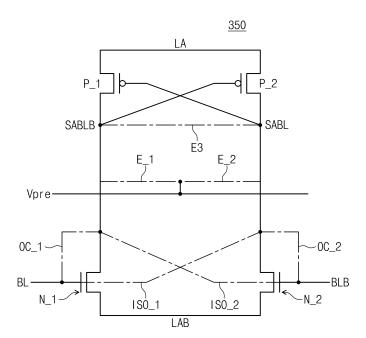

- [0088] 도 17은 본 발명의 또 다른 실시 예에 따른 감지 증폭기를 보여주는 블록도이다. 도 17을 참조하면, 감지 증폭기(350)는 제 1 및 제 2 격리/오프셋 제거부들(351, 352) 및 감지 증폭부(353)를 포함한다. 감지 증폭부(353, sense amplifying unit)는 pMOS 감지 증폭부(353p), nMOS 감지 증폭부(353n), 및 등화 회로(353e, equalizing circuit)를 포함한다. 도 17의 감지 증폭기(350)는 도 4의 감지 증폭기(150)와 비교하여, 등화 회로(353e)를 더 포함한다. 이하에서, 도 17의 감지 증폭기(350) 및 도 4의 감지 증폭기(150)의 차이점이 중점적으로 설명된다.

- [0089] 등화 회로(353e)는 비트 라인 쌍(BL, BLB) 및 센싱 비트 라인 쌍(SABL, SABLB)를 프리 차지 전압(Vpre)으로 등 화시킬 수 있다. 예를 들어, 감지 증폭기(350)의 프리 차지 동작시, 격리 신호(ISO) 및 오프셋 제거 신호(OC)가

로직 하이가 되어고, 비트 라인 쌍(BL, BLB) 및 센싱 비트 라인 쌍(SABL, SABLB)은 하나의 노드로 연결될 수 있다. 이 때, 등화 회로(353e)는 등화 신호(PEQ)에 응답하여, 비트 라인 쌍(BL, BLB) 및 센싱 비트 라인 쌍(SABL, SABLB)은 프리 차지 전압(Vpre)으로 충전 및 등화될 수 있다.

- [0090] 감지 증폭기(350)의 전하 공유 동작시, 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 로직 로우가 되어, 비트 라인 쌍(BL, BLB) 및 센싱 비트 라인 쌍(SABL, SABLB)은 서로 격리된다. 등화 회로(353e)는 등화 신호(PEQ)에 응답하여, 센싱 비트 라인 쌍(SABL, SABLB)을 프리 차지 전압(Vpre)으로 충전할 수 있다. 즉, 도 17의 감지 증폭기(350)는 도 5의 감지 증폭기(150)와 달리, 전하 공유시 동작에서 센싱 비트 라인 쌍(SABL, SABLB)을 프리차지 전압(Vpre)으로 충전할 수 있다.

- [0091] 도 18은 도 17에 도시된 감지 증폭기를 상세하게 보여주는 회로도이다. 도 19는 도 18에 도시된 감지 증폭기의 등가회로를 보여주는 회로도이다. 간결한 설명을 위하여, 복수의 스위치들(ISO\_1, ISO\_2, OC\_1, OC\_2, E\_1, E\_2, E\_3)은 도 19에서 파선으로 도시된다.

- [0092] 도 18 및 도 19를 참조하면, 감지 증폭기(350)는 제 1 및 제 2 격리/오프셋 제거부들(351, 352) 및 감지 증폭부 (353)를 포함한다. 제 1 격리/오프셋 제거부(351)는 제 1 격리 스위치(ISO\_1) 및 제 1 오프셋 제거 스위치 (OC\_1)를 포함한다. 제 2 격리/오프셋 제거부(352)는 제 2 격리 스위치(ISO\_1) 및 제 2 오프셋 제거 스위치 (OC\_2)를 포함한다. 감지 증폭부(350)는 제 1 및 제 2 pMOS 트랜지스터들(P\_1, P\_2), 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2), 및 제 1 내지 제 3 등화 스위치들(E\_1-E\_3)을 포함한다. 도 17의 제 1 및 제 2 격리 스위치들(ISO\_1, ISO\_2), 제 1 및 제 2 오프셋 제거 스위치들(OC\_1, OC\_2), 제 1 및 제 2 pMOS 트랜지스터들(P\_1, P\_2), 및 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)은 도 6을 참조하여 설명되었으므로, 이에 대한 상세한 설명은 생략된다.

- [0093] 제 1 내지 제 3 등화 스위치들(E\_1, E\_2, E\_3)은 등화 회로(353e)를 구성할 수 있다. 제 1 및 제 2 등화 스위치들(E\_1, E\_2)는 센싱 비트 라인 쌍(SABL, SABLB) 사이에 직렬 연결된다. 제 3 등화 스위치(E\_3)는 센싱 비트 라인 쌍(SABAL, SABLB) 사이에 연결된다. 제 1 내지 제 3 등화 스위치들(E\_1, E\_2, E\_3)은 등화 신호(PEQ)에 응답하여 동작한다. 예를 들어, 도 19에 도시된 바와 같이, 등화 신호(PEQ)가 로직 하이인 경우, 제 1 내지 제 3 등화 스위치들(E\_1, E\_2, E\_3)이 턴-온된다. 센싱 비트 라인 쌍(SABL, SABLB)은 제 1 및 제 2 등화 스위치들(E\_1, E\_2)에 의해 프리차지 전압(Vpre)으로 충전된다. 센싱 비트 라인 쌍(SABL, SABLB)은 제 3 등화 스위치(E\_3)에 의해 등화(equalize)된다.

- [0094] 예시적으로, 감지 증폭기(350)의 프리-차지 동작 및 전하 공유 동작시 등화 신호(PEQ)가 로직 하이가 될 수 있다. 다시 말해서, 감지 증폭기(350)의 프리-차지 동작 시 등화 회로(353e)는 등화 신호(PEQ)에 응답하여 비트라인 쌍(BL, BLB) 및 센싱 비트라인 쌍(SABL, SABLB)이 프리 차지 전압(Vpre)으로 충전 및 등화시킬 수 있다. 또한, 감지 증폭기(350)의 전하 공유 동작시 등화 회로(353e)는 등화 신호(PEQ)에 응답하여, 센싱 비트라인 쌍(SABL, SABLB)을 프리 차지 전압(Vpre)으로 충전하고 등화시킬 수 있다.

- [0095] 도 20은 도 18 및 도 19에 도시된 감지 증폭기의 동작을 보여주는 타이밍도이다. 예시적으로, 도 20의 X축은 시간을 가리키고, Y축은 신호 레벨을 가리킨다. 도 20을 참조하면, 제 2, 제 4, 및 제 5 구간들(t1~t2, t3~t4, t4~t5)의 동작은 도 14를 참조하여 설명되었으므로, 이에 대한 상세한 설명은 생략된다.

- [0096] 도 20에 도시된 제 1 구간(t0~t1) 동안 감지 증폭기(350)는 프리 차지 동작을 수행한다. 이 때, 격리 신호(ISO) 및 오프셋 제거 신호(OC)는 로직 하이가 되고, 비트 라인 쌍(BL, BLB) 및 센싱 비트 라인 쌍(SABL, SABLB)은 하나의 노드로 연결된다. 등화 신호(PEQ)가 활성화되고, 등화 회로(353e)는 등화 신호(PEQ)에 응답하여 비트 라인 쌍(BL, BLB) 및 센싱 비트 라인 쌍(SABL, SABLB)을 프리 차지 전압(Vpre)으로 충전 및 등화시킬 수 있다.

- [0097] 도 20에 도시된 제 3 구간(t2~t3) 동안 감지 증폭기(350)는 전하 공유 동작을 수행한다. 이 때, 등화 신호(PEQ)가 활성화된다. 이에 따라, 센싱 비트라인 쌍(SABL, SABLB)는 프리차지 전압(Vpre)으로 충전된다.

- [0098] 도 21은 본 발명의 또 다른 실시 예에 따른 감지 증폭기를 보여주는 회로도이다. 도 21을 참조하면, 감지 증폭기(450)는 제 1 및 제 2 격리/오프셋 제거부들(451, 452) 및 감지 증폭부(453)를 포함한다. 제 1 격리/오프셋 제거부(451)는 제 1 격리 스위치(ISO\_1) 및 제 1 오프셋 제거 스위치(OC\_1)를 포함한다. 제 2 격리/오프셋 제거부(452)는 제 2 격리 스위치(ISO\_2) 및 제 2 오프셋 제거 스위치(OC\_2)를 포함한다. 감지 증폭부(453)는 제 1 및 제 2 pMoS 트랜지스터들(P\_1, P\_2), 제 1 및 제 2 nMoS 트랜지스터들(N\_1, N\_2), 및 제 1 내지 제 3 등화스위치들(E\_1~E\_3)을 포함한다. 도 21의 구성 요소들은 도 19를 참조하여 설명되었으므로, 이에 대한 설명은 생략된다. 이하에서, 도 21의 감지 증폭기(450) 및 도 19의 감지 증폭기(350)의 차이점이 중점적으로 설명된다.

- [0099] 도 19에 도시된 바와 달리, 도 21에 도시된 제 1 nMOS 트랜지스터(N\_1)의 일단은 제 3 제어 신호(LAB')를 수신한다. 예시적으로, 제 3 제어 신호(LAB')는 제 2 제어 신호(LAB)와 동일한 신호일 것이다. 단, 제 3 제어 신호(LAB')는 배선 저항(R)으로 인한 신호 잡음을 포함할 수 있다. 그러나, 도 15 및 도 16을 참조하여 설명된 바와 같이 감지 증폭기(450)는 오프셋 제거 동작을 통해 배선 저항(R)으로 인한 신호 잡음을 보상할 수 있다. 예시적으로, 제 1 및 제 2 nMOS 트랜지스터들(N\_1, N\_2)을 서로 분리하여 배치함으로써, 감지 증폭기(450)의 레이아웃이 간결해질 수 있다.

- [0100] 상술된 본 발명의 또 다른 실시 예에 따르면, 감지 증폭기(450)는 오프셋 제거 동작을 기반으로 감지 증폭기 (450)의 오프셋을 보상하고, 프리 센싱 동작을 기반으로 비트라인들 간 커플링을 감소시킬 수 있다. 따라서, 향 상된 성능을 갖는 감지 증폭기 및 그것이 적용된 메모리 장치가 제공된다.

- [0101] 도 22는 본 발명의 실시 예들에 따른 감지 증폭기의 효과를 설명하기 위한 그래프이다. 예시적으로, 도 22의 X 축은 시간을 가리키고, Y축은 메모리 셀의 셀 전압을 가리킨다. 도 22를 참조하면, 메모리 셀에 충전된 셀 전압은 시간이 경과함에 따라 도 22에 도시된 바와 같이 감소할 것이다. 이 때, 셀 전압이 기준값 이하가 될 경우, 메모리 장치는 리프레쉬 동작을 수행한다.

- [0102] 예시적으로, 종래의 감지 증폭기가 적용된 메모리 장치의 리프레쉬 주기는 제 1 주기(tREF\_1)일 것이다. 오프셋 제거 동작을 수행하는 감지 증폭기가 적용된 메모리 장치의 리프레쉬 주기는 제 2 주기(tREF\_2)일 것이다. 본 발명에 따른 감지 증폭기가 적용된 메모리 장치의 리프레쉬 주기는 제 3 주기(tREF\_3)일 것이다.

- [0103] 다시 말해서, 본 발명에 따른 감지 증폭기는 오프셋 제거 동작을 통해 감지 증폭기의 오프셋을 보상하고, 프리-센싱 동작을 통해 비트 라인들 간 커플링 영향을 감소시킬 수 있다. 이에 따라, 유효 센싱 마진이 증가하므로 셀 전압이 기준값 이하라도 본 발명에 따른 감지 증폭기는 메모리 셀에 저장된 데이터를 독출할 수 있다. 따라서, 메모리 장치의 리프레쉬 주기가 증가하므로, 메모리 장치의 리프레쉬 전류(IDDR5)가 감소되므로, 감소된 비용을 갖는 감지 증폭기 및 그것이 적용된 메모리 장치가 제공된다.

- [0104] 도 23은 본 발명에 따른 감지 증폭기가 적용된 메모리 장치를 예시적으로 보여주는 도면이다. 도 23을 참조하면, 메모리 장치(1000)는 복수의 셀 어레이들(1110~11m0), 복수의 감지 증폭기들(1210~12n0), 및 더미 어레이들(1310, 1320)을 포함한다. 복수의 감지 증폭기들(1210~12n0) 각각은 복수의 비트 라인 감지 증폭 유닛들을 포함할 수 있다. 복수의 메모리 셀 어레이들(1110~11 m0)과 연결된 복수의 비트 라인 쌍들(BL, BLB)은 각각 복수의 비트 라인 감지 증폭 유닛들과 연결될 수 있다. 예시적으로, 메모리 장치(1000)는 오픈 비트 라인 구조를 갖는다. 오픈 비트 라인 구조를 갖는 메모리 장치(1000)는 비트 라인 쌍(BL, BLB)의 캐패시턴스가 서로 다를 경우, 프리차지 신호 잡음이 발생할 수 있다. 이에 따라, 비트 라인 쌍(BL, BLB)의 캐패시턴스를 균등하게 유지하기 위하여 비트 라인 쌍이 서로 교차하여 비트 라인 감지 증폭기에 연결된다.

- [0105] 이 때, 더미 어레이들(1310, 1320)은 메모리 장치(1000)의 가장자리(edge)에 배치될 수 있다. 더미 어레이들 (1310, 1320)의 일부 비트 라인들은 상보 비트 라인으로서 인접한 비트 라인 감지 증폭기들과 연결된다. 더미 어레이들(1310, 1320)의 나머지 비트 라인들은 더미 비트 라인들(BL\_d)으로써 비트 라인 감지 증폭기와 연결되지 않을 것이다. 즉, 메모리 장치(100)의 가장자리(edge)에 배치된 더미 비트 라인들(BL\_d)로 인하여 메모리 장치 면적의 오버헤드가 발생할 것이다.

- [0106] 도 24는 본 발명에 따른 감지 증폭기가 적용된 메모리 장치를 예시적으로 보여주는 도면이다. 도 24를 참조하면, 메모리 장치(2000)는 복수의 메모리 셀 어레이들(2110~21m0), 복수의 감지 증폭기들(2210~22n0), 및 복수의 캐패시터들(CAP)을 포함한다. 복수의 감지 증폭기들(2210~22n0)은 복수의 비트 라인 감지 증폭기들을 포함하고, 복수의 비트 라인 감지 증폭기들은 도 1 내지 도 22를 참조하여 설명된 감지 증폭기를 포함할 수 있다.

- [0107] 도 24의 메모리 장치(2000)는 도 23의 메모리 장치(1000)와 달리 복수의 캐패시터들(CAP)을 포함한다. 복수의 캐패시터들(CAP)은 메모리 장치(2000)의 가장자리(edge)에 배치될 수 있다. 즉, 메모리 장치(2000)는 더미 어레이를 포함하지 않을 것이다. 도 24를 참조하여 설명된 바와 같이, 오픈 비트 라인 구조를 갖는 메모리 장치는 비트 라인 쌍(BL, BLB)의 캐패시턴스를 균등하게 유지하기 위하여 비트 라인 쌍(BL, BLB)이 서로 교차되어 비트라인 감지 증폭기에 연결될 것이다.

- [0108] 그러나, 도 1 내지 도 22를 참조하여 설명된 방법을 기반으로 본 발명에 따른 감지 증폭기는 오프셋 제거 동작을 통해 비트 라인 쌍(BL, BLB)의 캐패시턴스 불균형으로 인한 차이를 보상할 수 있다. 즉, 메모리 장치(2000)는 도 23에 도시된 더미 어레이들(1310, 1320) 대신 복수의 캐패시터들(CAP)을 메모리 장치(2000)의 가장자리에 배치될 수 있다. 복수의 캐패시터들(CAP)과 연결된 라인들은 상보 비트 라인들(BLB)로서 인접한 비트 라인 감지

증폭기(BLSA)에 연결될 수 있다. 인접한 비트 라인 감지 증폭기들(BLSA)은 오프셋 제거 동작을 기반으로 비트라인 쌍(BL, SABL)의 캐패시턴스 불균형으로 인한 차이를 보상할 수 있다.

- [0109] 상술된 바와 같이, 본 발명에 따른 감지 증폭기를 오픈 비트 라인 구조의 메모리 장치에 적용할 경우, 비트 라인 쌍(BL, BLB)의 캐패시턴스 불균형이 보상되므로, 더미 어레이가 없는 오픈 비트 라인 구조의 메모리 장치가 제공된다. 따라서, 향상된 면적 및 감소된 비용을 갖는 감지 증폭기 및 그것이 적용된 메모리 장치가 제공된다.

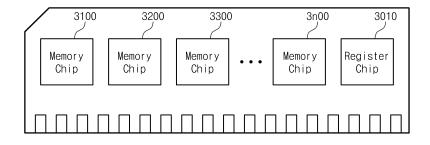

- [0110] 도 25는 본 발명에 따른 메모리 장치가 적용된 메모리 모듈을 보여주는 도면이다. 도 25를 참조하면, 메모리 모듈(3000)은 복수의 메모리 칩들(3100~3n00) 및 레지스터 칩(3010)을 포함한다. 복수의 메모리 칩들(3100~3n000)은 도 1에 도시된 메모리 장치(100)를 포함할 수 있다.

- [0111] 복수의 메모리 칩들(3100~3n00)은 외부 장치(예를 들어, 호스트, 메모리 컨트롤러, AP 등)로부터 커맨드, 어드 레스, 데이터 등을 수신하고, 데이터의 읽기/쓰기 동작을 수행할 수 있다. 레지스터 칩(3010)은 외부 장치로부터 커맨드, 제어 신호 등을 수신하고, 수신된 커맨드, 제어 신호 등을 기반으로 모드 레지스터 셋(MRS) 정보를 저장할 수 있다.

- [0112] 예시적으로, 복수의 메모리 칩들(3100~3n00)은 각각 도 4 내지 도 22를 참조하여 설명된 감지 증폭기들을 포함 할 수 있다. 예시적으로, 복수의 메모리 칩들(3100~3n00) 각각은 도 24에 도시된 메모리 장치(2000)일 수 있다.

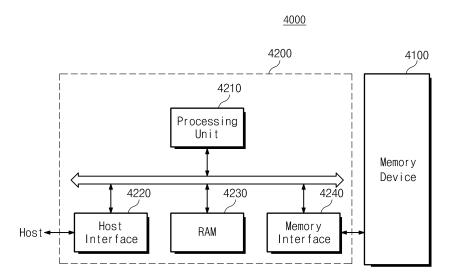

- [0113] 도 26은 본 발명에 따른 메모리 장치가 적용된 메모리 시스템을 예시적으로 보여주는 블록도이다. 도 26을 참조하면, 메모리 시스템(4000)은 메모리 장치(4100) 및 메모리 컨트롤러(4200)를 포함한다.

- [0114] 메모리 컨트롤러(4200)는 호스트(Host) 및 메모리 장치(4100)에 연결된다. 메모리 컨트롤러(4100)는 메모리 장치(4200)로부터 읽은 데이터를 호스트(Host)에 전달하고, 호스트(Host)로부터 전달되는 데이터를 메모리 장치(4100)에 저장한다.

- [0115] 메모리 컨트롤러(4200)는 프로세싱 유닛(4210), 호스트 인터페이스(4220), 램(4230) 그리고 메모리 인터페이스 (4240)와 같은 잘 알려진 구성 요소들을 포함할 것이다. 프로세싱 유닛(4210)은 메모리 컨트롤러(4200)의 제반 동작을 제어할 것이다. 호스트 인터페이스(4220)는 호스트(Host) 및 메모리 컨트롤러(4200) 사이의 데이터 교환을 수행하기 위한 프로토콜을 포함할 것이다. 예시적으로, 메모리 컨트롤러(4200)는 USB, MMC, PCI-E, ATA(Advanced Technology Attachment), Serial-ATA, Parallel-ATA, SCSI, ESDI, 그리고 IDE(Integrated Drive Electronics), eMMC(embeded Multi Media Card), UFS(Universal Flash Storage) 등과 같은 다양한 인터페이스 프로토콜들 중 하나를 통해 외부(호스트)와 통신하도록 구성될 것이다. 램(4230)은 프로세싱 유닛(4210)의 동작메모리로서 이용될 것이다. 예시적으로, 램(4230)은 도 1 내지 도 24를 참조하여 설명된 잠지 증폭기 및 메모리 장치를 포함할 수 있다. 또한, 램(4230)은 도 1 내지 도 24를 참조하여 설명된 동작 방법을 기반으로 동작할 수 있다.

- [0116] 메모리 인터페이스(4240)는 메모리 장치(4100)와 인터페이싱할 것이다. 메모리 컨트롤러(4200)는 오류 정정 블록을 추가적으로 포함할 수 있다. 오류 정정 블록은 메모리 장치(4100)로부터 읽어진 데이터의 오류를 검출하고, 정정할 것이다.

- [0117] 메모리 컨트롤러(4200) 및 메모리 장치(4100)는 하나의 반도체 장치로 집적될 수 있다. 예시적으로, 메모리 컨트롤러(4200) 및 메모리 장치(4100)는 하나의 반도체 장치로 집적되어, 메모리 카드를 구성할 것이다. 예를 들면, 메모리 컨트롤러(4200) 및 메모리 장치(4100)는 하나의 반도체 장치로 집적되어 PC 카드(PCMCIA), 컴팩트플래시 카드(CF), 스마트 미디어 카드(SM/SMC), 메모리 스틱, 멀티미디어 카드(MMC, RS-MMC, MMCmicro), SD 카드(SD, miniSD, microSD), 유니버설 플래시 기억장치(UFS) 등을 구성할 것이다.

- [0118] 다른 예로서, 메모리 컨트롤러(4200) 및 메모리 장치(4100)는 하나의 반도체 장치로 집적되어 반도체 디스크/드라이브(SSD, Solid State Disk/Drive)를 구성할 것이다. 메모리 시스템(4000)이 반도체 디스크(SSD)로 이용되는 경우, 메모리 시스템(4000)에 연결된 호스트(Host)의 동작 속도는 획기적으로 개선될 것이다.

- [0119] 다른 예로서, 메모리 시스템(4000)은 PDA, 포터블(portable) 컴퓨터, 웹 타블렛(web tablet), 무선 전화기 (wireless phone), 모바일 폰(mobile phone), 디지털 뮤직 플레이어(digital music player), 또는 정보를 무선 환경에서 송수신할 수 있는 장치들에 적용될 것이다.

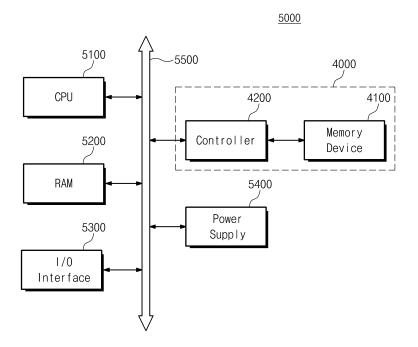

- [0120] 도 27은 도 26에 도시된 메모리 시스템을 포함하는 컴퓨팅 시스템을 예시적으로 보여주는 블록도이다. 도 27를 참조하면, 컴퓨팅 시스템(5000)은 중앙 처리 장치(5100), 램(5200, RAM, Random Access Memory), 입출력 인터

페이스(5300), 전원(5400), 그리고 메모리 시스템(4000)을 포함한다.

- [0121] 메모리 시스템(4000)은 시스템 버스(5600)를 통해, 중앙처리장치(5100), 램(5200), 입출력 인터페이스(5300), 그리고 전원(5400)에 전기적으로 연결된다. 입출력 인터페이스(5300)를 통해 제공되거나, 중앙 처리 장치(510 0)에 의해서 처리된 데이터는 메모리 시스템(4000)에 저장된다. 메모리 시스템(4000)은 컨트롤러(4200) 및 불휘 발성 메모리 장치(4100)를 포함한다.

- [0122] 예시적으로, 램(5200)은 컴퓨팅 시스템(5000)의 동작 메모리일 수 있다. 램(5200)은 도 1 내지 도 24를 참조하여 설명된 메모리 장치 또는 감지 증폭기를 포함할 수 있다. 또한, 도 1 내지 도 24를 참조하여 설명된 동작 방법을 기반으로 동작할 수 있다. 또한, 도 25를 참조하여 설명된 메모리 모듈을 포함할 수 있다.

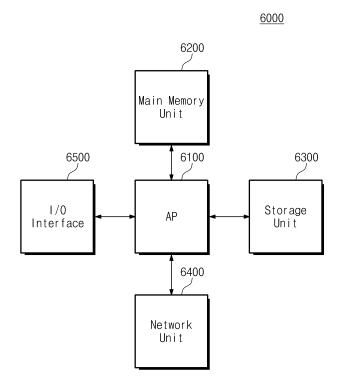

- [0123] 도 28은 본 발명에 따른 메모리 장치가 적용된 사용자 시스템을 예시적으로 보여주는 블록도이다. 예시적으로, 사용자 시스템(6000)은 UMPC (Ultra Mobile PC), 워크스테이션, 넷북(net-book), PDA (Personal Digital Assistants), 포터블(portable) 컴퓨터, 웹 타블렛(web tablet), 무선 전화기(wireless phone), 모바일 폰 (mobile phone), 스마트폰(smart phone), e-북(e-book), PMP (portable multimedia player), 휴대용 게임기, 데비케이션(navigation) 장치, 블랙박스(black box), 디지털 카메라(digital camera), DMB (Digital Multimedia Broadcasting) 재생기, 디지털 음성 녹음기(digital audio recorder), 디지털 음성 재생기(digital audio player), 디지털 영상 녹화기(digital picture recorder), 디지털 영상 재생기(digital video player) 등과 같은 컴퓨팅 시스템들 중 하나로 제공될 수 있다.

- [0124] 사용자 시스템(6000)은 응용 프로세서(6100), 주 저장부(6200), 보조 저장부(6300), 네트워크부(6400), 및 입출력 인터페이스(6500)를 포함한다. 응용 프로세서(6100)는 사용자 시스템(6000)에 포함된 구성 요소들, OS(Operating system) 등을 구동시킬 수 있다. 예시적으로, 응용 프로세서(6100)는 그래픽 엔진, 사용자 시스템(6000)에 포함된 구성 요소들을 제어하는 컨트롤러들 및 인터페이스들을 포함할 수 있다.

- [0125] 주 저장부(6200)는 사용자 시스템(6000)의 동작 메모리일 수 있다. 주 저장부(6200)는 응용 프로세서(6100) 및 보조 저장부(6300) 간 속도 차이를 보상하기 위한 버퍼 메모리일 수 있다. 예시적으로, 주 저장부(6200)는 DRAM(Dynamic Random Access Memory), SDRAM(Synchronous DRAM), SRAM(Static RAM), DDR SDRAM(Double Date Rate SDRAM), DDR2 SDRAM, DDR3 SDRAM, PRAM(Phase-change RAM), MRAM(Magnetic RAM), RRAM(Resistive RAM) 등과 같은 랜덤 액세스 메모리 장치로 제공될 수 있다. 예시적으로, 주 저장부(6200)는 도 1 내지 도 24를 참조하여 설명된 메모리 장치 또는 감지 증폭기를 포함할 수 있다. 또한, 주 저장부(6200)는 도 1 내지 도 24를 참조하여 설명된 동작 방법을 기반으로 동작할 수 있다.

- [0126] 보조 저장부(6300)는 데이터를 저장할 수 있다. 예를 들어, 보조 저장부(6300)는 외부로부터 수신한 데이터를 저장할 수 있다. 또는 보조 저장부(6300)는 보조 저장부(6300)에 저장된 데이터를 응용 프로세서(6100)로 전송할 수 있다. 예시적으로, 보조 저장부(6300)는 DRAM(Dynamic Random Access Memory), SDRAM(Synchronous DRAM), SRAM(Static RAM), DDR SDRAM(Double Date Rate SDRAM), DDR2 SDRAM, DDR3 SDRAM, PRAM(Phase-change RAM), MRAM(Magnetic RAM), RRAM(Resistive RAM), NAND flash, NOR flash 등과 같은 대용량 반도체 메모리 소자 또는 HDD(Hard Disk Drive)와 같은 대용량 자기 디스크 장치로 제공될 수 있다.

- [0127] 네트워크부(6400)은 외부 장치들과 통신을 수행할 수 있다. 예시적으로, 네트워크부(6400)은 CDMA(Code Division Multiple Access), GSM(Global System for Mobile communication), WCDMA(wideband CDMA), CDMA-2000, TDMA(Time Dvision Multiple Access), LTE(Long Term Evolution), Wimax, WLAN, UWB, 블루투스, WI-DI 등과 같은 무선 통신을 지원할 수 있다.

- [0128] 입출력 인터페이스(6500)는 사용자 시스템(1000)에 데이터 또는 명령어를 입력 또는 출력하는 인터페이스를 제공한다. 입출력 인터페이스(6500)는 카메라, 터치 스크린, 동작 인식 모듈, 마이크, 디스플레이, 스피커 등과 같인 입출력 장치들로 제공될 수 있다.

- [0129] 상술된 본 발명에 따르면, 감지 증폭기는 프리 차지, 오프셋 제거, 전하 공유, 프리 센싱, 및 재저장 동작을 순 차적으로 수행한다. 감지 증폭기는 오프셋 제거 동작을 기반으로 감지 증폭기의 오프셋을 보상하고, 프리 센싱 동작을 기반으로 비트 라인 간 커플링 영향을 감소시킨다. 이에 따라, 감지 증폭기는 유효 센싱 마진(effective sensing margine)을 향상시킬 수 있다. 따라서, 향상된 성능을 갖는 감지 증폭기 및 그것이 적용된 메모리 장치가 제공된다.

- [0130] 본 발명의 상세한 설명에서는 구체적인 실시 예에 관하여 설명하였으나, 본 발명의 범위에서 벗어나지 않는 한

도 내에서 여러가지 변형이 가능하다. 그러므로, 본 발명의 범위는 상술한 실시 예에 국한되어 정해져서는 안되며 후술하는 특허청구범위뿐만 아니라 이 발명의 특허청구범위와 균등한 것들에 의해 정해져야 할 것이다.

### 부호의 설명

[0131] 100 : 메모리 장치

110 : 어드레스 버퍼

120 : 로우 디코더

130 : 컬럼 디코더

140 : 메모리 셀 어레이

150 : 감지 증폭기

160 : 입출력 버퍼

151, 152 : 제 1 및 제 2 격리/오프셋 제거부들

153 : 감지 증폭부

153p, 153n : pMOS 및 nMOS 감지 증폭부들

MC : 메모리 셀

BL, BLB : 비트 라인 쌍

SABL, SABLB : 센싱 비트 라인 쌍

LA, LAB : 제 1 및 제 2 제어 신호들

ISO : 격리 신호

OC : 오프셋 제거 신호

ISO\_1, ISO\_2 : 제 1 및 제 2 격리 스위치들

OC\_1, OC\_2 : 제 1 및 제 2 오프셋 제거 스위치들

## 도면1

## 도면10

# <u>150</u>

## 도면25

3000