# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

| (51) Int. CI. <sup>6</sup><br>_H01L 27/04 | (11) 공개번호 특1996-0009159<br>(43) 공개일자 1996년03월22일      |

|-------------------------------------------|-------------------------------------------------------|

| (21) 출원번호<br>_(22) 출원일자                   | 특 1995-0027756<br>1995년08월30일                         |

| (30) 우선권주장<br>(71) 출원인                    | 94-206967 1994년08월31일 일본(JP)<br>오끼덴끼고오교 가부시끼가이샤 진구지 준 |

| (72) 발명자                                  | 일본국 도오꾜도 미나도꾸 도라노몬 1쪼메 7반 12고<br>구라찌 이꾸오              |

| (7.1) 5117101                             | 일본국 도오꾜도 미나도꾸 도라노몬 1쪼메 7반 12고 오끼덴끼고오교 가부시<br>끼가이샤 나이  |

| (74) 대리인                                  | 윤여범, 박해선                                              |

| 심사청구 : 없음                                 |                                                       |

### (54) 반도체 장치

## 요약

반도체 장치에 있어서, 출력버퍼회로가 갖는 MOSFET의 정전파괴를 보다 효과적으로 방지한다.

LDD 구조의 MOSFET(14)를 사용하여 출력버퍼회로를 구성하고, MOSFET(14)의 정전파괴를 방지하기 위한 보호소자(16)를 옵셋 게이트 구조의 MOSFET로 한다. 그리고 이들 MOSFET 14의  $N^{\dagger}$ 층(18)과 보호소자(16)  $N^{\dagger}$ 층(20)을 분리하여 이간시켜서 기판에 설치한다. 출력단자  $T_{OUT}$ 로부터 주입된 정전차아지는 보호소자(16)를 통하여 기판중에 유입한다. 그러나  $N^{\dagger}$ 층(18, 20)의 사이에 개재하는 기판 이 필드산화막의 저항성분에 의해 전압강하가 발생한다. 따라서 기판중에 정전차아지가 유입되어도, 이 전압강하의 작용에 의해, 버퍼용 MOSFET(14)의 채널 및 그의 근방영역에 있어서의 기판전위의 변동을 감소시킬 수가 있고, 그 결과, 버퍼용 MOSFET(14)의 스냅백의 발생을 억제할 수 있다. 이 때문에 목적을 달성할 수 있다.

# 대표도

# 도1

# 명세서

[발명의 명칭]

반도체 장치

[도면의 간단한 설명]

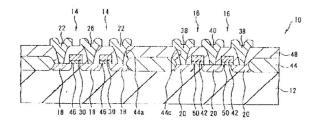

제1도는 실시예 1의 요부구성을 개략적으로 나타내는 단면도,

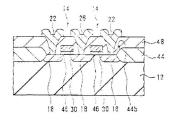

제2도는 실시예 1의 요부구성을 개략적으로 나타내는 단면도,

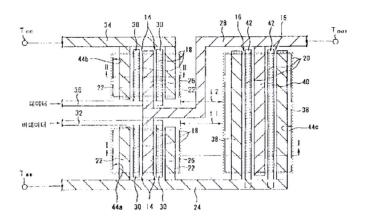

제3도는 실시예 1에 관하여 버퍼용 MOSFET 및 보호소자와 그 주변의 배선구조를 개략적으로 나타내는 평면도.

본 내용은 요부공개 건이므로 전문 내용을 수록하지 않았음

# (57) 청구의 범위

### 청구항 1

제1도전형의 반도체 기판에 설치된 집적회로, 이 집적회로를 위한 출력버퍼회로, 이 출력버퍼회로를 위한 보호회로 및, 상기 반도체기판에 전압을 공급하기 위한 전압공급회로를 구비하고, 상기 출력버퍼회로는 버퍼용 MOSFET를 가지며, 상기 보호회로는 상기 버퍼용 MOSFET의 정전파괴를 방지하기 위한 보호소자를 가지며, 이들 버퍼용 MOSFET 및 보호소자는 상기 반도체 기판에 형성된 제2도전형의 불순물 확산층으로 이루어지는 반도체 장치에 있어서, 상기 버퍼용 MOSFET의 불순물 확산층과 상기 보호소자의 불순물확산층을 분리하여 이간 배치하는 것을 특징으로 하는 반도체 장치.

## 청구항 2

제1항에 있어서, 상기 반도체 장치의 출력단자 및 접지단자의 사이에, 버퍼용 MOSFET와 보호소자를 병렬접속하는 것을 특징으로 하는 반도체 장치.

# 청구항 3

제1항에 있어서, 상기 반도체 장치의 출력단자 및 구동전원단자의 사이에, 버퍼용 MOSFET와 보호소자를 병렬접속하는 것을 특징으로 하는 반도체 장치.

### 청구항 4

제1항에 있어서, 보호소자를 MOSFET 또는 pn 다이오드로 한 것을 특징으로 하는 반도체 장치.

### 청구항 5

제1항에 있어서, 버퍼용 MOSFET의 불순물 확산층과 보호소자의 불순물 확산층과의 이간거리를 최저 5년 이상으로 하는 것을 특징으로 하는 반도체 장치.

### 청구항 6

제1항에 있어서, 반도체 기판에 설치된 접지단자에 접속되는 제2도전형의 가아드링을 구비하고, 이 가아드링의 내측에 보호소자의 불순물 확산층을 설치하는 것을 특징으로 하는 반도체 장치.

### 청구항 7

제1항에 있어서, 반도체 기판중에 매입된 제2도전형의 제1웰과, 이 제2월중에 매입된 제1도전형의 제2웰을 구비하고, 상기 제1 및 제2웰을 접지단자에 접속시키고, 제2웰에 보호소자의 불순물 확산층을 설치하여 이루어지는 것을 특징으로 하는 반도체 장치.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

### 도면

## 도면1

## 도면2

# 도면3