(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第3914135号 (P3914135)

(45) 発行日 平成19年5月16日 (2007.5.16)

(24) 登録日 平成19年2月9日(2007.2.9)

(51) Int.C1.

FI

HO1L 21/60

(2006, 01)

HO1L 21/60 311W

請求項の数 6 (全 11 頁)

(21) 出願番号 (22) 出願日 特願2002-324445 (P2002-324445) 平成14年11月7日 (2002.11.7)

(65) 公開番号

特開2004-158725 (P2004-158725A)

(43) 公開日 審査請求日 平成16年6月3日 (2004.6.3) 平成15年10月3日 (2003.10.3) |(73)特許権者 000006183

三井金属鉱業株式会社

東京都品川区大崎1丁目11番1号

||(74)代理人 100081994

弁理士 鈴木 俊一郎

(74)代理人 100103218

弁理士 牧村 浩次

|(74)代理人 100107043

弁理士 高畑 ちより

|(74)代理人 100110917

弁理士 鈴木 亨

|(72)発明者 川 崎 秀 一

東京都品川区大崎1丁目11番1号 三井 金属鉱業株式会社 マイクロサーキット事

業部内

最終頁に続く

(54) 【発明の名称】電子部品実装用フィルムキャリアテープ

# (57)【特許請求の範囲】

### 【請求項1】

長尺の絶縁フィルムの表面に導電性金属からなる多数の配線パターンが<u>形成されてなり</u>、かつ該長尺の絶縁フィルムの幅方向に配線パターンが少なくとも2個併設されてなると 共に、

該それぞれの配線パターンが、接続端子部分を除いて、それぞれ独立にソルダーレジスト層により被覆されており、かつそれぞれの配線パターン表面に形成されたソルダーレジスト層が、複数個に分割および / または分画され、

<u>該絶縁フィルムに形成された1個のフィルムキャリアの占有面積が、該フィルムキャリ</u>アに実装される電子部品の面積と略同一であり、

該分割あるいは分画されたソルダーレジスト層と、該分割あるいは分画されたソルダーレジスト層の区画に隣接するソルダーレジスト層の区画との間隙が 2 0 μ m ~ 3 mmの範囲内にあることを特徴とする電子部品実装用フィルムキャリアテープ。

### 【請求項2】

前記それぞれの配線パターン表面に、ソルダーレジスト層が 2 ~ 1 6 分割および / または分画されて形成されていることを特徴とする<u>請求項第1項記載</u>の電子部品実装用フィルムキャリアテープ。

# 【請求項3】

前記長尺の絶縁フィルムの厚さが75μm以下であることを特徴とする<u>請求項第1項記</u>載の電子部品実装用フィルムキャリアテープ。

20

30

40

50

### 【請求項4】

前記フィルムキャリアの電子部品が実装される側と反対の表面に外部と電気的に接触するための金属球を配置可能に形成されていることを特徴とする<u>請求項第1項記載</u>の電子部品実装用フィルムキャリアテープ。

# 【請求項5】

前記配線パターンの表面に塗設されたソルダーレジスト層の硬化後の配線パターン上における区画部分以外の平均厚さが3~50µmの範囲内にあることを特徴とする<u>請求項第</u>1項記載の電子部品実装用フィルムキャリアテープ。

#### 【請求項6】

前記ソルダーレジスト層が、接続端子部分を除いて配線パターン領域部の20%以上に 形成されていることを特徴とする<u>請求項第1項記載</u>の電子部品実装用フィルムキャリアテ ープ。

### 【発明の詳細な説明】

[0001]

# 【発明の属する技術分野】

本発明は、反り変形の低減された電子部品実装用フィルムキャリアテープに関する。さらに詳しくは本発明は、COF(Chip On Film)、CSP(Chip Size Package)、BGA(Boll Grid Array)のようにフィルムキャリアのサイズが実装する電子部品と概略同一であり、かつ長尺の絶縁フィルムからなるテープの幅方向に2つ以上のフィルムキャリアが並んで製造される電子部品実装用フィルムキャリアテープであって、それぞれのフィルムキャリアにおいて反り変形が著しく低減された電子部品実装用フィルムキャリアテープに関する。

#### [00002]

## 【発明の技術的背景】

集積回路などの電子部品を電子機器に搭載するために電子部品実装用フィルムキャリアテープが使用されている。この電子部品実装用フィルムキャリアテープは、長尺の絶縁フィルムの表面に導電性金属からなる配線パターンを形成し、このうち多くの電子部品実装用フィルムキャリアテープは、この配線パターンの表面に、端子部分を残して、ソルダーレジスト層を形成することにより製造されている。このような電子部品実装用フィルムキャリアテープにおいてソルダーレジスト層を形成する樹脂としては、エポキシ樹脂などの熱硬化性樹脂が使用されている。

### [0003]

ソルダーレジスト層を形成しない電子部品実装用フィルムキャリアテープにおいては大きな反り変形は見られないが、ソルダーレジスト層を形成する熱硬化性樹脂は、加熱して硬化させる際にわずかに硬化収縮するという特性を有しており、このようなソルダーレジスト層を形成する熱硬化性樹脂の硬化収縮に電子部品実装用フィルムキャリアテープには幅方向、長手方向に反り変形が生ずる。

# [0004]

このような長尺のフィルムキャリアテープの幅方向、長手方向に生じた反り変形は、たとえば加熱下に多数のロール間をフィルムキャリアを通過させる方法、発生したそり変形とは逆方向にフィルムキャリアテープを反らせながら(逆反りを与えながら)加熱する方法などにより、是正することができる。このような反り取り方法は、絶縁フィルムからなるテープの幅方向に1つの配線パターンが形成されたフィルムキャリアテープの反り取り方法として特に有効である。

# [0005]

ところで最近の電子部品の実装技術においては、COF (Chip On Film)、CSP (Chip Size Package)あるいはBGA (Boll Grid Array)などのように実装する電子部品とフィルムキャリアとが略同一の面積であるフィルムキャリアが使用されることが多くなってきている。このようなフィルムキャリアは、占有面積が小さいために、絶縁フィルムからなるテープの幅方向に複数個(例えば2個あるいは4個)並べて製造することができる。このようなCSP、COF、BGAなどでは、それぞれのフィルムキャリアにソルダーレジスト層が形成される

ため、ソルダーレジスト層が形成されたそれぞれのフィルムキャリアが反っており幅方向に複数のフィルムキャリアが形成されたテープに逆反りをかけたとしても、幅方向に隣接するフィルムキャリアの境界部分でテープが曲がってしまい、湾曲変形したフィルムキャリア部分にそれぞれ有効に逆反りをかけることができない。このためCSP、BGAのようにテープの幅方向に複数のフィルムキャリアを形成する電子部品実装用フィルムキャリアテープでは、それぞれのフィルムキャリアに生じた反り変形を是正する有効な反り取り方法が存在しないのが実情である。

[0006]

### 【特許文献1】

特願2001-249499号明細書

[0007]

#### 【発明の目的】

本発明は、テープの幅方向に複数のフィルムキャリアが形成された電子部品実装用フィルムキャリアテープにおけるそれぞれのフィルムキャリアの反り変形を低減した電子部品実 装用フィルムキャリアテープを提供することを目的としている。

#### [00008]

本発明の電子部品実装用フィルムキャリアテープは、長尺の絶縁フィルムの表面に導電性金属からなる多数の配線パターンが<u>形成されてなり、かつ該長尺の絶縁フィルムの幅方</u>向に配線パターンが少なくとも2個併設されてなると共に、

該それぞれの配線パターンが、接続端子部分を除いて、それぞれ独立にソルダーレジスト層により被覆されており、かつそれぞれの配線パターン表面に形成されたソルダーレジスト層が、複数個に分割および / または分画され、

<u>該絶縁フィルムに形成された1個のフィルムキャリアの占有面積が、該フィルムキャリ</u>アに実装される電子部品の面積と略同一であり、

該分割あるいは分画されたソルダーレジスト層と、該分割あるいは分画されたソルダーレジスト層の区画に隣接するソルダーレジスト層の区画との間隙が 2 0 μm ~ 3 mmの範囲内にあることを特徴としている。

### [0010]

本発明の電子部品実装用フィルムキャリアテープでは、ソルダーレジストを分割して塗布しており、分割されたそれぞれのソルダーレジスト層における硬化収縮による応力が小さいために、そのフィルムキャリアにおける変形を小さくすることができる。

[0011]

### 【発明の具体的説明】

次に本発明の電子部品実装用フィルムキャリアテープについて図面を参照しながら具体的 に説明する。

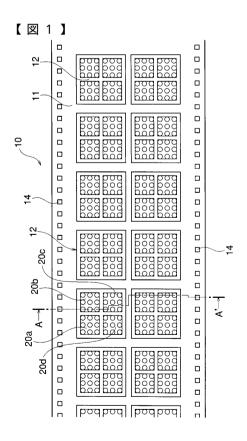

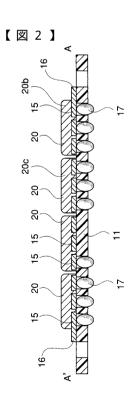

図 1 は、本発明の電子部品実装用フィルムキャリアテープの一例を示す平面図であり、図 2 は、図 1 におけるA - A' 断面図である。

### [0012]

図 1 および図 2 に示すように、本発明の電子部品実装用フィルムキャリアテープ 1 0 は、長尺の絶縁フィルム 1 1 の表面に多数のフィルムキャリア 1 2 が形成されてなる。

この長尺の絶縁フィルム11は、エッチングする際に酸などと接触することから、こうした薬品に侵されない耐薬品性およびボンディングする際の加熱によっても変質しないような耐熱性を有している。この絶縁フィルム11を形成する素材の例としては、ポリエステル、ポリアミドおよびポリイミドなどを挙げることができる。特に本発明では、ポリイミドからなるフィルムを用いることが好ましい。このようなポリイミドは、他の樹脂と比較して、卓越した耐熱性を有すると共に、耐薬品性にも優れている。

### [0013]

このポリイミド樹脂の例としては、ピロメリット酸2無水物と芳香族ジアミンとから合成される全芳香族ポリイミド、ビフェニルテトラカルボン酸2無水物と芳香族ジアミンとから合成されるビフェニル骨格を有する全芳香族ポリイミドを挙げることができる。特に本

10

20

30

40

20

30

40

50

発明ではビフェニル骨格を有する全芳香族ポリイミド(例;商品名:ユーピレックスS、宇部興産(株)製)が好ましく使用される。ビフェニル骨格を有する全芳香族ポリイミドは、他の全芳香族ポリイミドよりも吸水率が低い。本発明で使用可能な絶縁フィルムの厚さに特に制限はないが、厚さが $7.5~\mu$ m以下の絶縁フィルムは自己形態保持力が低くなり、変形が生じやすいので、本発明は絶縁フィルムの厚さ(平均厚さ)が $7.5~\mu$ m以下、好ましくは $5.0~1.2.5~\mu$ mの範囲内にある絶縁フィルムを用いた薄型のフィルムキャリアを製造する際に有用性が高い。

# [0014]

このような長尺の絶縁フィルム11の幅方向の縁部には、この絶縁フィルム11を搬送し、また位置決めを行うためにスプロケットホール14が多数形成されている。また、この絶縁フィルム11には、さらに位置決めホール、デバイスホール、外部端子となるハンダボールを配置するハンダボール穴、電子部品との接続を確保するためのスリットなどが形成されていてもよい。これらは、パンチング工程、レーザー光を用いた穿孔工程により形成することができる。

#### [0015]

このようにして必要な透穴を形成した絶縁フィルムに、配線パターン15を形成する。この配線パターン15は、たとえば、上記のような絶縁フィルム11の表面に導電性金属箔を配置し、この導電性金属箔の表面に感光性樹脂を塗布し、こうして形成された感光性樹脂層に所望のパターンを用いて露光現像して感光性樹脂からなるパターンを形成し、このパターンをマスキング材として使用して導電性金属箔を選択的にエッチングすることにより形成することができる。ここで使用する導電性金属の例としては、アルミニウム箔および銅箔を挙げることができる。このような導電性金属箔としては、通常は3~35μm、好ましくは9~25μmの範囲内にある金属箔を使用することができる。また、導電性金属の核を絶縁フィルム表面に設けて、その核に導電性金属を析出させてもよい。本発明で使用される導電性金属箔としては銅箔を使用することが好ましく、ここで使用可能な銅箔には、電解銅箔と圧延銅箔とがあるが、エッチング特性、操作性などを考慮する

# [0016]

と電解銅箔を使用することが好ましい。

本発明の電子部品実装用フィルムキャリアテープにおいて、上記導電性金属から形成された配線パターンによって形成されるフィルムキャリア12は絶縁フィルムからなるテープの幅方向に複数個形成されており、図1には、フィルムキャリア12がテープの幅方向に2個併存された態様が示されている。

本発明の電子部品実装用フィルムキャリアテープにおいては、上記のようなフィルムキャリア 1 2 は、テープの幅方向に、それぞれ独立して複数形成されている。たとえば、有効幅 3 5 mmの絶縁フィルム 1 1 には 1 辺が例えば14mmのフィルムキャリアを2個幅方向に並べて形成することができ、また、有効幅 7 0 mmの絶縁フィルム 1 1 には、1 辺がたとえば14mmのフィルムキャリアを 4 個幅方向に並べて形成することができる。

### [0017]

電子部品実装用フィルムキャリアテープ10に形成されているフィルムキャリアがCSPあるいはBGAの場合には、絶縁フィルム11の配線パターン15が形成されている面には、電子部品との接続を確保する端子部分16を残して、形成された配線パターンの表面にソルダーレジストインクを塗布してソルダーレジスト層20を形成をする。ここで塗布するソルダーレジスト層20を形成する樹脂は、通常は熱硬化性樹脂を有機溶媒に溶解もしくは分散させた塗布液であり、このようなソルダーレジストインクを塗布した後、加熱することによりソルダーレジスト層20を形成する。そして、このソルダーレジストインクが硬化してソルダーレジスト層20を形成する際にはソルダーレジスト層を形成する樹脂は僅かに硬化収縮するため、このソルダーレジストインクが塗布された部分はソルダーレジスト層20を内側にして反り変形が生ずる。

## [0018]

なお、ソルダーレジスト層の形成が不要なタイプの電子部品実装用フィルムキャリアテー

プもある。

このようにテープの幅方向にフィルムキャリア12が複数並んで形成されている場合、このテープに逆反りをかけてもフィルムキャリア12の間でテープが折れ曲がるだけで、反り変形が生じているフィルムキャリア12の部分にはほとんど逆反りがかからない。したがって、個々のフィルムキャリア12についてみると、ほとんど反り変形は是正されない

[0019]

したがって、上記のようなテープの幅方向に複数のフィルムキャリア 1 2 を並べて形成する場合には、それぞれのフィルムキャリア 1 2 自体に反り変形が発生しないようにするのが効率的である。

反り変形が生ずる原因は、絶縁フィルム、導電性金属などの材料の膨張係数の差や、前述のようにソルダーレジストの硬化収縮であり、この硬化収縮により生ずる内部応力が絶縁フィルムなどの自己形態保持性よりも恒常的に高くなったときに、ソルダーレジスト層に内在する応力がフィルムキャリアの反り変形として表在化するのである。そして、ソルダーレジスト層 2 0 の形成面積が大きくなると、大面積のソルダーレジスト層 2 0 中における内部応力が相互に連帯して大きな内部応力となりやすい。しかしながら、このような大きな内部応力が発生しているソルダーレジスト層 2 0 においても、部分的にみると、その内部応力はそれほど大きいものではない。

[0020]

そこで、本発明では従来一体に塗布されて形成されて全体が一体化していたソルダーレジスト層 2 0 をいくつかに分割あるいは分画して塗布形成し、それぞれの分割あるいは分画された区画における応力のできるだけ小さくし、この区画されたソルダーレジスト層 2 0 の部分にある絶縁フィルム 1 1 の自己形態支持力と拮抗する程度以下に抑えて区画されたソルダーレジスト層 2 0 形成部における反り変形を最小限に抑えているのである。

[0021]

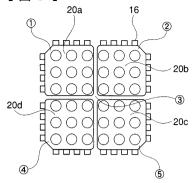

すなわち、本発明の電子部品実装用フィルムキャリアテープ 1 0 では、図 1 ~ 3 に示すようにソルダーレジスト層 2 0 を、 A 区画 2 0 a、 B 区画 2 0 b、 C 区画 2 0 c、 D 区画 2 0 d のように複数の区画に分割してソルダーレジストを塗布・形成する。

本発明においてソルダーレジスト層 2 0 を形成する樹脂は、硬化性樹脂であり、例えば、例えば、エポキシ樹脂、ウレタン変性エポキシ樹脂、フェノール樹脂、ポリイミド樹脂前駆体などの熱硬化性樹脂が好ましく使用される。このような熱硬化性樹脂は、溶媒中に溶解もしくは分散されており、スクリーンマスクを用いてスキージーによる塗布が可能なように、通常は 1 0 ~ 4 0 Pa・s、好ましくは 2 0 ~ 3 0 Pa・s の範囲内の粘度に調整されている。

[0022]

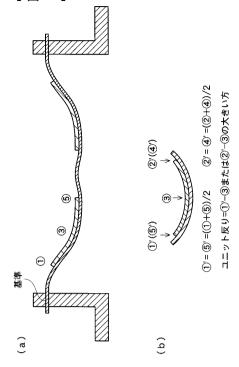

図1~3においては、ソルダーレジスト層20を形成する領域は、A区画20a、B区画20b、C区画20c、D区画20dを併せた領域であるが、従来はこれらの領域を一体としてソルダーレジストを塗布していた。しかしながら、このように広範囲にソルダーレジストを塗布し、硬化させると、樹脂が硬化する際に硬化収縮し、個々のフィルムキャリア12に、図4に示すようにソルダーレジスト層20を内側にした反り変形が生ずる。

[0023]

本発明の電子部品実装用フィルムキャリアテープでは、上記のようなソルダーレジストを塗布すべき領域を複数に分割して、ソルダーレジストを塗布する。すなわち、図1および3において、ソルダーレジストを塗布すべき領域は、A区画20a、B区画20b、C区画20cおよびD区画20dを併せた領域であるが、図1および図3に示す例では、この領域を4分割してそれぞれの区画を隣接する区画から独立させてソルダーレジストを塗布し、硬化させて4区画に分割されたソルダーレジスト層20を形成している。なお、フィルムキャリアの縦、横サイズが5mm未満の場合には問題となる程のそり変形は生じない場合が多いので、本発明はフィルムキャリアの縦・横サイズが5mm以上であるフィルムキャリアにおいてソルダーレジストを分割形成することが好ましい。

10

20

30

40

このようにソルダーレジスト層を分割することにより、それぞれの区画内にはソルダーレジストの硬化収縮による応力は発生するが、その応力は小さく、絶縁フィルムおよびその上に形成されている配線パターンなどに内在する応力と拮抗させることにより、そのフィルムキャリア内における変形を最小限に留めることができる。

### [0024]

このようなソルダーレジスト層 2 0 はフィルムキャリアのサイズ、絶縁フィルム、ソルダーレジスト、その他の材料の物性値にもよるが、 2 ~ 1 6 分割することが好ましく、さらに 2 ~ 8 分割することが特に好ましい。このようにソルダーレジスト層 2 0 を分割することにより、それぞれの区画におけるソルダーレジストの硬化による収縮応力が小さくなり、フィルムキャリア全体の変形も小さくなる。なお、分割後のソルダーレジストのサイズは、絶縁フィルム、ソルダーレジストなどの物性値が複雑に絡み合っているので、1辺のサイズを必ずしも 5 mm未満にする必要はない。

### [0025]

本発明の電子部品実装用フィルムキャリアテープ10においてはソルダーレジスト層20を分割および / または分画する各区画の形状および相対的な大きさに特に制限はないが、ソルダーレジストが塗布される領域をできるだけ均等に分割できるようにすることが好ましい。それぞれの区画に生ずる応力を均一化することにより、フィルムキャリア全体の変形がより小さくなる。すなわち、それぞれの区画の面積を均等にすること共に、それぞれの区画の形態は略同一とすることが好ましい。本発明の電子部品実装用フィルムキャリアテープでは、区画されたソルダーレジストの各区画の一辺の長さを2~20mm程度、好ましくは2.5~7.5mm程度にすることが望ましい。

### [0026]

# [0027]

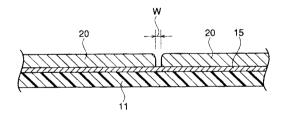

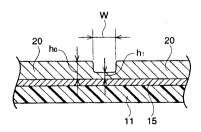

上記のように分割および / または分画されたソルダーレジスト層の厚さ( $h_0$ )は、従来のソルダーレジスト層の厚さと同様であり、硬化後の平均厚さは配線パターンの上面において通常は  $3\sim 5$  0  $\mu$  m、好ましくは  $5\sim 4$  0  $\mu$  mの範囲内にある。また、本発明の電子部品実装用フィルムキャリアテープにおいて、ソルダーレジスト層 2 0 は、図 5 (a)に示すように分割されており、隣接する区画との間に上記のようなソルダーレジスト層が形成されていない部分を有するが、それぞれの区画に生じた内部応力が隣接する区画に伝達しなければよく、例えば図 5 (b)に示すように区画されたソルダーレジスト層 2 0 が少なくとも一部で隣接するソルダーレジスト層の区画と連結され分画されていてもよい。この場合、区画と区画との間のソルダーレジスト層の厚さ( $h_1$ )は、ソルダーレジスト層の通常の厚さ( $h_0$ )の1/2以下であり、 $h_1$ は0であってもよい。

# [0028]

こうした区画されたソルダーレジスト層 2 0 を形成には、従来のスクリーンに区画に対応するようにマスキングを形成して樹脂を塗布すればよい。また、近時採用され始めている貼着タイプのソルダーレジストの場合には、間隙を形成してソルダーレジストを貼着すればよい。さらに、感光性樹脂を用いたソルダーレジストの場合には、樹脂を塗布した後、ソルダーレジスト層が分割および / または分画されるように露光・現像すればよい。また、区画間の少なくとも一部が連結されるように分画されたソルダーレジスト層はソルダーレジスト塗布液の塗布の際に用いるスクリーンマスクの線幅を調整することにより形成することができる。

# [0029]

20

30

上記のようにしてソルダーレジスト層を形成した後、ソルダーレジスト層 2 0 から露出した端子部分(リード、ボンディングパット、その他) 1 6 の表面をメッキ処理する。メッキ処理には、錫メッキ、ニッケルメッキ、ニッケル・金の多層メッキ、ニッケル・パラジウム・金の多層メッキ、ハンダメッキ、錫・ビスマスメッキなどがある。なお、分割されたソルダーレジスト層の間にある配線パターンの表面には上記のメッキ層が形成されている。【 0 0 3 0 】

このメッキ処理は、ソルダーレジスト層を形成する前に行ってもよい。

上記のようにして製造された本発明の電子部品実装用フィルムキャリアテープは通常の方法により使用することができる。例えば、分割して形成されたソルダーレジスト層上に接着剤などを用いて電子部品(図示なし)を配置し、この電子部品に形成されたバンプ電極と接続端子16との間に電気的接続を形成することにより、電子部品を実装することができる。この電気的接続の形成には、例えば金線のような導電性金属線などを用いることができる。本発明の電子部品実装用フィルムキャリアテープにおいて、実装する電子部品とキャリアテープとは略同等の占有面積を有している。

### [0031]

本発明の電子部品実装用フィルムキャリアテープに形成されている接続端子16は、配線パターン15を介してハンダボールと接続している。

上記のように本発明の電子部品実装用フィルムキャリアテープは、ソルダーレジスト層が分割されているので、ソルダーレジストの硬化の際の硬化収縮に起因するフィルムキャリアの反り変形を低減することができる。

#### [0032]

本発明の電子部品実装用フィルムキャリアテープにおけるフィルムキャリアの変形は、次のようにして測定する。図 4 (a)に示すように、スプロケットホールを用いて移動させるフィルムキャリアテープのスプロケットホールが形成されている部分を基準点として、製造されたフィルムキャリアテープにおける、一つのフィルムキャリアについて図 3 に示す測定ポイント 1 ~ 5 の基準点に対する高さを測定する。このような得られた値からこのフィルムキャリアテープが図 4 に示されているように変形していることを考慮して、計算により測定しようとするフィルムキャリア(ユニット)の 1 ' ( 5 ' )、2 ' ( 4 ' )の値を求める。 1 ' = 5 ' = ( 1 + 5 ) / 2 を求め、同様に 2 ' = 4 ' = ( 2 + 4 ) / 2 を求める。

そして、本発明におけるユニット反りは、 1 '- 3 または 2 '- 3 の値のうち大きいほうが本発明における反り変形である。

### [0033]

上記のようにしてソルダーレジスト層を分割あるいは分画することにより、フィルムキャリアの反り変形は、分割しないソルダーレジスト層を有するフィルムキャリアの反り変形の 50%以下になる。

上記のように本発明の電子部品実装用フィルムキャリアテープでは、ソルダーレジスト層を分割あるいは分画して形成することにより、フィルムキャリアの反り変形が低減され、 信頼性の高い電子部品実装用フィルムキャリアテープが得られる。

### [0034]

# 【発明の効果】

本発明の電子部品実装用フィルムキャリアテープは、ソルダーレジスト層が複数に分割あるいは分画されているために、ソルダーレジストインクが硬化する際の収縮に伴う応力が分散される。このため本発明の電子部品実装用フィルムキャリアテープでは、ソルダーレジスト層の硬化収縮によるフィルムキャリアの反り変形は著しく低減され、電子部品の実装精度が確実に向上する。

### [0035]

特に本発明の電子部品実装用フィルムキャリアテープは、CSP、COF、BGAなどとして特に有用性が高い。

# [0036]

40

20

### 【実施例】

次に本発明の電子部品実装用フィルムキャリアテープについて、反りの発生しやすい、接続端子以外の配線パターン全面にソルダーレジストを形成する場合に対しての実施例を示して説明するが、本発明はこれらによって限定されるものではない。

### [0037]

# 【実施例1】

平均厚さ 5 0 μm、幅 4 8 mmのポリイミドフィルム(宇部興産(株)製、商品名:ユーピレックスS)にスプロケットホールおよびハンダボールを配置するためのハンダボール穴をパンチングにより穿設した。このポリイミドフィルムには、図 1 に示すように、一辺が1 7 mmのフィルムキャリアが二列形成できるようにハンダボール穴を穿設した。

### [0038]

次いで、このポリイミドフィルムに平均厚さ 2 5 μ m の電解銅箔を貼着し、この電解銅箔上に感光性樹脂を塗布し、露光・現像した。こうして現像された感光性樹脂からなるパターンをマスキング材として、電解銅箔をエッチングすることにより銅からなる配線パターンを形成した。

このようにして形成された配線パターンの表面にソルダーレジストインクを塗布して加熱硬化させることによりソルダーレジスト層(硬化後の平均厚さ:10μm)を形成した。ここで形成されたソルダーレジスト層は、スクリーンにマスクと形成することにより、図1に示すように、4分割されており、各区画の間には200μmの幅でソルダーレジストが塗布されていない部分(区画部分)が存在する。

#### [0039]

こうして 4 分割されたソルダーレジスト層を形成した後、ソルダーレジスト層により被覆されていない接続端子およびソルダーレジスト層の区画部をニッケルメッキ後、金メッキ処理し、さらにフィルムキャリアテープ全体に常法に従って反り取りを行った。

得られた電子部品実装用フィルムキャリアテープ長さ方向の中心部分に近い部分に形成されたフィルムキャリアを無作為に連続 6 列 1 2 個選択して、これらのフィルムキャリアについて反り変形を測定した。

### [0040]

結果を表 1 に示す。なお、表 1 において上段、下段と記載したのは、このフィルムキャリアテープを図 1 に示すように配置した際に上側になるフィルムキャリアと下側になるフィルムキャリアとを区別するためのものであり、本発明の電子部品実装用フィルムキャリアテープの製造工程におけるテープの向きとは無関係である。

### [0041]

# 【表1】

# 表 1

|    | 第1ピース   | 第 2 ピ─ス  | 第3ピース    | 第 4 ピース  | 第5ピース   | 第 6 ピース | 平均值     |

|----|---------|----------|----------|----------|---------|---------|---------|

| 上段 | 0.35mm  | −0.005mm | 0.015mm  | 0.023mm  | 0.150mm | 0.071mm | 0.035mm |

| 下段 | 0.012mm | 0.051mm  | -0.019mm | -0.016mm | 0.017mm | 0.180mm |         |

# [0042]

# 【比較例1】

実施例 1 において、ソルダーレジスト層を分割しなかった以外は同様にして電子部品実装用フィルムキャリアテープを製造した。

得られた電子部品実装用フィルムキャリアテープについて、実施例と同様にして無作為に連続6列12個のフィルムキャリアを選択して、これらのフィルムキャリアの反り変形を測定した。

# [0043]

10

20

30

結果を表2に記載する。

[0044]

【表2】

表 2

|    | 第 1 ピース | 第2ピース   | 第 3 ピース | 第 4 ピース | 第 5 ピース | 第6ピース   | 平均値     |

|----|---------|---------|---------|---------|---------|---------|---------|

| 上段 | 0.112mm | 0.050mm | 0.074mm | 0.078mm | 0.084mm | 0.061mm | 0.085mm |

| 下段 | 0.098mm | 0.074mm | 0.093mm | 0.092mm | 0.072mm | 0.089mm | 0.065mm |

[0045]

上記表 1 と表 2 とを比較すると明らかなように、ソルダーレジスト層を 4 分割することにより、フィルムキャリアの反り変形量を平均値で半分以下に低減することができる。

【図面の簡単な説明】

- 【図1】 図1は、本発明の電子部品実装用フィルムキャリアテープの一例を示す平面図である。

- 【図2】 図2は、図1におけるA-A′断面図である。

- 【図3】 図3は、本発明の電子部品実装用フィルムキャリアテープを形成するひとつのフィルムキャリアを抜き出して説明する説明図である。

- 【図4】 図4は、本発明においてフィルムキャリアの反り変形を測定する方法を示す図である。

- 【図5】 図5は、ソルダーレジスト層の区画部の断面の例を示す図である。

10

【図3】

【図4】

【図5】 (a)

# フロントページの続き

# 審査官 田中 永一

(56)参考文献 特開平06-005662(JP,A)

特開平05-029395(JP,A)

特開平11-145205(JP,A)

特開昭60-216573(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60

H01L 23/12