# (19)中华人民共和国国家知识产权局

# (12)发明专利

审查员 杜君

(10)授权公告号 CN 106849675 B (45)授权公告日 2019.07.05

(21)申请号 201710191750.5

(22)申请日 2017.03.28

(65)同一申请的已公布的文献号 申请公布号 CN 106849675 A

(43)申请公布日 2017.06.13

(73) 专利权人 无锡芯朋微电子股份有限公司 地址 214028 江苏省无锡市新区龙山路旺 庄科技创业中心C栋

(72)**发明人** 李海松 赵倡申 刘文亮 易扬波 周飙 张韬 芮华政

(74)专利代理机构 江苏圣典律师事务所 32237 代理人 王玉国

(51) Int.CI.

**HO2M** 3/335(2006.01)

权利要求书4页 说明书11页 附图6页

#### (54)发明名称

开关电源的控制电路及其方法

#### (57)摘要

本发明公开了开关电源的控制电路及其方法,由恒流控制模块根据FB管脚和CS管脚上的反馈信息,产生并输出控制开关电源输出电流的控制信号,调节功率晶体管的开通占空比,调整电源系统的输出电流Io为恒定值;恒流精度补偿模块根据FB管脚和CS管脚上的反馈信息,调节恒流控制模块和采样保持模块的电路计算参数,使输出恒流精度不受工作模式变化和/或输入条件变化的影响;定时器判定FB管脚上电压VFB到达谷值的时刻;压控振荡器根据恒流控制模块输出的控制信号和定时器的输出信号,调节功率晶体管的开关频率,使开关电源工作于QR模式或CCM模式,当输出电压变化时,QR模式保持不变或CCM模式电流连续的深度保持相近。

CN 106849675 B

- 1. 开关电源的控制电路, 其特征在于: 包含第一比较器(1)、第一RS锁存器(G1)、恒流控 制模块(8)、恒流精度补偿模块(9)、采样保持模块(10)、低通滤波器(11)、第二比较器(2)、 第二RS锁存器(G2)、压控振荡器(12)、定时器(13)、与逻辑门(G3)、驱动模块(3)以及功率晶 体管(M1),所述恒流控制模块(8)的第一输入端与第一RS锁存器(G1)的QB输出端、恒流精度 补偿模块(9)的第一输入端相连;恒流控制模块(8)的第二输入端与管脚FB、第一比较器(1) 的正相输入端相连;恒流控制模块(8)的第三输入端与驱动模块(3)的输出端、功率晶体管 (M1)的栅极、恒流精度补偿模块(9)的第二输入端相连;恒流控制模块(8)的第四输入端与 恒流精度补偿模块(9)的第一输出端相连;恒流控制模块(8)的第五输入端与采样保持模块 (10)的输出端相连;恒流控制模块(8)的输出端与低通滤波器(11)的输入端相连;采样保持 模块(10)的输入端与管脚CS、第二比较器(2)的正相输入端、功率晶体管(M1)的源极相连; 采样保持模块(10)的控制端与恒流精度补偿模块(9)的第二输出端相连;低通滤波器(11) 的输出端与压控振荡器(12)的输入端、第二比较器(2)的负相输入端相连;压控振荡器(12) 的输出端与与逻辑门(G3)的第一输入端相连;定时器(13)的输出端与与逻辑门(G3)的第二 输入端相连; 定时器 (13) 的输入端与第一RS锁存器 (G1) 的R输入端、第一比较器 (1) 的输出 端相连: 与逻辑门(G3)的输出端与第二RS锁存器(G2)的S输入端相连: 第二比较器(2)的输 出端与第二RS锁存器(G2)的R输入端相连;第二RS锁存器(G2)的输出端与驱动模块(3)的输 入端相连。

- 2.根据权利要求1所述的开关电源的控制电路,其特征在于:所述采样保持模块(10)包括第一电流镜像单元(15)、第二电流镜像单元(16)、第一开关(S1)、第二开关(S2)、第三开关(S3)、第四开关(S4)、第二晶体管(M2)、第一电容(C1)、第一电阻(R1)、第一运放器(14)、第一反相器(G4),所述第一开关(S1)、第三开关(S3)的控制端受控于恒流精度补偿模块(9)的第二输出端的输出信号;第一运放器(14)的控制端所接电位与第一开关(S1)、第三开关(S3)的控制端所接信号相同;第二开关(S2)、第四开关(S4)的控制端所接信号与所述第一开关(S1)、第三开关(S3)的控制端所接信号相反;第一运放器(14)的正相输入端与第一开关(S1)的第一端、第一电容(C1)相连;第一运放器(14)的负相输入端与第三开关(S3)的第一端、第四开关(S4)的第一端相连;第一运放器(14)的输出端与第一电流镜像单元(15)的输入端、第二开关(S2)的第一端相连;第一开关(S1)的第二端与第一电流镜像单元(15)的输出端相连;第二开关(S2)的第二端与第二晶体管(M2)的栅极相连;第三开关(S3)的第二端连接至管脚CS;第四开关(S4)的第二端与第一电阻(R1)、第二晶体管(M2)的源极相连;第二晶体管(M2)的源极相连;第二晶体管(M2)的漏极与第二电流镜像单元(16)的输入端相连;第二电流镜像单元(16)的输出端连接至所述恒流控制模块(8)的第五输入端。

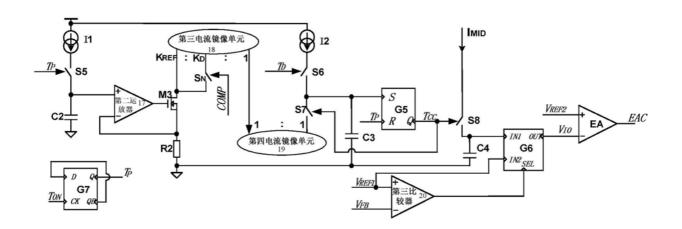

- 3.根据权利要求1所述的开关电源的控制电路,其特征在于:所述恒流控制模块(8)包括第一恒流源(I1)、第二恒流源(I2)、第五开关(S5)、第六开关(S6)、第七开关(S7)、第八开关(S8)、开关(S<sub>N</sub>)、第二电容(C2)、第三电容(C3)、第四电容(C4)、第二电阻(R2)、第三晶体管(M3)、第二运放器(17)、第三比较器(20)、第三RS锁存器(G5)、二选一数据选择器(G6)、第一D触发器(G7)和误差放大器(EA),所述误差放大器(EA)的输出端为所述恒流控制模块(8)的输出端;误差放大器(EA)的正相端与基准电压端V<sub>REF2</sub>相连;误差放大器(EA)的负相端与二选一数据选择器(G6)的输出端相连;二选一数据选择器(G6)的IN1输入端与第八开关(S8)的第一端、第四电容(C4)相连;二选一数据选择器(G6)的IN2输入端与第三比较器(20)

的正相输入端、基准电压端VREF1相连;二选一数据选择器(G6)的SEL选择端与第三比较器(20)的输出端相连;第三比较器(20)的负相输入端连接至管脚FB;第八开关(S8)的第二端连接至所述采样保持模块(10)的输出端;第八开关(S8)的控制端与第七开关(S7)的控制端、第三RS锁存器(G5)的Q输出端相连;第三RS锁存器(G5)的R输入端与第五开关(S5)的控制端、第一D触发器(G7)的Q输出端相连;第三RS锁存器(G5)的S输入端与第六开关(S6)的第一端、第七开关(S7)的第一端、第三电容(C3)相连;第六开关(S6)的第二端与第二电流源(I2)相连;第六开关(S6)的控制端连接至第一RS锁存器(G1)的QB输出端;第七开关(S7)的第二端与第四电流镜像单元(19)的输出端相连;第四电流镜像单元(19)的输入端与第三电流镜像单元(18)的第一输入第与第三晶体管(M3)的漏极、开关(SN)的第一端相连;第三电流镜像单元(18)的第二输入第与开关(SN)的第二端相连;开关(SN)受控于所述恒流精度补偿模块(9)的第一输出端信号;第三晶体管(M3)的源极与第二电阻(R2)、第二运放器(17)的负相输入端相连;第三晶体管(M3)的栅极与第二运放器(17)的输出端相连;第二运放器(17)的正相输入端与第五开关(S5)的第一端、第二电容(C2)相连;第五开关(S5)的第二端与第一恒流源(I1)相连。

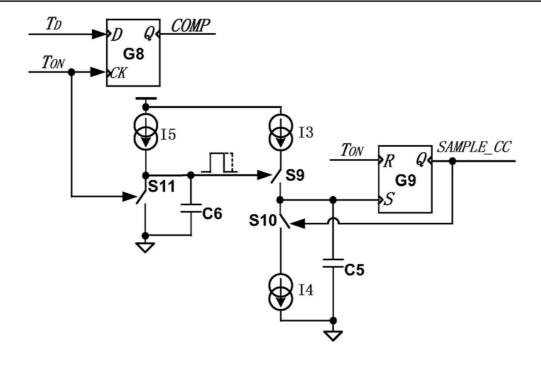

4.根据权利要求1所述的开关电源的控制电路,其特征在于:所述恒流精度补偿模块(9)包括第二D触发器(G8)、第四RS锁存器(G9)、第三恒流源(I3)、第四恒流源(I4)、第五恒流源(I5)、第九开关(S9)、第十开关(S10)、第十一开关(S11)、第五电容(C5)和第六电容(C6),第二D触发器(G8)的D输入端与第一RS锁存器(G1)的QB输出端相连;第二D触发器(G8)的Q输出端与所述恒流控制模块(8)相连;第二D触发器(G8)的CK输入端与第十一开关(S11)的控制端、第四RS锁存器(G9)的R输入端相连并连接至所述驱动模块(3)的输出端;第九开关(S9)的控制端与第十一开关(S11)的第一端、第五恒流源(I5)、第六电容(C6)的第一端相连;第九开关(S9)的第一端与第三恒流源(I3)相连;第九开关(S9)的第二端与第十开关(S10)的第一端、第四RS锁存器(G9)的S输入端以及第五电容(C5)的第一端相连;第十开关(S10)的第二端与第四恒流源(I4)相连;第四RS锁存器(G9)的Q输出端连接至所述采样保持模块(10);第十一开关(S11)的第二端、第五电容(C5)的第二端以及第六电容(C6)的第二端连接至电源地。

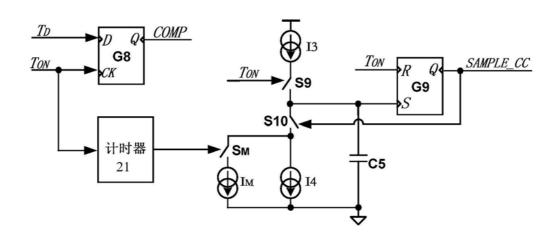

5.根据权利要求1所述的开关电源的控制电路,其特征在于:所述恒流精度补偿模块(9)包括第二D触发器(G8)、第四RS锁存器(G9)、计时器(21)、第三恒流源(I3)、第三恒流源(I4)、第九开关(S9)、第十开关(S10)、开关(S<sub>M</sub>)、第五电容(C5)和电流源(I<sub>M</sub>),所述第二D触发器(G8)的D输入端和与所述第一RS锁存器(G1)的QB输出端相连;第二D触发器(G8)的CK输入端与第九开关(S9)的控制端、第四RS锁存器(G9)的R输入端以及计时器(21)的输入端相连并连接至所述驱动模块(3)的输出端;第二D触发器(G8)的Q输出端与所述恒流控制模块(8)相连;第九开关(S9)的第一端与第三恒流源(I3)相连;第九开关(S9)的第二端与第十开关(S10)的第一端、第五电容(C5)、第四RS锁存器(G9)的S输入端相连;第十开关(S10)的第二端与第四恒流源(I4)、开关(S<sub>M</sub>)的第一端相连;开关(S<sub>M</sub>)的第二端与电流源(I<sub>M</sub>)相连;开关(S<sub>M</sub>)的控制端与计时器(21)的输出端相连。

6.利用权利要求1所述控制电路实现开关电源的控制方法,其特征在于:由恒流控制模块(8)根据FB管脚和CS管脚上的反馈信息,产生并输出控制开关电源输出电流的控制信号,适应性地调节功率晶体管(M1)的开通占空比,调整电源系统的输出电流I<sub>0</sub>为恒定值;恒流

精度补偿模块(9)根据FB管脚和CS管脚上的反馈信息,适应性地调节恒流控制模块(8)和采样保持模块(10)的电路计算参数,使输出恒流精度不受工作模式变化和/或输入条件变化的影响;定时器(13)判定FB管脚上电压VFB到达谷值的时刻;压控振荡器(12)根据恒流控制模块(8)输出的控制信号和定时器(13)对输出信号,调节功率晶体管(M1)的开关频率,使开关电源工作于QR模式或CCM模式,且当输出电压变化时,QR模式保持不变或CCM模式电流连续的深度保持相近。

7.根据权利要求6所述的开关电源的控制方法,其特征在于:所述采样保持模块(10)包括第一电流镜像单元(15)、第二电流镜像单元(16)、第一开关(S1)、第二开关(S2)、第三开关(S3)、第四开关(S4)、第二晶体管(M2)、第一电容(C1)、第一电阻(R1)、第一运放器(14)以及第一反相器(G4),当第一开关(S1)、第三开关(S3)闭合时,第一运放器(14)工作于跨导模式,即第一电流镜像单元(15)的输出电流 $I_{C1}$ 给第一电容(C1)充电, $I_{C1}$ 表示为: $I_{C1}$ =K1\*( $V_{C1}$ - $V_{CS}$ )\* $G_M$ ,其中,K1为所述第一电流镜像单元(15)的电流镜像比例, $V_{C1}$ 为第一电容(C1)上电压, $V_{CS}$ 为控制电路CS管脚上电压, $V_{CM}$ 为第一运放器(14)工作于跨导模式时的跨导,

$$V_{C1}$$

表示为:  $V_{C1} = V_{CS} - \frac{C\frac{dV_{CS}}{dt}}{G_M \times K1}$

其中,C为所述第一电容(C1)的容值;

当C/GM趋近于0时,得到Vc1=Vcs;

当第一开关(S1)、第三开关(S3)打开时,第二开关(S2)、第四开关(S4)闭合,第一运放器(14)工作于跟随模式,将第一电容(C1)上电压Vc1传输至第二晶体管(M2)的源极,并通过第一电阻(R1)、第二晶体管(M2)和第二电流镜像单元(16)转换并镜像为电流I<sub>MID</sub>,输出至恒流控制模块(8)的第五输入端。

8.根据权利要求6所述的开关电源的控制方法,其特征在于:所述恒流控制模块(8)包 括第一恒流源(I1)、第二恒流源(I2)、电流源I<sub>M</sub>、第五开关(S5)、第六开关(S6)、第七开关 (S7)、第八开关(S8)、开关SN、第二电容(C2)、第三电容(C3)、第四电容(C4)、第二电阻(R2)、 第三晶体管(M3)、第二运放器(17)、第三比较器(20)、第三RS锁存器(G5)、二选一数据选择 器(G6)、第一D触发器(G7)和误差放大器(EA),所述第一D触发器(G7)连接构成二分频电路, 产生逐个周期的开关周期信号Tp,第五开关(S5)受控于信号Tp,闭合时第一恒流源(I1)对第 二电容(C2)充电,将所得电压通过第二运放器(17)和第二电阻(R2)产生电流,且比例镜像 并输出至第四电流镜像单元(19),第三电流镜像单元(18)的输入电流与输出电流的比例为 (Kref+Kp):1,Kref和Kp为常数,Kp的值受控于开关Sn的开关状态,第四电流镜像单元(19)的输 入电流与输出电流的比例为1:1;第六开关(S6)受控于信号TD,闭合时第二恒流源(I2)对第 三电容(C3)充电并在充电结束时保持所得电压;第七开关(S7)受控于第三RS锁存器(G5)的 Q输出端信号,在信号Te开始为高电平,即开关周期开始时由第四电流镜像单元(19)的输出 电流对第三电容(C3)放电;当第三电容(C3)上电压达到第三RS锁存器(G5)的翻转阈值时, 第三RS锁存器(G5)的Q输出端信号翻转为低电平,放电过程结束并产生时间信号Tcc;第八开  $\dot{\xi}$  (S8) 受控于时间信号 $T_{CC}$ ,闭合时电流 $I_{MID}$ 对第四电容(C4) 充电,并将电压 $V_{C4}$ 传输至二选 一数据选择器 (G6) 的IN1输入端; 第四电容 (C4) 的电压VC4表示为:

$$V_{C4} = V_{CS\_MID} * (K_{REF} + K_D) * \frac{T_D}{T_P};$$

二选一数据选择器 (G6) 的 IN2输入端与基准电压端V<sub>REF1</sub>相连,V<sub>REF1</sub>为控制电路内部电路产生,二选一数据选择器 (G6) 的 SEL端电位选择 IN1端输入数据或者 IN2端输入数据作为输出数据,SEL端电位受控于第三比较器 (20) 的输出信号;当FB管脚上电压V<sub>FB</sub>小于V<sub>REF1</sub>时,二选一数据选择器 (G6) 的 SEL端电位选择 IN2端数据,V<sub>REF1</sub>端输出至误差放大器 (EA) 的负相输入端,误差放大器 (EA) 的正相输入端与基准电压端V<sub>REF2</sub>相连,其中,V<sub>REF2</sub>>V<sub>REF1</sub>,此时,误差放大器 (EA) 输出高电压值,逐个开关周期的变压器 (T1) 原边电流峰值快速上升,传递至开关电源输出级的能量快速增大,开关电源快速启动;当FB管脚电压V<sub>FB</sub>大于V<sub>REF1</sub>时,二选一数据选择器 (G6) 的 SEL端电位选择 IN1端数据,第四电容 (C4) 电压V<sub>C4</sub>输出至误差放大器 (EA) 的负相输入端,工作状态平衡时,

$$V_{CS\_MID} * (K_{REF} + K_D) * \frac{T_D}{T_P} = V_{C4} = V_{REF2},$$

输出电流Io表示为:

$$I_O = \frac{N_P}{N_S} * \frac{V_{CS\_MID}}{R_{CS}} * \frac{T_D}{T_P} = \frac{N_P}{N_S} * \frac{1}{R_{CS}} * \frac{T_D}{T_P} * \frac{V_{REF2}}{K_{REF} + K_D} ,$$

其中 $\frac{N_P}{N_S}$ 为变压器(T1)原次边匝数比, $R_{CS}$ 为原边电流检测电阻阻值,

对于选定 $\frac{N_P}{N_S}$ 和Rcs的开关电源,输出电流 $I_0$ 为恒定值,

其中,所述变压器(T1)、原边电流检测电阻Rcs和所述开关电源的控制电路包含于所述 开关电源中,变压器(T1)原边的第一端连接至所述开关电源的控制电路中的功率晶体管 (M1)的漏极;变压器(T1)的原边的第二端连接至所述开关电源的输入电压V<sub>IN</sub>;原边电流检 测电阻Rcs的第一端连接至所述开关电源的控制电路中的功率晶体管(M1)的源极;原边电流 检测电阻Rcs的第二端连接至电源地;变压器(T1)的次边连接至所述开关电源的输出级。

- 9.根据权利要求8所述的开关电源的控制方法,其特征在于:第一恒流源(I1)和第二恒流源(I2)的电流相等,第二电容(C2)、第三电容(C3)与第四电容(C4)的容值相等。

- 10.根据权利要求8所述的开关电源的控制方法,其特征在于:恒流精度补偿模块(9)包括第二D触发器(G8)、第四RS锁存器(G9)、第三恒流源(I3)、第四恒流源(I4)、第五恒流源(I5)、第九开关(S9)、第十开关(S10)、第十一开关(S11)、第五电容(C5)和第六电容(C6),第二D触发器(G8)在功率晶体管(M1)导通开始时刻检测管脚FB上电压VFB是否降低至阈值VTH以下,即所述变压器(T1)消磁是否结束,以此输出模式补偿信号COMP至恒流控制模块(8),进而调节比例参数KD,达到补偿不同工作模式间输出恒流差值的效果;第五恒流源(I5)与第十一开关(S11)、第六电容(C6)构成下降沿延时电路,调节计算管脚CS上电压Vcs采样时刻所基于的脉宽长度,进而调节采样Vcs的时刻距离功率晶体管(M1)实际导通中点的位置,从而补偿不同输入电压间输出恒流差值。

# 开关电源的控制电路及其方法

#### 技术领域

[0001] 本发明涉及一种开关电源的控制电路及其方法,适用于电源管理集成电路系统,属于功率半导体技术领域。

## 背景技术

[0002] 反激式开关电源的输出电流可以表示为:  $I_o = \frac{N_P}{N_S} * \frac{I_{PRI\_PK} + I_{PRI\_O}}{2} * \frac{T_D}{T_P}$ , 其中,

$\frac{N_P}{N_S}$ 为变压器原次边匝数比, $I_{PRI\_PK}$ 为变压器励磁期间的原边电流峰值, $I_{PRI\_O}$ 为变压器励磁期间的原边电流初值, $T_D$ 为变压器消磁时间, $T_D$ 为反激式开关电源的单个开关周期时间。该表达式亦可以表示为: $I_O = \frac{N_P}{N_S} * \frac{V_{CS\_PK} + V_{CS\_O}}{2R_{CS}} * \frac{T_D}{T_P}$ ,其中, $R_{CS}$ 为原边电流检测电阻阻值,

$V_{CS\_PK}$ 为变压器励磁期间 $R_{CS}$ 两端电压的峰值, $V_{CS\_0}$ 为变压器励磁期间 $R_{CS}$ 两端电压的初值。当反激式开关电源工作于非连续电流模式 (DCM) 时,由于 $V_{CS\_0}$ 为0,输出电流则可以简化表示

为:  $I_o = \frac{N_P}{N_S} * \frac{V_{CS\_PK}}{2R_{CS}} * \frac{T_D}{T_P}$ 。传统的恒流控制方式即为利用该简化表达式,选定变压器原次

边匝数比 $\frac{N_P}{N_S}$ 和原边电流检测电阻阻值 $R_{CS}$ 后,保持每个开关周期内的 $V_{CS\_PK}$ 为固定值,再调制 开 关 周 期  $T_P$  与 变 压 器 消 磁 时 间  $T_D$  之 间 的 比 例 固 定 为 K ,使 得 输 出 电 流  $I_O = \frac{N_P}{N_S} * \frac{V_{CS\_PK}}{2R_{CS}} * \frac{1}{K}$ ,从而达到控制输出电流恒定的目的。

[0003] 上述传统的输出恒流控制方式一个明显的不足点是,当反激式开关电源工作于连续电流模式 (CCM),即 $V_{CS\_0}$ 不为0时,该恒流控制方式失效。而且即使对于工作于DCM模式的反激式开关电源,该恒流控制方式要求 $T_P$ 与 $T_D$ 之间的比例严格固定,与DCM模式中的谷底导通 (QR)模式亦不兼容。如此,采用上述恒流控制方式的电源具有效率低的缺点,且为了保证不工作于CCM模式,变压器设计亦受到限制。

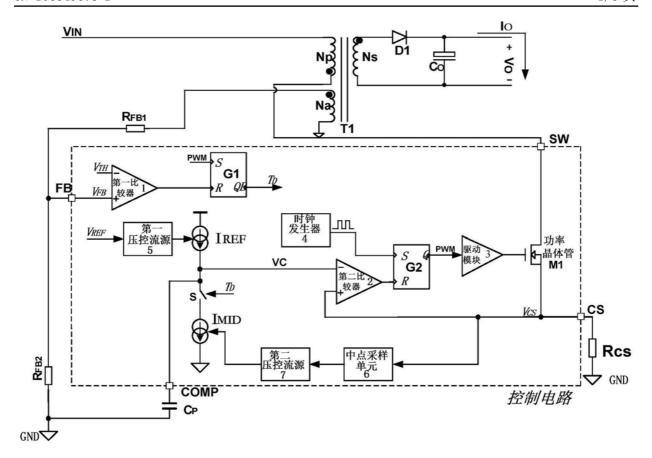

[0004] 其系统结构如图1所示。其主要包含:变压器T1、二极管D1、电容Co、电阻R<sub>FB1</sub>、电阻R<sub>FB2</sub>、电阻R<sub>CS</sub>和控制电路,其连接关系为:变压器T1的辅边Na与电阻R<sub>FB1</sub>第一端相连;电阻R<sub>FB1</sub>第二端与电阻R<sub>FB2</sub>第一端以及控制电路的FB管脚相连;电阻R<sub>FB2</sub>第二端与电源地相连;变压器T1的原边N<sub>P</sub>与控制电路的SW管脚相连;变压器T1的次边Ns与二极管D1阳极相连;二极管D1阴极与输出电容Co相连;电阻R<sub>CS</sub>的第一端与控制电路的CS管脚相连;电阻R<sub>CS</sub>的第二端与电源地相连;电容C<sub>P</sub>的第一端与控制电路的COMP管脚相连;电容C<sub>P</sub>的第二端与电源地相连;所述控制电路包含:第一比较器1、RS锁存器G1、第一压控流源5、电流源 $I_{REF}$ 、第二压控流源7、电流源 $I_{MID}$ 、开关S、中点采样单元6、第二比较器2、时钟发生器4、RS锁存器G2、驱动模块3以及功率晶体管M1,第一比较器1正相端与FB管脚相连,第一比较器1负相端与基准电压 $V_{TH}$

相连;第一比较器1的输出端与RS锁存器G1的R输入端相连;RS锁存器G1的S输入端与驱动模块3的输出端以及功率晶体管M1的栅极相连;RS锁存器G1的Q输出端与开关S的控制端相连;开关S的第一端与电流源I<sub>REF</sub>以及第二比较器2的负相端相连;电流源I<sub>REF</sub>的控制端与第一压控流源5的输出端相连;第一压控流源5的输入端与基准电压V<sub>REF</sub>相连;开关S的第二端与电流源I<sub>MID</sub>相连;电流源I<sub>MID</sub>的控制端与第二压控流源7的输出端相连;第二压控流源7的输入端与中点采样单元6的输出端相连;中点采样单元6的输入端与管脚CS、功率晶体管M1的源极、第二比较器2的正相端相连;第二比较器2的输出端与RS锁存器G2的R输入端相连;RS锁存器G2的S输入端与时钟发生器4的输出端相连;RS锁存器G2的输出端与驱动模块3的输入端相连;功率晶体管M1的漏极与管脚SW相连;其工作原理为:中点采样单元6检测功率晶体管M1导通中点时刻的CS管脚上的电压V<sub>CS\_MID</sub>,通过压控电流源产生电流I<sub>MID</sub>,且I<sub>MID</sub>=K<sub>C</sub>\*V<sub>CS\_MID</sub>,其中K<sub>G</sub>为控制电路内部设计参数,此外,第一比较器1将FB管脚上的电压V<sub>FB</sub>与基准电压V<sub>TH</sub>相比较,获得逐个开关周期的变压器消磁时间T<sub>D</sub>。在非消磁时间内,基准电流I<sub>REF</sub>给电容C<sub>P</sub>充电,在消磁时间内,则电流I<sub>REF</sub>—I<sub>MID</sub>给电容C<sub>P</sub>充电,逐个周期累加直至电容C<sub>P</sub>上电压稳定为有限量V<sub>C</sub>,此时I<sub>REF</sub>\*T<sub>P</sub>—I<sub>MID</sub>\*T<sub>D</sub>收敛为0,即:I<sub>REF</sub>\*T<sub>P</sub>=K<sub>C</sub>\*V<sub>CS\_MID</sub>\*T<sub>D</sub>,根据反激式开关电源

的输出电流表达式,此时输出电流可以表示为:  $I_o = \frac{N_P}{N_S} * \frac{I_{REF}}{R_{CS} * K_G}$ ,其中 $\frac{N_P}{N_S}$ 为变压器原

次边匝数比, $R_{CS}$ 为原边电流检测电阻阻值,对于选定 $\frac{N_P}{N_S}$ 和 $R_{CS}$ 的开关电源来说,输出电流为恒定值。

[0005] 上述工作方式虽然兼容了CCM和QR工作模式,但是所需的电容CcM的容值较大,难以集成至控制电路内部,增加了控制电路管脚和电源系统的成本。

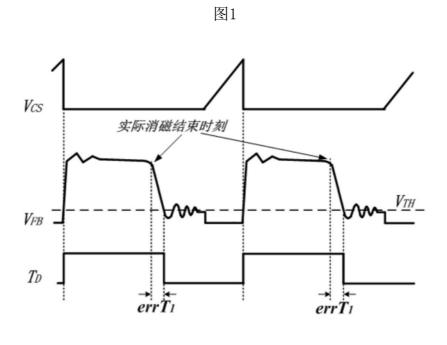

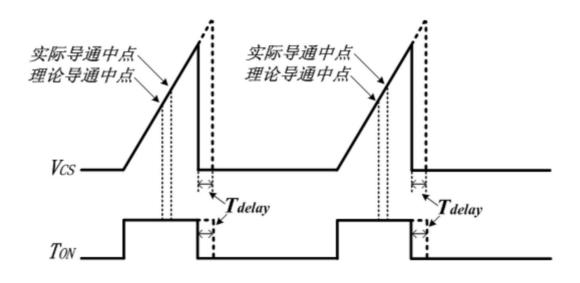

[0006] 进一步地,该输出恒流控制方式通过比较FB管脚上电压 $V_{FB}$ 和基准值 $V_{TH}$ 来检测变压器消磁时间 $T_D$ ,其示例波形如图2a所示为工作于DCM模式时的波形,消磁结束时刻由于进入谐振区段, $V_{FB}$ 下降斜率相对缓慢,检测到的消磁时间 $T_D$ 实际上包含了一半的谐振周期时间;图2b所示为工作于CCM模式时的波形,由于次边输出二极管电流未消磁至0,无谐振周期, $V_{FB}$ 下降斜率较为快速,检测到的消磁时间 $T_D$ 基本等于实际消磁时间。那么,CCM和DCM模式下检测的消磁时间与实际消磁时间之间的差不同,进而使得CCM和DCM模式下的输出电流不同。

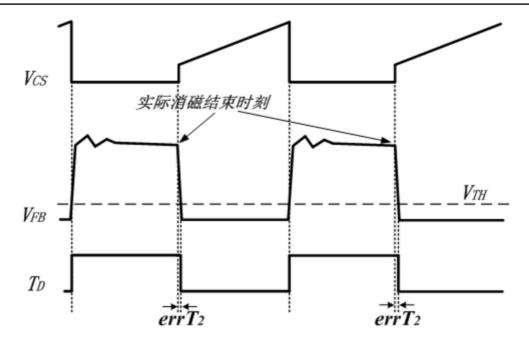

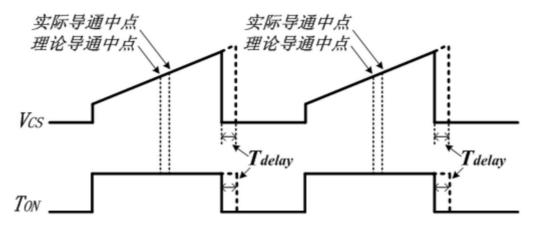

[0007] 进一步地,该输出恒流控制方式通过功率晶体管M1导通时间Ton来产生采样信号,检测Vcs\_MID,功率晶体管M1存在关断延时Tdelay,使得检测到的Vcs\_MID与实际的Vcs\_MID间存在偏差,图3a所示为较高输入电压下的工作波形,由于CS管脚上电压Vcs上升斜率较大,偏差值较大,图3b所示为较低输入电压下的工作波形,由于CS管脚上电压Vcs上升斜率较小,偏差值较小,进而使得不同的输入电压下的输出电流不同。

[0008] 综上所述,上述工作方式不仅增加了控制电路管脚和电源系统的设计成本,而且还具有工作模式间输出电流差异大、输入电压调整率低、恒流精度差等缺点。因此,急需设计一种新的兼容CCM和QR模式的输出恒流控制方式,消除其缺点。

#### 发明内容

[0009] 本发明的目的是克服现有技术存在的不足,提供一种既支持CCM和QR工作模式,又

不增加电源系统成本,且输出恒流精度高的开关电源控制电路及其方法。

[0010] 本发明的目的通过以下技术方案来实现:

开关电源的控制电路,特点是:包含第一比较器、第一RS锁存器、恒流控制模块、恒 [0011] 流精度补偿模块、采样保持模块、低通滤波器、第二比较器、第二RS锁存器、压控振荡器、定 时器、与逻辑门、驱动模块以及功率晶体管,所述恒流控制模块的第一输入端与第一RS锁存 器的Q输出端、恒流精度补偿模块的第一输入端相连;恒流控制模块的第二输入端与管脚 FB、第一比较器的正相输入端相连:恒流控制模块的第三输入端与驱动模块的输出端、第一 RS锁存器的S输入端、功率晶体管的栅极、恒流精度补偿模块的第二输入端相连:恒流控制 模块的第四输入端与恒流精度补偿模块的第一输出端相连;恒流控制模块的第五输入端与 采样保持模块的输出端相连:恒流控制模块的输出端与低通滤波器的输入端相连;采样保 持模块的输入端与管脚CS、第二比较器的正相输入端、功率晶体管的源极相连;采样保持模 块的控制端与恒流精度补偿模块的第二输出端相连;低通滤波器的输出端与压控振荡器的 输入端、第二比较器的负相输入端相连;压控振荡器的输出端与与逻辑门的第一输入端相 连;定时器的输出端与与逻辑门的第二输入端相连;定时器的输入端与第一RS锁存器的R输 入端、第一比较器的输出端相连;与逻辑门的输出端与第二RS锁存器的S输入端相连;第二 比较器的输出端与第二RS锁存器的R输入端相连;第二RS锁存器的输出端与驱动模块的输 入端相连。

[0012] 进一步地,上述的开关电源的控制电路,其中,所述采样保持模块包括第一电流镜像单元、第二电流镜像单元、第一开关、第二开关、第三开关、第四开关、第二晶体管、第一电容、第一电阻、第一运放器、第一反相器,所述第一开关、第三开关的控制端受控于恒流精度补偿模块的第二输出端的输出信号;第一运放器的控制端所接电位与第一开关、第三开关的控制端所接信号相同;第二开关、第四开关的控制端所接信号与所述第一开关、第三开关的控制端所接信号相反;第一运放器的正相输入端与第一开关的第一端、第一电容相连;第一运放器的负相输入端与第三开关的第一端、第四开关的第一端相连;第一运放器的输出端与第一镜像单元的输出端、第二开关的第一端相连;第一开关的第二端与第一电流镜像单元的输入端相连;第二开关的第二端与第二电流镜像单元的输入端相连;第二品体管的漏极与第二电流镜像单元的输入端相连;第二电流镜像单元的输出端连接至所述恒流控制模块的第二电流镜像单元的输入端相连;第二电流镜像单元的输出端连接至所述恒流控制模块的第五输入端。

[0013] 进一步地,上述的开关电源的控制电路,其中,所述第一电流镜像单元的输出电流与输入电流比例为1:1,所述第二电流镜像单元的输出电流与输入电流比例为1:1。

[0014] 进一步地,上述的开关电源的控制电路,其中,所述恒流控制模块包括第一恒流源、第二恒流源、电流源、第五开关、第六开关、第七开关、第八开关、开关SN、第二电容、第三电容、第二电阻、第三晶体管、第二运放器、第三比较器、第三RS锁存器、二选一数据选择器、第一D触发器和误差放大器,所述误差放大器的输出端为所述恒流控制模块的输出端;误差放大器的正相端与基准电压端VREF2相连;误差放大器的负相端与二选一数据选择器的输出端相连;二选一数据选择器的IN1输入端与第八开关的第一端、第四电容相连;二选一数据选择器的IN2输入端与第三比较器的正相输入端、基准电压端VREF1相连;二选一数据选择器的SEL选择端与第三比较器的输出端相连;第三比较器的负相输入端连接至管

脚FB;第八开关的第二端连接至所述采样保持模块的输出端;第八开关的控制端与第七开关的控制端、第三RS锁存器的Q输出端相连;第三RS锁存器的R输入端与第五开关的控制端、第一D触发器的Q输出端相连;第三RS锁存器的S输入端与第六开关的第一端、第七开关的第一端、第三电容相连;第六开关的第二端与第二电流源相连;第六开关的控制端连接至第一比较器的输出端;第七开关的第二端与第四电流镜像单元的输出端相连;第四电流镜像单元的输出端相连;第三电流镜像单元的第一输入端与第三晶体管的漏极、开关SN的第一端相连;第三电流镜像单元的第二输入端与开关SN的第二端相连;开关SN受控于所述恒流精度补偿模块的第一输出端信号;第三晶体管的源极与第二电阻、第二运放器的负相输入端相连;第三晶体管的栅极与第二运放器的输出端相连;第二运放器的正相输入端与第五开关的第一端、第二电容相连;第五开关的第二端与第一恒流源相连。

[0015] 进一步地,上述的开关电源的控制电路,其中,所述恒流精度补偿模块包括第二D触发器、第四RS锁存器、第三恒流源、第四恒流源、第五恒流源、第九开关、第十开关、第十一开关、第五电容和第六电容,第二D触发器的D输入端与第一比较器的输出端相连;第二D触发器的Q输出端与所述恒流控制模块的开关SN相连;第二D触发器的CK输入端与第十一开关的控制端、第四RS锁存器的R输入端相连并连接至所述驱动模块的输出端;第九开关的控制端与第十一开关的第一端、第五恒流源、第六电容的第一端相连;第九开关的第一端与第三恒流源相连;第九开关的第二端与第十开关的第一端、第四RS锁存器的Q输出端连接至所述采样保持模块;第十一开关的第二端与第四恒流源相连;第四RS锁存器的Q输出端连接至所述采样保持模块;第十一开关的第二端、第五电容的第二端以及第六电容的第二端连接至电源地。

[0016] 进一步地,上述的开关电源的控制电路,其中,所述恒流精度补偿模块包括第二D触发器、第四RS锁存器、计时器、第三恒流源、第三恒流源、第九开关、第十开关、开关SM、第五电容和第六电容,所述第二D触发器的D输入端和与所述第一比较器的输出端相连;第二D触发器的CK输入端与第九开关的控制端、第四RS锁存器的R输入端以及计时器的输入端相连并连接至所述驱动模块的输出端;第二D触发器的Q输出端与所述恒流控制模块的开关SN的控制端相连;第九开关的第一端与第三恒流源相连;第九开关的第二端与第十开关的第一端、第五电容、第四RS锁存器的S输入端相连;第十开关的第二端与第四恒流源、开关的第一端相连;开关的第二端与电流源相连;开关的输入端与计时器的输出端相连。

[0017] 本发明开关电源的控制方法,其中,由恒流控制模块根据FB管脚和CS管脚上的反馈信息,产生并输出控制开关电源输出电流的控制信号,适应性地调节功率晶体管的开通占空比,调整电源系统的输出电流Io为恒定值;恒流精度补偿模块根据FB管脚和CS管脚上的反馈信息,适应性地调节恒流控制模块和采样保持模块的电路计算参数,使输出恒流精度不受工作模式变化和/或输入条件变化的影响;定时器判定FB管脚上电压VFB到达谷值的时刻;压控振荡器根据恒流控制模块输出的控制信号和定时器对输出信号,调节功率晶体管的开关频率,使开关电源工作于QR模式或CCM模式,且当输出电压变化时,QR模式保持不变或CCM模式电流连续的深度保持相近。

[0018] 再进一步地,上述的开关电源的控制方法,其中,所述采样保持模块包括第一电流镜像单元、第二电流镜像单元、第一开关、第二开关、第三开关、第四开关、第二晶体管、第一

电容、第一电阻、第一运放器以及第一反相器,当第一开关、第三开关闭合时,第一运放器工作于跨导模式,即第一电流镜像单元的输出电流 $I_{C1}$ 给第一电容充电, $I_{C1}$ 表示为:  $I_{C1}$ =K1\* ( $V_{C1}$ - $V_{CS}$ )\* $G_M$ ,其中, $V_{C1}$ 为第一电容上电压, $V_{CS}$ 为控制电路CS管脚上电压, $G_M$ 为第一运放器工作于跨导模式时的跨导,

[0019]

$$V_{C1}$$

表示为:  $V_{C1} = V_{CS} - \frac{C \frac{dV_{CS}}{dt}}{G_M \times K1}$ ,

[0020] 当C/G<sub>M</sub>趋近于0时,得到V<sub>C1</sub>=V<sub>CS</sub>;

[0021] 当第一开关、第三开关打开时,第二开关、第四开关闭合,第一运放器工作于跟随模式,将第一电容上电压Vc1传输至第二晶体管的源极,并通过第一电阻转换为电流I<sub>MID</sub>,镜像并输出至恒流控制模块的第五输入端。

[0022] 再进一步地,上述的开关电源的控制方法,其中,所述恒流控制模块包括第一恒流源、第二恒流源、电流源、第五开关、第六开关、第七开关、第八开关、开关、第二电容、第三电容、第三电容、第二电阻、第三晶体管、第二运放器、第三比较器、第三RS锁存器、二选一数据选择器、第一D触发器和误差放大器,所述第一D触发器连接构成二分频电路,产生逐个周期的开关周期信号Tp,第五开关受控于信号Tp,闭合时第一恒流源对第二电容充电,将所得电压通过第二运放器和第二电阻产生电流,且比例镜像并输出至第四电流镜像单元,第三电流镜像单元的输入电流与输出电流的比例为(KREF+KD):1,KREF和KD为常数,KD的值受控于开关SN的开关状态,第四电流镜像单元(19)的输入电流与输出电流的比例为1:1;第六开关受控于信号Tp,闭合时第二恒流源对第三电容充电并在充电结束时保持所得电压;第七开关受控于第三RS锁存器的Q输出端信号,在信号Tp开始为高电平,即开关周期开始时由第四电流镜像单元的输出电流对第三电容放电;当第三电容上电压达到第三RS锁存器的翻转阈值时,第三RS锁存器的Q输出端信号翻转为低电平,放电过程结束并产生时间信号Tcc;第八开关受控于时间信号Tcc,闭合时电流IMD对第四电容充电,并将电压Vc4传输至二选一数据选

择器的IN1输入端;第四电容的电压

$$V_{C4}$$

表示为:  $V_{C4} = V_{CS\_MID} * (K_{REF} + K_D) * \frac{T_D}{T_P}$ ;

[0023] 二选一数据选择器的IN2输入端与基准电压端V<sub>REF1</sub>相连,V<sub>REF1</sub>为控制电路内部电路产生,二选一数据选择器的SEL端电位选择IN1端输入数据或者IN2端输入数据作为输出数据,SEL端电位受控于第三比较器的输出信号;当FB管脚上电压V<sub>FB</sub>小于V<sub>REF1</sub>时,二选一数据选择器的SEL端电位选择IN2端数据,V<sub>REF1</sub>端输出至误差放大器的负相输入端,误差放大器的正相输入端与基准电压端V<sub>REF2</sub>相连,其中,V<sub>REF2</sub>>V<sub>REF1</sub>,此时,误差放大器输出高电压值,逐个开关周期的变压器原边电流峰值快速上升,传递至电源输出级的能量快速增大,开关电源快速启动;当FB管脚电压V<sub>FB</sub>大于V<sub>REF1</sub>时,二选一数据选择器的SEL端电位选择IN1端数据,第四电容电压V<sub>C4</sub>输出至误差放大器的负相输入端,工作状态平衡时,

[0024]

$$V_{CS\_MID} * (K_{REF} + K_D) * \frac{T_D}{T_P} = V_{C4} = V_{REF2}$$

,

[0025] 输出电流 I<sub>0</sub>表示为:

$$[0026] \qquad I_O = \frac{N_P}{N_S} * \frac{V_{CS\_MID}}{R_{CS}} * \frac{T_D}{T_P} = \frac{N_P}{N_S} * \frac{1}{R_{CS}} * \frac{T_D}{T_P} * \frac{V_{REF2}}{K_{REF} + K_D} \; ,$$

[0027] 其中 $\frac{N_P}{N_S}$ 为变压器原次边匝数比, $R_{CS}$ 为原边电流检测电阻阻值,

[0028] 对于选定 $\frac{N_P}{N_S}$ 和 $R_{CS}$ 的开关电源来说,输出电流 $I_0$ 为恒定值。

[0029] 再进一步地,上述的开关电源的控制方法,其中,第一恒流源和第二恒流源的电流相等,第二电容、第三电容与第四电容的容值相等。

[0030] 再进一步地,上述的开关电源的控制方法,其中,所述恒流精度补偿模块包括第二D触发器、第四RS锁存器、第三恒流源、第四恒流源、第五恒流源、第九开关、第十开关、第十一开关、第五电容和第六电容,第二D触发器在功率晶体管导通开始时刻检测管脚FB上电压VFB是否降低至阈值VTH以下,即变压器消磁是否结束,以此输出模式补偿信号COMP至恒流控制模块,进而调节比例参数KD,达到补偿不同工作模式间输出恒流差值的效果;第五恒流源与第十一开关、第六电容构成下降沿延时电路,调节计算管脚CS上电压Vcs采样时刻所基于的脉宽长度,进而调节采样Vcs的时刻距离功率晶体管实际导通中点的位置,从而补偿不同输入电压间输出恒流差值。

[0031] 本发明与现有技术相比具有显著的优点和有益效果,具体体现在以下方面:

[0032] ①本发明支持连续和/或准谐振工作模式下恒流输出的同时,不增加控制电路的管脚和电源系统的元件和设计成本,且通过检测工作模式和/或对谐振周期来调节恒流控制电路中的比例参数,以补偿不同工作模式间的恒流输出偏差,通过检测功率开关的关断延时和原边电流采样静差,适应性地调整原边电流采样的位置,以补偿恒流输出在不同输入电压下的偏差;另外,在启动初期屏蔽对原边信息的检测结果,设立独立的启动参数,使得输出电容快速充电,输出电压快速建立,开关电源快速启动;通过控制与补偿,提高开关电源的恒流输出精度及开关电源的启动速度;

[0033] ②通过检测工作模式和/或对谐振周期来调节恒流控制电路中的比例参数,以补偿不同工作模式间的恒流输出偏差,通过检测功率开关的关断延时和原边电流采样静差,适应性地调整原边电流采样的位置,以补偿恒流输出在不同输入电压下的偏差,具有恒流精度高等特点;

[0034] ③本发明开关电源控制电路在启动初期屏蔽对原边信息的检测结果,设立独立的启动参数,使得输出电容快速充电,输出电压快速建立,提高启动速度,尤其是容性负载时的启动速度;

[0035] ④本发明开关电源控制电路根据V<sub>FB</sub>值适应性地调节开关频率,即开关频率适应于 开关电源恒流输出时的负载,保证开关电源一直工作于准谐振模式和/或连续工作模式,而 连续工作模式的深度又不随负载改变而变化,从而保证开关具有高转换效率且无饱和损坏 的风险;

[0036] ⑤实现连续和/或准谐振工作模式下恒流输出的同时,不增加控制电路的管脚和电源系统的元件和设计成本;既支持CCM和QR工作模式,又不增加电源系统成本,且输出恒流精度高。

#### 附图说明

[0037] 图1:背景技术开关电源的控制电路及其电源系统的原理示意图:

- [0038] 图2a:工作于DCM模式时消磁时间检测偏差的波形示意图:

- [0039] 图2b:工作于CCM模式时消磁时间检测偏差的波形示意图:

- [0040] 图3a:较高输入电压原边电流采样偏差的工作波形示意图:

- [0041] 图3b:较低输入电压原边电流采样偏差的工作波形示意图;

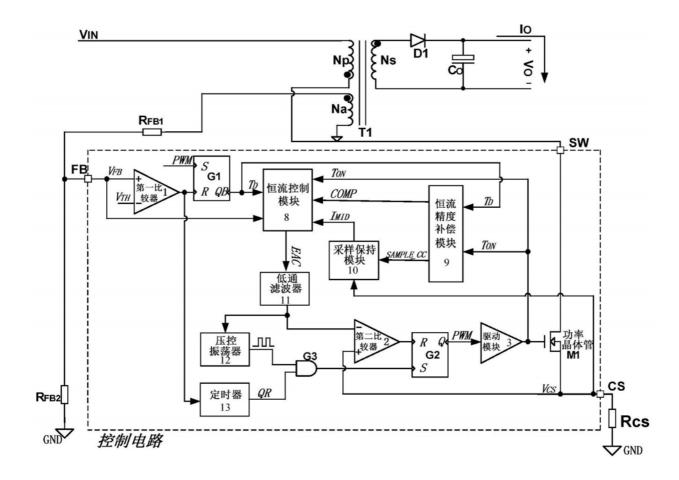

- [0042] 图4:本发明开关电源的控制电路及其电源系统的原理示意图;

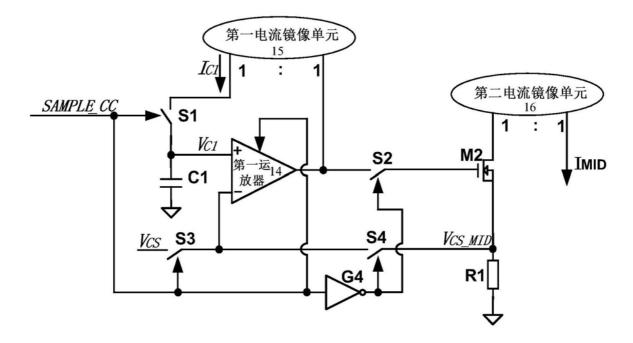

- [0043] 图5:本发明采样保持模块的原理示意图;

- [0044] 图6:本发明恒流控制模块的原理示意图;

- [0045] 图7:本发明恒流精度补偿模块的原理示意图;

- [0046] 图8:本发明恒流精度补偿模块的另一形式原理示意图;

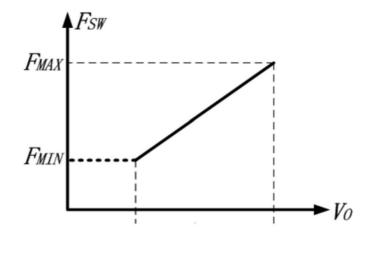

- [0047] 图9a:本发明开关电源控制电路的开关频率波形示意图;

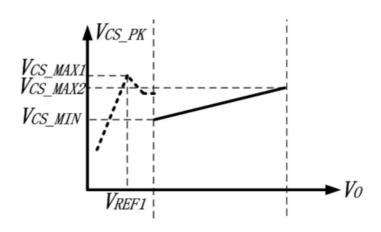

- [0048] 图9b:本发明开关电源控制电路的变压器原边电流峰值波形示意图;

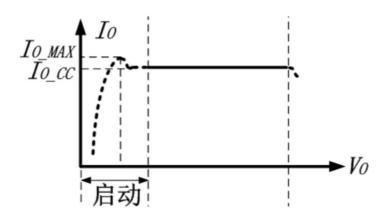

- [0049] 图9c:本发明开关电源控制电路的开关电源输出电流波形示意图。

## 具体实施方式

[0050] 为了对本发明的技术特征、目的和效果有更加清楚的理解,现对照附图详细说明 具体实施方案。

[0051] 开关电源的控制电路及其电源系统,如图4所示,电源系统包含变压器T1、输出二极管D1、输出电容 $C_0$ 、电阻 $R_{FB1}$ 、电阻 $R_{FB2}$ 、电阻 $R_{CS}$ 以及控制电路,控制电路的管脚FB分别与电阻 $R_{FB1}$ 、电阻 $R_{FB2}$ 相连,控制电路的管脚CS与电阻 $R_{CS}$ 相连,控制电路的管脚SW与变压器T1的原边 $N_P$ 相连。

[0052] 控制电路包含第一比较器1、第一RS锁存器G1、恒流控制模块8、恒流精度补偿模块 9、采样保持模块10、低通滤波器11、第二比较器2、第二RS锁存器G2、压控振荡器12、定时器 13、与逻辑门G3、驱动模块3以及功率晶体管M1,所述恒流控制模块8的第一输入端与第一RS 锁存器G1的Q输出端、恒流精度补偿模块9的第一输入端相连;恒流控制模块8的第二输入端 与管脚FB、第一比较器1的正相输入端相连;恒流控制模块8的第三输入端与驱动模块3的输 出端、第一RS锁存器G1的S输入端、功率晶体管M1的栅极、恒流精度补偿模块9的第二输入端 相连;恒流控制模块8的第四输入端与恒流精度补偿模块9的第一输出端相连;恒流控制模 块8的第五输入端与采样保持模块10的输出端相连;恒流控制模块8的输出端与低通滤波器 11的输入端相连: 采样保持模块10的输入端与管脚CS、第二比较器2的正相输入端、功率晶 体管M1的源极相连;采样保持模块10的控制端与恒流精度补偿模块9的第二输出端相连;低 通滤波器11的输出端与压控振荡器12的输入端、第二比较器2的负相输入端相连;压控振荡 器12的输出端与与逻辑门G3的第一输入端相连;定时器13的输出端与与逻辑门G3的第二输 入端相连;定时器13的输入端与第一RS锁存器G1的R输入端、第一比较器1的输出端相连;与 逻辑门G3的输出端与第二RS锁存器G2的S输入端相连;第二比较器2的输出端与第二RS锁存 器G2的R输入端相连:第二RS锁存器G2的输出端与驱动模块3的输入端相连。

[0053] 由恒流控制模块8根据FB管脚和CS管脚上的反馈信息,产生并输出控制开关电源输出电流的控制信号,适应性地调节功率晶体管M1的开通占空比,调整电源系统的输出电流Io为恒定值;恒流精度补偿模块9根据FB管脚和CS管脚上的反馈信息,适应性地调节恒流控制模块8和采样保持模块10的电路计算参数,使输出恒流精度不受工作模式变化和/或输

入条件变化的影响;定时器13判定FB管脚上电压VFB到达谷值的时刻;压控振荡器12根据恒流控制模块8输出的控制信号和定时器13对输出信号,调节功率晶体管M1的开关频率,使开关电源工作于QR模式或CCM模式,且当输出电压变化时,QR模式保持不变或CCM模式电流连续的深度保持相近。

[0054] 如图5所示,采样保持模块10包括第一电流镜像单元15、第二电流镜像单元16、第一开关S1、第二开关S2、第三开关S3、第四开关S4、第二晶体管M2、第一电容C1、第一电阻R1、第一运放器14、第一反相器G4,第一开关S1、第三开关S3的控制端受控于恒流精度补偿模块9的第二输出端的输出信号;第一运放器14的控制端所接电位与第一开关S1、第三开关S3的控制端所接信号相同;第二开关S2、第四开关S4的控制端所接信号与所述第一开关S1、第三开关S3的控制端所接信号相反;第一运放器14的正相输入端与第一开关S1的第一端、第一电容C1相连;第一运放器14的负相输入端与第三开关S3的第一端、第四开关S4的第一端相连;第一运放器14的输出端与第一镜像单元15的输出端、第二开关S2的第一端相连;第一开关S1的第二端与第一电流镜像单元15的输入端相连;第二开关S2的第二端与第二电阻R1、第二品体管M2的源极相连;第二晶体管M2的漏极与第二电流镜像单元16的输入端相连;第二电流镜像单元16的输入端相连;第二电流镜像单元16的输入端相连;第二电流镜像单元16的输出端连接至所述恒流控制模块8的第五输入端。第一电流镜像单元15的输出电流与输入电流比例为1:1。

[0055] 采样保持模块10包括第一电流镜像单元15、第二电流镜像单元16、第一开关S1、第二开关S2、第三开关S3、第四开关S4、第二晶体管M2、第一电容C1、第一电阻R1、第一运放器14以及第一反相器G4,当第一开关S1、第三开关S3闭合时,第一运放器14工作于跨导模式,即第一电流镜像单元15的输出电流 $I_{C1}$ 给第一电容C1充电, $I_{C1}$ 表示为: $I_{C1}$ =K1\*( $V_{C1}$ - $V_{CS}$ )\*G<sub>M</sub>,其中, $V_{C1}$ 为第一电容C1上电压, $V_{CS}$ 为控制电路CS管脚上电压, $G_M$ 为第一运放器14工作于跨导模式时的跨导,

[0056]

$$V_{C1}$$

表示为:  $V_{C1} = V_{CS} - \frac{C\frac{dV_{CS}}{dt}}{G_M \times K1}$ ,

[0057] 当C/G<sub>M</sub>趋近于0时,得到V<sub>C1</sub>=V<sub>CS</sub>;

[0058] 当第一开关S1、第三开关S3打开时,第二开关S2、第四开关S4闭合,第一运放器14工作于跟随模式,将第一电容C1上电压 $V_{C1}$ 传输至第二晶体管M2的源极,并通过第一电阻R1转换为电流 $I_{MID}$ ,镜像并输出至恒流控制模块8的第五输入端。

[0059] 如图6所示,恒流控制模块8包括第一恒流源I1、第二恒流源I2、电流源IM、第五开关S5、第六开关S6、第七开关S7、第八开关S8、开关SN、第二电容C2、第三电容C3、第四电容C4、第二电阻R2、第三晶体管M3、第二运放器17、第三比较器20、第三RS锁存器G5、二选一数据选择器G6、第一D触发器G7和误差放大器EA,误差放大器EA的输出端为所述恒流控制模块10的输出端;误差放大器EA的正相端与基准电压端VREF2相连;误差放大器EA的负相端与二选一数据选择器G6的输出端相连;二选一数据选择器G6的IN1输入端与第八开关S8的第一端、第四电容C4相连;二选一数据选择器G6的IN2输入端与第三比较器20的证相输入端、基准电压端VREF1相连;二选一数据选择器G6的SEL选择端与第三比较器20的输出端相连;第三比较器20的负相输入端连接至管脚FB;第八开关S8的第二端连接至所述采样保持模块10的

输出端;第八开关S8的控制端与第七开关S7的控制端、第三RS锁存器G5的Q输出端相连;第三RS锁存器G5的R输入端与第五开关S5的控制端、第一D触发器G7的Q输出端相连;第三RS锁存器G5的S输入端与第六开关S6的第一端、第七开关S7的第一端、第三电容C3相连;第六开关S6的第二端与第二恒流源I2相连;第六开关S6的控制端连接至第一比较器1的输出端;第七开关S7的第二端与第四电流镜像单元19的输出端相连;第四电流镜像单元19的输入端与第三电流镜像单元18的第一输入端与第三晶体管M3的漏极、开关SN的第一端相连;第三电流镜像单元18的第二输入端与开关SN的第二端相连;开关SN受控于所述恒流精度补偿模块9的第一输出端信号;第三晶体管M3的源极与第二电阻R2、第二运放器17的负相输入端相连;第三晶体管M3的栅极与第二运放器17的输出端相连;第二运放器17的正相输入端与第五开关S5的第一端、第二电容C2相连;第五开关S5的第二端与第一恒流源I1相连。

[0060] 恒流控制模块8包括第一恒流源I1、第二恒流源I2、电流源IM、第五开关S5、第六开关S6、第七开关S7、第八开关S8、开关SN、第二电容C2、第三电容C3、第四电容C4、第二电阻R2、第三晶体管M3、第二运放器17、第三比较器20、第三RS锁存器G5、二选一数据选择器(G6)、第一D触发器G7和误差放大器EA,所述第一D触发器G7连接构成二分频电路,产生逐个周期的开关周期信号TP,第五开关S5受控于信号TP,闭合时第一恒流源I1对第二电容C2充电,将所得电压通过第二运放器17和第二电阻R2产生电流,且比例镜像并输出至第四电流镜像单元19,第三电流镜像单元18的输入电流与输出电流的比例为( $K_{REF}+K_D$ ):1, $K_{REF}$ 和 $K_D$ 为常数, $K_D$ 的值受控于开关SN的开关状态,第四电流镜像单元19的输入电流与输出电流的比例为1:1:第六开关S6受控于信号TP,闭合时第二恒流源I2对第三电容C3充电并在充电结束时保持所得电压;第七开关S7受控于第三RS锁存器G5的Q输出端信号,在信号TP开始为高电平,即开关周期开始时由第四电流镜像单元19的输出电流对第三电容C3放电;当第三电容C3上电压达到第三RS锁存器G5的翻转阈值时,第三RS锁存器G5的Q输出端信号翻转为低电平,放电过程结束并产生时间信号Tcc;第八开关S8受控于时间信号Tcc,闭合时电流IMID对第四电容C4充电,并将电压Vc4传输至二选一数据选择器G6的IN1输入端;第四电容C4的电压

$$V_{C4}$$

表示为:  $V_{C4} = V_{CS\_MID} * (K_{REF} + K_D) * \frac{T_D}{T_P};$

[0061] 二选一数据选择器G6的IN2输入端与基准电压端V<sub>REF1</sub>相连,V<sub>REF1</sub>为控制电路内部电路产生,二选一数据选择器G6的SEL端电位选择IN1端输入数据或者IN2端输入数据作为输出数据,SEL端电位受控于第三比较器20的输出信号;当FB管脚上电压V<sub>FB</sub>小于V<sub>REF1</sub>时,二选一数据选择器G6的SEL端电位选择IN2端数据,V<sub>REF1</sub>端输出至误差放大器EA的负相输入端,误差放大器EA的正相输入端与基准电压端V<sub>REF2</sub>相连,其中,V<sub>REF2</sub>>V<sub>REF1</sub>,此时,误差放大器EA的品电压值,逐个开关周期的变压器原边电流峰值快速上升,传递至电源输出级的能量快速增大,开关电源快速启动;当FB管脚电压V<sub>FB</sub>大于V<sub>REF1</sub>时,二选一数据选择器G6的SEL端电位选择IN1端数据,第四电容C4电压V<sub>C4</sub>输出至误差放大器EA的负相输入端,工作状态平衡时,

[0062]

$$V_{CS\_MID} * (K_{REF} + K_D) * \frac{T_D}{T_P} = V_{C4} = V_{REF2}$$

,

[0063] 输出电流I<sub>0</sub>表示为:

$$[0064] \qquad I_O = \frac{N_P}{N_S} * \frac{V_{CS\_MID}}{R_{CS}} * \frac{T_D}{T_P} = \frac{N_P}{N_S} * \frac{1}{R_{CS}} * \frac{T_D}{T_P} * \frac{V_{REF2}}{K_{REF} + K_D} \; ,$$

[0065] 其中 $\frac{N_P}{N_S}$ 为变压器原次边匝数比, $R_{CS}$ 为原边电流检测电阻阻值,

[0066] 对于选定 $\frac{N_P}{N_S}$ 和Rcs的开关电源来说,输出电流 $I_0$ 为恒定值。

[0067] 第一恒流源I1和第二恒流源I2的电流相等,第二电阻R2与第一电阻R1的阻值相等,第二电容C2、第三电容C3与第四电容C4的容值相等。

[0068] 如图7所示,恒流精度补偿模块9包括第二D触发器G8、第四RS锁存器G9、第三恒流源I3、第四恒流源I4、第五恒流源I5、第九开关S9、第十开关S10、第十一开关S11、第五电容C5和第六电容C6,第二D触发器G8的D输入端与第一比较器1的输出端相连;第二D触发器G8的Q输出端与所述恒流控制模块8的开关SN的控制端相连;第二D触发器G8的CK输入端与第十一开关S11的控制端、第四RS锁存器G9的R输入端相连并连接至所述驱动模块3的输出端;第九开关S9的控制端与第十一开关S11的第一端、第五恒流源I5、第六电容C6的第一端相连;第九开关S9的第一端与第三恒流源I3相连;第九开关S9的第二端与第十开关S10的第一端、第四RS锁存器G9的S输入端以及第五电容C5的第一端相连;第十开关S10的第二端与第四恒流源I4相连;第四RS锁存器G9的Q输出端连接至所述采样保持模块10;第十一开关S11的第二端、第五电容C5的第二端以及第六电容C6的第二端连接至电源地。

[0069] 恒流精度补偿模块9包括第二D触发器G8、第四RS锁存器G9、第三恒流源I3、第四恒流源I4、第五恒流源I5、第九开关S9、第十开关S10、第十一开关S11、第五电容C5和第六电容C6,第二D触发器G8在功率晶体管M1导通开始时刻检测管脚FB上电压 $V_{FB}$ 是否降低至阈值 $V_{TH}$ 以下,即变压器消磁是否结束,以此输出模式补偿信号COMP至恒流控制模块8,进而调节比例参数 $K_D$ ,达到补偿不同工作模式间输出恒流差值的效果;第五恒流源I5与第十一开关S11、第六电容C6构成下降沿延时电路,调节计算管脚CS上电压 $V_{CS}$ 采样时刻所基于的脉宽长度,进而调节采样 $V_{CS}$ 的时刻距离功率晶体管M1实际导通中点的位置,从而补偿不同输入电压间输出恒流差值。

[0070] 如图8所示,恒流精度补偿模块9包括第二D触发器G8、第四RS锁存器G9、计时器21、第三恒流源I3、第三恒流源I4、第九开关S9、第十开关S10、开关SM、第五电容C5和第六电容C6,所述第二D触发器G8的D输入端和与第一比较器1的输出端相连;第二D触发器G8的CK输入端与第九开关S9的控制端、第四RS锁存器G9的R输入端以及计时器(21)的输入端相连并连接至所述驱动模块3的输出端;第二D触发器G8的Q输出端与恒流控制模块8的开关SN的控制端相连;第九开关S9的第一端与第三恒流源I3相连;第九开关S9的第二端与第十开关S10的第一端、第五电容C5、第四RS锁存器G9的S输入端相连;第十开关S10的第二端与第四恒流源I4、开关SM的第一端相连;开关SM的第二端与电流源IM相连;开关SM的输入端与计时器21的输出端相连。

[0071] 如图9a所示,如图9b所示,如图9c所示,本发明开关电源的控制电路的一组示例工作波形。控制电路的管脚FB上电压 $V_{FB}$ 与输出电压 $V_0$ 为正比例关系。在启动阶段,当 $V_{FB}$ 值小于基准电压 $V_{REF1}$ 时,开关频率 $F_{SW}$ 保持不变,而恒流控制模块8的输出信号EAC则调节变压器原

边电阻RCS上电压峰值Vcs\_PK快速上升,开关电源逐个周期传递至次边输出电容Co上的能量快速增大,输出电压Vo快速上升,电源快速启动;当VFB值大于基准电压VREF1时,Vcs\_PK的值达到最大Vcs\_MAXI,输出电流Io达到最大Io\_MAX,恒流控制模块8开始适应性地调节Vcs\_PK的值,使之逐渐趋近于稳定,稳定时的Vcs\_PK的值与正常工作状态的输出电压Vo值有关。在正常工作状态,压控振荡器12根据恒流控制模块8的输出信号适应性地调节开关频率Fsw的值,调节范围为FMIN至FMAX,与此同时,恒流控制模块8的输出信号根据开关电源的输入输出条件适应性地调节Vcs\_PK的值,调节范围为Vcs\_MIN至Vcs\_MAX2,而输出电流Io恒定为Io\_cc。在输入输出条件不超过正常工作范围的情况下,输出电流Io在不同的输入输出条件下保持高精度的恒定。

[0072] 支持连续和/或准谐振工作模式下恒流输出的同时,不增加控制电路的管脚和电源系统的元件和设计成本,且通过检测工作模式和/或对谐振周期来调节恒流控制电路中的比例参数,以补偿不同工作模式间的恒流输出偏差,通过检测功率开关的关断延时和原边电流采样静差,适应性地调整原边电流采样的位置,以补偿恒流输出在不同输入电压下的偏差。此外,在启动初期屏蔽对原边信息的检测结果,设立独立的启动参数,使得输出电容快速充电,输出电压快速建立,开关电源快速启动。结合上述控制与补偿,来提高开关电源的恒流输出精度及开关电源的启动速度。

[0073] 本发明实现连续和/或准谐振工作模式下恒流输出的同时,不增加控制电路的管脚和电源系统的元件和设计成本;既支持CCM和QR工作模式,又不增加电源系统成本,且输出恒流精度高;通过检测工作模式和/或对谐振周期来调节恒流控制电路中的比例参数,以补偿不同工作模式间的恒流输出偏差,通过检测功率开关的关断延时和原边电流采样静差,适应性地调整原边电流采样的位置,以补偿恒流输出在不同输入电压下的偏差,具有恒流精度高等特点。

[0074] 本发明开关电源控制电路在启动初期屏蔽对原边信息的检测结果,设立独立的启动参数,使得输出电容快速充电,输出电压快速建立,提高启动速度,尤其是容性负载时的启动速度;根据VFB值适应性地调节开关频率,即开关频率适应于开关电源恒流输出时的负载,保证开关电源一直工作于准谐振模式和/或连续工作模式,而连续工作模式的深度又不随负载改变而变化,从而保证开关具有高转换效率且无饱和损坏的风险。

[0075] 其电源系统设计简洁、成本低、启动速度快、容性负载启动可靠且输出恒流精度高。

[0076] 需要说明的是:以上所述仅为本发明的优选实施方式,并非用以限定本发明的权利范围;同时以上的描述,对于相关技术领域的专门人士应可明了及实施,因此其它未脱离本发明所揭示的精神下所完成的等效改变或修饰,均应包含在申请专利范围中。

图2a

图2b

图3a

图3b

图4

图5

图6

图7

图8

图9a

图9b

图9c