# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-354266 (P2005-354266A)

(43) 公開日 平成17年12月22日 (2005. 12. 22)

| (51) Int.C1. <sup>7</sup> | F 1                          |           |              | テーマコード      | (参考)     |

|---------------------------|------------------------------|-----------|--------------|-------------|----------|

| HO3F 3/4                  | HO3F                         | 3/45      | A            | 5 J O 3 9   |          |

| HO3F 1/2                  | P HO3F                       | 1/22      |              | 5 J O 5 5   |          |

| HO3K 5/0                  | нозк                         | 5/08      | $\mathbf{E}$ | 5,1500      |          |

| HO3K 17/3                 | Н03К                         | 17/30     | E            |             |          |

|                           |                              | 審査請求      | 未請求          | 請求項の数 14 OL | (全 33 頁) |

| (21) 中爾悉县                 | 特願2004 171047 (P2004 171047) | (71) 虫酶 A | 300060       | Q21         |          |

(21) 出願番号 (22) 出願日

特願2004-171047 (P2004-171047) | (71) 出願人 302062931 平成16年6月9日(2004.6.9)

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74)代理人 100080816

弁理士 加藤 朝道

(72) 発明者 西村 浩一

神奈川県川崎市中原区下沼部1753番地 NECエレクトロニクス株式会社内

Fターム(参考) 5J039 DA09 DB05 KK16 KK17 KK18

KK22 MM03 MM16

5J055 AX02 BX10 CX24 DX13 DX14

DX22 DX63 EX07 EY21 EZ04 EZ08 EZ10 FX05 FX12 GX01

GX06

最終頁に続く

### (54) 【発明の名称】電圧比較器回路

# (57)【要約】

#### 【課題】

簡易な構成により高速化を実現する電圧比較器の提供

# 【解決手段】

差動入力端子In<sup>+</sup>、In<sup>-</sup>からの差動電圧を入力し 互いに逆極性の第1の差動対 (MP1、MP2)及び第 2の差動対(MN1、MN2)を有する入力差動段と、 入力差動段の差動出力に接続され、第1の差動対の差動 出力信号と第2の差動対の差動出力信号とを加算するフ オールデッドカスコード型の差動段(MP3、MP4、 MP5、MP6、MN3、MN4)と、対向配置され、 フォールデッドカスコード型の差動段の差動出力をそれ ぞれ入力に受け、出力同士が出力端子に共通接続された 互いに逆極性の第1のカレントミラー回路(CM1)及 び第2のカレントミラー回路(СМ2)を備え、フォー ルデッドカスコード型の差動段は第1の差動対の差動出 力信号と第2の差動対の差動出力信号とを加算し、フォ ールデッドカスコード型の差動段の出力を、前記第1及 び第2のカレントミラー回路でそれぞれ折り返し出力端

#### 【特許請求の範囲】

# 【請求項1】

差動入力信号を入力とし第1及び第2の電流源でそれぞれ駆動される第1及び第2導電型の第1及び第2の差動対を有する入力段差動段と、

前記第1及び第2の差動対の差動出力の負荷をなし、前記第1の差動対の差動出力信号と前記第2の差動対の差動出力信号とそれぞれを加算して折り返し、差動出力するフォールデッドカスコード(folded cascode)型の差動段と、

第1及び第2電源間に対向配置され、前記フォールデッドカスコード型の差動段の差動 出力をそれぞれ入力に受け、出力同士が出力端子に共通接続された、第1及び第2導電型 の第1及び第2のカレントミラー回路と、

を備えている、ことを特徴とする差動増幅器。

#### 【請求項2】

前記フォールデッドカスコード型の差動段は、

前記第1の電源と第2の電源間に、制御端子同士がそれぞれ接続されている第1乃至第3のトランジスタ対と、二つの電流源とを少なくとも含み、前記第1の電源側に接続される前記第1のトランジスタ対と前記第2のトランジスタ対は、カスコードカレントミラー回路を構成し、

前記第1の差動対の差動出力は、前記第1のトランジスタ対と前記第2のトランジスタ対との接続点に接続され、

前記第2の差動対の差動出力は、前記第2の電源に一端が共通接続された前記二つの電流源の他端と前記第3のトランジスタ対との接続点に接続され、

前記第2のトランジスタ対の一の出力が、前記第2のカレントミラー回路の入力端に接続され、前記第3のトランジスタ対の一の出力が、前記第1のカレントミラー回路の入力端に接続されている、ことを特徴とする請求項1記載の差動増幅器。

## 【請求項3】

前記フォールデッドカスコード型の差動段は、

前記第1の電源と第2の電源間に、制御端子同士がそれぞれ接続されている第1乃至第3のトランジスタ対と、二つの電流源とを少なくとも含み、前記第2の電源側に接続される前記第1のトランジスタ対と前記第2のトランジスタ対はカスコードカレントミラー回路を構成し、

前記第1の差動対の差動出力は、前記第1の電源に一端が共通接続された前記二つの電流源の他端と前記第3のトランジスタ対との接続点に接続され、

前記第2の差動対の差動出力は、前記第1のトランジスタ対と前記第2のトランジスタ対との接続点に接続され、

前記第2のトランジスタ対の一の出力が、前記第1のカレントミラー回路の入力端に接続され、前記第3のトランジスタ対の一の出力が、前記第2のカレントミラー回路の入力端に接続されている、ことを特徴とする請求項1記載の差動増幅器。

### 【請求項4】

前記フォールデッドカスコード型の差動段は、

前記第1の電源と前記第2の電源間に、第3のカレントミラー回路と、ゲート同士が接続された第1のトランジスタ対と、二つの電流源とを少なくとも備え、

前記第1の差動対の差動出力は、前記第3のカレントミラー回路の入力端及び前記第1 のカレントミラー回路の入力端にそれぞれ接続され、

前記第2の差動対の差動出力は、前記第1のトランジスタ対と、前記二つの電流源の接続点にそれぞれ接続され、

前記第1のトランジスタ対の一の出力が、前記第2のカレントミラー回路の入力端に接続され、前記第3のカレントミラー回路の出力が、前記第2のカレントミラー回路の入力端に接続されている、ことを特徴とする請求項1記載の差動増幅器。

#### 【請求項5】

前記第1及び第2のカレントミラー回路の出力端の電流駆動能力は、入力端の電流駆動

10

20

30

40

能力のk倍(ただし、kは1より大の所定数)である、ことを特徴とする請求項1乃至4 のいずれか一に記載の差動増幅器。

### 【請求項6】

請求項1乃至5のいずれか一に記載の前記差動増幅器を備え、

前記差動増幅器の出力を受ける波形整形回路を備えている電圧比較器。

#### 【請求項7】

前記波形整形回路は、バッファ回路及び/又はインバータを含む、請求項6記載の電圧 比較器。

#### 【請求項8】

請求項1乃至5のいずれか一に記載の前記差動増幅器を備えた半導体集積回路装置。

#### 【請求項9】

差 動 増 幅 器 と 、 前 記 差 動 増 幅 器 の 出 力 に 複 数 段 縦 続 接 続 さ れ た イ ン バ ー タ と 、 を 備 え た 電圧比較器において、

前記差動増幅器が、

第 1 の P チャネル M O S トランジスタと第 2 の P チャネル M O S トランジスタで 構成さ れる第1の差動対と、

第 1 の N チャネル M O S トランジスタと第 2 の N チャネル M O S トランジスタで構成さ れる第2の差動対と、

各々のゲートが共通接続されて第1の電圧源に接続された第3と第4のNチャネルMO Sトランジスタと、

各々のゲートが共通接続され、各々のソースが共通接続された第3と第4のPチャネル MOSトランジスタと、

各々のゲートが共通接続されて第2の電圧源に接続された第5と第6のPチャネルMO Sトランジスタと、

入 力 が 前 記 第 4 の N チャ ネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン に 接 続 さ れ 、 共 通 端 子 が 第 1の電源に接続された第1のカレントミラー回路と、

入力が前記第6のPチャネルMOSトランジスタのドレインに接続され、共通端子が第 2の電源に接続された第2のカレントミラー回路と、

前記第1の差動対の共通に接続されたソースと第1の電源間に接続される第1の定電流 源と、

前 記 第 2 の 差 動 対 の 共 通 に 接 続 さ れ た ソ ー ス と 第 2 の 電 源 間 に 接 続 さ れ た 第 2 の 定 電 流 源と.

前 記 第 3 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ の ソ - ス と 第 2 の 電 源 間 に 接 続 さ れ た 第 3 の 定電流源と、

前 記 第 4 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ の ソ ー ス と 第 2 の 電 源 間 に 接 続 さ れ た 第 4 の 定電流源と、

を備え、

前 記 第 1 の 差 動 対 を 構 成 す る 第 1 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン が 前 記 第 3 の N チャネル M O S トランジスタのソースに共通接続され、

前 記 第 1 の 差 動 対 を 構 成 す る 第 2 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン が 前 記 第 4のNチャネルMOSトランジスタのソースに共通接続され、

前 記 第 2 の 差 動 対 を 構 成 す る 前 記 第 1 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン と 前 記 第 3 の P チャネル M O S トランジスタのドレインと前 記 第 5 の P チャネル M O S トラン ジスタのソースとが共通接続され、

前 記 第 2 の 差 動 対 を 構 成 す る 前 記 第 2 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン と 前 記 第 4 の P チャネル M O S トランジスタのドレインと前 記 第 6 の P チャネル M O S トラン ジスタのソースとが共通接続され、

前 記 第 3 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ の ゲ ー ト と 前 記 第 5 の P チ ャ ネ ル M O S ト ラ ンジスタのドレインと前記第3のNチャネルMOSトランジスタのドレインとが共通接続 され、

10

20

30

40

前記第1のカレントミラー回路の出力と前記第2のカレントミラー回路の出力を共通接続して出力端子とし、

前記第1のPチャネルMOSトランジスタのゲートと前記第1のNチャネルMOSトランジスタのゲートを共通接続して反転入力端子とし、

前記第2のPチャネルMOSトランジスタのゲートと前記第2のNチャネルMOSトランジスタのゲートを共通接続して正転入力端子とする、ことを特徴とする電圧比較器。

#### 【請求項10】

差動増幅器と、前記差動増幅器の出力に複数段縦続接続されたインバータと、を備えた電圧比較器において、

前記差動増幅器が、

第 1 の P チャネル M O S トランジスタと第 2 の P チャネル M O S トランジスタで構成される第 1 の差動対と、

第 1 の N チャネル M O S トランジスタと第 2 の N チャネル M O S トランジスタで構成される第 2 の差動対と、

各々のゲートが共通接続され、各々のソースが共通接続された第 3 と第 4 の N チャネル M O S トランジスタと、

各々のゲートが共通接続されて第 1 の電圧源に接続された第 5 と第 6 の N チャネル M O S トランジスタと、

各々のゲートが共通接続され第2の電圧源に接続された第3と第4のPチャネルMOSトランジスタと、

入力が前記第6のNチャネルMOSトランジスタのドレインに接続され、共通端子が第 1の電源に接続された第1のカレントミラー回路と、

入力が前記第4の P チャネル M O S トランジスタのドレインに接続され、共通端子が第 2 の電源端子に接続された第 2 のカレントミラー回路と、

前記第1の差動対の共通に接続されたソースと第1の電源間に接続される第1の定電流源と、

前記第2の差動対の共通に接続されたソースと第2の電源間に接続された第2の定電流源と、

前記第3のPチャネルMOSトランジスタのソースと第1の電源間に接続された第3の 定電流源と、

前記第4のPチャネルMOSトランジスタのソースと第2の電源間に接続された第4の 定電流源と、

を備え、

前記第1の差動対を構成する第1のPチャネルMOSトランジスタのドレインが前記第 5のNチャネルMOSトランジスタのソースと共通接続され、

前記第1の差動対を構成する第2のPチャネルMOSトランジスタのドレインが前記第6のNチャネルMOSトランジスタのソースに共通接続され、

前記第2の差動対を構成する第1のNチャネルMOSトランジスタのドレインが前記第3のPチャネルMOSトランジスタのソースに共通接続され、

前記第2の差動対を構成する第2のNチャネルMOSトランジスタのドレインが前記第4のPチャネルMOSトランジスタのソースに共通接続され、

前記第3のNチャネルMOSトランジスタのゲートが前記第5のNチャネルMOSトランジスタのドレインと前記第3のPチャネルMOSトランジスタのドレインに共通接続され、

前記第1のカレントミラー回路の出力と前記第2のカレントミラー回路の出力を共通接続して出力端子とし、

前記第1のPチャネルMOSトランジスタのゲートと前記第1のNチャネルMOSトランジスタのゲートを共通接続して反転入力端子とし、

前記第2のPチャネルMOSトランジスタのゲートと前記第2のNチャネルMOSトランジスタのゲートを共通接続して正転入力端子としている、ことを特徴とする電圧比較器

10

20

30

40

# 【請求項11】

前記第1と第2のカレントミラー回路は、入力電流と出力電流の比が、入力電流:出力 電流=1:k(ただし、kは1より大の数)である、ことを特徴とする請求項9又は10 記載の電圧比較器。

#### 【 請 求 項 1 2 】

差 動 増 幅 器 と 、 前 記 差 動 増 幅 器 の 出 力 に 複 数 段 縦 続 接 続 さ れ た イ ン バ ー タ と 、 を 備 え た 電圧比較器において、

前記差動増幅器が、

第 1 の P チャネル M O S トランジスタと第 2 の P チャネル M O S トランジスタで 構成さ れる第1の差動対と、

第 1 の N チャネル M O S トランジスタと第 2 の N チャネル M O S トランジスタで構成さ れる第2の差動対と、

各 々 の ゲ ー ト が 共 通 接 続 さ れ 、 第 1 の 電 圧 源 に 接 続 さ れ た 第 3 と 第 4 の N チ ャ ネ ル M O Sトランジスタと、

前 記 第 1 の 差 動 対 の 共 通 に 接 続 さ れ た ソ - ス と 第 1 の 電 源 間 に 接 続 さ れ る 第 1 の 定 電 流 源と、

前 記 第 2 の 差 動 対 の 共 通 に 接 続 さ れ た ソ ー ス と 第 2 の 電 源 間 に 接 続 さ れ た 第 2 の 定 電 流 源と、

前 記 第 3 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ の ソ ー ス と 第 2 の 電 源 間 に 接 続 さ れ た 第 3 の 定電流源と、

前 記 第 4 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ の ソ - ス と 第 2 の 電 源 間 に 接 続 さ れ た 第 4 の 定電流源と、

入力端子が前記第1のNチャネルMOSトランジスタのドレインと前記第3のNチャネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン と に 共 通 接 続 さ れ 、 共 通 端 子 が 第 1 の 電 源 端 子 に 共 通 接 続された第1のカレントミラー回路と、

入力端子が前記第2のNチャネルMOSトランジスタのドレインと前記第4のNチャネ ル M O S トランジスタのドレインとに共通接続され、共通端子が第 1 の電源端子に共通接 続された第2のカレントミラー回路と、

入力端子が前記第1のカレントミラー回路の出力端子に接続され、共通端子が第2の電 源に接続された第3のカレントミラー回路と、

前 記 第 1 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン が 前 記 第 3 の N チ ャ ネ ル M O S ト ランジスタのソースに接続され、

前 記 第 2 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ の ド レ イ ン が 前 記 第 4 の N チ ャ ネ ル M O S ト ランジスタのソースに接続され、

前 記 第 2 の カ レン ト ミ ラ - 回 路 の 出 力 端 子 と 前 記 第 3 の カ レン ト ミ ラ - 回 路 の 出 力 端 子 を共通接続して出力端子とし、

前記第1のPチャネルMOSトランジスタのゲートと前記第1のNチャネルMOSトラ ンジスタのゲートを共通接続して反転入力端子とし、

前 記 第 2 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ の ゲ ー ト と 前 記 第 2 の N チ ャ ネ ル M O S ト ラ ンジスタのゲートを共通接続して正転入力端子としている、ことを特徴とする電圧比較器

# 【請求項13】

前記第2と第3のカレントミラー回路は、入力電流と出力電流の比が、入力電流:出力 電流=1:k(k>1)である、ことを特徴する請求項12記載の電圧比較器。

# 【請求項14】

請求項9乃至13のいずれか一記載の電圧比較器を備えた半導体集積回路装置。

【発明の詳細な説明】

# 【技術分野】

[0001]

30

10

20

40

20

30

40

50

(6)

本発明は、差動増幅器及び該差動増幅器を備えた電圧比較器回路に関し、特に、高速の差動インターフェース回路等に用いて好適な電圧比較器回路に関する。

### 【背景技術】

### [0002]

近時、高速の差動インターフェース回路が各種装置で多用されている。例えばTFT\_LCD(Thin Film Transistor Liquid Crystal Display)分野ではLCDドライバLSIとタイミングコントローラLSIとの間のインターフェースとして、RSDS(Reduce d Swing Differencial Signaling:米国NS社の登録商標)やmini‐LVDS(mini Low Voltage Differencial Signaling:米国TI社の登録商標)等が標準化されつつある。これらのレシーバー回路には、差動入力をもった電圧比較器回路が使われている。

[0003]

電圧比較器回路に入力される周波数は、RSDSで、約85MHz、mini-LVDSでは、約200MHzの差動信号である。また、入力差動電圧は、差動信号成分で±50mV、同相信号成分で、0.3V~VDD-0.5V程度である。

#### [0004]

電圧比較器回路に要求される特性として、これらの仕様を満たす回路が要求されている。しかし、現在発表されている回路構成では、同相信号成分の規格を満足し、かつ、動作速度をも満足することは困難である。

#### [00005]

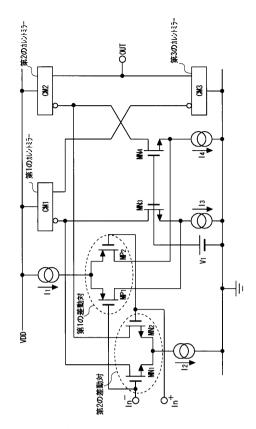

図 6 は、非特許文献 1 (IEEE J. Solid-State Circuits. vol.29 No.12.Dec.1994 pp.1 505~1513 "A Compact Power-Efficient 3V CMOS Rail-to-Rail Input/Output Operational Amplifire for VLSI Cell Libraries")記載の差動増幅回路の構成を示す図である

### [0006]

図6を参照すると、この差動増幅器は、第1のPチャネルMOSトランジスタMP1と、第2のPチャネルMOSトランジスタMP2で構成される第1の差動対と、第1のNチャネルMOSトランジスタMN1と第2のNチャネルMOSトランジスタMN1と第2のNチャネルMOSトランジスタMN2で構成された差動増幅回路において、各々のゲートが共通接続された第3と第4のNチャネルMOSトランジスタMN3、MN4と、各々のゲートが共通接続され、かつ各々のソースが共通接続された第3と第6のPチャネルMOSトランジスタMP3、MP4と、各々のゲートが共通接続された第3と第6のPチャネルMOSトランジスタMP5、MP6と、前記第1の差動対(MP1、MP2)の共通に接続されたソースと正電流源(電流 I1を供給)と、第2の差動対(MN1、MN2)の共通に接続されたソースと負電源間に接続された第2の定電流源(電流 I2を供給)と、第3のNチャネルMOSトランジスタMN3のソースと負電源間に接続された第3の定電流源(電流 I3を供給)とを備えている。

# [0007]

第1の差動対を構成する第1と第2のPチャネルMOSトランジスタMP1、MP2のドレインが第3と第4のNチャネルMOSトランジスタMN3、MN4のソースにそれぞれ接続されている。

# [0008]

また、第2の差動対を構成する第1のNチャネルMOSトランジスタMN1のドレインと、第3のPチャネルMOSトランジスタMP3のドレインと第5のPチャネルMOSトランジスタMP5のソースとが共通接続され、第2の差動対を構成する第2のNチャネルMOSトランジスタMP4のドレインと第6のPチャネルMOSトランジスタMP6のソースとが共通接続されている。

## [0009]

第 3 の P チャネル M O S トランジスタ M P 3 のゲートと第 5 の P チャネル M O S トラン

20

30

40

ジスタMP5のドレインと、第3のNチャネルMOSトランジスタMN3のドレインとが 共通接続されている。

[0010]

第1のNチャネルMOSトランジスタMN1のゲートと第1のPチャネルMOSトランジスタMP1のゲートを共通接続して正転入力端子とし、第2のNチャネルMOSトランジスタMN2のゲートと第2のPチャネルMOSトランジスタMP2のゲートを共通接続して反転入力端子としている。

[0011]

第 6 の P チャネルMOSトランジスタMP 6 のドレインと第 4 の N チャネルMOSトランジスタMN 4 のドレインを共通接続して出力端子としている。

[0012]

電圧比較器回路は、差動増幅器を応用したものであり、図6の従来の差動増幅器を電圧 比較器回路として使うことができる。しかしながら、図6の差動増幅器を、実際に電圧比 較器回路として使う場合には、波形整形が必要である。

[ 0 0 1 3 ]

その波形整形の目的のため、この差動増幅回路の後段に、CMOSインバータを接続する必要がある。

[0014]

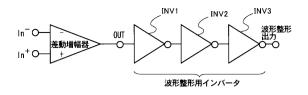

図9は、その具体的な構成を示す図である。図9を参照すると、差動増幅器の出力に、第1のCMOSインバータINV1の入力端子を接続する。第1のCMOSインバータINV1の後段に、更なる波形整形を目的として、第2と第3のCMOSインバータINV2、INV3をシリーズに接続し、第3のCMOSインバータINV3の出力を最終出力とする。

[ 0 0 1 5 ]

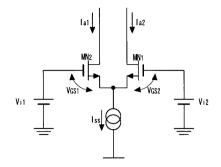

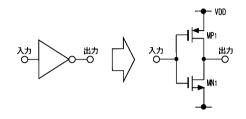

図10は、図9のCMOSインバータの具体的な回路構成の例を示す図である。図10を参照すると、CMOSインバータは、正電源VDDにソースが接続された、PチャネルMOSトランジスタMP1と、PチャネルMOSトランジスタMP1のドレインにドレインが接続されて出力端子に接続され、ソースが負電源VSS(GND)に接続されたNチャネルMOSトランジスタMN1と、を備え、PチャネルMOSトランジスタMP1とNチャネルMOSトランジスタMN1のゲートは共通接続されて入力端子に接続されている

[0016]

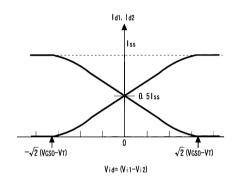

以下、この差動増幅器を電圧比較器回路として使った場合について、解析を行う。まず、MOSトランジスタで構成された差動増幅器についての基本動作について、図7と図8を参照しながら説明する。図7は、差動増幅回路の基本回路構成であり、図8は、その入力電圧対出力電流の直流伝達特性を示したものある。NチャネルMOSトランジスタMN1とMN2はソースが共通接続され、その共通接続されたソースと負電源間に定電流源Issが接続されている。そして、MN1のゲートには電圧源Vi1が、MN2のゲートには電圧源Vi1が、MN2のゲートには電圧源Vi1が、MN2のゲートには電圧源Vi1が大り、MN1のゲートには電圧源Vi1が大り、MN2のゲート・ソース間電圧をそれぞれVss1とVss2と、入力電圧の関係から次式(1)が成り立つ。

$V_{i1} - V_{i33} + V_{i33} - V_{i2} = 0$  ....(1)

[ 0 0 1 7 ]

そして、ドレイン電流をそれぞれ  $I_{d-1}$ 、  $I_{d-2}$  とし、 M O S トランジスタ M N 1 と M N 2 のゲート幅とゲート長をそれぞれ M と L 、 移動度を  $\mu$  、 単位面積当たりのゲート酸化膜容量を  $C_0$  、 閾値を  $V_T$  とすると、トランスコンダクタンス (次式( 2 )参照)、 M O S トランジスタ M N 1 と M N 2 のゲート - ソース間電圧  $V_{G-S-1}$  、  $V_{G-S-2}$  は、次式( 3 )、( 4 )で与えられる。

$$\beta = \frac{W}{L} \mu C_0 \qquad (2)$$

[0018]

$$V_{GS1} = \sqrt{\frac{2I_{a1}}{\beta}} + V_T \qquad -----(3)$$

[0019]

$$V_{\rm GS2} = \sqrt{\frac{2I_{d2}}{\beta}} + V_{\rm F} \qquad \cdots \qquad (4)$$

# [0020]

ここで、バイアス電流  $I_{s,s}$  が完全に M N 1 のトランジスタの方に切り替わる差動電圧  $V_{i,d}$  を求めると、(1)、(3)、(4)式より、次式(5)が導出される。

$$\Delta V_{id} = V_{i1} - V_{i2} = \left(\sqrt{\frac{2I_{ee}}{\beta}} - V_{T}\right) - V_{T} = \sqrt{\frac{2I_{ee}}{\beta}} - \cdots - (5)$$

#### [ 0 0 2 1 ]

そして、 V  $_{i=1}$  = V  $_{i=2}$  の時のゲート・ソース間電圧 V  $_{G}$   $_{S}$  を V  $_{G}$   $_{S}$   $_{0}$  とすると、このとき M N 1 と M N 2 のドレイン電流はそれぞれ I  $_{S}$   $_{S}$  / 2 となり、次式( 6 )が得られる

$V_{\rm GS01} = \sqrt{\frac{I_{\rm SS}}{\beta}} + V_{\rm T} \qquad ------(6)$

## [0022]

従って、(5)式と(6)式より、次式(7)となる。

$$\therefore \Delta V_{id} = \sqrt{2} \left( V_{GS0} - V_T \right) \qquad (7)$$

# [0023]

この(7)式は、MOS差動段が完全に切り替わる条件式となる。このようにして、入力差動電圧が、(7)式で表された値以上の時は、差動段のバイアス電流源が片方のトランジスタに流れ、もう片方のトランジスタの電流は0となる。これが比較器動作となる。

# [0024]

但し、このように完全に切り替わらなくても、本差動段の次段の構成によっては、これ以下の差動電圧でも充分比較器の動作をする。これは、この差動段が充分な利得を持っているからである。この差動段において、入力電圧と差動段を構成するドレイン電流との関係グラフを示したものが、図 8 である。

10

20

30

50

#### [0025]

図 6 の差動増幅器について詳細な説明を行う。図 6 の差動増幅器は、いわゆるフォールデッドカスコード型の差動増幅器回路である。

#### [0026]

この回路は、入力電圧範囲によって次の3つの動作モードをもつ。

#### [ 0 0 2 7 ]

[1] < 第1と第2の差動対の両方が動作している場合 >

入力電圧をVinとして、

$$V_{DD} - (V_{GS(MP1/2)} + V_{DS(satYD)}) > V_{in} > V_{GS(MPD/2)} + V_{DS(satYD)} - - - - (8)$$

10

20

### [0028]

V <sub>G S ( M N 1 / 2 )</sub> : N チャネル M O S トランジスタ M N 1 / 2 のゲート - ソース間電圧、

V<sub>DS(sat)(I2)</sub>:電流源I2を構成するNチャネルMOSトランジスタの飽 和点でのドレイン・ソース間電圧(5極管領域で動作するぎりぎりの電圧)、

$V_{GS(MP1/2)}: P$ チャネルMOSトランジスタMP1/2のゲート・ソース間電圧、

V<sub>DS(sat)(I1)</sub>:電流源I1を構成するPチャネルMOSトランジスタの飽和点でのドレイン・ソース間電圧(5極管領域で動作するぎりぎりの電圧)、

の条件の時、第1と第2の差動対の両方が動作状態となる。

#### 【 0 0 2 9 】

まずIn  $^+$  側がIn  $^-$  より高く、かつ(7)式以上の電圧が入力されたと仮定すると、この回路は、電圧比較器回路動作をするので、第1の差動対(MP1、MP2)のバイアス電流I $_1$  は、全て第2のPチャネルMOSトランジスタMP2の方に流れる。そして第1のPチャネルMOSトランジスタMP1の方の電流は0となる。一方、第2の差動対(MN1、MN2)のバイアス電流I $_2$  は、全て第1のNチャネルMOSトランジスタMN1の方に流れる。そして、第2のNチャネルMOSトランジスタMN2の方の電流は0となる。この時の各トランジスタのバイアス電流状態をみると、第3のNチャネルMOSトランジスタMN3のドレイン電流をI<sub>D(MN3)</sub>とし、第4のNチャネルMOSトランジスタMN4のドレイン電流をI<sub>D(MN 4)</sub>として、次式(9)、(10)が成り立つ

30

$$I_{D(MM3)} = I_4 - I_1$$

.....(9)

$I_{D(MM3)} = I_3$  .....(10)

# [0030]

ここで、I」とI₃とI₄の関係を以下のようにする。

$$I_3 = I_4 \ge I_1$$

-----(11)

40

50

## [0031]

一方、第 5 の P チャネル M O S トランジスタ M P 5 のドレイン電流  $I_{D(MP5)}$  は第 3 の N チャネル M O S トランジスタ M N 3 のドレイン電流  $I_{D(MN3)}$  と同じであるので、次式( 1 2 )が成り立つ。

$$I_{D(MP5)} = I_{D(MP3)} \qquad -----(12)$$

## [0032]

また、 第 3 の P チャネル M O S トランジスタ M P 3 のドレイン電流 I <sub>D ( M P 3 )</sub> は第

30

40

I<sub>D (MP5)</sub> = I<sub>3</sub>、 I<sub>D (MN1)</sub> = I<sub>2</sub>、 だから、次式(13)が成り立つ。

$$I_{D(MP3)} = I_{D(MP5)} + I_{D(MN1)} = I_3 + I_2$$

----(13)

### [0033]

第4のPチャネルMOSトランジスタMP4は第3のPチャネルMOSトランジスタMP3と各々のゲートとソースが共通接続されているので、各々のドレイン電流は等しくなる。従って、第4のPチャネルMOSトランジスタMP4のドレイン電流 I<sub>D(MP4)</sub>は、次式(14)で与えられる。

$$I_{D(MP4)} = I_{D(MP3)} = I_3 + I_2$$

-----(14)

# [0034]

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MP2)} = I_3 + I_2$$

-----(15)

## [0035]

$$I_{out} = (I_3 + I_2) - (I_4 - I_1)$$

----(16)

ここで、 $I_3 = I_4$  であるので、結果的に出力端電流 $I_{out}$  は

$$I_{out} = I_1 + I_2 \qquad ------(17)$$

の電流吐き出し能力を持ち、ハイレベルとなる。電位的にはほぼ正電源のVDDとなる

### [0036]

# [0037]

一方、第 5 の P チャネル M O S トランジス P M P S のドレイン電流 I D O ( M P S ) は、第 S の N チャネル M O S トランジス P M P S のドレイン電流 I D O ( P S ) と同じであるので、次式( P O ) で与えられる。

$$I_{D(MP5)} = I_{D(MP5)}$$

-----(20)

### [0038]

$$I_{D(MP3)} = I_{D(MP5)} + I_{D(MP1)} = I_3 - I_1$$

----(21)

# [0039]

第4のPチャネルMOSトランジスタMP4は第3のPチャネルMOSトランジスタMP3と各々のゲートとソースが共通接続されているので、各々のドレイン電流は等しくなる。従って、第4のPチャネルMOSトランジスタMP4のドレイン電流 I<sub>D(MP4)</sub>も、次式(22)で与えられる。

$$I_{D(MP4)} = I_{D(MP3)} = I_3 - I_1$$

-----(22)

## [0040]

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MP2)} = I_3 - I_1 - I_2 \qquad -----(23)$$

# [0041]

同様にして、出力電流は(18)式と(23)式で示した電流の引き算値になる。すなわち出力端電流 I。utは、出力端から吐き出す電流を正として、次式(24)で与えられる。

# [ 0 0 4 2 ]

ここで、 $I_3 = I_4$  であることから、結果的に、出力端電流 $I_{out}$  は

$$I_{out} = I_1 + I_2 \qquad (25)$$

の電流吸い込み能力を持ち、ローレベルとなる。電位的にはほぼ負電源(GND)の 0Vとなる。

# [0043]

40

20

[2] < 第1の差動対のみが動作している場合 > 上述した「1]場合に対し、この場合の入力電圧 ∀inが、

$$0 < V_{in} < V_{GS(M0D/2)} + V_{DS(sat)(D)}$$

-----(26)

の時には、第1の差動段のみしか動作しない。これは、 $I_2$ を構成する定電流源として働くMOSトランジスタのドレインとソース間電圧がとれなくなり、 $I_2$ =0となる。結果として第2の差動段が動作しなくなる。この時の出力端子(OUT)における駆動電流は、詳細な解析方法は省略するが、[1]の場合と同様にして解析すると、吐き出し電流/吸い込み電流とも、次式(27)で与えられる。

$$I_{out} = I_1 \qquad -----(27)$$

# [0044]

[ 3 ] <第 2 の差動対のみが動作している場合> 上述した [ 1 ] の場合に対し、この場合の入力電圧∀inが、

$$V_{DD} > V_{in} > V_{DD} - (V_{GS(MP1/2)} + V_{DS(sat)(D)})$$

-----(28)

の時には、第2の差動段のみしか動作しない。これは、 $I_1$ を構成する定電流源として働くMOSトランジスタのドレインとソース間電圧がとれなくなり、 $I_1$ =0となる。結果として第1の差動段が動作しなくなる。この時の出力端子(OUT)における駆動電流は、詳細な解析方法は省略するが、[1]の場合と同様にして解析すると、吐き出し電流/吸い込み電流とも、次式(29)となる。

$$I_{out} = I_2$$

-----(29)

## [0045]

以上のことからわかるように、出力の駆動能力は、全て差動入力段のバイアス電流値に 直接、依存する。

[0046]

従って、駆動能力を上げるためには、差動段のバイアス電流を上げるしか方法はない。 この駆動電流は、電圧比較器回路の出力端子に繋がる寄生容量を、チャージ / ディスチャージするのに使われる。従って、動作速度はこのバイアス電流に依存する。

[0047]

入力周波数が上がってくると、この差動増幅器の出力は、正弦( s i n )波に近くなってくる。

[0048]

従って、この出力sin波を矩形波に変換するための、いわゆる波形整形するためのCMOSインバータ回路が、この差動増幅器の後段に接続される。

[ 0 0 4 9 ]

CMOSインバータは、閾値として約VDD/2に設定されているので、CMOSインバータの入力波形が、このVDD/2を横切った時を境として、これ以下の時は、出力がハイレベル(VDD)となり、これ以上の時は、出力がローレベル(VSS(GND))になる。このようにして、波形整形が行われる。CMOSインバータが多段(ここでは3段)にしてあるのは、1段では、完全に波形整形ができないためである。

[0050]

なお、特許文献1には、PチャネルMOSトランジスタよりなる差動増幅器とNチャネルMOSトランジスタよりなる差動増幅器の出力を合成し、同相入力電圧を電源電位からGNDまで広くとれるようにした構成が開示されている。

10

30

20

50

20

30

40

50

### [0051]

【非特許文献 1】 IEEE J. Solid-State Circuits. vol.29 No.12.Dec.1994 pp.1505~151 3 "A Compact Power-Efficient 3V CMOS Rail-to-Rail Input/Output Operational Amp lifier for VLSI Cell Libraries"

【特許文献 1 】特開平 3 - 6 2 7 1 2 号公報

【発明の開示】

【発明が解決しようとする課題】

[0052]

上述したように、図7の差動増幅器を使った電圧比較器回路を高速動作させるには、第1の電流源~第4の電流源の電流値を大きくする必要がある。この結果、消費電力が大となる。

[0053]

また、出力端子の波形が電源いっぱいに振れないため、この電圧比較器回路の後段に接続されるインバータのNチャネルMOSトランジスタとPチャネルMOSトランジスタの両方が同時にオンし、いわゆる貫通電流が流れ、ひいては、消費電力の増大につながる。

[0054]

さらに、図7の差動増幅器を高速動作させるために、出力駆動電流を上げようとすると、駆動電流が、第1と第2の定電流源で決まっており、これらの電流 I 1、 I 2 を増加させる必要がある。その結果、消費電力が増える。また出力端子波形が電源いっぱいに振れないのは、トランジスタが、縦積みになっていることも起因の一つである。

[0055]

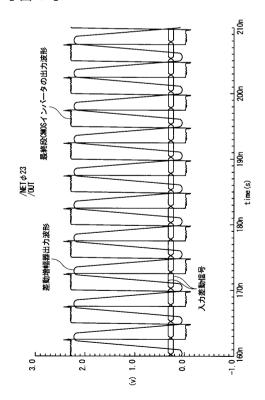

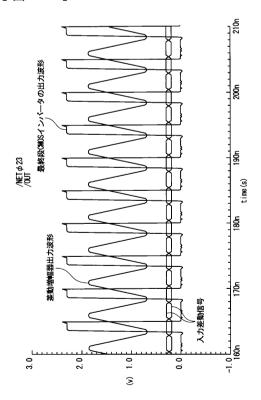

この図7の差動増幅器を、図9に示した構成とし、入力差動信号の周波数を200MHz、差動振幅を±50mV、同相信号電圧を0.3Vとした時の各出力波形(シミュレーション値)を、図11に示す。

[0056]

図 1 1 をみてわかるように、入力差動信号のデューティが 5 0 % にもかかわらず、最終出力波形のデューティは 5 0 % から大きくはずれていることがわかる。

[ 0 0 5 7 ]

したがって、本発明は、このような問題点に鑑みて創案されたものであって、その目的は、簡単な回路構成で、高速動作が可能な差動増幅器及び該差動増幅器を備えた電圧比較器を提供することにある。

【課題を解決するための手段】

[0058]

本願で開示される発明は、上記目的を達成するため、概略以下の通りとされる。

[0059]

本発明の一つのアスペクト(側面)に係る差動増幅器は、差動入力信号を入力とし第1及び第2の電流源でそれぞれ駆動される第1及び第2導電型の第1及び第2の差動対を有する入力段差動段と、前記第1及び第2の差動対の差動出力の負荷をなし、前記第1の差動対の差動出力信号と前記第2の差動対の差動出力信号とそれぞれを加算して折り返し、差動出力するフォールデッドカスコード(folded cascode)型の差動段と、第1及び第2電源間に対向配置され、前記フォールデッドカスコード型の差動段の差動出力をそれぞれ入力に受け、出力同士が出力端子に共通接続された、第1及び第2導電型の第1及び第2のカレントミラー回路と、を備えている。

[0060]

本発明に係る差動増幅器において、前記フォールデッドカスコード型の差動段は、前記第1の電源と第2の電源間に、制御端子同士がそれぞれ接続されている第1乃至第3のトランジスタ対と、二つの電流源とを少なくとも含み、前記第1の電源側に接続される前記第1のトランジスタ対と前記第2のトランジスタ対は、カスコードカレントミラー回路を構成し、前記第1の差動対の差動出力は、前記第1のトランジスタ対と前記第2の下ランジスタ対との接続点に接続され、前記第2の差動対の差動出力は、前記第2の電源に一端

30

40

50

が共通接続された前記二つの電流源の他端と前記第3のトランジスタ対との接続点に接続され、前記第2のトランジスタ対の一の出力が、前記第2のカレントミラー回路の入力端に接続され、前記第3のトランジスタ対の一の出力が、前記第1のカレントミラー回路の入力端に接続される構成としてもよい。

# [0061]

本発明の他のアスペクトに係る差動増幅器においては、前記フォールデッドカスコード型の差動段は、前記第1の電源と第2の電源間に、制御端子同士がそれぞれ接続されている第1乃至第3のトランジスタ対と、二つの電流源とを少なくとも含み、前記第2の電源側に接続される前記第1のトランジスタ対と前記第2のトランジスタ対はカスコードカレントミラー回路を構成し、前記第1の差動対の差動出力は、前記第1の電源に一端が共通接続された前記二つの電流源の他端と前記第3のトランジスタ対との接続点に接続され、前記第2の差動対の差動出力は、前記第1のトランジスタ対と前記第2のトランジスタ対との接続点に接続され、前記第2のトランジスタ対の一の出力が、前記第1のカレントミラー回路の入力端に接続される構成としてもよい。

#### [0062]

本発明の他のアスペクトに係る差動増幅器においては、前記フォールデッドカスコード型の差動段は、前記第1の電源と前記第2の電源間に、第3のカレントミラー回路と、ゲート同士が接続された第1のトランジスタ対と、二つの電流源とを少なくとも備え、前記第1の差動対の差動出力は、前記第3のカレントミラー回路の入力端及び前記第1のカレントミラー回路の入力端にそれぞれ接続され、前記第1のトランジスタ対と、前記二つの電流源の接続点にそれぞれ接続され、前記第1のトランジスタ対の一の出力が、前記第2のカレントミラー回路の入力端に接続され、前記第3のカレントミラー回路の出力が、前記第2のカレントミラー回路の入力端に接続される構成としてもよい。

#### [0063]

本発明のさらに他のアスペクト(側面)に係る電圧比較器は、上記差動増幅器の出力段に波形整形回路を備えている。波形整形回路は、インバータ又はバッファ回路よりなる。

# 【発明の効果】

### [0064]

本発明によれば、入力差動段、フォールデッドカスコード差動段、電源間に対向配置された第1及び第2のカレントミラー回路を備えた簡易な構成により、高速動作を実現している。

# [0065]

本発明によれば、第1及び第2のカレントミラー回路に、電流増幅機能を持たせることで、駆動能力を増加させ、高速動作を可能にしたものである。

# [0066]

本発明によれば、波形整形の目的で、差動増幅器の出力の後段に、バッファを備え、バッファの出力を、電圧比較器の出力とする。

# 【発明を実施するための最良の形態】

# [0067]

本発明を実施するための最良の形態について図面を参照して以下に説明する。本発明は、差動入力信号を入力し互いに逆極性の第1及び第2の差動対を有する入力差動段と、前記入力差動段の差動出力に接続され、前記第1の差動対の差動出力信号と前記第2の差動対の差動出力信号とを加算するフォールデッドカスコード(folded Cascode;折り返しカスコード)型の差動段と、電源間に対向配置され、フォールデッドカスコード型の差動段の差動出力をそれぞれ入力に受け、出力同士が出力端子に共通接続された互いに逆極性の第1及び第2のカレントミラー回路(CM1、CM2)と、を備えている。入力差動段の出力電圧(差動出力)を受け、折り返して電流出力するフォールデッドカスコード型の差動段は、前記第1の差動対の差動出力信号と、前記第2の差動対の差動出力信号とを加

20

30

40

50

算し、前記フォールデッドカスコード型の差動段の出力を、前記第1及び第2のカレントミラー回路でそれぞれ折り返し出力端子から出力する。第1及び第2のカレントミラー回路に、電流増幅機能を持たせることで、駆動能力を増加させ、高速動作を可能にしたものである。本発明によれば、波形整形回路として、差動増幅器の出力の後段に、複数段のインバータ(又はバッファ回路)を備え、波形整形回路の出力を、電圧比較結果出力とする。以下実施例に即して詳説する。

# 【実施例】

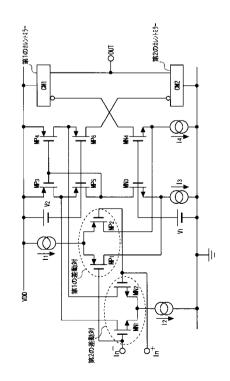

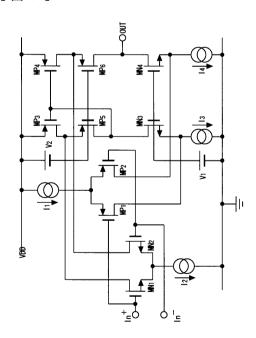

# [0068]

図1は、本発明の第1の実施例の差動増幅器の等価回路を示す図である。正転入力と反 転入力をもった電圧比較回路に適用される差動増幅器である。図1を参照すると、第1の 実 施 例 の 差 動 増 幅 器 は 、 ソ ー ス が 共 通 接 続 さ れ た 第 1 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ M P 1 と第 2 の P チャネル M O S トランジスタ M P 2 からなる第 1 の差動対と、ソースが共 通接 続 され た 第 1 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 1 と 第 2 の N チ ャ ネ ル M O S ト ラ ンジスタMN2からなる第2の差動対と、ゲートが共通接続されて第1の電圧源(V1) に接続されている第 3 と第 4 の N チャネルMOSトランジスタMN3、MN 4 と、ゲート が共通接続され、ソースが共通接続されて正電源VDDに接続されている第3と第4のP チャネルMOSトランジスタMP3、MP4と、ゲートが共通接続されて第2の電圧源( V2)に接続されている第5と第6のPチャネルMOSトランジスタMP5、MP6と、 入 力 が 第 4 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 4 の ド レ イ ン に 接 続 さ れ 、 共 通 端 子 が 正 電源VDDに接続されている第1のカレントミラー回路CM1と、入力が第6のPチャネ ル M O S トランジス タ M P 6 の ド レ イ ン に 接 続 さ れ 、 共 通 端 子 が 負 電 源 端 子 ( G N D ) に 接続されている第2のカレントミラー回路CM2と、第1の差動対を構成するPチャネル MOSトランジスタMP1、MP2の共通に接続されたソースと正電源VDD間に接続さ れる 第 1 の 定 電 流 源 ( I 1 ) と 、 第 2 の 差 動 対 を 構 成 す る N チャ ネ ル M O S ト ラ ン ジ ス タ MN1、MN2の共通に接続されたソースと負電源(GND)間に接続された第2の定電 流 源 ( I 2 ) と 、 第 3 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 3 の ソ ー ス と 負 電 源 ( G N D ) 間 に 接 続 さ れ た 第 3 の 定 電 流 源 ( I 3 ) と 、 第 4 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 4のソースと負電源(GND)間に接続された第4の定電流源(I4)と、を備えている

# [0069]

第 1 の差動対を構成する第 1 の P チャネル M O S トランジスタ M P 1 のドレインが第 3 の N チャネル M O S トランジスタ M N 3 のソースに接続され、第 1 の差動対を構成する第 2 の P チャネル M O S トランジスタ M P 2 のドレインは第 4 の N チャネル M O S トランジスタ M N 4 のソースに接続されている。

# [0070]

20

30

40

0

[0071]

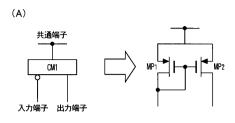

ここで、カレントミラー回路の具体的な構成例について示す。図4は、図1の第1のカレントミラー回路CM1(電流吐き出し型)と第2のカレントミラー回路CM2(電流吸い込み型)の構成例である。図4(A)を参照すると、図1における第1のカレントミラー回路CM1は、2つのPチャネルMOSトランジスタMP1とMP2で構成され、各々のソースとゲートがお互いに共通接続される。そしてPチャネルMOSトランジスタMP1のゲートとドレインを共通接続してカレントミラー回路CM1の入力端子となり、PチャネルMOSトランジスタMP2のドレインがカレントミラー回路CM1の出力端子となる。そして、共通接続したソースがカレントミラー回路の共通端子となる。

[0072]

次に、図4(B)を参照すると、図1における第2のカレントミラー回路CM2は、2つのNチャネルMOSトランジスタMN1とMN2で構成され、各々のソースとゲートがお互いに共通接続される。そしてNチャネルMOSトランジスタMN1のゲートとドレインを共通接続してカレントミラー回路の入力端子となり、NチャネルMOSトランジスタMN2のドレインがカレントミラー回路CM2の出力端子となる。そして、共通接続したソースがカレントミラー回路CM2の共通端子となる。

[0073]

次に、図1で示した差動増幅器を使った電圧比較器回路についての構成例を示す。図9に示した、従来例と同じように、差動増幅器回路の後段に、CMOSインバータ(図10)を3段縦続接続する。

[0074]

図 1 の差動増幅器について詳細な説明を行う。この差動増幅器は、いわゆるフォールデッドカスコード型の差動増幅器を応用したものである。ここで、本回路の動作を説明する

[0075]

<第1と第2の差動対の両方が動作している場合>

$I_{D(MN4)} = I_4 - I_{D(MP2)} = I_4 - I_1$  -----(30)  $I_{D(MN3)} = I_3 - I_{D(MP1)} = I_3$  -----(31)

[0076]

ここで、I」とIュとIュの関係を以下のようにする。

$$I_3 = I_4 \ge I_1$$

----(32)

## [0077]

一方、第 5 の P チャネル M O S トランジス g M P 5 のドレイン電流  $I_{D(MP5)}$  は第 3 の N チャネル M O S トランジス g M N 3 のドレイン電流  $I_{D(MN3)}$  と等しいので、次式が成り立つ。

$$I_{D(MP5)} = I_{D(MD73)} \qquad -----(33)$$

10

20

30

## [0078]

$$I_{D(MP3)} = I_{D(MP5)} + I_{D(MP1)} = I_3 + I_2$$

-----(34)

# [0079]

第4のPチャネルMOSトランジスタMP4は第3のPチャネルMOSトランジスタMP3と各々のゲートとソースが共通接続されているので、各々のドレイン電流は等しくなる。従って第4のPチャネルMOSトランジスタMP4のドレイン電流I<sub>D(MP4)</sub>は、次式で与えられる。

$$I_{D(MP4)} = I_{D(MP3)} = I_3 + I_2$$

----(35)

## [0800]

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MP2)} = I_3 + I_2$$

-----(36)

# [0081]

上述した(30)式と(36)式で示した電流がそれぞれ第1と第2のカレントミラー回路CM1、CM2の入力電流となる。ここで第1と第2のカレントミラー回CM1、CM2路の入力電流と出力電流比は、次式で与えられる。

40

50

## [0082]

ここで、 k > 1 の特性をもつものとすると、出力端電流 I 。 u t は、第 1 と第 2 のカレントミラー回路出力電流の加算になるので、出力端に流れ込む電流を正として、次式( 3 8 )で与えられる。

$$I_{out} = k(I_3 + I_2) - k(I_4 - I_1)$$

----(38)

## [0083]

ここで I₃ = I₄ であることから、結果的に、出力端電流 I。utは、次式の電流吸い

込み能力を持ち、ローレベルとなる。

$$I_{out} = k(I_1 + I_2)$$

-----(39)

### [0084]

電位的には、ほぼ負電源(GND)の0Vとなる。

#### [0085]

$$I_{D(MN4)} = I_4 - I_{D(MP2)} = I_4$$

-----(40)

$I_{D(MN3)} = I_3 - I_{D(MP1)} = I_3 - I_1$  -----(41)

#### [0086]

一方、第 5 の P チャネル M O S トランジスタ M P 5 のドレイン電流  $I_{D(MP5)}$  は第 3 の N チャネル M O S トランジスタ M N 3 のドレイン電流  $I_{D(MN3)}$  と等しいので、次式( 4 2 )が成り立つ。

$$I_{D(MP5)} = I_{D(MP3)}$$

----(42)

## [0087]

$I_{D\ (MP5)}=I_3-I_1$ 、 $I_{D\ (MN1)}=0$ 、だから、次式(43)が成り立つ

$$I_{D(MP3)} = I_{D(MP5)} + I_{D(MN1)} = I_3 - I_1$$

-----(43)

### [0088]

第4のPチャネルMOSトランジスタMP4は第3のPチャネルMOSトランジスタMP3と各々のゲートとソースが共通接続されているので、各々のドレイン電流は等しくなる。従って、第4のPチャネルMOSトランジスタMP4のドレイン電流I<sub>D(MP4)</sub>も、同様に次式(44)で与えられる。

$$I_{D(MP4)} = I_{D(MP3)} = I_3 - I_1$$

----(44)

# [0089]

また、第6の P チャネル M O S トランジス g M P 6 のドレイン電流  $I_{D(MP6)}$  は、第4の P チャネル M O S トランジス g M P 4 のドレイン電流  $I_{D(MP4)}$  から第 2 の N チャネル M O S トランジス g M N 2 のドレイン電流  $I_{D(MN2)}$  を引いた値になり、この状態ではこの  $I_{D(MN2)}$  が  $I_{2}$  であるから、次式で与えられる。

20

30

50

20

30

40

50

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MP2)} = I_3 - I_1 - I_2$$

----(45)

# [0090]

上式(40)と(45)で示した電流が、それぞれ第1と第2のカレントミラー回路 CM1、CM2の入力電流となる。

### [0091]

従って、出力端電流 I。utは、出力端から吐き出す電流を正として、次式(46)で与えられる。

$$I_{out} = kI_4 - k(I_3 - I_1 - I_2)$$

----(46)

# [0092]

ここで  $I_3 = I_4$  であることから、結果的に、出力端電流  $I_{out}$  は次式(47)の電流吐き出し能力を持ち、ハイレベルとなる。

$$I_{out} = k(I_1 + I_2)$$

-----(47)

### [0093]

電位的にはほぼ正電源のVDDとなる。

#### [0094]

ここで、(39)式と(47)式をみてわかるように、ローレベル時の吸い込み電流能力とハイレベル時の吐き出し電流能力は、同じ電流値であるため、負荷に寄生容量がついた場合にでも、立ち上がり波形と立ち下がり波形は対称となり、これを波形整形したディジタル波形も、デューティ50%の出力が得られる。

### [0095]

以上の説明は、Nチャネルトランジスタで構成された差動対とPチャネルトランジスタで構成された差動対の両方が動作している時の説明である。入力差動信号の同相信号電圧が下がってくるとNチャネルで構成された差動対が動作しなくなる。逆に入力差動信号の同相信号電圧が上がってくるとPチャネルで構成された差動対が動作しなくなる。この時の動作説明を以下に行う。

# [0096]

< 第 1 の差動対のみが動作している場合 >

図 1 において、 N チャネル差動段をバイアスする電流源 I 2 は通常 N チャネル M O S トランジスタで構成される。この時、 N チャネル差動段が正常動作する入力電圧の最低電圧 V<sub>in (min)</sub> は、次式(48)で与えられる。

$$V_{in(\min.)} = V_{GS(MN1/2)} + V_{DS(sat)(D)} \qquad -----(48)$$

## [0097]

V <sub>G S ( M N 1 / 2 )</sub> : N チャネル M O S トランジスタ M N 1 / 2 のゲート - ソース間 雷 F

V<sub>DS(sat)(I2)</sub>:電流源I<sub>2</sub>を構成するNチャネルMOSトランジスタの飽 和点でのドレイン・ソース間電圧(5極管領域で動作するぎりぎりの電圧)

#### [0098]

2 の差動対の方は入力電圧範囲外であるため、動作しない。すなわち、第 1 の N チャネル M O S トランジスタ M N 1 と第 2 の N チャネル M O S トランジスタ M N 2 の両方のドレイン電流がゼロとなる。

# [0099]

この時の各トランジスタのバイアス電流状態をみると、第3のNチャネルMOSトランジスタMN3のドレイン電流を $I_{D(MN3)}$ とし、第4のNチャネルMOSトランジスタMN4のドレイン電流を $I_{D(MN4)}$ として、それぞれ、次式(49)、(50)で与えられる。

$$I_{D(M0N)} = I_4 - I_1$$

-----(49)

$I_{D(M0N)} = I_3$  -----(50)

### [0100]

一方、第 5 の P チャネル M O S トランジス タ M P 5 のドレイン電流  $I_{D(MP5)}$  は、第 3 の N チャネル M O S トランジス タ M N 3 のドレイン電流  $I_{D(MN3)}$  と同じであることから、次式(5 1)で与えられる。

$$I_{D(MP5)} = I_{D(M073)}$$

----(51)

### [0101]

$$I_{D(MP3)} = I_{D(MP5)} = I_3$$

----(52)

# [0102]

第4のPチャネルMOSトランジスタMP4は第3のPチャネルMOSトランジスタMP3と各々のゲートとソースが共通接続されているので、各々のドレイン電流は等しくなる。従って、第4のPチャネルMOSトランジスタMP4のドレイン電流 I<sub>D(MP4)</sub>は、次式(53)で与えられる。

$$I_{D(MP4)} = I_{D(MP3)} = I_3$$

-----(53)

# [0103]

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MN2)} = I_3$$

-----(54)

#### [ 0 1 0 4 ]

従って、この時、出力端子OUTはローレベルとなり、その時の吸い込み電流能力 I。 u t は、次式(55)で与えられる。

# [0105]

$$I_{out} = kI_3 - k(I_4 - I_1) = kI_1$$

-----(55)

40

20

(21)

$$\begin{split} I_{D(MDV4)} &= I_4 - I_{D(MP2)} = I_4 & -----(56) \\ I_{D(MDV3)} &= I_3 - I_{D(MP1)} = I_3 - I_1 & -----(57) \end{split}$$

[0107]

一方、第 5 の P チャネル M O S トランジスタ M P 5 のドレイン電流  $I_{D(MP5)}$  は第 3 の N チャネル M O S トランジスタ M N 3 のドレイン電流  $I_{D(MN3)}$  と同じであることから、次式( 5 8 )で与えられる。

$$I_{D(MP5)} = I_{D(MN3)} \qquad -----(58)$$

[0108]

また、第3の P チャネル M O S トランジスタ M P 3 のドレイン電流  $I_{D(MP3)}$  は、第5の P チャネル M O S トランジスタ M P 5 のドレイン電流  $I_{D(MP5)}$  と第1の N チャネル M O S トランジスタ M N 1 のドレイン電流  $I_{D(MN1)}$  の加算であるが、この状態では、  $I_{D(MN1)}$  = 0 であるから、次式で与えられる。

$$I_{D(MP3)} = I_{D(MP5)} = I_3 - I_1$$

----(59)

[0109]

第4のPチャネルMOSトランジスタMP4は、第3のPチャネルMOSトランジスタMP3と各々のゲートとソースが共通接続されているため、各々のドレイン電流は等しくなる。従って、第4のPチャネルMOSトランジスタMP4のドレイン電流I<sub>D(MP4</sub>、は、次式(60)で与えられる。

[0110]

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MP2)} = I_3 - I_1$$

-----(61)

[0111]

従って、この時、出力端子OUTはハイレベルとなり、その時の吐き出し電流能力 I。 u t は次式(62)で与えられる。 10

20

30

40

50

$$I_{out} = kI_4 - k(I_3 - I_1) = kI_1$$

----(62)

### [0112]

< 第 2 の差動対のみが動作している場合 >

図 1 において、 P チャネルトランジスタ差動対をバイアスする電流源 I <sub>1</sub> は通常 P チャネル M O S トランジスタで構成される。この時、 P チャネル差動段が正常動作する入力電圧の最高電圧 V <sub>i n (max.)</sub> は、次式( 6 3 )で与えられる。

# [0113]

$V_{GS(MP1/2)}: P$  チャネルMOSトランジスタMP1/2のゲート・ソース間電圧

V<sub>DS(sat)(I1)</sub>:電流源I<sub>1</sub>を構成するPチャネルMOSトランジスタの飽和点でのドレイン・ソース間電圧(5極管領域で動作するぎりぎりの電圧)

# [0114]

入力電圧がこの $V_{in}$  ( $m_{ax}$ .) 以上の場合、 $P_{in}$  アキャネル MOS トランジスタ差動対が動作をしない。従って、この場合、 $N_{in}$  アキネルトランジスタ差動対のみの動作となる。この状況において、まず、 $I_{in}$  側が $I_{in}$  より高い電圧入力されたと仮定すると、第2の差動対のバイアス電流  $I_{in}$  は全て第1の $N_{in}$  チャネル MOS トランジスタ MN1の方に流れる。そして第2の $N_{in}$  チャネル MOS トランジスタ MN2の方の電流はゼロとなる。一方、第1の差動対の方は入力電圧範囲外であるため、動作しない。すなわち、第1の $P_{in}$  チャネル MOS トランジスタ MP1と第2の $P_{in}$  チャネル MOS トランジスタ MP1と第2の $P_{in}$  アナマネル MOS トランジスタ MN3のドレイン電流がゼロとなる。この時の各トランジスタのバイアス電流状態をみると、第3の Nチャネル MOS トランジスタ MN3のドレイン電流を  $I_{in}$  ( $in_{in}$  MN3) とし、第4の Nチャネル MOS トランジスタ MN3のドレイン電流を  $I_{in}$  ( $in_{in}$  MN3) とすると、次式(64)、(65)が成り立つ。

$$I_{D(MN4)} = I_4 - I_{D(MP2)} = I_4$$

-----(64)

$I_{D(MN3)} = I_3 - I_{D(MP1)} = I_3$  -----(65)

# [0115]

$$I_{D(MP5)} = I_{D(MDV3)} \qquad ------(66)$$

### [0116]

$$I_{D(MP3)} = I_{D(MP5)} + I_{D(MN1)} = I_3 + I_2$$

-----(67)

# [0117]

第 4 の P チャネル M O S トランジスタ M P 4 は第 3 の P チャネル M O S トランジスタ M P 3 と各々のゲートとソースが共通接続されているので、各々のドレイン電流は等しくな る。従って、第 4 の P チャネル M O S トランジスタ M P 4 のドレイン電流  $I_{D\ (MP4)}$  は、次式 ( 6 8 ) で与えられる。

$$I_{D(MP4)} = I_{D(MP3)} = I_3 + I_2$$

----(68)

### [0118]

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MN2)} = I_3 + I_2$$

-----(69)

# [0119]

従って、この時、出力端子OUTはローレベルとなる。その時の吸い込み電流能力I。 u t は、第1と第2のカレントミラー回路の入出力電流比が1:kであるから、次式(7 0)が成り立つ。

$$I_{out} = k(I_3 + I_2) - kI_4 = kI_2$$

----(70)

### [0120]

次に、今度はI n  $^-$  側がI n  $^+$  より低い電圧入力されたと仮定すると、本実施例の回路は比較器回路動作をするので、第2の差動対のバイアス電流I  $_2$  は全て第2のNチャネルMOSトランジスタMN2の方に流れる。そして第1のNチャネルMOSトランジスタMN1の方の電流は0となる。一方、第1の差動対は入力電圧範囲外の入力電圧のため、動作しない。すなわち第1のPチャネルMOSトランジスタMP1と第2のPチャネルMOSトランジスタMP2の両方のドレイン電流がゼロとなる。この時の各トランジスタのバイアス電流状態をみると、第3のNチャネルMOSトランジスタMN3のドレイン電流を $I_{D(MN3)}$  とし、第4のNチャネルMOSトランジスタMN4のドレイン電流を $I_{D(MN4)}$  とし、次式(71)、(72)で与えられる。

$$\begin{split} I_{D(M0/4)} &= I_4 - I_{D(M/2)} = I_4 & ------(71) \\ I_{D(M0/3)} &= I_3 - I_{D(M/1)} = I_3 & ------(72) \end{split}$$

# [0121]

一方、第 5 の P チャネル M O S トランジスタ M P 5 のドレイン電流  $I_{D(MP5)}$  は第 3 の N チャネル M O S トランジスタ M N 3 のドレイン電流  $I_{D(MN3)}$  と同じであるので、次式( 7 3 )が成り立つ。

$$I_{D(MP5)} = I_{D(M0V3)} \qquad -----(73)$$

## [0122]

$$I_{D(MP3)} = I_{D(MP5)} = I_3$$

-----(74)

10

20

20

30

40

50

### [0123]

第4のPチャネルMOSトランジスタMP4は、第3のPチャネルMOSトランジスタMP3と各々のゲートとソースが共通接続されているため、各々のドレイン電流は等しくなる。従って、第4のPチャネルMOSトランジスタMP4のドレイン電流I<sub>D(MP4</sub>、は、次式(75)で与えられる。

$$I_{D(MP4)} = I_{D(MP3)} = I_3$$

-----(75)

# [0124]

$$I_{D(MP6)} = I_{D(MP4)} - I_{D(MP2)} = I_3 - I_2$$

-----(76)

# [0125]

従って、この時、出力端子OUTはハイレベルとなり、その時の吐き出し電流能力I。 u t は次式(77)で与えられる。

$$I_{out} = kI_4 - k(I_3 - I_2) = kI_2$$

----(77)

### [0126]

次に、図 4 に示したカレントミラー回路の動作について説明を行う。例えば図 4 ( A )において、第 1 、第 2 の P チャネル M O S トランジスタ M P 1 と M P 2 のゲート幅をそれぞれ W  $_{\rm MP1}$  、 W  $_{\rm MP2}$  、ゲート長をそれぞれ L  $_{\rm MP1}$  、 L  $_{\rm MP2}$  とした時、次式( 7 8 )の関係が成り立つものとする。

$$\frac{W_{MP1}}{L_{MP1}}: \frac{W_{MP2}}{L_{MP2}} = 1: k \qquad -----(78)$$

# [0127]

カレントミラー回路の入力電流  $I_{in}$  と出力電流  $I_{out}$  の関係は、次式(79)となる。

$$I_{out} = kI_{in} \qquad -----(79)$$

# [0128]

これは、MOSトランジスタのゲート・ソース間電圧 V<sub>GS</sub>とドレイン電流 I<sub>G</sub>の関係を示した(2)式、(3)式、(4)式をみてわかるように、ドレイン電流は、W/Lに比例するからである。

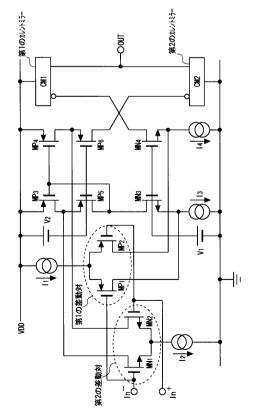

#### [0129]

図2は、本発明の第2の実施例の差動増幅器の構成を示す図である。図2の構成は、図1のPチャネルMOSトランジスタMP3、MP4を、それぞれNチャネルMOSトランジスタMN3、MN4とし、図1のPチャネルMOSトランジスタMP5、MP6を、NチャネルMOSトランジスタMN5、MN6とし、図7の吸い込み型電流源I3、I4と、NチャネルMOSトランジスタMN3、MN4を、それぞれ、吐出型電流源I3、I4

30

40

50

、 P チャネル M O S トランジスタ M P 3 、 M P 4 とし、 図 1 の極性を対称として構成した ものである。

### [0130]

図2を参照すると、第2の実施例の差動増幅器は、第1のPチャネルMOSトランジス タ M P 1 と第 2 の P チャネル M O S トランジスタ M P 2 で 構成される第 1 の差動対と、第 1 の N チャネル M O S トランジスタ M N 1 と第 2 の N チャネル M O S トランジスタ M N 2 で構成される第2の差動対とを備え、ゲートが共通接続され、各々のソースが共通接続さ れた第3と第4のNチャネルMOSトランジスタMN3、MN4と、ゲートが共通接続さ れ、 かつ 第 1 の 電 圧 源 に 接 続 さ れ た 第 5 と 第 6 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 5 、 MN6と、ゲートが共通接続され、かつ第2の電圧源に接続された第3と第4のPチャネ ル M O S トランジス タ M P 3 、 M P 4 と、入力が 第 6 の N チャネル M O S トランジス タ M N6のドレインに接続され、共通端子が正電源(VDD)に接続された第1のカレントミ ラー回路CM1と、入力が第4のPチャネルMOSトランジスタMP4のドレインに接続 され、共通端子が負電源端子(GND)に接続された第2のカレントミラー回路CM2と 、第1の差動対の共通に接続されたソースと正電源VDD間に接続される第1の定電流源 (I1)と、第2の差動対の共通に接続されたソースと負電源(GND)間に接続された 第 2 の 定 電 流 源 ( I 2 ) と 、 第 3 の P チャ ネル M O S ト ラ ン ジ ス タ M P 3 の ソ ー ス と 正 電 源(VDD)間に接続された第3の定電流源(I3)と、第4のPチャネルMOSトラン ジスタMP4のソースと正電源(VDD)間に接続された第4の定電流源(I4)とから 構成され、第1の差動対を構成する第1のPチャネルMOSトランジスタMP1のドレイ ン が 第 5 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 5 の ソ - ス と 共 通 接 続 さ れ 、 第 1 の 差 動 対 を 構 成 す る 第 2 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ M P 2 の ド レ イ ン が 第 6 の N チ ャ ネ ル M O S トランジスタ M N 6 のソースに共通接続され、第 2 の差動対を構成する第 1 の N チャ ネルMOSトランジスタMN1のドレインが第3のPチャネルMOSトランジスタMP3 のソースに共通接続され、第2の差動対を構成する第2のNチャネルMOSトランジスタ MN2のドレインが第4のPチャネルMOSトランジスタMP4のソースに共通接続され . 第 3 の N チャネル M O S トランジスタ M N 3 の ゲートが第 5 の N チャネル M O S トラン ジス タ M N 5 の ド レ イ ン と 第 3 の P チ ャ ネ ル M O S ト ラ ン ジ ス タ M P 3 の ド レ イ ン に 共 通 接続され、第1のカレントミラー回路CM1の出力と第2のカレントミラー回路CM2の 出力を共通接続して出力端子OUTとし、第1のPチャネルMOSトランジスタMP1の ゲ ー ト と 第 1 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 1 の ゲ ー ト を 共 通 接 続 し て 反 転 入 力 端 子In`とし、第2のPチャネルMOSトランジスタMP2のゲートと第2のNチャネル MOSトランジスタMN2のゲートを共通接続して正転入力端子In + とする。ここで、 第 1 と第 2 のカレントミラー回路 C M 1 、 C M 2 は、入力電流と出力電流比が 1 : k ( k > 1 )である。そして、従来例と同様に、差動増幅器の後段に3段縦続接続したCMOS インバータを接続して、電圧比較器回路を構成する。

# [0131]

図 2 についての動作は、基本的に、図 1 における動作と同じであり、回路が対称になっただけなので、その説明を省略する。

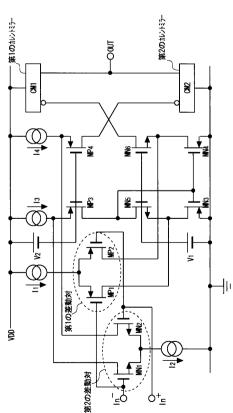

### [0132]

図3は、本発明の第3の実施例の差動増幅器の構成を示す図である。図3を参照すると、第3の実施例の差動増幅器は、第1のPチャネルMOSトランジスタMP1と第2のPチャネルMOSトランジスタMP1と第2のPチャネルMOSトランジスタMN1と第2のNチャネルMOSトランジスタMN2で構成される第2の差動対とを備え、各々のゲートが共通接続され、かつ第1の電圧源(V1)に接続された第3と第4のNチャネルMOSトランジスタMN3、MN4と、第1の差動対の共通に接続されたソースと正電源VDD間に接続される第1の定電流源(I1)と、第2の差動対の共通に接続されたソースと負電源GND間に接続された第2の定電流源(I2)と、第3のNチャネルMOSトランジスタMN4のソースと負電源

30

50

( G N D )間に接続された第 4 の定電流源( I 4 )と、入力端子が第 1 の N チャネル M O SトランジスタMN1のドレインと第3のNチャネルMOSトランジスタMN3のドレイ ンとに共通接続され、共通端子が正電源(VDD)端子に共通接続された第1のカレント ミラー回路 C M 1 と、入力端子が第 2 の N チャネル M O S トランジスタ M N 2 のドレイン と第4のNチャネルMOSトランジスタMN4のドレインとに共通接続され、共通端子が 正電源VDD端子に共通接続された第2のカレントミラー回路CM2と、入力端子が第1 のカレントミラー回路CM1の出力端子に接続され、共通端子が負電源(GND)端子に 接続された第3のカレントミラー回路CM3と、第1のPチャネルMOSトランジスタM P 1 のドレインが第 3 の N チャネル M O S トランジスタ M N 3 のソースに接続され、第 2 の P チャネル M O S トランジスタ M P 2 のドレインが第 4 の N チャネル M O S トランジス タ M N 4 のソースに接続され、 第 2 のカレントミラー回路 C M 2 の出力端子と第 3 のカレ ントミラー回路CM3の出力端子を共通接続して出力端子OUTとし、第1のPチャネル M O S トランジスタM P 1 のゲートと第 1 の N チャネル M O S トランジスタ M N 1 のゲー トを共通接続して反転入力端子In゚とし、第2のPチャネルMOSトランジスタMP2 の ゲ ー ト と 第 2 の N チ ャ ネ ル M O S ト ラ ン ジ ス タ M N 2 の ゲ ー ト を 共 通 接 続 し て 正 転 入 力 端 子 In ^ とする。 第 2 と第 3 の カ レン ト ミ ラ ー 回 路 C M 2 、 C M 3 は 、 入 力 電 流 と 出 力 電 流 比 が 1 : k ( k > 1 ) で あ る 。 差 動 増 幅 器 の 後 段 に 、 図 9 に 示 し た よ う に 、 C M O S インバータ(図10)を3段縦続接続して、電圧比較器回路を構成する。

#### [ 0 1 3 3 ]

次に、図3に示した差動増幅器の動作を説明する。図3に示した差動増幅器においても、図1、図2に示した差動増幅器と同様、入力電圧によって3つのモードをもつが、ここでは、代表して、そのなかでPチャネル差動対とNチャネル差動対の両方が動作している場合について説明を行う。

# [0134]

まずIn ̄側がIn<sup>+</sup> より高い電圧が入力され、かつ、上式(7)で示した以上の差動入力電圧だと仮定すると、図9の回路は、比較器として動作する。第1の差動対のバイでス電流I<sub>1</sub> は、全て第2のPチャネルMOSトランジスタMP2の方に流れる。そ差動対のバイアス電流I<sub>2</sub> は、全て第1のNチャネルMOSトランジスタMN1の方に流れる。一方、第2のガイアス電流 I<sub>2</sub> は、全て第1のNチャネルMOSトランジスタMN1の方に流れる。そして、第2のNチャネルMOSトランジスタMN3のドレイン電流状態をみると、第3のNチャネルMOSトランジスタMN3のドレイン電流をI<sub>D(MN3</sub>)とすると、第4のNチャネルMOSトランジスタMN4のドレイン電流 I<sub>D(MN4</sub>)は電流源 I<sub>4</sub> の値から第2のPチャネルMOSトランジスタMN4のドレイン電流 I<sub>D(MN4</sub>)は電流源 I<sub>3</sub> の値から第1のPチャネルMOSトランジスタMN3のドレイン電流 I<sub>D(MN3)</sub>を引いた値であり、第3のNチャネルMOSトランジスタMN3のドレイン電流 I<sub>D(MN3)</sub>は電流源 I<sub>3</sub> の値から第1のPチャネルMOSトランジスタMP1のドレイン電流 I<sub>D(MP1)</sub>を引いた値であるから、次式(80)、(81)が成り立つ。

$$I_{D(MP4)} = I_4 - I_{D(MP2)} = I_4 - I_1 \qquad -----(80)$$

$$I_{D(MP3)} = I_3 - I_{D(MP1)} = I_3 \qquad -----(81)$$

# [0135]

ここで、I」とIュとIュの関係を以下のようにする。

$$I_2 = I_4 \ge I_1$$

-----(82)

# [0136]

次に、第1のカレントミラー回路(CM1)の入力電流  $I_{in}$  (  $c_{M1}$  ) を求めると、この  $I_{in}$  (  $c_{M1}$  ) は第1のNチャネルMOSトランジスタのドレイン電流  $I_{D}$  ( MN

$_{1\ )}$  と第  $_{3}$  の  $_{N}$  チャネル  $_{M}$  O  $_{S}$  トランジスタのドレイン電流  $_{I\ D\ (M\ N\ 3\ )}$  の和であり、それと同じ電流が第  $_{1}$  のカレントミラー回路の出力電流  $_{I\ C\ M\ 1\ )}$  となるから、第  $_{1}$  のカレントミラー回路の入力電流:出力電流  $_{2}$   $_{1}$  1 として、次式(  $_{2}$  8 3 )が成り立つ。

$$I_{in(CM1)} = I_{D(MOV1)} + I_{D(MOV3)} = I_2 + I_3 = I_{out(CM1)}$$

-----(83)

# [0137]

次に第 2 のカレントミラー回路( C M 2 )の入力電流  $I_{in(cM1)}$  を求めると、この  $I_{in(cM1)}$  は第 2 の N チャネル M O S トランジスタのドレイン電流  $I_{D(MN2)}$  と第 4 の N チャネル M O S トランジスタのドレイン電流  $I_{D(MN4)}$  の和であるから、次式( 8 4 )が成り立つ。

$$I_{in(CM2)} = I_{D(MN2)} + I_{D(MN4)} = I_4 - I_1$$

----(84)

# [0138]

そして、第 2 のカレントミラー回路の入力電流:出力電流 = 1 : k とすると、第 2 のカレントミラー回路の入力電流  $I_{in}$  (  $C_{M2}$ ) の k 倍が第 2 のカレントミラー回路の出力電流  $I_{out}$  (  $C_{M2}$ ) となるから、次式(  $B_{in}$  5 )が成り立つ。

$$I_{out(CM2)} = kI_{in(CM2)} = k(I_4 - I_1)$$

----(85)

### [0139]

第3のカレントミラー回路(СМ3)の入力端子は第1のカレントミラー回路の出力端子と共通接続されている。従って、第3のカレントミラー回路(СМ3)の入力電流  $I_i$   $n_i$   $n_$

$$I_{in(CM3)} = I_{out(CM1)} \qquad -----(86)$$

### [0140]

そして、第3のカレントミラー回路(СМ3)の入力電流:出力電流 = 1 : k とすると、第3のカレントミラー回路(СМ3)の入力電流  $I_{in(CM3)}$  の k 倍が、第3のカレントミラー回路(СМ3)の出力電流  $I_{out(CM3)}$  となるから、次式(87)が成り立つ。

$$I_{out(CM3)} = kI_{in(CM3)} = k(I_2 + I_3)$$

-----(87)

# [0141]

従って出力端子 O U T の出力電流  $I_{out}$  は、この場合、出力端子に流れ込む方向を正として、第 3 のカレントミラー回路の出力電流  $I_{out}$  ( $c_{M3}$ ) から第 2 のカレントミラー回路の出力電流  $I_{out}$  を引いた値になり、  $I_{3}$  =  $I_{4}$  として、次式( 8 8 )が成り立つ。

$$I_{out} = I_{out(CM3)} - I_{out(CM2)} = k \big(I_2 + I_3\big) - k \big(I_4 - I_1\big) = k \big(I_1 + I_2\big) \quad --(88)$$

#### **7** 0 1 1 2 **3**

そして、出力端子 O U T はローレベルとなり、電位的にはほぼ負電源( G N D )の 0 V となる。

50

40

10

20

20

30

40

次に、今度はI n  $^{-}$  側がI n  $^{+}$  より低い電圧入力されたと仮定すると、図3の差動増幅器は、比較器の回路動作をするので、第1の差動対のバイアス電流I  $_1$  は、全て第1の P チャネル M O S トランジスタ M P 1 の方に流れる。そして、第2の P チャネル M O S トランジスタ M P 2 の方の電流はゼロとなる。一方、第2の差動対のバイアス電流I  $_2$  は、全て第2の N チャネル M O S トランジスタ M N 2 の方に流れる。そして、第1の N チャネル M O S トランジスタ M N 1 の方の電流は、ゼロとなる。この時の各トランジスタのバイアス電流状態をみると、第3の N チャネル M O S トランジスタ M N 3 のドレイン電流をI  $_{D}$   $_{C}$  M N  $_{3}$   $_{3}$  とし、第4の N チャネル M O S トランジスタ M N 4 の ドレイン電流を I  $_{D}$   $_{C}$  M N  $_{4}$   $_{0}$  として、次式(89)、(90)が成り立つ。

$$I_{D(MN4)} = I_4 - I_{D(MP2)} = I_4$$

-----(89)

$I_{D(MN3)} = I_3 - I_{D(MP1)} = I_3 - I_1$  ----(90)

[0144]

ここで、I₁とI₃とI₄の関係を以下のようにする。

$$I_3 = I_4 \ge I_1$$

-----(91)

[0145]

次に第1のカレントミラー回路(CM1)の入力電流  $I_{in(CM1)}$  を求めると、この  $I_{in(CM1)}$  は第1の N チャネル M O S トランジスタのドレイン電流  $I_{D(MN1)}$  と第3の N チャネル M O S トランジスタのドレイン電流  $I_{D(MN3)}$  の和であり、それと同じ電流が第1のカレントミラー回路の出力電流  $I_{out}$  (CM1) となるから、第1のカレントミラー回路の入力電流:出力電流 = 1:1として、次式(92)が成り立つ

$$I_{in(\mathit{CM}1)} = I_{\mathit{D(MMV1)}} + I_{\mathit{D(MMV3)}} = I_3 - I_1 = I_{\mathit{out(CM1)}} \quad -----(92)$$

[0146]

次に第 2 のカレントミラー回路( C M 2 )の入力電流  $I_{in}$   $(C_{M2})$  を求めると、この  $I_{in}$   $(C_{M1})$  は第 2 の N チャネル M O S トランジスタのドレイン電流  $I_{D(MN2})$  の和であるから、次式( 9 3 )が成り立つ。

$$I_{in(CM2)} = I_{D(MN2)} + I_{D(MN4)} = I_2 + I_4$$

----(93)

[0147]

そして、第 2 のカレントミラー回路の入力電流:出力電流 = 1 : k とすると、第 2 のカレントミラー回路の入力電流  $I_{in}$  (  $C_{M2}$ ) の k 倍が第 2 のカレントミラー回路の出力電流  $I_{nu}$  た  $C_{M2}$  となることから、次式( 9 4 )が成り立つ。

$$I_{out(CM2)} = kI_{in(CM2)} = k(I_2 + I_4) \qquad -----(94)$$

[0148]

第3のカレントミラー回路(СМ3)の入力端子は第1のカレントミラー回路の出力端子と共通接続されている。従って、第3のカレントミラー回路(СМ3)の入力電流  $I_i$   $n_i$   $n_$

$$I_{in(CM3)} = I_{out(CM1)}$$

----(95)

# [0149]

そして、第 3 のカレントミラー回路の入力電流:出力電流 = 1 : k とすると、第 3 のカレントミラー回路の入力電流  $I_{in}$  (  $C_{M3}$ ) の k 倍が第 3 のカレントミラー回路の出力電流  $I_{out}$  (  $C_{M3}$ ) となるから、次式( 9 6 )が成り立つ。

$$I_{out(CM3)} = kI_{int(CM3)} = k(I_3 - I_1)$$

-----(96)

10

### [0150]

従って、出力端子 O U T の出力電流 I 。 u t は、この場合、出力端子から流れ込む方向を正として、第 3 のカレントミラー回路の出力電流 I 。 u t (CM3) から第 2 のカレントミラー回路の出力電流 I 。 u t (CM2) を引いた値になり、 I 3 = I 4 として、次式( 9 7 )が導出される。

$$I_{out} = I_{out(CM2)} - I_{out(CM3)} = k(I_2 + I_4) - k(I_3 - I_1) = k(I_1 + I_2) - -(97)$$

# [0151]

そして、出力端子OUTはハイレベルとなり、電位的にはほぼ正電源(VDD)のOVとなる。このようにして、比較器の動作を行う。

# [0152]

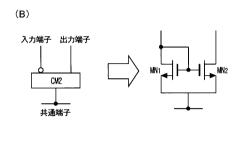

図5は、本実施例の回路シミュレーション結果の一例を示す図である。図5には、図1の差動増幅器を、図9に示した構成とし、入力差動信号の周波数を200MHz、差動振幅を±50mV、同相信号電圧を0.3Vとした時の各出力波形(シミュレーション値)が示されている。図5からわかるように、本実施例によれば、CMOSインバータの最終出力波形のデューティは、ほぼ(実質的に)50%となっていることがわかる。すなわち、従来構成のシミュレーション結果である図11に示したように、50%から大きくはずれることは無い。

# [0153]

30

20

このように、本実施例の電圧比較器回路は、特に電源電圧が低く、かつ広い入力電圧範囲をもった高速の差動インターフェース回路に適する。本実施例の回路によれば、少ない素子数で、比較的低消費電力で、入力電圧範囲が広く、高速の電圧比較器回路が実現できる。本発明は、高速差動インターフェース回路用の半導体集積回路装置に用いて好適とされる。

# [0154]

以上本発明を上記実施例に即して説明したが、本発明は上記実施例の構成にのみ限定されるものでなく、本発明の範囲内で当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

### 【図面の簡単な説明】

40

50

# [ 0 1 5 5 ]

- 【 図 1 】 本 発 明 の 第 1 の 実 施 例 の 差 動 増 幅 器 の 回 路 構 成 を 示 す 図 で あ る 。

- 【図2】本発明の第2の実施例の差動増幅器の回路構成を示す図である。

- 【図3】本発明の第3の実施例の差動増幅器の回路構成を示す図である。

- 【図4】図1、図2、図3におけるカレントミラー回路の一構成を示す図である。

- 【図5】本発明におけるシミュレーションの入出力波形を示す図である。

- 【図6】従来の差動増幅回路の回路構成を示す図である。

- 【図7】従来の差動増幅段の回路構成を示す図である。

- 【図8】図7における入出力特性を示す図である。

- 【図9】従来の電圧比較器回路の例を示す図である。

【図10】CMOSインバータの具体回路例の図である。

【図11】従来例におけるシミュレーションの入出力波形図である。

# 【符号の説明】

[0156]

CM1、CM2、CM3 カレントミラー回路

I1、I2、I3、I4 電流源(電流値)

Ιn <sup>†</sup> 非反転入力端子

In 反転入力端子

INV1~INV3 CMOSインバータ

MN1~MN6 NFャネルMOSトランジスタ

MP1~MP4 PFャネルMOSトランジスタ

V 1 、 V 2 電圧源

V D D 正電源

【図2】

【図3】

【図4】

【図5】

【図6】

# 【図7】

# 【図8】

# 【図11】

# 【図9】

# 【図10】

# フロントページの続き

F ターム(参考) 5J500 AA01 AA12 AC36 AC65 AF15 AH10 AK02 AK05 AK09 AM17 AM21 AS16 AT02 AT06 DN01 DN12 DP01

【要約の続き】 子から出力する。 【選択図】 図1