# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 109590037 B (45) 授权公告日 2021.01.26

审查员 庄海民

(21) 申请号 201811639484.9

(22) 申请日 2018.12.29

(65) 同一申请的已公布的文献号 申请公布号 CN 109590037 A

(43) 申请公布日 2019.04.09

(73) 专利权人 天津大学 地址 300072 天津市南开区卫津路92号

(72) 发明人 段学欣 刘建涛 韩子钰 陈雪娇 刘展宁

(74) 专利代理机构 北京华夏正合知识产权代理 事务所(普通合伙) 11017 代理人 韩登营 曲芳兵

(51) Int.CI.

B01L 3/00 (2006.01)

权利要求书2页 说明书6页 附图3页

#### (54) 发明名称

亚微米流道微流控芯片的制作方法

#### (57) 摘要

本发明公开了一种亚微米流道微流控芯片 的制作方法,包括步骤:A、在一基底上沉积用作 底电极的金属钼;并刻蚀出指定形状的底电极; B、在底电极上沉积覆盖整个基底的氮化铝薄膜; C、在氮化铝薄膜上沉积覆盖整个基底的PSG,并 利用反应离子刻蚀方法刻蚀PSG以刻蚀出流道的 形状,将刻蚀后剩余的PSG作为流道牺牲层;D、在 流道牺牲层上沉积覆盖整个基底的氮化铝薄膜; 并在其上沉积用作顶电极的金属钼;并刻蚀出指 定形状的顶电极:E、在顶电极上沉积覆盖整个基 底的氮化铝薄膜作为流道结构层,并在其上刻蚀 出流道出入口:G、利用氢氟酸溶液释放流道牺牲 四层,以获取亚微米流道微流控芯片;其中,顶电极 与底电极成对设置,且均与流道牺牲层重叠设 置。由上,本申请可以实现精准地制备目标亚微 米流道微流控芯片。

- 1.一种亚微米流道微流控芯片的制作方法,其特征在于,包括步骤:

- A、在一基底上沉积用作底电极的金属钼;并刻蚀出指定形状的底电极;

- B、在所述底电极上沉积覆盖整个基底的氮化铝薄膜;

- C、在所述氮化铝薄膜上沉积覆盖整个基底的PSG,并利用反应离子刻蚀方法刻蚀PSG以刻蚀出流道的形状,将刻蚀后的PSG作为流道牺牲层;

- D、在所述流道牺牲层上沉积覆盖整个基底的氮化铝薄膜;并在其上沉积用作顶电极的金属钼;并刻蚀出指定形状的顶电极;

- E、在所述顶电极上沉积覆盖整个基底的氮化铝薄膜作为流道结构层,并在其上刻蚀出流道出入口:

- G、利用氢氟酸溶液释放所述流道牺牲层,以获取亚微米流道微流控芯片;

- 其中,所述顶电极与所述底电极成对设置,且均与所述流道牺牲层重叠设置。

- 2.根据权利要求1所述的方法,其特征在于,所述步骤A之前,还包括步骤:

- A'、将所述基底单面抛光以及进行去除表面杂质的处理。

- 3.根据权利要求2所述的方法,其特征在于,步骤A'所述去除表面杂质的处理,包括:

- 将单面抛光的基底分别利用食人鱼和氢氟酸溶液去除表面的杂质;其中,所述食人鱼为体积比为3:1的浓硫酸和双氧水。

- 4.根据权利要求2所述的方法,其特征在于,步骤A所述沉积用作底电极的金属钼之前,还包括:

利用光刻工艺将掩膜版底电极槽图形转移到所述基底上,进行刻蚀,刻蚀出底电极槽, 并沉积氮化铝薄膜。

5.根据权利要求1所述的方法,其特征在于,所述步骤E,包括:

利用光刻工艺将流道的出入口和电极焊盘图形转移到所述流道结构层上;并刻蚀出与所述流道牺牲层的端部连接的流道的出入口,以及刻蚀出与所述底电极及顶电极分别连接的电极焊盘图形并在所述电极焊盘图形上沉积金电极。

6.根据权利要求1所述的方法,其特征在于,所述流道牺牲层的高度为700nm,宽度1μm; 所述氢氟酸溶液中氢氟酸和水的体积比为1:5;

步骤C所述刻蚀出流道的形状的方式为:利用反应离子刻蚀方法刻蚀。

- 7.一种基于牺牲层工艺的亚微米流道微流控芯片的制作方法,其特征在于,包括步骤:

- M1、在一基底上沉积用作底电极的金属钼;并刻蚀出指定形状的底电极;

- M2、在所述底电极上沉积覆盖整个基底的氮化铝薄膜:

- M3、在所述氮化铝薄膜上沉积覆盖整个基底的PSG,并刻蚀出流道的形状,将刻蚀后的PSG作为流道牺牲层;

- M4、在所述流道牺牲层上沉积覆盖整个基底的氮化铝薄膜作为流道结构层,并在其上刻蚀出流道出入口;

- M5、利用氢氟酸溶液释放所述流道牺牲层;

- 其中,所述底电极成对设置,每对底电极分别设置于所述流道牺牲层的底部的两侧且与流道牺牲层重叠设置。

- 8.根据权利要求1所述的方法,其特征在于,所述步骤M1之前,还包括步骤:

- M1'、将所述基底单面抛光以及进行去除表面杂质的处理;其中,所述去除表面杂质的

处理,包括:

将单面抛光的基底分别利用食人鱼和氢氟酸溶液去除表面的杂质;其中,所述食人鱼为体积比为3:1的浓硫酸和双氧水。

9.根据权利要求2所述的方法,其特征在于,步骤M1所述沉积用作底电极的金属钼之前,还包括:

利用光刻工艺将掩膜版底电极槽图形转移到所述基底上,进行刻蚀,刻蚀出底电极槽,并沉积氮化铝薄膜。

10.根据权利要求7所述的方法,其特征在于,所述步骤M4,包括:

利用光刻工艺将流道的出入口和电极焊盘图形转移到所述流道结构层上;并刻蚀出与所述流道牺牲层的端部连接的流道的出入口,以及刻蚀出与所述底电极连接的电极焊盘图形并在所述电极焊盘图形上沉积金电极。

# 亚微米流道微流控芯片的制作方法

#### 技术领域

[0001] 本发明涉及生命科学与医学领域,并且特别地,涉及亚微米流道微流控芯片的制作方法。

## 背景技术

[0002] 微流控芯片技术作为一种新兴的技术,其用在医疗上,具有检测所需样本量和试剂量少的特点,吸引了众多科研院所及企业的关注。微流控芯片的主要特征是芯片容纳流体的有效结构为微流道,即芯片流道至少在一个维度上为微米级尺寸。

[0003] 在制备亚微米流道微流控芯片时,由于电极和流道之间的对准的误差需要控制在 1微米以内,因此目前的手动对准方式无法保证精度。无法精准地制备目标亚微米流道微流 控芯片。

[0004] 因此,目前亟需一种亚微米流道微流控芯片的制作方法,无需使用手动对准电极和流道,即可精准地制备目标亚微米流道微流控芯片。

#### 发明内容

[0005] 有鉴于此,本发明的主要目的在于提供了亚微米流道微流控芯片的制作方法,以实现精准地制备目标亚微米流道微流控芯片。

[0006] 本申请提供一种亚微米流道微流控芯片的制作方法,包括步骤:

[0007] A、在一基底上沉积用作底电极的金属钼;并刻蚀出指定形状的底电极;

[0008] B、在所述底电极上沉积覆盖整个基底的氮化铝薄膜;

[0009] C、在所述氮化铝薄膜上沉积覆盖整个基底的PSG,并刻蚀出流道的形状,将刻蚀后剩余的PSG作为流道牺牲层:

[0010] D、在所述流道牺牲层上沉积覆盖整个基底的氮化铝薄膜;并在其上沉积用作顶电极的金属钼;并刻蚀出指定形状的顶电极;

[0011] E、在所述顶电极上沉积覆盖整个基底的氮化铝薄膜作为流道结构层,并在其上刻蚀出流道出入口;

[0012] G、利用氢氟酸溶液释放所述流道牺牲层,以获取亚微米流道微流控芯片:

[0013] 其中,所述顶电极与所述底电极成对设置,且均与所述流道辆牲层重叠设置。

[0014] 由上,本申请通过上述流程制得的亚微米流道微流控芯片,无需使用手动对准电极和流道,即可精准地制备目标亚微米流道微流控芯片,本申请以PSG作为流道牺牲层,其尺寸为亚微米级别,通过对其释放精确地获取亚微米流道。

[0015] 优选地,所述步骤A之前,还包括步骤:

[0016] A'、将所述基底单面抛光以及进行去除表面杂质的处理。

[0017] 由上,有利于增加基底与其上沉积的层与的贴合度。

[0018] 优选地,步骤A'所述去除表面杂质的处理,包括:

[0019] 将单面抛光的基底分别利用食人鱼和氢氟酸溶液去除表面的杂质:其中,所述食

人鱼为体积比为3:1的浓硫酸和双氧水。

[0020] 由上,有利于增加基底与其上沉积的层与的贴合度。

[0021] 优选地,步骤A所述沉积用作底电极的金属钼之前,还包括:

[0022] 利用光刻工艺将掩膜版底电极槽图形转移到所述基底上,进行刻蚀,刻蚀出底电极槽,并沉积氮化铝薄膜。

[0023] 由上,由于通常流道和电极的位置在设计时就已经固定,且检测电极和敏感流道距离非常近。为了得到光滑平整的流道,在设计时需要将检测的底电极埋在高阻硅材质的基底上,需要在基底上将底电极的槽挖出,在刻蚀出底电极槽的整个基底上沉积氮化铝薄膜(利用物理气相沉积,相当于在基底表面整体生成一层,整体高度同时变化),因此基于前述刻蚀出的底电极槽,此时仍然存在一个与所述底电极槽形状一致的凹槽,使后续的在其上沉积的金属钼电极(底电极)可以沉积到该凹槽中,并将不需要的金属钼电极刻蚀掉,使流道内表面更加平整。同时,沉积氮化铝薄膜的好处是在下一步刻蚀金属钼(底电极)时作为阳挡层保护硅基底不被刻蚀。

[0024] 优选地,所述步骤E,包括:

[0025] 利用光刻工艺将流道的出入口和电极焊盘图形转移到所述流道结构层上;并刻蚀出与所述流道牺牲层的端部连接的流道的出入口,以及刻蚀出与所述底电极及顶电极分别连接的电极焊盘图形并在所述电极焊盘图形上沉积金电极。

[0026] 由上,金电极层作为和外界检测电路电学连接的接口。

[0027] 优选地,所述流道牺牲层的高度为700nm,宽度1µm;所述氢氟酸溶液中氢氟酸和水的体积比为1:5。

[0028] 由上,流道牺牲层的高度为700nm,宽度1µm以保证流道为亚微米流道。体积比为1:5的氢氟酸水溶液有利于流道牺牲层的释放。利用反应离子刻蚀方法刻蚀的好处是有利于克服湿法刻蚀造成的过刻以及侧向刻蚀非常严重,导致流道被完全刻蚀掉使得实验失败的缺陷。

[0029] 本申请还提供一种亚微米流道微流控芯片的制作方法,包括步骤:

[0030] M1、在一基底上沉积用作底电极的金属钼;并刻蚀出指定形状的底电极;

[0031] M2、在所述底电极上沉积覆盖整个基底的氮化铝薄膜:

[0032] M3、在所述氮化铝薄膜上沉积覆盖整个基底的PSG,并刻蚀出流道的形状,将刻蚀后剩余的PSG作为流道牺牲层:

[0033] M4、在所述流道牺牲层上沉积覆盖整个基底的氮化铝薄膜作为流道结构层,并在其上刻蚀出流道出入口:

[0034] M5、利用氢氟酸溶液释放所述流道牺牲层:

[0035] 其中,所述底电极成对设置,每对底电极分别设置于所述流道牺牲层的底部的两侧且与流道牺牲层重叠设置。

[0036] 由上,本申请通过上述流程制得的亚微米流道微流控芯片,无需使用手动对准电极和流道,即可精准地制备目标亚微米流道微流控芯片。

[0037] 优选地,所述步骤M1之前,还包括步骤:

[0038] M1'、将所述基底单面抛光以及进行去除表面杂质的处理;其中,所述去除表面杂质的处理,包括:

[0039] 将单面抛光的基底分别利用食人鱼和氢氟酸溶液去除表面的杂质;其中,所述食人鱼为体积比为3:1的浓硫酸和双氧水。

[0040] 由上,有利于增加基底与其上沉积的层与的贴合度。

[0041] 优选地,步骤M1所述沉积用作底电极的金属钼之前,还包括:

[0042] 利用光刻工艺将掩膜版底电极槽图形转移到所述基底上,进行刻蚀,刻蚀出底电极槽,并沉积氮化铝薄膜。

[0043] 由上,由于通常流道和电极的位置在设计时就已经固定,且检测电极和敏感流道距离非常近。为了得到光滑平整的流道,在设计时需要将检测的底电极埋在高阻硅材质的基底上,需要在基底上将底电极的槽挖出,在刻蚀出底电极槽的整个基底上沉积氮化铝薄膜(利用物理气相沉积,相当于在基底表面整体生成一层,整体高度同时变化),因此基于前述刻蚀出的底电极槽,此时仍然存在一个与所述底电极槽形状一致的凹槽,使后续的在其上沉积的金属钼电极(底电极)可以沉积到该凹槽中,并将不需要的金属钼电极刻蚀掉,,使流道内表面更加平整。同时,沉积氮化铝薄膜的好处是在下一步刻蚀金属钼(底电极)时作为阻挡层保护硅基底不被刻蚀。

[0044] 优选地,所述步骤M4,包括:

[0045] 利用光刻工艺将流道的出入口和电极焊盘图形转移到所述流道结构层上;并刻蚀出与所述流道牺牲层的端部连接的流道的出入口,以及刻蚀出与所述底电极连接的电极焊盘图形并在所述电极焊盘图形上沉积金电极。

[0046] 由上,金电极层作为和外界检测电路电学连接的接口。

[0047] 综上所述,本申请通提供的上述亚微米流道微流控芯片的制作方法,可精准地制备目标亚微米流道微流控芯片。

### 附图说明

[0048] 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

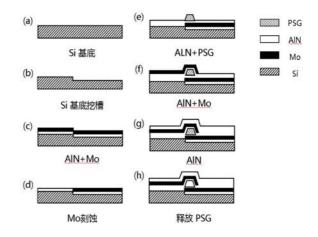

[0049] 图1为本申请实施例一提供的一种亚微米流道微流控芯片的制作方法;

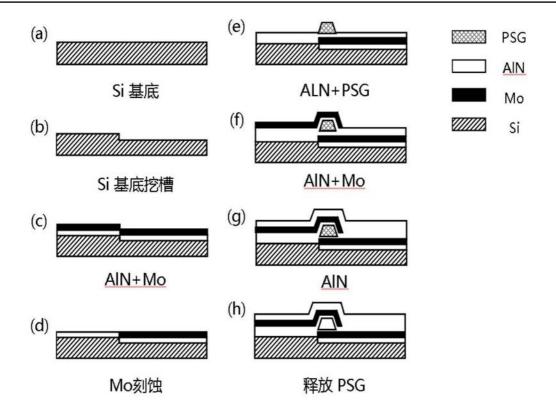

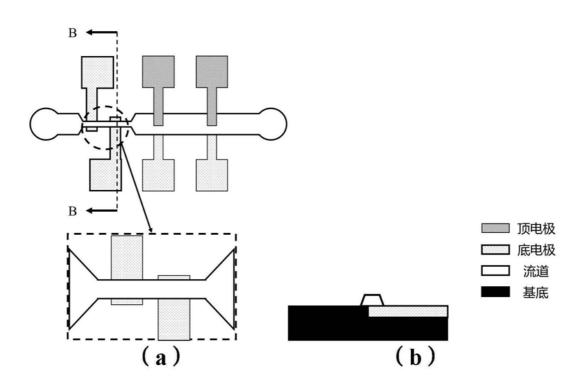

[0050] 图2(a) 为本申请实施例一提供的制作方法制作的亚微米流道微流控芯片俯视图及局部放大示意图;(b) 为左侧图(a) 中的A-A处的纵切示意图;

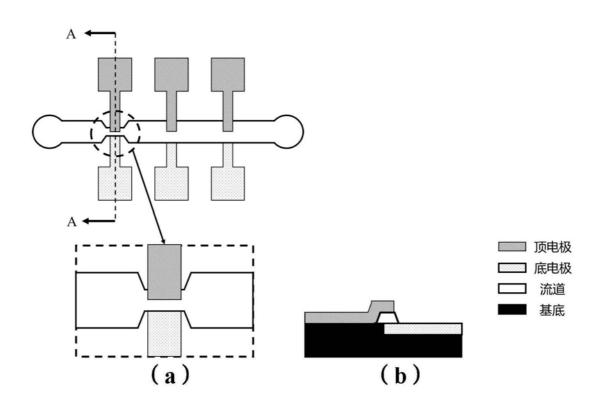

[0051] 图3为本申请实施例二提供的一种亚微米流道微流控芯片的制作方法;

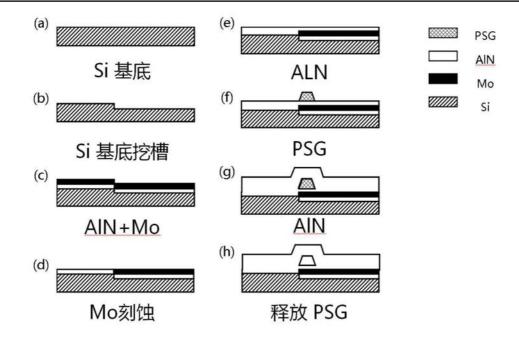

[0052] 图4(a) 为本申请实施例二提供的制作方法制作的亚微米流道微流控芯片的俯视图及局部放大示意图;(b) 为左侧图(a) 中的B-B处纵切示意图;

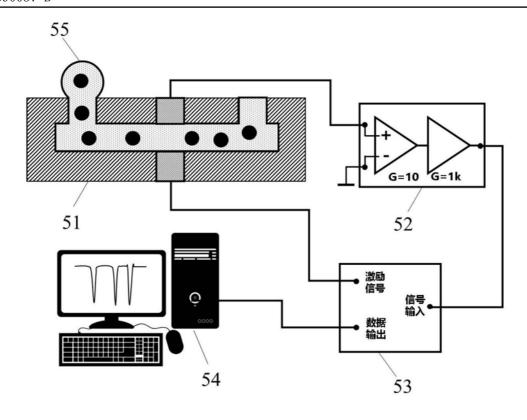

[0053] 图5为本申请提供的芯片及与其连接的检测系统。

#### 具体实施方式

[0054] 为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员

在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的区间。

[0055] 实施例一

[0056] 本申请提供一种亚微米流道微流控芯片的制作方法,包括步骤:

[0057] S101,将单面抛光的高阻硅片分别利用食人鱼(浓硫酸:双氧水=3:1)和氢氟酸溶液去除表面的杂质。

[0058] S102,利用光刻工艺将掩膜版底电极槽图形转移到硅片(Si基底)上,进行刻蚀,挖出300nm深的电极槽。

[0059] S103,沉积300nm厚的氮化铝(AIN)作为绝缘层与阻挡层,并在氮化铝薄膜上沉积300nm厚的金属钼,氮化铝的作用是在下一步刻蚀金属钼时作为阻挡层保护硅基底不被刻蚀。

[0060] S104,利用光刻工艺将底电极形状转移到金属钼层(MO)上,然后刻蚀金属钼制作底电极。

[0061] S105,在刻蚀好的底电极上沉积30nm厚的氮化铝(AIN),用于保护底电极。然后是在氮化铝上沉积700nm厚的PSG作为流道牺牲层,并利用光刻工艺将流道形状从掩膜版转移到PSG(磷硅酸盐薄膜)上,并将其余PSG刻蚀掉,形成PSG流道。

[0062] S106,沉积300nm厚的氮化铝,用于保护PSG牺牲层和即将沉积的金属钼。然后沉积300nm厚的金属钼,并利用光刻工艺将掩膜版上的顶电极图形转移到金属钼层上,将多余的金属钼刻蚀掉,形成顶电极。

[0063] S107,沉积2μm厚的氮化铝作为流道结构层,并利用光刻工艺将流道的出入口和电极焊盘图形转移到氮化铝层上,并刻蚀出图形,为后续电极焊盘沉金和PSG流道释放做准备。然后是利用lift-off工艺沉积金电极层,作为和外界检测电路电学连接的接口,如图5所示,为连接外界的检测电路的芯片。如图5所示。其中,51为微流控芯片;52为前置放大器;53为阻抗频谱仪;54为控制系统;55为样本入口。亚微米粒子溶液从样本入口55进入微流控芯片51,通过检测区域。底电极连接由阻抗频谱仪提供的激励信号;顶电极为检测电极,并将信号引入前置电流放大器,经过放大的信号引入阻抗频谱仪的信号接收端,进行信号解调,并获得信号;进一步地,阻抗频谱仪解调的信号传输给信号处理分析装置,进行信号处理分析、结果显示和存储。

[0064] S108,利用氢氟酸溶液(氢氟酸:水=1:5)释放PSG牺牲层。此微流控芯片设计时,因为底电极、PSG流道牺牲层和顶电极的对准误差需要控制在1微米以内,手动对准已经无法实现。所以设计上述工艺,利用高精度的光刻机在加工过程中进行对准操作,保证精度。

[0065] 上述步骤S101~S108,分别对应图1中的(a)~(h)。其中,图2(a)为本申请通过上述步骤制得的亚微米流道微流控芯片及局部放大示意图;其中(b)为左侧图(a)中的A-A处的纵切示意图;

[0066] 其中,由于通常流道和电极的位置在设计时就已经固定,且检测电极和敏感流道距离非常近。为了得到光滑平整的流道,在设计时需要将检测的底电极埋在高阻硅为材质的基底上,需要在基底上将底电极的槽挖出,使金属钼电极可以沉到电极槽中,使流道内表面平滑。

[0067] 在制造高度700nm,宽度1µm的敏感流道时,通过优化工艺参数,解决了流道加工过程中的多个工艺难题。并利用光刻工艺将掩膜版上的流道图形转移到PSG牺牲层上,利用缓

冲氧化物刻蚀液 (Buffered Oxide Etch, BOE) 刻蚀PSG,但是因为敏感区域流道宽度非常小,湿法刻蚀对环境条件 (如温度) 要求比较苛刻,经常造成过刻,且侧向刻蚀非常严重,敏感流道被完全刻蚀掉导致实验失败,为了解决这个问题本课题引入反应离子刻蚀,利用干法刻蚀PSG。反应离子刻蚀方法属于各向同性刻蚀,也会带来侧向刻蚀的问题,但是对于本项目来说,一定的可控侧向刻蚀正是制造亚微流道所需要的,不但不会使得流道被刻蚀掉而且还有利于流道的刻蚀。

[0068] 其中,在制作宽度小于1µm的流道时,使用反应离子刻蚀方法。

[0069] 除解决了PSG牺牲层刻蚀问题后,还需要解决了PSG流道牺牲层释放过程中氮化铝结构层脱落的问题。在亚微米流道微流控芯片制作完成后,需使用氢氟酸溶液 (49%氢氟酸:水=1:5)释放PSG牺牲层,但是将芯片放入氢氟酸溶液中一段时间后,最上层的氮化铝结构层脱落,通过对工艺流程的仔细分析,发现两个问题对氢氟酸释放PSG有影响,一个是氮化铝结构层的应力,另一个是氢氟酸释放PSG时的浸泡时间。因为在氮化铝成膜时,生长条件对氮化铝的应力有影响,应力过大会导致氮化铝薄膜变形,致使氮化铝薄膜凸起或者凹陷。经过分析,该实验需要氮化铝结构层应力为0。氮化铝作为结构层时,其需要稳定保持成膜时的形状,不需要凸起或者凹陷,因此在释放PSG流道时就不会出现氮化铝结构层因为应力而脱落。通过调整了氮化铝结构层的成膜条件,例如调整成膜功率和成膜温度,控制氮化铝结构层的应力为0。氢氟酸溶液释放PSG牺牲层相当于湿法刻蚀,刻蚀的时间和需要刻蚀的PSG厚度、形状和刻蚀速率有关,因为本项目的PSG牺牲层被氮化铝结构层覆盖,所以刻蚀时间和其他标准的生产工艺不同,需要一个和本项目相匹配的刻蚀时间。

[0070] 在解决上述问题后,又重新加工了一批芯片,在制造的过程中利用多个测试片调整氮化铝结构层的成膜条件,控制氮化铝结构层的应力在0左右,从而制作出符合本项目要求的氮化铝结构层。并且在利用氢氟酸溶液释放PSG牺牲层时使用了弹性刻蚀时间,同一批芯片因为具有不同的形状,所以每个芯片的刻蚀时间不做统一要求,而是每隔5min查看一次,将PSG流道牺牲层完全释放的芯片取出,PSG流道牺牲层未完全释放的微流控芯片放回氢氟酸溶液中继续刻蚀。通过控制氮化铝结构层的应力和控制氢氟酸溶液浸泡时间,制造出了亚微米流道微流控芯片。

[0071] 实施例二

[0072] 本申请提供另一种亚微米流道微流控芯片的制作方法,包括步骤:

[0073] S201,为利用食人鱼和氢氟酸溶液将高阻硅片上的杂质去除干净。

[0074] S202,利用光刻工艺将掩膜版上的底电极槽图形转移到硅片上,并刻蚀出电极槽.

[0075] S203,依次沉积300nm厚的氮化铝薄膜和300nm厚的金属钼薄膜,氮化铝薄膜的作用为阻挡层和绝缘层,在后续刻蚀金属钼电极时保护硅基底。

[0076] S204,将掩膜版上的底电极图形利用光刻工艺转移到金属钼上,并刻蚀出底电极。

[0077] S205, 沉积30nm厚的氮化铝薄膜, 作为阻挡层, 在后续刻蚀PSG时保护底电极。

[0078] S206,沉积700nm厚的PSG薄膜,并利用光刻工艺将流图形状转移到PSG薄膜上,将不需要的PSG刻蚀掉。

[0079] S207,沉积2µm厚的氮化铝薄膜作为结构层,并利用光刻工艺将流道出入口和电极焊盘图形转移到氮化铝薄膜上,并刻蚀出图形,为后续释放PSG牺牲层和沉积金电极做准备。然后是利用lift-off工艺沉积金电极层,作为和外界检测电路电学连接的接口。

[0080] S208,利用氢氟酸溶液(氢氟酸:水=1:5)释放PSG流道牺牲层。

[0081] 上述步骤S201~S208,分别对应图3中的(a)~(h)。

[0082] 综上所述,本申请通提供的上述亚微米流道微流控芯片的制作方法,可精准地制备目标亚微米流道微流控芯片。

[0083] 以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

图1

图2

图3

图4

图5