(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4759089号 (P4759089)

(45) 発行日 平成23年8月31日(2011.8.31)

(24) 登録日 平成23年6月10日(2011.6.10)

(51) Int. Cl. FLHO1L 21/336 612D (2006, 01) HO1L 29/78 HO1L 29/786 HO1L 29/78 618B (2006, 01) HO1L 51/05 (2006.01) HO1L 29/78 619A G02F 1/1368 (2006, 01) HO1L 29/28 100AGO2F 1/1368

請求項の数 10 (全 19 頁)

(21) 出願番号 特願2010-1747 (P2010-1747) (22) 出願日 平成22年1月7日(2010.1.7) (62) 分割の表示 特願2005-189152 (P2005-189152) の分割 原出願日 平成17年6月29日 (2005.6.29) (65) 公開番号 特開2010-114459 (P2010-114459A) 平成22年5月20日 (2010.5.20) (43) 公開日 平成22年1月7日(2010.1.7) 審査請求日 (31) 優先権主張番号 2004-075984 平成16年9月22日 (2004.9.22) (32) 優先日 (33) 優先権主張国 韓国(KR)

(73)特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

イドードン 20

||(74)代理人 100094112

弁理士 岡部 譲

(74)代理人 100064447

弁理士 岡部 正夫

||(74)代理人 100104352

弁理士 朝日 伸光

前置審査

最終頁に続く

(54) 【発明の名称】液晶表示装置の製造方法

### (57)【特許請求の範囲】

### 【請求項1】

基板上にゲート電極を形成する段階と、

上部面を有するゲート絶縁膜を形成する段階と、

前記ゲート絶縁膜上に金属層を形成する段階と、

露光技術を用いて前記金属層上に形成したマスク層をマスクとして前記金属層をパターニングしてソース電極及びドレイン電極を形成し、前記ゲート絶縁膜上部の前記ソース電極とドレイン電極間に位置するチャネル領域を定義する段階と、

前記マスク層上及び前記ゲート絶縁膜上部に定義された前記チャネル領域に低分子有機半導体物質を蒸着する段階と、

前記低分子有機半導体物質上に、前記ソース電極とドレイン電極それぞれの上部面の下に位置する上部面を有する第 1 保護膜を形成する段階と、

前記ソース電極とドレイン電極それぞれの厚さを前記低分子有機半導体物質の厚さと前記第1保護膜の厚さの合計より大きくした状態で、前記マスク層の側面部をストリップ液と接触させて、前記マスク層と共に前記マスク層上部面に位置する前記第1保護膜及び前記低分子有機半導体物質を除去し、前記ゲート絶縁膜上部に定義されたチャネル領域に半導体層と第1保護膜を形成する段階とを含む液晶表示装置の製造方法。

### 【請求項2】

前記ゲート絶縁膜の上部面は平坦なことを特徴とする請求項1に記載の液晶表示装置<u>の</u>製造方法。

#### 【請求項3】

前記ゲート絶縁膜は<u>画素領域</u>にさらに位置して、前記第1保護膜は前記画素領域で前記 ゲート絶縁膜の上部面と直接的に接触することを特徴とする請求項1に記載の液晶表示装 置の製造方法。

## 【請求項4】

前記半導体層は<u>画素領域</u>にさらに位置することを特徴とする請求項1に記載の液晶表示 装置の製造方法。

### 【請求項5】

前記低分子有機半導体物質は透明物質であることを特徴とする請求項 1 に記載の液晶表示装置の製造方法。

【請求項6】

前記低分子有機半導体物質は85%以上の光透過度を有することを特徴とする請求項5 に記載の液晶表示装置の製造方法。

## 【請求項7】

前記低分子有機半導体物質はペンタセンを含むことを特徴とする請求項 6 に記載の液晶表示装置の製造方法。

### 【請求項8】

前記ソース電極及び前記ドレイン電極の厚さは3、000 以上の厚さを有することを 特徴とする請求項1に記載の液晶表示装置の製造方法。

### 【請求項9】

前記第1保護膜上部に位置して、前記ソース電極及びドレイン電極それぞれの上部面と直接的に接触する第2保護膜をさらに含むことを特徴とする請求項1に記載の液晶表示装置の製造方法。

#### 【請求項10】

前記基板はプラスチック基板であることを特徴とする請求項1に記載の液晶表示装置<u>の</u> 製造方法。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は液晶表示装置に係り、さらに詳細には低分子有機半導体物質を利用した液晶表示装置及びその製造方法に関する。

【背景技術】

### [0002]

近来になって社会が本格的な情報化時代に入るによって大量の情報を処理及び表示するディスプレー分野が急速に発展し、最近では特に薄形化、軽量化、低消費電力化の優秀な性能をもった薄膜トランジスタ(Thin Film Transistor:TFT)型液晶表示装置(TFT・LCD)が開発されて既存のブラウン管を取り替えている。

## [0003]

液晶表示装置の画像具現原理は液晶の光学的異方性と分極性質を利用することであって、周知のように液晶は分子構造が細長くて配列に方向性を有する光学的異方性と電界内に置かれる場合に分子配列方向が変化する分極性質を帯びる。ここに液晶表示装置は液晶層を間に置いて相互に向い合う面でそれぞれ画素電極と共通電極が形成されたアレイ基板とカラーフィルター基板を合着させて構成された液晶パネルを構成要素にしており、これら電極間の電界変化を介して液晶分子の配列方向を人為的に調節してこの時変化する光の透過率を利用しているいるな画像を表示する非発光素子である。

#### [0004]

最近には特に画像表現の基本単位である画素をマトリックス方式に配列してスイッチング素子を各画素に配置させて独立的に制御するアクティブマトリックス方式が解像度及び動画像具現能力で優れて注目されているが、このようなスイッチング素子として薄膜トランジスタ(TFT)を用いたTFT・LCDが知られている。

10

20

30

40

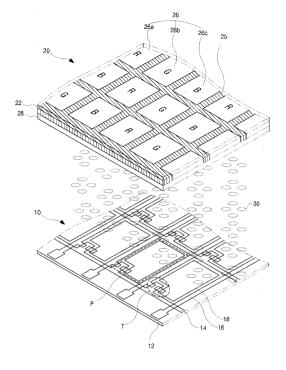

#### [0005]

図1は従来による液晶表示装置の分解斜視図である。

#### [0006]

図示したように、液晶層 3 0 を間に置いてアレイ基板 1 0 とカラーフィルター基板 2 0 が対面合着された構成を有するが、このうち下部のアレイ基板 1 0 は第 1 透明基板 1 2 及びこれの上面で縦横交差配列されて複数の画素領域 P を定義する複数個のゲート配線 1 4 とデータ配線 1 6 を含み、これら両配線 1 4 、 1 6 の交差地点には薄膜トランジスタ T が具備されて各画素領域 P に用意された画素電極 1 8 と 1 対 1 対応接続されている。

### [0007]

またこれと向い合う上部のカラーフィルター基板 2 0 は第 2 透明基板 2 2 及びこれの背面に前記ゲート配線 1 4 とデータ配線 1 6 そして薄膜トランジスタ T などの非表示領域を遮るように各画素領域 P を縁取りする格子形状のブラックマトリックス 2 5 が形成されており、これら格子内部で各画素領域 P に対応するように順次的に繰り返し配列された赤、緑、青色カラーフィルター層 2 6 が形成されており、前記ブラックマトリックス 2 5 と赤、緑、青色カラーフィルター層 2 6 の全面にかけて透明な共通電極 2 8 が用意されている

#### [00008]

そして図面上に明確に図示しなかったが、これら両基板10、20はその間に介在した液晶層30の漏洩を防止するために縁に沿ってシーリング剤等で封止した状態で各基板10、20と液晶層30の境界部分には液晶の分子配列方向に方向性を付与する上、下部配向膜が介在され、各基板10、20の少なくとも一つの外側面には偏光板が付着される。

#### [0009]

液晶パネル背面にはバックライトが具備されて光を供給するので、ゲート配線14で薄膜トランジスタTのオン / オフ信号が順次的にスキャンされて選択された画素領域Pの画素電極18にデータ配線16の画像信号が伝えられるとこれら間の垂直電界によりその間の液晶分子が駆動されて、これによる光の透過率変化でいろいろ画像を表示することができる。

#### [0010]

一方、このような液晶表示装置においてアレイ基板 1 0 とカラーフィルター基板 2 0 の 母体になる第 1 及び第 2 透明基板 1 2 、 2 2 は伝統的にガラス基板が使われてきたが、最 近になってノート・パンコンや P D A のような小型の携帯用端末機が広く普及するによっ てこれらに適用可能なようにガラスより軽くて軽量と同時に柔軟な特性をもっていて破損 危険が少ないプラスチック基板を利用した液晶パネルが紹介されたことがある。

### [0011]

しかし、プラスチック基板を利用した液晶パネルは液晶表示装置の製造特性上特にスイッチング素子である薄膜トランジスタが形成されるアレイ基板の製造には200 以上の高温を必要とする高温工程が多くて耐熱性及び耐化学性がガラス基板より悪いプラスチック基板で前記アレイ基板を製造することには難しさがあって、上部基板を形成するカラーフィルター基板のみをプラスチック基板で製造して下部基板であるアレイ基板は通常的なガラス基板を利用して液晶表示装置を製造しているのが実情であった。

## [0012]

このような問題を解決しようと最近には低分子有機物質等を利用した 2 0 0 以下の低温工程を進行してプラスチック材質のフレキシブルなアレイ基板を製造する技術が提案された。

#### [0013]

以後には200 以下の低温工程を進行するプラスチック基板を利用したフレキシブルなアレイ基板の製造方法に対して説明する。

### [0014]

200 以下の低温工程で薄膜トランジスタを含む画素を形成することにおいて、電極と配線を形成する金属物質と絶縁膜と保護膜等の形成は低温蒸着またはコーティングの方

10

20

30

40

法などを介して形成しても薄膜トランジスタの特性に別影響を与えないが、チャネルを形成する半導体層を一般的な半導体物質である<u>シリコン</u>を用いて低温工程により形成するようになれば、耐久構造が緻密ではなく電気伝導度等の重要特性が低下する問題が発生する。したがって、これを克服しようと<u>シリコン</u>などの従来の半導体物質の代わりに半導体特性を有した有機物質を利用して半導体層を形成している。このような半導体特性を有する有機物質は大別して高分子半導体物質と低分子半導体物質に分けられており、前記低分子半導体物質は高分子半導体物質に対して電気伝導度等の優秀な物性を持っているので主に<u>シリコン</u>を代わる半導体物質に利用されているが、水分に非常に脆弱で溶液形態で作りにくい短所がある。

以下図面を参照して従来のフレキシブルなアレイ基板の製造方法に対して説明する。

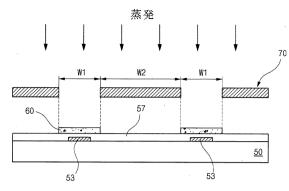

## [0015]

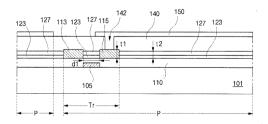

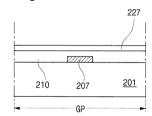

図2は従来によるフレキシブルプラスチック基板を利用する液晶表示装置用に用いられる低分子有機半導体物質からなった半導体層を含むアレイ基板の概略的な断面図である。

[0016]

図示したように、プラスチック基板 5 0 上に金属物質を蒸着してパターニングしてゲート配線(図示せず)を含んでゲート電極 5 3 を形成して、続いて前記ゲート配線(図示せず)とゲート電極 5 3 上に全面に有機絶縁物質をコーティングしてゲート絶縁膜 5 7 を全面に形成する。

### [0017]

次に、低分子有機半導体物質をシャドーマスク70を利用した蒸発法を利用して前記ゲート電極53と重なるように各画素毎に分離された半導体層60を形成する。ガラス基板を利用した場合はシリコンさらに正確にはSiH4をCVD法を利用して蒸着してマスクを利用してパターニングすることによって形成したが、ペンタセン(pentacene)(C₂₂H₁₄)のような粉末形態である低分子有機半導体物質の特性上前述したCVD法による蒸着が難しくまたこれをパターニングすることにおいてフォトエッチング法による場合水分を含有するフォトレジストと接触するようになったりまたはフォトレジストを現像または除去するために現像液やストリップ液に露出することによってその特性低下などが発生する問題があり、図示したようなパターニングされたシャドーマスク70を利用して蒸発法により形成されている。

## [0018]

しかし、前述したシャドーマスク70を利用した蒸発法による有機半導体物質パターン 形成はパターン間間隔w2及びパターン自体サイズの制限を有するようになる。さらに詳 細に説明すると金属物質で形成されるシャドーマスク70を製作するにおいてそのパター ンの幅w1または長さが最小40μm以上にならなければならない問題がある。すなわち シャドーマスク70の開口部はその幅w1または長さが最小限40μm以上になるよう に形成され、また、前記開口部と開口部間の間隔w2においても120µm以上になって こそシャドーマスク70製作が可能である。これはそれより小さい開口部と開口部間の間 隔を有するシャドーマスクを製作するにしても蒸発法の特性上材料の拡散を防止できない のでそれより小さいパターンを得にくい。したがってこのような構造を有するシャドーマ スク70を利用して基板50上に形成される低分子有機半導体層60は最小限その幅また は長さが40μm以上になっている。画素内に形成される薄膜トランジスタにおいて半導 体層に形成されるチャネルのサイズは10μm以下になっており、実際的にこのようなチ ャネル領域を除いては半導体層の体積またはサイズを減らすことが画素の開口率向上に寄 与し、同一なサイズを有するアクティブ領域なら同一サイズ内に画素が多く形成されるほ ど解像度が増加するようになるが解像度が増加するほど画素のサイズは小さくなるように なって、共に前記画素内部に形成される例えば薄膜トランジスタのサイズは小くならなけ ればならないし、この場合チャネルの大きさも小さくすべきことは明らかである。

### [0019]

しかし前述したシャドーマスクを利用した低分子有機半導体層パターンの形成は40 µ m以上のサイズを有するようになるので高解像度のアレイ基板の製造にはその限界がある

10

20

30

40

### [0020]

また、前述したように、半導体層を形成すると言ってもその上部にソース及びドレイン電極をパターニングする過程において、その下部に半導体層がフォトレジストの現像液またはソース及びドレイン電極を成す金属物質のストリップ液等により損傷される等の問題が発生することによってアレイ基板の製造に困難が多い。

#### 【発明の概要】

【発明が解決しようとする課題】

## [0021]

前述した問題を解決するために本発明は提案されたものであって、水分に非常に弱い特性を有する低分子有機半導体物質をシャドーマスクを利用しないで数 μ m まで調節可能な微細パターンで形成することができ、前記微細パターンされた低分子有機半導体層の損傷なしに低分子有機半導体物質を利用した液晶表示装置用アレイ基板の製造方法を提供することにその目的がある。また、半導体層を形成して、その上部にソース及びドレイン電極をパターニングする過程において、半導体層がフォトレジストの現像液またはソース及びドレイン電極を成す金属物質のストリップ液等により損傷されることを防止する液晶表示装置を提供することに目的がある。

#### 【課題を解決するための手段】

#### [0022]

前記のような目的を達成するために、本発明の第1特徴では画素領域と;ゲート電極と、上部面を有するゲート絶縁膜と、前記ゲート絶縁膜の上部面に形成されたソース電極及びドレイン電極と、前記ゲート絶縁膜の上部面に配置されて、前記ソース電極とドレイン電極間でチャネル領域を定義して、低分子有機半導体物質からなった半導体層を含み、基板上に前記画素領域に隣接するように位置する薄膜トランジスタと;前記チャネル領域を覆っており、前記ソース電極とドレイン電極それぞれの上部面と一致したりまたはその下に位置する上部面を有する第1保護膜を含む液晶表示装置を提供する。

#### [0023]

前記ゲート絶縁膜の上部面は平坦なことを特徴として、前記ソース電極とドレイン電極の厚さは前記半導体層の厚さと前記第1保護膜の厚さの合計と同一であったりまたは大きいことを特徴とする。

### [0024]

前記ゲート絶縁膜は前記画素領域にさらに位置して、前記第1保護膜は前記画素領域で 前記ゲート絶縁膜の上部面と直接的に接触することを特徴とする。

### [0025]

前記半導体層は前記画素領域にさらに位置することを特徴とする。

#### [0026]

前記低分子有機半導体物質は透明物質であることを特徴として、前記低分子有機半導体物質は大体 8 5 %以上の光透過度を有することを特徴としており、前記低分子有機半導体物質はペンタセンを含むことを特徴とする。

## [0027]

前記ソース電極及び前記ドレイン電極の厚さは3、000 以上の厚さを有することを 特徴として、前記チャネル領域は大体40µmより小さい幅を有することを特徴とする。

#### [0028]

前記第1保護膜上部に位置して、前記ソース電極及びドレイン電極それぞれの上部面と 直接的に接触する第2保護膜をさらに含む。

## [0029]

前記基板はプラスチック基板であることを特徴とする。

#### [0030]

本発明の第 2 特徴では、基板上にゲート電極を形成する段階と;ゲート絶縁膜を形成する段階と;ソース電極と、ドレイン電極と、前記ゲート絶縁膜上部の前記ソース電極とド

10

20

30

40

レイン電極間に位置するチャネル領域を形成する段階と;前記チャネル領域に蒸発(evaporating)法により低分子有機半導体物質からなった半導体層を形成する段階と;前記ソース電極及び前記ドレイン電極のそれぞれの上部面と一致したりまたはその下に位置する上部面を有するように第1保護膜を形成する段階を含む液晶表示装置の製造方法を提供する。

### [0031]

前記ゲート絶縁膜を形成する段階は平坦な上部面を有するゲート絶縁膜を形成する段階を含むことを特徴とする。

### [0032]

前記半導体層と前記第1保護膜を形成する段階は、前記半導体層の厚さと前記第1保護膜の厚さの合計が前記ソース電極と前記ドレイン電極の厚さと同一であり又はより小さいように前記半導体層と前記第1保護膜を形成する段階を含むことを特徴とする。

#### [0033]

前記第1保護膜上部に位置して、前記ソース電極と前記ドレイン電極それぞれの上部面に直接接触する第2保護膜を形成する段階をさらに含むことを特徴とする。

#### [0034]

前記ソース電極、前記ドレイン電極と前記チャネル領域を形成する段階は:前記ゲート 絶縁膜上に金属層を形成する段階と;前記ソース電極、前記ドレイン電極そして前記チャ ネル領域を形成するために、前記ソース電極と前記ドレイン電極の上部面にあるパターニ ングされたマスク層を有して前記金属層をパターニングする段階を含むことを特徴とする

#### [0035]

前記半導体層を形成する段階は前記パターニングされたマスク層の上部面上に低分子有機半導体物質を蒸発法により形成する段階をさらに含むことを特徴として、前記第1保護膜を形成する段階は前記パターニングされたマスク層の上部面に第1保護膜を形成する段階を含むことを特徴としており、前記パターニングされたマスク層を除去することによって前記パターニングされたマスク層上部面に位置する前記第1保護膜及び前記半導体層を除去する段階をさらに含むことを特徴とする。

#### [0036]

前記半導体層を形成する段階は、画素領域に前記低分子有機半導体物質を蒸発法により形成する段階を含むことを特徴とする。

## [0037]

前記ゲート絶縁膜を形成する段階は画素領域に前記ゲート絶縁膜を形成する段階を含むことを特徴とする。

### [0038]

前記半導体層を形成する段階は:前記画素領域に前記低分子有機半導体物質を蒸発法によりパターニングする段階と;前記画素領域で前記ゲート絶縁膜の上部面に前記低分子有機半導体物質を直接的に接触する段階を含むことを特徴とする液晶表示装置の製造方法を提供する。

### [0039]

前記チャネル領域に半導体層を形成する段階は:前記チャネル領域、前記ソース電極そして前記ドレイン電極に対応するオープニングを有するシャドーマスクを適用する段階と;前記チャネル領域に前記低分子有機半導体物質を蒸発法によりパターニングする段階を含むことを特徴として、前記ゲート絶縁膜を形成する段階は、画素領域に前記ゲート絶縁膜を形成する段階を含むことを特徴とする。

## [0040]

前記画素領域に前記第1保護膜を形成する段階と;前記画素領域で、前記ゲート絶縁膜の上部に前記第1保護膜を直接的に接触する段階をさらに含むことを特徴とする。

### [0041]

前記ゲート電極を形成する段階は、プラスチック基板上に前記ゲート電極を形成する段

10

20

30

40

20

30

50

階を含むことを特徴として、前記形成段階のそれぞれは大体 2 0 0 より低い温度下でなされることを特徴とする。

#### 【発明の効果】

## [0042]

本発明による低分子有機半導体物質を利用した液晶表示装置用アレイ基板はシャドーマスクを利用しないで数 μ m まで調節可能な微細パターンを形成したり、またはシャドーマスクを利用して低分子有機半導体層を形成しても今後工程でパターニングが可能な製造方法を提供することによって開口率及び輝度を向上させる効果がある。

### [0043]

また、水分に弱い低分子有機半導体物質を利用して損傷なしに半導体層を微細パターニングすることができる製造方法を提供することによって高解像度を有する有機薄膜トランジスタを具備したフレキシブルな液晶表示装置を提供する効果がある。

#### 【図面の簡単な説明】

## [0044]

- 【図1】従来による液晶表示装置の分解斜視図。

- 【図2】従来によるフレキシブルプラスチック基板を利用する液晶表示装置用低分子有機 半導体物質からなった半導体層を含むアレイ基板の概略的な断面図。

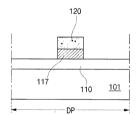

- 【図3A】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の1を示す図。

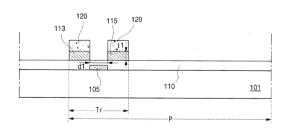

- 【図3B】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の2を示す 図。

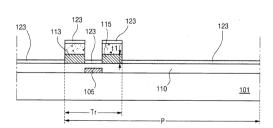

- 【図3C】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の3を示す図。

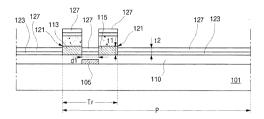

- 【図4A】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の4を示す図。

- 【図4B】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の5を示す 図。

- 【図4C】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の6を示す図。

- 【 図 5 A 】本発明の第 1 実施形態の液晶表示装置のアレイ基板を製造する工程の 7 を示す 図。

- 【 図 5 B 】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の8を示す 図。

- 【図5C】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の9を示す図。

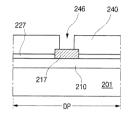

- 【図6A】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の10を示す図。

- 【図6B】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の11を示す図。

- 【図6C】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の12を示 40 す図。

- 【図7A】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の13を示す図。

- 【図7B】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の14を示す図。

- 【図7C】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の15を示す図。

- 【図8A】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の16を示す図。

- 【図8B】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の17を示

す図。

- 【図8C】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の18を示す図。

- 【図9A】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の19を示す図。

- 【図9B】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の20を示す図

- 【図9C】本発明の第1実施形態の液晶表示装置のアレイ基板を製造する工程の21を示す図。

- 【図10A】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の1を示す図。

- 【図10B】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の2を示す図。

- 【図10C】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の3を示す図。

- 【図11A】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の4を示す図。

- 【図11B】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の5を示す図。

- 【図11C】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の6を示 す図。

- 【図12A】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の7を示す図。

- 【図12B】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の8を示す図。

- 【図12C】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の9を示す図。

- 【図13A】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の10を示す図。

- 【 図 1 3 B 】本発明の第 2 実施形態の液晶表示装置のアレイ基板を製造する工程の 1 1 を 示す図。

- 【図13C】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の12を示す図。

- 【図14A】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の13を示す図。

- 【図14B】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の14を 示す図。

- 【図14C】本発明の第2実施形態の液晶表示装置のアレイ基板を製造する工程の15を 示す図。

【発明を実施するための形態】

[0045]

以下図面を参照して本発明をさらに詳細に説明する。

<第1実施形態>

[0046]

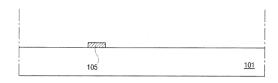

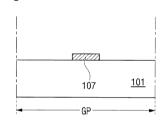

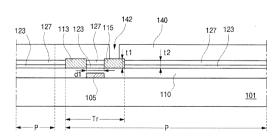

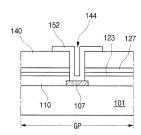

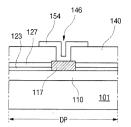

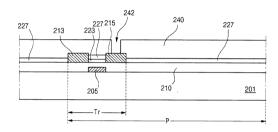

図3 A ないし図3 C、図4 A ないし図4 C、図5 A ないし図5 C、図6 A ないし図6 C、図7 A ないし図7 C、図8 A ないし図8 C、そして図9 A ないし図9 C は本発明の第1 実施形態による液晶表示装置のアレイ基板を製造する工程を示す概略的な断面図であって、図3 B、図4 B、図5 B、図6 B、図7 B、図8 B 及び図9 B はゲートパッド領域 G Pに対する製造工程断面図であり、図3 C、図4 C、図5 C、図6 C、図7 C、図8 C 及び図9 C はデータパッド部 D P に対する製造工程断面図である。

10

20

30

40

20

30

40

50

#### [0047]

図面には示さなかったが、プラスチック基板を利用するとその柔軟性により工程進行のための搬送進行時に撓みが甚だしく発生するのでこのようなことを防止するためにガラス材質のリジッド基板に付着して工程は進められる。

### [0048]

まず図3Aないし図3Cに示したように、プラスチック基板101上に金属物質を200 以下の低温工程でスパッタリングを行って全面に蒸着して、フォトレジストを前記蒸着された金属物質上に塗布して光が通過する透過領域と光が通過しない遮断領域を有するマスク(図示せず)を位置させた後露光し、前記露光されたフォトレジストを現像することによってゲート配線(図示せず)とゲート電極105及びゲートパッド電極107が形成されなければならない部分にフォトレジストパターン(図示せず)を形成する。以後、前記フォトレジストパターン(図示せず)外部に露出された金属物質をエッチングすることによって基板101上にゲート配線(図示せず)とゲート電極105及びゲートパッド電極107を形成する。以後前記ゲート配線(図示せず)とゲート電極105及びゲートパッド電極107上部に残っているフォトレジストパターン(図示せず)をアッシングまたはストリップして除去する。

## [0049]

次に、図4Aないし図4Cに示したように、前記ゲート配線(図示せず)とゲート電極105及びゲートパッド電極107が形成された基板101上に有機絶縁物質例えばPVP(polyvinylpyrrolidine)、BCB(benzocyclobutene)のうちから選択される物質を基板101全面に塗布してゲート絶縁膜110を形成する。この時、前記ゲート絶縁膜110は有機絶縁物質で形成されたので下部のゲート配線(図示せず)とゲート電極105及びゲートパッド電極107の段差に影響を受けなくてその表面が平坦に形成される。

#### [0050]

しかし、本発明は前記ゲート絶縁膜 1 1 0 が段差構造を有する場合も含む。これに対する具体的な説明は以後に説明する。

#### [0051]

次に、前記ゲート絶縁膜110上に形成されたゲート配線(図示せず)と同一な金属物質を200 以下の低温雰囲気で蒸着して金属層(図示せず)を形成する。この時、前記金属層(図示せず)の厚さは従来には1500 ないし2000 の厚さで形成されているが、本発明においては後に行なわれるリフトオフ工程の特性上3000 以上の厚さであり、後工程で形成される低分子有機半導体層とその上部に形成された第1保護膜の厚さを合せた厚さより厚い厚さになるように形成することが望ましい。

### [0052]

次に、前記金属層(図示せず)上にフォトレジストを全面に塗布して、透過領域と遮断領域を有するマスク(図示せず)を位置させた後露光して、前記露光されたフォトストを現像することによってデータ配線(図示せず)とソース及びドレイン電極113などを形成するための金属パターンが形成されなければならない領域にだけフォトレジストパターン120が残っているようにする。以後、「図示せず」をエッチングすることによって最小3000 の厚さを有するデータ配線(図示せず)で第1間隔 d 1 を有して離隔したドレイン電極113、前記ソースを形成する。この時、前記データ配線(図示せず)をパッド電極113とを形成する。この時、前記データにおけるフォトレジストンで第1間隔 d 1 を形成する。この時、前記データ配線(図示せず)とソース及びドレイン電極113、115の離隔された第1間隔 d 1 は半導体層形成後電

20

30

40

50

子の移動通路になるチャネルを形成するようになる部分であるので、最終完成した液晶表示装置のモデルによってその間隔のサイズが変わるだろうが高解像度具現のためには 1 0 μ m 以下に形成されることが望ましい。しかし、高解像度モデルだけでなく通常的な解像度具現のための間隔で従来のシャドーマスクのパターンサイズの最小限界である 4 0 μ m より狭く形成されることもできる。

### [0053]

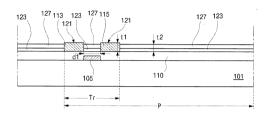

次に、図5Aないし図5Cに示したように、前記データ配線(図示せず)とソース及び ドレイン電極113、115とデータパッド電極117が形成された基板101上に前記 フォトレジストパターン120を含むゲート絶縁膜110の全面に、シャドーマスクを利 用せず透過度が85%以上であるペンタセン(pentacene; C ¸ ¸ H <sub>1 4</sub> )のよ うな低分子有機半導体物質を蒸発する工程を行って500 程度の厚さを有する低分子有 機半導体層123を形成する。この時、蒸発工程特性上蒸発により形成される物質層は段 差になった部分の側面部には蒸着比率が非常に落ちることによって、段差がある限界値以 上になれば平面垂直な状態の前記段差になった部分の側面においては蒸着されなくなり、 物質層の切断が発生するようになることが生ずる。したがってこのような蒸発工程の特性 を利用して、本発明の第1実施形態ではデータ配線(図示せず)とソース及びドレイン電 極113、115とデータパッド電極117を3000 以上の厚さ(または高さ)を有 するように形成し、その上部の残っているフォトレジストパターンの厚さが加えられて蒸 着される低分子有機半導体層123の切断が発生するようになる。すなわち、ソース及び ドレイン電極113、115とデータパッド電極117の上部に残っているフォトレジス トパターン120の側面部には低分子有機半導体層が形成されないようになる。そして前 記低分子半導体層は本発明の特徴上その後の工程においても画素領域に形成された低分子 半導体層は除去されなくて残っているようになるのでその透過度が85%以上になる低分 子有機半導体物質で形成されている。

#### [0054]

次に、図6Aないし図6Cに示したように、前記低分子有機半導体層123が形成された基板101全面に無機絶縁物質である酸化 $\frac{1}{2}$  りの変を全面に蒸着して第1保護膜127を形成する。この時、前記酸化 $\frac{1}{2}$  りの蒸着においても蒸着特性上段差が大きい部分すなわちソース及びドレイン電極113、115とデータパッド電極117とその上部のフォトレジストパターン120の側面部には蒸着物質すなわち酸化シリコン(SiO2)が蒸着されなくなって第1保護膜127の切断が発生するようになる。この時、前記ソース及びドレイン電極113、115とデータパッド電極117はその厚さ t1が前記低分子有機半導体層123とその上部の第1保護膜127の厚さを合せた厚さ t2より厚く形成されることによって、前記フォトレジストパターン120との接触面121が前記画素領域Pに形成された第1保護膜127の表面より高い所に形成されることが本発明の特徴である。

## [0055]

次に、図7Aないし図7Cに示したように、第1保護膜127まで形成された基板101をフォトレジストを除去するためのストリップ液にディッピングしてデータ配線(図示せず)、ソース及びドレイン電極113、115とデータパッド電極117上部に残っているフォトレジストパターン120を除去する。この場合前述したようにソース及びドレイン電極113、115とデータパッド電極117の厚さ t 1が有機低分子半導体層123とその上部の第1保護膜127の厚さを合せた厚さ t 2より厚く形成されて前記ソース及びドレイン電極113、115そしてデータパッド電極117と前記フォトレジストパターン120た形成された第1保護膜127の表面より高い所に形成されることによって、前記接触面121の露出した両側面部でストリップ液が前記フォトレジストパターン120を溶かして浸透し、最終的に前記フォトレジストパターン120を溶かして浸透し、最終的に前記フォトレジストパターン120上部に形成された低分子有機半導体層123とその上

20

30

40

50

部の第1保護膜127も共に除去される。このようなフォトレジストパターン120及び その上部に積層されたパターンまで共に除去する方法をリフトオフ法というが、さらに詳 細に説明するとフォトレジストパターン120と反応するストリップ液は前述した構造に おいては上部には低分子有機半導体層123及び第1保護膜127が形成されているので フォトレジストパターン120と直接接触することができないが、前記ソース及びドレイ ン電極113、115とデータパッド電極117により段差が発生した部分すなわち、前 記ソース及びドレイン電極113、115とデータパッド電極117上部に形成されたフ ォトレジストパターン120の側面部はストリップ液と接触するようになって、前記スト リップ液がソース及びドレイン電極113、115とその上部に形成されたフォトレジス トパターン120の接触面121で浸透して前記フォトレジストパターン120と反応す ることによって前記フォトレジストパターン120を基板101から分離される。この時 、ソース及びドレイン電極113、115とデータ配線(図示せず)とデータパッド電極 117が形成された領域以外の基板101上領域に形成された低分子有機半導体層123 とその上部の第1保護膜127は相変らず基板101上に残っているようになって、前述 したストリップ工程進行時ストリップ液に非常に弱い低分子有機半導体層は上部の第1保 護膜により前記ストリップ液との接触が遮断されることによって水分と反応しなくなるの でストリップ液と接触による低分子有機半導体層の損傷は発生しない。

#### [0056]

前述したように、前記第1実施形態では、前記有機絶縁物質で構成されたゲート絶縁膜110は段差なしに平坦な上部面を有して、前記データライン、前記ソース電極113、前記ドレイン電極115そしてデータパッド電極117それぞれの厚さt1は前記半導体層123及び前記第1保護膜127の総厚さt2と同一であるか又は大きい。しかし、前記ゲート絶縁膜110が段差構造で形成された上部面を有することもできる。前記ゲート絶縁膜110が段差構造を有する上部面を有する時、前記第1保護膜127の上部面は、前記リフトオフ工程が容易いように前記ソース電極113と前記ドレイン電極115それぞれの上部面と一致するかまたはその下に位置することもできる。

#### [0057]

言い換えると、前記ソース電極113と前記ドレイン電極115それぞれの上部面と一致するか又はその下に位置するように前記第1保護膜127の上部面を調節することによって前記フォトレジストパターン120の側壁は前記第1保護膜127により覆われないことである。したがって、前記フォトレジストパターン120は效果的に除去されることによって、前記リフト工程中に前記フォトレジストパターン120と重なる前記半導体層123と前記第1保護膜127を除去することができる。

### [0058]

したがって、こういう場合前記ゲート絶縁膜110は平坦な上部面を有する必要がなくて、前記ソース電極113とドレイン電極115の厚さt1は前記第1保護膜127と前記半導体層123の総厚さt2と同一であったり大きい。もしも前記第1保護膜127の上部面が前記ソース電極113及び前記ドレイン電極115それぞれの上部面と一致するかその下にあるならば、前記フォトレジストパターン120の全体側壁は前記リフトオフ工程を遂行する時露出するので前記フォトレジストパターン120は效果的に除去される

#### [0059]

この時、前記ソース及びドレイン電極113、115間に形成された低分子有機半導体層123は前記ソース及びドレイン電極113、115の間隔d1によりパターニングされることでその幅または長さが40μm以下である微細パターン形成が可能になる。

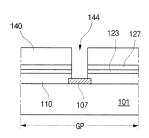

## [0060]

次に、図8Aないし図8Cに示したように、前記データ配線(図示せず)を含むソース及びドレイン電極113、115とデータパッド電極117上部のフォトレジストパターン(図7Aないし図7Cの120)が除去された基板101上に有機絶縁物質例えばPVP(polyvinylpyrrolidine)、BCB(benzocyclobu

tene)のうちから選択される物質をコーティングすることによって全面に第2保護膜140を形成する。この時、前記第2保護膜140は前述した有機物質でコーティングされて形成されることによってその表面が平坦に形成される。

#### [0061]

以後、前記第2保護膜140をマスク(図示せず)を利用してパターニングすることによってドレイン電極115とゲートパッド電極107とデータパッド電極117を露出させるドレインコンタクトホール142と、ゲートパッドコンタクトホール144とデータパッドコンタクトホール146を形成する。

#### [0062]

次に、図9Aないし図9Cに示したように、透明導電性物質例えばインジウム・スズ・オキサイド(indium・tin・oxide)またはインジウム・ジンク・オキサイド(indium・zinc・oxide)のうちから選択される物質を全面に蒸着してパターニングすることによって前記ドレインコンタクトホール142を介してドレイン電極115と接触する画素電極150を各画素領域P別に形成すると同時にゲートパッド部GPにおいてはゲートパッドコンタクトホール144を介してゲートパッド電極107と接触するゲート補助パッド電極152を形成して、データパッド部DPにおいてはデータパッドコンタクトホール146を介してデータパッド電極117と接触するデータ補助パッド電極154を形成することによってアレイ基板を完成する。

<第2実施形態>

### [0063]

本発明の第1実施形態はシャドーマスクを利用せず、低分子有機半導体物質を形成することによってシャドーマスク特性上からくる微細パターンの困難さを解決するための発明であったが、低分子有機半導体層が画素領域にも形成されているので、たとえばその透過度が85%以上になる低分子有機半導体層を用いていると表示装置では問題にならないが、そのことは85%以上の透過度を有する低分子有機半導体物質を利用しなければならないという制限となる。こういう透過度が優秀な低分子半導体物質を利用すると、画素領域において微ずかではあるが輝度を低下させるようになる。

#### [0064]

本発明の第2実施形態はこのような第1実施形態をさらに改良したことであって低分子有機半導体層の微細パターン形成が可能なことと同時に画素領域には形成されないようにしたことを特徴とする。

## [0065]

本発明の第2実施形態は低分子有機半導体層を形成する以前までの段階すなわちデータ配線を含むソース及びドレイン電極とデータパッド電極を形成して、その上部にフォトレジストパターンが残っているようにする段階までは第1実施形態と同一であるので図面及びその説明は省略して以後の段階に対してだけ図面を参照しながら説明する。

## [0066]

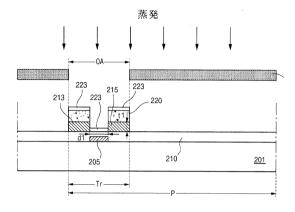

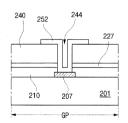

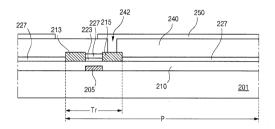

図10Aないし図10C、図11Aないし図11C、図12Aないし図12C、図13Aないし図13C、そして図14Aないし図14Cは本発明の第2実施形態による液晶表示装置のアレイ基板を製造する工程を示す概略的な断面図で、図10A、図11A、図12A及び図13Aは本発明の第2実施形態による低分子有機半導体物質を利用した液晶表示装置用アレイ基板を製造する方法を図示した製造断面図で薄膜トランジスタを含む一つの画素領域に対する製造工程断面図であり、図10B、図11B、図12B及び図13Bゲートパッド領域に対する製造工程断面図であり、図10C、図11C、図12C及び図13Cはデータパッド部に対する製造工程断面図である。

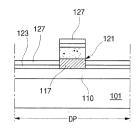

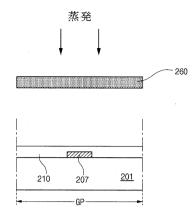

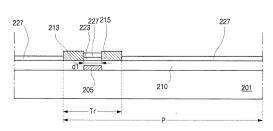

## [0067]

まず、図10Aないし図10Cに示したように、前記データ配線とソース及びドレイン電極213、215とデータパッド電極217が形成されて、その上にフォトレジストパターン220が残っている基板201上にシャドーマスク260を位置させて、前記シャドーマスク260を介した低分子有機半導体物質の蒸発工程を実施する。この時、前記シ

10

20

30

40

ャドーマスク260はゲートパッド部GPとデータパッド部DPに対し開口部OAなく、画素領域Pに対応する部分においても下部のソース及びドレイン電極213、215と前記両電極213、215間の離隔された領域d1にだけ開口部OAを有するようになっていることによって、このような構造を有するシャドーマスク260を利用して低分子有機半導体物質の蒸発工程時ソース及びドレイン電極213、215上部及び前記両電極213、215間の離隔された領域d1にだけ低分子有機半導体層223が形成されて、画素領域Pとゲート及びデータパッド部GP、DPには低分子有機半導体層が形成されないことが特徴である。この時、前記低分子有機半導体層を形成する低分子有機半導体物質に第1実施形態とは違って透過度の制限がなくなる。液晶表示装置のアレイ基板において画素領域Pのうち薄膜トランジスタ形成部分(Tr)は上部のカラーフィルター基板(図示せず)に形成されるブラックマトリックスにより遮られるようになる部分であるので低分子有機半導体層223が透過度が優秀な低分子有機半導体物質で形成されても、透過度が低い低分子有機半導体物質で形成されようがとにかく影響を受けなくなる。

[0068]

このようなシャドーマスク260を利用した低分子有機半導体層223の形成は従来に説明したように前記シャドーマスク260の開口部OAパターンのサイズ及び間隔の制限で長さまたは幅が40μm以下である微細パターンを形成しにくい短所があるが、本発明の第2実施形態の場合前記シャドーマスク260により40μm以上の幅と長さを有する低分子有機半導体層223が形成され、その後の工程により前記低分子有機半導体層を損傷なしにパターニングする段階を行えるようになるので、そのことは問題にならない。

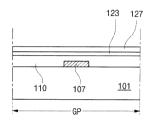

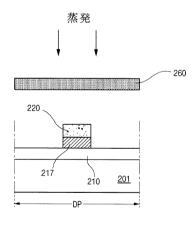

[0069]

次に、図11Aないし図11Cに示したように、前記ソース及びドレイン電極213、215目の離隔した領域d1に低分子有機半導体層223が形成された基板201全面に無機絶縁物質である酸化シリコン(SiO₂)を全面に蒸着して第1保護膜227を形成する。この時、前記酸化シリコン(SiO₂)の蒸着により形成された第1保護膜227は第1実施形態と一緒に段差が大きい部分すなわちソース及びドレイン電極213、215とデータパッド電極217とその上部のフォトレジストパターン220の側面部にはほとんど形成されないことが特徴である。この時、本発明の特徴上前記ソース及びドレイン電極213、215とデータパッド電極217はその厚さt1が前記低分子有機半導体層223とその上部の第1保護膜227の厚さを合せた厚さt2より厚く形成されることによって、前記フォトレジストパターン220との接触面221が前記画素領域Pに形成された第1保護膜27の表面より高い所に形成されたことが特徴である。

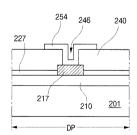

[0070]

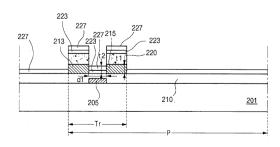

次に、図12Aないし図12Cに示したように、第1保護膜227まで形成された基板 201をストリップ液にディッピングすることで、第1実施形態で説明したようにリフト オフ法により前記ソース及びドレイン電極213、215とデータパッド電極217上部 に残っているフォトレジストパターン220を除去する。

[0071]

この時、前記ソース及びドレイン電極213、215間に形成された低分子有機半導体層223は前記ソース及びドレイン電極213、215の離隔間隔d1だけの幅または長さでパターニングされることで、シャドーマスク(図10Aないし図10Cの260)利用による微細パターン形成の制限を克服している。

[0072]

本実施形態で、前記ゲート絶縁膜210は平坦な上部面を有するが、本発明の範囲はこの実施例に限定されない。前記ゲート絶縁膜210が段差構造を有する上部面の場合、前記第1保護膜227の上部面は前記リフトオフ工程が容易できるように前記ソース電極213及び前記ドレイン電極215それぞれの上部面と一致したりその下にあることも出来る。

[0073]

10

20

30

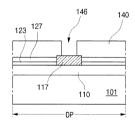

次に、図13Aないし図13Cに示したように、前記ソース及びドレイン電極213、 215とデータパッド電極217上部のフォトレジストパターン(図12Aないし図12 Cの220)が除去された基板201上に有機絶縁物質例えばPVP(polyviny lpyrrolidine)、BCB(benzocyclobutene)のうちから 選択される物質をコーティングすることによって全面に第2保護膜240を形成する。

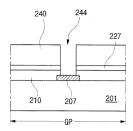

## [0074]

以後、前記第 2 保護膜 2 4 0 をマスクを利用してパターニングすることによって、ドレイン電極 2 1 3 とゲートパッド電極 2 0 7 とデータパッド電極 2 1 7 を露出させるドレインコンタクトホール 2 4 2 と、ゲートパッドコンタクトホール 2 4 4 とデータパッドコンタクトホール 2 4 6 を形成する。

## [0075]

次に、図14Aないし図14Cに示したように、透明導電性物質例えばインジウム・スズ・オキサイド(indium・tin・oxide)またはインジウム・ジンク・オキサイド(indium・zinc・oxide)のうちから選択される物質を全面に蒸着してパターニングすることによってドレインコンタクトホール242を介してドレイン電極213と接触する画素電極250を各画素領域P別に形成すると同時に、ゲートパッド部GPにおいてはゲートパッドコンタクトホール244を介してゲートパッド電極207と接触するゲート補助パッド電極252を形成して、データパッド部DPにおいてはデータパッドコンタクトホール246を介してデータパッド電極217と接触するデータ補助パッド電極254を形成することによってアレイ基板を完成する。

### 【符号の説明】

#### [0076]

101:基板

1 0 5 : ゲート電極

1 1 0 : ゲート絶縁膜

1 1 3 : ソース電極

1 1 5 : ドレイン電極

123:低分子有機半導体層

1 2 7 : 第 1 保護膜

1 4 0 : 第 2 保護膜

142:ドレインコンタクトホール

150:画素電極

P:画素領域

Tr:薄膜トランジスタ

d 1:第1間隔

t 1:ソース及びドレイン電極厚さ

t 2 : 半導体層の厚さと第1保護膜の厚さを合せた厚さ

10

20

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図4C】

【図4A】

【図5A】

【図4B】

【図5B】

【図6A】

【図6B】

【図7C】

【図8A】

【図8B】

【図 6 C】

【図7A】

【図7B】

【図8C】

【図9A】

【図9B】

【図9C】

【図10A】

【図10B】

【図10C】

【図11A】

【図11B】

【図11C】

【図12A】

【図12B】

【図12C】

【図13A】

【図14B】

【図14C】

【図13B】

【図13C】

【図14A】

## フロントページの続き

(72)発明者 ソ ヒョンシク

大韓民国 431-050 キョンギド アニャンシ ドンアング ビサンドン 308-3 ヒョソンサンアビラ 3-202

(72)発明者 ペク スンハン

大韓民国 407-764 インチョン ケヤング ケサン3ドン ハナ アパート 22-60 5

(72)発明者 チェ ナックボン

大韓民国 440-723 キョンギド スウォンシ チャンアング チョンチョンドン サムソ ンネマン アパート 102-1302

## 審査官 綿引 隆

(56)参考文献 特開2004-048032(JP,A)

特開2003-309268(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 29/786

H01L 21/336

H 0 1 L 5 1 / 0 5

G02F 1/1368