## (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

H01L 29/78 (2006.01) H01L 21/336 (2006.01)

(21) 출원번호 10-2012-0000341

(22) 출원일자 **2012년01월03일** 심사청구일자 **2012년01월03일**

(65) 공개번호 **10-2013-0079703**

(43) 공개일자 2013년07월11일

(56) 선행기술조사문헌 KR1020100038437 A\*

> US20110095267 A1\* KR1020080018559 A\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2013년12월05일

(11) 등록번호 10-1337267

(24) 등록일자 2013년11월29일

(73) 특허권자

고려대학교 산학협력단

서울 성북구 안암동5가 1

(72) 발명자

김상식

서울 강남구 대치동 1014-3 대치삼성아파트 108동 1205호

이명원

서울 강서구 등촌1동 두산위브센티움 1022호

전영인

경기 하남시 덕풍2동 하남자이아파트 109동 303호

(74) 대리인

특허법인주원

전체 청구항 수 : 총 8 항

심사관: 최정민

## (54) 발명의 명칭 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조방법

#### (57) 요 약

단결정 실리콘 나노와이어를 이용한 트랜지스터 및 그 제조 방법이 개시된다. 단결정 실리콘 나노와이어를 이용한 트랜지스터는 기판, 및 기판상에 형성된 단결정 나노와이어를 포함한다. 이때 단결정 실리콘 나노 와이어는, 단결정 실리콘 나노와이어의 길이 방향으로 서로 이격되어 형성되는 소스 영역과 드레인 영역, 소스 영역과 드레인 영역 사이에 위치하는 채널 영역을 포함하고, 길이 방향과 수직 방향으로의 채널 영역의 두께는 소스 영역과 드레인 영역의 두께보다 작다. 이와 같이, 트랜지스터의 채널로 사용되는 단결정 실리콘 나노와이어 채널 영역의 직경을 인접하는 소스 영역과 드레인 영역보다 작게 구현함으로써, 소스와 드레인의 기생저항이 작으면서도 우수한 정전기적 제어효과를 가지는 나노와이어를 이용한 트랜지스터를 제조할 수 있게 된다. 또한, 상기 단결정 실리콘 나노와이어를 이용한 트랜지스터는 채널 영역을 둘러싸는 게이트 전극, 및 단결정 실리콘 나노와이어 채널 영역과 게이트 전극 사이에 고유전율(high-k) 게이트 절연막을 더 포함할 수 있다. 이와 같이, 단결정 실리콘 나노와이어를 이용한 트랜지스터의 게이트 전극을 게이트 올 어라운드(Gate All Around; GAA)형으로 구성함으로써, 미세 크기를 가지면서도 단채널 효과를 극복할 수 있는 구조의 나노와이어를 이용한 트랜지스터 소자를 제조할수 있게 된다.

## 대 표 도 - 도5

이 발명을 지원한 국가연구개발사업

과제고유번호 과C6A1602

부처명교육과학기술부연구사업명2단계두뇌한국21

연구과제명 2단계BK21사업 6차년도 국고지원금

기 여 율 1/1

주관기관 고려대학교 산학협력단 연구기간 2011.03.01 ~ 2012.02.28

## 특허청구의 범위

## 청구항 1

삭제

## 청구항 2

삭제

## 청구항 3

삭제

## 청구항 4

삭제

## 청구항 5

단결정 실리콘 기판으로부터 단결정 실리콘 나노와이어를 형성하는 단계; 및

상기 형성된 단결정 실리콘 나노와이어를 트랜지스터 기판으로 전사하는 단계를 포함하는 단결정 실리콘 나노와 이어를 이용한 트랜지스터 제조 방법으로서.

상기 단결정 나노와이어를 형성하는 단계는,

상기 단결정 실리콘 나노와이어의 길이 방향으로 서로 이격되도록 상기 단결정 실리콘 나노와이어의 미리 설정 된 영역에 각각 소스 영역과 드레인 영역을 형성하고, 상기 소스 영역과 상기 드레인 영역 사이에 위치하는 채 널 영역을 형성하는 소자 영역 형성 단계; 및

상기 길이 방향과 수직 방향으로의 상기 채널 영역의 두께를 상기 소스 영역과 상기 드레인 영역의 두께보다 작 게 형성하는 채널 영역 두께 축소 단계를 포함하며,

상기 소자 영역 형성 단계는 상기 단결정 실리콘 나노와이어의 채널 영역, 소스와 드레인 영역 형성을 위해 불순물을 주입하는 단계를 포함하고,

상기 채널 영역 두께 축소 단계는 상기 채널 영역의 불순물 농도와 상기 소스 및 드레인 영역의 불순물 농도 사이의 불순물의 농도 차이에 따른 이방성 식각을 이용하여 상기 채널 영역의 두께를 축소시키는 단계를 포함하는 것을 특징으로 하는 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조 방법.

## 청구항 6

제 5항에 있어서,

상기 채널 영역을 둘러싸는 게이트 전극을 형성하는 단계를 더 포함하는 것을 특징으로 하는 단결정 실리콘 나 노와이어를 이용한 트랜지스터 제조 방법.

## 청구항 7

제 6항에 있어서,

상기 단결정 실리콘 나노와이어 채널 영역과 상기 게이트 전극 사이에 고유전율(high-k) 게이트 절연막을 형성하는 단계를 더 포함하는 것을 특징으로 하는 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조 방법.

## 청구항 8

삭제

## 청구항 9

단결정 실리콘 기판으로부터 단결정 실리콘 나노와이어를 형성하는 단계; 및

상기 형성된 단결정 실리콘 나노와이어를 트랜지스터 기판으로 전사하는 단계를 포함하는 단결정 실리콘 나노와 이어를 이용한 트랜지스터 제조 방법으로서,

상기 단결정 나노와이어를 형성하는 단계는,

상기 단결정 실리콘 나노와이어의 길이 방향으로 서로 이격되도록 상기 단결정 실리콘 나노와이어의 미리 설정 된 영역에 각각 소스 영역과 드레인 영역을 형성하고, 상기 소스 영역과 상기 드레인 영역 사이에 위치하는 채 널 영역을 형성하는 소자 영역 형성 단계; 및

상기 길이 방향과 수직 방향으로의 상기 채널 영역의 두께를 상기 소스 영역과 상기 드레인 영역의 두께보다 작 게 형성하는 채널 영역 두께 축소 단계를 포함하며,

상기 단결정 나노와이어를 형성하는 단계는,

상기 단결정 실리콘 기판상에 실리콘 산화막을 형성하는 단계;

상기 실리콘 산화막상에 실리콘 질화막을 형성하는 단계;

상기 실리콘 질화막을 식각하여 실리콘 나노와이어 엑티프 패턴을 형성하는 단계;

상기 실리콘 질화막을 마스크로 실리콘 기판을 식각하여 실리콘 컬럼구조물을 형성하는 단계;

상기 실리콘 컬럼구조물을 결정 구조에 따라 이방성 식각하여 모래시계 형태의 실리콘 구조물을 형성하는 단계;

상기 실리콘 구조물 위에 상기 나노와이어의 채널 영역 노출시키는 단계;

상기 채널 영역이 노출된 모래시계 형태의 실리콘 구조물을 산화시키는 단계;

상기 실리콘 질화막을 제거하는 단계; 및

상기 실리콘 구조물로부터 산화막을 제거하는 단계를 포함하는 것을 특징으로 하는 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조방법.

## 청구항 10

단결정 실리콘 기판으로부터 단결정 실리콘 나노와이어를 형성하는 단계; 및

상기 형성된 단결정 실리콘 나노와이어를 트랜지스터 기판으로 전사하는 단계를 포함하는 단결정 실리콘 나노와 이어를 이용한 트랜지스터 제조 방법으로서.

상기 단결정 나노와이어를 형성하는 단계는,

상기 단결정 실리콘 나노와이어의 길이 방향으로 서로 이격되도록 상기 단결정 실리콘 나노와이어의 미리 설정 된 영역에 각각 소스 영역과 드레인 영역을 형성하고, 상기 소스 영역과 상기 드레인 영역 사이에 위치하는 채 널 영역을 형성하는 소자 영역 형성 단계; 및

상기 길이 방향과 수직 방향으로의 상기 채널 영역의 두께를 상기 소스 영역과 상기 드레인 영역의 두께보다 작 게 형성하는 채널 영역 두께 축소 단계를 포함하며,

상기 단결정 나노와이어를 형성하는 단계는,

상기 단결정 실리콘 기판상에 실리콘 산화막을 형성하는 단계;

상기 실리콘 산화막상에 실리콘 질화막을 형성하는 단계;

상기 실리콘 질화막을 식각하여 실리콘 나노와이어 엑티프 패턴을 형성하는 단계;

상기 실리콘 질화막을 마스크로 실리콘 기판을 식각하여 실리콘 컬럼구조물을 형성하는 단계;

상기 실리콘 컬럼구조물을 결정 구조에 따라 이방성 식각하여 모래시계 형태의 실리콘 구조물을 형성하는 단계;

상기 모래시계 형태의 실리콘 구조물을 산화시키는 단계;

상기 실리콘 구조물 위에 상기 나노와이어의 채널 영역 노출시키는 단계;

상기 노출된 채널 영역을 미리 설정된 깊이로 제거하는 단계;

상기 실리콘 질화막을 제거하는 단계; 및

상기 실리콘 구조물로부터 산화막을 제거하는 단계를 포함하는 것을 특징으로 하는 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조방법.

## 청구항 11

제 5, 9, 10항 중 어느 한 항에 있어서,

상기 이방성 식각은 이방성 식각 용액 테트라메틸 암모늄 하이드록사이드(tetramethyl ammonium hydroxide; TMAH)를 이용하여 수행되는 것을 특징으로 하는 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조 방법.

## 청구항 12

제 9 또는 10항에 있어서,

상기 단결정 실리콘은 열산화 방법으로 산화시키는 것을 특징으로 하는 단결정 실리콘 나노와이어를 이용한 트 랜지스터 제조 방법.

## 청구항 13

제 9 또는 10항에 있어서,

상기 실리콘 질화막의 제거 이후,

상기 실리콘 질화막이 제거된 단결정 실리콘 기판 영역에서, 상기 실리콘 산화막을 제거하고, 다시 실리콘 열산화막을 형성하는 단계를 더 포함하는 것을 특징으로 하는 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조방법.

## 명 세 서

## 기술분야

[0001] 본 발명은 반도체 소자 및 그 제조 방법에 관한 것으로서, 더욱 상세하게는 나노와이어를 이용하여 제작되는 트랜지스터 및 그 제조 방법에 관한 것이다.

## 배경기술

- [0002] 종래의 바텀-업 (bottom-up) 방식의 나노와이어 제조 방법에 있어서, 나노와이어 합성 및 그의 전기적, 광학적 및 물리적 특성에 대한 연구는 상당한 진전을 보이고 있지만, 이를 원하는 위치에 정렬(alignment)하는 방법은 아직 집적 시스템에 응용하는데 한계점이 있다.

- [0003] 이에 반해, 탑-다운 (top-down) 방식으로 나노와이어를 제작하는 경우 정렬에 대한 문제점은 극복이 가능하나, 주로 SOI 기판과 전자빔 리소그라피(e-beam lithography)를 통해 제작되고 있어 나노와이어 소자의 생산성에 있어 문제점이 있다.

- [0004] 최근에 SOI 기판이 아닌 단결정 실리콘 기판을 이용한 나노와이어 제작에 관한 다양한 방법이 소개되고 있지만 이를 이용한 소자는 딱딱한(rigid) 기판에 구현되거나 또는 플렉시블 기판에 구현되더라도 바텀-게이트 (bottom-gate) 및 탑-게이트(top-gate) 구조를 가지고 있는 경우가 대부분이다.

- [0005] 그런데 나노와이어는 그 직경이 감소할수록, 나노와이어 소자의 정전기적 제어효과는 우수해지지만, 소스/드레인의 기생저항이 커지는 문제점이 있다.

- [0006] 또한, 소자 크기가 작아짐에 따라, 소자 형성 영역 특히 액티브 영역에 형성되는 트랜지스터의 채널 길이가 줄 어들며, 이에 따라 소스/드레인 영역이 채널 영역의 전계에 미치는 영향이 현저해지고 게이트 전국에 의한 채널 구동 능력이 열화되는 단채널 효과(short channel effect)가 나타나는 문제점이 나타나게 된다.

## 발명의 내용

## 해결하려는 과제

- [0007] 본 발명은 상술한 종래의 문제점을 해결하기 위해 안출된 것으로서, 소스와 드레인의 기생저항이 작으면서도 우수한 정전기적 제어효과를 가지는 나노와이어를 이용한 트랜지스터 소자 및 그 제조 방법을 제공하는 것을 목적으로 한다.

- [0008] 또한, 미세 크기를 가지면서도 단채널 효과를 극복할 수 있는 구조의 나노와이어를 이용한 트랜지스터 소자 및 그 제조 방법을 제공하는 것을 목적으로 한다.

## 과제의 해결 수단

- [0009] 상기 목적을 달성하기 위해 본 발명에 따른 단결정 실리콘 나노와이어를 이용한 트랜지스터는 기판, 및 기판상에 형성된 단결정 나노와이어를 포함한다. 이때 단결정 실리콘 나노 와이어는, 단결정 실리콘 나노와이어의 길이 방향으로 서로 이격되어 형성되는 소스 영역과 드레인 영역, 소스 영역과 드레인 영역 사이에 위치하는 채널 영역을 포함하고, 길이 방향과 수직 방향으로의 채널 영역의 두께는 소스 영역과 드레인 영역의 두께보다 작다.

- [0010] 이와 같이, 트랜지스터의 채널로 사용되는 단결정 실리콘 나노와이어 채널 영역의 직경을 인접하는 소스 영역과 드레인 영역보다 작게 구현함으로써, 소스와 드레인의 기생저항이 작으면서도 우수한 정전기적 제어효과를 가지는 나노와이어를 이용한 트랜지스터를 제조할 수 있게 된다.

- [0011] 또한, 상기 단결정 실리콘 나노와이어를 이용한 트랜지스터는 채널 영역을 둘러싸는 게이트 전국, 및 단결정 실리콘 나노와이어 채널 영역과 게이트 전국 사이에 고유전율(high-k) 게이트 절연막을 더 포함할 수 있다.

- [0012] 이와 같이, 단결정 실리콘 나노와이어를 이용한 트랜지스터의 게이트 전국을 게이트 올 어라운드(Gate All Around; GAA)형으로 구성함으로써, 미세 크기를 가지면서도 단채널 효과를 극복할 수 있는 구조의 나노와이어를 이용한 트랜지스터 소자를 제조할 수 있게 된다.

- [0013] 또한, 상기 단결정 실리콘 나노와이어를 이용한 트랜지스터의 기판은 플렉시블 기판일 수 있다.

- [0014] 또한, 본 발명에 따른 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조 방법은, 단결정 실리콘 기판으로부터 단결정 실리콘 나노와이어를 형성하는 단계, 및 형성된 단결정 실리콘 나노와이어를 트랜지스터 기판으로 전사하는 단계를 포함한다.

- [0015] 이때, 단결정 나노와이어를 형성하는 단계는, 단결정 실리콘 나노 와이어의 길이 방향으로 서로 이격되도록 단결정 실리콘 나노 와이어의 미리 설정된 영역에 각각 소스 영역과 드레인 영역을 형성하고, 소스 영역과 드레인 영역 사이에 위치하는 채널 영역을 형성하는 소자 영역 형성 단계, 및 길이 방향과 수직 방향으로의 상기 채널 영역의 두께를 소스 영역과 드레인 영역의 두께보다 작게 형성하는 채널 영역 두께 축소 단계를 포함한다.

- [0016] 또한, 상기 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조 방법은 채널 영역을 둘러싸는 게이트 전극을 형성하는 단계, 및 단결정 실리콘 나노와이어 채널 영역과 상기 게이트 전극 사이에 고유전율(high-k) 게이트 절연막을 형성하는 단계를 더 포함할 수 있다.

- [0017] 또한, 소자 영역 형성 단계는, 단결정 실리콘 나노와이어의 채널 영역, 소스와 드레인 영역 형성을 위해 불순물을 주입하는 단계를 포함하고, 채널 영역 두께 축소 단계는 채널 영역의 불순물 농도와 소스 및 드레인 영역의 불순물 농도 사이의 불순물의 농도 차이에 따른 이방성 식각을 이용하여 상기 채널 영역의 두께를 축소시키는 단계를 포함할 수 있다.

- [0018] 또한, 단결정 나노와이어를 형성하는 단계는, 단결정 실리콘 기판상에 실리콘 산화막을 형성하는 단계, 실리콘 산화막상에 실리콘 질화막을 형성하는 단계, 실리콘 질화막 및 산화막을 식각하여 실리콘 나노와이어 액티프 패턴을 형성하는 단계, 실리콘 질화막을 마스크로 실리콘 기판을 식각하여 실리콘 컬럼구조물을 형성하는 단계, 실리콘 컬럼구조물을 결정 구조에 따라 이방성 식각하여 모래시계 형태의 실리콘 구조물을 형성하는 단계, 실리콘 구조물 위에 나노와이어의 채널 영역 노출시키는 단계, 채널 영역이 노출된 모래시계 형태의 실리콘 구조물을 산화시키는 단계, 및 실리콘 질화막을 제거하는 단계, 및 실리콘 구조물로부터 산화막을 제거하는 단계를 포함할 수 있다.

- [0019] 또한, 단결정 나노와이어를 형성하는 단계는, 단결정 실리콘 기판상에 실리콘 산화막을 형성하는 단계, 실리콘 산화막상에 실리콘 질화막을 형성하는 단계, 실리콘 질화막 및 산화막을 식각하여 실리콘 나노와이어 엑티프 패턴을 형성하는 단계, 실리콘 질화막을 마스크로 실리콘 기판을 식각하여 실리콘 컬럼구조물을 형성하는 단계,

실리콘 컬럼구조물을 결정 구조에 따라 이방성 식각하여 모래시계 형태의 실리콘 구조물을 형성하는 단계, 모래시계 형태의 실리콘 구조물을 산화시키는 단계, 실리콘 구조물 위에 나노와이어의 채널 영역 노출시키는 단계, 노출된 채널 영역을 미리 설정된 깊이로 제거하는 단계, 실리콘 질화막을 제거하는 단계, 및 실리콘 구조물로부터 산화막을 제거하는 단계를 포함할 수 있다.

- [0020] 또한, 이방성 식각은 이방성 식각 용액 테트라메틸 암모늄 하이드록사이드(tetramethyl ammonium hydroxide; TMAH)를 이용하여 수행될 수 있다.

- [0021] 또한, 단결정 실리콘은 열산화 방법으로 산화시킬 수 있다.

- [0022] 또한, 실리콘 질화막 및 산화막의 제거 이후에 단결정 실리콘 기판상에 열산화막을 형성하는 단계를 더 포함할 수 있다.

## 발명의 효과

- [0023] 본 발명에 의하면, 트랜지스터의 채널로 사용되는 단결정 실리콘 나노와이어 채널 영역의 직경을 인접하는 소스 영역과 드레인 영역보다 작게 구현함으로써, 소스와 드레인의 기생저항이 작으면서도 우수한 정전기적 제어효과를 가지는 나노와이어를 이용한 트랜지스터를 제조할 수 있게 된다.

- [0024] 또한, 단결정 실리콘 나노와이어를 이용한 트랜지스터의 게이트 전극을 게이트 올 어라운드(Gate All Around; GAA)형으로 구성함으로써, 미세 크기를 가지면서도 단채널 효과를 극복할 수 있는 구조의 나노와이어를 이용한 트랜지스터 소자를 제조할 수 있게 된다.

#### 도면의 간단한 설명

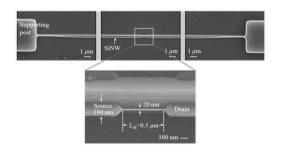

[0025] 도 1은 본 발명에 따른 단결정 실리콘 나노와이어를 이용한 트랜지스터 제조 방법에 따라 제조된 나노와이어의 SEM 사진.

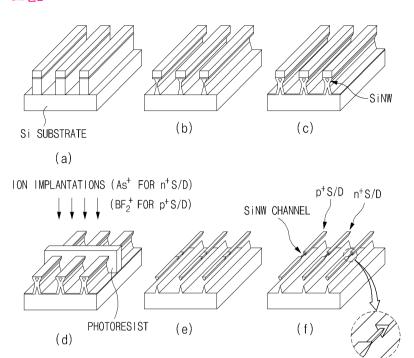

도 2는 본 발명의 제1실시예에 따른 단결정 실리콘 나노와이어 제조공정도.

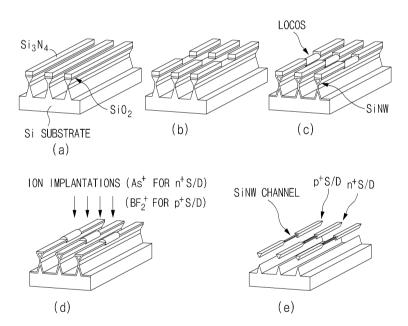

도 3은 본 발명의 제2실시예에 따른 단결정 실리콘 나노와이어 제조공정도.

도 4는 본 발명의 제3실시예에 따른 단결정 실리콘 나노와이어 제조공정도.

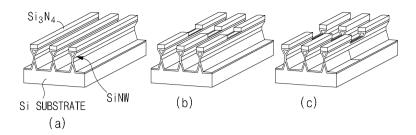

도 5는 본 발명의 제1실시예 내지 제3실시예에 따른 단결정 실리콘 나노와이어를 이용한 소자 제조공정도.

#### 발명을 실시하기 위한 구체적인 내용

- [0026] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 설명한다.

- [0027] 도 1은 본 발명에 따른 단결정 실리콘 나노와이어를 이용한 트랜지스터의 일 실시예에 따라 제조된 나노와이어 의 SEM 사진이다. 도 1에서 제조된 나노와이어는 지지 기둥(Supporting Pad)에 의해 지지되고 있고, 채널 영역의 직경이 인접한 소스 영역 및 드레인 영역의 직경보다 작게 형성된 것을 확인할 수 있다.

- [0028] 이와 같이, 트랜지스터의 채널로 사용되는 단결정 실리콘 나노와이어 채널 영역의 직경을 인접하는 소스 영역과 드레인 영역보다 작게 구현함으로써, 소스와 드레인의 기생저항이 작으면서도 우수한 정전기적 제어효과를 가지는 나노와이어를 이용한 트랜지스터를 제조할 수 있게 된다.

- [0029] 또한, 상기 단결정 실리콘 나노와이어를 이용한 트랜지스터는 채널 영역을 둘러싸는 게이트 전국, 및 단결정 실리콘 나노와이어 채널 영역과 게이트 전국 사이에 고유전율(high-k) 게이트 절연막을 더 포함할 수 있다.

- [0030] 이와 같이, 단결정 실리콘 나노와이어를 이용한 트랜지스터의 게이트 전국을 게이트 올 어라운드(Gate All Around; GAA)형으로 구성함으로써, 미세 크기를 가지면서도 단채널 효과를 극복할 수 있는 구조의 나노와이어를 이용한 트랜지스터 소자를 제조할 수 있게 된다.

- [0031] 이하 본 발명을 구체적인 예와 함께 보다 상세하게 설명한다.

- [0032] [제1실시예]

- [0033] 도 2는 본 발명의 제1실시예에 따른 단결정 실리콘 나노와이어 제조공정도이다. 도 2에는 고농도 불순물이 주입

된 소스/드레인 영역과 저농도 불순물이 주입된 채널 영역의 불순물 농도 차이에 따른 이방성 습식 식각용액의 식각률 차이를 이용하여 나노와이어 채널의 직경이 얇은 단결정 실리콘 나노와이어를 제조하는 방법이 도시되어 있다.

- [0034] 우선, 결정구조가 (100)인 단결정 실리콘 기판상에 제1열산화막과 실리콘 질화막을 증착한 후, 사진 공정을 통하여 실리콘 나노와이어 액티프 패턴을 형성한다. 이후, 상기 실리콘 질화막을 마스크로 사용하여 실리콘 건식 식각공정을 통하여 실리콘 기판을 등방성 식각함으로써 실리콘 컬럼구조를 형성한다(도 2a).

- [0035] 이후, 이방성 식각용액인 테트라메틸 암모늄 하이드록사이드(tetramethyl ammonium hydroxide, TMAH)를 이용하여 실리콘 컬럼구조를 습식 식각하면 모래시계 형태의 실리콘 구조물이 형성된다(도 2b). 이와 같이, (111) 결정구조에 대한 이방성 식각 용액의 습식 식각률이 (100) 또는 (110) 결정구조에 대한 습식 식각률에 비해 훨씬 느리기 때문에 (111) 결정구조는 식각 방지층으로 작용하여 모래시계 형태의 실리콘 구조물을 형성할 수 있다.

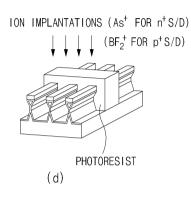

- [0036] 이후, 모래시계 형태의 실리콘 구조물을 열산화하여 제2열산화막 성장을 통하여 삼각형 형태의 실리콘 나노와이어를 형성한다(도 2c). 이후, 실리콘 질화막을 제거하고 사진 공정을 통하여 나노와이어의 소스/드레인 영역을 정의한 후 이온주입 공정을 통한 불순물을 주입한다(도 2d).

- [0037] 이때, 실리콘 질화막의 제거 후 불순물 주입 이전에, 단결정 실리콘 기판상에서 제1열산화막을 제거하고 다시 제3열산화막을 형성할 수도 있다. 이 경우, 실리콘 질화막의 제거시 손상된 제1열산화막 대신 양호한 상태의 제3열산화막을 단결정 실리콘 기판상에 형성할 수 있게 된다.

- [0038] 이후 포토레지스트(Photoresist)를 제거하고 불순물을 활성화시키기 위한 열처리를 진행한다. 이후 제1열산화막 및 제2열산화막을 제거하여 기판으로부터 릴리즈된 실리콘 나노와이어를 형성한다(도 2e).

- [0039] 마지막으로 이방성 식각용액인 테트라메틸 암모늄 하이드록사이드(tetramethyl ammonium hydroxide, TMAH)를 이용하여 실리콘 나노와이어를 습식 식각하여 고농도 불순물이 주입된 소스/드레인 영역의 실리콘 나노와이어 직경은 그대로 유지한 채 수nm 또는 수십 nm 급의 채널 직경을 가지는 단결정 실리콘 나노와이어를 형성한다(도 2f).

- [0040] [제2실시예]

- [0041] 도 3은 본 발명의 제2실시예에 따른 단결정 실리콘 나노와이어 제조공정도이다.

- [0042] 도 3에 도시된 바와 같이, 본 발명의 제2실시예에 따른 단결정 실리콘 기판을 이용한 얇은 채널 직경을 가지는 실리콘 나노와이어 제조방법에서는, 나노와이어의 채널 영역을 노출시킨 후 열산화막을 성장시켜 실리콘 나노와이어 제3일 이어 채널영역의 직경을 감소시킴으로써, 고농도 불순물이 주입될 소스/드레인 영역의 실리콘 나노와이어 직경은 두껍게 유지한 채 수nm 또는 수십 nm 급의 채널 직경을 가지는 단결정 실리콘 나노와이어를 제작한다.

- [0043] 이때, 제2실시예에서의 공정 중 일부는 도 2a 내지 도 2b 공정과 동일하기 때문에, 이후 실리콘 나노와이어 채 널영역의 직경을 줄이는 공정을 상세히 설명한다.

- [0044] 도 2a 내지 도 2b 공정을 통한 모래시계 형태의 실리콘 구조물을 형성한 후 (도 3a), 사진 식각공정을 통하여 나노와이어의 채널영역을 노출시킨다(도 3b). 이후, 실리콘 나노와이어를 열산화하여 제2열산화막을 형성하게 되면 실리콘 질화막 아래의 소스/드레인 영역의 실리콘 나노와이어는 측면에서만 산화막이 성장하는 반면, 채널 영역의 실리콘 나노와이어는 측면뿐만 아니라 윗면에서도 산화막이 성장하게 되므로 소스/드레인 보다 얇은 채널의 실리콘 나노와이어를 형성할 수 있다(도 3c).

- [0045] 이후 실리콘 질화막을 제거하고 사진 공정을 통하여 나노와이어의 소스/드레인 영역을 정의한 후 이온주입 공정을 통한 불순물을 주입한다(도 3d). 이때, 제1실시예에서와 같이, 실리콘 질화막의 제거 후 불순물 주입 이전에 단결정 실리콘 기판상에서 제1열산화막을 제거하고 다시 제3열산화막을 형성할 수도 있다.

- [0046] 이후 포토레지스트(Photoresist)를 제거하고 불순물을 활성화시키기 위한 열처리를 진행한다. 마지막으로, 제1 열산화막 및 제2열산화막을 제거하게 되면 기판으로부터 릴리즈된 얇은 채널 영역을 가지는 실리콘 나노와이어 를 형성할 수 있다(도 3e).

- [0047]

- [0048] [제3실시예]

- [0049] 도 4는 본 발명의 제3실시예에 따른 단결정 실리콘 나노와이어 제조공정도이다.

- [0050] 도 4에 도시된 바와 같이, 본 발명의 제3실시예에 따른 단결정 실리콘 기판을 이용한 얇은 채널 직경을 가지는 실리콘 나노와이어 제조방법에서는, 나노와이어의 채널 영역만을 노출시켜 실리콘 건식 식각을 통하여 실리콘 나노와이어 채널영역의 직경을 감소시킴으로써, 고농도 불순물이 주입될 소스/드레인 영역의 실리콘 나노와이어 직경은 두껍게 유지한 채 수nm 또는 수십 nm 급의 채널 직경을 가지는 단결정 실리콘 나노와이어를 제작한다.

- [0051] 제3실시예에서는 공정 일부가 제1실시예의 도 2a내지 도 2c 공정까지와 동일하기 때문에, 이후 실리콘 나노와이 어 채널영역의 직경을 줄이는 공정을 상세히 설명한다.

- [0052] 도 2a 내지 도 2c 공정을 통한 삼각형 형태의 실리콘 나노와이어를 형성한 후(도 4a), 사진 식각공정을 통하여 나노와이어의 채널영역을 노출시킨다(도 4b).

- [0053] 이후, 실리콘 나노와이어 건식 식각을 통하여 소스/드레인 보다 얇은 채널의 실리콘 나노와이어를 형성한다(도 4c). 이때, 소스/드레인 영역의 실리콘 나노와이어는 실리콘 질화막이 건식 식각 방지막으로 사용되기 때문에 건식 식각에 영향을 받지 않게 된다.

- [0054] 이후 실리콘 질화막을 제거하고 사진 공정을 통하여 나노와이어의 소스/드레인 영역을 정의한 후 이온주입 공정을 통한 불순물을 주입한다(도 4d). 이때, 제 1 및 2 실시예에서와 마찬가지로 실리콘 질화막의 제거 후 불순물 주입 이전에, 단결정 실리콘 기판상에서 제1열산화막을 제거하고 다시 제3열산화막을 형성할 수도 있다.

- [0055] 이후 포토레지스트(Photoresist)를 제거하고 불순물을 활성화시키기 위한 열처리를 진행한다. 마지막으로, 제1 열산화막 및 제2열산화막을 제거하게 되면 기판으로부터 릴리즈된 얇은 채널 영역을 가지는 실리콘 나노와이어를 형성할 수 있다(도 4e).

- [0056] [제4실시예]

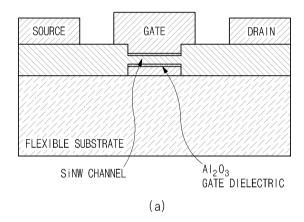

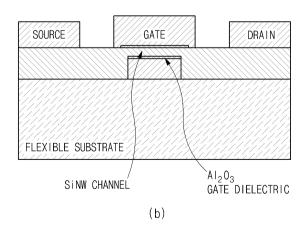

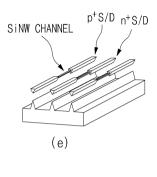

- [0057] 도 5는 본 발명의 제1실시예 내지 제3실시예에 따른 단결정 실리콘 나노와이어를 이용한 소자 제조공정도이다.

- [0058] 도 5에 도시된 바와 같이, 본 발명의 제4실시예에서는 제1실시예 내지 제3실시예의 방법을 적용하여 제작된 나 노와이어를 이용하여 플렉시블 전면 게이트 트랜지스터를 제조한다.

- [0059] 본 발명의 제1실시예 내지 제3실시예의 방법에 의하여 형성된 얇은 채널 직경을 가지는 실리콘 나노와이어를 이용하면, 도 5a 또는 도 5b에 도시된 바와 같이 실리콘 나노와이어를 절연성 플렉시블 기판에 전사한 후 게이트 절연막과 금속 전극을 형성하여 전면 게이트 구조를 갖는 트랜지스터를 제작할 수 있다.

- [0060] 이때, 얇은 채널 직경을 가지는 단결정 실리콘 나노와이어를 전사할 절연성 플렉시블 기판은 고무, 섬유, 종이 및 플라스틱 기판 등을 포함한다. 한편, 얇은 채널 직경을 가지는 단결정 실리콘 나노와이어를 다른 절연성 기판으로의 전사는 점착 특성이 좋은 포토리지스트(photoresist) 또는 레진(resin)과 같은 폴리머(polymer) 등으로 이루어질 수 있으며, 전사 이후에는 산소 플라즈마를 이용한 건식 에싱(ashing) 및 에탄올(Ethanol)을 이용한 습식 식각을 통해 제거할 수 있다.

- [0061] 본 발명에서는 단결정 실리콘 기판을 이용하여 기존의 CMOS 호환 공정을 통한 얇은 채널 직경을 가지는 실리콘 나노와이어를 제작한 후, 이를 다른 플랙시블 절연성 기판에 전사함으로써 제작되는 플랙시블 전면 게이트 트랜 지스터 소자 및 그의 제조방법을 제공한다.

- [0062] 따라서, 본 발명의 단결정 실리콘 나노와이어 제작방법을 이용하여 제작된 플렉시블 전면 게이트 전계효과 트랜 지스터는 짧은 채널 효과를 제어하기에 우수하며, 소스/드레인 기생저항 성분이 작아 전류 구동능력이 우수하다는 이점이 있다.

- [0063] 또한, 본 발명의 단결정 실리콘 나노와이어 제작방법을 이용한 플렉시블 전면 게이트 터널링 전계효과 트랜지스터는 터널링 확률을 더욱 효과적으로 제어하여 ON/OFF 스위칭 특성을 향상시킬 수 있는 이점이 있다.

- [0064] 한편, 본 발명은 잘 알려진 기존의 실리콘 공정 기술을 그대로 적용함으로써 전자빔 리소그라피 공정과 SOI 웨이퍼를 사용하지 않고서도 채널 영역의 직경이 수십 mm급인 나노와이어 소자를 생산할 수 있는 장점이 있다.

- [0065] 본 발명에 따른 단결정 실리콘 기판을 이용한 얇은 채널 직경을 가지는 실리콘 나노와이어 제조 및 플렉시블 전

면 게이트 트랜지스터 제작 방법은 단결정 실리콘 기판을 사용하여 웨이퍼 단위의 공정에서 얇은 채널 직경을 가지는 단결정 실리콘 나노와이어를 제조한 후, 이를 다른 플렉시블 절연성 기판에 전사하고 금속 전극을 사진 공정 및 리프트 오프 공정을 통하여 플렉시블 전면 게이트 트랜지스터를 제작한다.

- [0066] 본 발명의 일실시예에 따른 얇은 채널 직경을 가지는 단결정 실리콘 나노와이어 제작 방법은 잘 알려진 기존의 실리콘 공정 기술을 그대로 적용 가능하며, 불순물 농도 차이에 따른 이방성 식각용액인 테트라메틸 암모늄 하이드록사이드(tetramethyl ammonium hydroxide, TMAH)의 식각률 차이를 이용하여 고농도 불순물이 주입된 소스/드레인 영역의 실리콘 나노와이어 직경은 그대로 유지한 채 수nm 또는 수십 nm 급의 채널 직경을 가지는 단결 정 실리콘 나노와이어를 형성할 수 있다.

- [0067] 본 발명의 다른 실시예에 따른 얇은 채널 직경을 가지는 단결정 실리콘 나노와이어 제작 방법들은 잘 알려진 기존의 실리콘 공정 기술을 그대로 적용 가능하며, 선택적 산화 (Local Oxidation of Silicon, LOCOS) 공정 또는 실리콘 건식 식각 공정을 통하여 고농도 불순물이 주입된 소스/드레인 영역의 실리콘 나노와이어 직경은 그대로 유지한 채 수nm 또는 수십 nm 급의 채널 직경을 가지는 단결정 실리콘 나노와이어를 형성할 수 있다.

- [0068] 또한, 본 발명에 따른 얇은 채널 직경을 가지는 단결정 실리콘 나노와이어는, 전면 게이트 상보형 전계효과 트랜지스터(c-MOSFET), 전면 게이트 상보형 터널링 효과를 이용한 트랜지스터, 전면 게이트 상보형 이온화 충돌 전계효과 트랜지스터(cI-MOS), 전면 게이트 상보형 junction-less 트랜지스터, 전면 게이트 Capacitorless 1T-DRAM 소자, 전면 게이트 비휘발성 메모리소자 등 다양한 소자의 제조에 적용될 수 있다.

- [0069] 본 발명이 비록 일부 바람직한 실시예에 의해 설명되었지만, 본 발명의 범위는 이에 의해 제한되어서는 아니 되고. 특허청구범위에 의해 뒷받침되는 상기 실시예의 변형이나 개량에도 미쳐야 할 것이다.

## 도면

## 도면1

# 도면2

## 도면3

# 도면4

## 도면5