## (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 116155267 A (43) 申请公布日 2023. 05. 23

(21)申请号 202211673606.2

(22)申请日 2022.12.26

(71) 申请人 无锡中微亿芯有限公司 地址 214000 江苏省无锡市滨湖区建筑西 路777号A6幛1-4层

(72) 发明人 朱倩 刘彤 陈波寅 徐玉婷 徐彦峰

(74) 专利代理机构 无锡华源专利商标事务所 (普通合伙) 32228

专利代理师 过顾佳

(51) Int.CI.

H03L 7/081 (2006.01)

*H03L* 7/085 (2006.01)

*H03K 5/135* (2006.01)

权利要求书3页 说明书7页 附图4页

#### (54) 发明名称

一种延时时长可配置的延时链电路

#### (57) 摘要

本申请公开了一种延时时长可配置的延时链电路,涉及数字电路领域,该延时链电路包括粗调模块和精调模块,粗调模块受控于配置信号中的粗调配置信号并产生与粗调配置信号对应的两个环回输出,精调模块受控于配置信号中的精调配置信号并对两个环回输出进行相位插值产生延时差均等的时钟输出信号,时钟输出信号相对于时钟输入信号的延时时长与该延时链电路获取到的配置信号对应,因此只需要改变配置信号,就能改变输入到输出的延时时间从而得到所需的延时时长,避免了传统延迟锁相环电路的延时不确定性,使得延时时长可以灵活准确配置

1.一种延时时长可配置的延时链电路,其特征在于,所述延时链电路包括粗调模块和精调模块,所述粗调模块包括M级依次级联的延时单元以及若干个数据选择器,各个数据选择器相连形成环回结构,第一级延时单元的输入端获取时钟输入信号,数据选择器形成的环回结构的两个输出端连接所述精调模块;所述粗调模块根据配置端获取到的粗调配置信号控制各个数据选择器的导通状态,并产生与所述粗调配置信号对应的第一环回输出Va和所述第二环回输出Vb并输出给所述精调模块,所述第一环回输出Va和所述第二环回输出Vb之间的相位差为一个延时单元产生的延时时长;

所述精调模块根据配置端获取到的精调配置信号在获取到的所述第一环回输出Va和所述第二环回输出Vb之间进行相位插值,产生相对于所述时钟输入信号具有与配置信号对应的延时时长的时钟输出信号,所述配置信号包括提供给所述粗调模块的粗调配置信号和提供给所述精调模块的精调配置信号。

2.根据权利要求1所述的延时链电路,其特征在于,所述粗调模块包括M级依次级联的基本模组,每个基本模组包括一个延时单元和若干个数据选择器,M个基本模组中的延时单元依次相连形成级联结构,M个基本模组中的数据选择器依次相连形成环回结构,同一级基本模组中的多个数据选择器的控制端相连;

第一级基本模组中的延时单元的第一输入端获取所述时钟输入信号,第一级基本模组中的延时单元的第二输入端连接高电平,其余各级基本模组中的延时单元的第一输入端连接前一级基本模组中的延时单元的输出端、第二输入端连接前一级基本模组中的数据选择器的控制端。

3.根据权利要求2所述的延时链电路,其特征在于,每一级基本模组中包括数据选择器 MUX1和数据选择器MUX2,各级基本模组中的数据选择器形成的环回结构包括:

每一级基本模组中的MUX1的第一输入端连接同一级基本模组中的延时单元的输出端、 所述MUX1的第二输入端连接后一级基本模组中的MUX1的输出端,第一级基本模组中的MUX1 的输出端连接所述精调模块输出所述第二环回输出Vb;最后一级基本模组中的MUX1的第二 输入端连接高电平;

每一级基本模组中的MUX2的第一输入端连接同一级基本模组中的延时单元的第一输入端、所述MUX2的第二输入端连接后一级基本模组中的MUX2的输出端,第一级基本模组中的MUX2的输出端连接所述精调模块输出所述第一环回输出Va;最后一级基本模组中的MUX2的第二输入端连接高电平;

同一级基本模组中的数据选择器的控制端获取到高电平,MUX1和MUX2同时导通各自的第二输入端,或者,同一级基本模组中的数据选择器的控制端获取到低电平,MUX1和MUX2同时导通各自的第一输入端。

4.根据权利要求3所述的延时链电路,其特征在于,所述粗调模块根据配置端获取到的 粗调配置信号控制各个数据选择器的导通状态的方法包括:

利用转换单元将通过配置端获取到的二进制的粗调配置信号转换为十进制数值Q;给前Q-1级基本模组中的数据选择器的控制端提供高电平,使得前Q-1级基本模组中的MUX1和MUX2同时导通第二输入端,并给第Q级基本模组中的数据选择器的控制端提供低电平,使得第Q级基本模组中的MUX1和MUX2同时导通第一输入端。

5.根据权利要求2所述的延时链电路,其特征在于,在每个延时单元中,第一与非门的

第一输入端连接所述延时单元的第二输入端,第一与非门的第二输入端连接所述延时单元的第一输入端,所述第一与非门的输出端连接第二与非门的第二输入端,所述第二与非门的第一输入端连接所述延时单元的第二输入端,所述第二与非门的输出端连接反相器后连接所述延时单元的输出端。

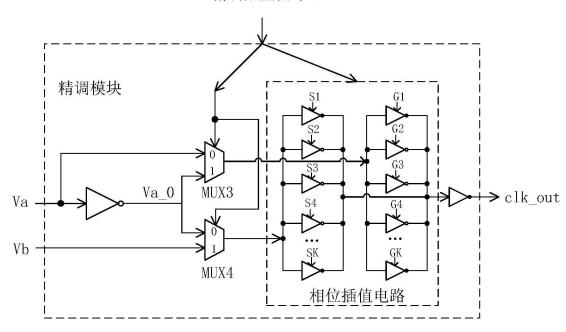

6.根据权利要求1所述的延时链电路,其特征在于,所述精调模块包括数据选择器MUX3、数据选择器MUX4和相位插值电路,MUX3的第一输入端连接所述粗调模块获取所述第一环回输出Va,所述第一环回输出Va经过反相器后产生Va\_0输出到MUX3的第二输入端和MUX4的第一输入端,MUX4的第二输入端连接所述粗调模块获取所述第二环回输出Vb;MUX3的输出端连接相位插值电路的一个输入端,MUX4的输出端连接所述相位插值电路的另一个输入端,所述相位插值电路的输出端通过反相器输出所述时钟输出信号;

其中,Va\_0与所述第一环回输出Va和所述第二环回输出Vb之间的相位差相等,MUX3和MUX4的控制端相连从而同时导通各自的第一输入端或者同时导通各自的第二输入端,所述精调模块根据配置端获取到的精调配置信号控制MUX3和MUX4的导通状态,以及控制所述相位插值电路的工作状态。

7.根据权利要求1所述的延时链电路,其特征在于,所述延时链电路还包括零延时模块和校准模块,所述时钟输入信号经过所述零延时模块提供给所述校准模块,所述精调模块产生的时钟输出信号也提供给所述校准模块,所述校准模块根据输入的信号产生校准信号,所述校准信号用于指示时钟输出信号相对于所述时钟输入信号之间的延时时长;

产生所述延时链电路的配置信号的方法包括:根据所述校准信号调节所述延时链电路的配置信号直至时钟输出信号相对于所述时钟输入信号具有目标延时时长。

- 8.根据权利要求7所述的延时链电路,其特征在于,所述校准模块包括第一触发单元、第二触发单元和鉴相器,所述零延时模块输出的时钟信号经过第一触发单元连接所述鉴相器的第一输入端,所述时钟输出信号经过所述第二触发单元连接所述鉴相器的第二输入端,所述鉴相器的输出端连接所述校准模块的输出端并用于输出所述校准信号;所述第一触发单元的输出在所述时钟输入信号的第N+1个时钟周期的上升沿处由低电平切换为高电平,所述第二触发单元的输出在所述时钟输出信号的第一个时钟周期的上升沿处由低电平切换为高电平,N为参数且起始值为1。

- 9.根据权利要求8所述的延时链电路,其特征在于,产生所述延时链电路的配置信号的方法包括:

依次调节所述配置信号,直至所述校准模块输出的校准信号从低电平切换为高电平时,得到使得所述时钟输出信号相对于所述时钟输入信号具有N个时钟周期的目标延时时长的配置信号;

其中,所述鉴相器在所述第一输入端的信号的相位晚于所述第二输入端的信号的相位 时输出低电平,所述鉴相器在所述第一输入端的信号的相位不晚于所述第二输入端的信号 的相位时输出高电平。

10.根据权利要求8所述的延时链电路,其特征在于,N=1,所述第一触发单元包括第一DQ触发器和第二DQ触发器,所述零延时模块输出的时钟信号连接所述第一DQ触发器的时钟端和所述第二DQ触发器的时钟端,所述第一DQ触发器的输入端D获取所述校准模块的使能信号,所述第一DQ触发器的输出端Q通过两个依次相连的反相器连接所述第二DQ触发器的

输入端D,所述第二DQ触发器的输出端Q连接所述鉴相器的第一输入端;所述第二DQ触发器的输出端Q输出的信号相对于所述时钟输入信号具有一个时钟周期的延时时长;

所述第二触发单元包括第三DQ触发器,所述时钟输出信号连接所述第三DQ触发器的时钟端,所述第三DQ触发器的输入端D获取所述校准模块的使能信号,所述第三DQ触发器的输出端Q连接所述鉴相器的第二输入端。

## 一种延时时长可配置的延时链电路

#### 技术领域

[0001] 本申请涉及数字电路领域,尤其是一种延时时长可配置的延时链电路。

### 背景技术

[0002] 延时链电路就是一种延迟锁相环电路,主要在数字电路中用作相位延迟补偿以及时钟调整。传统的简单延迟锁相环电路包括四级串联的延迟单元以及一个鉴相器,通过插入鉴相器来检测输入时钟和最后一级延迟单元的输出时钟之间的相位差,以此产生成比例的平均电压来负反馈调节每一级延迟单元的延时。

[0003] 对于大的环路增益,输入时钟和最后一级延迟单元的输出时钟之间的相位差很小,即这四级串联的延迟单元将输入时钟几乎准确地延时了一个时钟周期,从而建立了准确的时钟沿间隔。但是实际上,这四级串联的延迟单元产生的总延时时长并不能准确的等于一个时钟周期,导致这四级串联的延迟单元可能将输入时钟延时了一个时钟周期也可能延时了两个时钟周期,从而导致相邻时钟沿的时间间隔可能被固定在2/4个时钟周期而不是1/4个时钟周期,此时相邻时钟延的间隔也就不确定,延时具有不确定性。

#### 发明内容

[0004] 本申请人针对上述问题及技术需求,提出了一种延时时长可配置的延时链电路,本申请的技术方案如下:

[0005] 延时链电路包括粗调模块和精调模块,粗调模块包括M级依次级联的延时单元以及若干个数据选择器,各个数据选择器相连形成环回结构,第一级延时单元的输入端获取时钟输入信号,数据选择器形成的环回结构的两个输出端连接精调模块;粗调模块根据配置端获取到的粗调配置信号控制各个数据选择器的导通状态,并产生与粗调配置信号对应的第一环回输出Va和第二环回输出Vb并输出给精调模块,第一环回输出Va和第二环回输出Vb之间的相位差为一个延时单元产生的延时时长;

[0006] 精调模块根据配置端获取到的精调配置信号在获取到的第一环回输出Va和第二环回输出Vb之间进行相位插值,产生相对于时钟输入信号具有与配置信号对应的延时时长的时钟输出信号,配置信号包括提供给粗调模块的粗调配置信号和提供给精调模块的精调配置信号。

[0007] 其进一步技术方案为,粗调模块包括M级依次级联的基本模组,每个基本模组包括一个延时单元和若干个数据选择器,M个基本模组中的延时单元依次相连形成级联结构,M个基本模组中的数据选择器依次相连形成环回结构,同一级基本模组中的多个数据选择器的控制端相连;

[0008] 第一级基本模组中的延时单元的第一输入端获取时钟输入信号,第一级基本模组中的延时单元的第二输入端连接高电平,其余各级基本模组中的延时单元的第一输入端连接前一级基本模组中的延时单元的输出端、第二输入端连接前一级基本模组中的数据选择器的控制端。

[0009] 其进一步技术方案为,每一级基本模组中包括数据选择器MUX1和数据选择器MUX2,各级基本模组中的数据选择器形成的环回结构包括:

[0010] 每一级基本模组中的MUX1的第一输入端连接同一级基本模组中的延时单元的输出端、MUX1的第二输入端连接后一级基本模组中的MUX1的输出端,第一级基本模组中的MUX1的输出端连接精调模块输出第二环回输出Vb;最后一级基本模组中的MUX1的第二输入端连接高电平;

[0011] 每一级基本模组中的MUX2的第一输入端连接同一级基本模组中的延时单元的第一输入端、MUX2的第二输入端连接后一级基本模组中的MUX2的输出端,第一级基本模组中的MUX2的输出端连接精调模块输出第一环回输出Va;最后一级基本模组中的MUX2的第二输入端连接高电平;

[0012] 同一级基本模组中的数据选择器的控制端获取到高电平,MUX1和MUX2同时导通各自的第二输入端,或者,同一级基本模组中的数据选择器的控制端获取到低电平,MUX1和MUX2同时导通各自的第一输入端。

[0013] 其进一步技术方案为,粗调模块根据配置端获取到的粗调配置信号控制各个数据选择器的导通状态的方法包括:

[0014] 利用转换单元将通过配置端获取到的二进制的粗调配置信号转换为十进制数值 Q;给前Q-1级基本模组中的数据选择器的控制端提供高电平,使得前Q-1级基本模组中的 MUX1和MUX2同时导通第二输入端,并给第Q级基本模组中的数据选择器的控制端提供低电平,使得第Q级基本模组中的MUX1和MUX2同时导通第一输入端。

[0015] 其进一步技术方案为,在每个延时单元中,第一与非门的第一输入端连接延时单元的第二输入端,第一与非门的第二输入端连接延时单元的第一输入端,第一与非门的输出端连接第二与非门的第二输入端,第二与非门的输出端连接反相器后连接延时单元的输出端。

[0016] 其进一步技术方案为,精调模块包括数据选择器MUX3、数据选择器MUX4和相位插值电路,MUX3的第一输入端连接粗调模块获取第一环回输出Va,第一环回输出Va经过反相器后产生Va\_0输出到MUX3的第二输入端和MUX4的第一输入端,MUX4的第二输入端连接粗调模块获取第二环回输出Vb;MUX3的输出端连接相位插值电路的一个输入端,MUX4的输出端连接相位插值电路的另一个输入端,相位插值电路的输出端通过反相器输出时钟输出信号;

[0017] 其中,Va\_0与第一环回输出Va和第二环回输出Vb之间的相位差相等,MUX3和MUX4的控制端相连从而同时导通各自的第一输入端或者同时导通各自的第二输入端,精调模块根据配置端获取到的精调配置信号控制MUX3和MUX4的导通状态,以及控制相位插值电路的工作状态。

[0018] 其进一步技术方案为,延时链电路还包括零延时模块和校准模块,时钟输入信号经过零延时模块提供给校准模块,精调模块产生的时钟输出信号也提供给校准模块,校准模块根据输入的信号产生校准信号,校准信号用于指示时钟输出信号相对于时钟输入信号之间的延时时长;

[0019] 产生延时链电路的配置信号的方法包括:根据校准信号调节延时链电路的配置信号直至时钟输出信号相对于时钟输入信号具有目标延时时长。

[0020] 其进一步技术方案为,校准模块包括第一触发单元、第二触发单元和鉴相器,零延时模块输出的时钟信号经过第一触发单元连接鉴相器的第一输入端,时钟输出信号经过第二触发单元连接鉴相器的第二输入端,鉴相器的输出端连接校准模块的输出端并用于输出校准信号;第一触发单元的输出在时钟输入信号的第N+1个时钟周期的上升沿处由低电平切换为高电平,第二触发单元的输出在时钟输出信号的第一个时钟周期的上升沿处由低电平切换为高电平,N为参数且起始值为1。

[0021] 其进一步技术方案为,产生延时链电路的配置信号的方法包括:

[0022] 依次调节配置信号,直至校准模块输出的校准信号从低电平切换为高电平时,得到使得时钟输出信号相对于时钟输入信号具有N个时钟周期的目标延时时长的配置信号;

[0023] 其中,鉴相器在第一输入端的信号的相位晚于第二输入端的信号的相位时输出低电平,鉴相器在第一输入端的信号的相位不晚于第二输入端的信号的相位时输出高电平。

[0024] 其进一步技术方案为,N=1,第一触发单元包括第一DQ触发器和第二DQ触发器,零延时模块输出的时钟信号连接第一DQ触发器的时钟端和第二DQ触发器的时钟端,第一DQ触发器的输入端D获取校准模块的使能信号,第一DQ触发器的输出端Q通过两个依次相连的反相器连接第二DQ触发器的输入端D,第二DQ触发器的输出端Q连接鉴相器的第一输入端;第二DQ触发器的输出端Q输出的信号相对于时钟输入信号具有一个时钟周期的延时时长;

[0025] 第二触发单元包括第三DQ触发器,时钟输出信号连接第三DQ触发器的时钟端,第三DQ触发器的输入端D获取校准模块的使能信号,第三DQ触发器的输出端Q连接鉴相器的第二输入端。

[0026] 本申请的有益技术效果是:

[0027] 本申请公开了一种延时时长可配置的延时链电路,该延时链电路包括受控于配置信号中的粗调配置信号的粗调模块,以及受控于配置信号中的精调配置信号的精调模块,利用粗调模块和精调模块可以得到相对于时钟输入信号经过所需要的延时时长的时钟输出信号,也即延时时长与配置信号对应,从而避免了传统延迟锁相环电路的延时不确定性,使得延时时长可以准确配置。

[0028] 而且由于时钟输出信号相对于时钟输出信号的延时时长的延时时长与配置信号对应,因此通过改变配置信号就可以产生得到具有不同的延时时长时钟输出信号,延时时长灵活可调。

[0029] 该延时链电路还包括校准模块,利用校准模块可以准确的校准得到所需的配置信号,从而准确的输出所需的时钟输出信号。

#### 附图说明

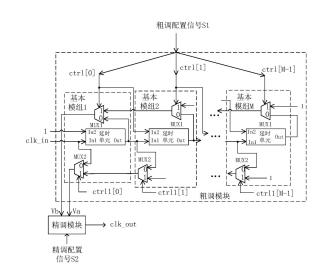

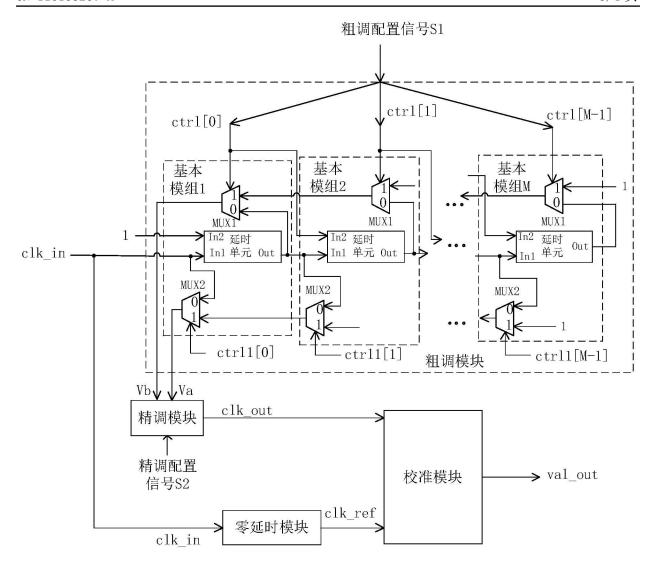

[0030] 图1是本申请一个实施例中的延时链电路的电路结构图。

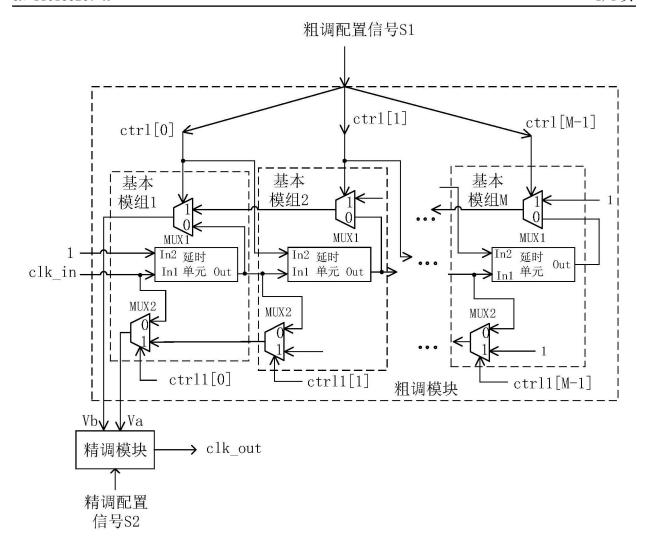

[0031] 图2是本申请一个实施例中的单个延时单元的电路结构图。

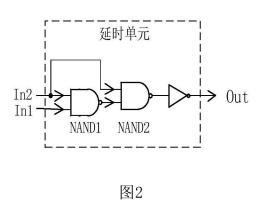

[0032] 图3是本申请一个实施例中的精调模块的电路结构图。

[0033] 图4是本申请另一个实施例中的延时链电路的电路结构图。

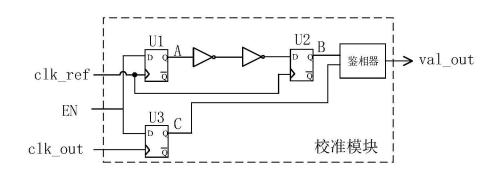

[0034] 图5是本申请一个实施例中的校准模块的电路结构图。

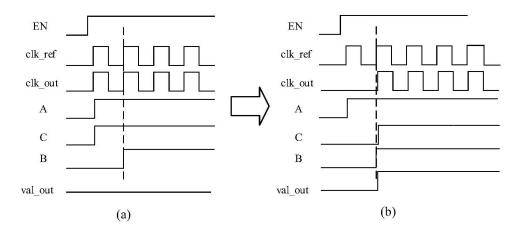

[0035] 图6是一个实例中在两种配置信号下的工作时序图,(a)是配置信号为0000000000 时的工作时序图,(b)是配置信号为011010010时的工作时序图。

### 具体实施方式

[0036] 下面结合附图对本申请的具体实施方式做进一步说明。

[0037] 本申请公开了一种延时时长可配置的延时链电路,请参考图1,该延时链电路包括粗调模块和精调模块,该粗调模块包括配置端,粗调模块通过配置端获取粗调配置信号S1。精调模块包括配置端,精调模块通过配置端获取精调配置信号S2。粗调配置信号S1和精调配置信号S2都来自于提供给延时链电路的配置信号,在一个实施例中,配置信号、粗调配置信号S1和精调配置信号S2都为二进制格式,配置信号由粗调配置信号S1和精调配置信号S2拼接而成,比如粗调配置信号S1是配置信号的高位部分,精调配置信号S2是配置信号的低位部分。

[0038] 粗调模块包括M级依次级联的延时单元以及若干个数据选择器,各个延时单元用于形成相同的延时时长。各个数据选择器相连形成环回结构,各级延时单元的输出端均连接数据选择器形成的环回结构。第一级延时单元的输入端获取时钟输入信号clk\_in。数据选择器形成的环回结构的两个输出端连接精调模块。粗调模块根据配置端获取到的粗调配置信号S1控制各个数据选择器的导通状态,并产生与粗调配置信号S1对应的第一环回输出Va和第二环回输出Vb输出给精调模块,第一环回输出Va和第二环回输出Vb之间的相位差为一个延时单元的延时时长。

[0039] 精调模块根据配置位获取到的精调配置信号S2在获取到的第一环回输出Va和第二环回输出Vb之间进行相位插值,最终产生相对于时钟输入信号clk\_in具有与获取到的完整的配置信号对应的延时时长的时钟输出信号clk\_out,从而实现延时时长的可调。

[0040] 在一个实施例中,粗调模块包括M级依次级联的基本模组,如图1所示包括基本模组1~基本模组M。每个基本模组包括一个延时单元和若干个数据选择器。M个基本模组中的延时单元依次相连形成级联结构,M个基本模组中的数据选择器依次相连形成环回结构。同一级基本模组中的多个数据选择器的控制端相连。

[0041] 第一级基本模组中的延时单元的第一输入端In1获取时钟输入信号clk\_in,第一级基本模组中的延时单元的第二输入端In2连接高电平。其余各级基本模组中的延时单元的第一输入端In1连接前一级基本模组中的延时单元的输出端Out,其余各级基本模组中的延时单元的第二输入端In2连接前一级基本模组中的数据选择器的控制端。比如图1中,基本模组1中的两个数据选择器MUX1和MUX2的控制端相连均为ctrl[0],基本模组2中的延时单元的第二输入端In2连接基本模组1中的数据选择器的控制端获ctrl[0]。同样的,基本模组2中的两个数据选择器MUX1和MUX2的控制端相连均为ctrl[1],基本模组3中的延时单元的第二输入端In2连接基本模组2中的数据选择器的控制端获ctrl[1],虽然图上未示出,但可以其次类推。

[0042] 每一级基本模组中的延时单元的结构相同,用于实现延时,请参考图2,在一个实施例中,在每个延时单元中,第一与非门NAND1的第一输入端连接延时单元的第二输入端In2,第一与非门NAND1的第二输入端连接延时单元的第一输入端In1。第一与非门NAND1的输出端连接第二与非门NAND2的第二输入端,第二与非门NAND2的第一输入端连接延时单元的第二输入端In2,第二与非门NAND2的输出端连接若干个依次级联的反相器后连接延时单元的输出端Out,图2仅示出一个反相器。当改变粗调配置信号时In2也会随之改变,当In2为0此时In1所代表的延时信息便会被阻断不会传到下一级。

[0043] 在一个实施例中,每一级基本模组中包括数据选择器MUX1和数据选择器MUX2,各级基本模组中的数据选择器形成的环回结构包括,请参考图1:每一级基本模组中的MUX1的第一输入端连接同一级基本模组中的延时单元的输出端Out,该MUX1的第二输入端连接后一级基本模组中的MUX1的输出端,第一级基本模组中的MUX1的输出端连接精调模块输出第二环回输出Vb,最后一级基本模组中的MUX1的第二输入端连接高电平。每一级基本模组中的MUX2的第一输入端连接同一级基本模组中的延时单元的第一输入端In1、第二输入端连接后一级基本模组中的MUX2的输出端,第一级基本模组中的MUX2的输出端连接精调模块输出第一环回输出Va,最后一级基本模组中的MUX2的第二输入端连接高电平。

[0044] 由于同一级基本模组中的数据选择器的控制端相连,因此同一级基本模组中的数据选择器的导通状态相同。在本申请中,当同一级基本模组中的数据选择器的控制端获取到高电平时,该级基本模组中的MUX1和MUX2同时导通各自的第二输入端,也就是本级MUX会选择后一级MUX的输出作为输入的那一端进行输出。或者,当同一级基本模组中的数据选择器的控制端获取到低电平时,该级基本模组中的MUX1和MUX2同时导通各自的第一输入端,也就是该级MUX会选择将本级延时单元的第一输入端In1和输出端Out的延时信息进行输出比如在图1中,MUX1的第一输入端为0端、第二输入端为1端,MUX2的第一输入端为0端、第二输入端为1端。则比如当基本模组1中的数据选择器的控制端ctrl[0]获取到高电平时,基本模组1中的MUX1和MUX2均导通1端。再比如当基本模组2中的数据选择器的控制端ctrl[1]获取到低电平时,基本模组1中的MUX1和MUX2均导通0端。

[0045] 在一个实施例中,粗调模块根据配置端获取到的粗调配置信号S1控制各个数据选择器的导通状态的方法包括:利用转换单元将通过配置端获取到的二进制的粗调配置信号S1转换为十进制数值Q,然后根据该十进制数值Q给各个基本模组中的MUX的控制端提供所需的高电平或低电平,以此抽出相应个数的延时单元的延时信息,当需要抽出Q个延时单元的延时信息时:给前Q-1级基本模组中的数据选择器的控制端提供高电平,使得前Q-1级基本模组中的MUX1和MUX2同时导通第二输入端,并给第Q级基本模组中的数据选择器的控制端提供低电平,使得第Q级基本模组中的MUX1和MUX2同时导通第一输入端。从而使用前Q级级联的延时单元对时钟输入信号clk\_in做延时处理后输出Va和Vb。而对于第Q+1级基本模组之后的各级基本模组,可以给这些基本模组中的数据选择器的控制端提供高电平,也可以提供低电平,对输出的Va和Vb没有影响。

[0046] 在一个实施例中,请参考图3,精调模块包括数据选择器MUX3、数据选择器MUX4和相位插值电路,MUX3的第一输入端连接粗调模块获取第一环回输出Va,第一环回输出Va经过反相器后产生Va\_0输出到MUX3的第二输入端和MUX4的第一输入端。Va\_0与第一环回输出Va和第二环回输出Vb之间的相位差相等。MUX4的第二输入端连接粗调模块获取第二环回输出Vb。MUX3的输出端连接相位插值电路的一个输入端,MUX4的输出端连接相位插值电路的另一个输入端,相位插值电路的输出端通过反相器输出时钟输出信号clk\_out。MUX3的控制端和MUX4的控制端相连,当MUX3和MUX4的控制端获取到高电平时,MUX3和MUX4同时导通各自的第二输入端(图3中的1端);当MUX3和MUX4的控制端获取到低电平时,MUX3和MUX4同时导通各与的第二输入端(图3中的1端)。

[0047] 精调模块根据配置端获取到的精调配置信号S2给MUX3和MUX4的控制端提供高电平或低电平以控制MUX3和MUX4的导通状态,以及精调模块还根据配置端获取到的精调配置

信号S2控制相位插值电路的工作状态。

[0048] 在一个实施例中,可以直接取精调配置信号S2的最高位或最低位提供给MUX3和MUX4的控制端,并按照其余各位的精调配置信号S2来控制相位插值电路。

[0049] 请参考图3,当给MUX3和MUX4的控制端提供低电平时,MUX3和MUX4均选通0端也即第一输入端,MUX3输出Va给相位插值电路、MUX4输出Va\_0给相位插值电路,相位插值电路在Va和Va\_0之间进行相位插值。当给MUX3和MUX4的控制端提供高电平时,MUX3和MUX4均选通1端也即第二输入端,MUX3输出Va\_0给相位插值电路、MUX4输出Vb给相位插值电路,相位插值电路在Va和Va\_0之间进行相位插值。

[0050] 目前常用的相位插值电路的结构如图3所示,相位插值电路包括2K条完全相同的支路,K为相位插值的长度,其决定了插值的相位的数量,每条支路上包括一个带控制端的反相器,精调模块根据精调配置信号S2给控制端S1~SK以及控制端G1~GK提供高电平或低电平,以控制MUX3的输出信号与MUX4的输出信号的权重,从而决定输出的c1k\_out更靠近MUX3的输出信号还是更靠近MUX4的输出信号。相位插值电路的具体调节方式可以参考现有的相位插值电路的工作逻辑,该实施例不赘述。

[0051] 如上所述在本申请中,可以利用配置信号控制粗调模块和精调模块,从而输出相对于时钟输入信号clk\_in具有所需的延时时长的时钟输出信号clk\_out。为了使得输出的时钟输出信号clk\_out的延时时长的准确度更高,在一个实施例中,该延时链电路还包括零延时模块和校准模块,以及利用零延时模块和校准模块实现的确定配置信号的方法。请参考图4,时钟输入信号clk\_in经过零延时模块后提供clk\_ref给校准模块,精调模块产生的时钟输出信号clk\_out也提供给校准模块,校准模块根据输入的两路信号clk\_ref和clk\_out产生校准信号val\_out,该校准信号val\_out用于指示时钟输出信号clk\_out相对于时钟输入信号clk\_in之间的延时时长。则根据校准信号val\_out调节延时链电路的配置信号直至时钟输出信号clk\_out相对于时钟输入信号clk\_in具有目标延时时长,即可产生该延时链电路的配置信号,然后将该配置信号提供给粗调模块和精调模块,即可输出所需的时钟输出信号clk out。

[0052] 其中,零延时模块的输出的时钟信号clk\_ref相对于时钟输入信号clk\_in具有固定时延,该固定时延是固定不可选的。且当配置信号各位均为0,粗调模块和精调模块中所有数据选择器均选通第一输入端时、通过精调模块产生的时钟输出信号clk\_out相对于时钟输入信号clk in也具有该固定时延。零延时模块可以采用现有常见的零延时电路实现。

[0053] 在一个实施例中,校准模块包括第一触发单元、第二触发单元和鉴相器,零延时模块输出的时钟信号clk\_ref经过第一触发单元连接鉴相器的第一输入端,精调模块产生的时钟输出信号clk\_out经过第二触发单元连接鉴相器的第二输入端,鉴相器的输出端连接校准模块的输出端并用于输出校准信号val\_out。第一触发单元的输出在时钟输入信号clk\_in的第N+1个时钟周期的上升沿处由低电平切换为高电平,第二触发单元的输出在时钟输出信号clk\_out的第一个时钟周期的上升沿处由低电平切换为高电平,N为参数且起始值为1。

[0054] 鉴相器在第一输入端的信号的相位晚于第二输入端的信号的相位时输出低电平,鉴相器在第一输入端的信号的相位不晚于第二输入端的信号的相位时输出高电平。则从0开始依次调节配置信号,直至校准模块输出的校准信号val\_out从低电平切换为高电平时,

得到使得时钟输出信号clk\_out相对于时钟输入信号clk\_in具有N个时钟周期的目标延时时长的配置信号。

[0055] 在实际应用时,比较常用的需要产生相对于时钟输入信号c1k\_in具有一个时钟周期的延时时长的时钟输出信号c1k\_out。则N=1,如图5所示,第一触发单元包括第一DQ触发器U1和第二DQ触发器U2,零延时模块输出的时钟信号c1k\_ref连接第一DQ触发器U1的时钟端和第二DQ触发器U2的时钟端,第一DQ触发器U1的输入端D获取校准模块的使能信号EN,第一DQ触发器的输出端Q通过两个依次相连的反相器连接第二DQ触发器U2的输入端D,第二DQ触发器的输出端Q连接鉴相器的第一输入端。由于DQ触发器上升沿触发,通过在第一DQ触发器U1的输出端Q后加入两个反相器会使第二DQ触发器U2的输入端D端点上升沿晚于第二DQ触发器U2的时钟输入的第一个上升沿,从而使得第二DQ触发器的输出端Q输出的信号相对于时钟输入信号具有一个时钟周期的延时时长。

[0056] 第二触发单元包括第三DQ触发器U3,精调模块输出的时钟输出信号clk\_out连接第三DQ触发器U3的时钟端,第三DQ触发器U3的输入端D获取校准模块的使能信号EN,第三DQ触发器U3的输出端Q连接鉴相器的第二输入端。

[0057] 在配置信号的各位信号均为0时,精调模块输出的时钟输出信号clk\_out与零延时模块输出的时钟信号clk\_ref的相位齐平,则第一DQ触发器U1的输出端A端与第三DQ触发器U3的输出端C端的相位也齐平,导致此时第二DQ触发器U2的输出端B端的相位晚于C端的相位,鉴相器输出的校准信号val\_out为低电平。由于校准模块的使能信号EN和零延时模块输出的时钟信号clk\_ref都是固定不变的,因此按照对应的十进制数值依次递增1步的方式调节调节配置信号来增加clk\_out相对于clk\_in的延时时长,可以调节C端的相位逐渐变晚并逼近B端的相位,直至调节到C端的相位不晚于B端的相位时,校准信号val\_out由低电平切换至高电平,此时C端的相位可能是与B端的相位齐平,也可能在精度范围内略晚于B端的相位。得到此时的配置信号,利用得到的该配置信号控制粗调模块和精调模块可以使得clk\_out相对于clk\_in正好具有一个时钟周期的延时时长。

[0058] 比较常用的,配置P位的配置信号SP-1:0,其中高M位作为粗调配置信号S1,低P-M位作为精调配置信号S2。粗调模块包括2<sup>M</sup>个基本模组并受控于粗调配置信号S1产生两个相差一个粗调延时单元的环回输出。粗调模块共可以产生2<sup>M</sup>步延时,精调模块共可以产生2<sup>P-M</sup>步延时,整个延时链电路共可以产生2<sup>P</sup>个均分的延时信息。

[0059] 比如在一个实例中,假设配置信号共包括9位信号,其中高5位作为粗调配置信号S1提供给粗调模块、低4位作为精调配置信号S2提供给精调模块,当配置信号的各个配置位均为0而使得配置信号为0000000000时的工作时序图如图6中的(a)所示。通过依次增大配置信号至210步时,也即配置信号变为011010010时的工作时序图如图6中的(b)所示。通过对比(a)和(b)可以看出,通过增大配置信号,clk\_out的相位不断延后,直至校准信号val\_out由低电平切换至高电平,由此得到所需的配置信号为011010010,及输出相对输入延时一个时钟周期时的配置信号。

[0060] 以上所述的仅是本申请的优选实施方式,本申请不限于以上实施例。可以理解,本领域技术人员在不脱离本申请的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本申请的保护范围之内。

图1

# 精调配置信号S2

图3

图4

图5

图6