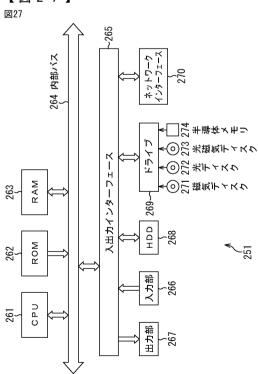

(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第4110389号 (P4110389)

(45) 発行日 平成20年7月2日(2008.7.2)

(24) 登録日 平成20年4月18日 (2008.4.18)

(51) Int. Cl.

G 1 1 B 20/14 (2006.01) HO 3 M 7/14 (2006.01) G11B 20/14 341A HO3M 7/14 B

請求項の数 15 (全 62 頁)

(21) 出願番号

特願2003-6925 (P2003-6925)

(22) 出願日 (65) 公開番号 平成15年1月15日 (2003.1.15) 特開2004-220698 (P2004-220698A)

FL

(43) 公開日

平成16年8月5日 (2004.8.5)

審査請求日 平成17年10月5日(2005.10.5)

(73)特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74)代理人 100082131

弁理士 稲本 義雄

|(72)発明者 中川 俊之

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

審査官 小林 大介

最終頁に続く

(54) 【発明の名称】変調装置および変調方法、記録媒体、並びにプログラム

### (57)【特許請求の範囲】

### 【請求項1】

(d, k; m, n; r)の可変長符号の変換規則に基づいて入力ビット列からチャネルビット列を生成し、さらに前記チャネルビット列から出力符号列を生成する変調装置において、

前記出力符号列のDSVを制御するために、前記入力ビット列に挿入されるDSV制御ビットを決定する制御ビット決定手段を備え、

前記制御ビット決定手段は、

前記入力ビット列の所定位置に、前記DSV制御ビットの第1の候補ビットを挿入して、第1のビット列候補を生成する第1のビット列候補生成手段と、

前記入力ビット列の所定位置に、前記DSV制御ビットの第2の候補ビットを挿入して、第2のビット列候補を生成する第2のビット列候補生成手段と、

前記第1のビット列候補をシフトさせながら、少なくとも<u>前記</u>変換規則に基づいて変換するために必要なビット数分保持する第1の保持手段と、

前記第2のビット列候補をシフトさせながら、少なくとも前記変換規則に基づいて変換するために必要なビット数分保持する第2の保持手段と、

前記第1の保持手段の全てのビットに前記第1のビット列候補が保持されている状態において、前記第1の保持手段により保持されている前記第1のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用いて変調することにより、第1のチャネルビット列候補を生成する第1の変調手段と、

前記第2の保持手段の全てのビットに前記第2のビット列候補が保持されている状態において、前記第2の保持手段により保持されている前記第2のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用いて変調することにより、第2のチャネルビット列候補を生成する第2の変調手段と、

前記第1のチャネルビット列候補に基づいて、第1のDSV値を演算する第1のDSV演算手段と、

前記第 2 のチャネルビット列候補に基づいて、第 2 のDSV値を演算する第 2 のDSV演算手段と、

前記第1のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第1のタイミング情報を生成する第1の情報生成手段と、

前記第2のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第2のタイミング情報を生成する第2の情報生成手段と、

前記第1のタイミング情報および前記第2のタイミング情報のうち、先に入力されたタイミング情報に基づいたタイミングで、前記第1のDSV値および前記第2のDSV値に基づいて、前記第1の候補ビットまたは前記第2の候補ビットのいずれかを前記DSV制御ビットと判定する判定手段と

を備えることを特徴とする変調装置。

# 【請求項2】

前記<u>第1の</u>情報生成手段は、前記変換規則に基づいて、拘束長が4の符号語変換に対して、1箇所または2箇所の変調切れ目を検出することにより、前記<u>第1の</u>タイミング情報を生成し、

前記第2の情報生成手段は、前記変換規則に基づいて、拘束長が4の符号語変換に対して、1箇所または2箇所の変調切れ目を検出することにより、前記第2のタイミング情報を生成する

ことを特徴とする請求項1に記載の変調装置。

### 【請求項3】

# 前記判定手段は、

前記第1の候補ビットを前記DSV制御ビットと判定した場合、前記<u>第2の保持手段</u>に保持されている情報を、前記<u>第1の保持手段</u>に保持されている情報に置き換えさせるための処理を更に実行し、

前記第2の候補ビットを前記DSV制御ビットと判定した場合、前記<u>第1の保持手段</u>に保持されている情報を、前記<u>第2の保持手段</u>に保持されている情報に置き換えさせるための処理を更に実行する

ことを特徴とする請求項1に記載の変調装置。

### 【請求項4】

前記第1のDSV値演算手段は、

前記第1のチャネルビット列候補をNRZI化する第1のNRZI化手段と、

前記第1のNRZI化手段によりNRZI化された3105 キャネルビット列候補を基に、第1の区間DSVを演算する第1の区間DSV演算手段と、

前記判定手段による前記DSV制御ビットの判定結果に基づいて、<u>第1の</u>累積DSVを演算する第1の累積DSV演算手段と、

前記第1の区間DSV演算手段により演算された前記第1の区間DSVと、前記<u>第1の</u>累積DSV演算手段により演算された前記第1の累積DSVを加算する第1の加算手段と

### を備え、

前記第2のDSV値演算手段は、

前記第2のチャネルビット列候補をNRZI化する第2のNRZI化手段と、

前記第2のNRZI化手段によりNRZI化された第2のチャネルビット列候補を基に、第2の区間DSVを演算する第2の区間DSV演算手段と、

前記判定手段による前記DSV制御ビットの判定結果に基づいて、第2の累積DSVを演算する第2の累積DSV演算手段と、

10

20

30

30

40

前記第2の区間DSV演算手段により演算された前記第2の区間DSVと、前記第2の累積DSV演算手段により演算された前記第2の累積DSVを加算する第2の加算手段と

### を備え、

前記判定手段は、前記第1の加算手段の加算結果である前記第1のDSV値および前記第2の加算手段の加算結果である前記第2のDSV値に基づいて、前記第1の候補ビットまたは前記第2の候補ビットのいずれかを前記DSV制御ビットと判定する

ことを特徴とする請求項1に記載の変調装置。

### 【請求項5】

前記第1のDSV値演算手段は、

<u>前記第1のチャネルビット列候補</u>に、予め設定されたユニークなパターンを含む同期 パターンを挿入する第1の同期信号挿入手段を

更に備え、

前記第2のDSV値演算手段は、

前記第2のチャネルビット列候補に、前記同期パターンを挿入する、第2の同期信号 挿入手段を

更に備え、

前記第1のNRZI化手段は、前記第1の同期信号挿入手段により前記同期信号が挿入された前記第1のチャネルビット列候補をNRZI化し、

前記第2のNRZI化手段は、前記第2の同期信号挿入手段により前記同期信号が挿入された前記第2のチャネルビット列候補をNRZI化する

ことを特徴とする請求項4に記載の変調装置。

#### 【請求項6】

前記第1の同期信号挿入手段、前記第2の同期信号挿入手段、前記第1のNRZI化手段、前記第2のNRZI化手段、前記<u>第1</u>の区間DSV演算手段、および、前記<u>第2</u>の区間DSV演算手段は、その内部に、第3の保持手段をそれぞれ備え、

前記判定手段は、

前記第1の候補ビットを前記DSV制御ビットと判定した場合、前記第2の同期信号挿入手段に含まれている前記<u>第3の</u>保持手段に保持されている情報を、前記第1の同期信号挿入手段に含まれている前記<u>第3の</u>保持手段に保持されている情報に置き換えさせ、前記第2のNRZI化手段に含まれている前記<u>第3の</u>保持手段に保持されている情報を、前記第1のNRZI化手段に含まれている前記<u>第3の</u>保持手段に保持されている情報に置き換えさせ、前記第2の区間DSV演算手段に含まれている前記<u>第3の</u>保持手段に保持されている情報を、前記第1の区間DSV演算手段に含まれている前記<u>第3の</u>保持手段に保持されている情報をに置き換えさせるための処理を更に実行し、

前記第2の候補ビットを前記DSV制御ビットと判定した場合、前記第1の同期信号挿入手段に含まれている前記<u>第3の</u>保持手段に保持されている情報を、前記第2の同期信号挿入手段に含まれている前記<u>第3の</u>保持手段に保持されている情報に置き換えさせ、前記第1のNRZI化手段に含まれている前記<u>第3の</u>保持手段に保持されている情報を、前記第2のNRZI化手段に含まれている前記<u>第3の</u>保持手段に保持されている情報に置き換えさせ、前記第1の区間DSV演算手段に含まれている前記<u>第3の</u>保持手段に保持されている情報を、前記第2の区間DSV演算手段に含まれている前記<u>第3の</u>保持手段に保持されている情報を、前記第2の区間DSV演算手段に含まれている前記<u>第3の</u>保持手段に保持されている情報に置き換えさせるための処理を更に実行する

ことを特徴とする請求項5に記載の変調装置。

# 【請求項7】

前記制御ビット決定手段により決定された前記DSV制御ビットを、前記入力ビット列の 所定位置に挿入するDSV制御ビット挿入手段と、

前記DSV制御ビット挿入手段により、前記DSV制御ビットが挿入された前記入力ビット列を、所定のビット数だけ保持する第3の保持手段と、

前記変換規則に基づき、前記<u>第3の</u>保持手段により保持されている、前記DSV制御ビットが挿入された前記ビット列を前記チャネルビット列に変調する第3の変調手段と

10

20

30

40

#### を更に備え、

前記<u>第3の</u>変調手段は、前記<u>第3の</u>保持手段により保持されている前記ビット列のうち、時間的に入力された前記入力ビットから後に入力された入力ビットの方向に順番に、前記チャネルビット列に変調する

ことを特徴とする請求項1に記載の変調装置。

### 【請求項8】

前記<u>第1乃至第3の</u>変調手段は、<u>基本データ長</u>であるmビットのデータの入力を受ける時間に、<u>基本チャネルビット長</u>であるnビットの前記チャネルビット列を出力することを特徴とする請求項7に記載の変調装置。

### 【請求項9】

前記第3の変調手段により変調された前記チャネルビット列をNRZI化することにより、前記出力符号列を生成するNRZI化手段

を更に備えることを特徴とする請求項7に記載の変調装置。

### 【請求項10】

前記変換規則では、前記入力ビット列または前記挿入後ビット列の1ブロック内の「1」の個数を2で割った余りが、前記チャネルビット列の対応する1ブロック内の「1」の個数を2で割った余りと一致する

ことを特徴とする請求項1に記載の変調装置。

### 【請求項11】

前記変換規則では、前記チャネルビット列における最小ランdの連続が所定の回数以下に制限される

ことを特徴とする請求項1に記載の変調装置。

#### 【請求項12】

前記変換規則では、最小ラン d = 1、最大ラン k = 7、変換前の基本データ長 m = 2、 および変換後の基本チャネルビット長 n = 3 である

ことを特徴とする、請求項1に記載の変調装置。

### 【請求項13】

第1および第2の保持手段を用いて、(d,k;m,n;r)の可変長符号の変換規則 に基づいて入力ビット列からチャネルビット列を生成し、更に前記チャネルビット列から 出力符号列を生成する変調装置の変調方法において、

前記入力ビット列の所定位置に、前記DSV制御ビットの第1の候補ビットを挿入して、 第1のビット列候補を生成する第1のビット列候補生成ステップと、

前記入力ビット列の所定位置に、前記DSV制御ビットの第2の候補ビットを挿入して、 第2のビット列候補を生成する第2のビット列候補生成ステップと、

前記第1のビット列候補をシフトさせながら、少なくとも前記変換規則に基づいて変換するために必要なビット数分前記第1の保持手段に保持するように制御する第1の保持制御ステップと、

前記第2のビット列候補をシフトさせながら、少なくとも前記変換規則に基づいて変換するために必要なビット数分前記第1の保持手段に保持するように制御する第2の保持制御ステップと、

前記第1の保持手段の全てのビットに前記第1のビット列候補が保持されている状態において、前記第1の保持手段により保持されている前記第1のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用いて変調することにより、第1のチャネルビット列候補を生成する第1の変調ステップと

前記第2の保持手段の全てのビットに前記第2のビット列候補が保持されている状態において、前記第2の保持手段により保持されている前記第2のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用いて変調することにより、第2のチャネルビット列候補を生成する第2の変調ステップと

10

20

30

40

50

`

<u>前記第1のチャネルビット列候補に基づいて、第1のDSV値を演算する第1のDSV演算ス</u>テップと、

<u>前記第2のチャネルビット列候補に基づいて、第2のDSV値を演算する第2のDSV演算ス</u>テップと、

前記第1のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第1のタイミング情報を生成する第1の情報生成ステップと、

前記第2のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第2のタイミング情報を生成する第2の情報生成ステップと、

前記第1のタイミング情報および前記第2のタイミング情報のうち、先に入力されたタイミング情報に基づいたタイミングで、前記第1のDSV値および前記第2のDSV値に基づいて、前記第1の候補ビットまたは前記第2の候補ビットのいずれかを前記DSV制御ビットと判定する判定ステップと

を含むことを特徴とする変調方法。

### 【請求項14】

第1および第2の保持手段を用いて、(d , k ; m , n ; r )の可変長符号の変換規則 に基づいて入力ビット列からチャネルビット列を生成し、更に前記チャネルビット列から 出力符号列を生成する処理をコンピュータに実行させるプログラムであって、

前記入力ビット列の所定位置に、前記DSV制御ビットの第1の候補ビットを挿入して、 第1のビット列候補を生成する第1のビット列候補生成ステップと、

前記入力ビット列の所定位置に、前記DSV制御ビットの第2の候補ビットを挿入して、 第2のビット列候補を生成する第2のビット列候補生成ステップと、

前記第1のビット列候補をシフトさせながら、少なくとも前記変換規則に基づいて変換するために必要なビット数分前記第1の保持手段に保持するように制御する第1の保持制御ステップと、

前記第2のビット列候補をシフトさせながら、少なくとも前記変換規則に基づいて変換するために必要なビット数分前記第1の保持手段に保持するように制御する第2の保持制御ステップと、

前記第1の保持手段の全てのビットに前記第1のビット列候補が保持されている状態において、前記第1の保持手段により保持されている前記第1のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用いて変調することにより、第1のチャネルビット列候補を生成する第1の変調ステップと

前記第2の保持手段の全てのビットに前記第2のビット列候補が保持されている状態において、前記第2の保持手段により保持されている前記第2のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用いて変調することにより、第2のチャネルビット列候補を生成する第2の変調ステップと

前記第1のチャネルビット列候補に基づいて、第1のDSV値を演算する第1のDSV演算ステップと、

<u>前記第2のチャネルビット列候補に基づいて、第2のDSV値を演算する第2のDSV演算ス</u>テップと、

前記第1のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第1のタイミング情報を生成する第1の情報生成ステップと、

前記第2のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第2のタイミング情報を生成する第2の情報生成ステップと、

前記第1のタイミング情報および前記第2のタイミング情報のうち、先に入力されたタイミング情報に基づいたタイミングで、前記第1のDSV値および前記第2のDSV値に基づいて、前記第1の候補ビットまたは前記第2の候補ビットのいずれかを前記DSV制御ビットと判定する判定ステップと

を含むことを特徴とするコンピュータが読み取り可能なプログラムが記録されている記

10

20

30

40

録媒体。

【請求項15】

第1および第2の保持手段を用いて、(d, k; m, n; r)の可変長符号の変換規則 <u>に基づいて</u>入力ビット列からチャネルビット列を生成し、更に前記チャネルビット列から 出力符号列を生成する処理をコンピュータに実行させるプログラムであって、

(6)

前記入力ビット列の所定位置に、前記DSV制御ビットの第1の候補ビットを挿入して、 第1のビット列候補を生成する第1のビット列候補生成ステップと、

前記入力ビット列の所定位置に、前記DSV制御ビットの第2の候補ビットを挿入して、 第2のビット列候補を生成する第2のビット列候補生成ステップと、

前記第1のビット列候補をシフトさせながら、少なくとも前記変換規則に基づいて変換するために必要なビット数分前記第1の保持手段に保持するように制御する第1の保持制御ステップと、

前記第2のビット列候補をシフトさせながら、少なくとも前記変換規則に基づいて変換するために必要なビット数分前記第1の保持手段に保持するように制御する第2の保持制御ステップと、

前記第1の保持手段の全てのビットに前記第1のビット列候補が保持されている状態に おいて、前記第1の保持手段により保持されている前記第1のビット列候補を、時間的に 最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用 いて変調することにより、第1のチャネルビット列候補を生成する第1の変調ステップと

<u>`</u>

前記第2の保持手段の全てのビットに前記第2のビット列候補が保持されている状態において、前記第2の保持手段により保持されている前記第2のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、前記変換規則を用いて変調することにより、第2のチャネルビット列候補を生成する第2の変調ステップと

,

前記第1のチャネルビット列候補に基づいて、第1のDSV値を演算する第1のDSV演算ステップと、

前記第2のチャネルビット列候補に基づいて、第2のDSV値を演算する第2のDSV演算ステップと、

前記第1のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第1のタイミング情報を生成する第1の情報生成ステップと、

前記第2のチャネルビット列候補に基づいて、前記DSV制御ビットを決定するために必要な第2のタイミング情報を生成する第2の情報生成ステップと、

前記第1のタイミング情報および前記第2のタイミング情報のうち、先に入力されたタイミング情報に基づいたタイミングで、前記第1のDSV値および前記第2のDSV値に基づいて、前記第1の候補ビットまたは前記第2の候補ビットのいずれかを前記DSV制御ビットと判定する判定ステップと

を含むことを特徴とするプログラム。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は変調装置および変調方法、記録媒体、並びにプログラムに関し、特に、データ伝送や記録媒体への記録に用いて好適な変調装置および変調方法、記録媒体、並びにプログラムに関する。

[0002]

【従来の技術】

データを所定の伝送路に伝送したり、または例えば磁気ディスク、光ディスク、光磁気ディスク等の記録媒体に記録したりする際、伝送路や記録媒体に適するように、データの変調が行われる。

[0003]

10

20

30

40

20

30

40

50

このような変調方法の1つとして、ブロック符号が知られている。このブロック符号は、データ列を $m \times i$  ビットからなる単位(以下データ語という)にブロック化し、このデータ語を適当な符号則に従って、 $n \times i$  ビットからなる符号語に変換するものである。そしてこの符号は、i = 1 のときには固定長符号となり、またi が複数個選べるとき、すなわち、1乃至i max(最大のi)の範囲の所定のi を選択して変換したときには可変長符号となる。このブロック符号化された符号は可変長符号(d, k; m, n; r) と表される

# [0004]

ここで、iは拘束長と称され、imaxはr(最大拘束長)となる。またdは、連続する"1"の間に入る、"0"の最小連続個数、例えば"0"の最小ランを示し、kは連続する"1"の間に入る、"0"の最大連続個数、例えば"0"の最大ランを示している。

[0005]

ところで、上述のようにして得られる可変長符号を、光ディスクや光磁気ディスク等に記録する場合、例えば、コンパクトディスクやミニディスクでは、可変長符号において、 " 1 "を反転とし、 " 0 "を無反転として、NRZI(Non Return to Zero Inverted)変調し、NRZI変調された可変長符号(以下、記録波形列とも称する)に基づいて、記録が行なわれている。この他に、記録密度のあまり大きくなかった初期のISO(International Stand ards Organization / 国際標準化機構)規格のMO(Magnet-Optical Disk / 光磁気ディスク)では、記録変調されたビット列をNRZI変調せずに、そのまま記録した。

[0006]

記録波形列の最小反転間隔をTminとし、最大反転間隔をTmaxとするとき、線速方向に高密度に記録を行うためには、最小反転間隔Tminは長い方が、すなわち、最小ランdは大きい方が良く、またクロックの再生の面からは、最大反転間隔Tmaxは短い方が、すなわち最大ランkは小さい方が望ましく、この条件を満足するために、種々の変調方法が提案されている。

[0007]

具体的には、例えば光ディスク、磁気ディスク、または、光磁気ディスク等において、提案もしくは実際に使用されている変調方式として、可変長符号であるRLL(1-7)((1,7;m,n;r)とも表記される)、さらに、ISO規格のMOに用いられている固定長RLL(1-7)((1,7;m,n;1)とも表記される)などがある。

[00008]

現在開発研究されている、記録密度の高い光ディスクや光磁気ディスク等のディスク装置では、例えば、可変長RLL (1 - 7)符号などの、最小ラン d=1 のRLL符号 (Run Length Limited Code) がよく用いられている。

[0009]

可変長RLL(1-7)のパラメータは(1, 7; 2, 3; 2)であり、記録波形列のビット間隔をTとすると、(d+1)Tで表される最小反転間隔 T minは 2 (=1+1) Tとなる。データ列のビット間隔をTdataとすると、この(m/n)× 2 で表される最小反転間隔 T minは 1 . 3 3 (= (2 / 3 )× 2 ) T dataとなる。また(k+1) T で表される最大反転間隔 T max は 8 (=7+1) T ((= (m/n) × 8 T data = 1 (2 / 3 )× 8 T data = 5 . 3 3 T data) である。さらに検出窓幅 T wは (m/n) × T dataで表され、その値は 0 . 6 7 (= 2 / 3 ) T dataとなる。

[0010]

RLL(1-7)による変調を行ったチャネルビット列におけるTの発生頻度を調べると、Tminである2Tが一番多く、以下3T、4T、5Tと続く。エッジ情報が早い周期で多く発生する2Tや3Tなどは、クロック再生に有利となる場合が多い。

[0011]

しかしながら、線速方向の記録密度をさらに高くしていくと、今度は逆に、Tminが問題となってくる。すなわち最小ランである2Tが、連続して発生し続けた時は、記録波形に

歪みが生じやすくなってくる。なぜならは、2 Tの波形出力は、他の波形出力よりも小さいので、例えばノイズ、デフォーカス、もしくはタンジェンシャル・チルト等による影響を受け易くなるからである。

#### [0012]

このように、高線密度記録の際には、Tmin(2T)の連続した記録は、ノイズ等の外乱の影響を受けやすくなり、したがって、データ再生時において、誤りが発生し易くなる。この場合における、データ再生誤りのパターンとしては、例えば、連続するTmin(2T)の先頭から最後までのエッジが一斉にシフトして誤るケースがある。すなわち、発生するビットエラー長が長くなってしまう。

#### [0013]

ところで、記録媒体へのデータの記録、もしくは、データの伝送の際には、記録媒体もしくは伝送路に適した符号化変調が行われるが、これら変調符号に直流成分および低域成分が含まれていると、例えば、ディスク装置のサーボの制御におけるトラッキングエラーなどの、各種のエラー検出信号に変動が生じ易くなったり、もしくは、ジッターが発生し易くなったりする。従って、変調符号には、直流成分および低域成分をなるべく含めないようにする方が良い。

### [0014]

このような課題に対して、一般的に、DSV ( Digital Sum Value ) 制御を行うことが提案されている。DSVとは、チャネルビット列をNRZI化し(すなわちレベル符号化し)、そのビット列(データのシンボル)の "1"を「+1」、"0"を「-1」として、符号を加算した際の、最大最小のぶれの大きさを示す。また、符号を加算する各時点の値を、RDS(Running Digital Sum)と呼ぶ。DSVを小さくすること、即ち、RDSの絶対値を0に近づけることを、DSV制御という。DSVは、符号列の直流成分および低域成分の目安として用いることが出来る。これより、DSV制御を行うことは、符号列の直流成分および低域成分を抑圧することに相当する。

### [0015]

上記、可変長RLL(1-7)による変調符号は、DSV制御が行われていない。変換効率が良いために、例えば、DVD(Digital Versatile Disk)の8-16符号のように、変調時にDSV制御を行うことができない。このような場合のDSV制御は、例えば、変調後の符号化列(チャネルビット列)において、所定の間隔に区切ってDSV計算を行い、DSV制御ビットを符号化列(チャネルビット列)内の所定の位置に挿入することによって、実現する。

# [0016]

しかしながら、DSV制御ビットは、基本的には冗長ビットである。従って、符号変換の効率から考えれば、DSV制御ビットはなるべく少ない方が良い。

### [0017]

またさらに、挿入されるDSV制御ビットによって、最小ランdおよび最大ランkは、変化しない方が良い。(d,k)が変化すると、記録再生特性に影響を及ぼしてしまうからである。

### [0018]

ただし、実際のRLL符号は、最小ランは必ず守る必要があるが、最大ランについてはその限りではない。場合によっては最大ランを破るパターンを同期信号に用いるフォーマットも存在する。例えば、DVD (Digital Versatile Disk)の8 - 16符号における最大ランは11Tだが、同期信号パターン部分において、最大ランを超える14Tを与え、同期信号の検出能力を上げている。

#### [0019]

従って、高密度化に対応して変換効率の優れたRLL(1-7)方式を用いるためには、高 線密度化に対して、より適するように最小ランの連続を制御すること、および、DSV制御 をなるべく効率良く行うことは、重要である。

### [0020]

以上に対して、データ列に第1のDSV制御ビットを挿入した第1のデータ列と、第2のDSV

10

20

30

40

制御ビットを挿入した第2のデータ列を生成するDSV制御ビット挿入手段と、最小ランdが1とされ、かつ、データ列の要素内の"1"の個数と、変換される符号語列の要素内の"1"の個数を、2で割った時の余りが、どちらも1もしくは0で一致するような変換テーブルを用いて、第1のデータ列と第2のデータ列の両方を変調する変調手段と、変換テーブルを用いて変調された第1のデータ列の第1の区間DSVと第2のデータ列の第2の区間DSVを計算し、それらをそれまでの累積DSVと加算した値から、変換テーブルを用いて変調された第1のデータ列と第2のデータ列の一方を選択して出力するDSV計算手段とを備えることを特徴とする変調装置が開示されている(例えば、特許文献1参照)。

[0021]

【特許文献1】

特開平11-177431号公報

[0022]

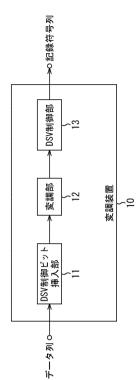

図1は、従来の変調装置の構成例を示すブロック図である。

[0023]

図 1 に示すように、変調装置 1 0 は、入力されたデータ列に対して、所定の間隔でDSV制御ビットとして、" 1 "または" 0 "を挿入するDSV制御ビット挿入部 1 1 を備える。

[0024]

このDSV制御ビット挿入部11では、DSV制御ビット"1"を挿入するデータ列と、DSV制御ビット"0"を挿入するデータ列とが用意される。また、DSV制御ビット挿入部11は、DSV区間の位置を調整し、1つのDSV区間のチャネルビット列は、1つのDSV制御ビットを含む入力ビット列より変換されたものであるようにする。

【 0 0 2 5 】

変調部12は、DSV制御ビット挿入部11でDSV制御ビットの挿入されたデータ列を変調する。DSV制御部13は、変調部12で変調された符号語列をNRZI化してレベルデータとした後にDSV計算を行い、最終的にDSV制御の行われた記録符号列を出力する。

[0026]

また、変換コードとして、 d = 1、 k = 7、 m = 2、 n = 3の基礎コードと、データ列の要素内の「1」の個数を2で割ったときの余りと、変換される符号語列内の「1」の個数を2で割った余りが、どちらも1もしくは0で一致するような変換規則と、最小ランdの連続を所定の回数以下に制限する第1の置き換えコードと、ラン長制限を守るための第2の置き換えコードを有することを特徴とした変換テーブルが開示されている(例えば、特許文献2参照)。

[0027]

【特許文献2】

特開平11-346154号公報

[0028]

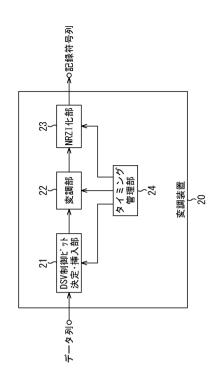

図2は、従来の変調装置の他の構成例を示すブロック図である。

[0029]

図2に示すように、変調装置20は、DSV制御ビットである「1」または「0」を決定し、入力されたデータ列に、任意の間隔で挿入するDSV制御ビット決定・挿入部21、DSV制御ビットが挿入されたデータ列を変調する変調部22、および、変調部22の出力を記録波形列に変換するNRZI化部23を備える。また、変調装置20は、タイミング信号を生成し、各部に供給してタイミングを管理するタイミング管理部24を備える。

[0030]

【発明が解決しようとする課題】

しかしながら、上述したような方法によるDSV制御を実現する場合、具体的な制御信号などについて工夫する必要があるという課題があった。

[0031]

例えば、上述したような方法においては、区間外に存在する次のDSV制御ビットを含んだ 変換により生成されたチャネルビット列により、算出された区間DSVに誤差が生じてしま 10

20

30

40

わないように、DSV区間をずらす処理が行われているが、このような処理を実現するためには、各部の動作を制御する制御信号について工夫する必要がある。

#### [0032]

また、例えば、上述したような方法において、区間DSVの算出に使用したレジスタには、前回の算出に利用した値が全て格納されたままであり、その中の不必要な値により、次に算出された区間DSVに誤差が生じてしまう場合があるので、このような処理を実現するためには、各部の動作を制御する制御信号および各部の動作について工夫する必要がある。

### [0033]

本発明はこのような状況に鑑みてなされたものであり、DSV制御を良く行うことによって、直流成分および低域成分を抑圧し、安定したシステムを構成することが出来るようにするものである。

### [0034]

#### 【課題を解決するための手段】

本発明の変調装置は、出力符号列のDSVを制御するために、入力ビット列に挿入されるD SV制御ビットを決定する制御ビット決定手段を備え、制御ビット決定手段は、入力ビット 列の所定位置に、DSV制御ビットの第1の候補ビットを挿入して、第1のビット列候補を 生成する第1のビット列候補生成手段と、入力ビット列の所定位置に、DSV制御ビットの 第2の候補ビットを挿入して、第2のビット列候補を生成する第2のビット列候補生成手 段と、第1のビット列候補をシフトさせながら、少なくとも変換規則に基づいて変換する ために必要なビット数分保持する第1の保持手段と、第2のビット列候補をシフトさせな がら、少なくとも変換規則に基づいて変換するために必要なビット数分保持する第2の保 持手段と、第1の保持手段の全てのビットに第1のビット列候補が保持されている状態に おいて、第1の保持手段により保持されている第1のビット列候補を、時間的に最も先に 入力されたデータから後に入力された方向に順番に参照して、変換規則を用いて変調する ことにより、第1のチャネルビット列候補を生成する第1の変調手段と、第2の保持手段 の全てのビットに第2のビット列候補が保持されている状態において、第2の保持手段に より保持されている第2のビット列候補を、時間的に最も先に入力されたデータから後に 入力された方向に順番に参照して、変換規則を用いて変調することにより、第2のチャネ ルビット列候補を生成する第2の変調手段と、第1のチャネルビット列候補に基づいて、 第1のDSV値を演算する第1のDSV演算手段と、第2のチャネルビット列候補に基づいて、 第2のDSV値を演算する第2のDSV演算手段と、第1のチャネルビット列候補に基づいて、 DSV制御ビットを決定するために必要な第1のタイミング情報を生成する第1の情報生成 手段と、第2のチャネルビット列候補に基づいて、DSV制御ビットを決定するために必要 な第2のタイミング情報を生成する第2の情報生成手段と、第1のタイミング情報および 第2のタイミング情報のうち、先に入力されたタイミング情報に基づいたタイミングで、 第1のDSV値および第2のDSV値に基づいて、第1の候補ビットまたは第2の候補ビットの いずれかをDSV制御ビットと判定する判定手段とを備えることを特徴とする。

# [0036]

第1の情報生成手段には、変換規則に基づいて、拘束長が4の符号語変換に対して、1箇所または2箇所の変調切れ目を検出することにより、第1のタイミング情報を生成させ、第2の情報生成手段には、変換規則に基づいて、拘束長が4の符号語変換に対して、1箇所または2箇所の変調切れ目を検出することにより、第2のタイミング情報を生成させるようにすることができる。

# [0041]

判定手段には、第1の候補ビットをDSV制御ビットと判定した場合、 $\frac{第2の保持手段}$ に保持されている情報を、 $\frac{第1の保持手段}$ に保持されている情報に置き換えさせるための処理を更に実行させるようにすることができ、第2の候補ビットをDSV制御ビットと判定した場合、 $\frac{第1の保持手段}$ に保持されている情報を、 $\frac{第2の保持手段}$ に保持されている情報に置き換えさせるための処理を更に実行させるようにすることができる。

# [0044]

10

20

30

20

30

40

50

第1のDSV値演算手段には、第1のチャネルビット列候補をNRZI化する第1のNRZI化手段と、第1のNRZI化手段によりNRZI化された第1のチャネルビット列候補を基に、第1の区間DSVを演算する第1の区間DSV演算手段と、判定手段によるDSV制御ビットの判定結果に基づいて、第1の累積DSVを演算する第1の区間DSVと、第1の累積DSV演算手段により演算された第1の区間DSVと、第1の累積DSV演算手段により演算された第1の区間DSVと、第1の累積DSV演算手段により演算された第1の別累積DSVを加算する第1の加算手段とを備えさせるようにすることができ、第2のDSV値演算手段によりNRZI化された第2のチャネルビット列候補をNRZI化する第2のNRZI化手段と、第2のNRZI化手段によりNRZI化された第2のチャネルビット列候補を基に、第2の区間DSVを演算する第2の区間DSVを演算する第2の区間DSVを演算する第2の区間DSVを演算する第2の区間DSVを演算する第2の区間DSVと、第2の累積DSV演算手段により演算された第2の国間DSVと、第2の累積DSV演算手段により演算された第2の国間DSVと、第2の国間DSVと、第2の国間DSVを加算する第2の回りの加算手段とを備えさせるようにすることができ、判定手段には、第1の加算手段の加算結果である第1のDSV値に基づいて、第1の候補ビットまたは第2の解補ビットのいずれかをDSV制御ビットと判定させるようにすることができる。

第1のDSV値演算手段には、第1のチャネルビット列候補に、予め設定されたユニークなパターンを含む同期パターンを挿入する第1の同期信号挿入手段を更に備えさせるようにすることができ、第2のDSV値演算手段には、第2のチャネルビット列候補に、同期パターンを挿入する、第2の同期信号挿入手段を更に備えさせるようにすることができ、第1のNRZI化手段には、第1の同期信号挿入手段により同期信号が挿入された第1のチャネルビット列候補をNRZI化させ、第2の所ZI化手段には、第2の同期信号挿入手段により同期信号が挿入された第2のチャネルビット列候補をNRZI化させるようにすることができる

[0045]

第1の同期信号挿入手段、第2の同期信号挿入手段、第1のNRZI化手段、第2のNRZI化 手段、第1の区間DSV演算手段、および、第2の区間DSV演算手段は、その内部に、第3の 保持手段をそれぞれ備えさせるようにすることができ、判定手段には、第1の候補ビット をDSV制御ビットと判定した場合、第2の同期信号挿入手段に含まれている第3の保持手 段に保持されている情報を、第1の同期信号挿入手段に含まれている第3の保持手段に保 持されている情報に置き換えさせ、第2のNRZI化手段に含まれている第3の保持手段に保 持されている情報を、第1のNRZI化手段に含まれている第3の保持手段に保持されている 情報に置き換えさせ、第2の区間DSV 演算手段に含まれている第3の保持手段に保持され ている情報を、第1の区間DSV演算手段に含まれている第3の保持手段に保持されている 情報に置き換えさせるための処理を更に実行させるようにすることができ、第2の候補ビ ットをDSV制御ビットと判定した場合、第1の同期信号挿入手段に含まれている第3の保 持手段に保持されている情報を、第2の同期信号挿入手段に含まれている第3の保持手段 に保持されている情報に置き換えさせ、第1のNRZI化手段に含まれている第3の保持手段 に保持されている情報を、第2のNRZI化手段に含まれている第3の保持手段に保持されて いる情報に置き換えさせ、第1の区間DSV演算手段に含まれている第3の保持手段に保持 されている情報を、第2の区間DSV演算手段に含まれている第3の保持手段に保持されて いる情報に置き換えさせるための処理を更に実行させるようにすることができる。

[0046]

制御ビット決定手段により決定されたDSV制御ビットを、入力ビット列の所定位置に挿入するDSV制御ビット挿入手段と、DSV制御ビット挿入手段により、DSV制御ビットが挿入された入力ビット列を、所定のビット数だけ保持する第3の保持手段と、変換規則に基づき、第3の保持手段により保持されている、DSV制御ビットが挿入されたビット列をチャネルビット列に変調する第3の変調手段とを更に備えさせるようにすることができ、第3の変調手段には、第3の保持手段により保持されているビット列のうち、時間的に入力された入力ビットから後に入力された入力ビットの方向に順番に、チャネルビット列に変調させるようにすることができる。

20

30

40

50

#### [0047]

第1乃至第3の変調手段は、<u>基本データ長</u>であるmビットのデータの入力を受ける時間に、<u>基本チャネルビット長</u>であるnビットのチャネルビット列を出力させるようにすることができる。

# [0048]

第3の変調手段により変調されたチャネルビット列をNRZI化することにより、出力符号列を生成するNRZI化手段を更に備えさせるようにすることができる。

### [0049]

変換規則においては、入力ビット列または挿入後ビット列の1ブロック内の「1」の個数を2で割った余りが、チャネルビット列の対応する1ブロック内の「1」の個数を2で割った余りと一致するものとすることができる。

#### [0050]

変換規則では、チャネルビット列における最小ランdの連続が所定の回数以下に制限されるものとすることができる。

#### [0051]

変換規則では、最小ラン d = 1、最大ラン k = 7、変換前の基本データ長m = 2、および変換後の基本チャネルビット長 n = 3であるものとすることができる。

#### [0052]

本発明の変調方法は、入力ビット列の所定位置に、DSV制御ビットの第1の候補ビット を挿入して、第1のビット列候補を生成する第1のビット列候補生成ステップと、入力ビ ット列の所定位置に、DSV制御ビットの第2の候補ビットを挿入して、第2のビット列候 補を生成する第2のビット列候補生成ステップと、第1のビット列候補をシフトさせなが ら、少なくとも変換規則に基づいて変換するために必要なビット数分第1の保持手段に保 持するように制御する第1の保持制御ステップと、第2のビット列候補をシフトさせなが ら、少なくとも変換規則に基づいて変換するために必要なビット数分第1の保持手段に保 持するように制御する第2の保持制御ステップと、第1の保持手段の全てのビットに第1 のビット列候補が保持されている状態において、第1の保持手段により保持されている第 1のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順番 に参照して、変換規則を用いて変調することにより、第1のチャネルビット列候補を生成 する第1の変調ステップと、第2の保持手段の全てのビットに第2のビット列候補が保持 されている状態において、第2の保持手段により保持されている第2のビット列候補を、 時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、変換規則 を用いて変調することにより、第2のチャネルビット列候補を生成する第2の変調ステッ プと、第1のチャネルビット列候補に基づいて、第1のDSV値を演算する第1のDSV演算ス テップと、第2のチャネルビット列候補に基づいて、第2のDSV値を演算する第2のDSV演 算ステップと、第1のチャネルビット列候補に基づいて、DSV制御ビットを決定するため に必要な第1のタイミング情報を生成する第1の情報生成ステップと、第2のチャネルビ ット列候補に基づいて、DSV制御ビットを決定するために必要な第2のタイミング情報を 生成する第2の情報生成ステップと、第1のタイミング情報および第2のタイミング情報 のうち、先に入力されたタイミング情報に基づいたタイミングで、第1のDSV値および第 2のDSV値に基づいて、第1の候補ビットまたは第2の候補ビットのいずれかをDSV制御ビ ットと判定する判定ステップとを含むことを特徴とする。

# [0053]

本発明の記録媒体に記録されているプログラムは、入力ビット列の所定位置に、DSV制御ビットの第1の候補ビットを挿入して、第1のビット列候補を生成する第1のビット列候補生成ステップと、入力ビット列の所定位置に、DSV制御ビットの第2の候補ビットを挿入して、第2のビット列候補を生成する第2のビット列候補生成ステップと、第1のビット列候補をシフトさせながら、少なくとも変換規則に基づいて変換するために必要なビット数分第1の保持手段に保持するように制御する第1の保持制御ステップと、第2のビット列候補をシフトさせながら、少なくとも変換規則に基づいて変換するために必要なビット列候補をシフトさせながら、少なくとも変換規則に基づいて変換するために必要なビ

20

30

40

50

ット数分第1の保持手段に保持するように制御する第2の保持制御ステップと、第1の保 持手段の全てのビットに第1のビット列候補が保持されている状態において、第1の保持 手段により保持されている第1のビット列候補を、時間的に最も先に入力されたデータか ら後に入力された方向に順番に参照して、変換規則を用いて変調することにより、第1の チャネルビット列候補を生成する第1の変調ステップと、第2の保持手段の全てのビット に第2のビット列候補が保持されている状態において、第2の保持手段により保持されて いる第2のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向 に順番に参照して、変換規則を用いて変調することにより、第2のチャネルビット列候補 を生成する第2の変調ステップと、第1のチャネルビット列候補に基づいて、第1のDSV 値を演算する第1のDSV演算ステップと、第2のチャネルビット列候補に基づいて、第2 のDSV値を演算する第2のDSV演算ステップと、第1のチャネルビット列候補に基づいて、 DSV制御ビットを決定するために必要な第1のタイミング情報を生成する第1の情報生成 ステップと、第2のチャネルビット列候補に基づいて、DSV制御ビットを決定するために 必要な第2のタイミング情報を生成する第2の情報生成ステップと、第1のタイミング情 <u>報および第2のタイミング情報の</u>うち、先に入力されたタイミング情報に基づいたタイミ ングで、第1のDSV値および第2のDSV値に基づいて、第1の候補ビットまたは第2の候補 ビットのいずれかをDSV制御ビットと判定する判定ステップとを含むことを特徴とする。 [0054]

本発明のプログラムは、入力ビット列の所定位置に、DSV制御ビットの第1の候補ビッ トを挿入して、第1のビット列候補を生成する第1のビット列候補生成ステップと、入力 ビット列の所定位置に、DSV制御ビットの第2の候補ビットを挿入して、第2のビット列 候補を生成する第2のビット列候補生成ステップと、第1のビット列候補をシフトさせな がら、少なくとも変換規則に基づいて変換するために必要なビット数分第1の保持手段に 保持するように制御する第1の保持制御ステップと、第2のビット列候補をシフトさせな がら、少なくとも変換規則に基づいて変換するために必要なビット数分第1の保持手段に 保持するように制御する第2の保持制御ステップと、第1の保持手段の全てのビットに第 1のビット列候補が保持されている状態において、第1の保持手段により保持されている 第1のビット列候補を、時間的に最も先に入力されたデータから後に入力された方向に順 番に参照して、変換規則を用いて変調することにより、第1のチャネルビット列候補を生 成する第1の変調ステップと、第2の保持手段の全てのビットに第2のビット列候補が保 持されている状態において、第2の保持手段により保持されている第2のビット列候補を 、時間的に最も先に入力されたデータから後に入力された方向に順番に参照して、変換規 則を用いて変調することにより、第2のチャネルビット列候補を生成する第2の変調ステ ップと、第1のチャネルビット列候補に基づいて、第1のDSV値を演算する第1のDSV演算 ステップと、第2のチャネルビット列候補に基づいて、第2のDSV値を演算する第2のDSV 演算ステップと、第1のチャネルビット列候補に基づいて、DSV制御ビットを決定するた めに必要な第1のタイミング情報を生成する第1の情報生成ステップと、第2のチャネル ビット列候補に基づいて、DSV制御ビットを決定するために必要な第2のタイミング情報 を生成する第2の情報生成ステップと、第1のタイミング情報および第2のタイミング情 報のうち、先に入力されたタイミング情報に基づいたタイミングで、第1のDSV値および 第2のDSV値に基づいて、第1の候補ビットまたは第2の候補ビットのいずれかをDSV制御 ビットと判定する判定ステップとを含むことを特徴とする。

### [0055]

本発明の変調装置および変調方法、並びにプログラムにおいては、入力ビット列の所定位置に、DSV制御ビットの第1の候補ビットが挿入され、第1のビット列候補が生成され、入力ビット列の所定位置に、DSV制御ビットの第2の候補ビットが挿入され、第2のビット列候補が生成され、第1のビット列候補がシフトされながら、少なくとも変換規則に基づいて変換するために必要なビット数分第1の保持手段に保持されるように制御され、第2のビット列候補がシフトされながら、少なくとも変換規則に基づいて変換するために必要なビット数分第1の保持手段に保持されるように制御され、第1の保持手段の全ての

ビットに第1のビット列候補が保持されている状態において、第1の保持手段により保持されている第1のビット列候補が、時間的に最も先に入力されたデータから後に入力された方向に順番に参照され、変換規則を用いて変調されることにより、第1のチャネルビット列候補が生成され、第2の保持手段の全てのビットに第2のビット列候補が保持されている状態において、第2の保持手段により保持されている第2のビット列候補が、時間的に最も先に入力されたデータから後に入力された方向に順番に参照され、変換規則を用いて変調されることにより、第2のチャネルビット列候補が生成され、第1のチャネルビット列候補に基づいて、第1のDSV値が演算され、第2のチャネルビット列候補に基づいて、第2のDSV値が演算され、第1のチャネルビット列候補に基づいて、DSV制御ビットを決定するために必要な第1のタイミング情報が生成され、第2のチャネルビット列候補に基づいて、DSV制御ビットを決定するために必要な第2のタイミング情報が生成され、第1のタイミング情報が生成され、第1のタイミング情報および第2のタイミング情報のうち、先に入力されたタイミング情報に基づいたタイミングで、第1のDSV値および第2のDSV値に基づいて、第1の候補ビットまたは第2の候補ビットのいずれかがDSV制御ビットと判定される。

[0056]

【発明の実施の形態】

以下、図を参照して、本発明の実施の形態について説明する。

[0057]

以下においては、説明の便宜上、変換される前のデータの「0」と「1」の並び(変換前のデータ列)を、(000011)のように、( )で区切って表し、変換された後の符号の「0」と「1」の並び(符号語列)を、"000100100"のように、""で区切って表すことにする。以下に示す表1は、本発明のデータを符号に変換する変換テーブルの例を表している。

[0058]

【表1】

10

# 1,77PP\_table

```

(d, k; m, n; r) = (1, 7; 2, 3; 4)

データ

符号

*0* (Before 0:*=1. Before 1:*=0)

11

10

001

01

010

0011

010 100

0010

010 000

10

0001

000 100

000011

000 100 100

000001

010 100 100

00001000

000 100 100 100

000 100 000 010

00001001

000 100 000 001

00001010

00001011

000 100 000 101

00000000

010 100 100 100

20

00000001

010 100 000 010

00000010

010 100 000 001

00000011

010 100 000 101

#110111-01

:101 010 101 -> 001 000 000

001

00000:000 010 101 (cbit replace)

0000t:

```

-----

Termination table

00

000

0000

010

100

000010

000

100

000

000000

010

100

000

-----

# [0059]

### [0060]

また、表1は、基礎コードの要素に不確定符号(\*を含む符号)を含んでいる。不確定符号は、直前および直後の符号語列の如何によらず、最小ランdと最大ランkを守るように、"0"か"1"に決定される。すなわち表1において、変換する2ビットのデータ列が

50

30

20

30

40

50

(11)であったとき、その直前の符号語列によって、"000"または"101"が選択され、そのいずれかに変換される。すなわち、直前の符号語列の1チャネルビットが"1"である場合、最小ランdを守るために、2ビットのデータ(11)は、符号語"000"に変換され、直前の符号語列の1チャネルビットが"0"である場合、最大ランkが守られるように、符号語"101"に変換される。

### [0061]

また、表1の変換テーブルは、最小ランの連続を制限する置き換えコードを含んでいる。データ列が(110111)であり、さらに直後のデータ列が(01)、(001)、もしくは(0000)である場合、または、データ列(110111)の直後のデータ列が(0000)と続き、ここで終端される場合、データ列(110111)は、符号語"00100000"に置き換えられる。なお、直後のデータ列が上述したようなデータ列でない場合、このデータ列(110111)は、2ビット単位((11),(01),(11))で符号化され、符号語列"101010101"または"000010101

### [0062]

さらに、表1の変換コードは、データ列の要素内の「1」の個数を2で割った時の余りと、変換される符号語列の要素内の「1」の個数を2で割った時の余りが、どちらも1または0で同一(対応するいずれの要素も、「1」の個数が奇数または偶数)となるような変換規則を持っている。例えば、変換コードのうちのデータ列の要素(000001)は、"010100100%の符号語列の要素に対応しているが、それぞれの要素の「1」の個数は、データ列では1個、対応する符号語列では3個であり、どちらも2で割ったときの余りが1(奇数)で一致している。同様にして、変換コードのうちのデータ列の要素(0000000)は、"010100100100%の符号語列の要素に対応しているが、それぞれ「1」の個数は、データ列では0個、対応する符号語列では4個であり、どちらも2で割ったときの余りが0(偶数)で一致している。

### [0063]

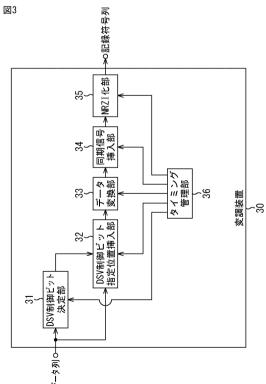

次に、図3を参照して、他システムへの応用を容易に行うことができるような、変調のレジスタ構成を有し、より好適なDSV制御を実現するように、変調切れ目を検出して、区間DSVを算出する区間を制御する変調装置について説明する。この変調装置においては、データ列が、表1に従って、可変長符号(d,k;m,n;r)=(1,7;2,3;4)に変換される。

# [0064]

図3に示すように、変調装置30は、入力されたデータ列に基づいて、データ列に挿入するDSV制御ビットとして、「1」または「0」を決定するDSV制御ビット決定部31、値が決定されたDSV制御ビットを、入力されたデータ列にタイミングを合わせて挿入するDSV制御ビット指定位置挿入部32、決定されたDSV制御ビットが挿入されたデータ列を所定の変換テーブルを用いてチャネルビットに変換するデータ変換部33、データ変換部33より供給されたチャネルビット列の所定の位置に所定の同期信号を挿入する同期信号挿入部34、および、同期信号挿入部34の出力を記録波形列または伝送符号列に変換するNRZI化部35を備える。また、変調装置30は、タイミング信号を生成し、DSV制御ビット決定部31、DSV制御ビット指定位置挿入部32、データ変換部33、同期信号挿入部34、およびNRZI化部35に供給してタイミングを管理するタイミング管理部36を備える。

### [0065]

なお、図3において、DSV制御ビット指定位置挿入部32は、タイミング管理部36に処理のタイミングを管理されているものとして説明したが、これに限らず、例えば、DSV制御ビット指定位置挿入部32が、入力ビット列の伝送タイミングを調整する機能をさらに有し、DSV制御ビット決定部31より供給されるDSV制御ビットを、伝送タイミングを調整された入力ビット列の所定位置に挿入するようにしてもよい。

### [0066]

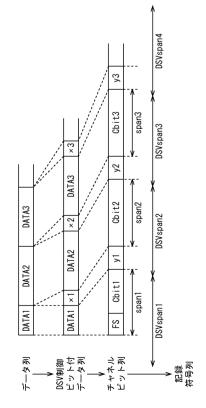

図4は、図3の変調装置30の処理を説明する図である。データ列には、ユーザデータの

20

30

40

他に、例えば、ECC (Error Correcting Code)等の情報データが含まれている。DSV制御ビット決定部 3 1 の決定に基づき、DSV制御ビット指定位置挿入部 3 2 において、DSV制御ビットである  $\times$  1 、  $\times$  2 、および  $\times$  3 が、データ列内に任意の間隔で挿入される。

#### [0067]

また、DATA 1 には、フレーム間で同期をとるためのフレーム同期信号(以下、FS (Frame Sync)と称する)が挿入される。このため、DATA 1 においては、DSV制御ビットを挿入する間隔であるDSV区間は、短く設定される。

### [0068]

すなわち、FSに加えて、DATA 1 に対応するチャネルビットからなるCbit 1 を含むDSV区間の長さであるspan 1、DATA 2 に対応するチャネルビットからなるCbit 2 を含むDSV区間の長さであるspan 2、およびDATA 3 に対応するチャネルビットからなるCbit 3 を含むDSV区間の長さであるspan 3 が、全て同じ長さ(span 1 = span 2 = span 3 )となるように、DATA 1 の長さが決定される。

### [0069]

従って、挿入されたFSがFS(bit)であり、DATA 2 およびDATA 3 がともにx(bit)である場合、変換テーブルの変換率がm: n=2:3であるので、DATA 1 は、x-FS \* 2 / 3(bit)となる。

# [0070]

なお、挿入するDSV制御ビットの値を正確に制御するために、区間DSVspan 1、DSVspan 2、およびDSVspan 3 は、後述するように、実際にDSV制御ビットが挿入されている位置よりも前方に区切られる。この際、各区間内には、1つのDSV制御ビットのみが挿入されている。

### [0071]

以上のように、チャネルビット列(NRZI化後の記録符号列もしくは伝送符号列などの出力符号列)には、FSが挿入された後において、等しい間隔でDSV制御ビットが挿入されており、DSV制御が行われている。

### [0072]

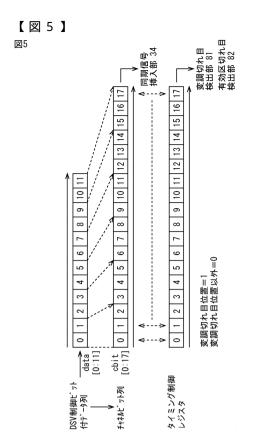

図 5 は、入力されたデータ列からチャネルビット列への変換における、レジスタ構成を示す模式図である。

# [0073]

図 5 は、データ列を、表 1 の変換テーブルに基づいてチャネルビット列へ変換する際に、最低限必要なレジスタの構成例であり、レジスタとしては、変換前のDSV制御ビットを挿入されたデータ列を格納するために、data [0:11]の12ビット、そして、データ変換後のチャネルビット列を格納するために、cbit [0:17]の18ビットが構成されている。変調装置30においては、拘束長i=1の判定はデータ列[0:1]において行われる。

# [0074]

また、その他にタイミング用レジスタ等も構成されている。なお、後述する変調切れ目位置を示すレジスタ等の、タイミング制御を行うためのレジスタも、チャネルビット列を格納するレジスタと同数のデータを格納できるように構成されており、互いに同じ位置が対応されている。また、これらタイミング制御のためのレジスタには、例えばアクティブ時において「1」が格納され、それ以外の位置には「0」が格納される。

# [0075]

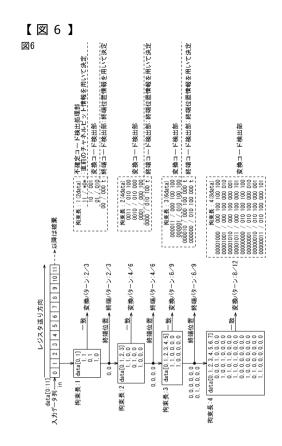

図 6 は、図 5 を用いて説明したレジスタを有するデータ変換部 3 3 において、データからチャネルビット変換を行う場合の具体例である。

# [0076]

図 6 において、DSV制御ビット付きデータ列が、data [ 0:11] の 12 ビットに、data [ 0:11] から順に入力され、レジスタ数字の大きいほうヘクロックごとにシフトされていく。そして、data [ 11] までシフトされたデータは、次のシフト時に捨てられる。

# [0077]

data [ 0 , 1 ] に 2 データ入力された時点で、チャネルビット変換を行うために、まずdata [ 0 , 1 ] が参照される。このとき、data [ 0 , 1 ] = [ 1 , 1 ] である場合、(1 1 ) から、" 1 0 1"または" 0 0 0"に変換が行われる。

# [ 0 0 7 8 ]

また、data [0,1]が、[0,1]または [1,0]である場合、(10)から"001"に、(01)から"010"に変換が行われる。そして、data [0,1] = [0,0]である場合、そこが終端位置であれば、(00)から、"000"に変換が行われ、そうでなければ、(00)は、拘束長i=1においてパターン変換されず、レジスタには、さらに2 データが入力される。

### [0079]

新たに 2 データ(合計 4 データ)が入力されると、data [0,1,2,3] が参照される。このとき、data [0,1,2,3] が、 [1,1,0,0]、 [0,1,0,0]、 または、 [1,0,0,0] である場合、拘束長 i=2 の変換コードが用いられて、(0011)から"010100"に、(0011)から"010100"に、それぞれ変換が行われる。

#### [0800]

そして、data [0,1,2,3] = [0,0,0,0] である場合、そこが終端位置であれば、(0000)から、"010100"に変換が行われ、そうでなければ、(0000)は、拘束長 i=2 においてパターン変換されず、さらに 2 データが入力される。

# [0081]

新たに 2 データ(合計 6 データ)が入力されると、data [0,1,2,3,4,5] が参照される。このとき、data [0,1,2,3,4,5] が、 [1,1,0,0,0,0] 、または、 [1,0,0,0,0] である場合、拘束長 i=3 の変換コードが用いられて、(0 0 0 0 1 1 )から" 0 0 0 1 0 0 1 0 0"に、(0 0 0 0 0 1 )から" 0 1 0 1 0 0 1 0 0"に、それぞれ変換が行われる。

### [0082]

そして、data [0,1,2,3,4,5]が、[0,0,0,0,0,0,0]、または、[0,1,0,0,0,0]である場合、そこが終端位置であれば、(00000)から"010100000"に、(000010)から、"00010000"に変換が行われ、そうでなければ、(000000)または(000010)は、拘束長i=3においてパターン変換されず、さらに2データが入力される。

# [0083]

# [0084]

#### [0085]

以上のように、入力されたDSV制御ビット付データ列は、チャネルビット列に変換される

10

20

30

40

。そして、パターンが確定した後、再度、拘束長 i = 1 の変換コードから参照されて、次のパターン変換が実行され、上述したような動作が繰り返される。

### [0086]

図 5 に示すように、チャネルビット列が 1 8 ビットのレジスタにより供給されるまでに、データ変換は終了しており、この、データ変換が終了したチャネルビット列が、同期信号 挿入部 3 4 へ供給される。

### [0087]

図 7 は、データ変換部 3 3 において、データ列から最小ラン連続制限コードを検出する場合の具体例である。

#### [0088]

図 7 に示されるように、DSV制御ビット付データ列が、図 6 を用いて説明した場合と同様に、データ変換部 3 3 内部のデータレジスタのdata [0:11]に、data [0]から順に入力され、レジスタ数字の大きいほうヘクロックごとにシフトされていく。そして、data [11]までシフトされたデータは、次のシフト時に捨てられる。

#### [0089]

また、最小ラン連続制限コード検出のためにdata [0:11]を参照する前に、図6を用いて説明したように、データ列のチャネルビット列へのパターン変換が行われるので、変換されたチャネルビット列は、図5を用いて説明した、変換後のチャネルビット列cbit [0:17]のレジスタに格納される。

# [0090]

拘束長i=1において、data[0,1]=[1,0]であり、直前の6データがdata[2,3,4,5,6,7]=[1,1,1,0,1,1]であって、さらに所定の条件に一致する場合、すなわち、(01)を検出し、その直前の6データにおいて(110111)を検出し、さらに所定の条件に一致する場合において、最小ラン連続制限コードを検出したと判定される。

### [0091]

また、拘束長i = 2において、data [ 0 , 1 , 2 , 3 ] = [ 0 , 1 , 0 , 0 ]、またはda ta [ 0 , 1 , 2 , 3 ] = [ 1 , 1 , 0 , 0 ]であり、直前の 6 データがdata [ 4 , 5 , 6 , 7 , 8 , 9 ] = [ 1 , 1 , 1 , 0 , 1 , 1 ]であって、さらに所定の条件に一致する場合、すなわち、(0 0 1 0 )または(0 0 1 1 )を検出し、その直前の 6 データにおいて(1 1 0 1 1 1 )を検出し、さらに、所定の条件に一致する場合においても、最小ラン連続制限コードを検出したと判定される。

#### [0092]

さらに、拘束長i = 2において、data [ 0 , 1 , 2 , 3 ] = [ 0 , 0 , 0 , 0 , 0 ] で終端位置を示しており、直前の 6 データがdata [ 4 , 5 , 6 , 7 , 8 , 9 ] = [ 1 , 1 , 1 , 0 , 1 , 1 ] であって、さらに所定の条件に一致する場合、すなわち、( 0 0 0 0 ) で終端する終端位置を検出し、その直前の 6 データにおいて( 1 1 0 1 1 1 ) を検出し、さらに、所定の条件に一致する場合においても、最小ラン連続制限コードを検出したと判定される。

### [0093]

さらに、拘束長i=3において、data[0,1,2,3,4,5]=[0,0,0,0,0,0,0,0] またはdata[0,1,2,3,4,5]=[1,0,0,0,0,0,0] であり、直前の6 データがdata[6,7,8,9,10,11]=[1,1,1,1,0,1,1] であって、さらに、所定の条件に一致する場合、すなわち、(000000)または(00001)を検出し、その直前の6 データにおいて(110111)を検出し、さらに、所定の条件に一致する場合においても、最小ラン連続制限コードを検出したと判定される

### [0094]

そして最小ラン連続制限コードが検出されたとき、既に置かれていたチャネルビット列が 、所定のチャネルビット列に置き換えられる。 10

20

30

40

20

30

40

### [0095]

例えば、data [2,3,4,5,6,7] = [1,1,1,0,1,1] の場合、すなわち、拘束長 i = 1 において最小ラン連続制限コードが検出された場合、置き換えられるチャネルビット列は、cbit [3,4,5,6,7,8,9,10,11] である。

### [0096]

また、data [4,5,6,7,8,9] = [1,1,1,1,0,1,1] の場合、すなわち、拘束長i = 2 において最小ラン連続制限コードが検出された場合、置き換えられるチャネルビット列は、cbit [6,7,8,9,10,11,12,13,14] である。

### [0097]

同様に、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] = [ 1 , 1 , 1 , 0 , 1 , 1 ] の場合、すなわち、拘束長i = 3 において最小ラン連続制限コードが検出された場合、置き換えられるチャネルビット列は、cbit [ 9 , 1 0 , 1 1 , 1 2 , 1 3 , 1 4 , 1 5 , 1 6 , 1 7 ] である。

### [0098]

以上のようにして、チャネルビット列からチャネルビット列への置き換え変換が行われる。また、図 5 に示すように、チャネルビット列は、置換処理が完了したのち、1 8 ビットのレジスタにより供給され、このようにして置換されたチャネルビット列が同期信号挿入部3 4 へ供給される。

#### [0099]

図 6 に示されるように、パターン変換は全て同じチャネルクロックのタイミングにおいて行われず、データが入力されるまで決定しないで待つ場合がある。例えば、 "10"の決定と"00001"の決定は、4データ分の入力にかかる時間だけの差がある。

### [0100]

このような変換形式においては、データレジスタ内に次のDSV制御ビットが入った場合、 ただちにパターン変換処理が開始される。

### [0101]

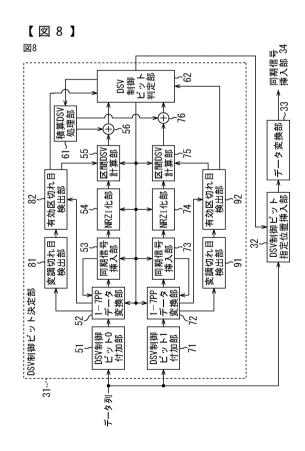

図8は、変調装置30のDSV制御ビット決定部31の詳細な構成例を示すブロック図である。図8において、データ列は、DSV制御ビット決定部31およびDSV制御ビット指定位置挿入部32に供給される。

# [0102]

DSV制御ビット決定部 3 1 において、 2 列のデータ変換およびDSV計算が行われており、値が「 0 」のDSV制御ビットを挿入されたデータ列を処理する列と、値が「 1 」のDSV制御ビットを挿入されたデータ列を処理する列とが、それぞれ独立に動作する。すなわち、DSV制御ビット決定部 3 1 に供給されたデータ列は、入力されたデータ列に所定の間隔で、値が「 0 」のDSV制御ビットを付加するDSV制御ビット 0 付加部 5 1、および、入力されたデータ列に所定の間隔で、値が「 1 」のDSV制御ビットを付加するDSV制御ビット 1 付加部 7 1 に供給される。

### [0103]

DSV制御ビット 0 付加部 5 1 により、値が「 0 」のDSV制御ビットが付加されたデータ列は、1 - 7 PPデータ変換部 5 2 に供給される。1 - 7 PPデータ変換部 5 2 は、供給されたデータを保持するレジスタ、タイミング制御を行うためのレジスタ、および、チャネルビット列を格納するレジスタを内部に有し、(d,k;m,n;r)=(1,7;2,3;4)のパラメータを持つ表 1 の変換テーブルを用いて、DSV制御ビットが付加されたデータ列をチャネルビット列に変換し、同期信号挿入部 5 3 に供給する。

#### [0104]

同期信号挿入部53は、タイミング制御を行うためのレジスタや、チャネルビット列を格納するレジスタを内部に有し、1-7PPデータ変換部52から供給されたチャネルビット列の所定の位置に、変換テーブルの変換コードとして存在しないユニークなパターンを含む同期信号を挿入し、NRZI化部54に供給する。

### [0105]

なお、同期信号挿入部53において、チャネルビット列に同期信号を挿入するために、1-7PPデータ変換部52は、表1のtermination tableを必要に応じて用いるなどによって、データ列の任意の位置において、変換を終端させる。そして、同期信号挿入部53は、チャネルビット列の終端位置に続いて、同期信号を挿入する。

### [0106]

また、チャネルビット列に同期信号を挿入した同期信号挿入部53は、挿入した同期信号の最終ビットの情報を1-7PPデータ変換部52に供給する。1-7PPデータ変換部52 は、必要に応じて、供給された同期信号の最終ビットの情報を参照し、表1の変換テーブルを用いて、データ列を変換する。

### [0107]

NRZI化部54は、タイミング制御を行うためのレジスタや、チャネルビット列を格納するレジスタを内部に有し、同期信号挿入部53より供給された、同期信号を挿入されたチャネルビット列をNRZI化し、区間DSV計算部55に供給する。

#### [0108]

区間DSV計算部55は、NRZI化されたチャネルビット列より、所定のDSV区間におけるDSV計算を行う。DSVは、NRZI化されたチャネルビットの値が「1」の場合「+1」、チャネルビットの値が「0」の場合「-1」として演算される。演算結果としては、例えば、所定のDSV区間における最大最小ピークや、所定のDSV区間における最終ビットのRDSなどが与えられる。この結果が、加算器56に供給される。

### [0109]

積算DSV処理部 6 1 は、これまでに算出されてきた区間DSVを全て加減算した積算DSVを、予め保持している。積算DSVは、例えば、現在実行している所定のDSV区間における直前のRDSである。そして、積算DSV処理部 6 1 は、所定のタイミングで、保持している積算DSVを加算器 5 6 に供給する。

#### [0110]

加算器 5 6 は、区間DSV計算部 5 5 により供給された区間DSVに、積算DSV処理部 6 1 により供給された積算DSVを加算して、新しい積算DSVを算出し、DSV制御ビット判定部 6 2 に供給する。新しい積算DSVは、例えば、現在実行している所定のDSV区間における直前のRDSと、所定のDSV区間における最終ビットのRDSとの加算結果である。

### [0111]

また、1-7PPデータ変換部52は、DSV制御ビットが挿入されたデータ列に対して、表 1の変換テーブルによる変調の切れ目に関する情報からなる変調切れ目情報を、変調切れ 目検出部81に供給する。さらに1-7PPデータ変換部52は、DSV制御ビットが挿入さ れたデータ列に対して、DSV区間の切れ目位置に関する情報を含むDSV区間切れ目信号を、 有効区切れ目検出部82に供給する。

#### [0112]

変調切れ目検出部81は、供給された変調切れ目情報に基づいて、変調切れ目位置を検出する。変調切れ目位置を検出した変調切れ目検出部81は、変調切れ目位置に関する情報を含む変調切れ目信号を有効区切れ目検出部82に供給する。

#### [0113]

有効区切れ目検出部82は、1-7PPデータ変換部52より供給されたDSV区間の切れ目位置を示すDSV区間切れ目信号に基づいて、変調切れ目検出部81より供給された変調の切れ目信号が示す変調切れ目位置の中から、対応するDSV区間のDSV制御ビットの判定を行うタイミングを制御する有効区切れ目位置を検出し、有効区切れ目位置を示す有効区切れ目信号を区間DSV計算部55およびDSV制御ビット判定部62に供給する。

# [0114]

以上のように、入力されたデータ列に値が「0」のDSV制御ビットを挿入する側のシステムが構成される。また、入力されたデータ列に値が「1」のDSV制御ビットを挿入する側のシステムも、同様に構成される。すなわち、DSV制御ビット0付加部51にはDSV制御ビット1付加部71が対応し、1-7PPデータ変換部52には1-7PPデータ変換部72が

10

20

30

40

20

30

40

50

対応し、同期信号挿入部53には同期信号挿入部73が対応し、NRZI化部54にはNRZI化部74が対応し、区間DSV計算部55には区間DSV計算部75が対応し、加算器56には加算器76が対応し、変調切れ目検出部81には変調切れ目検出部91が対応し、有効区切れ目検出部82には有効区切れ目検出部92が対応し、それぞれ、基本的に同様の処理が行われる。

### [0115]

DSV制御ビット判定部62は、加算器56より、値が「0」のDSV制御ビットが挿入されたデータ列に基づいた積算DSVの供給を受け、加算器76より、値が「1」のDSV制御ビットが挿入されたデータ列に基づいた積算DSVの供給を受ける。そして、DSV制御ビット判定部62は、これら2つの積算DSVに基づいて、データ列に挿入するDSV制御ビットの値を判定する。すなわち、DSV制御ビット判定部62は、両者の積算DSVのうち、例えば、絶対値の小さいほうのDSV制御ビットを選択する。

#### [0116]

なお、DSV制御ビット判定部62によりデータ列に挿入するDSV制御ビットの値として判定された側の積算DSVは、積算DSV処理部61に供給される。積算DSV処理部61は、供給された新しい積算DSVに基づいて、保持している積算DSVを更新する。

#### [0117]

DSV制御ビット判定部62は、データ列に挿入するDSV制御ビットの値を判定すると、その判定結果をDSV制御ビット指定位置挿入部32に供給する。DSV制御ビット指定位置挿入部32は、DSV制御ビット判定部62より供給された判定結果に基づいて、DSV制御ビットをデータ列の所定の位置に挿入し、データ変換部33に供給する。

#### [0118]

また、DSV制御ビット判定部62は、データ列に挿入するDSV制御ビットの値として判定された側を特定する情報を、1-7PPデータ変換部52、同期信号挿入部53、NRZI化部54、区間DSV計算部55、1-7PPデータ変換部72、同期信号挿入部73、NRZI化部74、および、区間DSV計算部75に供給し、各部が参照するレジスタの内容を必要に応じて更新させる。

#### [0119]

すなわち、データ列に挿入するDSV制御ビットの値として判定された側の各部が参照したレジスタの値を、判定されなかった反対側の各部が参照したレジスタの値のそれぞれに対応させて、格納する。結局、値が「0」のDSV制御ビットを付加する側が参照する各レジスタの内容と、値が「1」のDSV制御ビットを付加する側が参照する各レジスタの内容とを、選択されたDSV制御ビット側が参照する各レジスタの値を用いて、一致させる。

### [ 0 1 2 0 ]

データ列に挿入するDSV制御ビットの値を決定するDSV制御ビット決定部31は、以上のように構成される。

# [0121]

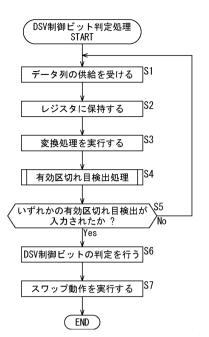

次に、DSV制御ビット決定部31の動作について説明する。

### [0122]

最初に、入力されたデータ列は、DSV制御ビット決定部 3 1 のDSV制御ビット 0 付加部 5 1 およびDSV制御ビット 1 付加部 7 1 に供給される。入力されたデータ列は、同様にして、D SV制御ビット指定位置挿入部 3 2 に供給される。

### [0123]

データ列を供給されたDSV制御ビット 0 付加部 5 1 は、値が「 0 」のDSV制御ビットを、所定の間隔でデータ列に付加する。 1 - 7 PPデータ変換部 5 2 は、DSV制御ビット 0 付加部 5 1 において値が「 0 」のDSV制御ビットを付加されたデータ列を取得して、図 5 を用いて説明したように、レジスタに順次保持し、表 1 の変換テーブルに基づいて、取得したデータ列を符号語からなるチャネルビット列に変換する。

### [0124]

また、1-7PPデータ変換部52は、必要に応じて、同期信号挿入部53より供給された

同期信号の最終ビットに関する情報を参照し、取得したデータ列をチャネルビット列に変換する。変換されたチャネルビット列は、同期信号挿入部53に供給される。また、1-7Pデータ変換部52は、データ変調の際に、変調切れ目位置にフラグを立てた変調切れ目位置情報を、変調切れ目位置検出部81に供給し、さらに、DSV区間切れ目信号を、有効区切れ目検出部82に供給する。

### [0125]

変換されたチャネルビット列を供給された同期信号挿入部53は、チャネルビット列の所定の位置に所定のパターンの同期信号を挿入し、NRZI化部54に供給する。また、同期信号挿入部53は、1-7PPデータ変換部52がデータ変調の際に、直前のチャネルビット列の最終ビットの値を参照できるように、挿入した同期信号の最終ビットの値に関する情報を1-7PPデータ変換部52に供給する。

10

### [ 0 1 2 6 ]

そして、NRZI化部54は、同期信号挿入部53において同期信号を挿入されたチャネルビット列をNRZI化し、区間DSV計算部55に供給する。

### [0127]

また、1-7PPデータ変換部52より変調切れ目位置情報を供給された変調切れ目検出部81は、変調の切れ目位置を検出し、変調切れ目位置信号を作成し、有効区切れ目検出部82に供給する。

### [0128]

他方、データ列を供給されたDSV制御ビット1付加部71は、値が「1」のDSV制御ビットを、所定の間隔でデータ列に付加する。1-7PPデータ変換部72は、1-7PPデータ変換部52と同様に、DSV制御ビットが付加されたデータ列をチャネルビット列に変換する

20

### [0129]

また、1-7PPデータ変換部72は、必要に応じて、同期信号挿入部73より供給された同期信号の最終ビットに関する情報を参照し、取得したデータ列をチャネルビット列に変換する。変換されたチャネルビット列は、同期信号挿入部73に供給される。また、1-7PPデータ変換部72は、変調切れ目位置情報を変調切れ目位置検出部91に供給し、さらに、DSV区間切れ目信号を有効区切れ目検出部92に供給する。

# [0130]

30

同期信号挿入部73は、同期信号を挿入し、NRZI化部74に供給する。また、同期信号挿入部73は、挿入した同期信号の最終ビットの値に関する情報を1-7PPデータ変換部72に供給する。そして、NRZI化部74は、同期信号挿入部73において同期信号を挿入されたチャネルビット列をNRZI化し、区間DSV計算部75に供給する。

# [0131]

また、1-7PPデータ変換部72より変調切れ目位置情報を供給された変調切れ目検出部91は、変調の切れ目位置を検出し、変調切れ目位置信号を作成し、有効区切れ目検出部92に供給する。

### [0132]

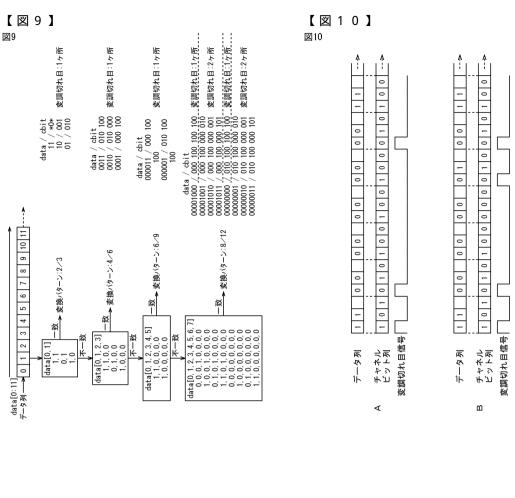

図 9 は、1-7PPデータ変換部 5 2または72が変調切れ目位置にフラグを立てる様子の具体例を示す図である。以下、1-7PPデータ変換部 5 2の処理であるものとして説明するが、1-7PPデータ変換部72も、同様の処理を実行する。

40

### [0133]

図 9 において示されるように、 1 - 7 PPデータ変換部 5 2 のDSV制御ビットつきデータ列用のレジスタに、DSV制御ビット付きデータ列が、data [ 0 : 1 1 ] の 1 2 ビットのdata [ 0 ] から順に入力され、レジスタ数字の大きいほうヘクロックごとにシフトされていく。そして、data [ 1 1 ] までシフトされたデータは、次のシフト時に捨てられる。また、データ列と対応するチャネルビット列との関係は、図 5 を用いて上述したようになっている。

# [0134]

20

30

40

50

また、上述したように、変調切れ目位置を示すレジスタ等の、タイミング制御を行うためのレジスタは、チャネルビット列を格納するレジスタと同数のデータを格納できるように構成されており、互いに同じ位置が対応されている。また、これらタイミング制御のためのレジスタには、例えばアクティブ時において「1」が格納され、それ以外の位置には「0」が格納される。

### [0135]

データ列は、レジスタのデータ入力順の前方向(すなわち、data [0] 側)から、 2 データ毎に処理される。data [0,1]=[1,1] ,data [0,1]=[0,1] 、または data [0,1]=[1,0] である場合、 (11) , (10) 、または (01) を検出した 1-7 PPデータ変換部 5 2 は、上述したように、表 1 の変換テーブルに基づいて、変換パターンを確定する。そして、cbit [0,1,2] に、変換されたチャネルビット列が格納される。このとき、cbit [2] と同じ位置の変調切れ目位置を示すレジスタに 1 が格納される。

### [0136]

#### [ 0 1 3 7 ]

data [0,1,2,3] = [0,0,0,0] の場合、拘束長i=2 において変換パターンは確定されず、新たなるデータ列が順に入力される。新たに2 データ(合計 6 データ)が入力されると、1-7 PPデータ変換部 5 2 は、data [0,1,2,3,4,5] を参照する。そして、data [0,1,2,3,4,5] が、[1,1,0,0,0,0,0]、または [1,0,0,0,0] である場合、(000011)、または (0000011)、または (0000011)、を検出した 1-7 PPデータ変換部 5 2 は、上述したように、表 1 の変換テーブルに基づいて、変換パターンを確定する。そして、cbit [0,1,2,3,4,5,6,7,8] に、変換されたチャネルビット列が格納される。このとき、cbit [8] と同じ位置の変調切れ目位置を示すレジスタに 1 が格納される。

### [0138]

data [0,1,2,3,4,5] が、[0,0,0,0,0,0]、または [0,1,0,0]0、0、0、0、0]の場合、拘束長i=3において変換パターンは確定されず、新たなるデータ列が順に入力される。新たに2 データ(合計 8 データ)が入力されると、1-7 PPデータ変換部 5 2 は、data [0,1,2,3,4,5,6,7] を参照し、上述したように、表 1 の変換テーブルに基づいて、変換パターンを確定する。

#### [0139]

、(0000101010)から"0001000001"に、(00001011)から"0001010101"に、それぞれ変換する。そして、変換後のチャネルビット用のレジスタのcbit [0,1,2,3,4,5,6,7,8,9,10,11]に、変換されたチャネルビット列が格納される。

### [0140]

このとき、変調切れ目位置を示すレジスタの所定の位置に、1が格納される。

#### [0141]

具体的には、data [ 0 , 1 , 2 , 3 , 4 , 5 , 6 , 7 ] が、 [ 0 , 0 , 0 , 1 , 0 , 0 , 0 , 0 , 0 ] 、または、 [ 0 , 0 , 0 , 0 , 0 , 0 , 0 ] の場合、変調切れ目位置は 1 箇所であり、変調切れ目位置を示すレジスタの、cbit [ 0 , 1 , 2 , 3 , 4 , 5 , 6 , 7 , 8 , 9 , 1 0 , 1 1 ] におけるcbit [ 1 1 ] と同じ位置に、 1 が格納される。

#### [0142]

また、data [ 0 , 1 , 2 , 3 , 4 , 5 , 6 , 7 ] が、 [ 1 , 0 , 0 , 1 , 0 , 0 , 0 , 0 ] 、 [ 0 , 1 , 0 , 1 , 0 , 0 , 0 ] 、 [ 1 , 1 , 0 , 1 , 0 , 0 , 0 ] 、 [ 1 , 1 , 0 , 1 , 0 , 0 , 0 , 0 ] 、 [ 1 , 1 , 0 , 0 , 0 , 0 , 0 ] 、 または、 [ 1 , 1 , 0 , 0 , 0 , 0 , 0 , 0 ] の場合、変調切れ目位置は 2 箇所であり、変調切れ目位置を示すレジスタの、cbit [ 0 , 1 , 2 , 3 , 4 , 5 , 6 , 7 , 8 , 9 , 1 0 , 1 1 ] におけるcbit [ 1 1 ] およびcbit [ 2 ] と同じ位置に、 1 が格納される。

### [0143]

なお、表 1 においては、上述したパターン以外にtermination tableにおける変換パターンが存在するが、これらのパターンについての動作も、基本的に上記と同様である。すなわち、表 1 のtermination tableと一致した上で、さらに同期信号の挿入される位置が検出された場合、変換パターンが確定される。この場合の変調切れ目位置については、それぞれ変換されたチャネルビットに対して 1 箇所に与えられる。

#### [0144]

さらに、表 1 においては、最小ラン連続制限を行う変換パターンが存在するが、これらの動作についても、基本的に上記と同様である。すなわち、最小ラン連続制限コードを用いて変換が行われた場合、変調切れ目位置は、変換された 9 チャネルビットに対して 1 箇所に与えられる。

# [0145]

以上のように、入力データ列から、チャネルビット列へ、全てのパターン変換が行われ、変調切れ目情報が与えられる。そして、次のパターン変換は、パターンが確定し、変調切れ目情報が発生した後、再度、拘束長i=1から始まり、上述したような動作を繰り返す。このとき、チャネルビット列および変調切れ目情報は、変換処理が完了したのち、図5における、18ビットのレジスタにより出力され、変換済みのチャネルビット列および変調切れ目情報が、図8の同期信号挿入部53に供給される。

# [0146]

図 8 に戻り、変調切れ目検出部 8 1 は、上述したように、 1 - 7 PPデータ変換部 5 2 の、変調切れ目位置情報が示されているレジスタを参照し、変調切れ目位置を検出する。

#### [0147]

なお、変調切れ目検出部91も、上述した場合と同様に、変調切れ目位置情報が示されているレジスタを参照し、変調切れ目位置を検出する。この場合、1-7PPデータ変換部52と同様の処理を、1-7PPデータ変換部72が行い、同期信号挿入部53と同様の処理を、同期信号挿入部73が行う。

#### [0148]

ところで、この例においては変換率m:nは2:3とされているので、入力データ列に対する発生符号語列の関係は、符号語のデータ量3に対して、データ語のデータ量は2となる。従って、入力データ列はその中から、2クロックの間に所定の2データ語だけが入力され、その後、1クロック分その入力が停止される。このようにして、入力データと出力符号との変換率に関するずれが調整される。この関係は、図10、図11および図12の

10

20

30

40

データ列、チャネルビット列において示されている。

### [0149]

図10は、図8に示す変調切れ目検出部81による変調切れ目の検出の様子を示す図である。図10において、左から右に時間が経過しており、データ列は、左から順にレジスタに入力され、チャネルビット列に変換されている。

#### [0150]

図10Aにおいて、2ビットのデータ列(11)は"101"に変換されており、"101"の先頭の"1"に対応する変調切れ目を示すレジスタの位置に「1」が格納されている。変調切れ目検出部81は、上述したように、このレジスタを参照し、変調切れ目位置を検出し、変調切れ目信号を制御する。

### [0151]

次に、8ビットのデータ列(00000000)は"010100100100"に変換されており、"010100100100100"の先頭の"0"に対応する変調切れ目を示すレジスタの位置に「1」が格納されている。変調切れ目検出部81は、上述したように、このレジスタを参照し、変調切れ目位置を検出し、変調切れ目信号を制御する。

#### [0152]

同様に、4ビットのデータ列(0011)は、"010100"に変換されており、"010100"の先頭の"0"に対応する変調切れ目を示すレジスタの位置に「1」が格納されている。変調切れ目検出部81は、上述したように、このレジスタを参照し、変調切れ目位置を検出し、変調切れ目信号を制御する。

#### [ 0 1 5 3 ]

同様に、図10Bにおいて、2ビットのデータ列(11)は"101"に変換されており、"101"の先頭の"1"に対応する変調切れ目を示すレジスタの位置に「1」が格納されている。変調切れ目検出部81は、上述したように、このレジスタを参照し、変調切れ目位置を検出し、変調切れ目信号を制御する。

### [0154]

次に、8ビットのデータ列(0000001)は"010100000010"に変換されており、"01010000010"の先頭の"0"および右から3番目の"0"に対応する変調切れ目を示すレジスタの位置に「1」が格納されている。変調切れ目検出部81は、上述したように、このレジスタを参照し、変調切れ目位置を検出し、変調切れ目信号を制御する。

# [0155]

同様に、4ビットのデータ列(0011)は、"010100"の先頭の"0"に対応する変調切れ目を示すレジスタの位置に「1」が格納されている。変調切れ目検出部81は、上述したように、このレジスタを参照し、変調切れ目位置を検出し、変調切れ目信号を制御する。

# [0156]

以上のように、拘束長i = 4 における変換のパターンにより、変調切れ目の個数が変化する。

# [0157]

なお、変調切れ目検出部 8 1 が、上述した、拘束長 i = 4 すなわち、 8 データにおけるパターン変換時の変調切れ目位置を、前方の1ヶ所に統一して、これを変調切れ目信号として出力しても、DSV制御ビット決定部 3 1 は動作することができる。この場合、上述した方式とは、区間DSV計算結果に差異を生じることになる。

### [0158]

変調切れ目検出部 8 1 により作成された変調切れ目信号は、有効区切れ目検出部 8 2 に供給される。変調切れ目信号を供給された有効区切れ目検出部 8 2 は、1 - 7 PPデータ変換部 5 2 により供給されたDSV区間切れ目信号に基づいて、有効区切れ目位置を検出し、有効区切れ目信号を区間DSV計算部 5 5 およびDSV制御ビット判定部 6 2 に供給する。

### [0159]

50

10

20

30

なお、変調切れ目検出部 9 1 も変調切れ目検出部 8 1 と同様に動作し、変調切れ目検出部 9 1 により作成された変調切れ目信号は、有効区切れ目検出部 9 2 に供給される。変調切れ目信号を供給された有効区切れ目検出部 9 2 は、1 - 7 PPデータ変換部 7 2 により供給されたDSV区間切れ目信号に基づいて、有効区切れ目位置を検出し、有効区切れ目信号を区間DSV計算部 7 5 およびDSV制御ビット判定部 6 2 に供給する。

### [0160]

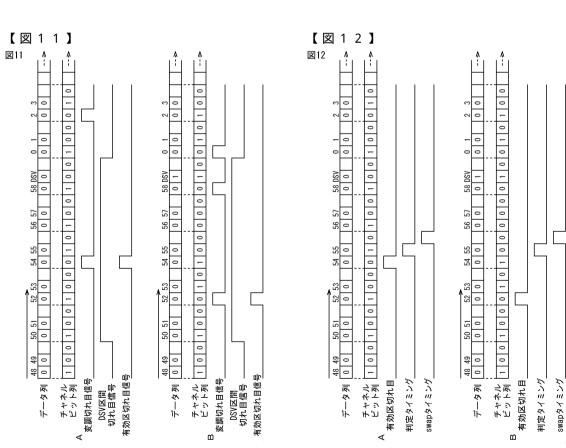

図11は、有効区切れ目検出部82または92による有効区切れ目信号の制御の様子の例を示す図である。図11において、左から右に時間が経過しており、データ列は、左から順にレジスタに入力され、チャネルビット列に変換されている。

#### [0161]

図11の例においては、DSV制御ビットは、データ列に対して、60データ毎に挿入されている。すなわち、データ列が59データ続いた後に、DSV制御ビットが挿入される。また、DSV区間切れ目位置は、60データのDSV区間において、51データ目の位置(図11内のデータ列50)に発生するように制御されている。すなわち、DSV区間切れ目位置信号は、1-7PP変換テーブルにおいて、データ列が可変長符号に変換されることを考慮して、DSV制御ビット位置に対して、9データだけ前方で、DSV区間切れ目位置が与えられるように設定されている。

### [0162]

DSV制御ビットは任意の値であるので、データ列にDSV制御ビットが挿入されることにより、変換されたチャネルビット列に差異が生じる。すなわち、1つのDSV制御ビットが制御する区間において、区間DSVの計算時、データ列の変換に次の未決定のDSV制御ビットが関係しないほうが、より正確にDSVを算出することができる。従って、DSV区間切れ目位置は、実際のDSV区間における切れ目位置と異なる位置に与えられる。

#### [ 0 1 6 3 ]

表1に示した1-7PP変換テーブルにおいて、1度の変調のために参照される最大のデータ列の大きさは、(11011100000)の11データである。また、2データ毎に変換処理が行われていることと合わせて、次のDSV区間のDSV制御ビットを含まずに変換されるデータ列であること(次のDSV制御ビットの影響を受けないデータ列であること)を保障できるのは、49データ目における変換までとなる。次の51データ目における変換では、1度の変調のために参照される最大のデータ列の中には、次のDSV区間のDSV制御ビットが含まれている。従って、60データのDSV区間におけるDSV区間切れ目位置を、51データ目以下の設定とする。

#### [0164]

ところで、このDSV区間切れ目位置は、低域抑圧特性と関係があり、なるべく後方に位置させるほうが、周波数の低域が抑圧され、変調装置としての性能が向上し、望ましい。以上より図11において、51データ目(図11内のデータ列50)に、DSV区間切れ目位置が与えられている。

### [0165]

結局、DSV制御ブロック切れ目位置信号におけるDSV区間において、挿入されたDSV制御ビットは、1つだけとなるように設定されている。

# [0166]

図11Aにおいて、DSV区間は60データであり、60データ目に値が「0」のDSV制御ビットが挿入されている。また、データ列は「0」のみで構成され、(00000000)として、繰り返し"010100100100"に変換されている。そして先頭の6データは、図示されていない、前の2データの(00)とともに、(0000000000変換が行われているとする。この時、次の変換単位である8データの、(0000000000000円には、DSV制御ビットが含まれている。

#### [0167]

10

20

30

40

次のDSV区間の3データ目となる。従って、変調切れ目検出部81は、55データ目、および、次のDSV区間の3データ目が、「1」となるように制御された変調切れ目信号を有効区切れ目検出部82に供給する。

### [0168]

またDSV区間切れ目位置は、上述したように、51データ目となるので、1-7PP変換部52は、51データ目以降より、値が「1」となるDSV区間切れ目信号を有効区切れ目検出部82に供給する。上記DSV区間切れ目信号は、区間DSV制御処理が終了したのち、値を「0」に戻す。例えば、図11Aのように、1データ目において、DSV区間切れ目信号が「1」から「0」に反転される。

#### [0169]

そして、有効区切れ目検出部82は、供給された変調切れ目信号およびDSV区間切れ目信号に基づいて、DSV切れ目位置が「1」となった後、最初の変調切れ目である、55データ目を有効区切れ目として検出し、55データ目が「1」となるように制御された有効区切れ目信号を作成し、区間DSV計算部55およびDSV制御ビット判定部62に供給する。

### [0170]

一方の図11Bは、DSV制御ビット1付加部71において、60データ目に値が「1」のDSV制御ビットが挿入され、他のデータを「0」としている図である。そして先頭の4データは、図示されていない、前の4データの(0000)とともに、(000000)の変換が行われているとする。

# [0171]

この時、次の変換単位である 8 データの、(0000001)内には、DSV制御ビットが含まれている。

# [0172]

DSV制御ビットを含む (0000001)は、"01010000010"に変換されている。この場合、上述したように、53データ目および59データ目の2箇所が変調切れ目となる。

### [ 0 1 7 3 ]

そして、有効区切れ目検出部92は、供給された変調切れ目信号およびDSV区間切れ目信号に基づいて、DSV切れ目位置が「1」となった後、最初の変調切れ目である、53データ目を有効区切れ目として検出し、53データ目が「1」となるように制御された有効区切れ目信号を作成し、区間DSV計算部75およびDSV制御ビット判定部62に供給する。

# [0174]

図11Bの場合、図11Aの場合と変調切れ目位置がずれている。通常ランダムパターンの入力においては、値が「0」のDSV制御ビットを付加したデータ列と、値が「1」のDSV制御ビットを付加したデータ列とは、速やかに収束し、変調切れ目付近においては、同様な変調切れ目位置となる。しかし、特有なパターンにおいては、上記のように収束せず、変調切れ目付近においても、変調切れ目位置がずれている場合があり、DSV区間に影響を及ぼす場合がある。

### [0175]

しかし、有効区切れ目検出部 8 2 および 9 2 は、この場合においても、通常の場合と同様に、そのまま、互いにずれた有効区切れ目信号を出力する。

#### [0176]

なお、図11においては、図5に示されるレジスタ分の遅延を考慮せずに、DSV区間を示した。しかしながら、これに限らず、これを例えば、図5のチャネルビット列を格納するレジスタcbit [0]において、DSV区間のカウントが行われ、データ列、チャネルビット列、および変調切れ目情報が、cbit [17]において参照されるようにしても良い。この場合、DSV区間のカウンタに対し、参照するデータ列、チャネルビット列、および変調切れ目情報は、図5に示すように18bit分遅延されているが、有効区切れ目検出部82および92は、上述した場合と同様にして、有効区切れ目の検出を行う。

# [0177]

50

20

10

30

以上のように、検出された有効区切れ目のタイミングに基づいて、区間DSV計算部55は、対象となるDSV区間のチャネルビット列より区間DSVを算出し、加算器56に供給する。また、区間DSV計算部75も同様に区間DSVを算出し、検出された有効区切れ目のタイミングに基づいて、加算器76に供給する。

### [0178]

加算器 5 6 は、供給された区間DSVに、積算DSV処理部 6 1 より供給された積算DSVを加算し、新しく算出された積算DSVをDSV制御ビット判定部 6 2 に供給する。加算器 7 6 も同様に、供給された区間DSVに、積算DSV処理部 6 1 より供給された積算DSVを加算し、新しく算出された積算DSVを、DSV制御ビット判定部 6 2 に供給する。

### [0179]

2つの新たな積算DSVの供給を受けたDSV制御ビット判定部62は、有効区切れ目検出部82および92より供給された有効区切れ目信号のタイミングに基づいて、データ列に挿入するDSV制御ビットの値を判定する。DSV制御ビット判定部62は、加算器56および76より供給された、2つの新たに算出された積算DSVのうち、例えば、絶対値が小さい方を選択する。そして、DSV制御ビット判定部62は、挿入するDSV制御ビットの値が決定されると、その情報をDSV制御ビット指定位置挿入部32に供給するとともに、選択された方の新たな積算DSVを積算DSV処理部61に供給する。

### [0180]

さらにDSV制御ビット判定部62は、次のDSV区間の演算のために使用されるレジスタの値を制御するために、スワップ動作の起動を行う。すなわち、選択された側を指定する情報を、1-7PPデータ変換部52、同期信号挿入部53、NRZI化部54、区間DSV計算部55、1-7PPデータ変換部72、同期信号挿入部73、NRZI化部74、および、区間DSV計算部75に供給する。そして、選択された側の各部が参照したレジスタの値を用いて、選択されなかった反対側の各部が参照したレジスタの値から置き換えて記憶させる。

#### [0181]

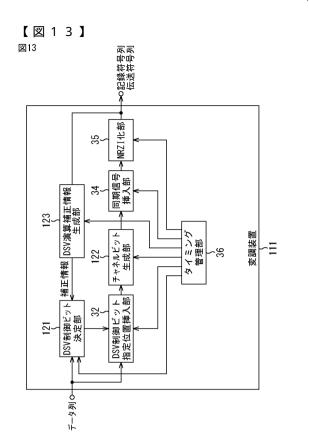

図 1 2 は、DSV制御ビット判定部 6 2 によるスワップタイミングを決定する様子を示す図である。

# [0182]

図12Aにおいて、DSV制御ビット判定部62には、値が「0」のDSV制御ビットを挿入されたデータ列による、有効区切れ目信号が供給されている。また、図12Bにおいて、DS V制御ビット判定部62には、値が「1」のDSV制御ビットを挿入されたデータ列による、有効区切れ目信号が供給されている。図12Bの場合と、図12Aの場合とでは、有効区切れ目位置が異なっている。図12Bの場合が、図12Aの場合と比較して、先に有効区切れ目信号が供給されている。

### [0183]

この場合、DSV制御ビット判定部62は、両方の有効区切れ目が出現した次のタイミングにおいて、DSV制御ビットの判定を行う。すなわち、図12の場合、図12Bよりも図12Aのほうが有効区切れ目位置が遅いので、図12Aの有効区切れ目位置の次のタイミングにおいて、判定を行う。すなわち、DSV制御ビット判定部62は、値が「0」のDSV制御ビットを挿入されたデータ列の有効区切れ目の次のタイミングにおいて、DSV制御ビットの判定を行っている。そして、さらにその次のタイミングにおいて、各レジスタを制御して、選択された側のレジスタの内容に一致させるように、スワップ動作が行われる。

### [0184]

ここで、DSV制御ビットが「0」の側が選択されたと仮定すると、DSV制御ビット判定部62は、加算器56より供給された、新たなDSV積算値を積算DSV処理部61へ供給する。さらに、その判定結果をDSV制御ビット指定位置挿入部32に供給するとともに、1-7PPデータ変換部52、同期信号挿入部53、NRZI化部54、区間DSV計算部55、1-7PPデータ変換部72、同期信号挿入部73、NRZI化部74、および、区間DSV計算部75に対しても、供給する。

# [0185]

10

20

30

そして、選択されたDSV制御ビットが「0」の側である、1 - 7PPデータ変換部52のレジスタ内容を、1 - 7PPデータ変換部72に記憶させる。同様にして、同期信号挿入部53のレジスタ内容を、同期信号挿入部73に記憶させ、またNRZI化部54のレジスタ内容を、NRZI化部74に記憶させ、さらに、区間DSV計算部55のレジスタ内容を、区間DSV計算部75に記憶させる。以上のようなスワップ動作を行い、データの連続性を保つようにする。

#### [0186]

図12においては、有効区切れ目位置が異なっている場合を示したが、有効区切れ目位置が同じである場合についても、同様にして行われる。すなわち、DSV制御ビット判定部62は、両方の有効区切れ目が出現したの次のタイミングにおいて、DSV制御ビットの判定を行う。さらにその次のタイミングにおいて、各レジスタを制御して、選択された側のレジスタの内容に一致させるように、スワップ動作を行う。

#### [0187]

なお、図12に示す例においては、図5に示されるレジスタ分の遅延を考慮せずに有効区切れ目が検出されているように説明したが、これに限らず、レジスタ分の遅延を考慮してもよい。その場合も、DSV制御ビット判定部62は、上述した場合と同様の動作を行う。

### [0188]

上記のとおり、DSV制御ビット判定部62は、データ列に挿入するDSV制御ビットの値として選択された方が参照したレジスタの値を用いて、選択されなかった反対側が参照したレジスタの値を更新し、互いに一致させる(スワップする)ようにした。このとき、DSV制御ビット判定部62は、各レジスタ内において、次のDSVspanに入るべきであるDSV制御ビット、もしくは、次のDSVspanに入るべきDSV制御ビットが含まれた情報を格納しないように、スワップタイミングを制御する。

#### [ 0 1 8 9 ]

DSV制御ビット判定部 6 2 よりDSV制御ビットの値に関する情報を取得したDSV指定位置挿入部 3 2 は、指定された値のDSV制御ビットをデータ列に挿入し、データ変換部 3 3 に供給する。データ変換部 3 3 は、DSV制御ビットが挿入されたデータ列を、表 1 の変換テーブルを参照して、チャネルビット列に変換し、同期信号挿入部 3 4 に供給する。同期信号挿入部 3 4 は、チャネルビット列に所定の同期信号を挿入し、NRZI 化部 3 5 に供給する。NRZI 化部 3 5 は、供給されたチャネルビット列を記録符号列もしくは伝送符号列などの出力符号列に変換し、出力する。

## [0190]

以上のようにして、変調装置30は、入力されたデータ列を変調する。これにより、変調装置30は、挿入するDSV制御ビットの値をより正確に決定することができる。

# [0191]

上述した変調装置 3 0 で実行される方法によるDSV制御においては、スワップするタイミング位置として、データレジスタ内に、次のDSVspanに入るべきであるDSV制御ビットを含まないという制限があった。このため、実際のDSV制御位置が前方にシフトし、DSV制御の効果も制限された。

### [0192]

これに対して、DSV区間内のなるべく後方でDSV制御を行うために、スワップ時に、データレジスタにDSV制御ビットを含んでも良いように構成するようにすることができる。

### [0193]

図13万至図26を参照して、スワップ時に、データレジスタにDSV制御ビットを含んでも良いように構成した、本発明に係る変調装置111の実施の形態を、図面を参照しながら説明する。この実施の形態でも、データ列が、表1に従って、可変長符号(d,k;m,n;r)=(1,7;2,3;4)に変換される。

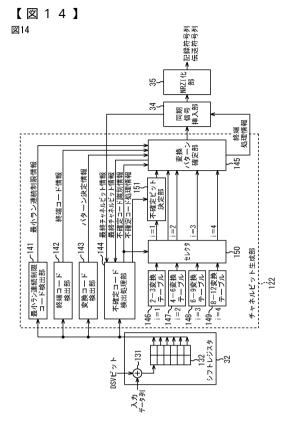

#### [0194]

図13は、本発明に係る変調装置111の構成を示すブロック図である。なお、図3における場合と対応する部分には同一の符号を付してあり、その説明は適宜省略する。

10

20

30

40

### [0195]

図13に示すように、変調装置111は、入力されたデータ列に基づいて、データ列に挿入するDSV制御ビットとして、「1」または「0」を決定するDSV制御ビット決定部121、値が決定されたDSV制御ビットを、入力されたデータ列にタイミングを合わせて挿入するDSV制御ビット指定位置挿入部32、決定されたDSV制御ビットが挿入されたデータ列を所定の変換テーブルを用いてチャネルビットに変換するチャネルビット生成部122、チャネルビット生成部122より供給されたチャネルビット列の所定の位置に所定の同期信号を挿入する同期信号挿入部34、同期信号挿入部34の出力を記録符号列もしくは伝送符号列などの出力符号列に変換するNRZI化部35、および、記録符号列もしくは伝送符号列などの出力符号列に変換するNRZI化部35、および、記録符号列もしくは伝送符号列などの出力符号列より得られた積算DSVより、補正情報を作成するDSV演算補正情報生成部123を備える。

10

### [0196]

また、変調装置111は、タイミング信号を生成し、DSV制御ビット決定部121、DSV制御ビット指定位置挿入部32、チャネルビット生成部122、同期信号挿入部34、NRZI化部35、およびDSV演算補正情報生成部123に供給してタイミングを管理するタイミング管理部36を備える。

### [0197]

なお、図13において、DSV制御ビット指定位置挿入部32は、タイミング管理部36に処理のタイミングを管理されているものとして説明したが、これに限らず、例えば、DSV制御ビット指定位置挿入部32が、入力ビット列の伝送タイミングを調整する機能をさらに有し、DSV制御ビット決定部121より供給されるDSV制御ビットを、伝送タイミングを調整された入力ビット列の所定位置に挿入するようにしてもよい。

20

#### [0198]

なお、図13の変調装置111においても、生成されるチャネルビット列(NRZI化後の記録符号列もしくは伝送符号列などの出力符号列)は、図4を用いて説明した場合と同様にして、FSが挿入された後において、等しい間隔でDSV制御ビットが挿入されており、DSV制御が行われるようになされている。

[0199]

すなわち、図13の変調装置111において、供給されるデータ列には、図4に示されるように、ユーザデータの他に、例えば、ECC(Error Correcting Code)等の情報データが含まれており、DSV制御ビット決定部121の決定に基づき、DSV制御ビット指定位置挿入部32において、DSV制御ビットである×1、×2、および×3が、データ列内に任意の間隔で挿入される。

30

### [0200]

また、DATA 1 には、フレーム間で同期をとるためのフレーム同期信号(FS)が挿入される。このため、DATA 1 においては、DSV制御ビットを挿入する間隔であるDSV区間は、短く設定される。

[0201]

すなわち、FSに加えて、DATA 1 に対応するチャネルビットからなるCbit 1 を含むDSV区間の長さであるspan 1、DATA 2 に対応するチャネルビットからなるCbit 2 を含むDSV区間の長さであるspan 2、およびDATA 3 に対応するチャネルビットからなるCbit 3 を含むDSV区間の長さであるspan 3 が、全て同じ長さ(span 1 = span 2 = span 3 )となるように、DATA 1 の長さは決定される。

40

# [0202]

従って、挿入されたFSがFS(bit)であり、DATA 2 およびDATA 3 がともにx(bit)である場合、変換テーブルの変換率がm: n = 2 : 3 であるので、DATA 1 は、x - FS \* 2 / 3 (bit)となる。

### [0203]

なお、挿入するDSV制御ビットの値を決定するために、区間DSVspan 1、区間DSVspan 2、および区間DSVspan 3 は、実際にDSV制御ビットが挿入されている位置よりも前方に区切ら

20

30

40

50

れる。この際、各DSV制御区間内には、1つのDSV制御ビットのみが挿入されている。

### [0204]

以上のように、チャネルビット列(NRZI化後の記録符号列もしくは伝送符号列などの出力符号列)は、FSが挿入された後において、等しい間隔でDSV制御ビットが挿入されており、DSV制御が行われている。

### [0205]

図14は、変調装置111の、DSV制御ビット指定位置挿入部32、および、チャネルビット生成部122の詳細な構成例を示すプロック図である。

### [0206]

DSV制御ビット指定位置挿入部32は、入力されたデータ列にDSV制御ビットを挿入する挿入部131、および、供給されたデータをシフトしながら保持するシフトレジスタ132 で構成されている。

#### [0207]

図14において、入力されたデータ列は、DSV制御ビット指定位置挿入部32の挿入部131において、後述するDSV制御ビット決定部121の処理により決定されたDSV制御ビットを挿入され、シフトレジスタ132に供給される。

### [0208]

シフトレジスタ132は、供給されたデータをシフトさせながら、チャネルビット生成部122の最小ラン連続制限コード検出部141、終端コード検出部142、変換コード検出部143、および、不確定コード検出処理部144に供給する。このとき、シフトレジスタ132は、最小ラン連続制限コード検出部141、終端コード検出部142、変換コード検出部143、および、不確定コード検出処理部144の各部がその処理を行うのに必要なビット数を、それぞれに供給する。

#### [0209]

チャネルビット生成部 1 2 2 は、コード検出を行う、最小ラン連続制限コード検出部 1 4 1、終端コード検出部 1 4 2、変換コード検出部 1 4 3、および、不確定コード検出処理部 1 4 4を備え、更に、表 1 に示すような変換テーブルの拘束長 i = 1 乃至 4 における変換テーブルをそれぞれ保持する 2 - 3 変換テーブル 1 4 6、4 - 6 変換テーブル 1 4 7、6 - 9 変換テーブル 1 4 8、および、4 - 1 2 変換テーブル 1 4 9を備える。また、チャネルビット生成部 1 2 2 は、更に、2 - 3 変換テーブル 1 4 6 乃至 8 - 1 2 変換テーブル 1 4 6 乃至 8 - 1 2 変換テーブル 1 4 9 のうちのいずれかに記憶されている変換パターンを選択して取得し、変換パターン確定部 1 4 5 に供給するセレクタ 1 5 0、不確定コード検出処理部 1 4 4 に供給された情報に基づいて、セレクタ 1 5 0、不確定コード検出処理部 1 4 4 に供給された情報に基づいて、セレクタ 1 5 0、もしくは、不確定ビット決定部 1 5 1 より供給された変換パターンの中から使用する変換コードを選択し、同期信号挿入部 3 4 に供給する変換パターン確定部 1 4 5 で構成されている。

# [0210]

最小ラン連続制限コード検出部141は、入力されたデータから、表1中の(110111)のパターンを検出する。最小ラン連続制限コード検出部141は、予め所定のビット数のデータ列を記憶しており、入力されたデータから(110111)を検出すると、さらに続く入力データ列を参照する。そして、(110111)の直後に続くパターンが(01)、(001)、または、(00000)である場合、もしくは、(110111)の直後に続くパターンが(0000)であり、さらに入力されたデータがここで終端される場合、最小ラン連続制限コード検出部141は、最小ラン連続制限コードを検出したと判定し、その情報を変換パターン確定部145に供給する。

# [0211]

なお、最小ラン連続制限コード検出部141は、予め所定のビット数のデータ列を記憶しており、上記とは逆に、入力されたデータから(01)、(001)、もしくは(00000)を検出した場合、または、入力されたデータから(0000)を検出し、さらに入力されたデータがここで終端される場合、その直前の入力データ列を6データ分参照する

20

30

40

50

ようにし、その参照の結果が(110111)である場合、最小ラン連続制限コードを検出したと判定し、その情報を変換パターン確定部145に供給するようにしてもよい。

### [0212]

不確定コード検出処理部144は、表1中の拘束長i=1における(11)を入力されたデータから検出する。不確定コード検出処理部144は、入力されたデータが(11)である場合、その情報をセレクタ150および変換パターン確定部145に供給する。そして、不確定コード検出処理部144は、直前のパターンの最終チャネルビットの情報を、変換パターン確定部145または同期信号挿入部34から取得し(すなわち、変調装置111において、直前のパターンの最終チャネルビットの情報は不確定コード検出処理部144にフィードバックされる)、取得した最終チャネルビットが0である場合、変換する符号を"101"に決定し、最終チャネルビットが1である場合、変換する符号を"101"に決定し、最終チャネルビットが1である場合、変換する符号を"00"に決定するように、不確定ビット決定部151に情報を供給する。

#### [0213]

変換コード検出部143は、表1中のtermination tableを除いた、(11)および(110111)以外のパターンを検出する。そして、拘束長i=1乃至4に対し、それぞれデータ列パターンが検出された場合、その情報を、変換パターン確定部145へ供給する

### [0214]

終端コード検出部142は、表1中のtermination tableから終端コードのパターンを検出する。すなわち、終端コード検出部142は、入力されたデータから(00)、(0000)、(000)を検出し、さらに、内部に有する終端位置カウンタによって与えられる情報が終端位置を示すと判定した場合、終端コードを検出したと判定し、その情報を変換パターン確定部145に供給する。

#### [ 0 2 1 5 ]

2-3変換テーブル 1 4 6 は、表 1 に示すような変換テーブルの拘束長 i=1 の変換パターンである 2-3 変換パターンを記憶し、 4-6 変換テーブル 1 4 7 は、拘束長 i=2 の変換パターンである 4-6 変換パターンを記憶し、 6-9 変換テーブル 1 4 8 は、拘束長 i=3 の変換パターンである 6-9 変換パターンを記憶し、 8-1 2 変換テーブル 1 4 9 は、拘束長 i=4 の変換パターンである 8-1 2 変換パターンを記憶している。 2-3 変換テーブル 1 4 6 乃至 8-1 2 変換テーブル 1 4 9 は、それぞれ、記憶している変換パターンを、セレクタ 1 5 0 に供給する。

## [0216]

なお、上述した、2 - 3 変換パターン、4 - 6 変換パターン、6 - 9 変換パターン、および8 - 1 2 変換パターンは、不確定コード検出処理部144、変換コード検出部143、終端コード検出部142、または最小ラン連続制限コード検出部141より供給される情報が、例えば、変換されるチャネルビット列と1対1に対応する識別用の情報を有するなどして、テーブルの各要素に対して個別に識別可能な情報である場合、表1中における、データ列からチャネルビット列への対応テーブルのような構造以外の構造であっても構成することができる。

### [0217]

セレクタ150は、不確定コード検出処理部144から供給された情報に基づいて、2-3変換テーブル146乃至8-12変換テーブル149のうちのいずれかに記憶されている、2-3変換パターン、4-6変換パターン、6-9変換パターン、または、8-12変換パターンの中から、使用する変換パターンを選択して取得し、変換パターン確定部145に供給する。なお、不確定コード検出処理部144が、入力されたデータから(11)を検出した場合、セレクタ150は、不確定コード検出処理部144から供給された情報に基づいて、変換テーブル146から取得した2-3変換パターンを、不確定ビット決定部151に供給する。

### [0218]

不確定ビット決定部151は、不確定コード検出処理部144から供給された情報に基づ

20

30

40

50

いて、セレクタ150より供給される2-3変換パターンの不確定符号を決定し、その情報を変換パターン確定部145に供給する。

### [0219]

変換パターン確定部145は、最小ラン連続制限コード検出部141、不確定コード検出処理部144、変換コード検出部143、および終端コード検出部142より取得した情報に基づいて、セレクタ150、もしくは、不確定ビット決定部151より供給された変換パターンの中から使用する変換コードを選択し、同期信号挿入部34に供給するようになされている。

### [0220]

また、変換パターン確定部145は、決定した変換パターンの最終チャネルビットの情報を不確定コード検出処理部144に供給する。さらに、同期信号挿入部34において、同期信号がチャネルビット列の所定の位置に挿入される場合、変換パターン確定部145は、必要に応じて、termination table内の所定のパターンが使用されたか否か等の情報からなる終端処理情報を、同期信号挿入部34に供給する。

#### [0221]

同期信号挿入部34は、変換パターン確定部145より供給されたチャネルビット列に、変換テーブルの変換コードとして存在しないユニークなパターンを含む同期信号を挿入する。同期信号挿入部34は、所定の間隔においてチャネルビット列の入力を中断し、所定の同期信号パターンを挿入する。同期信号挿入部34によりチャネルビット列に挿入された同期信号パターンは、他と区別が可能なチャネルビット列の形式で挿入されており、必要に応じて変換パターン確定部145より供給される終端処理情報を参照し、決定される。同期信号挿入部34は、チャネルビット列に同期信号を挿入すると、その同期信号を挿入したチャネルビット列を、NRZI化部35に供給する。また、同期信号挿入部34は、チャネルビット列に挿入した同期信号の最終チャネルビットの情報を、不確定コード検出処理部144に供給する。

### [0222]

終端処理情報は、データ列から表 1 の termination tableのうち、(00)または(0000)の終端パターンが検出された場合に、変換パターン確定部 1 4 5 より同期信号挿入部 3 4 に供給される。同期信号挿入部 3 4 は、復調時の整合性のために、データ列が termination table内の所定のパターンを用いてチャネルビット列化されたか否かの情報を含ませた同期信号を作成し、挿入する。

# [0223]

例えば、同期信号内の先頭チャネルビットに終端テーブル識別用ビットが設けられ、term ination table内の所定のパターンが使用された場合、この終端テーブル識別用ビットに1が挿入され、それ以外の通常テーブル等のパターンが使用された場合、終端テーブル識別用ビットに0が挿入されるようにすることで、データ列がtermination tableの所定のパターンを用いてチャネルビット列化されたか否かを識別することができる。

### [0224]

NRZI化部35は、同期信号挿入部34に供給されたチャネルビット列を、チャネルビット列の1を反転、0を非反転として、ビット列を並び直してNRZI化し、記録符号列もしくは伝送符号列などの出力符号列を作成する。換言すると、NRZI化前のチャネルビット列は、NRZI化後の出力符号列のエッジ位置を示すビット列であり、NRZI化後の出力符号列は、記録データもしくは伝送データのH/Lのレベルを示すビット列に相当する。

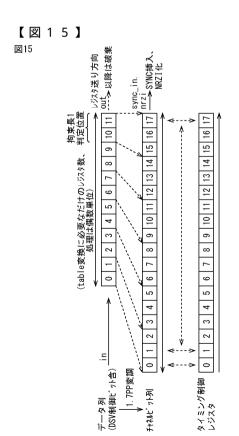

# [0225]

図 1 5 には、入力されたデータ列を、上述した表 1 に基づいてチャネルビット列へ変換する際に必要なレジスタの構成例が示されている。変換前のDSV制御ビットを挿入されたデータ列を格納するために、data [0:11]の12ビットのレジスタが構成され、チャネルビット生成部122の処理において変換された後のチャネルビット列を格納するために、cbit [0:17]の18ビットのレジスタが構成されている。また、その他にタイミング用レジスタ等も構成される。

20

30

40

50

#### [0226]

なお、変調切れ目位置を示すレジスタ等の、タイミング制御を行うためのレジスタも、チャネルビット列を格納するレジスタと同数のデータを格納できるように構成されており、互いに同じ位置が対応されている。また、これらタイミング制御のためのレジスタには、例えば、アクティブ時において「1」が格納され、それ以外の位置には「0」が格納される。

#### [0227]

図15に示されるレジスタにおいて、データ列は、図5を用いて説明した場合とは逆に、12ビット全てが入力された後、レジスタのデータ入力順の後ろ側、換言すれば、時間的に先に入力されたデータ(すなわち、data[11]側)から、2データ毎に処理される。すなわち、例えば、拘束長i=1の判定は、データ列[10:11]において行われる。

9 なわら、例えは、拘果長1= 「の判定は、テータ列[ T 0 : T T ] にのいて174 【 0 2 2 8 】

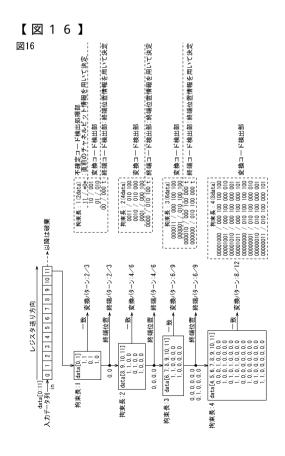

図16は、シフトレジスタ132よりDSV制御ビット付きデータ列を供給された不確定コード検出処理部144、変換コード検出部143、および終端コード検出部142の動作の具体例を示す図である。

#### [0229]

図 1 6 に示されるように、DSV制御ビット付きデータ列は、data [ 0 : 1 1 ] の 1 2 ビットに、data [ 0 ] から順に入力され、レジスタ数字の大きいほうヘクロックごとにシフトされていく。そして、data [ 1 1 ] までシフトされたデータは、次のシフト時に捨てられる。

[0230]

パターン変換の先頭位置において、不確定コード検出処理部144、変換コード検出部143、および終端コード検出部142は、data [10,11]を参照する。そして、data [10,11] = [1,1] である場合、(11)を検出した不確定コード検出処理部144は、上述したように動作し、その情報をセレクタ150および変換パターン確定部145に供給し、変換パターン確定部145または同期信号挿入部34から取得した直前のパターンの最終チャネルビットに基づいて、"101"または"000"に変換するように、不確定ビット決定部151に情報を供給する。

### [0231]

また、data [ 1 0 , 1 1 ] が、 [ 0 , 1 ] または [ 1 , 0 ] である場合、( 1 0 ) または ( 0 1 ) を検出した変換コード検出部 1 4 3 は、表 1 に示すような変換テーブルの拘束 長 i = 1 の変換コードを用いて、それぞれ " 0 0 1 " または " 0 1 0 " に変換するように、その情報を変換パターン確定部 1 4 5 に供給する。

[0232]

そして、data [ 1 0 , 1 1 ] = [ 0 , 0 ] である場合、(0 0 ) を検出した終端コード検出部 1 4 2 は、上述したように、内部に有する終端位置カウンタを参照する。そして、終端コード検出部 1 4 2 は、終端位置カウンタによって与えられる情報が終端位置を示すと判定した場合、(0 0 ) を " 0 0 0 "に変換し、終端するように、その情報を変換パターン確定部 1 4 5 に供給する。

[0233]

終端コード検出部142が内部に有する終端位置カウンタによって与えられる情報が終端位置を示さない場合、(00)は、拘束長i=1においてパターン変換されない。したがって、data[8,9,10,11]の4データが参照される。

# [0234]

変換コード検出部143および終端コード検出部142は、data [8,9,10,11]を参照する。そして、data [8,9,10,11]が、[1,1,0,0]、[0,1,0,0]、または、[1,0,0,0]である場合、変換コード検出部143は、表1に示すような変換テーブルの拘束長i = 2の変換コードを用いて、検出した(0011)を"010100"に、(0010)を"01000"に、または(0001)を"000100"に、それぞれ変換するように、情報を変換パターン確定部145に供給する。

20

30

40

50

### [0235]

そして、data [8,9,10,11] = [0,0,0,0]である場合、(0000)を検出した終端コード検出部142は、上述したように、内部に有する終端位置カウンタを参照する。そして、終端コード検出部142は、終端位置カウンタによって与えられる情報が終端位置を示すと判定した場合、"010100"に変換し、終端するように、その情報を変換パターン確定部145に供給する。

#### [0236]

終端コード検出部142が内部に有する終端位置カウンタによって与えられる情報が終端位置を示さない場合、(0000)は、拘束長i=2においてパターン変換されない。したがって、続いて6データが参照される。

### [0237]

なお、以上で説明した拘束長i=2の場合において、data[10,11]=[0,0]であることは、すでに拘束長i=1において判定済みであるので、data[8,9]についてのみ判定が行われるようにしてもよい。

### [0238]

変換コード検出部 1 4 3 および終端コード検出部 1 4 2 は、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] を参照する。そして、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] が、 [ 1 , 1 , 0 , 0 , 0 , 0 ] である場合、変換コード検出部 1 4 3 は、表 1 に示すような変換テーブルの拘束長 i = 3 の変換コードを用いて、検出した(0 0 0 0 1 1 ) を "0 1 0 1 0 0 1 0 0 "に、または(0 0 0 0 0 1 ) を "0 1 0 1 0 0 1 0 0 "に、それぞれ変換するように、情報を変換パターン確定部 1 4 5 に供給する。

### [0239]

そして、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] が、 [ 0 , 0 , 0 , 0 , 0 , 0 ] または [ 0 , 1 , 0 , 0 , 0 , 0 ] である場合、終端コード検出部 1 4 2 は、内部に有する終端 位置カウンタを参照する。そして、終端コード検出部 1 4 2 は、終端位置カウンタによって与えられる情報が終端位置を示すと判定した場合、検出した(0 0 0 0 0 0 ) を " 0 1 0 1 0 0 0 0 0 0 "に、(0 0 0 0 1 0 ) を " 0 0 0 1 0 0 0 0 0 "に、それぞれ変換し、終端するように、その情報を変換パターン確定部 1 4 5 に供給する。

#### [0240]

終端コード検出部142の内部に有する終端位置カウンタによって与えられる情報が終端位置を示さない場合、(000000)または(000010)は、拘束長i=3においてパターン変換されない。したがって、続いて8データが参照される。

#### [0241]

なお、以上で説明した拘束長i = 3 の場合において、data [ 8 , 9 , 1 0 , 1 1 ] = [ 0 , 0 , 0 , 0 ] であることは、すでに拘束長i = 2 において判定済みであるので、data [ 6 , 7 ] についてのみ判定が行われるようにしてもよい。

# [0242]

#### [0243]

また、data [ 4 , 5 , 6 , 7 , 8 , 9 , 1 0 , 1 1 ] が、 [ 0 , 0 , 0 , 1 , 0 , 0 , 0 , 0 ] 、 [ 1 , 0 , 0 , 1 , 0 , 0 , 0 ] 、 [ 0 , 1 , 0 , 1 , 0 , 0 , 0 ] 、 または、 [ 1 , 1 , 0 , 1 , 0 , 0 , 0 ] である場合、変換コード検出部 1 4 3 は

、表1に示すような変換テーブルの拘束長i = 4の変換コードを用いて、検出した(000010000)を"000100100100"に、(00001001)を"0001 00000010"に、(00001010)を"00010000001"に、(00010101)を"00010000001"に、(0000101010000001"に、(00001011)を"000100000101"に、それぞれ変換するように、情報を変換パターン確定部145に供給する。

## [0244]

以上で説明した拘束長i=4の場合において、data [8,9,10,11]=[0,0,0]0,0]であることは、すでに拘束長i=2において判定済みであるので、data [4,5],6,7]についてのみ判定が行われるようにしてもよい。

## [0245]

以上のように、入力されたDSV制御ビット付データ列は、チャネルビット列に変換される。そして、パターンが確定した後、再度、拘束長i = 1 から、次のパターン変換動作が繰り返される。図15に示すように、チャネルビット列が18ビットのレジスタにより供給されるまでに、データ変換は終了しており、データ変換が終了したのち、チャネルビット列が同期信号挿入部34へ供給される。

### [0246]

なお、これらの動作は、最大参照データは8データであるから、上述の動作を、レジスタの前方にシフトさせても良い。例えば、data [4,5,6,7,8,9,10,11]を用いて実行していたデータの検出位置を、4ビット前方にシフトさせ、data [0,1,2,3,4,5,6,7]としても良い。

### [0247]

最小ラン連続制限コード検出部141は、DSV制御ビット付データ列が入力されたシフトレジスタ132を参照し、最小ラン連続制限コードを検出する。

#### [0248]

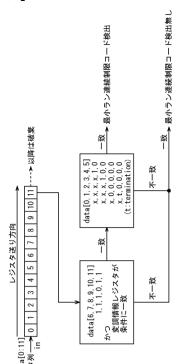

図 1 7 は、データ列から最小ラン連続制限コードを検出する最小ラン連続制限コード検出 部 1 4 1 の動作の具体例を示す図である。

## [0249]

図 1 7 において、DSV制御ビット付データ列が、図 1 6 の場合と同様に、data [ 0 : 1 1 ] に、data [ 0 ] から順に入力され、レジスタ数字の大きいほうへ、クロックごとにシフトされていく。そして、data [ 1 1 ] までシフトされたデータは、次のシフト時に捨てられる。

# [0250]

また、最小ラン連続制限コード検出部141によって、data [0:11]より最小ラン連続制限コードが検出された場合、図16を用いて説明したデータ列のチャネルビット列へのパターン変換結果ではなく、最小ラン連続制限コード変換に基づいて変換されたチャネルビット列が選択されて、図15を用いて説明した変換後のチャネルビット列cbit [0:17]のレジスタに格納される。

## [0251]

data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] = [ 1 , 1 , 1 , 0 , 1 , 1 ] であり、data [ 4 , 5 ] = [ 1 , 0 ] であって、さらに、後述する変調情報レジスタが条件に一致する場合、すなわち、(1 1 0 1 1 1 ) が検出され、その直後 2 データにおいて(0 1 ) が検出され、さらに、変調情報レジスタが条件に一致する場合、最小ラン連続制限コード検出部 1 4 1 は、最小ラン連続制限コードを検出したと判定し、その情報を変換パターン確定部 1 4 5 に供給する。

### [0252]

また、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] = [ 1 , 1 , 1 , 0 , 1 , 1 ] であり、data [ 3 , 4 , 5 ] = [ 1 , 0 , 0 ] であって、さらに、後述する変調情報レジスタが条件に一致する場合、すなわち、(1 1 0 1 1 1 1 ) が検出され、その直後 3 データにおいて(0 0 1 ) が検出され、さらに、変調情報レジスタが条件に一致する場合、最小ラン連続制限コード検出部 1 4 1 は、最小ラン連続制限コードを検出したと判定し、その情報を変換パ

10

20

30

40

ターン確定部145に供給する。

## [0253]

また、data [6,7,8,9,10,11] = [1,1,1,0,1,1]であり、data [2,3,4,5] = [0,0,0,0]で終端位置を示しており、さらに、後述する変調情報レジスタが条件に一致する場合、すなわち、(110111)が検出され、その直後4データにおいて(0000)で終端する終端位置が検出され、さらに、変調情報レジスタが条件に一致する場合、最小ラン連続制限コード検出部141は、最小ラン連続制限コードを検出したと判定し、その情報を変換パターン確定部145に供給する。

## [0254]

また、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] = [ 1 , 1 , 1 , 0 , 1 , 1 ] であり、data [ 1 , 2 , 3 , 4 , 5 ] = [ 0 , 0 , 0 , 0 , 0 ] であって、さらに、後述する変調情報 レジスタが条件に一致する場合、すなわち、( 1 1 0 1 1 1 ) が検出され、その直後 5 データにおいて( 0 0 0 0 0 ) が検出され、さらに、変調情報レジスタが条件に一致する場合、最小ラン連続制限コード検出部 1 4 1 は、最小ラン連続制限コードを検出したと判定 し、その情報を変換パターン確定部 1 4 5 に供給する。

### [0255]

変換パターン確定部 1 4 5 は、最小ラン連続制限コード検出部 1 4 1 より供給された情報に基づいて、データ列を所定のチャネルビット列に置き換える。このとき、置き換えられるチャネルビット列は、cbit [9,10,11,12,13,14,15,16,17]である。

### [0256]

このようにして、データ変換が終了して、生成されたチャネルビット列が、データ変換が終了したチャネルビット列を保持するための18ビットのレジスタに保持され、同期信号挿入部34に供給される。

### [0257]

なお、(110111)が検出された場合、その直後の参照データは最大で5データであるから、上述の動作を、1レジスタ前方にシフトさせても良い。すなわち、(110111)の検出位置を、data [5,6,7,8,9,10]としても良い。この場合、変換コード検出部143および終端コード検出部142が検出のために参照するレジスタの位置を、同様なだけ、または、さらに前方にシフトさせておく。

### [0258]

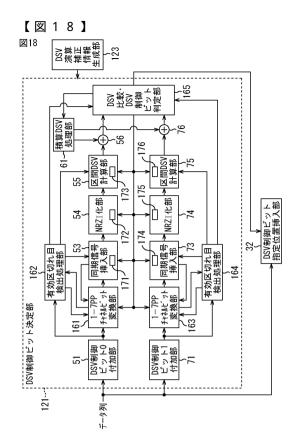

図18は、変調装置のDSV制御ビット決定部121の詳細な構成例を示すブロック図である。データ列は、DSV制御ビット決定部121に供給されるとともに、DSV制御ビット指定位置挿入部32に供給される。

# [0259]

なお、図18においては、図8における場合と応する部分には同一の符号を付してあり、 その説明は適宜省略する。

## [0260]

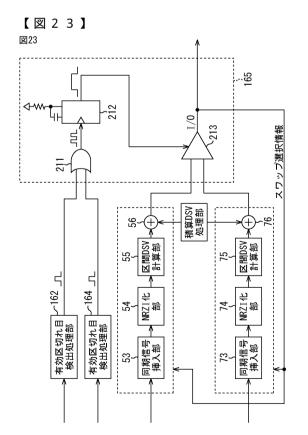

すなわち、図18のDSV制御ビット決定部121は、1-7PPデータ変換部52および72に変わって、1-7PPチャネルビット変換部161および163が設けられ、変調切れ目検出部82および有効区切れ目検出部83に変わって有効区切れ目検出処理部162が、変調切れ目検出部92および有効区切れ目検出部93に変わって有効区切れ目検出処理部164が、それぞれ設けられ、DSV制御ビット判定部62に変わって、DSV比較・DSV制御ビット判定部165が設けられている以外は、図8のDSV制御ビット決定部31と同様の構成を有するものである。

# [0261]

DSV制御ビット決定部121においては、2列のデータ変換およびDSV計算が行われており、値が「0」のDSV制御ビットを挿入されたデータ列を処理する列と、値が「1」のDSV制御ビットを挿入されたデータ列を処理する列とが、それぞれ独立に動作する。すなわち、DSV制御ビット決定部121に供給されたデータ列は、入力されたデータ列に所定の間隔

10

20

30

40

で、値が「0」のDSV制御ビットを付加するDSV制御ビット0付加部51、および、入力されたデータ列に所定の間隔で、値が「1」のDSV制御ビットを付加するDSV制御ビット1付加部71に供給される。

## [0262]

DSV制御ビット 0 付加部 5 1 により、値が「 0 」のDSV制御ビットが付加されたデータ列は、1 - 7 P P チャネルビット変換部 1 6 1 に供給される。1 - 7 P P チャネルビット変換部 1 6 1 は、データ列を格納するレジスタのほかに、チャネルビット列を格納するレジスタや、タイミング制御を行うためのレジスタを内部に有し、( d , k ; m , n ; r ) = (1 , 7 ; 2 , 3 ; 4 )のパラメータを持つ表 1 の変換テーブルを用いて、DSV制御ビットが付加されたデータ列をチャネルビット列に変換し、同期信号挿入部 5 3 に供給する。

[0263]

同期信号挿入部53は、タイミング制御を行うためのレジスタや、チャネルビット列を格納するレジスタであるレジスタ171を内部に有し、1-7PPチャネルビット変換部161から供給されたチャネルビット列の所定の位置に、変換テーブルの変換コードとして存在しないユニークなパターンを含む同期信号を挿入し、NRZI化部54に供給する。

[0264]

なお、同期信号挿入部53において、チャネルビット列に同期信号を挿入するために、1-7PPチャネルビット変換部161は、表1のtermination tableを必要に応じて用いるなどによって、データ列の任意の位置において、変換を終端させる。そして、同期信号挿入部53は、チャネルビット列の終端位置に続いて、同期信号を挿入する。

[0265]

また、チャネルビット列に同期信号を挿入した同期信号挿入部53は、挿入した同期信号の最終ビットの情報を、1-7PPチャネルビット変換部161に供給する。1-7PPチャネルビット変換部161に供給する。1-7PPチャネルビット変換部161は、必要に応じて、供給された同期信号の最終ビットの情報を参照し、表1の変換テーブルを用いて、データ列を変換する。

[0266]

NRZI化部54は、タイミング制御を行うためのレジスタや、チャネルビット列を格納するレジスタであるレジスタ172を内部に有し、同期信号挿入部53より供給された、同期信号が挿入されたチャネルビット列をNRZI化し、区間DSV計算部55に供給する。

[0267]

区間DSV計算部55は、タイミング制御を行うためのレジスタや、チャネルビット列を格納するレジスタであるレジスタ173を内部に有し、NRZI化されたチャネルビット列より、所定のDSV区間におけるDSV計算を行う。DSVは、NRZI化されたチャネルビットの値が「1」の場合「+1」とし、値が「0」の場合「-1」として演算される。演算結果としては、例えば、所定のDSV区間における最大最小ピークや、もしくは、所定のDSV区間における最終ビットのRDSなどが与えられる。この結果が加算器56に供給される。

[0268]

積算DSV処理部61は、これまでに算出されてきた区間DSVを全て加減算した積算DSVを、 予め保持している。積算DSVは、例えば、現在実行している所定のDSV区間における、その 直前のRDSである。そして、積算DSV処理部61は、所定のタイミングで、保持している積 算DSVを加算器56および加算器76に供給する。

[0269]

加算器 5 6 は、区間DSV計算部 5 5 により供給された区間DSVに、積算DSV処理部 6 1 により供給された積算DSVを加算して、新しい積算DSVを算出し、DSV比較・DSVビット判定部 1 6 5 に供給する。新しい積算DSVは、例えば、現在実行している所定のDSV区間におけるその直前のRDSと、実行中の所定のDSV区間における最終ビットのRDSとの加算結果である。

[0270]

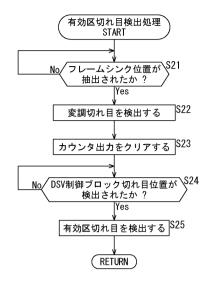

有効区切れ目検出処理部162は、供給されたデータ列から、フレームシンク(FS)位置を抽出し、変調区切れ位置およびDSV区間の切れ目位置を検出することにより、対応するDSV区間のDSV制御ビットの判定を行うタイミングを制御する有効区切れ目位置を検出し

10

20

30

40

、有効区切れ目位置を示す有効区切れ目信号を区間DSV計算部55およびDSV比較・DSVビット判定部165に供給する。

## [0271]

以上のように、入力されたデータ列に値が「 0 」のDSV制御ビットを挿入する側のシステムが構成される。また、入力されたデータ列に値が「 1 」のDSV制御ビットを挿入する側のシステムも、同様に構成される。

### [0272]

すなわち、DSV制御ビット 0 付加部 5 1 にはDSV制御ビット 1 付加部 7 1 が対応し、1 - 7 PPチャネルビット変換部 1 6 1 には 1 - 7 PPチャネルビット変換部 1 6 3 が対応し、同期信号挿入部 5 3 には同期信号挿入部 7 3 が対応し、NRZI 化部 5 4 にはNRZI 化部 7 4 が対応し、区間DSV計算部 5 5 には区間DSV計算部 7 5 が対応し、加算器 5 6 には加算器 7 6 が対応し、有効区切れ目検出処理部 1 6 2 には有効区切れ目検出処理部 1 6 4 が対応し、それぞれ、基本的に同様の処理を行う。

## [0273]

また、同期信号挿入部 7 3 には、レジスタ 1 7 4 が、NRZI 化部 7 4 には、レジスタ 1 7 5 が、区間DSV計算部 7 5 には、レジスタ 1 7 6 が、それぞれ設けられている。

### [0274]

次に、DSV制御ビット決定部位121の動作について説明する。

### [0275]

最初に、入力されたデータ列は、DSV制御ビット決定部121のDSV制御ビット0付加部5 1およびDSV制御ビット1付加部71に供給される。入力されたデータ列は、同様にして、DSV制御ビット指定位置挿入部32に供給される。

## [0276]

データ列を供給されたDSV制御ビット 0 付加部 5 1 は、データ列に、値が「 0 」のDSV制御ビットを所定の間隔で付加する。 1 - 7 P P チャネルビット変換部 1 6 1 は、DSV制御ビット 0 付加部 5 1 において値が「 0 」のDSV制御ビットを付加されたデータ列を取得し、表 1 の変換テーブルに基づいて、取得したデータ列を符号語からなるチャネルビット列に変換する。

## [0277]

また、1 - 7 PPチャネルビット変換部161は、必要に応じて、同期信号挿入部53より供給された同期信号の最終ビットに関する情報を参照し、取得したデータ列をチャネルビット列に変換する。変換されたチャネルビット列は、同期信号挿入部53に供給される。

### [0278]

変換されたチャネルビット列を供給された同期信号挿入部53は、チャネルビット列の所定の位置に所定のパターンの同期信号を挿入し、NRZI化部54に供給する。また、同期信号挿入部53は、1-7PPチャネルビット変換部161がデータ変換の際に、直前のチャネルビット列の最終ビットの値を参照できるように、挿入した同期信号の最終ビットの値に関する情報を1-7PPチャネルビット変換部161に供給する。

## [0279]

そして、NRZI化部 5 4 は、同期信号挿入部 5 3 において同期信号が挿入されたチャネルビ ・ ット列の入力を受けてNRZI化し、区間DSV計算部 5 5 に供給する。

### [0280]

また、有効区切れ目検出処理部162は、変調の切れ目位置およびDSVブロックの切れ目位置を検出することにより、有効区切れ目を検出し、区間DSV計算部55およびDSV比較・DSV制御ビット判定部165に供給する。

# [0281]

他方、データ列を供給されたDSV制御ビット1付加部71は、値が「1」のDSV制御ビットをデータ列に所定の間隔で付加する。1-7PPチャネルビット変換部163は、1-7PPチャネルビット変換部161と同様に、DSV制御ビットが付加されたデータ列をチャネルビット列に変換する。

10

20

30

40

## [0282]

また、1-7PPチャネルビット変換部163は、必要に応じて、同期信号挿入部73より 供給された同期信号の最終ビットに関する情報を参照し、取得したデータ列をチャネルビット列に変換する。変換されたチャネルビット列は、同期信号挿入部73に供給される。

## [0283]

同期信号挿入部73は、チャネルビット列の所定の位置に所定のパターンの同期信号を挿入し、NRZI化部74に供給する。また、同期信号挿入部73は、挿入した同期信号の最終ビットの値に関する情報を1-7PPチャネルビット変換部163に供給する。そして、NRZI化部74は、同期信号挿入部73において同期信号が挿入されたチャネルビット列の入力を受けて、NRZI化し、区間DSV計算部75に供給する。

### [0284]

また、有効区切れ目検出処理部164は、変調の切れ目位置およびDSVブロックの切れ目位置を検出することにより、有効区切れ目を検出し、区間DSV計算部55およびDSV比較・DSV制御ビット判定部165に供給する。

### [0285]

DSV比較・DSVビット判定部165は、加算器56から、値が「0」のDSV制御ビットを挿入されたデータ列に基づいた積算DSVの供給を受け、加算器76から、値が「1」のDSV制御ビットが挿入されたデータ列に基づいた積算DSVの供給を受ける。そして、DSV比較・DSVビット判定部165は、これら2つの積算DSVに基づいて、データ列に挿入するDSV制御ビットの値を判定する。すなわち、DSV比較・DSVビット判定部165は、例えば、両者のうち、絶対値の小さいほうのDSV制御ビットを選択する。

#### [0286]

なお、DSV比較・DSVビット判定部165によりデータ列に挿入するDSV制御ビットの値として判定された側の積算DSVは、積算DSV処理部61に供給され、積算DSV処理部61は、供給された新たな積算DSVに基づいて、保持している積算DSVを更新する。

## [0287]

DSV比較・DSVビット判定部 1 6 5 は、データ列に挿入するDSV制御ビットの値を判定すると、その判定結果をDSV制御ビット指定位置挿入部 3 2 に供給する。DSV制御ビット指定位置挿入部 3 2 は、DSV比較・DSVビット判定部 1 6 5 より供給された判定結果に基づいて、DSV制御ビットをデータ列の所定の位置に挿入し、チャネルビット生成部 1 2 2 に供給する。

# [0288]

また、DSV比較・DSVビット判定部165は、データ列に挿入するDSV制御ビットの値として判定された側を特定する情報を、1-7PPチャネルビット変換部161、同期信号挿入部53、NRZI化部54、区間DSV計算部55、1-7PPチャネルビット変換部163、同期信号挿入部73、NRZI化部74、および、区間DSV計算部75に供給し、各部が参照するレジスタの内容を必要に応じて更新させる。

## [0289]

すなわち、データ列に挿入するDSV制御ビットの値として判定された側の各部が参照したレジスタの値を、判定されなかった反対側の各部が参照したレジスタの値のそれぞれに対応させて、格納する。結局、値が「0」のDSV制御ビットを付加する側が参照する各レジスタの内容と、値が「1」のDSV制御ビットを付加する側が参照する各レジスタの内容とを、選択されたDSV制御ビット側が参照する各レジスタの値を用いて、一致させる。

### [0290]

データ列に挿入するDSV制御ビットの値を決定するDSV制御ビット決定部121は、以上のように構成される。

### [0291]

そして、DSV演算補正情報生成部123は、DSV制御ビット決定部121で決定したDSV制御ビットが挿入された、確定データ列による記録符号列もしくは伝送符号列などの出力符号列を基に、実際の累積DSVを作成し、これよりDSV演算補正情報を生成し、補正情報とし

10

20

30

てDSV制御ビット決定部121へ供給する。DSV制御ビット決定部121の積算DSV処理部61は、例えば、累積DSVが、所定の範囲内であるか否かを判定し、その判定結果によって、DSV制御ビット決定部121内の積算DSVの補正を行う。

### [0292]

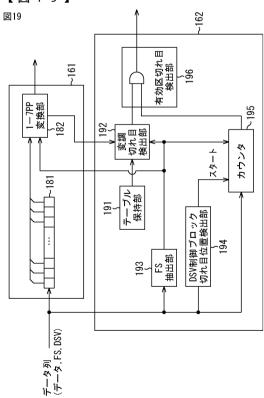

図19は、図18の1-7PPチャネルビット変換部161、および有効区切れ目検出処理部162の更に詳細な構成を示すブロック図である。また、図18の1-7PPチャネルビット変換部163は、1-7PPチャネルビット変換部161と同様の構成を有し、有効区切れ目検出処理部162と同様の構成を有しているので、その説明は省略する。

## [0293]

1 - 7PPチャネルビット変換部161のレジスタ181は、チャネルビット変換前のDSV制御ビット付きデータ列の供給を受け、図15を用いて説明したように、data [0]から順に入力され、レジスタ数字の大きいほうヘクロックごとにシフトされ、供給されたデータを蓄積する。そして、data [11]までシフトされたデータは、次のシフト時に捨てられる。1-7PP変換部182は、図16を用いて説明した場合と同様にして、レジスタ181に保持されている12ビットのデータを、表1に示すような変換テーブルの変換コードに基づいて、データ入力順の後ろ側(時間的に先に入力されたデータ、すなわち、data [10,11])から2データ毎に処理して、チャネルビットに変換する。そして、1-7P変換部182は、チャネルビット変換した情報を、変調切れ目検出部192に供給する。

### [0294]

有効区切れ目検出処理部162のFS(フレームシンク)抽出部193は、チャネルビット 変換前のDSV制御ビット付きデータ列の供給を受けて、フレームシンク位置を検出し、1 - 7PP変換部182、変調切れ目検出部192、および、カウンタ195に供給する。

### [0295]

変調切れ目検出部192は、FS抽出部193から供給される、フレームシンクの供給タイミングに基づいて、テーブル保持部191に保持されている、表1に示す変換テーブルの変換コードのうち、変調切れ目が2箇所のパターンに関する情報と、1-7PP変換部182からのチャネルビット変換情報を参照して、変調切れ目情報を生成し、有効区切れ目検出部196に供給する。

## [0296]

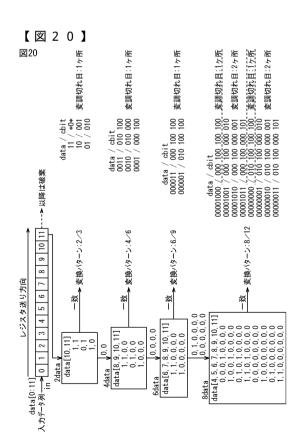

図 2 0 は、有効区切れ目検出処理部 1 6 2 または有効区切れ目検出処理部 1 6 4 の変調切れ目検出部 1 9 2 が、変調切れ目位置にフラグを立てる様子の具体例を示す図である。

## [0297]

図 2 0 において、 1 - 7 PPチャネルビット変換部 1 6 1 のレジスタ 1 8 1 のdata [ 0 : 1 1 ] の 1 2 ビットに、制御ビット付きデータ列がdata [ 0 ] から順に入力され、レジスタ数字の大きいほうへ、クロックごとにシフトされていく。そして、data [ 1 1 ] までシフトされたデータは、次のシフト時に捨てられる。また、データ列と対応するチャネルビット列との関係は、図 1 5 における場合と同様になっている。

## [0298]

なお、図15において説明したように、変調切れ目位置を示すレジスタ等の、タイミング制御を行うためのレジスタは、チャネルビット列を格納するレジスタと同数のデータを格納できるように構成されており、互いに同じ位置が対応されている。また、これらタイミング制御のためのレジスタには、例えばアクティブ時において「1」が格納され、それ以外の位置には「0」が格納される。

# [0299]

データ列は、データ入力順において後ろ側(時間的に先に入力されたデータ、すなわち、data [ 1 0 , 1 1 ] から)から 2 データ毎に処理される。data [ 1 0 , 1 1 ] が、 [ 1 , 1 ] 、 [ 0 , 1 ] 、または、 [ 1 , 0 ] である場合、 ( 1 1 ) 、 ( 1 0 ) 、または ( 0 1 ) を検出した 1 - 7 P P 変換部 1 8 2 は、表 1 の変換テーブルに基づいて、変換パターン

10

20

30

40

を確定し、内部に有するチャネルビット変換後のデータを保持するレジスタのcbit [ 1 5 , 1 6 , 1 7 ] に、変換されたチャネルビット列を格納する。そして変調切れ目検出部 1 9 2 は、1 - 7 P P 変換部 1 8 2 からの変換チャネルビット情報と、テーブル保持部 1 9 1 に保持されている情報に基づいて、変調切れ目位置として、図 1 5 を用いて説明した 1 8 ビットのチャネルビットレジスタと同様に構成された、タイミング制御用の内部のレジスタのcbit [ 1 7 ] と同じ位置に「1 」を格納する。

[0300]

data [ 1 0 , 1 1 ] = [ 0 , 0 ] の場合、1 - 7 P P 変換部 1 8 2 は、拘束長i = 1 において変換パターンを確定しない。従って、1 - 7 P P 変換部 1 8 2 は、さらに、data [ 8 , 9 , 1 0 , 1 1 ] を参照する。

[0301]

そして、data [8,9,10,11]が、[1,1,0,0]、[0,1,0,0]、または、[1,0,0,0]である場合、(0011)、(0010)、または(0001)を検出した1-7PP変換部182は、表1の変換テーブルに基づいて、変換パターンを確定し、内部に有するチャネルビット変換後のデータを保持するレジスタのcbit [12,13,14,15,16,17]に、変換されたチャネルビット列を格納する。そして、変調切れ目検出部192は、1-7PP変換部182からの変換チャネルビット情報と、テーブル保持部191に保持されている情報に基づいて、変調切れ目位置として、内部のレジスタのcbit [17]と同じ位置に「1」を格納する。

[0302]

data [ 8 , 9 , 1 0 , 1 1 ] = [ 0 , 0 , 0 , 0 ] の場合、 1 - 7 P P 変換部 1 8 2 は、拘束長 i = 2 において変換パターンを確定しない。従って、 1 - 7 P P 変換部 1 8 2 は、さらに、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] を参照する。

[0303]

そして、data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] が、 [ 1 , 1 , 0 , 0 , 0 , 0 , 0 ] 、または、 [ 1 , 0 , 0 , 0 , 0 , 0 ] である場合、 ( 0 0 0 0 1 1 ) 、または ( 0 0 0 0 0 1 1 ) を検出した 1 - 7 P P 変換部 1 8 2 は、表 1 の変換テーブルに基づいて、変換パターンを確定し、内部に有するチャネルビット変換後のデータを保持するレジスタのcbit [ 9 , 1 0 , 1 1 , 1 2 , 1 3 , 1 4 , 1 5 , 1 6 , 1 7 ] に、変換されたチャネルビット列を格納する。そして、変調切れ目検出部 1 9 2 は、 1 - 7 P P 変換部 1 8 2 からの変換チャネルビット情報と、テーブル保持部 1 9 1 に保持されている情報に基づいて、変調切れ目位置として、内部のレジスタのcbit [ 1 7 ] と同じ位置に「1」を格納する。

[0304]

data [ 6 , 7 , 8 , 9 , 1 0 , 1 1 ] が、 [ 0 , 0 , 0 , 0 , 0 , 0 ]、または、 [ 0 , 1 , 0 , 0 , 0 , 0 ] の場合、 1 - 7 P P 変換部 1 8 2 は、拘束長 i = 3 において変換パターンを確定しない。従って、 1 - 7 P P 変換部 1 8 2 は、さらに、data [ 4 , 5 , 6 , 7 , 8 , 9 , 1 0 , 1 1 ] を参照し、上述したように、表 1 の変換テーブルに基づいて、変換パターンを確定する。

[0305]

[0306]

10

20

30

40

10

20

30

40

50

また、data [ 4 , 5 , 6 , 7 , 8 , 9 , 1 0 , 1 1 ] が、 [ 0 , 0 , 0 , 1 , 0 , 0 , 0 , 0 , 0 , 0 ]、 [ 1 , 0 , 0 , 1 , 0 , 0 , 0 , 0 ]、 [ 0 , 1 , 0 , 1 , 0 , 0 , 0 , 0 ]、 または、 [ 1 , 1 , 0 , 1 , 0 , 0 , 0 , 0 ] である場合、 ( 0 0 0 0 1 0 0 0 )、 ( 0 0 0 0 1 0 0 1 )、 ( 0 0 0 0 1 0 1 0 1 0 )、 または、 ( 0 0 0 0 1 0 1 1 ) を検出した 1 - 7 P P 変換部 1 8 2 は、表 1 の変換テーブルに基づいて、 変換パターンを確定し、 内部に有するチャネルビット変換後のデータを保持するレジスタのcbit [ 6 , 7 , 8 , 9 , 1 0 , 1 1 , 1 2 , 1 3 , 1 4 , 1 5 , 1 6 , 1 7 ] に、 変換されたチャネルビット列を格納する。 そして、 変調切れ目検出部 1 9 2 は、 1 - 7 P P 変換部 1 8 2 からの変換チャネルビット情報と、 テーブル保持部 1 9 1 に保持されている情報に基づいて、 変調切れ目位置として、 内部のレジスタの所定の位置に「 1 」を格納する。

[0307]

変調切れ目検出部 1 9 2 は、具体的には、例えば、data [ 4 , 5 , 6 , 7 , 8 , 9 , 1 0 , 1 1 ] に対応するチャネルビット列が、 [ 0 , 0 , 0 , 0 , 0 , 0 , 0 ] または [ 0 , 0 , 0 , 1 , 0 , 0 , 0 ] を変換したものであった場合、変調切れ目位置として、内部のレジスタのcbit [ 1 7 ] と同じ位置に「1」を格納する。

[0308]

また、変調切れ目検出部192は、data[4,5,6,7,8,9,10,11]に対応するチャネルビット列が、[1,0,0,1,0,0,0,0,0]、[0,1,0,1,0,0,0,0,0,0]、[1,1,0,0,0,0,0]、[0,1,0,0,0,0,0]、または、[1,1,0,0,0,0,0]を変換したものであった場合、変調切れ目位置は2箇所であり、変調切れ目位置として、内部のレジスタの、cbit[17]およびcbit[8]と同じ位置に「1」を格納する

[0309]

なお、表 1 においては、上述したパターン以外にtermination tableにおける変換パターンが存在するが、これらのパターンにおける動作についても、基本的に上記と同様である。すなわち、表 1 のtermination tableと一致した上で、さらに同期信号の挿入される位置が検出された場合、変換パターンが確定される。この場合の変調切れ目位置については、それぞれ変換されたチャネルビットに対して 1 箇所に与えられる。

[ 0 3 1 0 ]

さらに、表 1 においては、最小ラン連続制限を行う変換パターンが存在するが、これらの動作についても、基本的に上記と同様である。すなわち、最小ラン連続制限コードを用いて変換が行われた場合、変調切れ目位置は、変換された 9 チャネルビットに対して 1 箇所に与えられる。

[0311]

以上のように、入力データ列から、チャネルビット列へ、全てのパターン変換が行われ、変調切れ目情報が与えられる。そして、次のパターン変換は、パターンが確定し、変調切れ目情報が発生した後、再度、拘束長i = 1 から始まり、上述したような動作を繰り返す。このとき、チャネルビット列および変調切れ目情報は、変換処理が完了したのち、図15を用いて説明した18ビットのチャネルビットレジスタから出力され、変換済みのチャネルビット列が、図18の同期信号挿入部53に供給され、変調切れ目情報が、有効区切れ目196に供給される。

[0312]

ところで、これら変調切れ目位置を示すレジスタは、上記の例だけに限らず、それぞれの 変換において、変調の切れ目位置を示すことが出来ればよい。

[0313]

また同様に、図20のような変換処理についても、上記の例だけに限らず、例えば拘束長 iの大きい方から処理するなど、表1に基づくデータ変換が出来ればよい。

[0314]

ところで、この例においては、入力データ列に対する発生符号語列のデータ変換率m:n

は2:3とされているので、符号語のデータ量3に対して、データ語のデータ量は2となる。従って、2クロックの間に所定の2データ語だけが入力され、その後、1クロック分の入力が停止されることにより、入力データと出力符号との変換率に関するずれが調整される。この関係は、図21、図22、および、後述する図24のデータ列、チャネルビット列において示されている。

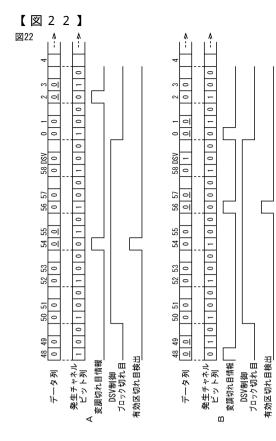

## [0315]

図 2 1 は、図 1 9 の変調切れ目検出部 1 9 2 から出力される変調切れ目の検出の様子を示す図である。図 2 1 において、左から右に時間が経過しており、データ列は、左から順にレジスタに入力され、チャネルビット列に変換されている。

## [0316]

図21Aに示されるように、2ビットのデータ列(11)は、1-7PP変換部182において、"101"に変換されており、変調切れ目検出部192において、"101"の時間的に前方、すなわち、先頭側の"1"で変調切れ目が検出されて、変調切れ目検出結果用のレジスタの対応する位置に、「1」が格納される。

### [0317]

次に、8ビットのデータ列(00000000)は、1-7PP変換部182において、 "010100100100"に変換されており、変調切れ目検出部192において、 "010100100100"の先頭側の "0"で変調切れ目が検出されて、変調切れ目検出結果用のレジスタの対応する位置に「1」が格納される。

## [0318]

同様に、4ビットのデータ列(0011)は、1-7PP変換部182において、"010100"に変換されており、変調切れ目検出部192において、"01010100"の先頭側の"0"で変調切れ目が検出されて、変調切れ目検出結果用のレジスタの対応する位置に「1」が格納される。

### [0319]

同様に、図21Bに示されるように、2ビットのデータ列(11)は、1-7PP変換部182において、"101"に変換されており、変調切れ目検出部192において、"101"の時間的に前方、すなわち、先頭側の"1"で変調切れ目が検出されて、変調切れ目検出結果用のレジスタの対応する位置に「1」が格納される。

## [0320]

次に、8ビットのデータ列(0000001)は、1-7PP変換部182において、 "01010000010"に変換されており、変調切れ目検出部192において、" 01010000010"の先頭側の"0"および右から3番目の"0" で変調切れ 目が検出されて、変調切れ目検出結果用のレジスタの対応する位置に「1」が格納される

### [0321]

同様に、4ビットのデータ列(0011)は、1-7PP変換部182において、"010100"に変換されており、変調切れ目検出部192において、"010100"の先頭側の"0"で変調切れ目が検出されて、変調切れ目検出結果用のレジスタの対応する位置に「1」が格納される。

# [0322]

以上のように、拘束長i = 4 における変換のパターンにより、変調切れ目の個数が変化する。

# [0323]

なお、変調切れ目検出部192において、拘束長i=4、すなわち、8データにおけるパターン変換時の変調切れ目位置を、前方の1ヶ所に統一して、これを変調切れ目信号として出力しても、DSV制御ビット決定部121は動作することができる。この場合、上述した方式とは、区間DSV計算結果に差異が生じることになる。有効区切れ目検出処理部162および有効区切れ目検出処理部164の変調切れ目検出部192は、図21Aおよび図21Bに示されるようにして、変調切れ目信号を制御する。

10

20

30

40

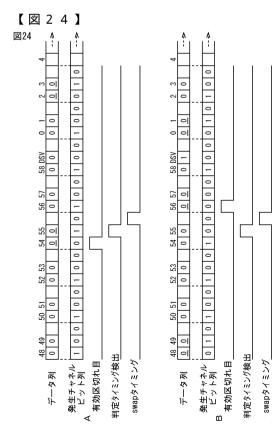

### [0324]

変調切れ目検出部 1 9 2 により生成された変調切れ目信号は、有効区切れ目検出部 1 9 6 に供給される。

## [0325]

DSV制御ブロック切れ目位置検出部 1 9 4 は、チャネルビット変換前のDSV制御ビット付きデータ列の供給を受けて、DSV区間の切れ目位置に関する情報を、カウンタ 1 9 5 に供給する。

## [0326]

カウンタ195は、チャネルビット変換前のDSV制御ビット付きデータ列の供給を受けるとともに、FS抽出部193からフレームシンク位置の抽出信号を受け、DSV制御ブロック切れ目位置検出部194により供給されたDSV区間切れ目信号に基づいてDSV制御ブロック切れ目信号を生成し、有効区切れ目検出部196に供給する。

### [0327]

変調切れ目信号、および、DSV制御ブロック切れ目信号を供給された有効区切れ目検出部 1 9 6 は、有効区切れ目位置を検出し、区間DSV計算部 5 5 およびDSV比較・DSVビット判定部 1 6 5 に供給する。

## [0328]