Feb. 1, 1966

## J. F. FOSTER ETAL

3,233,224

Feb. 1, 1966

3,233,224

Feb. 1, 1966

DATA PROCESSING SYSTEM

Feb. 1, 1966

## J. F. FOSTER ETAL

3,233,224

DATA PROCESSING SYSTEM

DATA PROCESSING SYSTEM

Feb. 1, 1966

3,233,224

DATA PROCESSING SYSTEM

48 XILSI93X XILIA 01

1

#### 3,233,224

## DATA PROCESSING SYSTEM

Jerry Flickwir Foster, Arcadia, Lawrence Le Roy Bewley, Covina, and James Russell Bennett, Glendora, Calif., 5 and Edward L. Glaser, Newton Square, Pa., assignors to Burroughs Corporation, Detroit, Mich., a corporation of Michigan Filed Sent. 15, 1960. Ser. No. 56, 164

Filed Sept. 15, 1960, Ser. No. 56,164 12 Claims. (Cl. 340-172.5)

This invention relates to digital computer systems and more particularly to high speed data processing systems.

Printing units have been used with data processors in which the information to be printed out is first edited by 15 the data processors. One example is in a banking system in which signals representing dollar signs, credit symbols, blanks to be left on the page, etc. are inserted in among other data signals by the data processor prior to being shifted out by the data processor to a printing unit 20 for printing. Typically, such an arrangement requires that a data processor waste valuable time in manipulating and editing data. Further, data processors are becoming much faster than the printing units which requires that the data processor do the editing operation and then 25 wait for the slower speed printing unit to finish a printing cycle before shifting the edited data signals out to the printing unit. Not only is time wasted by the data processor but also valuable storage space is consumed by the program needed by the data processor to perform the 30 editing operations.

In order to bring about a system balance and relieve the data processor of this data manipulation, a complete off-line editing system has been used. Such an editing system usually comprises a memory unit for storing data 35 prior to being edited, a buffer register in which the editing operations take place and a timing unit for controlling the sequence of operations during the editing operation. A programing unit is provided for determining the sequence with which data signals are taken from the 40memory unit and for determining when other data signals not stored in the memory unit are to be inserted among the data signals stored in the memory unit or when data signals in the memory unit are to be converted to other data signals. Since the program may vary con- 45 siderably depending on the desired editing, it is desirable to have a programing unit in which the program is easily changed. To this end plugboards have been used in which each step in the program is wired into the plug-50 board. Such a printing unit is then provided and coupled to the memory unit for receiving and printing out the edited data. Such an arrangement is generally undesirable since programs are long and it requires a great deal of equipment and time to wire each step of the pro-55gram into the plugboards. Furthermore, it results in a mass of unwieldy plug wires. Such plugboard program units are shown and described in the book entitled Arithmetic Operations in Digital Computers, written by R. K. Richards and published by the D. Van Nostrand Com-60 pany, Inc., on pages 320 to 326.

In contrast, the present invention provides an editing system utilizing programing by "exception" wherein the need for special print tapes is eliminated and the programer of the editing system is allowed to arrange information as desired for printing regardless of tape format. The invention provides for selective and conditional conversion which allows the programer to examine information and to convert it to other information. Insertions are also easily made. All these features are provided with the additional feature of a plugboard stored programing unit in which the wiring needed for programing is greatly reduced over that of previously existing editing systems.

An embodiment of the present invention provides an editing system for receiving data signals from a source of 5 input signals such as a data processor and a tape unit, for editing the data signals and providing edited output signals for printing out by a printing unit. The editing system comprises a memory unit in which the input information is stored and a buffer register utilized for mak-10 ing insertions and conversions and for providing output signals to a print control and storage unit.

A programing unit including a counting circuit is connected to the memory unit and normally counts through a predetermined sequence of states. A program plugboard unit is provided in the programing unit having exit and entry hubs, or electrical connectors. Gating circuits couple output circuits of the counting circuit to the exit hubs for providing an output signal at the exit hubs corresponding to each state of the counting circuit. The entry hubs are connected through counter skip control circuits to input circuits of the counting circuit ships intermediate steps to a state corresponding to the hub energized.

The counting circuit normally counts through a predetermined sequence of states addressing memory locations in the memory unit in a prescribed order corresponding to each state of the counting circuit to thereby cause the stored information in the memory unit to be shifted into the buffer register.

One form of editing is the rearranging of information prior to being entered into the buffer register. This is accomplished by interconnecting the exit hubs and the entry hubs to thereby cause the counter circuit to skip states. Thus, if the exit hub rendering an output signal at state five of the counter circuit is connected to an entry hub corresponding to a state ten input circuit of the counting circuit, the counting circuit will step from state five to ten rather than the normal step to state six, etc. Thus the programing unit comprises a novel circuit arrangement for operating according to programing by "exception" wherein the programing unit normally sequentially and continually steps through a predetermined sequence of steps. A modification of this sequence arises whenever the machine is programed to "except" this predetermined sequence. Such an arrangement allows data stored in the memory unit to be shifted into the buffer register, then to the printing unit, unaltered and automatically without the need of programing or wiring the plugboards. If the sequence with which information is read out of the memory unit is to be altered, it is done simply by inserting a wire between the appropriate exit and entry hubs on the plugboard. Whenever the sequential operation of the counting circuit is altered in response to the programed "exception," the intermediate steps are skipped and the counting circuit picks up at the programed new state and continues sequentially on from that point until another "exception" is programed or wired in.

A timing circuit is also provided for providing timing to the editing system. Two more sets of entry hubs or electrical connectors are provided which cooperate with the timing unit to provide another form of programing by "exception." In this form, programing by "exception" allows other data signals to be inserted into data signals stored in the memory unit and to be printed out. It also allows data signals stored in the buffer register to be conditionally converted to other data signals. Thus, whenever data signals representing characters such as a dollar sign, a blank, etc., are to be inserted in the data signals to be printed out, a wire is connected between the -5

15

20

30

appropriate exit hub and hubs on an insert or conversion plugboard which causes the program to appropriately alter the normal sequence and insert or convert the signals.

A better understanding of the present invention may be had with reference to the following detailed description and the figures in which:

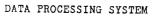

FIG. 1 is a block diagram of an input unit, editing system and a printing and storage unit embodying the present invention;

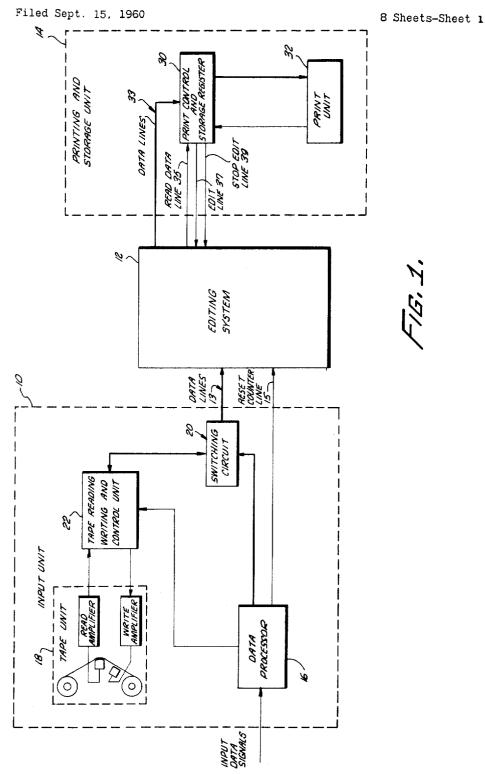

FIG. 2 is a general block diagram of the editing system 10 of FIG. 1 and embodying the present invention;

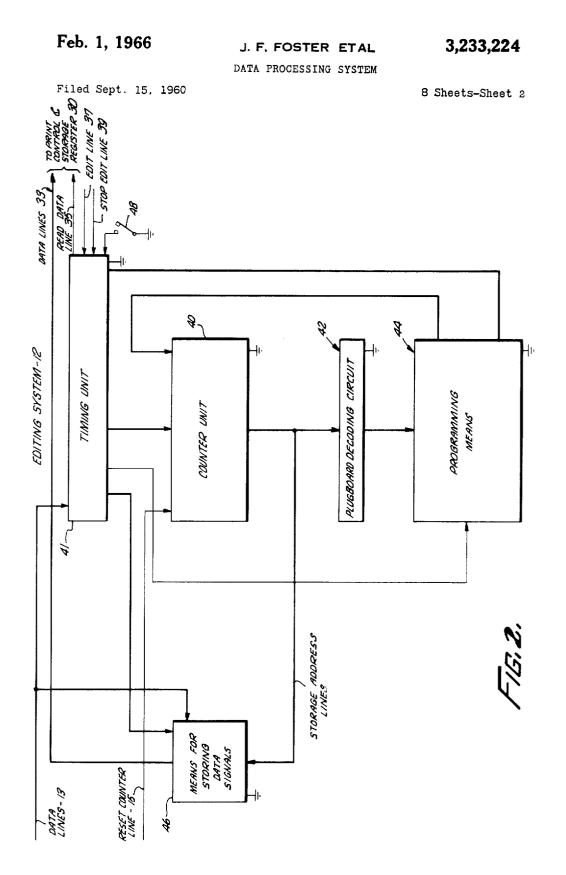

FIG. 3 is a specific schematic diagram, partly in block form, of a form of the editing system shown in FIG. 2;

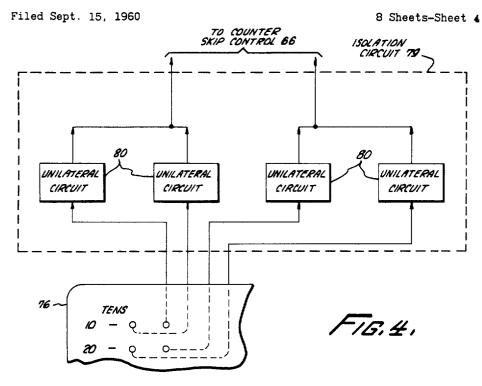

FIG. 4 is a block diagram of an isolation circuit for use in the editing system of FIG. 3;

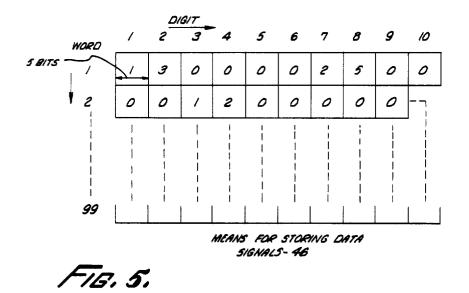

FIG. 5 is an illustrative drawing of storage locations in the means for storing data signals of FIGS. 3 and 13 with the contents thereof shown;

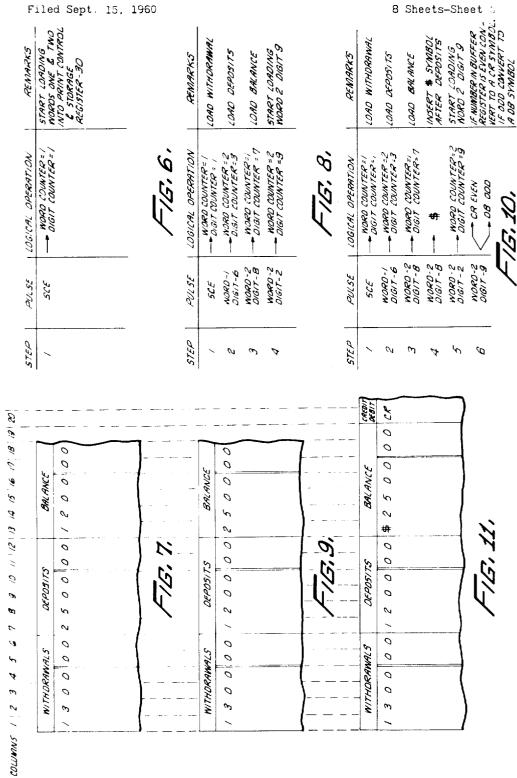

FIG. 6 is a typical written program, without any programed "exceptions" for the system of FIGS. 2 and 3.

FIG. 7 is a portion of a typical bank statement shown with the contents of the means for storing data signals shown in FIG. 5 printed out, without programed "exceptions," according to the program shown in FIG. 6;

"exceptions" for rearranging the stored data signals;

FIG. 9 is a portion of a typical bank statement shown with the contents of the means for storing data signals rearranged and printed out according to the program shown in FIG. 8;

FIG. 10 is a typical written program for rearranging, inserting and converting signals utilizing programing by "exception";

FIG. 11 is a portion of a typical bank statement with the contents of the means for storing data signals edited 35by the program shown in FIG. 10;

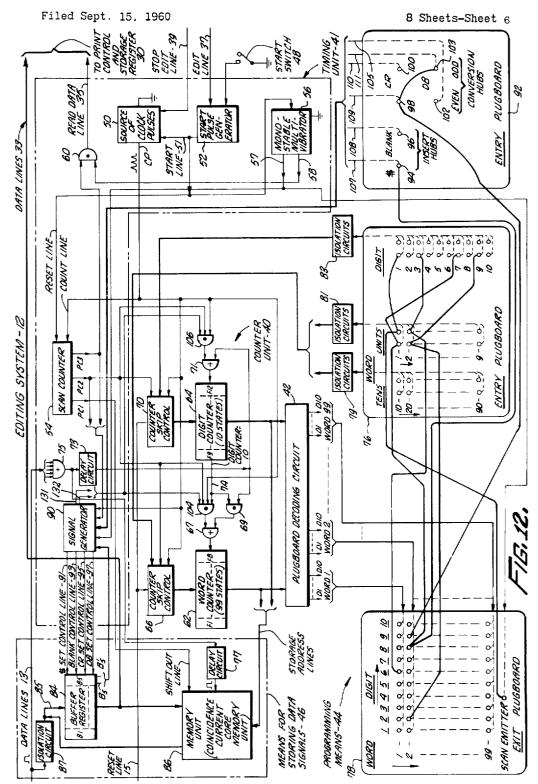

FIG. 12 is another specific schematic diagram partly in block form, of an editing system utilizing programing by "exception" and embodying the present invention;

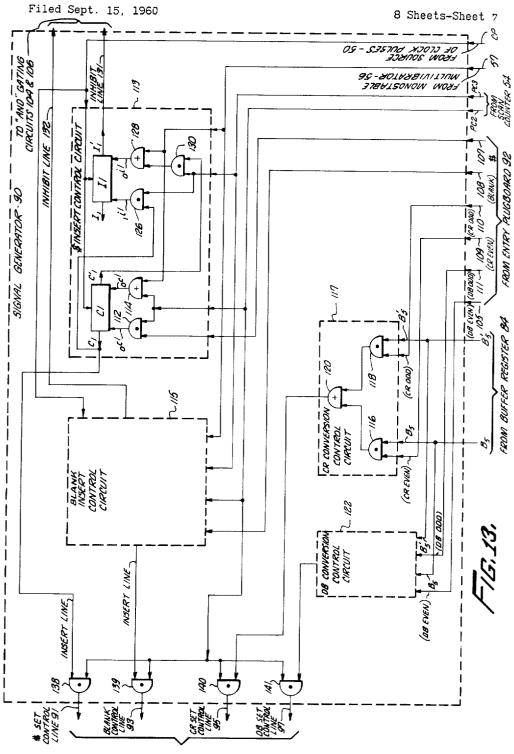

40FIG. 13 is a signal generator for use in the editing system of FIG. 12; and

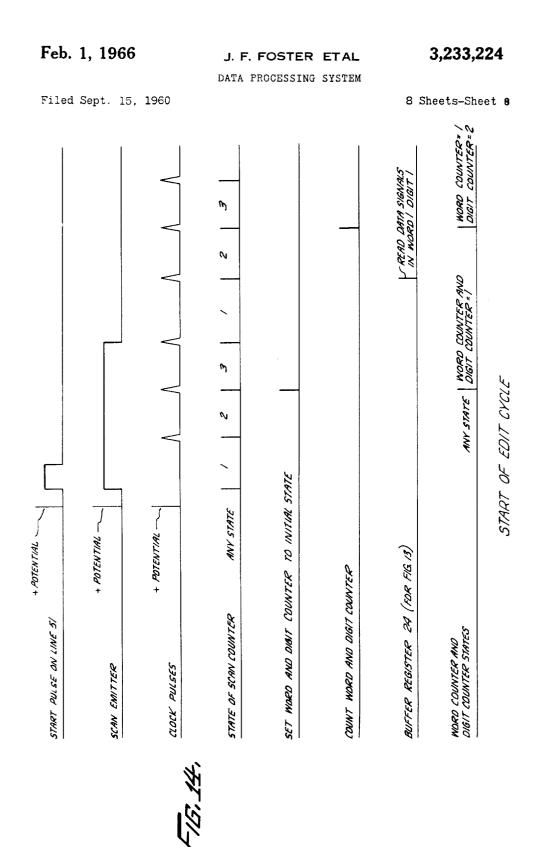

FIG. 14 is a wave shape and timing diagram of signals at designated points of the editing systems of FIGS. 3 and 12, during the beginning of the edit cycle.

Referring now to the drawings and to FIG. 1 in par- 45 ticular, an input unit 10 is shown for providing data and control signals to an editing system 12. The editing system 12 has a novel circuit arrangement for editing data signals supplied by the input unit 10 and for providing edited data signals to a printing and storage unit 14, 50 which then prints out characters represented by the edited data signals, on paper.

It should be noted that in the drawings the cables comprising a number of electrical lines or conductors are shown in heavy lines in order to distinguish them from 55 a single electrical conductor or line.

The input unit 10 comprises a data processor 16 which may receive input data signals from punched paper tape, punched cards, magnetic tape, etc., and then perform predetermined calculations on the input data signals. After 60 applied to the input circuit of the plugboard decoding the calculations are performed the data processor 16 provides coded output data signals, in groups of five bits, which may either be shifted directly to the editing system 12 for a line operation of the printer 14 or shifted through a tape reading, writing and control circuit 22 onto tape 65 in a tape unit 18 for off-line operation. Each group of five bits of data signals represent a character such as a number or a letter. After the groups of data signals are stored on the tape in the tape unit 18, they may be shifted out to the editing system 12 at a later time. The connec-70tions between the data processor 16, the tape unit 18 and the editing system 12 are made through a switching circuit 20. The operations of the switching circuit 29 and the tape reading, writing and control unit 22 are controlled by the data processor 16.

Data lines 13 and a reset counter line 15 connect output circuits of the data processor 16 to input circuits of the editing data system 12. It is on the data lines 13 that the groups of data signals from the tape unit 18 and the data processor 16 are applied by the switching circuit 20.

The editing system 12 has output circuits connected to input circuits of the printing and storage unit 14, by data lines 33 and a read data line 35. Also output circuits of the printing and storage unit 16 are connected to input circuits of the editing system 12 by an edit line 37 and a stop edit line 39. After the groups of data signals have been transferred from the input unit 10 to the editing system 12, the editing system 12 is then switched into an edit cycle either by a high potential signal on the edit line 39 or by actuating a switch in the editing system, as will be explained more fully hereinafter. During the edit cycle the groups of data signals stored in the editing system 12 are edited by "exception" in a novel circuit arrangement utilizing a stored program. After a group of data signals is edited the signals are applied to the data lines 33 for reading by the printing and storage unit 14.

The printing and storage unit 14 has a print control and storage register 30, which is connected to a print unit The print control and storage register 30 has a stor-32. FIG. 8 is a typical written program including programed 25 age register (not shown) responsive to a high potential signal on the read data lines 35 to read and store the group of edited data signals applied to the data lines 33 by the editing system 12. When enough groups of data signals are read by the storage register in the print control and storage register 30 to fill it, the print control and storage register 30 applies a high potential signal to the stop The editing system 12 is responsive to the edit line 39. high potential signal on the stop edit line 39 to stop editing the groups of data signals and applying them to the data lines 33. After the high potential signal is applied to the stop edit line 39, the printing and storage unit 14 goes into a printing cycle during which the characters, represented by the groups of data signals stored in the print control and storage register 30, are printed out by the print unit 32. It should be noted that the order in which the groups of data signals are shifted into the print control and storage register 30 is the order in which the characters, represented by the groups of data signals, will be printed out by the print unit 32.

FIG. 2 is a general block diagram of an editing system 12 useful for describing the general operation of the invention.

A counter unit 40 is provided having input circuits connected to output circuits of a timing unit 41 and a programing means 44. The output circuits of the counter unit 40 are connected to input circuits of a plug board decoding circuit 42 and a means for storing data signals 47. The counter unit 40 is responsive to a high potential signal on the reset counter line 15 to be reset to an initial state. The counter unit 40 is also responsive to timing pulses from the timing unit 41 to count through sequential states of operation. For each state of operation the counter unit 40 develops a digital binary coded output signal characteristic of its operating state which is circuit 42 and the input circuit of the means for storing data signals 46.

The plugboard decoding circuit 42 has an output circuit with a plurality of output lines which are connected to an input circuit of a programing means 44. The plugboard decoding circuit 42 is responsive to each binary coded output signal of the counter unit 40 to provide a unique digital signal on one out of its plurality of output lines corresponding to the operating state of the counter 40.

The means for storing data signals 46 has other input circuits connected to the data lines 13, and the timing unit 41. An output circuit of means for storing data signals is connected to the data lines 33, which are connected to the print control and storage register 30. The 75 means for storing data signals 46 contains a plurality of

storage locations, each arranged for storing five bits of binary coded information and therefore one group of data signals applied to the line 13.

The means for storing data signals 46 is responsive to a predetermined signal from the timing unit 41 to store 5 a group of data signals applied to the line 13. The storage location in which the group of data signals are to be stored is specified by address signals from the counter unit 40. The means for storing data signals 46 is also responsive to another output signal of the timing unit 41 for 10 shifting out signals from the storage location specified by the address signals from the counter unit 40, and to apply the group of data signals to the data line 33. When a group of data signals is shifted from the input unit 10 and stored in the editing system 12, called the load cycle, 15 this group of data signals is first applied to the data lines 13. Simultaneously, digital coded address signals are applied to the means for storing data signals, by the counter unit 40, corresponding to a storage location in the means for storing data signals 46 where the group of data signals is to be stored. The timing unit 41 then provides a signal to the means for storing data signals 46 causing it to store the group of data signals on the lines 13 in the addressed storage location. The means for storing data signals 45 is also responsive to a predetermined timing 25 signal from the timing unit 41 to shift out a group of data signals from a storage location, specified by the address signals from the counter unit 40 and to apply this group of data signals to the data lines 33.

The timing unit 41 has input circuits connected to the 30 edit line 37, the stop edit line 39, the data lines 13, the programing means 44 and through the normally open contacts of a switch 48 to ground (0 volt) potential. An output circuit of the timing unit 41 is also connected to the read data line 33, which is connected to an input cir- 35 cuit of the print control and storage register 30 and the programing means 44.

Consider now the operation of the editing system 12 with the programing means 44 removed from the circuit. During the load cycle a high potential signal is first ap- 40 plied to the reset counter line 15, which causes the counter to be set to its initial state. The first group of data signals applied to the data lines 13 cause the timing unit 41 to develop a predetermined signal at the input circuit of the means for storing data signals 46. This signal causes the group of data signals, on the data lines 45 13, to be read and stored in the storage location specified by the address signals from the counter unit 40. The timing unit 41 then counts the counter unit 40 up one state from the last state. Thus each time a new group of data signals are stored in the counter unit 40, it counts 50 up one state, and the storage locations in the means for storing data signals 46 are provided with groups of data signals for storage in a prescribed order. This continues until all storage locations in the means for storing data signals 46 have been filled.

Assume now that it is desired to switch the editing system 12 into an edit cycle. The switch 48 is actuated causing the timing unit 41 to start providing timing pulses to the counter unit 40. Responsive to the timing pulses, the counter unit 49 sequentially counts through a pre- 60 determined sequence of states. In each state of the counter unit 40 an address signal is provided to the means for storing data signals 46. The timing unit 41 also provides a timing pulse to the means for storing data signals 46 which causes it to provide a group of data signals on 65 the data lines 33 from the addressed storage location.

The programing means 44 may be an electrically controlled storage unit such as a core memory unit or a diode matrix. However, in a preferred embodiment the programing means 44 comprises a plurality of plugboards having hubs or electrical connectors for interconnecting lead wires to provide the stored program. The programing means 44 is programed to be responsive to predetermined signals from the plugboard decoding circuit 42 to provide output signals to the counter unit 40 75

and the timing unit 41. The timing unit 41 is responsive to the output signals of the programing means 44 to introduce "exceptions" into the above sequential operation of the editing system 12.

One "exception" which is introduced by the programing means 44 is the rearrangement of a group or groups of data signals in the means for storing data signals 46 during the editing cycle. When programed for this "exception," the programing means 44 is responsive to a programed output signal of plugboard decoding circuit 42 to provide a timing signal to the input circuit of the counter unit 40. Whenever the programing means 44 provides this timing signal to the input of the counter unit 40, the counter unit 40 does not go to its next sequential state of operation but jumps to a state corresponding to the output signal from the programing means 44. This not only causes the counter unit 40 to skip intermediate states but to skip data signals in intermediate storage locations of the means for storing data signals 46. This allows the sequence of data signals stored in the means for storing data signals 46 to be rearranged and shifted out to the print control and storage register 30 in any desired sequence. It should be noted that such a program arrangement allows the beginning of groups of data signals to be selected, then, without further programing the editing system 12 sequentially shifts these the groups of data. When the end of the groups is reached another "exception" may be introduced, similar to that described above, and cause the beginning of still other groups of data signals to be selected and then shifted out to the print control and storage register 30. Whenever data signals are applied to the data lines 33, which are to be read and stored by the print control and storage register 30, the timing unit 41 provides a high potential output signal on the read data line 35.

Another "exception" which is introduced by the programing means 44 is the insertion of a group of data signals representing a character. This is done by inserting the desired group of data signals in between other groups of data signals as they are shifted out to the print control and storage register 30. Usually the groups of data signals stored in the means for storing data signals 46 contain signals representing numbers and alphanumeric characters but are normally absent such characters as dollar signs, periods, commas, etc., and are absent signals for causing the print unit 32 to skip spaces in between words. By "exception" groups of data signals representing the above characters and spaces are introduced into the groups of data signals as shifted out to the print control and storage register 30.

Consider now the operation of the editing system 12 when an insert by "exception" is to be made. First a predetermined program is stored in the programing means 44. The program is arranged so that the programing means 44 will develop on insert output signal to the tim-55 ing unit 41 when the state of the counter unit 40 corresponds to the storage location in the means for storing data signals 46 which contains the group of data signals to be shifted out just prior to the group of data signals to be inserted. This causes the timing unit 41 to stop the counting of the counter unit 40 and causes the timing unit 41 to provide an insert signal to the means for storing data signals 46. The insert signal causes the means for storing data signals 46 to develop a group of data signals on the data lines 33 corresponding to the character to be inserted. The timing unit 41 then develops a high potential output signal on the read data line 35 to cause the print control and storage register 30 to read the inserted group of data signals applied on the data lines 33. After the group of data signals is inserted and the timing unit 41 causes the next group of data signals to be shifted out and causes the counter unit 40 to start counting, the counter unit 40 then sequentially continues its counting operations until another 'exception" is introduced by the stored program. Another "exception" which may be introduced by

Б

the programing means 44 is the conversion of a group of data signals to another group of data signals. Normally a group of data signals stored in the means for storing data signals 46 is shifted out and applied unaltered to the data lines 33 for reading by the print control and storage register 30. However, by the introduction of a predetermined program in the programing means 44 data signals stored in the means for storing data signals may be converted to other characters such as a "CR" symbol or a "DB" symbol. Conversion by "exception" 10 may also be done conditionally, that is, the group of data signals corresponding to the character to be converted may be conditionally converted to groups of data symbols representing another character. The condition may be, for example, whether the group of data signals 15 to be converted is even or odd.

Consider now the operation of the editing system 12 when the programing means 44 is programed to convert by "exception." The counting unit 40 normally sequentially counts through its states of operation causing 20 56 stays in a true state of operation for the length of groups of data signals to be shifted out and applied to the data lines 33. When the counter unit 40 is in the state representing the storage location of the group of data signals to be converted, the stored conversion program causes a conversion signal to be applied to the 25 timing unit 41. If the group of data signals in the addressed storage location meet the condition. i.e. odd or even, the timing unit 41 applies a convert signal to the means for storing data signals 46. This causes the means for storing data signals 46 to convert the ad- 30 dressed group of data signals to the desired group of data signals and apply them to the data lines 33.

With the general description of FIG. 2 in mind, a detailed description will be given of the editing system 12 shown in FIG. 3 wherein the "exception" of rearrang-35 ing the groups of data data signals stored in the means for storing data signals 46 is shown and described.

The timing unit 41 comprises a source of clock pulses 50, which provides timing pulses for synchronizing the operation of the editing system 12. The source of clock 40pulses 50 has two input circuits one of which is connected to a start line 51 while the other input circuit is connected to the stop edit line 39. The source of clock pulses 50 also has an output circuit designated CP. The source of clock pulses 50 is always responsive to a high potential 45 signal on the start line 51 to begin developing high potential, recurring pulses of potential at the output circuit CP. These pulses of potential will be referred to as clock pulses. The source of clock pulses 25 is also responsive to a high potential signal on the stop edit line 39 to immediately stop developing the clock pulses at the output circuit CP.

A start pulse generator 52 is also provided in the timing unit 41 and has two input circuits which are connected to the edit line 37, and to the normally open edit switch 48. The start pulse generator 52 has an output circuit connected to the start line 51 and develops a single high potential pulse of potential at its output circuit whenever the normally open edit switch 48 is actuated or a high potential signal is applied to the edit line 37.

The timing unit 41 also comprises a scan counter 54. The scan counter 54 has two input circuits, one of which is connected to the CP output circuit of the source of clock pulses 50 and the other one is connected to the start line 51. The scan counter 54 has three output circuits designated by the symbols PC1, PC2 and PC3. The scan counter 54 has three states of operation called states one, two and three during which high potential output signals are developed at the output circuits PC1, PC2 and PC3, respectively. The scan counter 27 is essentially a ring counter which is responsive to each clock pulse signal to step into another state of operation going through its states in the following order: state one, state two and state three and then back to state one. The scan

on the start line 51 to be reset, immediately jumping into state one, regardless of its present state independent of clock pulses.

A monostable multivibrator 56 is provided in the timing unit 41. The monostable multivibrator 56 has an input circuit connected to the start line 51 and two output circuits connected to lines 57 and 58. The monostable multivibrator 56 will be referred to as having two states of operation, a false state and a true state. When the monostable multivibrator is in a false state, a high potential output signal will always be provided on the line 53 and a low potential on the line 57. When the monostable multivibrator 56 is in true state, a high potential output signal will always be provided on the output line 57 and a low potential on the line 58. Normally the monostable multivibrator is in a faise state, but when a high potential signal is received on the start line 51, it is responsive thereto to go into a true state of operation. When in a true state, the monostable multivibrator time it takes for the scan counter 54 to go through states one, two and three and back to state one, and then it goes to a false state again and stays there until it receives another high potential input signal.

The timing unit 41 also comprises an "and" gating circuit 60 which has two input circuits. One input circuit of the "and" gating circuit 69 is connected to the PC3 output circuit of the scan counter 54 and the other input circuit is connected to the output line 58 of the monostable multivibrator 56. An output circuit of the "and" gating circuit 69 is connected to the read data line 35. The "and" gating circuit 60 provides a high potential output signal on the read data line 35 only when a high potential input signal is received at both of its input circuits, that is when the scan counter 54 is in state three and the monostable multivibrator 56 is false.

The counter unit 40 also comprises two counters 62 and 64 with associated control circuits. The counter 62 is called a word counter and comprises eight flip-flop circuits designated F1 through F8 for providing ninety-nine unique combinations of states of operation and thus digital binary coded output signals. The word counter 62 has a skip control input circuit connected to the output circuit of a counter skip control circuit 66 and a count control input circuit connected to the output circuit of an "or" gating circuit 67. The word counter 62 normally counts one state in response to each high potential signal from the "or" gating circuit 67, counting sequentially from a state one up to a state nine-50 ty-nine. A high potential output signal from the "or" gating circuit 67, when the word counter 62 is in state ninety-nine, causes it to recycle to the state one and repeat the cycle of operation.

The counter 64 is a digit counter and is similar to the 55 word counter 62, however, it only has ten unique states of operation, called states one through ten. The digit counter 64 comprises four flip-flop circuits designated F9 through F12, and has a skip control input circuit connected to an output circuit of a counter skip control circuit 70. Another input circuit, called the count input circuit is connected to an output circuit of an "or" gating circuit 71. The digit counter 64 also normally, sequentially counts through its states one through ten and then recycles to state one, doing so in response to each high 65 potential signal at the output circuit of the "or" gating circuit 71. The digit counting circuit 64 has an output circuit connected to a line 74 and each time the digit counter 64 counts into state ten, a high potential output signal is provided thereon.

The control circuit 66 has input circuits connected 70to a plug board 76 of the means for programing 44, the output circuit PC2 of the scan counter 54, the CP output circuit of the source of clock pulses 50 and the reset line 15. The counter skip control circuit 66 comcounter 54 is also responsive to a high potential signal 75 prises gating circuits for resetting the word counter 62

to any of its possible operating states in response to coded input signals from the plugboard 76 and the coincidence of a high potential signal at the output circuit PC2 of the scan counter 54 and a clock pulse. The coded signals from the plugboard 76 determine the state the 5 word counter 62 is to be set into. Whenever a high potential signal is developed on the reset line 15 the counter skip control circuit 66 resets the word counter 62 to its state one.

The counter skip control circuit 70 is similar to the 10control circuit 66 and has input circuits connected to the plug board 76 the output circuit PC2 of the scan counter 54, the CP output circuit of the source of clock pulses 50 and the reset line 15. The counter skip control circuit 70 also comprises gating circuits for resetting 15 the digit counter 64 to any one of its possible states depending on the coded signals applied to its input circuits by the plugboard 76 in coincidence with a high potential signal at the output circuit PC2 of the scan counter 54 and a clock pulse. The counter skip control circuit 70 20 output circuits of the word counter 62 and the digit countis also responsive to a high potential signal on the reset line 15 to reset the digit counter circuit 64 to state one.

The "or" gating circuit 67 has two input circuits one input circuit is connected to an "and" gating circuit 69 and the other is connected to the output circuit of an "and" gating circuit 69. The "and" gating circuit 68 has three input circuits, which are connected to the output circuit PC2 of the scan counter 54, the output circuit CP of the source of clock pulses 50 and the line 72. Thus the "or" gating circuit 67 will apply a high potential in-30 put to the word counter 62 causing it to count from one state to the next whenever the scan counter 54 is in state two, the digit counter 64 is in state 10 and there is a clock pulse or whenever there is a high potential output signal from the "and" gating circuit 69. The "and" circuit 69 has two input circuits. One input circuit is connected to the line 72 and the other is connected to the output circuit of a delay circuit 73. The delay circuit 73 has an input circuit connected to the output circuit of an "or" gating circuit 75. The "or" gating circuit 75 has input circuits connected to the data lines 13. Whenever there is a group of data signals on the data lines 13, at least one line will be a high potential signal. Thus the "or" gating circuit will develop a high potential output signal whenever a group of data signals are applied to the 45 lines 13. The delay circuit 73 is responsive to the rising edge of the high potential output signal of the "or" gating circuit 75 to provide an output signal after a delay long enough to store signals in the means for storing data signals 46.

Thus it is seen that the signal on the lines 13 must all drop to a low potential and then have the group of data signals applied thereto. The "or" gating circuit 71 has two input circuits, which are connected to the output circuit of an "and" gating circuit 72 and the output circuit of the delay circuit 73. The "and" gating circuit 72 has two input circuits which are connected to the output circuit PC2 of the scan counter 54 and the output circuit CP of the source of clock pulses 50. The "or" gating circuit 71 will provide a high potential output 60 signal and cause the digit counter 64 to count from one state to the next whenever the scan counter 54 is in state two and a clock pulse is received or whenever a new data signal is received on the data lines 13.

The means for storing data signals 46 has an input 65 circuit connected of the PC1 output circuit of the scan counter 54 and has another input circuit connected to the output circuits of the word counter 62 and the digit counter 64. The word counter 62 and the digit counter 64 provide storage address signals to the means for storing data signals 46. Each combination of states of the word counter 62 and the digit counter 64 correspond to a particular storage location in the means for storing data signals 46. Whenever a high potential output signal is applied to the PC1 output circuit of the scan 75 of storage location on the means for storing data signals

counter 54, it causes the storage location specified by the states of the word counter 62 and the digit counter 64 to be addressed and the group of data signals stored in this storage location to be applied to the data lines 33. The group of data signals on the data lines 33 remain thereon until after a new storage location is addressed. The means for storing data signals 46 also has an input circuit connected to the output circuit of the "or" gating circuit 75. Whenever a high potential output signal is received from the "or" gating circuit 75, the means for storing data signals 46 reads and stores the group of data signals on the data lines 13. The means for storing data signals 46 has ninety-nine words of storage space and ten digits of storage space within each word. Each digit of storage has five binary bits of storage space for storing one group of data signals. FIG. 5 is an illustrative drawing showing the words and digits of storage space.

The plugboard decoding circuit 42 is connected to the er 64, and provides a high potential output signal at one out of nine hundred ninety output circuits corresponding to each possible combination of states of the word counter 62 and the digit counter 64. For purposes of 25 illustration, the output lines from the plugboard decoding circuit 62 are shown divided into groups of words numbered 1 through 99 and within each group of words ten lines numbered D1 through D10, which, to be explained, represent, the word and digit signal storage locations within the means for storing data signals 46.

The programing means 44 comprises an exit plugboard 78 and the entry plugboard 76 having electrical wire hubs or wire connectors indicated by the general symbol 89. The exit plug board 78 has nine hundred 35 ninety hubs 80 arranged in horizontal rows and vertical columns, corresponding to the words and digits of storage space in the means for storing data signal 46. Thus, there are ninety-nine rows of hubs numbered 1 through 99 corresponding to the words of storage space one through ninety-nine and corresponding to each word there are ten hubs numbered 1 through 10 corresponding to the ten digits of storage within each word. The output circuits of the plugboard decoding circuit 42 are connected by the lines labeled by words and digits to the corresponding hubs on the exit plugboard 78. Thus the line labeled word 1, digit 1 of the plug board decoding circuit 42 is connected to the word 1, digit 1 hub on the exit plugboard 78. Similarly, the lines labeled word 1, digit 2 of the plugboard decoding circuit 22 is con-50 nected to the word 1, digit 2 hub on the exit plugboard 78, etc. Thus it is seen that for each combination of states of the word counter 62 and the digit counter 64 a high potential signal will be developed at one of the hubs 89 on the exit plugboard 78. A scan emitter hub is also provided on the exit plugboard 78, and is connected 55to the line \$7, which is connected to the output circuit of the monostable multivibrator 56 to control the resetting of the word and digit counters 62 and 64, respectively, by means of the plugboard 76.

The entry plugboard 76 also has rows and columns of hubs 80. Two columns of hubs 80 are provided for designating the tens digit and the units digit of a word of storage space in the means for storing data signals 46. A third column is provided for designating the digits within the words. In the tens column for designating the word, there are two hubs in each row, and similarly for the units column. The rows in the tens column are numbered 10 through 90 in increments of ten and the rows in the units column are numbered 1 through 9 in increments of one. 70 There are also two hubs in each row in the digit column and the rows are numbered 1 through 10 in increments of one. To be explained, it takes a connection from a hub in the exit plugboard 78 to one hub in the tens column and/or one hub in the units column to designate a word

3,233,224

46. It also takes a connection from the exit plugboard 78 to a single hub in the digit column to designate a digit within the word. The hubs in the tens, units and digits columns are connected to input circuit of isolation circuits 79, 81 and 83, respectively. The output circuits of the isolation circuits 78 and 31 are connected to the input circuits of the skip control circuit 66 and the output circuit of the isolation circuit 83 is connected to the input circuit of the counter skip control circuit 70. The isolation circuits prevent a high potential signal at one 9 hub in a row in each column from developing a high potential signal at the other hub in that same row and column.

Referring to FIG. 4, the isolation circuit 79 contains unilateral circuits 80 which allow signals to pass through in one direction and not the other. In the tens column, 15 row 10 of hubs are connected to input circuits of two unilateral circuits 80. The output circuits of the two isolation circuits 80 are connected together to a common output line which is connected to the skip control circuit 66. Thus the unilateral circuits 82 allow signals to pass 20 from the hubs to the common output line to the skip control circuit 66 but block signals from the common output line back to the hubs. Each of the other rows of hubs in the tens column are connected in pairs to similar unilateral circuits in the isolation circuit 74. Similarly, 25 each row of hubs in the units column and digits column are connected in pairs to unilateral circuits in the isolation circuits 81 and 83, respectively.

The skip control circuit 66 is responsive to a high potential signal at a hub in the tens and/or units column, 30 simultaneously with high potential signal at the output circuit PC2 of the scan counter 54 and a clock pulse to set the word counter 62 to a state corresponding to the hubs receiving the high potential signal. Thus the con-trol circuit 66 will set the word counter 62 to state one 35 if a high potential signal is applied to a units hub 1, but will set it to state eleven if a high potential signal is applied to both a tens hub 10 and a units hub 1. Similarly, the word counter 66 will be set to state ninety if a high potential is applied to a tens hub 90 above, but will be 40 set to state ninety-nine if a high potential signal is applied to both a tens hub 90 and a units hub 9. Similarly, the control circuit 70 is responsive to a high potential signal at one of the digit hubs simultaneously with a clock pulse and a high potential signal at the output circuit PC2 of 45 the scan counter 54 to set the digit counter 64 to the corresponding state.

With the specific structure of FIG. 3 in mind, an example will be given illustrating its operation. Since the printing system shown in FIG. 1 has been used in a banking 50 system wherein information is to be printed out on bank statements, the following example illustrates its operation in such a system.

Assume that the banking business in which the editing system 12 is to be used has preprinted statements such as that shown in FIG. 7 upon which information is to be printed by the print unit 32. The bank statement shown in FIG. 7 is arranged in three sections providing for withdrawals, deposits and for a balance. Each of the sections is divided into six columns. Thus, columns 1 through 6 are for withdrawals, columns 7 through 12 are for deposits and columns 13 through 18 are for the balance. The print control and storage register 30 prints out information a character at a time doing so in the same order in which the groups of data signals representing the characters are received from the editing system 12. Thus it is seen that the bank statement of FIG. 6 will be printed out a character at a time from left to right in the columns 1 through 18.

A better understanding of the editing system 12 of  $_{70}$ FIG. 3 may be had with reference to FIG. 14 and the following examples of the operation thereof. Assume now that data signals are stored in the means for storing data signals 46 and that the groups of data signals stored in each of the word and digit storage locations represent the 7.5 counts the digit counter 64 and the scan counter 54 into

character numbers shown in FIG. 5. Also assume that the only wires connected between the hubs on the exit plugboard 78 and the hubs on the entry plugboard 76 of FIG. 3 are those connected between the scan emitter of the exit plugboard 78 and a units hub 1 and a digit hub 1 on the entry plugboard 76. FIG. 14 shows wave shapes at designated points in the editing system of FIG. 3 during the time the editing system 12 is initially started into an edit cycle. First, the start switch 48 is actuated which causes the start pulse generator 52 to provide a high potential pulse on the start line 51. The pulse on the start line 51 causes the scan counter 54 to be reset to state one, the monostable multivibrator 56 to be triggered into a true state and the source of clock pulses 50 to start developing clock pulse signals at its output circuit CP.

During state one of the scan counter 54, the first time the means for storing data signals 46 is addressed by the output signals from the word counter 62 and the digit counter 64, an output signal corresponding to the group of data signals stored in the addressed storage location is applied to the data lines 33. It should be noted that the word counter 62 and the digit counter 64 may initially be in any state, and therefore the group of data signals in the addressed storage location is not to be read by the print control and storage register 30. The clock pulse signal at the end of state one of the scan counter 54 triggers it into state two. During state two of the scan counter 54, a high potential signal is applied at the output circuit PC2 of the scan counter 54 and also a high potential signal is applied at the scan emitter by the monostable multivibrator 56. Thus a high potential signal is applied to the units hub 1 and the digit hub 1 on the entry plugboard 76. The clock pulse signal at the end of state two causes the counter skip control circuits 66 and 70 to set the word counter 62 and the digit counter 64 into state one and counts the scan counter 54 into state three. Since the monostable multivibrator 56 is still true, the output signal of the "and" gating circuit 60 at the read data line 35 is a low potential signal. Therefore the print control and storage register 30 does not read the group of data signals on the data lines 33. The clock pulse signal at the end of state three of the scan counter 54 places it back into state one and shortly thereafter the monostable multivibrator 56 goes into a false state.

During state one of the scan counter 54, the second time a high potential signal is provided at the output circuit PC1, the word 1, digit 1 storage location of the means for storing data signals 46 is addressed. A group of data signals are then provided on the data lines 33 corresponding to those in the addressed storage location which is the numeral 1 (see FIG. 5). The clock pulse signal at the end of state one of the scan counter 54 places it into state two. The clock pulse signal at the end of state two places the scan counter 54 into state three and places the digit counter 64 into state two. Dur-55ing state three of the scan counter 54, the group of data signals stored in the word 1, digit 1 storage location of the means for storing data signals 46 is still applied to the data lines 33 and the "and" gating circuit 60 provides a high potential output signal at the read data line 60 35. This causes the print control and storage register 30 to read the group of data signals representing a number 1 on the data lines 33. The clock pulse signal at the end of state three places the scan counter 54 into state 65

During state one of the scan counter 54, the third time. the word counter 62 and the digit counter 64 are in states one and two, respectively. The word 1, digit 2 storage location of the means for storing data signals 46 is addressed causing a group of data signals representing the numeral 3 to be applied to the data lines 33. The clock pulse signal at the end of state one causes the scan counter 54 to count into state two. The clock pulse signal at the end of state two of the scan counter 54

state three. During state three of the scan counter 54 the group of data signals representing a character number 3 is still applied to the data lines 33 and the "and" gating circuit 60 provides a high potential output signal at the read data line 35. This causes the print control and 5 storage register 30 to read the group of data signal on the data lines 33.

In summary then, with the above assumed program or wire connections, during each state one, the storage location of the means for storing data signals 46, corre- 10 sponding to the states of the word counter 62 and the digit counter 64 will be addressed. This causes a group of data signals to be applied on the data lines 33 corresponding to those stored in the addressed storage location. During each state two of the scan counter 54 the 15 digit counter 64 will be counted into its next state. During each state three the group of data signals applied on the data lines 33 will be read by the print control and storage register 30. Reference to the bank statement of FIG. 7 and the stored information of FIG. 5 will reveal that the information stored in the storage locations word 1, digits 1 through 10 and word 2, digits 1 through 8 are printed out in the columns 1 through 18 in the same sequential order as they are stored.

It should be noted at this point, with regard to the 25 validity of the programming by exception that the pieces of information on the bank statement must occur in the stored sequential fashion to represent the correct, intelligible information and no other sequence would suffice. That is, a withdrawal of \$1,300.00 must be recorded with the digits 1-3-0-0-0 in sequence since any other sequence would represent an erroneous amount.

Therefore, it should now be evident that without program connections between word and digit hubs on the exit plugboard 78 there are no "exceptions" programmed in. This allows groups of data signals to be shifted out to the print control and storage register 30 and then printed out in an order determined by that in which the signals are received and stored by the means for storing data signals 46. Therefore, the groups of data 40 signals in word 1 and digits 1 through 10 storage locations are first shifted out to the print control and storage register 30, then those in the word 2, digits 1 through 10 storage location, etc. This operation continues until the storage register in the print control and storage register  $_{45}$ 30 is full and a high potential signal is applied to the stop edit line 39, which causes the source of clock pulses 50 to stop developing clock pulses at its output circuit CP. The printing and storage unit 14 then goes into a print cycle where the group of data signals stored in the print 50control and storage register 30 are sequentially printed out by the print unit 32.

Assume now that the data signals stored in the means for storing data signals 46 are again those shown in FIG. 5 and are in an order different from that in which they 55 are to be printed out by the print unit 32. Assume that the deposits amount is stored in the storage locations word 2, digits 3 through 8, and the balance amount is stored in the storage locations word 1, digits 7 through 10 and word 2, digits 1 and 2. This means that the 60 storage locations now cannot be sequentially addressed as in the above example but "exceptions" must be programmed or wired in the plugboards so that the groups of data signals stored in the means for storing data signals 46 will be rearranged before being read by the print 65 control and storage register 30. Thus the means for storing data signals 46 must first shift out data signals stored in word 1, digits 1 through 6, then the data signals stored in word 2, digits 3 through 8 and followed by digits 1 and 2. Following this latter group of data signals it is necessary to program an exception to skip the digits 3 through 8 of word 2 since they have been printed out and to commence the sequential print out with word 2, digit 9. This program is written out in FIG. 6.

In order to perform this rearrangement using programming by "exception" the program steps of FIG. 8 are needed. The impulse from the scan emitter is used to reset the word counter 62 and the digit counter 64 to state one. This allows the groups of data signals representing the withdrawal amount to first be shifted out to the print control and storage register 30. To effectuate this program step a wire is connected between the scan emitter on the exit plugboard 78 and the units hub 1 and digit hub 1 on the entry plugboard 76. The second step uses the impulse from the word 1 digit 6 hub to set the word counter 64 to state two and the digit counter to state three. This selects the first group of data signals of the deposits amount and allows the deposits amount to be shifted out next. Thus to effectuate this program step a wire is connected between the word 1 digit 6 hub on the exit plugboard 78 and the units hub 2 and digits hub 3 on the entry plugboard 76. The third step is to use the word 2 digit 8 pulse to reset the word counter to state one and the digit counter to state seven. This selects the first group of data signals of the balance amount and allows the balance amount to be shifted out next. To effectuate this a wire is connected between the word 2, digit 8 hub on the exit plugboard 78 and the units 1 hub and the digit 7 hub on the entry plugboard 76. Step 4 is to use the word 2, digit 3 pulse to set the digit counter 64 to state nine. This selects the first group of data signals of the next groups to be shifted out by means for storing data signals 46. To effectuate this a wire is connected between the word 2, digit 3 hub on the exit plugboard 78 and the units hub 2 and the digit hub 9 on the entry plugboard 76.

Consider now the operation of the editing system 12 as shown in FIG. 3 with the programed exceptions described above. Initially, the start switch 48 is actuated causing the scan counter 54 to be reset to state one, the monostable multivibrator 56 is triggered into a true state and the source of clock pulses 50 starts developing clock pulses. The clock pulse signal at the end of state one of the scan counter 54 triggers the scan counter 54 into state two. The clock pulse signal at the end of state two triggers scan counter into state three and sets both the word counter 62 and the digit counter 64 into state one.

During the state one of the scan counter 54, the second time, word counter 62 and digit counter 64 are still in state one and the corresponding storage location in the means for storing data signals 46 is addressed. Referring to FIG. 5, this causes a group of data signals representing the numeral one to be applied to the data lines 33. During state two, the second time, the digit counter 64 is counted into state two. During state three of the scan counter 54, data signals corresponding to those stored in the word 1 digit 1 storage location are still applied to the data lines 33 and the "and" gating circuit 60 develops a high potential signal on the read data lines 35 causing the first group of data signals of the withdrawal amount to be read and stored by the print control and storage register 30. During the following five times the scan counter 54 is in state three the rest of the groups of data signals of the withdrawal amount are applied to the data lines 33 and read and stored by the print control and storage register 30.

Assume now that the scan counter 54 is in state two, the word counter 62 is in state one and the digit counter 64 is in state six. The data signals stored in the word 1, digit 6 storage location of the means for storing data signals 46 are now being applied on the data lines 33 by the means for storing data signals 46. Also, there is a high potential signal on the word 1, digit 6 hub of the those stored in word 1, digits 7 through 10, and word 2, 70 exit plugboard 78 causing a high potential signal on the units hub 2 and the digits hub 3 on the entry plugboard 78. Thus during state two, the word counter 62 is set to state two and the digit counter 64 is set to state three. During state three of the scan counter 54 a high potential 75 signal is applied on the read data line 35 by the "and"

5

gating circuit 60. This causes the print control and storage register 30 to read the data signals on the data lines 33.

During the following state one of the scan counter 54 the word 2, digit 3 storage location of the means for storing data signals 46 is addressed and a group of signals representing the number 1 is applied to the data lines 33. During state two of the scan counter 54, the digit counter 64 is placed into state four. During the following state three of the scan counter 54 the group of data 10signals representing a number one is still applied to the data lines 33 and therefore read by the print control and storage register 30.

When the scan counter 54 goes into state three the following four times, groups of data signals from the 15 storage locations word 2, digits 4 through 8 will be applied to the data lines 33 and read by the print control and storage register 30.

Assume now that the word counter is in state two and the digit counter 64 in state eight. A group of data 20 signals representing the numeral 0 from the storage location word 2, digit 8 is applied to the data lines 33. A high potential signal is developed at the word 2 digit 8 hub on the exit plugboard 78 causing a high potential signal at the unit 1, digit 7 hub on the entry plugboard 76. This causes the word counter 62 to be set to state one and the digit counter 64 to state even. During state three of the scan counter 54 a high potential signal is applied to the read data line 35 causing the print control and storage register 30 to read the group of data signals 30 on the data lines 33.

Since the storage location word 1 digit 7 contains data signals corresponding to the first group of data signals of the balance amount, during the following state three of the scan counter 54 the first character of the balance 35amount will be applied to the data lines 33 and stored by the print control and storage register 30.

During the following five times that the scan counter 54 goes into state three the remainder of the groups of 40 signals of the balance amount are applied to the data lines 33 and read and stored by the print control and storage register 30. After the word counter 62 counts into state two and the digit counter 64 counts into state two a high potential signal is applied to the units hub 2, digit hub 2 on the entry plugboard 76 causing the digit counter 64 45 to be set to state 9. Thus it is seen that after the balance amount is shifted out of the means for storing data signals 46, the first of the next group or groups of data signals is selected by a programmed "exception" and the printing system 12 continues on sequentially shifting out 50groups of data signals from storage locations in the means for storing data signals 46 from this point on until another programed "exception" is reached.

When a group or groups of data signals in the means for storing data signals 46 are to be rearranged all that 55 is needed is to select the beginning of the group or groups of data signals by setting the word counter 62 and the digit counter 64 to the appropriate states and then allowing the editing system 12 to sequentially shift out the following groups of data signals. The editing system 12will then continue sequentially shifting out data signals until another point is reached where an "exception" has been programed in and the beginning of another group or groups of data signals is selected.

Other editing operations may be performed by pro-  $_{65}$ gramming by "exception," for example, groups of data signals representing sign characters, and data signals representing blanks, which are to be left on the paper as the characters are printed out, may be inserted in between digits of data signals stored in the means for storing 70 data signals 46. Also, stored digits may be converted absolutely or conditionally to other characters such as a credit symbol CR or a debit symbol DB. An example of a conditional conversion is a group of data signals may be converted to another group of data signals on the condi- 7.5

tion that the number to be converted is an even number or an odd number.

Before explaining FIG. 12, a brief explanation of terminology to be used will be given. Flip-flop circuits are bistable devices such as the Eccles-Jordan trigger circuits having two states, a true state and a false state. The flip-flop circuit will be designated by a capital letter followed by a number, i.e., C1, I1, etc. A flip-flop circuit has two input circuits and two output circuits, the output circuits being represented by the letter designation of the flip-flop circuit followed by a number subscript corresponding to the flip-flop number and to distinguish between the two output circuits a prime is affixed to the designation of one of the output circuits, thus  $C_1$ ,  $C_1'$ ,  $I_1$ and  $I_1'$ .

When the unprimed output circuit is a high potential level, the primed output circuit is a low potential level and the flip-flop circuit is said to be true. When the unprimed output circuit is a low potential level and the primed output circuit a high potential level, the flip-flop circuit is said to be false. The input circuits of the flip-flop circuits are designated by a lower case letter followed by a number corresponding to the capital letter and number, designating the flip-flop circuits. A subscript 1 and 0 is used in front of the lower case letter to designate the input which when pulsed sets the flip-flop circuit true and false, respectively, thus, 1c1, 0c1, 1i1, 0i1.

Referring now to FIG. 12 wherein a modification of the editing system of FIG. 3 is illustrated to include the latter-mentioned features of programing by "exception." To illustrate these "exceptions" the means for storing data signals 46 is shown as comprising a buffer register 84 and a memory unit 86.

The buffer register 84 comprises five flip-flop circuits designated B1 through B5 with associated gating circuits (not shown) for triggering the flip-flop circuits into states corresponding to the received input signals. The buffer register 84 has one input circuit connected in parallel circuit arrangement with the lines 85. The lines 85 comprise the same number of lines as in the data lines 13 and each is connected to an end of one of the data lines 13 through the isolation circuit 87. The isolation circuits are unilaterally conductive circuits in between the lines 85 and the data lines 13 and may be similar to the unilateral circuits of FIG. 4. The isolation circuit 87 allows signals to pass from the data lines 13 to the lines 85, however, it blocks signal flow in the reverse direction, as is well known. Other input circuits connected to a dollar sign, set control line 91, a blank space set control line 93, a credit, CR, set control line 95 and a debit, DB, set control line 97. The buffer register 84 is responsive to a group of data signals applied to the data lines 13 and thus the lines 85 to store the data signals. The buffer register 84 is also responsive to signals on the lines 91, 93, 95 and 97 to automatically store signals in the flip-flop circuits B1 through B5 representative of a dollar sign, a blank space, a credit symbol and a debit symbol, respectively, to be explained in detail.

The memory unit 86 is a coincident current core mem-60 ory unit arranged with ninety-nine words of storage space, each word of storage space comprising space for storing ten digit signals or groups of data signals. The memory unit 86 contains all the necessary read and write circuits for energizing all the core units of a digit of storage space. Thus the core units of a digit of storage space are simultaneously energized for shifting a group of data signals out and similarly for writing a group of data signals therein. It should also be noted that in a preferred embodiment of the invention a nondestructive type of core memory unit is used in which the storage content of each storage location is retained after shifting signals out. This allows the stored signals to be shifted out again at a subsequent time. The memory unit 86 has an input circuit connected in parallel circuit arrangement to the output circuit of the buffer register circuit 84.

Also an output circuit is connected in parallel circuit arrangement to the lines 85. The core memory circuit 86 has storage address lines connected to the output circuits of the word counter 62 and the digit counter 64. The memory unit 86 also has an input circuit connected to the PC1 output circuit of the scan counter 54 and is responsive to a high potential signal on the PC1 output circuit for addressing the storage location specified by the state of the word counter 62 and the digit counter 64. When a storage location is addressed, the group of data signals stored in the addressed storage location is shifted to the output circuit and applied to the lines 85 in parallel where the signals are automatically stored by the buffer register 84. The memory unit 86 also has an input circuit connected to the output circuit of a delay circuit 77. The memory unit 86 is responsive to a high potential output signal of the time delay circuit 77 to store a group of data signals corresponding to those stored in the buffer register 84. Again the storage location is specified by the states of the word counter 62 and the digit counter 64.

The input circuit of the delay circuit 77 is connected to the output circuit of the "or" gating circuit 75 in the timing circuit 41. The time delay circuit 77 has a shorter time delay than the time delay circuit 73.

Whenever a group of data signals is applied on the data lines 13, a high potential output signal is developed at the input circuit of the delay circuit 77. Thus a group of data signals is first applied to the data lines 13, 30 and stored in the buffer register 84. The time delay circuit 77 then causes the memory unit 86 to read and store the signals stored in the buffer register 84. After the signals are stored in the memory unit 86 the time delay circuit 73 causes the word counter 62 and digit 35 counter 64 to count to their next state.

An insert and conversion entry plugboard 92 is provided in the programing means 44 for inserting a group of data signals in between groups of data signals stored in the memory unit 86 and for conditionally converting signals representing characters stored in the memory unit 86 to signals representing other characters. There are two hubs 94 and 96 in the entry plugboard 92 for making inserts, the hub 94 is for inserting signals representing a dollar sign and the hub 96 is for inserting signals representing blanks, which ultimately cause the print unit 45 32 to leave spaces on the paper as characters are printed out.

The entry plugboard 92 has four conversion hubs 98, 100, 102 and 103 designated by the symbols credit even, credit odd, debit even and debit odd, respectively. The 50 credit even hub 98 and the credit odd hub 100 are for conditionally converting a group of data signals representing a character to signals representing the character credit.

The hubs 94, 96, 98, 100, 102 and 103 are connected 55 to lines 105, 107, 108, 109, 110 and 111, which are connected to input circuits of the signal generator 90. The signal generator 90 has other input circuits connected to the output circuits of the scan counter 54, the source of clock pulses 50, the B<sub>5</sub> and B<sub>5</sub>' output circuits of the flip- 60 flop circuits B5 in the buffer register B4, and the line 57 connected to the output circuit of the monostable multivibrator 56. The signal generator 90 has output circuits connected to the set control lines 91, 93, 95, 97, and the input circuits of the "and" gating circuits 104 and 106, 65 and an "and" gating circuit 144.

Refer now to FIG. 13, which shows a circuit diagram, partly in block form, the signal generator 90 will be examined in more detail. Two insert circuits are shown 113 and 115. Considering the insert control circuit 113, 70 dollar sign hub 94 is connected, by means of the line 107 to the  $_1c1$  input circuit of a dollar flip-flop circuit C1 through an "and" gating circuit 112. Another input circuit of the "and" gating circuit 112 is connected to the PC2 output circuit of the scan counter 54. The oc1 75 output circuits of the "and" gating circuits 116 and 118

input circuit of the dollar flip-flop circuit C1 is connected to the output circuit of an "or" gating circuit 114. The "or" gating circuit 114 has two input circuits which are connected to the PC2 output circuit of the scan counter 54 and the line 57, connected to the monostable multivibrator 56. In the following discussion an "or" gating circuit provides a high potential output signal only when any one or more of its input signals are at a high potential level. Thus the flip-flop circuit C1 will be triggered true, if it is false, at the occurrence of a clock pulse, whenever there is a high potential signal at the dollar sign hub 94 and a high potential signal is developed at the output circuit PC2 of the scan counter 54. Also the flip-flop circuit C1 will be triggered false at the occurrence of a clock pulse, if it is true, whenever a high potential signal is developed at the output circuit PC2 of the scan counter 54 or on the line 57. An "and" gating circuit 138 has two input circuits which are connected to an insert line or the C<sub>1</sub> output circuit of the 20flip-flop circuit C1 and the PC2 output circuit of the scan counter circuit 54. The output circuit of the "and" gating circuit 138 is connected to the dollar set control line 91. An inhibit flip-flop circuit I1 is provided. The inhibit flip-flop circuit II has its 1i1 input circuit connected to the output circuit of an "and" gating circuit 126, which has two input circuits, one input circuit is connected to the C<sub>1</sub> output circuit of flip-flop circuit C1 and the other is connected to the output circuit PC3 of the scan counter 54. The  $_0i1$  input circuit of the flipflop circuit I1 is connected to the output circuit of an "or" gating circuit 128, which has two input circuits, one input circuit is connected to the line 57 and the other is connected to the output circuit of an "and" gating circuit 130. The "and" gating circuit 130 has two input circuits, one input circuit being connected to the  $C_1$  output circuit of flip-flop circuit C1 and the other input circuit is connected to the output circuit PC3 of the scan counter 54. The  $I_1'$  output circuit of the inhibit flip-flop circuit I1 is connected to the line 131 and will be referred to as the inhibit line, to be explained. This line prevents the word counter 62 and the digit counter 64 from counting when the inhibit flip-flop circuit **I1** is true. Thus it is seen that a high potential signal at the out-

put circuit PC3 of the scan counter 57 when the dollar sign flip-flop circuit C1 is true will cause a high potential output signal from the "and" gating circuit 126 to the input circuit  $_1i1$  causing the inhibit flip-flop circuit II to be triggered true at the occurrence of a clock pulse. Also a high potential signal at the output circuit PC3 simultaneously with a false state of the dollar sign flipflop circuit C1 or a high potential signal on the line 57 will cause the inhibit flip-flop circuit I1 to be triggered false if it is true. The insert control circuit 115 is identical to the insert control circuit 113 except its input circuit is connected to the blank hub 96 rather than the dollar sign hub 94, and its insert output line is connected to the input circuit of an "and" gating circuit 139. Also an inhibit line 132 is connected to the output circuit of the insert control circuit 115, which is similar to the inhibit line 131 of an "and" gating circuit 139. The "and" gating circuit 139 has another input circuit connected to the PC2 output circuit of the scan counter 54. The output circuit of the "and" gating circuit 139 is connected to the blank set control line 93.

Two conversion control circuits 117 and 122 are provided. The conversion control circuit 117 has the credit even hub 98 connected to an input circuit of an "and" gating circuit 116, which has another input circuit connected to the B<sub>5</sub> output circuit of the flip-flop circuit B5 in the buffer register 84. The credit odd hub 100 is connected to an input circuit of an "and" gating circuit 118, which has another input circuit connected to the  $B_5'$  output circuit of the B5 flip-flop circuit. The

25

3,233,224

are connected to the input circuits of an "or" gating circuit 120. The output of the "or" gating circuit 12 is connected to a conversion line which is connected to an input circuit of an "and" gating circuit 140. Another input circuit of the "and" gating circuit 140 is connected to the PC2 output circuit of the scan counter 54. The output circuit of the "and" gating circuit 140 is connected to the credit set control line 95. The conversion control circuit 122 is identical to that of the conversion control circuit 111 except that it has input circuits connected to the debit even hub 102 and debit odd hub 103 rather than the credit even hub 98 and the credit odd hub 100. Also the conversion line is connected to an "and" gating circuit 144 which has another input circuit connected to the PC2 output circuit of the scan counter 15 54. The output circuit of the "and" gating circuit 144 is connected to the debit set control line 97.

Thus a high potential signal applied to the credit even hub 98 simultaneously with the true state of the sign flip-flop B5, or a high potential signal at the credit odd 20hub 110 simultaneously with the false state of the sign flip-flop B5 will cause a high potential output signal from the "and" gating circuit 120. If the scan counter is in state two when this occurs, a high potential signal is developed on the credit set control line 95. This causes 25 the buffer register 84 to store a group of data signals representing a credit symbol. The operation is similar for the conversion control circuit 122.

The "and" gating circuits 104 and 106 now replace the gating circuits 68 and 72 of the editing system of "and" 30 FIG. 3. This was done to add one more input circuit to each gate. The added input circuit is connected to the inhibit output lines 131 and 132 of the insert control circuits 113 and 115. Thus the digit counter 64 now counts when the inhibit flip-flop circuits in the insert cir- 35 cuits 113 and 115 are false, the scan counter 54 is in state two and there is a clock pulse. The word counter 62 only counts when all these conditions are met and the digit counter 64 is in state ten.

With the specific structure of the editing system 12  $^{40}$ shown in FIG. 12 in mind, an example will be given illustrating its operation. Assume that initially the memory unit 86 is loaded with the same groups of data signals shown in FIG. 5 and are to be edited, read and stored by the storage unit 14 for printing. The groups of data sig-45nals are to be rearranged as is discussed in connection with FIG. 3, but in addition a dollar sign is to be inserted in front of the balance amount. Further assume, that the digit signal stored in the storage location word 2, digit 9 is to be conditionally converted either to a credit symbol or a debit symbol depending on if it is even or odd, respectively. This time the bank statement is to be used during the printing operation is that shown in FIG. 11 therefore, the dollar sign is to be inserted in column 13, which follows the last digit of the deposits amount and the credit or debit symbols are to be placed in column 20 which follows immediately after the last digit of the balance amount.

FIG. 10 shows the required program for performing these editing operations by "exception." The first four 60 steps of the program are identical to the program shown in FIG. 8 for the editing system of FIG. 3. The fifth step is to use the word 2, digit 8 signal from the exit plugboard 78 to cause a group of data signals representing a dollar symbol to be inserted following the deposits 65 amount. Thus a wire is needed from the word 2 digit 8 hub on the exit plugboard 78 to the dollar sign hub 94 on the entry plugboard 92. Step 6 is to use the signal from the word 2 digit 9 exit plugboard 78 to cause either a credit symbol or a debit symbol to be placed after the 70 end of the balance amount. This step is performed by connecting a wire from the word 2 digit 9 hub on the exit plugboard 78 to the credit even hub 98 and the debit odd hub 103 on the entry plugboard 92.

FIG. 10, the start switch 48 is actuated. This causes an output pulse from the start pulse generator 52 which resets the scan counter 54 to state one, the monostable multivibrator 56 into a true state and causes the source of clock pulses 50 to start developing clock pulses. Since the monostable multivibrator 56 is true, the first clock pulse resets the flip-flop circuits in the insert control circuits 113 and 115 in the signal generator 90 and counts the scan counter 54 into state two. During state two of the scan counter 54 the scan emitter causes a high potential signal to be applied to the units 1 digit 1 hub on the entry plugboard 76. Therefore, the clock pulse signal at the end of state two of the scan counter 54 resets the word counter 62 and the digit counter 64 to state one and counts the scan counter 54 into state three. During state three the monostable multivibrator 56 is still true, therefore, the "and" gating circuit 60 develops a low potential output signal on the line 35. Since the potential on the line 35 is a low potential, the print control and storage register does not read the contents of the buffer register 84. The clock pulse signal at the end of state two of the scan counter 54 counts it into state one.