## (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-289107 (P2004-289107A)

(43) 公開日 平成16年10月14日(2004.10.14)

| (51) Int.C1. <sup>7</sup> | FI           |     |       |

|---------------------------|--------------|-----|-------|

| H O 1 L 21/822            | HO1L 27/04   | G   | 5F038 |

| HO1L 21/8238              | HO1L 27/08 3 | 21B | 5FO48 |

| HO1L 27/04                | HO1L 27/04   | F   |       |

| HO1L 27/092               |              |     |       |

審査請求 有 請求項の数 29 OL (全 24 頁)

|                                                                                                             |                                                                                                                                                                                                  | 一                                            |                                                                                                                                                       | 見ひり女父 ムラ                                                                                               | OL           | (± 24 | 具/       |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------|-------|----------|

| (21) 出願番号<br>(22) 出願日<br>(31) 優先権主張番号<br>(32) 優先日<br>(33) 優先権主張国<br>(31) 優先権主張番号<br>(32) 優先日<br>(33) 優先権主張国 | 特願2003-197900 (P2003-197900)<br>平成15年7月16日 (2003.7.16)<br>特願2002-211536 (P2002-211536)<br>平成14年7月19日 (2002.7.19)<br>日本国 (JP)<br>特願2003-19271 (P2003-19271)<br>平成15年1月28日 (2003.1.28)<br>日本国 (JP) | (74) 代理人<br>(74) 代理人<br>(74) 代理人<br>(74) 代理人 | 396023993<br>株神2<br>100099759<br>中地2<br>100099759<br>中地2<br>100092624<br>中地2<br>100102819<br>中地2<br>100100871<br>中地2<br>100100871<br>中地2<br>100100871 | は体理工学を<br>では<br>で<br>で<br>で<br>で<br>に<br>で<br>に<br>で<br>に<br>で<br>に<br>で<br>に<br>で<br>に<br>に<br>に<br>に | 研究セン<br>新横浜3 | •     |          |

|                                                                                                             |                                                                                                                                                                                                  | (74) 代理人<br>                                 | 100082898<br>弁理士 西山                                                                                                                                   | 雅也                                                                                                     |              |       |          |

|                                                                                                             |                                                                                                                                                                                                  |                                              |                                                                                                                                                       |                                                                                                        | 最終           | 頁に続   | <b>〈</b> |

#### (54) 【発明の名称】半導体集積回路装置

## (57)【要約】

【課題】近年、MOSトランジスタのウェル(基板)に順方向バイアス電圧を印加することが注目されているが、温度変化に対して最大限の順方向バイアス電圧を得ることが難しく、そのための回路構成や占有面積も問題になってきている。

【解決手段】第1導電型( $p^+$ ;  $n^+$ )のソース電極S およびドレイン電極Dとゲート電極Gとを有し、第2導電型(n; p)のウェル10; 20に形成されてなるM ISFET1; 2を備える半導体集積回路装置であって、前記ウェル10; 20の電位Vbp; Vbne、前記 MISFET1; 20ツース電極Sおよび該ウェル10; 20により形成されるダイオード11; 21に対して所定電流Ibp; Ibne順方向に流すことにより生成する基板バイアス回路110; 111~113を備えるように構成する。

【選択図】 図4

#### 図 4

本発明に係る半導体集積回路装置の原理構成を説明するための 断面図

#### 【特許請求の範囲】

#### 【請求項1】

第 1 導電型( p <sup>†</sup> ; n <sup>†</sup> )のソース電極( S )およびドレイン電極( D )とゲート電極( G )とを有し、第 2 導電型( n ; p )のウェル( 1 0 ; 2 0 )に形成されてなる M I S F E T ( 1 ; 2 )を備える半導体集積回路装置であって、

前記ウェル(10;20)の電位(Vbp;Vbn)を、前記MISFET(1;2)のソース電極(S)および該ウェル(10;20)により形成されるダイオード(11;21)に対して所定電流(Ibp;Ibn)を順方向に流すことにより生成する基板バイアス回路(110,111~113:3;4;151,161)を備えることを特徴とする半導体集積回路装置。

【請求項2】

請求項1に記載の半導体集積回路装置において、

該半導体集積回路装置(100)は、複数の回路ブロック(101~103)を有し、前記基板バイアス回路(111~113)は、前記各回路ブロック(101~103)毎にそれぞれ設けられていることを特徴とする半導体集積回路装置。

#### 【請求項3】

請求項2に記載の半導体集積回路装置において、さらに、

前記各基板バイアス回路(111~113)を、対応する前記各回路ブロック(101~103)毎に制御する電力制御ユニット(105)を備えることを特徴とする半導体集積回路装置。

【請求項4】

請求項2に記載の半導体集積回路装置において、電力制御ソフトウェアモジュールはCPU(101)で実行され、前記各回路ブロック(101~103)毎にそれぞれ設けられた前記基板バイアス回路(111~113)を個別に制御することを特徴とする半導体集積回路装置。

#### 【請求項5】

請求項4に記載の半導体集積回路装置において、前記各回路ブロック(101~103)は、レジスタ(111~113)を備え、前記各基板バイアス回路(111~113)は、該レジスタ(111~113)に格納されたデータに従って制御されることを特徴とする半導体集積回路装置。

【請求項6】

請求項5に記載の半導体集積回路装置において、前記各回路ブロック(101~103)は、データバス(104)に接続され、前記レジスタ(111~113)のデータは、該データバス(104)を介して書き込まれることを特徴とする半導体集積回路装置。

#### 【請求項7】

請求項1に記載の半導体集積回路装置において、

該半導体集積回路装置(100)は、複数の回路ブロック(150,160)を有し、前記基板バイアス回路(151,161)は、前記各回路ブロック(150,160)毎にそれぞれ設けられると共に、当該回路ブロックの制御信号(CSA,CSB)により制御されることを特徴とする半導体集積回路装置。

【請求項8】

請求項1に記載の半導体集積回路装置において、

該半導体集積回路装置(100)は、複数の回路ブロック(101~103;1010) を有し、

前記回路ブロック(1010)は、複数の機能ブロック(1110,1120,1130 ,1140)を有し、

前記基板バイアス回路(1111、1121、1131、1141)は、前記各機能ブロック(1110,1120,1130,1140)毎にそれぞれ設けられていることを特徴とする半導体集積回路装置。

#### 【請求項9】

20

10

30

40

請求項1に記載の半導体集積回路装置において、

該半導体集積回路装置は標準セル部(400)を有し、

前記基板バイアス回路(430-1~430-n)は、前記標準セル部の各行毎にそれぞれ設けられていることを特徴とする半導体集積回路装置。

#### 【請求項10】

請求項1に記載の半導体集積回路装置において、前記基板バイアス回路(110)は、第1の電源線(Vss; Vdd)と前記ウェル(10;20)のコンタクト領域(10a;20a)との間に設けられた電流源(3;4)を備え、該コンタクト領域(10a;20a)を介して前記ダイオード(11;21)に前記所定電流(Ibp;Ibn)を流すことを特徴とする半導体集積回路装置。

#### 【請求項11】

請求項10に記載の半導体集積回路装置において、前記電流源(3;4)は、前記第1の電源線(Vss;Vdd)を電源として前記所定電流(Ibp;Ibn)を発生することを特徴とする半導体集積回路装置。

#### 【請求項12】

請求項11に記載の半導体集積回路装置において、前記電流源(3;4)は、

制御信号(Cbp;Cbn)がゲート電極に供給され、ソース電極が第2の電源線(Vdd;Vss)に接続された前記MISFETと同じ極性の電流源用第1MISFET(32;42)と、

ソース電極が前記第1の電源線(Vss; Vdd)に接続され、ドレイン電極およびゲート電極が前記電流源用第1MISFET(32;42)のドレイン電極に接続された前記MISFETと異なる極性の電流源用第2MISFET(33;43)と、

前記電流源用第2MISFET(33;43)に対してカレントミラー接続され、ドレインが前記コンタクト領域(10a;20a)に接続される電流源用第3MISFET(34;44)とを備えることを特徴とする半導体集積回路装置。

#### 【請求項13】

請求項12に記載の半導体集積回路装置において、前記電流源(3;4)は、さらに、前記制御信号(Cbp;Cbn)の反転信号がゲート電極に供給され、ソース電極が前記コンタクト領域(10a;20a)に接続され、且つ、ドレイン電極が前記第2の電源線(Vdd;Vss)に接続された前記MISFETと同じ極性の電流源用第4MISFET(30;40)を備えることを特徴とする半導体集積回路装置。

## 【請求項14】

請求項11に記載の半導体集積回路装置において、前記電流源(3;4)は、

制御信号(Cbp;Cbn)がゲート電極に供給され、ソース電極が前記第1の電源線(Vss;Vdd)に接続された前記MISFETと異なる極性の電流源用第5MISFET(34;44)と、

前記制御信号(Cbp;Cbn)がゲート電極に供給され、ソース電極が前記コンタクト領域(10a;20a)に接続され、且つ、ドレイン電極が前記第2の電源線(Vdd;Vss)に接続された前記MISFETと同じ極性の電流源用第6MISFET(30;40)とを備えることを特徴とする半導体集積回路装置。

## 【請求項15】

第1導電型(p<sup>+</sup>)のソース電極(S)およびドレイン電極(D)とゲート電極(G)とを有し、第2導電型(n)の第1ウェル(10)に形成されてなる第1極性(p)の第1MISFET(1)、並びに、前記第2導電型(n<sup>+</sup>)のソース電極およびドレイン電極とゲート電極とを有し、前記第1導電型(p)の第2ウェル(20)に形成されてなる第2極性(n)の第2MISFET(2)を備える半導体集積回路装置であって、

前記第1ウェル(10)の電位(Vbp)を、前記第1MISFET(1)のソース電極および該第1ウェルにより形成されるダイオード(11)に対して所定電流(Ibp)を順方向に流すことによって生成する第1基板バイアス回路(110;111~113;3)と、

10

20

30

前記第2ウェル(20)の電位(Vbn)を、前記第2MISFET(2)のソース電極および該第2ウェルにより形成されるダイオード(21)に対して所定電流(Ibn)を順方向に流すことによって生成する第2基板バイアス回路(110;111~113;4)とを備えることを特徴とする半導体集積回路装置。

#### 【請求項16】

請求項15に記載の半導体集積回路装置において、

該半導体集積回路装置(100)は、複数の回路ブロック(101~103)を有し、前記第1および第2基板バイアス回路(3,4)は、前記各回路ブロック(101~10 3)毎にそれぞれ設けられていることを特徴とする半導体集積回路装置。

#### 【請求項17】

請求項16に記載の半導体集積回路装置において、さらに、

前記各第1および第2基板バイアス回路(3,4)を、対応する前記各回路ブロック(101~103)毎に制御する電力制御ユニット(105)を備えることを特徴とする半導体集積回路装置。

#### 【請求項18】

請求項16に記載の半導体集積回路装置において、電力制御ソフトウェアモジュールは CPU(101)で実行され、前記各回路ブロック(101~103)毎にそれぞれ設けられた前記基板バイアス回路(111~113)を個別に制御することを特徴とする半導体集積回路装置。

## 【請求項19】

請求項18に記載の半導体集積回路装置において、前記各回路ブロック(101~103)は、レジスタ(111~113)を備え、前記各基板バイアス回路(111~113)は、該レジスタ(111~113)に格納されたデータに従って制御されることを特徴とする半導体集積回路装置。

#### 【請求項20】

請求項19に記載の半導体集積回路装置において、前記各回路ブロック(101~103)は、データバス(104)に接続され、前記レジスタ(111~113)のデータは、該データバス(104)を介して書き込まれることを特徴とする半導体集積回路装置。

#### 【請求項21】

請求項15に記載の半導体集積回路装置において、

該半導体集積回路装置(100)は、複数の回路ブロック(150,160)を有し、前記第1および第2基板バイアス回路(3,4)は、前記各回路ブロック(150,160)毎にそれぞれ設けられると共に、当該回路ブロックの制御信号(CSA,CSB)により制御されることを特徴とする半導体集積回路装置。

#### 【請求項22】

請求項15に記載の半導体集積回路装置において、

該半導体集積回路装置(100)は、複数の回路ブロック(101~103;1010) を有し、

前記回路ブロック(1010)は、複数の機能ブロック(1110,1120,1130 ,1140)を有し、

前記第1および第2基板バイアス回路(3,4)は、前記各機能ブロック(1110,1 120,1130,1140)毎にそれぞれ設けられていることを特徴とする半導体集積 回路装置。

## 【請求項23】

請求項15に記載の半導体集積回路装置において、

該半導体集積回路装置は標準セル部(400)を有し、

前記第1および第2基板バイアス回路(3,4)は、前記標準セル部の各行毎にそれぞれ設けられていることを特徴とする半導体集積回路装置。

#### 【請求項24】

請求項15に記載の半導体集積回路装置において、

10

20

30

00

前記第1基板バイアス回路は、第1の電源線(Vss)と前記第1ウェル(10)のコンタクト領域(10a)との間に設けられた第1電流源(3)を備え、該第1ウェルのコンタクト領域(10a)を介して前記第1ダイオード(11)に前記所定電流(Ibp)を流し、且つ、

前記第2基板バイアス回路は、第2の電源線(Vdd)と前記第2ウェル(20)のコンタクト領域(20a)との間に設けられた第2電流源(4)を備え、該第2ウェルのコンタクト領域(20a)を介して前記第2ダイオード(21)に前記所定電流(Ibn)を流すことを特徴とする半導体集積回路装置。

#### 【請求項25】

請求項24に記載の半導体集積回路装置において、

前記第1電流源(3)は、前記第1の電源線(Vss)を電源として前記所定電流(Ibp)を発生し、且つ、前記第2電流源(4)は、前記第2の電源線(Vdd)を電源として前記所定電流(Ibn)を発生することを特徴とする半導体集積回路装置。

#### 【請求項26】

請求項25に記載の半導体集積回路装置において、

前記第1電流源(3)は、

第 1 制御信号( C b p )がゲート電極に供給され、ソース電極が前記第 2 の電源線( V d d )に接続された前記第 1 M I S F E T と同じ極性の第 1 電流源用第 1 M I S F E T ( 3 2 )と、

ソース電極が前記第1の電源線(Vss)に接続され、ドレイン電極およびゲート電極が前記第1電流源用第1MISFET(32)のドレイン電極に接続された前記第1MISFETと異なる極性の第1電流源用第2MISFET(33)と、

前記第1電流源用第2MISFET(33)に対してカレントミラー接続され、ドレインが前記第1ウェルのコンタクト領域(10a)に接続される第1電流源用第3MISFET(34)とを備え、且つ、

前記第2電流源(4)は、

第2制御信号(Cbn)がゲート電極に供給され、ソース電極が前記第1の電源線(Vss)に接続された前記第2MISFETと同じ極性の第2電流源用第1MISFET(42)と、

ソース電極が前記第2の電源線(Vdd)に接続され、ドレイン電極およびゲート電極が前記第2電流源用第1MISFET(42)のドレイン電極に接続された前記第2MISFET(43)と、

前記第2電流源用第2MISFET(43)に対してカレントミラー接続され、ドレインが前記第2ウェルのコンタクト領域(20a)に接続される第2電流源用第3MISFET(44)とを備えることを特徴とする半導体集積回路装置。

## 【請求項27】

請求項26に記載の半導体集積回路装置において、

前記第1電流源(3)は、さらに、

前記第1制御信号(Cbp)の反転信号がゲート電極に供給され、ソース電極が前記第1ウェルのコンタクト領域(10a)に接続され、且つ、ドレイン電極が前記第2の電源線(Vdd)に接続された前記第1MISFETと同じ極性の第1電流源用第4MISFET(30)を備え、且つ、

前記第2電流源(4)は、さらに、

前記第2制御信号(Cbn)の反転信号がゲート電極に供給され、ソース電極が前記第2ウェルのコンタクト領域(20a)に接続され、且つ、ドレイン電極が前記第1の電源線(Vss)に接続された前記第2MISFETと同じ極性の第2電流源用第4MISFET(40)を備えることを特徴とする半導体集積回路装置。

#### 【請求頃28】

請求項25に記載の半導体集積回路装置において、

前記第1電流源(3)は、

50

10

20

30

第 1 制御信号( C b p )がゲート電極に供給され、ソース電極が前記第 1 の電源線( V s s )に接続された前記第 1 M I S F E T と異なる極性の第 1 電流源用第 5 M I S F E T ( 3 4 ) と、

前記第1制御信号(Cbp)がゲート電極に供給され、ソース電極が前記第1ウェルのコンタクト領域(10a)に接続され、且つ、ドレイン電極が前記第2の電源線(Vdd)に接続された前記第1MISFETと同じ極性の第1電流源用第6MISFET(30)とを備え、且つ、

前記第2電流源(4)は、

第2制御信号(Cbn)がゲート電極に供給され、ソース電極が前記第2の電源線(Vdd)に接続された前記第2MISFETと異なる極性の第2電流源用第5MISFET(44)と、

前記第2制御信号(Cbn)がゲート電極に供給され、ソース電極が前記第2ウェルのコンタクト領域(20a)に接続され、且つ、ドレイン電極が前記第1の電源線(Vss)に接続された前記第2MISFETと同じ極性の第2電流源用第6MISFET(40)とを備えることを特徴とする半導体集積回路装置。

## 【請求項29】

請求項1~28のいずれか1項に記載の半導体集積回路装置において、該半導体集積回路 装置を、温度の上昇に従ってリーク電流が増大して遅延が減少する特性を示す低電圧で動 作させることにより、温度に対する動作遅延の変化を一定にしたことを特徴とする半導体 集積回路装置。

【発明の詳細な説明】

#### [0001]

【発明の属する技術分野】

本発明は半導体集積回路装置に関し、特に、低電圧で動作する高速のMISFETを備える半導体集積回路装置に関する。

#### [0002]

近年、例えば、携帯電話や携帯型PDA(Personal Digital Assistant)等の携帯情報機器の普及および高機能化に伴って、MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor:或いは、より広くMISFET(Metal-Insulator-Semiconductor FET))で構成した半導体集積回路装置に対しても、より一層の高速化並びに低消費電力化が望まれている。

#### [0003]

従来、СМОЅ(Сомр lementary MOЅ)回路の消費電力を低減するために駆動用の電源電圧を低下させることが行われてきた。しかしながら、電源電圧の低下は動作速度の低下をきたすため、高速動作を維持しつつ低消費電力を図るには、MOSトランジスタのしきい値電圧を下げる必要があった。ところで、MOSトランジスタのしきい値電圧の低下は、СМОS回路におけるスイッチング動作を高速化させることになるが、サブスレッショルドリーク電流が増加して消費電力の増大を招くことにもなる。

#### [0004]

そこで、近年、MOSトランジスタのウェル電圧(基板電圧:バックゲートの電圧)として順方向のバイアス電圧を印加することが注目されている。しかしながら、ウェル(基板)に対して順方向のバイアス電圧を印加するには、バイアス電圧発生回路による占有面積の増大等のさらなる問題も生じている。そこで、簡単な回路構成により適切なレベルの順方向基板(ウェル)バイアス電圧を発生することのできる基板バイアス回路を備えた半導体集積回路装置の提供が要望されている。

#### [0005]

## 【従来の技術】

近年、CMOS回路を高速且つ低消費電力で駆動するために、MOSトランジスタの基板(ウェル)に順方向のバイアス電圧を印加することが注目されている。

20

10

30

40

20

30

40

50

[0006]

具体的に、従来、アクティブ動作時には順方向基板バイアスFBBを与え、且つ、スタンバイモードでは零基板バイアスZBBを与えて、高速動作と低消費電力を両立した半導体集積回路装置(CMOSチップ)が提案されている(例えば、非特許文献1参照)。

[0007]

また、従来、MOSトランジスタに与える順方向の基板バイアス電圧を、温度上昇に対する異なる不純物濃度の拡散領域によるPN接合の電流電圧特性を利用して制御することで、温度変化が生じても大きなリーク電流が流れるのを防止した半導体集積回路装置が提案されている(特許文献1参照)。

[00008]

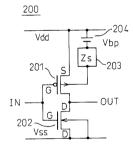

図1は従来の半導体集積回路装置の一例を示す回路図であり、前者(非特許文献 1: " 1.1 V 1 GHz Communications Router with ON-Chip Body Bias 150nm CMOS ")の要部構成を示すものである。図1において、参照符号200はインバータ部(CMOSインバータ)、201はpチャネル型MOSトランジスタ(pMOSトランジスタ)、202はnチャネル型MOSトランジスタ(nMOSトランジスタ)、202はnチャネル型MOSトランジスタ(nMOSトランジスタ)、そして、VbpはpMOSトランジスタ用基板バイアス電圧(pMOSトランジスタのnチャネル型ウェル領域(nウェル)に対するバイアス電圧)を示している。なお、各トランジスタにおいて、参照符号 I Nト電極、Dはドレイン電極、そして、Sはソース電極を示している。また、参照符号 I Nはインバータの入力を示し、OUTはインバータの出力を示している。

[0009]

図1に示されるように、従来の半導体集積回路装置の一例においては、pMOSトランジスタ201のnウェル(バックゲート)に対して、インピーダンス素子203を介して基板バイアス電圧Vbp(バイアス電圧発生回路204の出力電圧)を印加するようになっている。ここで、電源電圧Vddは、例えば、1.1Vであり、また、基板バイアス電圧Vbpは、Vdd-0.45V(例えば、0.55V)である。

[0010]

すなわち、図1に示す半導体集積回路装置において、例えば、動作時には p M O S トランジスタ2 0 1 の n ウェルに V d d - 0 . 4 5 V の順方向基板バイアス電圧 V b p を印加し、また、スタンバイモードでは零基板バイアス電圧を印加(基板バイアス電圧の印加を停止)することで動作時のしきい値電圧の低下(順方向基板バイアス電圧の印加)による高速化とスタンバイモードにおける消費電力の低減を両立するようになっている。なお、インピーダンス素子 2 0 3 は、例えば、温度上昇等により過大な電流が流れるのを制限するためのものである。

[ 0 0 1 1 ]

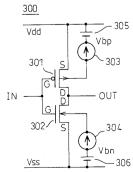

図2は従来の半導体集積回路装置の他の例を示す回路図である。図2において、参照符号300はインバータ部、301はpMOSトランジスタ、302はnMOSトランジスタ、303および304は電流源、そして、305および306はバイアス電圧発生回路を示している。なお、図2において、参照符号VbnはnMOSトランジスタ用基板バイアス電圧(nMOSトランジスタのpチャネル型基板(pチャネル型ウェル領域)に対するバイアス電圧)を示している。

[0012]

図 2 に示されるように、従来の半導体集積回路装置の他の例においては、 p M O S トランジスタ 3 0 1 の n チャネル型ウェル領域 ( n ウェル:バックゲート)に対して、電流源 3 0 3 を介して基板バイアス電圧 V b p (バイアス電圧発生回路 3 0 5 の出力電圧)を印加し、また、 n M O S トランジスタ 3 0 2 の p チャネル型ウェル領域 ( p ウェル:バックゲート)に対して、電流源 3 0 4 を介して基板バイアス電圧 V b n (バイアス電圧発生回路 3 0 6 の出力電圧)を印加するようになっている。ここで、 p M O S トランジスタ用基板

バイアス電圧 V b p は、高電位電源電圧 V d d よりも所定電圧だけ低い固定電圧であり、また、 n M O S トランジスタ用基板バイアス電圧 V b n は、低電位電源電圧 V s s よりも所定電圧だけ高い固定電圧である。

[0013]

すなわち、図 2 に示す半導体集積回路装置においては、例えば、MOSトランジスタに与える順方向の基板バイアス電圧を、温度上昇に対するp 拡散領域および n ウェルの間(p ウェルおよび n <sup>†</sup> 拡散領域の間)のPN接合の電流電圧特性とp <sup>†</sup> 拡散領域および n ウェルの間(p ウェルおよび n <sup>\*</sup> 拡散領域の間)のPN接合の電流電圧特性とを利用して制御することにより、ラッチアップの発生をなくして温度変化が生じても大きなリーク電流が流れるのを防止するものである。

[0014]

【非特許文献1】

S. Narendra et al., "1.1V 1GHz Communications Router with ON- Chip Body Bias 150nm CMOS", ISSCC 2002/SESSION 16/HIGH SPEED I/O 16.4, pp.270, 271, 466;

February 5, 2002

【特許文献1】

特開2001-345424号公報

[ 0 0 1 5 ]

【発明が解決しようとする課題】

上述したように、従来、MOSトランジスタの基板(ウェル)に順方向の基板バイアス電圧を与えてCMOS回路で構成される半導体集積回路装置を高速且つ低消費電力で駆動するようにしたものが提案されている。

[0016]

しかしながら、図1或いは図2に示す半導体集積回路装置においては、順方向の基板バイアス電圧(例えば、0.4~0.5 V程度)を発生するために所定の回路規模を有する基板電圧発生回路が必要なため、占有面積が増大するといった問題がある。さらに、順方向の基板バイアス電圧をある程度の余裕を持って設定する必要があるため、基板バイアス電圧が小さく抑えられ、トランジスタのしきい値電圧を最大限に低下させて高速動作を行うことは難しくなっている。

[0017]

本発明は、上述した従来の半導体集積回路装置が有する課題に鑑み、簡単な回路構成により適切なレベルの順方向基板(ウェル)バイアス電圧を発生することのできる基板バイアス回路を備えた半導体集積回路装置の提供を目的とする。

[0018]

【課題を解決するための手段】

本発明の第1の形態によれば、第1導電型のソース電極およびドレイン電極とゲート電極とを有し、第2導電型のウェルに形成されてなるMISFETを備える半導体集積回路装置であって、前記ウェルの電位を、前記MISFETのソース電極および該ウェルにより形成されるダイオードに対して所定電流を順方向に流すことにより生成する基板バイアス回路を備えることを特徴とする半導体集積回路装置が提供される。

[0019]

本発明の第2の形態によれば、第1導電型のソース電極およびドレイン電極とゲート電極とを有し、第2導電型の第1ウェルに形成されてなる第1極性の第1MISFET、並びに、前記第2導電型のソース電極およびドレイン電極とゲート電極とを有し、前記第1導電型の第2ウェルに形成されてなる第2極性の第2MISFETを備える半導体集積回路装置であって、前記第1ウェルの電位を、前記第1MISFETのソース電極および該第1ウェルにより形成されるダイオードに対して所定電流を順方向に流すことによって生成する第1基板バイアス回路と、前記第2ウェルの電位を、前記第2MISFETのソース

10

20

30

40

20

30

40

50

電極および該第2ウェルにより形成されるダイオードに対して所定電流を順方向に流すことによって生成する第2基板バイアス回路とを備えることを特徴とする半導体集積回路装置が提供される。

[0020]

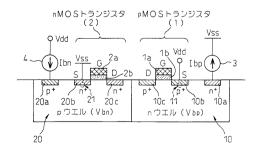

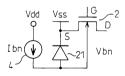

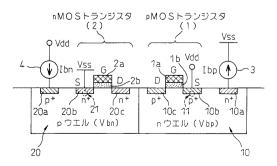

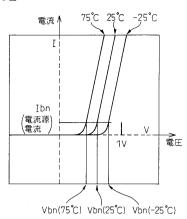

図3は本発明に係る半導体集積回路装置の原理構成を示す回路図であり、また、図4は本発明に係る半導体集積回路装置の原理構成を説明するための断面図である。ここで、図3に示す回路は、図4におけるnMOSトランジスタ(2)の部分に対応する。なお、pMOSトランジスタ1およびnMOSトランジスタ2で構成されるインバータ(CMOSインバータ)に関しては、図4も参照して後に詳述する。

[0021]

図 3 および図 4 において、参照符号 2 は n M O S トランジスタ、 4 は電流源、そして、 2 1 はダイオード (寄生ダイオード)を示している。また、図 4 において、参照符号 2 a は 導電電極、 2 b は絶縁膜、 2 0 は p チャネル型半導体基板( p チャネル型ウェル)、 2 0 a は p  $^+$  拡散領域、 2 0 b , 2 0 c は n  $^+$  拡散領域を示している。

[0022]

図3および図4に示されるように、nMOSトランジスタ2は、pチャネル型ウェル(pウェル)20に形成され、n<sup>+</sup>拡散領域(ソース電極S)20b、n<sup>+</sup>拡散領域(ドレイン電極D)20c、および、絶縁膜2bを介した導電電極(ゲート電極G)2aにより構成される。ここで、従来の一般的なpMOSトランジスタ(逆基板バイアスのトランジスタ)においては、p<sup>+</sup>拡散領域(コンタクト領域)20aを介してpウェル20(nMOSトランジスタ2のバックゲート)に対して低電位電源電圧Vssを印加するようになっているが、本発明においては、そのコンタクト領域(p<sup>+</sup>拡散領域)20aに対して、電流源4を介して高電位電源電圧Vddを与えるようになっている。なお、図3におけるダイオード21は、pウェル20とソース電極(S)20bとの間に形成される。

[0023]

本発明によれば、電流源4の出力電流(定電流)Ibnがpウェル20とソース電極S(n<sup>+</sup>拡散領域20b)で構成されるダイオード21に順方向に流れることで基板バイアス電圧Vbnが生成されるようになっている。ここで、電流Ibnは、例えば、動作時にスイッチング電流を含めて回路全体を流れる電流に対し、無視し得る程度の値(例えば、回路全体を流れる電流の1/10程度、或いは、それ以下)に設定される。

[0024]

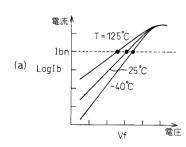

図 5 は本発明の半導体集積回路装置の原理を説明するためのダイオード特性を示す図である。

[0025]

図 5 に示されるように、ダイオード(2 1 )の電流・電圧特性は、各温度(例えば、 7 5 , 2 5 および・2 5 )に対して異なっている。本発明においては、ダイオード 2 1 に対して一定の電流源 4 の出力電流 I b n が流れることになるため、 p ウェル 2 0 に対して各温度における最大限の基板バイアス電圧を与えることができる。

[ 0 0 2 6 ]

すなわち、従来、 p ウェル 2 0 に与える順方向の基板バイアス電圧 V b n を考えた場合、例えば、半導体集積回路装置の規格値における上限の温度を考慮して(或いは、さらに所定のマージンも与えて:例えば、 7 5 )設定するため、順方向基板バイアス電圧( V b n )のレベルを高くしてトランジスタ( p M O S トランジスタ 2 )のしきい値電圧を可能な限り低くすることはできず、その結果、回路の動作速度を最大限に高速化することが困難であった。

[ 0 0 2 7 ]

これに対して、本発明の半導体集積回路装置によれば、回路の動作速度を使用される温度に応じて最大限に高速化することが可能である。また、本発明の半導体集積回路装置によれば、コンタクト領域をそのまま使用して電流源の出力をウェル(基板)に与え、ウェルとソース電極(拡散領域)により形成されるダイオ・ドを利用して基板バイアス電圧を発

20

30

40

50

生するため、簡単な回路構成で占有面積も小さく抑えることができる。さらに、本発明の 半導体集積回路装置によれば、順方向基板バイアス電圧を生成するための電流は、電流源 により規定されることになるため、温度変化等に依存することなく消費電力(回路を流れ る電流)を制御することができる。

[0028]

【発明の実施の形態】

以下、本発明に係る半導体集積回路装置の実施例を、添付図面を参照して詳述する。

[0029]

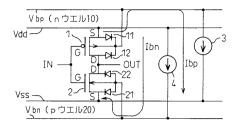

図 6 は本発明に係る半導体集積回路装置の一実施例を概念的に示す回路図であり、 C M O S インバータ部を示すものである。図 6 において、参照符号 1 は p M O S トランジスタ、 2 は n M O S トランジスタ、 1 1 , 1 2 ; 2 1 , 2 2 はダイオード (寄生ダイオード)、 そして、 3 , 4 は電流源を示している。

[0030]

図6および前述した図4に示されるように、nMOSトランジスタ2は、pウェル20に形成され、ソース電極S(n<sup>+</sup>拡散領域20b)、ドレイン電極D(n<sup>+</sup>拡散領域20c)、および、絶縁膜2bを介したゲート電極G(導電電極2a)により構成される。同様に、pMOSトランジスタ2は、nチャネル型ウェル(nウェル)10に形成され、ソース電極S(p<sup>+</sup>拡散領域)10b、ドレイン電極D(p<sup>+</sup>拡散領域)10c、および、絶縁膜1bを介したゲート電極G(導電電極)1a)により構成される。

[0031]

n M O S トランジスタ 2 において、コンタクト領域( p \* 拡散領域) 2 0 a には高電位電源電圧 V d d に繋がれた電流源 4 が接続され、 p ウェル 2 0 とソース電極 S ( n \* 拡散領域 2 0 b ) とで構成されるダイオード 2 1 に対して順方向の電流 I b n を流すようになっている。この電流 I b n が流されるダイオード 2 1 により p ウェル 2 0 には、所定の順方向基板バイアス電圧 V b n が発生する。ここで、図 5 を参照して前述したように、基板バイアス電圧 V b n は、動作温度に応じて最適なレベルに変化するため、すなわち、動作温度が高ければ(例えば、 7 5 のとき)、基板バイアス電圧 V b n は小さくなってトランジスタのしきい値電圧は高く設定され、また、動作温度が低ければ(例えば、 - 2 5 のとき)、基板バイアス電圧 V b n は大きくなってトランジスタのしきい値電圧は低く設定され、低いしきい値電圧のトランジスタによる回路の高速動作が十分に発揮されることになる。

[0032]

また、 p M O S トランジスタ 1 において、コンタクト領域( n <sup>+</sup> 拡散領域) 1 0 a には低電位電源電圧 V s s に繋がれた電流源 3 が接続され、 n ウェル 1 0 とソース電極 S ( p <sup>+</sup> 拡散領域 1 0 b ) とで構成されるダイオード 1 1 に対して順方向の電流 I b p を流すようになっている。この電流 I b p が流されるダイオード 1 1 により n ウェル 1 0 には、所定の順方向基板バイアス電圧 V b p が発生する。ここで、上述した n M O S トランジスタ 2 における基板バイアス電圧 V b p と同様に、 p M O S トランジスタ 1 における基板バイアス電圧 V b p は大きくなってトランジスタのしきい値電圧は近いで高ければ基板バイアス電圧 V b p は大きくなってトランジスタのしきい値電圧は低く設定され、低いしきい値電圧のトランジスタによる回路の高速動作が十分に発揮されることになる。

[0033]

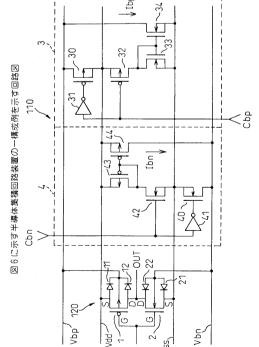

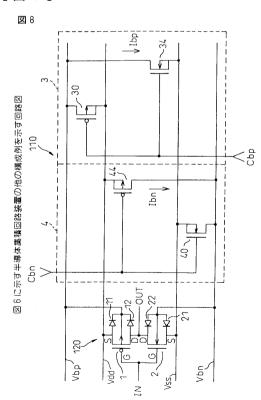

図 7 は図 6 に示す半導体集積回路装置の一構成例を示す回路図であり、基板バイアス回路 1 1 0 (電流源 3 , 4 )の一例を示すものである。

[0034]

図 7 に示されるように、電流源 4 は、インバータ 4 1 、 n M O S トランジスタ 4 0 , 4 2 および p M O S トランジスタ 4 3 , 4 4 を備えて構成されている。そして、制御信号 C b n が高レベル『 H 』のときに、 n M O S トランジスタ 4 2 がオンして p M O S トランジス

30

40

50

タ43に電流が流れ、さらに、pMOSトランジスタ43とカレントミラー接続されたpMOSトランジスタ44に電流Ibnが流れるようになっている。すなわち、制御信号Cbnが高レベル『H』のとき、高電位電源線(Vdd)からpMOSトランジスタ44、pウェル20(Vbn)およびダイオード21を介して低電位電源線(Vss:nMOSトランジスタ2のソース電極)に電流Ibnが流れるようになっている。ここで、制御信号Cbnが高レベル『H』のとき、nMOSトランジスタ40のゲートには、インバータ41により反転された低レベル『L』の制御信号Cbnが供給されるため、nMOSトランジスタ40はオフする。

[0035]

なお、制御信号 C b n が低レベル『 L 』のときは、 n M O S トランジスタ42がオフして n M O S トランジスタ40がオンするため、 n M O S トランジスタ2のバックゲート( p ウェル20)には低電位電源電圧 V s s が印加されることになる。

[0036]

また、電流源 3 は、インバータ 3 1、 p M O S トランジスタ 3 0 , 3 2 および n M O S トランジスタ 3 3 , 3 4 を備えて構成されている。そして、制御信号 C b p が低レベル『 L 』のときに、 p M O S トランジスタ 3 2 がオンして n M O S トランジスタ 3 3 に電流が流れ、さらに、 n M O S トランジスタ 3 3 とカレントミラー接続された n M O S トランジスタ 3 4 に電流 I b p が流れるようになっている。すなわち、制御信号 C b p が低レベル『 L 』のとき、高電位電源線(Vdd: p M O S トランジスタ 1 のソース電極)からダイオード 1 1、 n ウェル 1 0(V b p)および n M O S トランジスタ 3 4 を介して低電位電源線(Vss)に電流 I b p が流れるようになっている。ここで、制御信号 C b p が低レベル『 L 』のとき、 p M O S トランジスタ 3 0 のゲートには、インバータ 3 1 により反転された高レベル『 H 』の制御信号 C b p が供給されるため、 p M O S トランジスタ 3 0 はオフする。

[0037]

なお、制御信号 C b p が高レベル『 H 』のときは、 p M O S トランジスタ 3 2 がオフして p M O S トランジスタ 3 0 がオンするため、 p M O S トランジスタ 1 のバックゲート( n ウェル 1 0 )には高電位電源電圧 V d d が印加されることになる。

[ 0 0 3 8 ]

図 8 は図 6 に示す半導体集積回路装置の他の構成例を示す回路図であり、基板バイアス回路 1 1 0 (電流源 3 , 4 )の他の例を示すものである。

[0039]

すなわち、図 8 と図 7 との比較から明らかなように、本構成例において、電流源 4 は、 n M O S トランジスタ 4 0 および p M O S トランジスタ 4 4 を備え、制御信号 C b n が低レベル『L』のときに、 n M O S トランジスタ 4 0 がオフして p M O S トランジスタ 4 4 がオンし、この p M O S トランジスタ 4 4 に電流 I b n が流れるようになっている。なお、制御信号 C b n が高レベル『H』のときは、 n M O S トランジスタ 4 0 がオンするため、 n M O S トランジスタ 2 のバックゲート ( p ウェル 2 0 ) には低電位電源電圧 V s s が印加されることになる。

[0040]

また、電流源 3 は、 n M O S トランジスタ 3 4 および p M O S トランジスタ 3 0 を備え、制御信号 C b p が高レベル『H』のときに、 p M O S トランジスタ 3 0 がオフして n M O S トランジスタ 3 4 に電流 I b p が流れるようになっている。なお、制御信号 C b p が低レベル『L』のときは、 p M O S トランジスタ 3 0 がオンするため、 p M O S トランジスタ 1 のバックゲート ( n ウェル 1 0 ) には高電位電源電圧 V d d が印加されることになる。

[0041]

このように、図 8 に示す基板バイアス回路 1 1 0 (電流源 3 , 4 ) は、図 7 に示す基板バイアス回路よりも電流源 3 , 4 の安定性は多少劣るものの、図 7 の基板バイアス回路からn M O S トランジスタ 3 3 , 4 2 、 p M O S トランジスタ 3 2 , 4 3 、および、インバー

20

30

40

50

タ3 1 , 4 1 を省略して回路構成を簡略化することができるようになっている。なお、図8 に示す各電流源3 , 4 における制御信号 C b p , C b n の論理レベルと回路動作の関係は、図7 に示す各電流源3 , 4 における制御信号 C b p , C b n の論理レベルと回路動作の関係とは逆になっている。

[0042]

上述したように、図7或いは図8の回路において、基板バイアス電圧VbnおよびVbpの発生は、制御信号CbnおよびCbpのレベルに応じて制御される。ここで、制御信号Cbn,Cbpは、例えば、それぞれ1ビットの信号として構成することができる。また、基板バイアス回路110は、後述するように、例えば、回路ブロックや機能回路毎に設ければよく、その回路構成も単純で占有面積の小さいものとして構成することができる。さらに、回路構成も図7或いは図8の回路に限定されることなく様々に変更することができるのはいうまでもない。

[0043]

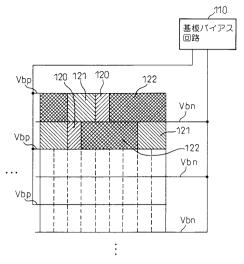

図 9 は本発明に係る半導体集積回路装置におけるインバータ部のレイアウトパターンの一例を示す図であり、図 1 0 は図 9 のインバータ部を複数有する半導体集積回路装置の一例を概略的に示す図である。

[0044]

図4並びに図6~図9に示されるように、nMOSトランジスタ2のpウェル20(コンタクト領域;p<sup>+</sup>拡散領域20a)にはバイアス電圧Vbnが印加され、また、pMOSトランジスタ1のnウェル10(コンタクト領域;n<sup>+</sup>拡散領域10a)にはバイアス電圧VbnおよびVbpは、例えば、第1層目の金属配線M12,M13およびM11,M14を介して基板バイアス回路110に接続される。ここで、高電位電源線(Vdd)および低電位電源線(Vss)は、例えば、第2層目の金属配線M21およびM22により共通接続されている。

[0045]

また、図9および図10に示されるように、各回路ブロックにおいては、例えば、複数のインバータ部(CMOSパターン)120、NAND部121、エクスクルーシブOR(EOR)122部等のゲートが規則的に配列され、基板バイアス回路110からのバイアス電圧(Vbn,Vbp)を各ゲート120,121,122等に供給するようになっている。

[0046]

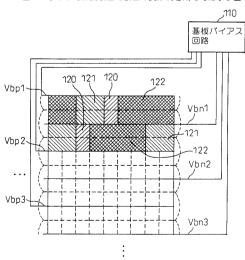

図11は図10に示す半導体集積回路装置の変形例を概略的に示す図である。

[0047]

図11と図10との比較から明らかなように、本変形例においては、論理ゲート(インバータ部120、NAND部121、EOR部122等)に対する各バイアス電圧(Vbn1,Vbn2,Vbn3,…;Vbp1,Vbp2,Vbp3,…)を基板バイアス回路110から独立に出力するようになっている。すなわち、図10の半導体集積回路装置では、基板バイアス回路110から1組のバイアス電圧Vbn,Vbpだけが出力されていたのに対して、図11に示す変形例では、基板バイアス回路110から複数組のバイアス電圧Vbn1,Vbp1;Vbn2,Vbp2;Vbn3,Vbp3;…が出力され、よりきめ細かな制御が可能となっている。

[0048]

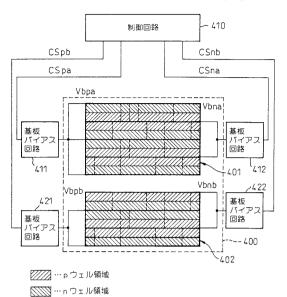

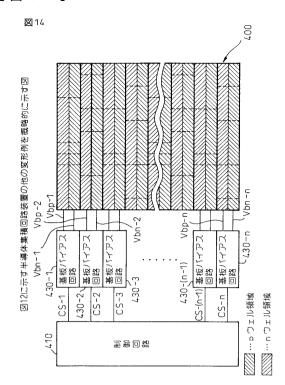

図12は図9のインバータ部を複数有する半導体集積回路装置の他の例を概略的に示す図であり、図13は図12に示す半導体集積回路装置の一変形例を概略的に示す図であり、そして、図14は図12に示す半導体集積回路装置の他の変形例を概略的に示す図である。図12~図14に示す各半導体集積回路装置は、各論理ゲート(各CMOS回路)を構成する行(ロウ)方向に配列されたpMOSトランジスタおよびnMOSトランジスタに着目したバイアス電圧の制御を示している。ここで、CMOS回路は、通常、同じ導電型(pチャネル型、或いは、nチャネル型)のトランジスタが行方向に整列され、且つ、図14の実施例を除き、2つのCMOS回路の同じ導電型のトランジスタが列(コラム)方

20

30

40

50

向に隣接するようにして形成されている。すなわち、CMOS構成の半導体集積回路装置において、列方向に隣接する2つのCMOS回路における同じ導電型のウェル領域(nウェル、或いは、pウェル)は一緒に形成されており、この各導電型のウェル領域に対して、それぞれバイアス電圧を印加するようになっている。

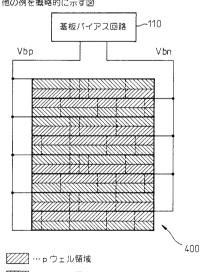

[0049]

図12に示す半導体集積回路装置は、前述した図10および図11に示す半導体集積回路装置を別の視点から描いたものであり、半導体集積回路装置を構成する標準セル部400に対して1つの基板バイアス回路110を設け、標準セル部400のpウェル領域およびnウェル領域に対して、基板バイアス回路110からそれぞれバイアス電圧VbpおよびVbnを印加するようになっている。

[0050]

図13に示す半導体集積回路装置は、標準セル部400を複数の(2つの)グループ401,402に分割し、各セルグループ401,402に対してそれぞれ基板バイアス回路411,412;421,422を設けるようになっている。ここで、図13に示す半導体集積回路装置では、各セルグループ401,402に対して、pウェル領域用の基板バイアス回路411,421およびnウェル領域用の基板バイアス回路4111,421を設け、それぞれ制御回路410からの制御信号CSpa,CSpbおよびCSna,CSnbにより基板バイアス電圧Vbpa,VbpbおよびVbna,Vbnbを制御するようになっている。

[0051]

図14に示す半導体集積回路装置では、異なる導電型のトランジスタが隣接しており、この場合には、隣接した領域でもそれぞれ独立して基板バイアス電圧を制御することができる。そして、標準セル部400の各行毎に基板バイアス回路430-1~430-nを設け、それぞれ制御回路410からの制御信号CS-1~CS-nにより基板バイアス電圧Vbp-1,Vbn-1~Vbp-n~Vbn-nを制御するようになっている。

[0052]

このように、標準セル部および基板バイアス回路(並びに、制御回路)の配置は、必要に応じて様々に変形することができる。なお、基板バイアス回路の構成は、例えば、図 7 および図 8 に示す回路をそのまま適用することができる。

[0053]

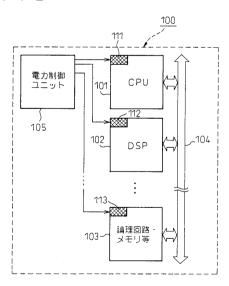

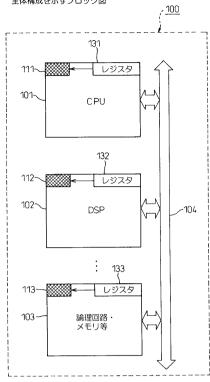

図 1 5 は本発明が適用された半導体集積回路装置の一例の全体構成を示すブロック図である。図 1 5 において、参照符号 1 0 0 は半導体集積回路装置(ワンチップIC)、 1 0 1 ~ 1 0 3 は各回路ブロックを示し、 1 0 1 はCPU(Central Processing Unit)、 1 0 2 はDSP(Digital Signal Processor)および 1 0 3 は論理回路・メモリ回路等の他の回路ブロック、 1 0 4 はバス、 1 0 5 は電力制御ユニット、そして、 1 1 1 ~ 1 1 3 は基板バイアス回路を示している。

[0054]

図15に示されるように、各回路ブロック101~103は、バス104を介して接続され、互いに様々なデータおよび信号を遣り取りするようになっている。各回路ブロック101~103には、それぞれ電力制御ユニット105からの制御信号により制御される基板バイアス回路111~113を備え、半導体集積回路装置100の動作状態に応じて、必要な回路ブロックの基板バイアス回路だけ活性化するようになっている。ここで、各基板バイアス回路111~113は、図7を参照して説明したような回路構成とすることができ、電力制御ユニット105から供給される制御信号の高レベル『H』か低レベル『L』か("1"か"0"か:1ビットの制御信号)により制御することが可能である。

[ 0 0 5 5 ]

すなわち、各回路ブロック101~103毎に簡単な回路構成で小型の基板バイアス回路 111~113を設け、動作状態に応じて各基板バイアス回路111~113の動作をそれぞれ1ビットの制御信号により制御することでより一層の低消費電力化を図ることができる。

20

30

40

50

[0056]

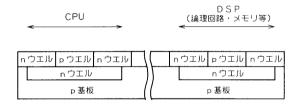

図16は図15に示す半導体集積回路装置の断面を概略的に示す図である。

[0057]

図16に示されるように、図15に示す複数の回路ブロック101~103を有する半導体集積回路装置(ワンチップIC)100は、例えば、トリプルウェル構造として構成され、各回路ブロック(CPU101、DSP102および論理回路・メモリ回路103等)は、それぞれ電気的に絶縁されるようになっている。これにより、各回路ブロック101~103毎に設けた基板バイアス回路111~113で独立して対応する回路ブロックの動作を制御するようになっている。

[0058]

図 1 7 は本発明が適用された半導体集積回路装置の他の例の全体構成を示すブロック図である。

[0059]

図17に示されるように、CPU101は、レジスタ131および基板バイアス回路111を備える。基板バイアス回路111は、レジスタ131に格納されたデータに従って制御される。同様に、DSP102は、レジスタ132、および、該レジスタ132に格納されたデータに従って制御される基板バイアス回路112を備え、また、論理回路・メモリ回路103は、レジスタ133、および、該レジスタ133に格納されたデータに従って制御される基板バイアス回路113を備える。ここで、ソフトウェアモジュールとして間からで電力制御動作は、CPU101で実行される。すなわち、ソフトウェアモジュールは、CPU101のキャッシュメモリまたは外部のメモリに記憶される。レジスタ112および113は、データバス104に接続され、該各レジスタ112,113のデータは、CPU101からデータバス104を介して書き込まれる。

[0060]

この例によれば、電力管理機構(消費電力制御)は容易に変更することができ、そのため、電力管理は、ワンチップIC100の構成や動作するアプリケーションに従って簡単にカスタマイズすることができる。

[0061]

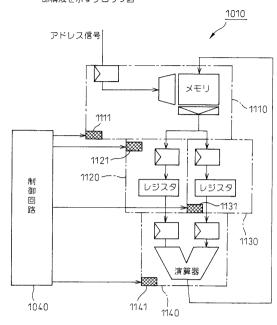

図 1 8 は本発明が適用された半導体集積回路装置の他の例における一部構成を示すブロック図であり、例えば、CPU 1 0 1 0 (図 1 5 の CPU 1 0 1 に相当)を示すものである

[0062]

図18に示されるように、CPU1010は、複数の機能ブロック1110~1140を備えて構成され、これら各機能ブロック1110~1140を備えて構成され、これら各機能ブロック1110~1140に対してそれぞれ基板バイアス回路1111~1141を設けるようになっている。すなわち、メモリブロック1110に対してはメモリプロック1110に対してはメモリプロック用基板バイアス回路11118設け、レジスタブロック1120および1130に対してはそれぞれレジスタブロック用基板バイアス回路1121および1131を設け、そして、演算器ブロック1140に対しては演算器ブロック用基板バイアス回路1111~1141は、制御回路1040からの各機能ブロック用の制御信号によりそれぞれ対応する機能ブロック1110~1140における基板バイアス電圧(Vbp,Vbn)を制御するようになっている。

[0063]

このように、基板バイアス電圧(Vbp,Vbn)の制御は、図15に示すようなCPU 101やDSP102といった回路ブロック単位ではなく、このような回路ブロック(例 えば、CPU)におけるより細かな機能ブロックを対象として制御することもできる。

[0064]

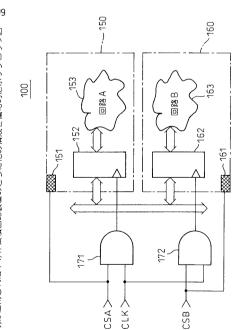

図 1 9 は本発明が適用された半導体集積回路装置のさらに他の構成を概略的に示すブロック図であり、ゲーティドクロック回路と組み合わせた場合の回路の一例を概略的に示すものである。

[0065]

図19に示されるように、半導体集積回路装置は、回路ブロック150の回路A(153)および回路ブロック160の回路B(163)に対して制御信号CSAおよびCSBとクロック信号CLKとの論理出力をクロックとしてそれぞれ供給するようになっている。すなわち、例えば、回路ブロック150におけるフリップフロップ152のクロック入力には、制御信号CSAとクロック信号CLKの論理積をとるANDゲート171の出力信号が供給され、また、回路ブロック160におけるフリップフロップ162のクロック入力には、制御信号CSBとクロック信号CLKの論理積をとるANDゲート172の出力信号が供給されている。さらに、回路ブロック150には、制御信号CSAにより制御される基板バイアス回路161が設けられている。

[0066]

すなわち、回路プロック150,160に対してそれぞれ基板バイアス回路151,161を設け、その基板バイアス回路151,161の制御信号としてゲーティドクロック回路用の制御信号CSA,CSBをそのまま利用するようになっている。これにより、回路プロック150,160がそれぞれ動作が必要でない時には、制御信号CSA,CSBによりフリップフロップ152,162に入力されるクロックを止めてAC電力を削減する一方、基板バイアス回路151,161により基板バイアスを制御してリーク電力を削減できる効果がある。

[0067]

ところで、従来、低電圧におけるCMOS回路では、温度が上昇すると遅延が減少することが知られている。具体的に、K. Kanda et al., "Design Impact of Positive Temperature Dependence on Drain Current in Sub-1-V CMOS VLSI",IEEE J. Solid-State Circuits, vol. 36,No. 10, pp.1559-1564, October 2001 には、ZTC(Zero-Temperature Coefficient)ポイントよりも低い電源電圧(例えば、0.5V:0.7V以下の低電圧)でCMOS回路を動作させたとき、それまでの高い電源電圧(例えば、3.3V)での動作とは異なり、温度の上昇に従って遅延が減少することが報告されている。

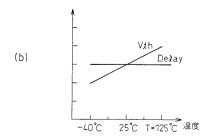

[ 0 0 6 8 ]

図 2 0 はトランジスタの遅延時間の温度依存性を説明するための図であり、図 2 0 (a)はダイオードを流れる電流 I b とそれにより発生する電圧 V f との関係を示し、また、図 2 0 (b)は本発明を低電圧(例えば、0.7 V以下)で動作する C M O S 回路に適用した場合を概念的に示すものである。

[0069]

本発明に係る半導体集積回路装置においては、例えば、図20(a)に示されるように(或いは、図5を参照して説明したように)、ダイオードを流れる電流 I b ( すなわち、図6および図7におけるダイオード21を流れる基板バイアス電流 I b n )を一定にしたとき、温度上昇に従って発生する電圧 V f ( 基板バイアス電圧 V b n )の値は小さくなる。【0070】

そのため、図20(b)に示されるように、温度上昇に従ってトランジスタのしきい値電圧 V t h は大きくなる。従って、本発明を、例えば、0.7V以下の低電圧で動作するCMOS回路に対して適用すると、上述した論文("Design Impact of Positive Temperature Dependence on Drain Current in Sub-1-V CMOS VLSI")にも示された低電圧動作のCMOS回路における温度の上昇に従って遅延が減少する特性が打ち消され(定性的に相殺され)、回路動作速度の遅延(Delay)を温度変化に依らず一定にすることが可能になる。

[ 0 0 7 1 ]

20

30

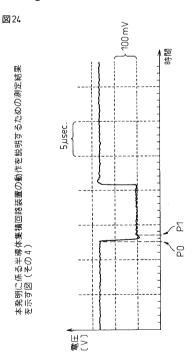

図21~図24は本発明に係る半導体集積回路装置の動作を説明するための測定結果を示す図である。

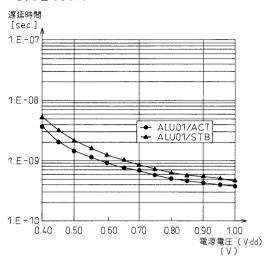

#### [0072]

図 2 1 は 3 2 ビットA L U (A r i t h m e t i c a n d L o g i c U n i t )を 2 7 で駆動したとき、基板バイアス回路を動作させた場合(A L U 0 1 / A C T )と基板バイアス回路を停止させた場合(A L U 0 1 / S T B )の電源電圧(V d d )に対する遅延時間の変化を測定した図である。

## [0073]

図 2 1 から明らかなように、電源電圧 V d d が 0 . 4 0 V ~ 1 . 0 0 V の全ての範囲において、基板バイアス回路を動作させない場合よりも動作させた場合の方が遅延時間の低減が可能なことが分かる。

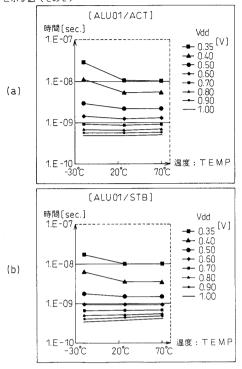

#### [0074]

図 2 2 は 3 2 ビット A L U を各電源電圧 V d d ( V d d = 0 . 3 5 , 0 . 4 0 , 0 . 5 0 , 0 . 6 0 , 0 . 7 0 , 0 . 8 0 , 0 . 9 0 , 1 . 0 0 V ) で温度 T を変化させて駆動したときの遅延時間の変化を測定した図であり、図 2 2 ( a ) は基板バイアス回路を動作させた場合 ( A L U 0 1 / アクティブ ) を示し、図 2 2 ( b ) は基板バイアス回路を停止させた場合 ( A L U 0 1 / スタンバイ ) を示すものである。

#### [0075]

図22(a)と図22(b)との比較から明らかなように、各電源電圧Vddおよび各温度TEMPにおいて、基板バイアス回路を動作させない場合よりも動作させた場合の方が遅延時間の低減が可能であるが、特に、電源電圧Vddが低い程且つ動作温度TEMPが低い程、遅延時間低減の効果が顕著なことが分かる。

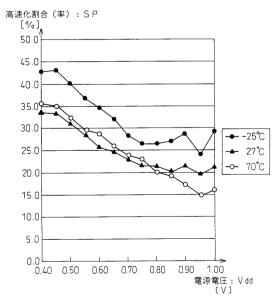

## [0076]

図23は32ビットALUを各温度(70 ,27 および・25 )で電源電圧Vddを変化させて駆動したときの高速化割合(率)SPの変化を示すものである。ここで、高速化割合SPは、SP=(1-ACT/STB)×100[%]として求められる。なお、ACTは基板バイアス回路を動作させた場合の遅延時間を示し、また、STBは基板バイアス回路を動作させない場合の遅延時間を示している。

## [ 0 0 7 7 ]

図 2 4 は p M O S トランジスタの n ウェル( 1 0 )において、制御信号 C b p による基板バイアス電圧の発生と、それによる n ウェルの電圧レベルの変化をシミュレートしたものである。

#### [0078]

図 2 4 から明らかなように、例えば、図 4 に示す n ウェル 1 0 の電圧レベルは、タイミング P 0 において制御信号 C b p が変化(低レベル『L』から高レベル『H』へ変化:図 7 参照)すると直ちに下降し、タイミング P 1 において順方向バイアス電圧が印加された所定の電圧(Vbn)になることが分かる。なお、制御信号 C b p が高レベル『H』から低レベル『L』へ変化すると、図 7 を参照して説明した n M O S トランジスタ 4 2 がオフして n M O S トランジスタ 4 0 がオンすることにより、 n ウェル 1 0 の電圧レベルは再び元の電圧(Vss)に直ちに戻ることになる。すなわち、例えば、図 7 に示されるように、基板バイアス回路 1 1 0 (電流源 3 ) は、制御信号 C b p (例えば、1 ビットの信号)の変化に応じて直ちに動作することが可能である。

#### [0079]

## 【発明の効果】

以上、詳述したように、本発明によれば、簡単な回路構成により適切なレベルの順方向基板(ウェル)バイアス電圧を発生することのできる基板バイアス回路を備えた半導体集積 回路装置を提供することができる。

#### 【図面の簡単な説明】

【図1】従来の半導体集積回路装置の一例を示す回路図である。

【図2】従来の半導体集積回路装置の他の例を示す回路図である。

50

10

20

30

20

30

40

- 【図3】本発明に係る半導体集積回路装置の原理構成を示す回路図である。

- 【図4】本発明に係る半導体集積回路装置の原理構成を説明するための断面図である。

- 【 図 5 】 本 発 明 の 半 導 体 集 積 回 路 装 置 の 原 理 を 説 明 す る た め の ダ イ オ ー ド 特 性 を 示 す 図 で あ る 。

- 【図6】本発明に係る半導体集積回路装置の一実施例を概念的に示す回路図である。

- 【図7】図6に示す半導体集積回路装置の一構成例を示す回路図である。

- 【図8】図6に示す半導体集積回路装置の他の構成例を示す回路図である。

- 【図9】本発明に係る半導体集積回路装置におけるインバータ部のレイアウトパターンの 一例を示す図である。

- 【図10】図9のインバータ部を複数有する半導体集積回路装置の一例を概略的に示す図である。

- 【図11】図10に示す半導体集積回路装置の変形例を概略的に示す図である。

- 【図12】図9のインバータ部を複数有する半導体集積回路装置の他の例を概略的に示す図である。

- 【図13】図12に示す半導体集積回路装置の一変形例を概略的に示す図である。

- 【図14】図12に示す半導体集積回路装置の他の変形例を概略的に示す図である。

- 【図 1 5 】本発明が適用された半導体集積回路装置の一例の全体構成を示すブロック図である。

- 【図16】図15に示す半導体集積回路装置の断面を概略的に示す図である。

- 【 図 1 7 】 本 発 明 が 適 用 さ れ た 半 導 体 集 積 回 路 装 置 の 他 の 例 の 全 体 構 成 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【 図 1 8 】 本 発 明 が 適 用 さ れ た 半 導 体 集 積 回 路 装 置 の 他 の 例 に お け る 一 部 構 成 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【図19】本発明が適用された半導体集積回路装置のさらに他の構成を概略的に示すブロック図である。

- 【図20】トランジスタの遅延時間の温度依存性を説明するための図である。

- 【図21】本発明に係る半導体集積回路装置の動作を説明するための測定結果を示す図(その1)である。

- 【図22】本発明に係る半導体集積回路装置の動作を説明するための測定結果を示す図( その2)である。

- 【図23】本発明に係る半導体集積回路装置の動作を説明するための測定結果を示す図( その3)である。

- 【図24】本発明に係る半導体集積回路装置の動作を説明するための測定結果を示す図(その4)である。

- 【符号の説明】

- 1 ... p M O S トランジスタ

- 2 ... n M O S トランジスタ

- 3 , 4 ... 電流源

- 1 0 0 ... 半導体集積回路装置

- 1 0 1 ... C P U

- 1 0 2 ... D S P

- 1 0 3 ... 論理回路・メモリ等

- 104…バス

- 1 0 5 ... 電力制御ユニット

- 1 1 0 ; 1 1 1 ~ 1 1 3 ; 4 1 1 , 4 1 2 , 4 2 1 , 4 2 2 ; 4 3 0 1 ~ 4 3 0 n ;

- 1 1 1 1 1 , 1 1 2 1 , 1 1 3 1 , 1 1 4 1 ; 1 5 1 , 1 6 1 ... 基板バイアス回路

- 120,200,300...インバータ部(СМОЅインバータ)

- 131,132,133...レジスタ

- G ... ゲート電極

- D ... ドレイン電極

S ... ソース電極

Vbn... pMOSトランジスタ用基板バイアス電圧

V b p ... n M O S トランジスタ用基板バイアス電圧

V d d ... 高電位電源電圧(高電位電源線)

V s s ... 低電位電源電圧(低電位電源線)

## 【図1】

図1 従来の半導体集積回路装置の一例を示す回路図

## 【図2】

図 2 従来の半導体集積回路装置の他の例を示す回路図

## 【図3】

図3

本発明に係る半導体集積回路装置の原理構成を示す回路図

## 【図4】

図 4

本発明に係る半導体集積回路装置の原理構成を説明するための 断面図

## 【図5】

## 図 5

・ 本発明の半導体集積回路装置の原理を説明するためのダイオード 特性を示す図

## 【図6】

#### 図 6

本発明に係る半導体集積回路装置の一実施例を概念的に示す 回路図

## 【図7】

# 図 7

## 【図8】

## 【図9】

## 図 9

本発明に係る半導体集積回路装置におけるインバータ部 のレイアウトバターンの一例を示す図

120 .10a(n+) ,Vdd (M21) S(10b:p+) ν̈́ьр(М11) pMOS(1) 10-M14-D(10c:p+) M13\_IN-\_OUT -D(20c:n+) 20~ nMOS(2) S(20b:n+)-Vbn (M12)

20a(p+)

Vss (M22)

## 【図10】

#### 図10

図9のインバータ部を複数有する回路ブロックを概略的に示す図

## 【図11】

#### 図11

図10に示す半導体集積回路装置の変形例を概略的に示す図

## 【図12】

#### 図 12

図9のインバータ部を複数有する半導体集積回路装置の 他の例を概略的に示す図

...nウェル領域

## 【図13】

#### 図13

図12に示す半導体集積回路装置の一変形例を概略的に示す図

## 【図14】

## 【図15】

#### 図15

本発明が適用された半導体集積回路装置の一例の全体構成を示す ブロック図

## 【図16】

図 16 図15に示す半導体集積回路装置の断面を概略的に示す図 <u>100</u>

## 【図17】

図17 本発明が適用された半導体集積回路装置の他の例の 全体構成を示すプロック図

## 【図18】

## 図 18

本発明が適用された半導体集積回路装置の他の例における 一部構成を示すブロック図

## 【図19】

## 【図20】

## 図20

トランジスタの遅延時間の温度依存性を説明するための図

## 【図21】

#### 図21

本発明に係る半導体集積回路装置の動作を説明するための測定結果を示す図(その1)

## 【図22】

#### 図22

本発明に係る半導体集積回路装置の動作を説明するための測定結果を示す図 (その2)

## 【図23】

#### 図23

本発明に係る半導体集積回路装置の動作を説明するための測定結果 を示す図(その3)

## 【図24】

## フロントページの続き

(72)発明者 石橋 孝一郎 埼玉県蕨市南町 3 - 7 - 6

(72)発明者 山下 高廣

東京都墨田区太平4-20-5 錦糸町ローヤルコーポ408

F ターム(参考) 5F038 AV06 AZ08 BG01 BG06 BG09 CA03 CA05 CA08 CD02 DF04

DF05 DF11 DF14 EZ20

5F048 AB03 AB04 AB10 AC03 BA01 BB14 BE02 BE03 BE09 BF17