### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-125971 (P2013-125971A)

(43) 公開日 平成25年6月24日 (2013.6.24)

(51) Int.Cl.

F 1

テーマコード (参考)

HO1L 21/02

(2006, 01)

HO1L 21/02

С

審査請求 未請求 請求項の数 28 OL 外国語出願 (全 15 頁)

(21) 出願番号 特願2012-273332 (P2012-273332) (22) 出願日 平成24年12月14日 (2012.12.14)

(31) 優先権主張番号 13/374,206

(32) 優先日 平成23年12月15日 (2011.12.15)

(33) 優先権主張国 米国(US)

(71) 出願人 501315784

パワー・インテグレーションズ・インコー

ポレーテッド

アメリカ合衆国・95138・カリフォルニア州・サン ホゼ・ヘリヤー アベニュ

ー/州・ザン ボセ・ベリヤー / ベ. ・5245

(74)代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 アレクセイ・コーディモフ

アメリカ合衆国、12180 ニュー・ヨーク州、トロイ、グラニット・レーン、3

(72) 発明者 ジャマル・ラムダニ

アメリカ合衆国、08869 ニュー・ジャージー州、ラリタン、リバー・パーク・

ドライブ、352

最終頁に続く

(54) 【発明の名称】半導体装置の製造のための複合ウェハ

### (57)【要約】 (修正有)

【課題】製造工程での薄いウエーハの機械的支持方法を 提供する。

【解決手段】複合ウェハは、垂直方向の第1の厚みおよび上面を有する第1の基板を含み、上面は、後の半導体材料エピタキシャル堆積のための状態に準備されている。第1の基板の下にキャリア基板102が配置される。キャリア基板102は、垂直方向の第1の厚みよりも大きい垂直方向の第2の厚みを有する。中間層が、第1の基板をキャリア基板に接合する。

【選択図】図1D

FIG. 1D

#### 【特許請求の範囲】

## 【請求項1】

複合ウェハであって、

垂直方向の第1の厚みおよび上面を有する第1の基板を備え、前記上面は、後の半導体材料エピタキシャル堆積のための状態に準備されており、前記複合ウェハはさらに、

前記第1の基板の下に配置されたキャリア基板を備え、前記キャリア基板は、垂直方向の前記第1の厚みよりも大きい垂直方向の第2の厚みを有し、前記複合ウェハはさらに、

前記第1の基板を前記キャリア基板に接合する中間層を備える、複合ウェハ。

## 【請求項2】

前記第1の厚みは約100~200μmの範囲内にある、請求項1に記載の複合ウェハ

【請求項3】

前記第2の厚みは約400μm以上である、請求項1に記載の複合ウェハ。

【請求項4】

前記第1の基板はサファイアを含む、請求項1に記載の複合ウェハ。

【請求項5】

前記キャリア基板は、サファイア、シリコン、炭化珪素、ダイアモンド、窒化ガリウム、窒化アルミニウム、窒化ホウ素、および酸化亜鉛からなるグループから選択される、請求項1に記載の複合ウェハ。

【請求項6】

前記上面は研磨された状態にある、請求項1に記載の複合ウェハ。

【請求項7】

第1の基板をキャリア基板に接合するステップを備え、前記第1の基板は、上面を有し、第1の材料の種類であり、第1の厚みを有し、前記キャリア基板は、第2の材料の種類であり、前記第1の厚みよりも大きい第2の厚みを有し、さらに、

前記第1の基板の上に1つ以上の窒化物層を形成するステップと、

前記1つ以上の窒化物層の中に窒化物系半導体装置を製造するステップとを備える、方法。

【請求項8】

前記キャリア基板を剥離するステップをさらに備える、請求項7に記載の方法。

【請求項9】

前記接合するステップは、前記第1の基板と前記キャリア基板との間に、前記キャリア基板を前記第1の基板に接合する中間層を形成するステップを含む、請求項7に記載の方法。

【請求項10】

前記中間層は二酸化珪素を含む、請求項9に記載の方法。

【請求項11】

前記第1の基板はサファイアを含み、前記第1の厚みは約100~200μmの範囲内にある、請求項7に記載の方法。

【請求項12】

前記第2の厚みは約400μm以上である、請求項7に記載の方法。

【請求項13】

前記キャリア基板は、サファイア、シリコン、炭化珪素、ダイアモンド、窒化ガリウム、窒化アルミニウム、窒化ホウ素、および酸化亜鉛からなるグループから選択される、請求項7に記載の方法。

【請求項14】

前記剥離するステップは、、化学溶液中のウェットエッチングを実行するステップを含む、請求項8に記載の方法。

【請求項15】

前記室化物系半導体装置はウェハの個々のダイの上に形成され、

20

10

30

40

前記剥離するステップの前に、前記個々のダイを分離するステップをさらに備える、請求項8に記載の方法。

#### 【請求項16】

前記室化物系半導体装置はウェハの個々のダイの上に形成され、

前記剥離するステップの後に、前記個々のダイを分離するステップをさらに備える、請求項8に記載の方法。

#### 【 請 求 項 1 7 】

前記1つ以上の窒化物層を形成するステップの前に、前記第1の基板の前記上面を研磨するステップをさらに備える、請求項7に記載の方法。

### 【請求項18】

1 7 1

10

20

30

前記上面を研磨するステップによって、原子的に平坦な上面が得られる、請求項17に記載の方法。

#### 【請求項19】

第1の基板およびキャリア基板を提供するステップを備え、前記第1の基板は、第1の材料の種類であり、100~200μmの範囲内にある第1の厚みを有し、前記キャリア基板は、第2の材料の種類であり、少なくとも350μmの第2の厚みを有し、さらに、前記第1の基板を前記キャリア基板に接合するステップを備える、方法。

#### 【請求項20】

前記接合するステップは、前記第1の基板と前記キャリア基板との間に中間層材料を形成するステップを含み、前記中間層材料は、前記第1の基板および前記キャリア基板の両方に付着する、請求項19に記載の方法。

#### 【請求項21】

前記接合するステップは、前記第1の基板を前記キャリア基板に接着剤で付けるステップを含む、請求項19に記載の方法。

#### 【請求項22】

前記第1および第2の材料の種類は、互いに実質的に一致する第1および第2の熱膨張係数をそれぞれ有する、請求項19に記載の方法。

#### 【請求項23】

前記第1の材料の種類は、サファイア、ダイアモンド、窒化ガリウム、窒化アルミニウム、窒化ホウ素、炭化珪素、および酸化亜鉛からなるグループから選択される、請求項19に記載の方法。

## 【請求項24】

前記第2の材料の種類は、シリコン、サファイア、および銅からなるグループから選択される、請求項19に記載の方法。

#### 【請求項25】

前記第1の基板の上に窒化物系半導体装置を製造するステップをさらに備える、請求項 19に記載の方法。

### 【請求項26】

前記キャリア基板から前記第1の基板を剥離するステップをさらに備える、請求項19に記載の方法。

## 【請求項27】

前記室化物系半導体装置は複数のダイとして製造され、

前記キャリア基板から前記第1の基板を剥離するステップと、

前記ダイの各々を個別化するステップとをさらに備える、請求項25に記載の方法。

#### 【請求項28】

前記室化物系半導体装置は複数のダイとして製造され、

前記ダイの各々を個別化するステップと、

個別化した前記ダイの各々について、前記キャリア基板から前記第1の基板を剥離するステップとをさらに備える、請求項25に記載の方法。

## 【発明の詳細な説明】

50

#### 【技術分野】

## [0001]

発明の詳細な説明

技術分野

本発明は一般に、基板上に半導体装置を製造するための半導体装置構造およびプロセスに関し、より特定的には、複合ウェハを利用して化合物半導体装置を製作する装置および方法に関する。

## 【背景技術】

[0002]

背景

フロントエンドオブライン(front-end-of-line: FEOL)処理とは、たとえばシリコンまたは窒化物系化合物半導体材料などの半導体材料中に電子装置(トランジスタなど)を直接形成することである。半導体材料は通常、ウェハと称される薄い円盤上に形成される。バックエンドオブライン(back-end-of-line: BEOL)処理とは、ウェハの表面上で個々の装置を金属(たとえばパターニングラインまたはトレース)と相互接続させる、製作プロセスの第二部である。BEOL処理の後、製造後処理(一般にバックエンド処理とも称される)を行う。バックエンド処理工程は典型的に、ウェハテスト、ウェハ裏面研削(裏面ラップ仕上げまたはウェハ薄板化とも称される)、ダイ分離、ダイ試験、パッケージング、および最終の装置試験を含む。

[0003]

ほとんどの場合、半導体ウェハは、FEOLおよびBEOL処理時の機械的安定性を確保する厚みを有して製作される。材料の種類にもよるが、たとえば、約650~750μmの厚みを有する直径4インチのウェハは通常、高温処理工程時の割れや反りを回避するのに十分な安定性を提供する。ウェハ裏面研削は、ウェハの厚みを減少させてダイ分離をより容易にし、かつ集積回路(ΙC)の高密度パッケージングを可能にする、バックエンド処理工程である。ダイ分離では、個々のダイまたはマイクロチップを単体化する。この分離プロセスは典型的に、(たとえばレーザを用いて)ウェハを機械的に切削またはウェハに刻みを付けた後、スクライブラインに沿ってウェハを切断して個々のダイを分離することを含む。

[0004]

特に明記しない限りさまざまな図面全体にわたって同様の参照番号は同様の部分を指す以下の図面を参照して、本発明の非限定的および非網羅的な実施例を説明する。

【図面の簡単な説明】

[0005]

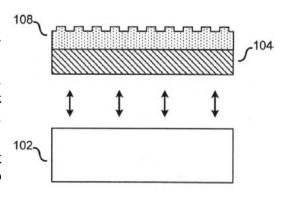

【図1A】本発明の実施例に従った、製造プロセスのある段階における例示的なウェハ構造を示す断面側面図である。

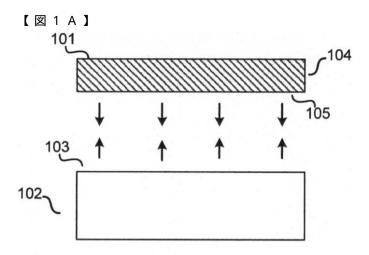

【図1B】本発明の実施例に従った、製造プロセスのある段階における例示的なウェハ構造を示す断面側面図である。

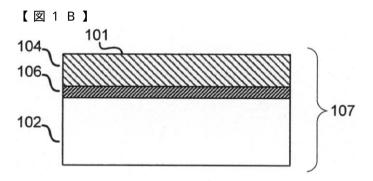

【図1C】本発明の実施例に従った、製造プロセスのある段階における例示的なウェハ構造を示す断面側面図である。

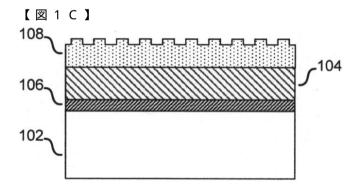

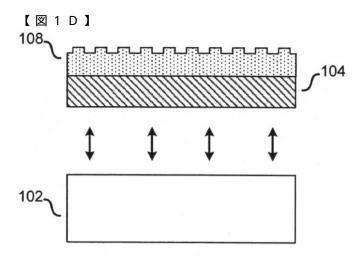

【図1D】本発明の実施例に従った、製造プロセスのある段階における例示的なウェハ構造を示す断面側面図である。

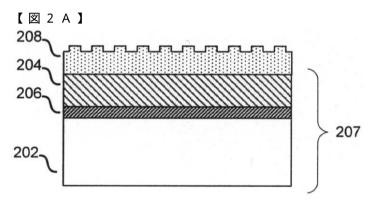

【図2A】本発明の実施例に従った、製造プロセスのある段階における別の例示的なウェ ハ構造を示す断面側面図である。

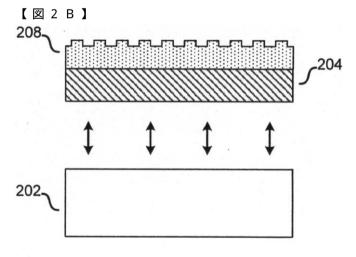

【図2B】本発明の実施例に従った、製造プロセスのある段階における別の例示的なウェ ハ構造を示す断面側面図である。

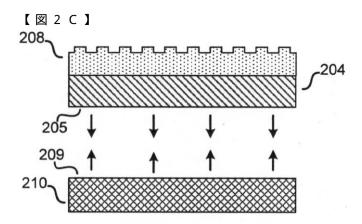

【図2C】本発明の実施例に従った、製造プロセスのある段階における別の例示的なウェ ハ構造を示す断面側面図である。

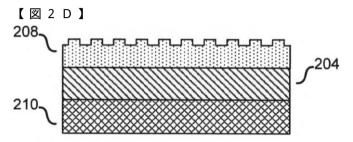

【図2D】本発明の実施例に従った、製造プロセスのある段階における別の例示的なウェ ハ構造を示す断面側面図である。 10

20

30

40

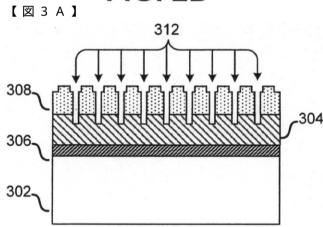

【図3A】本発明の実施例に従った、ダイ分離プロセスのある段階における例示的なウェ ハ構造を示す断面側面図である。

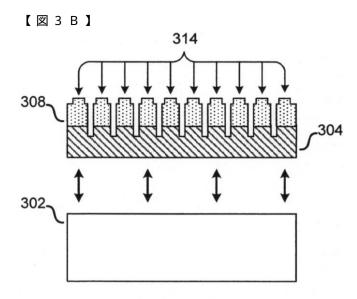

【図3B】本発明の実施例に従った、ダイ分離プロセスのある段階における例示的なウェ ハ構造を示す断面側面図である。

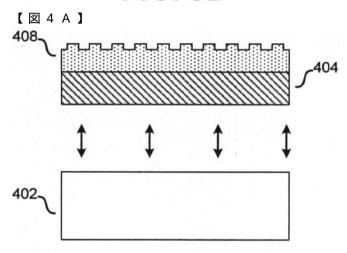

【図4A】本発明の実施例に従った、別のダイ分離プロセスのある段階における例示的なウェハ構造を示す断面側面図である。

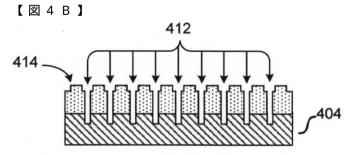

【図4B】本発明の実施例に従った、別のダイ分離プロセスのある段階における例示的なウェハ構造を示す断面側面図である。

【発明を実施するための形態】

## [0006]

図面のいくつかの図全体にわたって、対応する参照符号は対応する構成要素を示す。当業者であれば、図中の要素は簡単および明確にするために図示されており、必ずしも同じ割合で描かれているとは限らないことを認識するであろう。たとえば、図中のいくつかの要素の寸法は、本発明のさまざまな実施例をよりよく理解する助けとなるように、他の要素に対して誇張されていることがある。また、本発明のこれらのさまざまな実施例をより見やすくするために、商業的に実現可能な実施例において有用または必要な、一般的であるがよく理解された要素は描かれていない場合が多い。

## [0007]

以下の説明では、本発明の完全な理解を提供するために多数の特定的な詳細を記載する。しかし、本発明を実行するのに特定的な詳細を用いる必要はないことが当業者にとって明らかになるであろう。他の例では、本発明を不明瞭にするのを避けるために周知の材料または方法は詳細に説明していない。

#### [00008]

本明細書全体にわたって「一実施例」、「実施例」、「一例」または「例」と記載する場合、その実施例または例に関連して説明する特定の特徴、構造または特性が本発明の少なくとも一実施例に含まれることを意味する。したがって、本明細書全体にわたってきずまな箇所で「一実施例において」、「実施例において」、「一例」または「例」という語句が出てきたとしても、必ずしもすべてが同一の実施例または例を指しているとは限らない。さらに、特定の特徴、構造または特性を、1つ以上の実施例または例において任意の好適な組合せおよび/または下位の組合せにおいて組合わすことができる。特定の特徴、構造または特性は、集積回路、電子回路、組合せた論理回路、または所望の機能性を提供する他の好適な構成要素に含まれ得る。また、ここに提供される図面は当業者に説明するためのものであり、図面は必ずしも同じ割合で描かれているとは限らないことが認識される。

## [0009]

ここに用いられるように、ウェハとは、個別の半導体部品、集積回路(IC)、および他の超小型電子装置の製造に用いられる、シリコンまたはサファイア結晶などのバルク材料の薄片である。ウェハは典型的に円形の薄片に形成され、一般に、たとえば6、9、12インチなどの一定の直径のバルクブール(球)を平行に切削することによって得られる。ウェハは結晶質または非結晶質であり得る。結晶ウェハは特定的な結晶配向を有する。ウェハは基板または土台となり、この上に、エピタキシャル材料成長、ドーピング、イオン注入、エッチング、さまざまな材料の堆積、およびフォトリソグラフィパターニングなどの多くの製造プロセス工程の結果、トランジスタ、ダイオード、およびICなどの超小型電子装置が形成される。超小型電子装置(たとえばIC)は一般に、ウェハ全体にわたって配置された個々のダイの形態で複製される。

## [0010]

本開示内容の文脈では、基板は半導体、電気絶縁体材料、または金属のいずれかであり得る。製造プロセスに利用される基板の種類は典型的に、機械的強度、伝導率または電気絶縁性、光電用途における無線周波数信号吸収および/または透過性、ならびに熱伝導率や費用などの、用途の要件に依存する。一実施例では、キャリア基板とは、別の基板また

10

20

30

40

はウェハに接合されたウェハを指す。

## [0011]

サファイアは、窒化ホウ素、窒化アルミニウム、窒化ガリウム、窒化インジウム、およびそれらの三元、四元等の合金などの窒化物材料のエピタキシャル成長のために最も一般に用いられる基板材料の1つである。窒化物系装置については、FEOLおよびBEOL処理工程では典型的に、サファイア基板の厚みは300~650μmの範囲内にあることが要求される。一方、確実なダイ分離のためには、サファイア基板の厚みを、たとえば約150μmまで大幅に減少させなければならない。このプロセスは一般に基板薄板化といったれる。しかし、サファイアは非常に硬質の材料である(モース硬さスケールで9.0)。サファイアは硬質なため、切削、刻み付け、研磨、裏面ラップ仕上げおよび/または研削などの機械的処理が困難である。基板薄板化の際にウェハが割れることはウェハ全体の損失と同じであり得、歩留まり損失が高くなり、バックエンド費用が全体的に増加し得る。したがって、基板薄板化およびダイ分離は、窒化物材料系装置およびICのバックエンド処理における重要な課題である。

#### [0012]

本発明の実施例に従って、半導体装置を製造するために複合基板を利用する。一例では、複合基板は、比較的薄い基板にウェハ接合されたキャリア基板を含む。装置を製造する際、キャリア基板と薄基板とを合わせた厚みは、複合ウェハが割れずにFEOLおよびBEOL処理工程に耐え得るような安全な取扱いに十分の厚みである。換言すれば、キャリア基板は、製造プロセス時に薄基板に機械的支持を提供する。一実施例では、FEOLおよびBEOL処理工程の後であるがダイ分離の前に、薄基板からキャリア基板を除去する。別の実施例では、ダイ分離の後に、薄基板からキャリア基板を除去してもよい。このように、本発明の実施例では従来の基板薄板化のプロセスが無いため、歩留まり損失および全体的なバックエンド費用を減少させることができる。

#### [ 0 0 1 3 ]

図1A~図1Dは、製造プロセスのさまざまな段階における例示的な半導体ウェハ構造の断面側面図であり、キャリア基板102、薄基板104、中間層106、および集積装置108を含む。集積装置108は、ドーピング、イオン注入、エッチング、さまざまな材料の堆積、およびフォトリソグラフィパターニングなどの多くの製造プロセス工程の結果として形成される、トランジスタ、ダイオード、集積回路(IC)などの超小型電子装置を含み得る。

## [0014]

たとえば、図1Aは、キャリア基板102に取付けられている(すなわちウェハ接合されている)薄基板104(結晶質または多結晶質)を示す。薄基板104は、底面105および上面101を有して示される。一実施例では、薄基板104は、約50~250μmの範囲内の厚みを有するサファイア材料製のウェハを含む。他の実施例では、薄基板104は、窒化ホウ素、窒化アルミニウム、窒化ガリウム、窒化インジウム、およびそれらの三元、四元等の合金などの窒化物系半導体材料を含む。さらなる実施例では、薄基板104は、ダイアモンド、炭化珪素、または酸化亜鉛などの材料を含み得る。薄基板104の底面105は、キャリア基板102の上面103に接合されて示される。キャリア基板102は、FEOLおよびBEOL処理工程時に、薄基板104に強固で安定した機械的支持構造を提供する。

## [0015]

さまざまな実施例では、キャリア基板102は、結晶または多結晶材料製のウェハを含む。示される実施例では、キャリア基板102は、薄基板104よりもかなり大きい厚みを有する。キャリア基板102に利用可能な材料の例として、サファイア、シリコン、銅、窒化物系材料、ダイアモンド、炭化珪素、酸化亜鉛、グラファイト、または製造プロセス時に機械的安定性を提供する他の好適な材料が含まれる。キャリア基板102に利用可能な材料は、費用、取扱容易性、入手可能性、硬度(機械的強度)、薄基板104との熱・機械適合性(すなわち熱膨張係数の一致)、およびダイ分離技術に対する耐性などの、

10

20

30

40

10

20

30

40

50

多数の異なる考慮すべき事項に基づいて選択され得る。

### [0016]

一実施例では、キャリア基板102に用いられる材料の熱膨張係数は、薄基板104に用いられる材料の熱膨張係数と実質的に一致する。別の実施例では、キャリア基板102に用いられる材料は、薄基板104の材料と同じであってもよい。別の実施例では、キャリア基板102および基板104の熱膨張係数は等しくなくてもよいし、一致していなくてもよい。さらに、キャリア基板102のウェハ直径は、薄基板104のウェハ直径と実質的に等しくてもよいし、それより大きくてもよい。半導体処理技術の当業者であれば、本発明の一定の実施例では、半導体装置製造サイクルの最後にキャリア基板102を回収して再利用できることを認識するであろう。

[0017]

さまざまな実施例では、キャリア基板102は、複合ウェハ構造に十分な機械的強度を提供する厚みを有する。換言すれば、キャリア基板102と薄基板104とを合わせた厚みの合計は、FEOLおよびBEOL処理工程時に機械的に安定した構造を提供するのに十分であるべきである。一例では、キャリア基板102は、約300μm~1200μmの範囲内の厚みを有するシリコンまたはサファイアを含み、薄基板104は、約50~250μmの範囲内の厚みを有するサファイアを含む。

[0018]

(矢印で示されるような)薄基板104へのキャリア基板102の接合は、直接接合、接着接合、プラズマ活性化接合、陽極接合、共晶接合、ガラスフリット接合、熱圧着および反応性接合法を含む、さまざまな公知のウェハ接合技術を用いて行うことができる。一例として、接合は、キャリア基板102を薄基板104に機械的に押付けることによって達成することができる。または、底面105と上面103とが直接接触するように、薄基板104をキャリア基板102の上に積重ねてもよい。その後、キャリア基板102と薄基板104との間に堅固な接合を形成するのに十分な時間だけ、積重ねを高温アニールに曝す。

[0019]

接合は、ファンデルワールスカ(水素結合としても公知)によって、または接合すべきウェハの表面層の材料の相互浸透(共晶接合)によって達成することができる。この後者の接合法では、ともに接合される表面は極端に平坦であるべきであり、これはたとえば化学機械研磨(CMP)によって達成することができる。強固な接合を達成するのに必要な圧力および温度はウェハの材料によって異なり得、通常は摂氏200~600度である。キャリア基板102と薄基板104とを接合した結果は、複合ウェハ(基板)と称され得る。

[0020]

さらに図1Bに示すように、中間層106を用いてキャリア基板102を薄基板104にウェハ接合してもよい。中間層106は、薄基板104の底面105をキャリア基板102の上面103に付ける。キャリア基板102がシリコンまたはサファイアを含み、薄基板104がサファイアを含む一例では、第1工程として、二酸化珪素の薄層(0.01~1マイクロメートル)をキャリア基板102および薄基板104の一方または両方に堆積するか、熱成長させることができる。次に、キャリア基板102の上面103を薄基板104の底面105に接触させる。その後、約900~1200 で数時間アニールを行って2枚の基板を接合することによって、単一の複合ウェハ107を形成する。この例では、二酸化珪素を含む中間層106が底面105を上面103に接合する。

[0021]

他の実施例では、キャリア基板102を薄基板104に取付けるために利用される特定のウェハ接合技術(たとえば陽極接合)によっては、中間層106は形成されないか、必要としない場合もあることが認識される。

[0022]

中間層106として使用可能な他の材料の例として、エポキシ(接着接合)、酸化アル

ミニウム、ガラスフリット、はんだ、ポリマー、またはキャリア基板 1 0 2 と薄基板 1 0 4 との頑丈な接合を形成するのに好適な任意の他の材料が含まれる。

### [0023]

図1Bに示すように、複合ウェハ107はキャリア基板102、中間層106、および薄基板104を含む。複合ウェハ107をその後の半導体材料エピタキシャル堆積のために準備するために、上面101を適切に準備すべきである。換言すれば、上面101は、製造する半導体装置の活性領域を形成するために用いられる、後のエピタキシャル処理工程の準備ができているような準備状態にあるべきである。たとえば、上面101に対して機械的および/または化学的研磨を行うことによって、エピタキシャル堆積に好適な、極端に平坦な(たとえば原子的に平坦な)表面を作ってもよい。または、他の実施例では、エピタキシャル層の形成に利用される材料の種類および処理工程の種類によっては、上面を粗くしてもよい。

#### [0024]

図1 C は、F E O L および B E O L 処理工程の完了後の複合基板 1 0 7 を示しており、薄基板 1 0 6 上に直接配置された半導体装置 1 0 8 が製造されている。半導体装置 1 0 8 は典型的に、平面構造および / またはメサ構造形成、不純物の堆積 / 拡散、エッチング、絶縁、表面準備、金属化、パターニングなどを含み得る製造プロセスにかけられた、さまざまなエピタキシャル層(たとえばヘテロ構造)を含む。一実施例では、半導体装置 1 0 8 は、窒化物系の電子および / または光電半導体装置を含む。特定的な例では、半導体装置 1 0 8 は、窒化ガリウム(G a N)装置構造を含む。

#### [0025]

本発明の実施例では、図1Dに示すように、半導体装置108の形成の後であるがダイ分離の前に、薄基板104からキャリア基板102を取外すか、ディボンディング(剥離)する。上述のように、剥離は、用いられる特定の方法および/または中間層の使用にかかわらず、薄基板104からキャリア基板102を取外すプロセスである。図1Dに示す例では、剥離によって中間層106が除去される。剥離は、キャリア基板102、薄基板104および半導体装置108をそのまま残しておきつつ中間層材料106を選択的に除去する、化学溶液中のウェットエッチングなどの技術を含み得る。レーザリフトオフを用いて中間層106を除去してもよい。

## [0026]

さらに他の実施例では、薄基板 1 0 4 からキャリア基板 1 0 2 を剥離するが薄基板 1 0 4 および半導体装置 1 0 8 をそのまま残しておく化学的、機械的、または任意の他の好適な方法によって、キャリア基板 1 0 2 を破壊してもよい。キャリア基板 1 0 2 を剥離時に破壊しない実施例では、キャリア基板 1 0 2 を別の複合ウェハ構造に再利用できる(たとえば別の薄基板に取付けることができる)。

## [0027]

中間層を用いずにキャリア基板 1 0 2 と薄基板 1 0 4 とを接合した場合、他の分離技術を利用してもよい。たとえば、方向付けられた機械力を印加することによる機械的分離(「ナイフブレード」法)を利用してもよいし、局所加熱法(レーザリフトオフ)を適用してもよい。

## [0028]

剥離に続いて、半導体装置108を含む個々のダイを互いに分離することができる。ダイ分離は、たとえばレーザスクライブなどの多数の公知の技術のいずれかによって実行することができる。

## [0029]

図2A~図2Dは、製造プロセスのさまざまな段階における別の例示的な半導体ウェハ構造の断面側面図である。図2A~図2Dは、基板204の底面にコンタクト層をさらに追加した縦型装置を示す。図2Aは、図1Cに関連して説明したのと同じ態様で製造した複合ウェハ207(キャリア基板202、中間層206、および薄基板204を含む)ならびに半導体装置208の一例を示す。図2Bは、図1Dに関連して説明したのと同じ態

10

20

30

40

様でキャリア基板202から剥離された薄基板204を示す。図2A~図2Dに示す同様の名称および番号の要素は、上述のように結合および機能する。

## [0030]

図2 C は、薄基板 2 0 4 の底面 2 0 5 へのコンタクト層 2 1 0 の取付けまたは形成を示す断面側面図である。図示されるように、コンタクト層 2 1 0 の上面 2 0 9 を(矢印で示すように)薄基板 2 0 4 の底面 2 0 5 に取付ける。一実施例では、コンタクト層 2 1 0 は、薄基板 2 0 4 の半導体材料への電気的接続を提供する金属電極を含む。コンタクト層 2 1 0 は、通常の金属堆積技術を利用して形成することができる。図 2 D は、薄基板 2 0 4 の底面 2 0 5 にコンタクト層 2 1 0 を形成した後に得られる装置構造を示す。

## [0031]

図3Aは、ダイ分離プロセスの一部として溝312を形成した後の、図1Cに示す例示的な半導体ウェハ構造の断面側面図である。図3Aおよび図3Bに示す同様の名称および番号の要素は、上述のように結合および機能する。図示されるように、溝312は、半導体装置308の垂直方向の全厚みを貫通して薄基板304の一部にまで延在することによって、複数の半導体ダイ314を個別化する。ダイ314の各々は、別個の半導体電子よたは光電装置を含み得る。溝312は、ダイシング、レーザスクライブ、研削、エッチングなどを含む多数の公知の方法のいずれかで形成することができる。図3Bは、上述の分離プロセスの後に薄基板304から分離したキャリア基板302を示す。この時点で、薄基板304を、その後の溝312の各々との垂直方向の位置合せによって切断することによって、パッケージング前に半導体ダイ314を互いに完全に分離することができる。他の実施例では、ダイ分離プロセスの前に、薄基板304の底面にコンタクト金属層を形成してもよい。

## [0032]

図4Aおよび図4Bは、別のダイ分離プロセスの一部として溝412を形成した後の、図1Dに示す例示的な半導体ウェハ構造の断面側面図である。図4Aおよび図4Bに示す同様の名称および番号の要素は、上述のように結合および機能する。この例では、溝412の形成後(図3Aに示すように)ではなく形成前に、薄基板404からキャリア基板402を分離する。上述の技術のいずれかを用いて溝412を形成し、個々のダイ414を分離することができる。

## [ 0 0 3 3 ]

要約書に記載されていることを含む本発明の図示した例の上記の説明は、網羅的であること、または開示した厳密な形態に限定することを意図するものではない。本発明の特定的な実施例および例を例示目的でここに説明したが、本発明のより広範な思想および範囲から逸脱することなく、さまざまな同等の変更が可能である。実際、特定の例示的な厚み、材料の種類、処理工程などは説明のために提供されていること、ならびに本発明の教示内容に従って他の値も他の実施例および例において使用可能であることが認識される。これらの変更は、上記の詳細な説明に鑑みて本発明の例に加えられ得る。以下の請求項で用いられる用語は、明細書および請求項に開示される特定的な実施例に本発明を限定すると解釈してはならない。むしろ、範囲は、請求項解釈の確立された教義に従って解釈されるべき以下の請求項によって完全に判断されるべきである。したがって、本明細書および図面は限定的ではなく例示的であると見なされるべきである。

10

20

30

FIG. 1A

FIG. 1B

FIG. 1C

FIG. 1D

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 2D

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 4B

# フロントページの続き

(72)発明者 キエルティ・スワミナサン

アメリカ合衆国、08904 ニュー・ジャージー州、ハイランド・パーク、フォレスト・グレン・ドライブ、66

【外国語明細書】 2013125971000001.pdf