# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 109979519 B (45) 授权公告日 2021.03.16

- (21)申请号 201711440910.1

- (22) 申请日 2017.12.27

- (65) 同一申请的已公布的文献号 申请公布号 CN 109979519 A

- (43) 申请公布日 2019.07.05

- (73) **专利权人** 华邦电子股份有限公司 地址 中国台湾台中市大雅区科雅一路8号

- (72) 发明人 叶润林

- (74) 专利代理机构 北京同立钧成知识产权代理 有限公司 11205

代理人 马雯雯 臧建明

(51) Int.CI.

**G11C** 29/12 (2006.01)

**G11C** 29/50 (2006.01)

#### (56) 对比文件

- US 2011107161 A1,2011.05.05

- CN 105607865 A, 2016.05.25

- CN 103456367 A, 2013.12.18

- CN 106251903 A,2016.12.21

- CN 102655021 A,2012.09.05

- CN 104040504 A,2014.09.10

- US 2017040062 A1,2017.02.09

- US 2016217868 A1,2016.07.28

审查员 张慧敏

权利要求书3页 说明书8页 附图4页

#### (54) 发明名称

存储器完整性的检验方法、非易失性存储器以及电子装置

#### (57) 摘要

本发明提供一种存储器完整性的检验方法、非易失性存储器以及电子装置。所述方法包括下列步骤。获得非易失性存储器中至少一待检验存储单元的阀值电压。将读取电压以及所述阀值电压进行比对来判断所述至少一待检验存储单元所属的数据值。当确认所述至少一待检验存储单元所属的所述数据值后,依据所述数据值来设定预设电压。将所述预设电压与所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值。以及,判断所述至少一待检验存储单元的偏移数据值。以及,判断所述至少一待检验存储单元的后整性是否有缺陷。

1.一种存储器完整性的检验方法,其特征在于,包括:

获得非易失性存储器中至少一待检验存储单元的阀值电压;

将读取电压以及所述阀值电压进行比对来判断所述至少一待检验存储单元所属的数据值,其中当所述阀值电压大于所述读取电压时所述数据值具有第一逻辑状态,当所述阀值电压不大于所述读取电压时所述数据值具有第二逻辑状态;

当确认所述至少一待检验存储单元所属的所述数据值后,依据所述数据值来设定预设电压;

将所述预设电压与所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值,其中当所述至少一待检验存储单元的所述阀值电压大于所述预设电压时所述偏移数据值具有所述第一逻辑状态,当所述至少一待检验存储单元的所述阀值电压不大于所述预设电压时所述偏移数据值具有所述第二逻辑状态;

判断所述至少一待检验存储单元所属的所述数据值与所述至少一待检验存储单元的 所述偏移数据值是否相同;以及

响应于判断所述至少一待检验存储单元所属的所述数据值以及所述至少一待检验存储单元的所述偏移数据值相同,判定所述至少一待检验存储单元的完整性没有缺陷。

2.根据权利要求1所述的存储器完整性的检验方法,其特征在于,还包括:

响应于判断至少一待检验存储单元所属的所述数据值以及至少一待检验存储单元的 所述偏移数据值不同时,判定所述至少一待检验存储单元的完整性有缺陷。

3.根据权利要求1所述的存储器完整性的检验方法,其特征在于,还包括:

发送数据完整性诊断指令至所述非易失性存储器;

对所述非易失性存储器发送第一数据读取指令,以获得所述非易失性存储器中的状态 暂存器的状态数据,并依据该状态数据中的忙碌比特来判断所述非易失性存储器是否完成 所述数据完整性诊断指令;

当所述数据完整性诊断指令已完成时,对所述非易失性存储器发送第二数据读取指令,以获得所述状态暂存器的状态数据中的完整性验证比特;以及

依据所述完整性验证比特来判断所述非易失性存储器中的多个存储单元的完整性是 否有缺陷,其中所述存储单元包括所述至少一待检验存储单元。

4.一种非易失性存储器,其特征在于,包括:

存储器阵列,包括多个存储单元;以及

控制电路,耦接所述存储器阵列,

所述控制电路进行存储器的数据完整性检验以获得所述存储单元中的至少一待检验存储单元的阀值电压,将读取电压以及所述阀值电压进行比对来判断所述至少一待检验存储单元所属的数据值,其中当所述阀值电压大于所述读取电压时所述数据值具有第一逻辑状态,当所述阀值电压不大于所述读取电压时所述数据值具有第二逻辑状态,当确认所述至少一待检验存储单元所属的所述数据值后,所述控制电路依据所述数据值来设定预设电压,将所述预设电压与所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值,其中当所述至少一待检验存储单元的所述阀值电压大于所述预设电压时所述偏移数据值具有所述第一逻辑状态,当所述至少一待检验存储单元的所述阀值电压大于所述预设电压时所述偏移数据值具有所述第二逻辑状态,判断所述

至少一待检验存储单元所属的所述数据值与所述至少一待检验存储单元的所述偏移数据值是否相同;响应于判断所述至少一待检验存储单元所属的所述数据值以及所述至少一待检验存储单元的所述偏移数据值相同,判定所述至少一待检验存储单元的完整性没有缺陷。

5.根据权利要求4所述的非易失性存储器,其特征在于,还包括:

状态暂存器,储存状态数据,所述状态数据包括忙碌比特以及完整性验证比特,

其中所述忙碌比特用以表示所述非易失性存储器是否正在进行存储器的数据完整性 检验,所述完整性验证比特用以表示所述存储器阵列中所述存储单元的完整性是否有缺 陷。

6.根据权利要求4所述的非易失性存储器,其特征在于,还包括:

响应于判断至少一待检验存储单元所属的所述数据值以及至少一待检验存储单元的 所述偏移数据值不同时,所述控制电路判定所述至少一待检验存储单元的完整性有缺陷。

7.根据权利要求4所述的非易失性存储器,其特征在于,还包括:

电压产生器,用以产生所述读取电压以及所述数据值对应的所述预设电压。

8.一种电子装置,其特征在于,包括:

非易失性存储器,包括存储器阵列以及状态暂存器;以及

控制器,耦接所述非易失性存储器,

其中所述控制器发送数据完整性诊断指令至所述非易失性存储器,对所述非易失性存储器发送第一数据读取指令,以获得所述状态暂存器中的状态数据,并依据所述状态数据中的忙碌比特来判断所述非易失性存储器是否完成所述数据完整性诊断指令,当所述数据完整性诊断指令已完成时,所述控制器对所述非易失性存储器发送第二数据读取指令,以获得所述状态暂存器的所述状态数据中的完整性验证比特,并依据所述完整性验证比特来判断所述存储器阵列中的多个存储单元的完整性是否有缺陷,

其中当所述非易失性存储器接收数据完整性诊断指令后,获得所述非易失性存储器中的至少一待检验存储单元的阀值电压,将读取电压以及所述阀值电压进行比对来判断所述至少一待检验存储单元所属的数据值,其中当所述阀值电压大于所述读取电压时所述数据值具有第二逻辑状态,当确认所述至少一待检验存储单元所属的所述数据值后,所述非易失性存储器依据所述数据值来设定预设电压,将所述预设电压与所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值,其中当所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值具有所述第一逻辑状态,当所述至少一待检验存储单元的所述阀值电压大于所述预设电压时所述偏移数据值具有所述第二逻辑状态,判断所述至少一待检验存储单元所属的所述数据值与所述至少一待检验存储单元的所述偏移数据值是否相同,以及响应于判断所述至少一待检验存储单元所属的所述数据值以及所述至少一待检验存储单元的所述偏移数据值相同,判定所述至少一待检验存储单元的所述离移数据值相同,判定所述至少一待检验存储单元的完整性没有缺陷。

9.根据权利要求8所述的电子装置,其特征在于,还包括:

响应于判断至少一待检验存储单元所属的所述数据值以及至少一待检验存储单元的 所述偏移数据值不同时,判定所述至少一待检验存储单元的完整性有缺陷。 10.根据权利要求8所述的电子装置,其特征在于,所述非易失性存储器还包括:电压产生器,用以产生所述读取电压以及所述数据值对应的所述预设电压。

# 存储器完整性的检验方法、非易失性存储器以及电子装置

### 技术领域

[0001] 本发明涉及一种存储器的检验技术,尤其涉及一种存储器完整性的检验方法、非易失性存储器以及电子装置。

## 背景技术

[0002] 在不供电期间中仍可长时间储存数据的非易失性存储器(如,快取存储器)是诸多电子装置中的必要组件之一。非易失性存储器的可靠度问题与其自身的数据保留(data retention)生命期限有关,换句话说,非易失性存储器可能因为诸多原因或潜在理由而导致缩减自身可保留数据的时间,或是在存取数据时受到伤害,因而发生非易失性存储器对数据存取的劣化。这些潜在理由例如是,进行数据循环(如,程序化/抹除)操作之后的压力依赖漏流(Stress Induced Leakage Current(SILC))、程序化/抹除操作中的扰乱问题、装置中的游离离子、出厂前并未发现的存储器物理缺陷…等。

[0003] 在一般性消费型电子装置来说,存储器中的数据出错仅导致部分数据错误或功能缺失,并可通过许多方式进行补救。然而,若以自驾车或自动驾驶领域来说,部分数据的错误或系统延迟皆有可能导致系统当机,从而直接地关乎使用者的生命。为避免上述情况发生,在ISO 26262协定所规定的《道路车辆功能安全》国际标准中规定了汽车领域所使用的电子设备需要通过危害分析与风险评估(Hazard Analysis&Risk Assessment,HARA),以使产品的功能安全符合汽车安全完整性等级(ASIL)。因此,如何让电子产品能够诊断非易失性存储器的数据保留生命期限即将抵达,并在发现上述情况时能立刻处置,便是可作为技术研议的方向之一。

## 发明内容

[0004] 本发明提供一种存储器完整性的检验方法、非易失性存储器以及使用此非易失性存储器的电子装置,可自行判断非易失性存储器中的待检测存储单元是否完好或是已开始出现劣化可能有损坏风险的情况下,从而让非易失性存储器以及电子装置的功能安全能够符合国际标准规定。

[0005] 本发明的存储器完整性的检验方法包括下列步骤。获得非易失性存储器中至少一待检验存储单元的阀值电压。将读取电压以及所述阀值电压进行比对来判断所述至少一待检验存储单元所属的数据值。当确认所述至少一待检验存储单元所属的所述数据值后,依据所述数据值来设定预设电压。将所述预设电压与所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值。以及,判断所述至少一待检验存储单元所属的所述数据值以及所述偏移数据值是否相同,从而判定所述至少一待检验存储单元的完整性是否有缺陷。

[0006] 本发明的非易失性存储器包括存储器阵列以及控制电路。存储器阵列包括多个存储单元,且控制电路耦接所述存储器阵列。控制电路进行存储器的数据完整性检验以获得所述存储单元中的至少一待检验存储单元的阀值电压,将读取电压以及所述阀值电压进行

比对来判断所述至少一待检验存储单元所属的数据值。当确认所述至少一待检验存储单元所属的所述数据值后,控制电路依据所述数据值来设定预设电压,将所述预设电压与所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值,判断所述至少一待检验存储单元所属的所述数据值以及所述偏移数据值是否相同,从而判定所述至少一待检验存储单元的完整性是否有缺陷。

[0007] 本发明的电子装置包括非易失性存储器以及控制器。非易失性存储器包括存储器阵列以及状态暂存器。控制器耦接所述非易失性存储器。控制器发送数据完整性诊断指令至所述非易失性存储器为关性存储器发送第一数据读取指令,以获得所述状态暂存器中的状态数据,并依据所述状态数据中的忙碌比特来判断所述非易失性存储器是否完成所述数据完整性诊断指令。当所述数据完整性诊断指令已完成时,控制器对所述非易失性存储器发送第二数据读取指令,以获得所述状态暂存器的所述状态数据中的完整性验证比特,并依据所述完整性验证比特来判断所述存储器阵列中的多个存储单元的完整性是否有缺陷。当非易失性存储器接收数据完整性诊断指令后,将读取电压以及所述阀值电压进行比对来判断所述至少一待检验存储单元所属的数据值。当确认所述至少一待检验存储单元所属的数据值后,非易失性存储器依据所述数据值来设定预设电压,将所述预设电压与所述至少一待检验存储单元的所述阀值电压进行比对而获得所述至少一待检验存储单元的偏移数据值,以及判断所述至少一待检验存储单元所属的所述数据值以及所述偏移数据值是否相同,从而判定所述至少一待检验存储单元的完整性是否有缺陷。

[0008] 基于上述,本发明实施例所述的存储器完整性的检验方法、非易失性存储器以及使用此非易失性存储器的电子装置可对非易失性存储器中的多个待检测存储单元依据数据值所设定的预设电压来与待检测存储单元的阀值电压进行比对,以实现存储器的数据完整性检验,从而判断此待检测存储单元是否完好或是处于即将损坏但仍可使用的情况(也即,存储器完整性有缺陷)。换句话说,为避免非易失性存储器损坏,本发明实施例的非易失性存储器可先行对各个存储单元进行自检其存储器完整性是否良好,从而让电子装置能够提前知晓非易失性存储器是否有机率损毁,致使电子装置的功能安全能够符合国际标准规定。

[0009] 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

## 附图说明

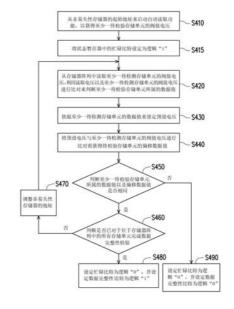

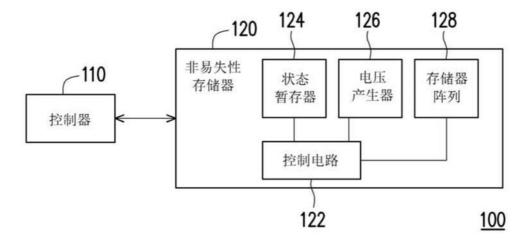

[0010] 图1是依照本发明实施例的一种电子装置的功能方块图;

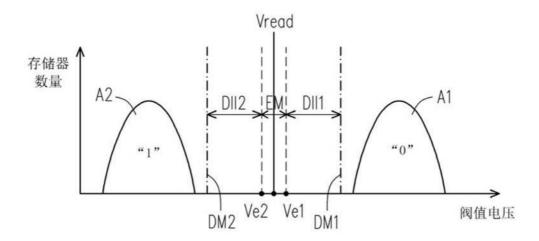

[0011] 图2是依照本发明实施例说明预设电压、存储单元的数据完整性区间、失效电压、以及识别区间的示意图;

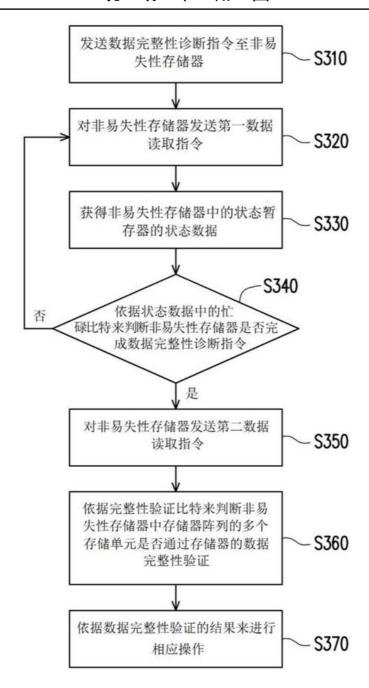

[0012] 图3是依照本发明实施例的控制器对非易失性存储器进行存储器完整性的检验方法的流程图;

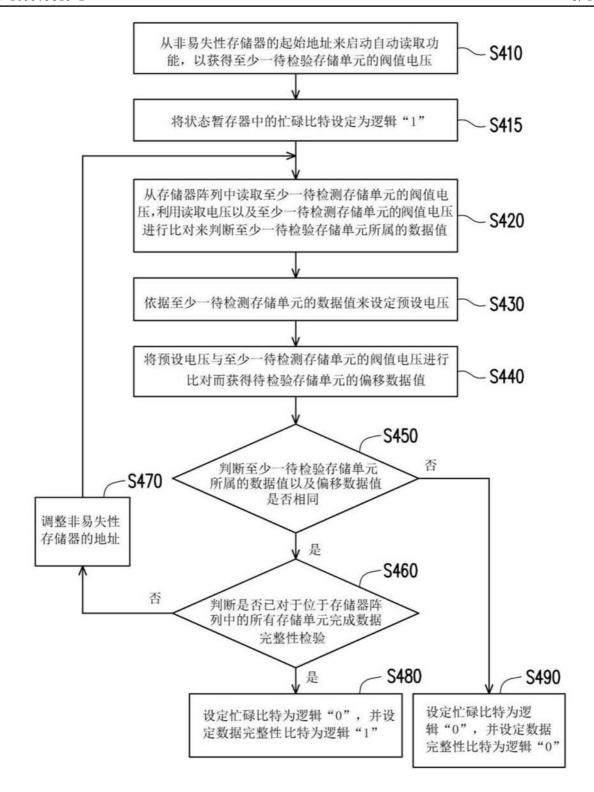

[0013] 图4是依照本发明实施例的存储器完整性的检验方法的详细流程图;

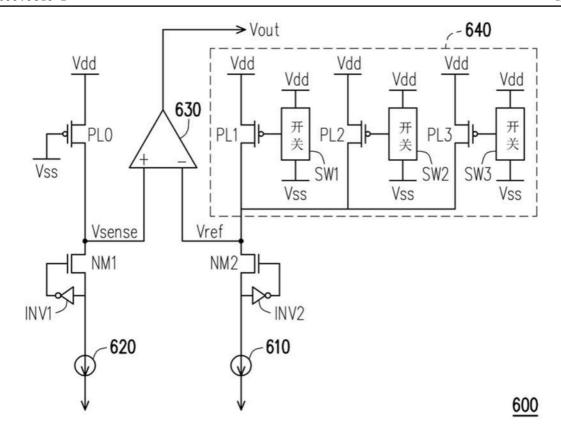

[0014] 图5是依照本发明实施例的非易失性存储器中的部分电路(包含电压产生器)的电路图。

[0015] 附图标记说明

- [0016] 100:电子装置;

- [0017] 110:控制器;

- [0018] 120:非易失性存储器;

- [0019] 122:控制电路;

- [0020] 124:状态暂存器;

- [0021] 126、640:电压产生器;

- [0022] 128:存储器阵列;

- [0023] 600:电路;

- [0024] 610:参考电流源;

- [0025] 620:存储单元电流源;

- [0026] 630:差动放大器;

- [0027] A1、A2:区域:

- [0028] Vread:读取电压:

- [0029] DII1、DII2:区间/数据完整性区间;

- [0030] EM:识别区间;

- [0031] DM1、DM2:电压/预设电压;

- [0032] Ve1、Ve2:电压/失效电压;

- [0033] S310~S370、S410~S440、S410~S490:步骤;

- [0034] NM1~NM2:N型晶体管;

- [0035] INV1~INV2:反相器;

- [0036] PL0~PL3:P型晶体管;

- [0037] SW1~SW3:开关;

- [0038] Vsense:检测电压;

- [0039] Vref:参考电压:

- [0040] Vss:接地电压;

- [0041] Vdd:电源电压。

### 具体实施方式

[0042] 图1是依照本发明实施例的一种电子装置100的功能方块图。电子装置100包括控制器110以及非易失性存储器120。控制器110可以是中央处理单元 (CPU) 或是存储器控制器。非易失性存储器120主要包括控制电路122以及存储器阵列128。非易失性存储器120还可包括状态暂存器124以及电压产生器126。非易失性存储器120可以是快取存储器,在此以串列式 (SPI) NOR型快闪存储器实现非易失性存储器120。本实施例的呈现方式可以是以电子装置100为主体、或是以非易失性存储器120为主体来呈现。存储器阵列128可包括多个存储单元。

[0043] 为使电子装置100以及非易失性存储器120能够具备对于非易失性存储器120自身功能的危害分析与风险评估(HARA),本发明实施例的非易失性存储器120可通过进行存储器的数据完整性检验来自行判断存储器阵列128中的待检测存储单元是否完好、或是已开始出现劣化可能有损坏风险的情况下(在此称此情况为存储器完整性有缺陷)。换句话说,

为避免非易失性存储器120损坏,本发明实施例可先行对各个存储单元进行自检其存储器完整性是否有缺陷,从而让电子装置100能够提前知晓非易失性存储器120是否有损毁的风险,致使电子装置100的功能安全能够符合国际标准规定。

[0044] 图2是依照本发明实施例说明预设电压DM1/DM2、存储单元的数据完整性区间 DII1/DII2、失效电压Ve1/Ve2、以及识别区间EM的示意图。图2是以快取存储器作为本实施 例中图1的非易失性存储器120的实作范例。快取存储器的存储单元数量(图2中的纵轴)与存储单元的阀值电压(图2中的横轴)之间的关系可如图2所示。当存储单元的阀值电压大于 预设的读取电压Vread时,可认为存储单元的数据值为逻辑"0";当存储单元的阀值电压小于预设的读取电压Vread时,可认为存储单元的数据值为逻辑"1"。一般而言,在正常使用下的快取存储器(即,存储器完整性无缺陷)中,存储单元的阀值电压在经过程序化/抹除操作后通常落入区域A1或区域A2。

[0045] 然而,在快取存储器的实际运作中,存储单元的阀值电压常会随数据循环的次数慢慢出现劣化的现象而往无法判断存储单元数据值的识别区间EM移动。详细而言,当存储单元的阀值电压出现劣化的现象而落入识别区间EM中时,快取存储器所属的控制电路将可能无法识别存储单元中所储存的数据为逻辑"0"或是逻辑"1",因而导致控制电路无法读取存储单元。其中,识别区间EM位于逻辑"0"对应的失效电压Ve1以及逻辑"1"对应的失效电压Ve2之间。此时,快取存储器将可能会发生数据读取错误而直接使得电子装置的功能缺失。换句话说,当存储单元的阀值电压落入识别区间EM中时,快取存储器便可能会直接损坏而无法进行其他操作。

[0046] 因此本发明实施例希望可让非易失性存储器120先行对各个存储单元进行自检以判断其存储器完整性是否有缺陷,进而提前防止当存储单元的阀值电压落入识别区间EM中发生读取错误才发现的状况。如图2所示,在区域A1到识别区间EM之间具备区间DII1,且在区域A2到识别区间EM之间具备区间DII2,若检测到存储单元的阀值电压位于这两个区间DII1及DII2时,可发现此存储单元虽然可以正常使用(也即,非易失性存储器可正常判断此存储单元的数据值),但此存储单元已开始出现劣化的倾向,其被存取速度以及反应时间事实上已较正常存储单元来说来的较慢,可能有损坏的风险(在此将其视为存储器完整性有缺陷)。

[0047] 因此,本发明实施例的主要概念在于,对非易失性存储器120中的每个存储单元进行存储器的完整性检验已确认其阀值电压是否仍落在区域A1及A2或已落入数据完整性区间DII1及区间DII12当中。若是有存储单元落在数据完整性区间DII1或DII2当中时,表示非易失性存储器中的部分存储单元可能有所劣化,因而可认定此非易失性存储器的数据完整性有缺陷。

[0048] 区间DIII位于逻辑"0"对应的预设电压DM1以及逻辑"0"对应的失效电压Ve1之间。区间DII2位于逻辑"1"对应的预设电压DM2以及逻辑"1"对应的失效电压Ve2之间。预设电压DM1/DM2减去读取电压Vread的绝对值大于失效电压Ve1/Ve2减去读取电压Vread的绝对值。数据完整性区间DII1及区间DII2与识别区间EM互不重叠。

[0049] 图3是依照本发明实施例的控制器110对非易失性存储器120进行存储器完整性的检验方法的流程图。图3主要是以控制器110为指令发送者,让非易失性存储器120进行数据完整性检验的操作流程。请同时参照图1及图3,于步骤S310中,控制器110发送数据完整性

诊断指令至非易失性存储器120的控制电路122。于步骤S320中,控制器110对非易失性存储器120发送第一数据读取指令。于步骤S330中,控制器110从非易失性存储器120获得非易失性存储器120中的状态暂存器124的状态数据。详细来说,每个状态数据具备多个比特,每个比特可以分别表示此非易失性存储器的各个状态。例如,本实施例的状态数据具备比特S0至比特S15。比特S0表示为忙碌比特,比特S10表示为完整性验证比特。本实施例中的第一数据读取指令可读取状态数据中的比特S0至S7,而本实施例中的第二数据读取指令则可读取状态数据中的比特S8至S15。非易失性存储器120的控制电路122在接收到第一数据读取指令时,便通过状态暂存器124以将具备忙碌比特的状态数据(如,比特S0至比特S7)传递给控制器110。

[0050] 于步骤S340中,控制器110依据状态数据中的忙碌比特来判断非易失性存储器120是否完成上述的数据完整性诊断指令。本实施例中,若非易失性存储器120正在执行相关操作时,忙碌比特将以逻辑"1"呈现;非易失性存储器120并未执行相关操作时,忙碌比特将以逻辑"0"呈现。当控制器110判断忙碌比特为逻辑"1"时,表示非易失性存储器120并未完成数据完整性诊断指令,因此便回到步骤S320以及S330以继续获得非易失性存储器120的状态数据,以持续地判断非易失性存储器120的状态是否仍然忙碌。当控制器110判断忙碌比特为逻辑"0"时,表示非易失性存储器120已完成数据完整性诊断指令。因此,从步骤S340进为步骤S350,控制器110对非易失性存储器120发送第二数据读取指令。非易失性存储器120的控制电路122在接收到第二数据读取指令时,便从状态暂存器124将具备完整性验证比特的状态数据(如,比特S8至比特S15)传递给控制器110。

[0051] 在步骤S360中,控制器110便依据状态数据中的完整性验证比特来判断非易失性存储器120中存储器阵列的多个存储单元是否通过存储器的数据完整性检验。本实施例中,当完整性验证比特为逻辑"1"时,表示非易失性存储器120中的每个存储单元的完整性皆没有缺陷,从而使非易失性存储器120通过存储器的数据完整性验证。另一方面,当完整性验证比特为逻辑"0"时,表示非易失性存储器120中有部分的存储单元的完整性有缺陷,从而使非易失性存储器120没有通过存储器的数据完整性验证。在步骤S370中,控制器110便会依据数据完整性验证的结果来进行相应操作。例如,当非易失性存储器120的完整性有缺陷时,控制器110可控制非易失性存储器120以使其自行将有所缺陷的部分存储单元直接不使用,仅使用正常运作的存储单元;或是,控制器110在得知非易失性存储器并未通过存储器的数据完整性验证后,可通过警示设备来让电子装置100的使用人员/维护人员判定是否需要更换非易失性存储器120。

[0052] 图4是依照本发明实施例的存储器完整性的检验方法的流程图。请同时参照图1及图4,于步骤S410中,非易失性存储器120中的控制电路122在接收到数据完整性诊断指令之后,便从非易失性存储器120的起始地址来启动自动读取功能,以获得至少一待检验存储单元的阀值电压。本实施例图4中的数据完整性诊断可针对存储器阵列128中的每个存储单元依序作为"待检验存储单元"。在步骤S415中,控制电路122将状态暂存器124中的忙碌比特设定为逻辑"1",以让控制器110知悉数据完整性的诊断正在执行。

[0053] 在步骤S420中,控制电路122从存储器阵列128中读取待检测存储单元的阀值电压,利用读取电压(如图2所示的电压Vread)与待检测存储单元的阀值电压进行比对(也即,控制电路122利用读取电压对待检测存储单元进行正常读取)来判断待检验存储单元所属

的数据值。所述数据值例如为逻辑"0"或是逻辑"1"。在步骤S420中的控制电路122还可依据 硬体设计而栓锁(latch)此数据值。读取电压Vread可由电压产生器126所产生。在步骤S430中,控制电路122依据待检测存储单元的数据值来设定预设电压。若待检测存储单元的数据值为逻辑"0",则将预设电压设定为图2中的电压DM1;若待检测存储单元的数据值为逻辑"1",则将预设电压设定为图2中的电压DM2。

[0054] 在步骤S440中,控制电路122将步骤S430所设定的预设电压与所述至少一待检测存储单元的阀值电压进行比对(也即,控制电路122利用所设定的预设电压对待检测存储单元进行偏移读取)而获得待检验存储单元的偏移数据值。具体而言,若设定的预设电压为DM1,当待检测存储单元的阀值电压大于预设电压DM1时,可认为其偏移数据值为逻辑"0";当待检测存储单元的阀值电压小于预设电压DM1时,可认为其偏移数据值为逻辑"1"。另一方面,若设定的预设电压为DM2,当待检测存储单元的阀值电压小于预设电压DM2时,可认为其偏移数据值为逻辑"1";当待检测存储单元的阀值电压大于预设电压DM2时,可认为其偏移数据值为逻辑"1";当待检测存储单元的阀值电压大于预设电压DM2时,可认为其偏移数据值为逻辑"0"。

[0055] 在步骤S450中,控制电路122判断待检验存储单元所属的数据值以及步骤S440中的偏移数据值是否相同。当待检验存储单元所属的数据值以及偏移数据值相同时,表示待检验存储单元的阀值电压同时大于图2中的失效电压Ve1以及预设电压DM1以位于区域A1中,或是待检验存储单元的阀值电压同时小于图2中的失效电压Ve2以及失效电压DM2以位于区域A2中。也就是说,此待检验存储单元正常运作,且待检验存储单元的阀值电压没有位于图2的数据完整性区间DII1或DII2中。因此,从步骤S450进入步骤S460,控制电路122判断是否已对于位于存储器阵列128中的所有存储单元完成数据完整性检验。若没有让位于存储器阵列128中的所有存储单元皆完成数据完整性检验的话,则从步骤S460进入步骤S470,控制电路122调整非易失性存储器120的地址(例如,将地址加1),并回到步骤S420以重复进行步骤S420至步骤S460。若已让位于存储器阵列128中的所有存储单元完成数据完整性检验的话,则从步骤S460进入步骤S480,控制电路122设定忙碌比特为逻辑"0"以表示非易失性存储器120并未忙碌,并设定数据完整性比特为逻辑"1"。逻辑"1"的数据完整性比特用以表示非易失性存储器120完成数据完整性检验且并无发现存储单元具备数据完整性的缺陷。

[0056] 假设待检验存储单元所属的数据值为逻辑"0"时,若控制电路122判断待检验存储单元所属的数据值(逻辑"0")以及偏移数据值(逻辑"1")不同的话,表示待检验存储单元的阀值电压大于图2中的失效电压Ve1但并未大于预设电压DM1,使得待检验存储单元的阀值电压位于数据完整性区间DII1中。另一方面,假设待检验存储单元所属的数据值为逻辑"1"时,若控制电路122判断待检验存储单元所属的数据值(逻辑"1")以及偏移数据值(逻辑"0")不同的话,表示待检验存储单元的阀值电压小于图2中的失效电压Ve2但并未小于预设电压DM2,使得待检验存储单元的阀值电压位于数据完整性区间DII2中。如此一来,非易失性存储器120的数据完整性便有所缺陷,因此便从步骤S450进入步骤S490,控制电路122设定忙碌比特为逻辑"0"以表示非易失性存储器120并未忙碌,并设定数据完整性比特为逻辑"0"。逻辑"0"的数据完整性比特用以表示非易失性存储器120完成数据完整性检验且有发现部分的存储单元具备数据完整性的缺陷。

[0057] 图4所示的流程图是以单个待检验存储单元(也即,1个bit)为单位来进行步骤

S420至步骤S460的数据完整性检验,应用本实施例者也可以8个待检验存储单元(也即,1个byte)为单位来同时进行步骤S420至步骤S460的数据完整性检验,只要此8个待检验存储单元皆为相同的数据值(逻辑"0"或逻辑"1")即可实现。于部分实施例中,存储器阵列终能被区分为多个区块,应用本实施例者也可以将整个区块中的待检验存储单元作为单位来同时进行步骤S420至步骤S460的数据完整性检验,只要此区块中的待检验存储单元的数据值皆为相同便可实现。

[0058] 图5是依照本发明实施例的非易失性存储器120中的部分电路(包含电压产生器128)的电路图。本实施例通过图5来说明如何设定/调整与存储单元的阀值电压相比较的参考电压(如,图2中的读取电压Vread、逻辑"0"对应的预设电压DM1、以及逻辑"1"对应的预设电压DM2)。应用本实施例者也可通过其他电路来实现上述参考电压的切换。图5的电路中包括差动电压感应器600。差动电压感应器600主要包括参考电流源610、存储单元电流源620、N型晶体管NM1及NM2、反相器INV1及INV2、P型晶体管PL0、差动放大器630以及电压产生器640。电压产生器640由多个P型晶体管PL1~PL3以及多个开关SW1~SW3构成。参考电流源610产生固定的参考电流。存储单元电流源620耦接待检测存储单元以获得待检测存储单元当中的阀值电压。差动放大器630的非反相输入端接收与待检测存储单元中的阀值电压相关的检测电压Vsense。差动放大器630的反相输入端则接参考电压Vref。P型晶体管PL0的控制端接地(如,接收接地电压Vss)。电压产生器640可用以产生读取电压Vread以及与数据值(如,逻辑"0"以及逻辑"1")对应的预设电压DM1/DM2。

[0059] 在本实施例中,当想要让参考电压Vref成为上述实施例图2中的读取电压Vread时,可控制开关SW1与SW2让P型晶体管PL1与PL2的控制端接地,且控制开关SW3让P型晶体管PL3的控制端接收电源电压Vdd,以使P型晶体管PL0与电压产生器640之间的感测比率调整为2:1。如此一来,便可让参考电压Vref等于读取电压Vread,以对待检验存储单元的阀值电压进行正常读取从而判断其所属的数据值。

[0060] 当待检验存储单元所属的数据值为逻辑"0"时,电路600便需要将参考电压Vref设定为图2的预设电压DM1。本实施例可控制开关SW1~SW3让P型晶体管PL1~PL3的控制端皆为接地,以使P型晶体管PL0与电压产生器640之间的感测比率降至3:1。如此一来,便可让参考电压Vref等于预设电压DM1,以对待检验存储单元的阀值电压进行逻辑"0"的偏移读取从而判断其所属的的偏移数据值。当待检验存储单元所属的数据值为逻辑"1"时,电路600便需要将参考电压Vref设定为图2的预设电压DM2。本实施例可控制开关SW1让P型晶体管PL1的控制端为接地,控制开关SW2~SW3让P型晶体管PL2~PL3的控制端接收电源电压Vdd,以使P型晶体管PL0与电压产生器640之间的感测比率调整为1:1。如此一来,便可让参考电压Vref等于预设电压DM1,以对待检验存储单元的阀值电压进行逻辑"1"的偏移读取从而判断其所属的的偏移数据值。

[0061] 综上所述,本发明实施例所述的存储器完整性的检验方法、非易失性存储器以及使用此非易失性存储器的电子装置可对非易失性存储器中的多个待检测存储单元的正常读取所获得的数据值与偏移读取所获得的偏移数据值进行比对,以实现存储器的数据完整性检验,从而判断此待检测存储单元是否完好或是已开始出现的劣化的倾向(也即,存储器完整性有缺陷)。换句话说,为避免非易失性存储器损坏,本发明实施例的非易失性存储器可先行对各个存储单元进行自检其存储器完整性是否良好,从而让电子装置能够提前知晓

非易失性存储器是否有机率损毁,致使电子装置的功能安全能够符合国际标准规定。

[0062] 虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定者为准。

图1

图2

图3

图4

图5