# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) Int. Cl.

**H05B 33/14** (2006.01) **H05B 33/26** (2006.01)

(21) 출원번호

10-2007-0018846

(22) 출원일자

2007년02월26일

심사청구일자 없음

(43) 공개일자

(71) 출원인

(11) 공개번호

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

김종무

서울 은평구 응암1동 92-9호 현대아트빌라 202호

10-2008-0078959

2008년08월29일

(74) 대리인

허용록

전체 청구항 수 : 총 15 항

#### (54) 유기전계발광표시장치 및 그 제조방법

#### (57) 요 약

본 발명은 본 발명은 유기전계발광표시장치에 관한 것으로, 특히 유기전계발광층의 수축 또는 특성 저하를 방지한 유기전계발광표시장치 및 그 제조방법을 개시한다. 개시된 본 발명의 유기전계발광표시장치는, 제 1 기판; 제 2 기판; 상기 제 1 기판 상에 형성된 유기전계발광층; 및 상기 제 2 기판 상에 형성된 박막 트랜지스터를 포함하고, 상기 유기전계발광층은 상기 제 1 기판의 제 1 전극 상에 형성된 홈 내측에 형성되고, 제 2 전극에 의해 차폐된 것을 특징으로 한다.

본 발명은 유기전계발광층이 외부 습기 또는 유기막의 가스(gas)에 의해 특성이 저하되는 것을 방지한 효과가 있다.

#### **대표도** - 도2

#### 특허청구의 범위

#### 청구항 1

제 1 기판;

제 2 기판;

상기 제 1 기판 상에 형성된 유기전계발광층; 및

상기 제 2 기판 상에 형성된 박막 트랜지스터를 포함하고,

상기 유기전계발광층은 상기 제 1 기판의 제 1 전극 상에 형성된 홈 내측에 형성되고, 제 2 전극에 의해 차폐된 것을 특징으로 하는 유기전계발광표시장치.

#### 청구항 2

제 1 항에 있어서, 상기 제 1 전극 상에 형성된 홈에서의 전극 두께는 다른 영역에서의 제 1 전극 두께의 절반 이하인 것을 특징으로 하는 유기전계발광표시장치.

#### 청구항 3

제 1 항에 있어서, 상기 유기전계발광층은 서브 픽셀을 구획하는 버퍼층 사이에 형성되는 것을 특징으로 하는 유기전계발광표시장치.

#### 청구항 4

제 1 항에 있어서, 상기 유기전계발광층은 백색 유기전계발광층 또는 적, 녹, 청이 적층된 유기전계발광층인 것을 특징으로 하는 유기전계발광표시장치.

#### 청구항 5

제 4 항에 있어서, 상기 제 1 기판 상에는 적, 녹, 청 컬러필터를 더 포함하는 것을 특징으로 하는 유기전계발 광표시장치.

#### 청구항 6

제 1 항에 있어서, 상기 유기전계발광층은 각각 적, 녹, 청 유기전계발광층인 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 7

기판을 제공하는 단계;

상기 기판 상에 금속막을 형성하여 제 1 전극을 형성하고, 계속하여 마스크를 포함하는 포토리쏘그래피방법으로 식각하여 픽셀 영역에 소정의 단차를 갖는 홈을 형성하는 단계;

상기 제 1 전극의 홈 영역에 유기전계발광층을 형성하는 단계; 및

상기 유기전계발광층이 형성된 기판 상에 금속막을 형성하여 제 2 전극을 형성하는 단계를 포함하는 유기전계발 광표시장치 제조방법.

#### 청구항 8

제 7 항에 있어서, 상기 제 1 전극은 ITO, IZO, ITZO중 어느 하나의 금속으로 형성하는 것을 특징으로 하는 유기전계발광표시장치 제조방법.

#### 청구항 9

제 7 항에 있어서, 상기 제 1 전극 상에 홈을 형성한 후, 픽셀 영역을 구획하는 버퍼층 형성 공정을 더 포함하는 것을 특징으로 하는 유기전계발광표시장치 제조방법.

#### 청구항 10

제 9 항에 있어서, 상기 유기전계발광층은 버퍼층 사이에 형성하는 것을 특징으로 하는 유기전계발광표시장치 제조방법.

#### 청구항 11

제 9 항에 있어서, 상기 제 1 전극 형성전 금속막을 기판 상에 형성한 다음, 식각하여 보조전극을 형성하는 공 정을 더 포함하는 것을 특징으로 하는 유기전계발광표시장치 제조방법.

#### 청구항 12

제 7 항에 있어서, 상기 제 1 전극에 형성된 홈 영역의 전극 두께는 다른 영역의 전극 두께보다 절반 이하인 것을 특징으로 하는 유기전계발광표시장치 제조방법.

#### 청구항 13

제 7 항에 있어서, 상기 유기전계발광층은 적, 녹, 청 유기전계발광층이 적충된 구조 또는 백색 유기전계발광층으로 형성하는 것을 특징으로 하는 유기전계발광표시장치 제조방법.

#### 청구항 14

제 7 항에 있어서, 상기 유기전계발광층은 각각 적, 녹, 청 유기전계발광층인 것을 특징으로 하는 유기전계발 광표시장치 제조방법.

#### 청구항 15

제 7 항에 있어서, 상기 기판 상에 제 1 전극 형성 후, 금속막을 형성한 다음 식각하여 보조전극을 형성하는 공 정을 더 포함하는 것을 특징으로 하는 유기전계발광표시장치 제조방법.

#### 명세서

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <14> 본 발명은 유기전계발광표시장치에 관한 것으로, 특히 유기전계발광충의 수축 또는 특성 저하를 방지한 유기전 계발광표시장치 및 그 제조방법에 관한 것이다.

- <15> 최근, 음극선관(Cathode Ray Tube)의 단점인 무게와 부피를 줄일 수 있는 각종 평판표시장치들이 개발되고 있다. 이러한 평판표시장치는 액정표시장치(Liquid Crystal Display), 전계 방출 표시장치(Field Emission Display), 플라즈마 디스플레이 패널(Plasma Display Panel) 및 전계발광(Electro-Luminescence)표시장치 등이 있다.

- <16> 최근에 이와 같은 평판표시장치의 표시품질을 높이고 대화면화를 시도하는 연구들이 활발히 진행되고 있다. 이들 중 전계발광표시장치는 스스로 발광하는 자발광 소자이다. 전계발광표시장치는 전자 및 정공 등의 캐리어를 이용하여 형광물질을 여기 시킴으로써 비디오 영상을 표시하게 된다. 이 전계발광표시장치는 사용하는 재료에 따라 무기 전계발광표시장치와 유기 전계발광표시장치로 크게 나누어진다. 상기 유기 전계발광표시장치은 100~200V의 높은 전압을 필요로 하는 무기 전계발광표시장치에 비해 5~20V 정도의 낮은 전압으로 구동됨으로써 직류 저전압 구동이 가능하다.

- <17> 또한, 유기 전계발광표시장치는 넓은 시야각, 고속 응답성, 고 콘트라스트비(contrast ratio) 등의 뛰어난 특징이 있으므로, 그래픽 디스플레이의 픽셀(pixel), 텔레비젼 영상 디스플레이나 표면 광원(Surface Light Source)의 픽셀로서 사용될 수 있으며, 얇고 가벼우며 색감이 좋기 때문에 차세대 평면 디스플레이로서 적합하다.

- <18> 한편, 이러한 유기 전계발광표시장치의 구동방식으로는 별도의 박막트랜지스터를 구비하지 않는 패시브 매트릭스 방식(Passive matrix type)이 주로 이용되고 있다.

- <19> 그러나, 상기 패시브 매트릭스 방식은 해상도나 소비전력, 수명 등에 많은 제한적인 요소가 있기 때문에, 고해 상도나 대화면을 요구하는 차세대 디스플레이 제조를 위한 액티브 매트릭스형 전계발광표시장치가 연구/개발되 고 있다.

- <20> 이하, 첨부된 도면을 참조하여 종래의 유기전계발광표시장치를 상세히 설명하면 다음과 같다.

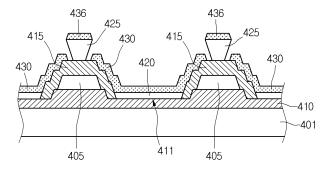

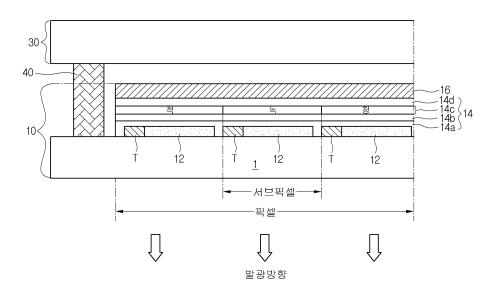

- <21> 도 1은 종래 하부발광방식 유기전계발광표시장치의 개략적인 단면도로서, 이는 하부 발광방식으로 동작하는 AMOLED의 단면 구조를 나타내고 있다.

- <22> 설명의 편의상 적(R), 녹(G), 청(B)의 서브 픽셀(sub pixel)들로 이루어진 하나의 픽셀(pixel) 영역을 중심으로 도시하였다.

- <23> 도시된 바와 같이, 제 1 기판(10)의 투명 기판(1) 상부에는 서브 픽셀별로 박막트랜지스터(T)와 제 1 전극(12)이 형성되어 있고, 상기 박막트랜지스터(T)및 제 1 전극(12)상부에는 적(Red), 녹(Green), 청(Blue) 컬러를 따는 유기전계발광충(14)이 형성되어 있고, 유기전계발광충(14)상부에는 제 2 전극(16)이 형성되어 있다. 상기제 1, 2 전극(12, 16)은 유기전계발광충(14)에 전계를 인가해주는 역할을 한다.

- <24> 이와 같이, 상기 유기전계발광층(14)이 형성된 제 1 기판(10)은 제 2 기판(30)과 실(40)에 의해 합착된다.

- 한 예로, 하부발광방식 구조에서 상기 제 1 전극(12)을 양극(anode)으로, 제 2 전극(16)을 음극(cathode)으로 구성할 경우 제 1 전극(12)은 투명도전성 물질에서 선택되고, 제 2 전극(16)은 일함수가 낮은 금속물질에서 선택되며, 이런 조건 하에서 상기 유기전계발광층(14)은 제 1 전극(12)과 접하는 층에서부터 정공주입층(14a; hole injection layer), 정공수송층(14b; hole transporting layer), 발광층(14c; emission layer), 전자수송층(14d; electron transporting layer) 순서대로 적층된 구조를 이룬다. 전자주입층을 더 포함할 수 있다.

- <26> 이때, 상기 발광층(14c)은 서브픽셀별로 적, 녹, 청 컬러를 구현하는 발광물질이 차례대로 배치된 구조를 가진다.

- <27> 이와 같이, 기존의 유기전계발광표시장치는 박막트랜지스터(T)와 전극을 포함하는 어레이 소자와 유기전계발광다이오드가 동일 기판 상에 적층된 구조로 이루어지는 것을 특징으로 하였다.

- <28> 그러나, 앞서 설명한 종래의 하부 발광방식의 유기전계발광표시장치는, 상기 어레이 소자 및 유기전계발광 다이오드가 형성된 기판과 별도의 인캡슐레이션용 기판의 합착을 통해 소자를 제작하는데, 이 경우 어레이 소자의수율과 유기전계발광 다이오드의 수율의 곱이 유기전계발광 소자의 수율을 결정하기 때문에, 후반 공정에 해당되는 유기전계발광 다이오드 공정에 의해 전체 공정 수율이 크게 제한되는 문제점이 있다. 이로 인하여, 양품의어레이 소자를 제조하는데 소요되었던 제반 경비 및 재료비 손실이 초래되고, 생산수율이 저하되는 문제점이 있다.

- <29> 또한, 하부 발광방식의 유기전계발광표시장치는, 유기전계발광층이 외부 습기 침투가 용이하여 유기전계발광층의 특성이 저하되는 문제가 있다.

#### 발명이 이루고자 하는 기술적 과제

- <30> 본 발명은, 유기전계발광층이 형성된 상부기판과, 박막트랜지스터 등이 형성된 하부기판으로 구성하고, 상부기판의 양전극 영역에 유기전계발광층이 증착될 홈을 형성하여 유기전계발광층의 수축을 방지한 유기전계발광표시장치 및 그 제조방법을 제공함에 그 목적이 있다.

- <31> 또한, 본 발명은 상부기판의 양전극 영역에 유기전계발광층을 전극에 의해 완전히 감싸지도록 구조 변경을 하여 유기전계발광층이 외부 습기 또는 유기막의 가스(gas)에 의해 특성이 저하되는 것을 방지한 유기전계발광표시장 치 및 그 제조방법을 제공함에 다른 목적이 있다.

#### 발명의 구성 및 작용

- <32> 상기한 목적을 달성하기 위한, 본 발명에 따른 유기전계발광표시장치는,

- <33> 제 1 기판;

- <34> 제 2 기판;

- <35> 상기 제 1 기판 상에 형성된 유기전계발광층; 및

- <36> 상기 제 2 기판 상에 형성된 박막 트랜지스터를 포함하고,

- <37> 상기 유기전계발광층은 상기 제 1 기판의 제 1 전극 상에 형성된 홈 내측에 형성되고, 제 2 전극에 의해 차폐된 것을 특징으로 한다.

- <38> 본 발명의 다른 실시예에 따른 유기전계발광표시장치 제조방법은,

- <39> 기판을 제공하는 단계;

- <40> 상기 기판 상에 금속막을 형성하여 제 1 전극을 형성하고, 계속하여 마스크를 포함하는 포토리쏘그래피방법으로 식각하여 픽셀 영역에 소정의 단차를 갖는 홈을 형성하는 단계;

- <41> 상기 제 1 전극의 홈 영역에 유기전계발광층을 형성하는 단계; 및

- <42> 상기 유기전계발광층이 형성된 기판 상에 금속막을 형성하여 제 2 전극을 형성하는 단계를 포함한다.

- <43> 본 발명에 의하면, 유기전계발광층이 형성된 상부기판과, 박막트랜지스터 등이 형성된 하부기판으로 구성하고, 상부기판의 양전극 영역에 유기전계발광층이 증착될 홈을 형성하여 유기전계발광층의 수축을 방지하였다.

- <44> 또한, 본 발명은 상부기판의 양전극 영역에 유기전계발광충을 전극에 의해 완전히 감싸지도록 구조 변경을 하여 유기전계발광층이 외부 습기 또는 유기막의 가스(gas)에 의해 특성이 저하되는 것을 방지하였다.

- <45> 이하, 첨부한 도면에 의거하여 본 발명의 실시 예를 자세히 설명하도록 한다.

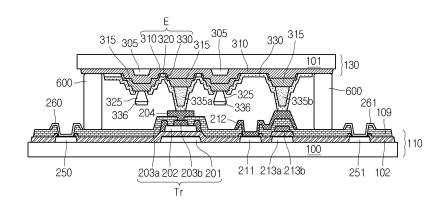

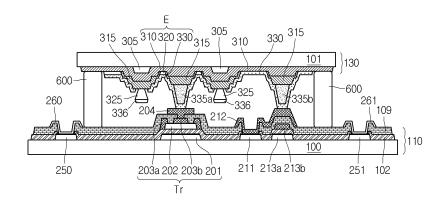

- <46> 도 2는 본 발명에 따른 유기전계발광표시장치의 합착 구조를 도시한 도면이다.

- <47> 도 2에 도시된 바와 같이, 본 발명의 실시예에 따른 유기전계발광표시장치는 적(R), 녹(G), 청(B)의 유기전계발 광 다이오드(E)가 서브 픽셀(sub pixel) 단위로 형성된 상부기판(130)과, 상기 유기전계발광 다이오드(E)에 대 응되도록 박막트랜지스터(Tr)를 포함하는 어레이층이 형성된 하부기판(110)이 씰재(600)에 의해 합착된 구조로 되어 있다.

- <48> 특히, 본 발명에서는 상부기판(130) 상에 형성되는 유기전계발광층(320)이 외부 습기 또는 제 1 컬럼스페이서 (335a) 및 제 2 컬럼스페이서(335b)와 같은 유기층으로부터 발생되는 아웃가싱(outgassing)에 의해 특성 저하가 발생되지 않도록 유기전계발광층(320)을 전극으로 밀폐시켰다. 상세하게는 상부기판(130)의 서브 픽셀 영역에 형성된 제 1 전극(310)중 유기전계발광층(320)이 형성될 영역에 소정의 단차를 갖는 홈을 형성하고, 홈 영역 내에 유기전계발광층(320)이 형성되도록 한 다음, 제 2 전극(330)에 의해 유기전계발광층(320)을 외부로부터 차단시켰다.

- <49> 즉, 제 1 전극(310)의 홈과 제 2 전극(330)에 의해 서브 픽셀 영역에 형성되는 유기전계발광층(320)은 완전히 봉입된다.

- <50> 또한, 상기 유기전계발광층(320)은 적(R), 녹(G), 청(B)의 유기전계발광층을 각각의 서브 픽셀 단위로 형성하고 있고, 각 유기전계발광층을 적, 녹, 청 유기전계발광층이 적충되어 백생광을 발생시키는 유기전계발광층으로 형성할 수 있다.

- <51> 또는, 상기 유기전계발광층(320)을 백색 유기전계발광층으로 형성할 수 있고, 유기전계발광층(320)이 백생광을 발생시키는 경우에는 상부기판(130) 상에 적, 녹, 청 컬러필터를 서브 픽셀 단위로 추가 형성할 수 있을 것이다.

- <52> 유기전계발광표시장치의 상부기판(130)과 하부기판(110)의 구체적인 구조는 다음과 같다.

- <53> 먼저, 하부기판(110)은 제 1 절연기판(100) 상에 알루미늄(Al) 또는 그 합금(AlNd)의 단일층, 알루미늄 또는 그 합금 상에 몰리브덴(Mo)의 이중층으로된 게이트 전극(201)과, 전원배선(211)과 제 1 더미패턴(213a)이 형성되어 있다. 또한, 제 1 절연기판(100) 양측 가장자리 영역에는 각각 외부로부터 전원을 공급 받기 위한 전원패드 (250)와 공통전압을 공급받기 위한 공통패드(251)가 각각 형성되어 있고, 각각의 전원패드(250)와 공통패드 (251) 상에는 ITO 또는 IZO와 같은 투명금속에 의해 전원패드 콘택부(260)와 공통패드 콘택부(261)가 형성되어 있다.

- <54> 상기 게이트 전극(201) 상부에는 게이트 절연막(102)을 사이에 두고 채널층과 오믹접촉층으로 구성된 액티브층 (202)이 형성되어 있고, 상기 액티브층(202)에는 각각 소스/드레인 전극(203a, 203b)이 형성되어 있어 하나의 스위칭 소자인 박막트랜지스터(Tr)를 이룬다. 상기 드레인 전극(203a, 203b) 상에는 보호막(109) 상에 형성된

콘택홀을 통하여 콘택부(204)가 형성되어 있어, 상부기판(130)의 제 2 전극(330)과 전기적 콘택되어 있다.

- <55> 전원배선(211) 영역에는 상부기판(130) 상에 전원을 공급하기 위해 전원배선(211) 상에는 전원전극(212)이 형성되어 있어, 상기 전원배선(211)으로부터 공급되는 전압을 상부기판(130)의 제 1 전극(310)에 공급할 수 있도록하였다. 상기 제 1 더미패턴(413a) 상부에는 제 2 더미패턴(413b)이 형성되어 있다. 즉, 전원전극(212)과 대응되는 상부기판(130) 상에는 제 1 전극(310)과 제 2 전극(330)이 직접 콘택되어 있어 전원전극(212)에서의 전원전압이 상부기판(130)의 제 1 전극(310)에 공급될 수 있도록 형성한다.

- <56> 상부기판(130)은 제 2 절연기판(101) 상에 보조전극(305)이 형성되어 있고, 상기 보조전극(305)이 형성된 제 2 절연기판(101) 상에는 제 1 전극(310)이 형성되어 있다. 이때 본 발명에서는 유기전계발광층(320)이 형성될 영역에 마스크 공정으로 식각하여 소정의 홈을 형성하였다. 제 1 전극(310) 상에 형성된 홈 영역에는 유기전계발광층(320)이 형성되어 있고, 보조전극(305) 상부와 제 1, 2 컬럼스페이서(335a, 335b)가 형성될 영역에 각각 버 퍼층(315)이 형성되어 있다.

- <57> 여기서, 제 1 전극(310)은 투명성 도전물질을 사용하고, 그 재질은 인듐-옥사이드(Indium-Tin-Oxide ; 이하" ITO" 라 함), 인듐-아연-옥사이드(Indium-Zinc-Oxide ; 이하" IZO" 라 함), 인듐-틴-아연-옥사이드(Indium-Tin-Zinc-Oxide ; 이하" ITZO" 라함) 등을 사용한다.

- <58> 또한, 보조전극(305) 상부의 버퍼층(315) 상에는 서브픽셀을 구분하기 위한 격벽(325)이 형성되어 있다.

- <59> 상기 유기전계발광층(320)이 형성된 영역과 제 1, 2 컬럼스페이서(335a, 335b) 상에는 제 2 전극(330)이 형성되어 있고, 격벽(325) 상에는 제 2 전극(330) 형성 공정 과정에서 형성된 금속패턴(336)이 형성되어 있다.

- <60> 본 발명에서는 유기전계발광층(320)이 형성될 제 1 전극(310) 영역에 소정의 단차를 갖는 홈을 형성하고, 그 홈 내부에 유기전계발광층(320)을 형성함으로써, 유기전계발광층(320)이 버퍼층(315) 및 제 1, 2 컬럼스페이서 (335a, 335b)와 완전히 차단될 수 있도록 하였다.

- <61> 따라서, 외부 습기 침투 또는 유기층인 컬럼스페이서로부터 발생되는 아웃가스에 의해 유기전계발광층(320)의 특성이 저하되지 않아 유기전계발광표시장치의 수명을 연장하고 소자 특성을 개선한 효과가 있다.

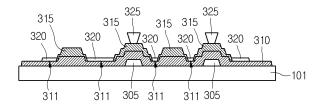

- <62> 도 3a 내지 도 3f는 본 발명에 따른 유기전계발광표시장치의 상부기판 제조공정을 도시한 단면도이다.

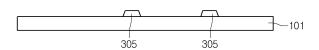

- <63> 도 3a 및 도 3b에 도시된 바와 같이, 제 2 절연기판(101) 상에 금속막을 형성한 다음, 마스크를 포함하는 포토리쏘그래피 방법으로 식각하여 보조전극(305)을 형성한다. 그런 다음, 보조전극(305)이 형성된 제 2 절연기판(101) 상에 투명성 금속재질 예를 들어 ITO, IZO, ITZO 등의 금속막을 형성한 다음, 마스크를 포함하는 포토리쏘그래피 방법으로 식각하여 제 1 전극(310)을 형성하고, 제 1 전극(310) 중 유기전계발광층이 형성될 영역(서브 픽셀 영역)에 소정의 홈(311)을 형성한다.

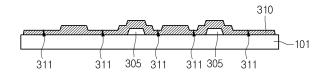

- <64> 상기와 같이 제 1 전극(310) 상에 홈(311)이 형성되면, 도 3c에 도시한 바와 같이, 절연막을 형성한 다음 식각 하여 보조전극(305) 상부와 컬럼스페이서가 형성될 영역에 버퍼층(315)을 형성한다.

- <65> 만약, 형성될 유기전계발광층이 적, 녹, 청 유기전계발광층이 적충된 구조이거나 백색광을 발생시키는 백색 유기전계발광층일 경우에는 제 1 전극(310)의 홈(311) 영역 또는 제 2 절연기판(101) 상에 추가적으로 적, 녹, 청 컬러필터 형성 공정을 추가할 수 있다.

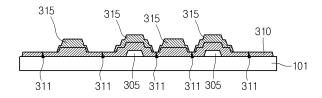

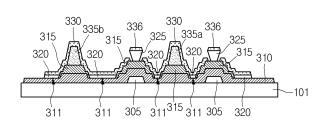

- <66> 상기와 같이 제 1 전극(310) 상에 버퍼층(315)이 형성되면 도 3d에 도시한 바와 같이, 상기 제 1 전극(310) 상에 유기전계발광층(320)을 형성한다. 이때, 본 발명에서는 서브 픽셀 영역에 대응되는 제 1 전극(310) 상에 형성된 홈(311)에 유기전계발광층(320)을 형성한다. 따라서, 상기 유기전계발광층(320)은 제 1 전극(310)에 형성된 홈(311) 내측에 형성된다.

- <67> 상기 홈(311)의 단차는 제 1 전극(310)의 두께의 절반 정도의 범위를 갖도록 한다. 따라서, 홈(311) 영역의 제 1 전극(310)의 두께는 다른 영역의 제 1 전극(310) 두께의 절반이하 정도이다. 예를 들어, 제 1 전극(310)의 두께가 200nm 내외이면 홈(311) 영역에서의 제 1 전극(310)의 두께는 100nm 내외를 갖도록 한다.

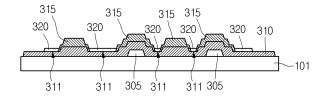

- <68> 상기와 같이 유기전계발광층(320)이 제 1 전극(310) 상에 형성되면, 도 3e에 도시한 바와 같이, 유기막을 제 2 절연기판(101) 상에 형성한 다음, 현상하여 격벽(325)을 형성한다. 그런 다음, 도 3f에 도시한 바와 같이, 유기막을 제 2 절연기판(101) 상에 형성한 다음 제 1, 2 컬럼스페이서(335a, 335b)를 형성하고, 계속해서 금속막을 제 2 절연기판(101) 상에 형성하여 제 2 전극(330)을 형성한다. 이때, 공정상 격벽(325) 상에는 금속패턴(336)이 남는다.

- <69> 따라서, 본 발명에서는 유기전계발광층(320)이 제 1 전극(310)의 홈(311) 영역에 형성되고, 그 위에 제 2 전극 (330)이 형성되어 인접한 컬럼스페이서와 이격되도록 하였다. 아울러, 버퍼층(315)과의 접촉 영역도 매우 적고 제 2 전극(330)이 유기전계발광층(320)을 외부와 차폐시키므로 유기전계발광층(320)의 특성저하를 최소화할 수 있다.

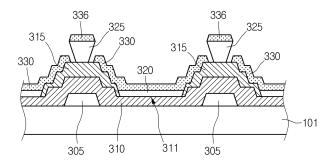

- <70> 도 4는 상기 도 3f의 유기전계발광층 영역을 확대한 도면으로서, 도시된 바와 같이, 제 2 절연기판(101) 상에는 보조전극(305)을 사이에 두고 유기전계발광층(320)이 제 1 전극(310) 상에 형성되어 있다. 유기전계발광층(320)이 제 1 전극(310) 상에는 형성된 홈(311) 영역에만 형성되어 있기 때문에 유기전계발광층(320)이 버퍼층 (315)들 사이에만 존재한다. 326은 제 2 전극(330) 형성중 남아 있는 금속패턴이다

- <71> 또한, 유기전계발광층(320) 상에는 제 2 전극(330)이 유기전계발광층(320)을 외부와 완전히 차단되도록 버퍼층 (315)과 유기전계발광층(320) 상에 형성되어 있다.

- <72> 따라서, 유기전계발광층(320)은 유기물로 형성되는 격벽(325) 또는 컬럼스페이서와 이격되어 유기물로부터 빈번 하게 발생되는 아웃가스가 유기전계발광층(320)에 영향을 받지 않는다.

- <73> 따라서, 유기전계발광층(320)은 유기막들과 이격되도록 형성되면서, 전극에 의해 완전히 외측과 차단되기 때문에 장시간 유기전계발광표시장치 사용에 따른 유기전계발광층(320)의 특성 저하를 최소화할 수 있다.

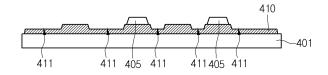

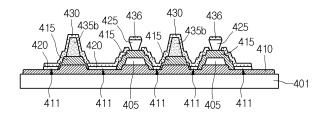

- <74> 도 5a 내지 도 5f는 본 발명의 다른 실시예에 따른 유기전계발광표시장치의 상부기판 제조공정을 도시한 단면도이다.

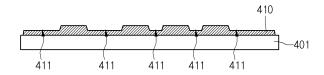

- <75> 도 5a 및 도 5b에 도시된 바와 같이, 투명성 절연기판(401) 상에 투명성 도전 물질을 형성하여 제 1 전극(410)을 형성하고, 마스크를 포함하는 포토리쏘그래피방법으로 식각하여 유기전계발광층이 형성될 영역에 홈(411)을 형성한다. 상기 투명성 도전 물질은 ITO, IZO, ITZO중 어느 하나를 사용한다. 상기 홈(411)의 단차는 제 1 전극(410)의 두께의 절반 정도의 범위를 갖도록 한다. 따라서, 홈(411) 영역의 제 1 전극(410)의 두께는 다른 영역의 제 1 전극(410) 두께의 절반이하 정도이다. 예를 들어, 제 1 전극(410)의 두께가 200mm 내외이면 홈(411) 영역에서의 제 1 전극(410)의 두께는 100mm 내외를 갖도록 한다.

- <76> 상기와 같이 절연기판(401) 상에 제 1 전극(410)이 형성되면, 금속막을 절연기판(401) 상에 형성한 다음, 마스 크를 포함하는 포토리쏘그래피방법으로 식각하여 보조전극(405)을 형성한다.

- <77> 만약, 형성될 유기전계발광층이 적, 녹, 청 유기전계발광층이 적층된 구조이거나 백색광을 발생시키는 백색 유기전계발광층일 경우에는 제 1 전극(410)의 홈(411) 영역 또는 절연기판(401) 상에 추가적으로 적, 녹, 청 컬러 필터 형성 공정을 추가할 수 있다.

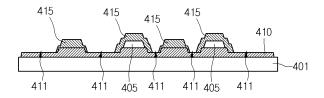

- <78> 그런 다음, 도 5c에 도시한 바와 같이, 절연기판(401) 상에 절연막을 형성한 다음, 식각하여 보조전극(405) 상부와 컬럼스페이서가 형성될 영역에 각각 버퍼층(415)을 형성한다.

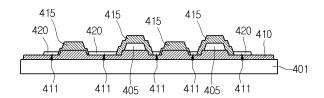

- <79> 상기와 같이 제 1 전극(410) 및 보조전극(405) 상에 버퍼층(415)이 형성되면 도 5d에 도시한 바와 같이, 제 1 전극(410) 상에 형성된 홈(411) 영역에 유기전계발광층(420)을 형성한다. 이때, 본 발명에서는 서브 픽셀 영역 에 대응되는 제 1 전극(410) 상에 홈(411)을 형성하고, 유기전계발광층(420)들을 모두 홈(411) 영역 내측에만 형성한다.

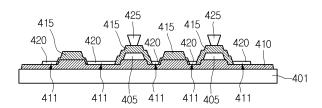

- <80> 상기와 같이 유기전계발광층(420)이 제 1 전극(410) 상에 형성되면, 도 5e에 도시한 바와 같이, 유기막을 절연기판(401) 상에 형성한 다음, 현상하여 격벽(425)을 형성한다. 그런 다음 도 5f에 도시한 바와 같이, 유기막을 절연기판(401) 상에 형성한 다음 제 1, 2 컬럼스페이서(435a, 435b)를 형성하고, 계속해서 금속막을 절연기판(401) 상에 형성하여 제 2 전극(430)을 형성한다. 이때, 공정상 격벽(425) 에는 제 2 전극(430)과 동일한 금속물질로된 금속패턴(436)이 형성된다.

- <81> 따라서, 본 발명에서는 유기전계발광층(420)이 제 1 전극(410)의 홈(411) 영역에 형성되고, 그 위에 제 2 전극 (430)이 형성되어 인접한 컬럼스페이서와 이격되도록 하였다. 즉 유기전계발광층(420)은 제 1 전극(410)과 제 2 전극(430)에 의해 외부와 완전히 차폐된다. 아울러, 버퍼층(415)과의 접촉 영역도 매우 적고 제 2 전극(430)이 유기전계발광층(420)을 외부와 차단시키므로 유기전계발광층(420)의 특성 저하를 최소화할 수 있다.

- <82> 도 6은 상기 도 5f의 유기전계발광층 영역을 확대한 도면이다.

- <83> 도 6에 도시된 바와 같이, 절연기판(401) 상에는 제 1 전극(410)이 형성되어 있고, 제 1 전극(410)의 서브 픽셀 영역에는 소정의 단차를 갖는 홈(411)이 형성되어 있다. 또한, 제 1 전극(410) 상에는 홈(411)을 사이에 두고

보조전극(405)이 형성되어 있고, 홈(411) 영역에는 유기전계발광층(420)이 형성되어 있다.

- <84> 따라서, 유기전계발광층(420)은 보조전극(405) 상에 형성된 버퍼층(415)들 사이에만 존재하게 된다. 제 2 전극 (430)이 유기전계발광층(420) 상에 형성되면서 유기전계발광층(420)은 외부 또는 인접한 유기층과 완전히 차단된다.

- <85> 또한, 유기전계발광층(420)은 유기물로 형성되는 격벽(425) 또는 컬럼스페이서들과 상당히 이격되어 있어 유기물로부터 빈번하게 발생되는 아웃가스가 유기전계발광층(420)에 영향을 주지 못한다. 도면에서 설명하지 않은 426은 금속패턴이다.

#### 발명의 효과

- <86> 이상에서 자세히 설명된 바와 같이, 본 발명은 유기전계발광층이 형성된 상부기판과, 박막트랜지스터 등이 형성된 하부기판으로 구성하고, 상부기판의 양전극 영역에 유기전계발광층이 증착될 홈을 형성하여 유기전계발광층의 수축을 방지한 효과가 있다.

- <87> 또한, 본 발명은 상부기판의 양전극 영역에 유기전계발광충을 전극에 의해 완전히 감싸지도록 구조 변경을 하여 유기전계발광충이 외부 습기 또는 유기막의 가스(gas)에 의해 특성이 저하되는 것을 방지한 효과가 있다.

- <88> 본 발명은 상기한 실시 예에 한정되지 않고, 이하 청구 범위에서 청구하는 본 발명의 요지를 벗어남이 없이 당해 발명이 속하는 분야에서 통상의 지식을 가진 자라면 누구든지 다양한 변경 실시가 가능할 것이다.

#### 도면의 간단한 설명

- <1> 도 1은 종래 하부발광방식 유기전계발광표시장치의 개략적인 단면도이다.

- <2> 도 2는 본 발명에 따른 유기전계발광표시장치의 구조를 도시한 도면이다.

- <3> 도 3a 내지 도 3f는 본 발명에 따른 유기전계발광표시장치의 상부기판 제조공정을 도시한 단면도이다.

- <4> 도 4는 상기 도 3f의 유기전계발광층 영역을 확대한 도면이다.

- <5> 도 5a 내지 도 5f는 본 발명의 다른 실시예에 따른 유기전계발광표시장치의 상부기판 제조공정을 도시한 단면도 이다.

- <6> 도 6은 상기 도 5f의 유기전계발광층 영역을 확대한 도면이다.

- <7> \*도면의 주요 부분에 대한 부호의 설명\*

- <8> 110: 하부기판 130: 상부기판

- <9> 201: 게이트 전극 203a: 소스 전극

- <10> 203b: 드레인 전극 311: 홈

- <11> 325: 격벽 320: 유기전계발광층

- <12> 335a: 제 1 컬럼스페이서 335b: 제 2 컬럼스페이서

- <13> 600: 씰재

# 도면

## 도면1

# 도면2

# 도면3a

## 도면3b

## 도면3c

### *도면3d*

## *도면3e*

# 도면3f

# 도면4

## 도면5a

## 도면5b

## 도면5c

## 도면5d

## *도면5e*

## 도면5f

## 도면6