# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 109427688 B (45) 授权公告日 2021. 12. 28

(21)申请号 201711291141.3

(22) 申请日 2017.12.08

(65) 同一申请的已公布的文献号 申请公布号 CN 109427688 A

(43) 申请公布日 2019.03.05

(30) 优先权数据 15/691,868 2017.08.31 US

(73) **专利权人** 台湾积体电路制造股份有限公司 地址 中国台湾新竹

(72) 发明人 黄诗涵 谢志宏

(74) 专利代理机构 北京德恒律治知识产权代理 有限公司 11409

代理人 章社杲 李伟

(51) Int.CI.

*H01L* 21/8244 (2006.01) *H01L* 27/11 (2006.01)

(56) 对比文件

TW 201539147 A,2015.10.16

CN 107068619 A, 2017.08.18

TW 201539147 A,2015.10.16

CN 106486343 A,2017.03.08

CN 103855097 A,2014.06.11

CN 103518253 A,2014.01.15

审查员 韩冰

权利要求书3页 说明书16页 附图28页

#### (54) 发明名称

静态随机存取存储(SRAM)器件及其相关的制造方法和系统

#### (57) 摘要

本发明的实施例提供了静态随机存取存储(SRAM)器件及其相关的制造方法和系统。在衬底上方形成多个栅极堆叠件。通过介电结构围绕栅极堆叠件。在介电结构上方形成多个接触线阻挡图案。使用三个或多个光刻掩模形成接触线阻挡图案。在介电结构中形成多个沟槽。接触线阻挡图案用作介电结构的保护掩模,以防止在介电结构的位于接触线阻挡图案下方的部分中形成沟槽。用导电材料填充沟槽以形成SRAM器件的多条接触线。

1.一种制造静态随机存取存储(SRAM)器件的方法,包括:

在衬底上方形成多个栅极堆叠件,其中,介电结构围绕所述多个栅极堆叠件;

在所述介电结构上方形成所述静态随机存取存储器件的多个接触线阻挡图案,其中,使用三个或更多个光刻掩模来形成所述多个接触线阻挡图案,并且在由第一方向和第二方向限定的俯视图中,所述多个接触线阻挡图案中的每个的位置与其他接触线阻挡图案的位置均不相同;

在所述介电结构中形成多个沟槽,其中,所述多个接触线阻挡图案中的每个用作所述 介电结构的保护掩模,以防止在所述介电结构的位于所述多个接触线阻挡图案下方的部分 中形成所述多个沟槽;以及

用导电材料填充所述沟槽以形成所述静态随机存取存储器件的多条接触线。

2. 根据权利要求1所述的方法,其中,形成所述多个接触线阻挡图案包括:

使用包括第一掩模图案的第一光刻掩模来形成第一接触线阻挡图案;

使用包括第二掩模图案的第二光刻掩模来形成第二接触线阻挡图案;以及

使用包括第三掩模图案的第三光刻掩模形成第三接触线阻挡图案。

- 3.根据权利要求2所述的方法,其中,形成所述多个沟槽包括蚀刻用于第一Vcc接触件的第一沟槽和用于第一Vss接触件的第二沟槽,并且,未蚀刻所述介电结构的设置在所述第一接触线阻挡图案下面且位于所述第一沟槽和所述第二沟槽之间的部分。

- 4.根据权利要求2所述的方法,其中,形成所述多个沟槽包括蚀刻用于第二Vcc接触件的第三沟槽和用于第一位线接触件的第四沟槽,并且其中,未蚀刻所述介电结构的设置在所述第二接触线阻挡图案下面且位于所述第三沟槽和所述第四沟槽之间的部分。

- 5.根据权利要求2所述的方法,其中,形成所述多个沟槽包括蚀刻用于第一节点接触件的第五沟槽和用于第二节点接触件的第六沟槽,并且其中,未蚀刻所述介电结构的设置在所述第三接触线阻挡图案下面且位于所述第五沟槽和所述第六沟槽之间的部分。

- 6.根据权利要求1所述的方法,还包括:在所述衬底上方形成多个鳍结构,并且,所述多个栅极堆叠件形成为每个栅极堆叠件均包裹在所述多个鳍结构中的一个的周围。

- 7.根据权利要求1所述的方法,其中,形成所述多个接触线阻挡图案包括:将掺杂剂注入到硅层的形成在所述介电结构上方的多个部分中,从而形成所述硅层的多个掺杂部分,其中,使用所述三个或多个光刻掩模中的相应光刻掩模来限定所述多个掺杂部分中的每一个。

- 8.根据权利要求1所述的方法,其中,通过相应的矩形掩模图案来限定所述多个接触线阻挡图案的每一个。

- 9. 一种制造静态随机存取存储 (SRAM) 器件的方法,包括:

形成多个栅极结构,其中,所述多个栅极结构的每个嵌入在层间电介质(ILD)中并且包裹在一个或多个半导体鳍结构周围;

在所述层间电介质上方形成硬掩模层;

在所述硬掩模层上方形成硅层:

在所述硅层中形成一个或多个第一掺杂组件,其中,通过第一光刻掩模来限定所述一个或多个第一掺杂组件;

在所述硅层中形成一个或多个第二掺杂组件,其中,通过与所述第一光刻掩模不同的

第二光刻掩模来限定所述一个或多个第二掺杂组件;

在所述硅层中形成一个或多个第三掺杂组件,其中,通过与所述第一光刻掩模和所述 第二光刻掩模不同的第三光刻掩模来限定所述一个或多个第三掺杂组件,并且在由第一方 向和第二方向限定的俯视图中,所述第一掺杂组件、所述第二掺杂组件和所述第三掺杂组 件中的每个的位置与另外的所述第一掺杂组件、所述第二掺杂组件和所述第三掺杂组件的 位置均不相同;

去除所述硅层的未掺杂部分;

图案化所述硬掩模层以在所述硬掩模层中限定多个沟槽,其中,所述硅层的所述第一掺杂组件、所述第二掺杂组件和所述第三掺杂组件中的每个防止在其自身下方形成沟槽线:

在所述层间电介质中蚀刻所述沟槽;以及

用金属材料填充所述层间电介质中的所述沟槽以形成所述静态随机存取存储器件的多个接触件。

- 10.根据权利要求9所述的方法,其中,所述图案化包括限定至少第一不连续的沟槽、第二不连续的沟槽和第三不连续的沟槽,从而用于所述静态随机存取存储器件中的每个静态随机存取存储单元。

- 11.根据权利要求10所述的方法,其中,所述第一不连续的沟槽包括沟槽区段,在所述 层间电介质中蚀刻所述沟槽区段并且用金属材料填充所述沟槽区段之后,形成位线接触件、Vcc接触件和Vss接触件。

- 12.根据权利要求11所述的方法,其中:

所述第二不连续的沟槽包括沟槽区段,在所述层间电介质中蚀刻所述沟槽区段并且用金属材料填充所述沟槽区段之后,形成第一节点接触件和第二节点接触件;以及

所述第三不连续的沟槽包括沟槽区段,在所述层间电介质中蚀刻所述沟槽区段并且用金属材料填充所述沟槽区段之后,形成Vss接触件、Vcc接触件和位线接触件。

13.一种制造静态随机存取存储(SRAM)器件的系统,包括:

至少三个彼此不同的光刻掩模,其中,所述至少三个光刻掩模中的每个包括一个或多个相应的掩模图案,并且,每个掩模图案配置为防止其自身下方的介电结构被去除而限定相应的接触线阻挡图案,并且,所述接触线阻挡图案配置为图案化所述静态随机存取存储器件的多条接触线;

其中,在由第一方向和第二方向限定的俯视图中,所述接触线阻挡图案中的每个的位置与其他接触线阻挡图案的位置均不相同。

- 14.根据权利要求13所述的系统,其中,所述至少三个光刻掩模包括:

- 第一光刻掩模,包括第一图案和第二图案;

- 第二光刻掩模,包括第三图案、第四图案和第五图案:以及

- 第三光刻掩模,包括第六图案和第七图案。

- 15.根据权利要求14所述的系统,其中:

所述第一图案配置为限定第一接触线阻挡图案,其中,所述第一接触线阻挡图案部分地限定第一Vcc接触件的边界和第一Vss接触件的边界;以及

所述第二图案配置为限定第二接触线阻挡图案,其中,所述第二接触线阻挡图案部分

地限定第二Vcc接触件的边界和第二Vss接触件的边界。

16.根据权利要求14所述的系统,其中:

所述第三图案配置为限定第三接触线阻挡图案,其中,所述第三接触线阻挡图案部分 地限定第一节点接触件的边界和第二节点接触件的边界;

所述第四图案配置为限定第四接触线阻挡图案,其中,所述第四接触线阻挡图案部分地限定第一位线接触件的边界和所述第一节点接触件的边界;以及

所述第五图案配置为限定第五接触线阻挡图案,其中,所述第五接触线阻挡图案部分地限定第二位线接触件的边界和所述第二节点接触件的边界。

17.根据权利要求14所述的系统,其中:

所述第六图案配置为限定第六接触线阻挡图案,其中,所述第六接触线阻挡图案部分地限定第一Vcc接触件的边界和第一位线接触件的边界;以及

所述第七图案配置为限定第七接触线阻挡图案,其中,所述第七接触线阻挡图案部分地限定第二Vcc接触件的边界和第二位线接触件的边界。

18.根据权利要求14所述的系统,其中:

所述接触线均在第一方向上延伸;

所述第一图案具有在与所述第一方向垂直的第二方向上测量的第一尺寸;

所述第六图案具有在所述第二方向上测量的第二尺寸,并且所述第一尺寸大于所述第二尺寸。

19.根据权利要求14所述的系统,其中:

所述接触线均在第一方向上延伸;

所述静态随机存取存储器件具有在与所述第一方向垂直的第二方向上测量的节距;以 及

在所述第二方向上测量的所述第四图案的尺寸大于所述静态随机存取存储器件的所述节距的1/2。

20.根据权利要求14所述的系统,其中,所述第一图案、所述第二图案、所述第三图案、所述第四图案、所述第五图案、所述第六图案和所述第七图案中的每个均成形为矩形。

# 静态随机存取存储(SRAM)器件及其相关的制造方法和系统

#### 技术领域

[0001] 本发明的实施例总体涉及半导体领域,更具体地,涉及静态随机存取存储(SRAM) 器件及其相关的制造方法和系统。

## 背景技术

[0002] 在深亚微米集成电路技术中,嵌入式静态随机存取存储(SRAM)器件已经成为高速通信、图像处理和芯片上系统(SOC)产品的流行存储单元。微处理器和SOC中的嵌入式SRAM的数量增加以满足每一新技术时代的性能要求。随着硅技术从一代到下一代的不断按比例缩小,最小几何尺寸块状平面晶体管的本征阈值电压(Vt)变化的影响降低了互补金属氧化物半导体(CMOS)SRAM单元静态噪声容限(SNM)。这种由越来越小的晶体管几何形状导致的SNM的减少是不期望的。当Vcc按比例缩小至较低电压时,进一步减小SNM。

[0003] 为了解决SRAM问题并且提高单元的收缩能力,在某些应用中经常考虑鳍式场效应晶体管 (FinFET) 器件。FinFET提供速度和器件稳定性。FinFET具有与顶面和相对侧壁相关联的沟道 (称为鳍沟道)。可以从额外的侧壁器件宽度 ( $I_{on}$ 性能) 以及较好的短沟道控制 (亚阈值泄漏) 获得益处。因此,期望FinFET在栅极长度按比例缩小和本征 $V_{t}$ 波动方面具有优势。然而,现有的FinFET SRAM器件仍然存在缺陷,例如与源极/漏极接触件和/或置放在鳍结构上的接触件之间的小工艺裕度有关的缺陷。此外,随着FinFET SRAM单元尺寸缩小,可能发生不期望的桥接。这些问题可能会对FinFET SRAM的性能和/或可靠性产生不利影响。

[0004] 因此,虽然现有的FinFET SRAM器件通常已经足够用于其期望目的,但它们还没有在各个方面完全令人满意。

### 发明内容

[0005] 根据本发明的一个方面,提供了一种制造静态随机存取存储(SRAM) 器件的方法,包括:在衬底上方形成多个栅极堆叠件,其中,介电结构围绕所述多个栅极堆叠件;在所述介电结构上方形成多个接触线阻挡图案,其中,使用三个或多个光刻掩模来形成所述多个接触线阻挡图案;在所述介电结构中形成多个沟槽,其中,所述多个接触线阻挡图案用作所述介电结构的保护掩模,以防止在所述介电结构的位于所述多个接触线阻挡图案下方的部分中形成所述多个沟槽;以及用导电材料填充所述沟槽以形成所述静态随机存取存储器件的多条接触线。

[0006] 根据本发明的另一个方面,提供了一种制造静态随机存取存储(SRAM)器件的方法,包括:形成多个栅极结构,其中,所述多个栅极结构的每个嵌入在层间电介质(ILD)中并且包裹在一个或多个半导体鳍结构周围;在所述层间电介质上方形成硬掩模层;在所述硬掩模层上方形成硅层;在所述硅层中形成一个或多个第一掺杂组件,其中,通过第一光刻掩模来限定所述一个或多个第一掺杂组件;在所述硅层中形成一个或多个第二掺杂组件,其中,通过与所述第一光刻掩模不同的第二光刻掩模来限定所述一个或多个第二掺杂组件;在所述硅层中形成一个或多个第二掺杂组件;在所述硅层中形成一个或多个第三掺杂组件,其中,通过与所述第一光刻掩模和所述第二

光刻掩模不同的第三光刻掩模来限定所述一个或多个第三掺杂组件;去除所述硅层的未掺杂部分;图案化所述硬掩模层以在所述硬掩模层中限定多个沟槽,其中,所述硅层的掺杂部分防止在其自身下方形成沟槽线;在所述层间电介质中蚀刻所述沟槽;以及用金属材料填充所述层间电介质中的所述沟槽以形成所述静态随机存取存储器件的多个接触件。

[0007] 根据本发明的又一个方面,提供了一种系统,包括:至少三个彼此不同的光刻掩模,其中,所述至少三个光刻掩模中的每个包括一个或多个相应的掩模图案,并且,每个掩模图案配置为限定相应的接触线阻挡图案,并且,所述接触线阻挡图案配置为图案化静态随机存取存储(SRAM)器件的多条接触线。

## 附图说明

[0008] 当结合附图进行阅读时,从以下详细描述可最佳地理解本发明的各个方面。应该注意,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各种部件的尺寸可以被任意增大或减小。还要强调的是,附图仅示出了本发明的典型实施例,因此不应认为是对范围的限制,因为本发明可以同样应用于其他实施例。

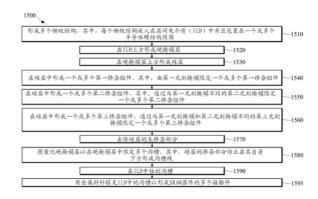

[0009] 图1是示例性FinFET器件的立体图。

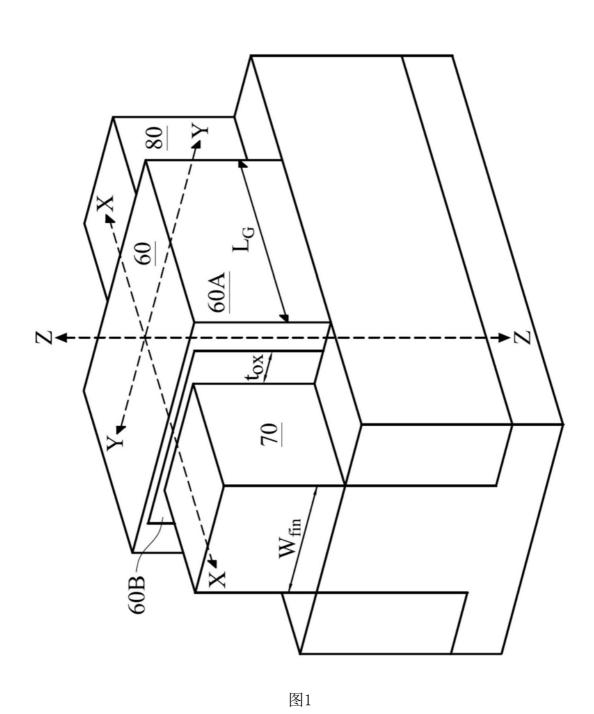

[0010] 图2示出根据本发明的实施例的用于1位SRAM单元的电路示意图。

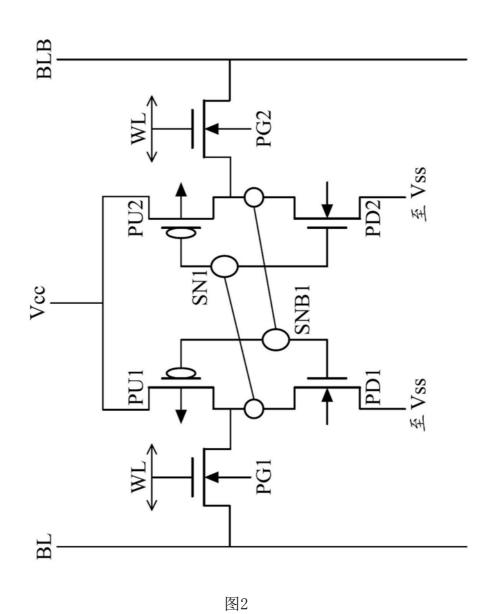

[0011] 图3示出根据本发明的实施例的各种掩模图案的顶视图。

[0012] 图4示出根据本发明的实施例的图3的1位SRAM单元和掩模图案的叠加的顶视图。

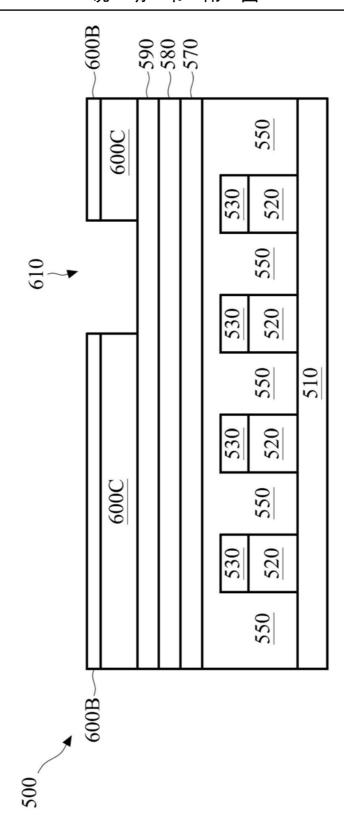

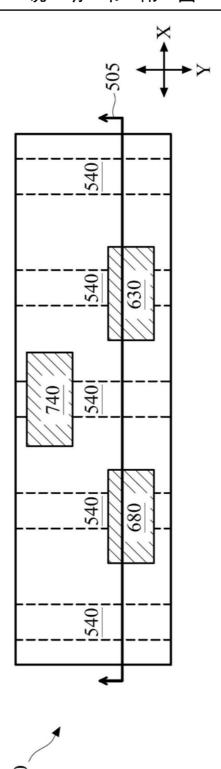

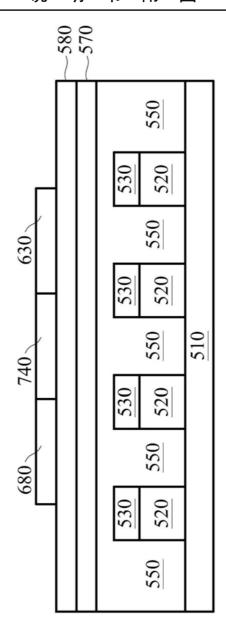

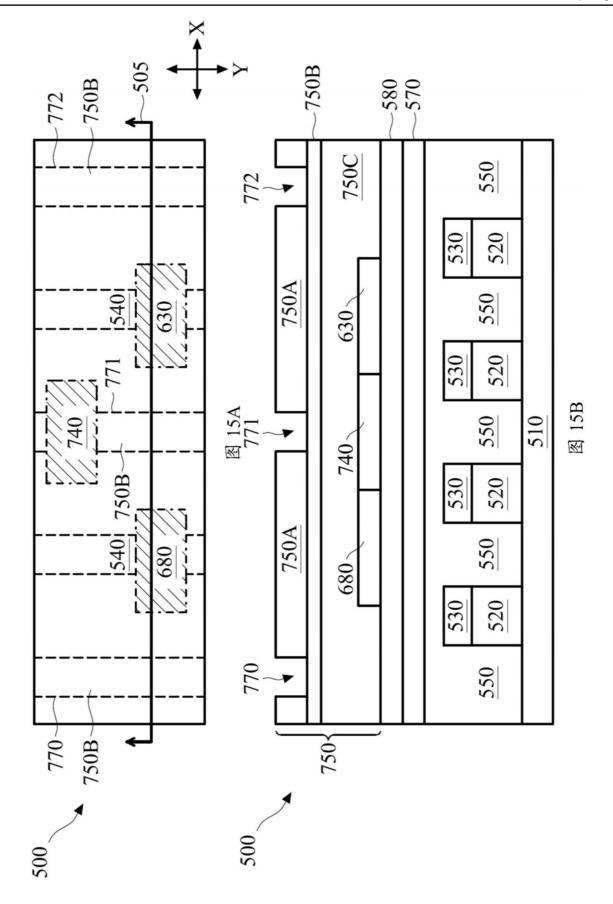

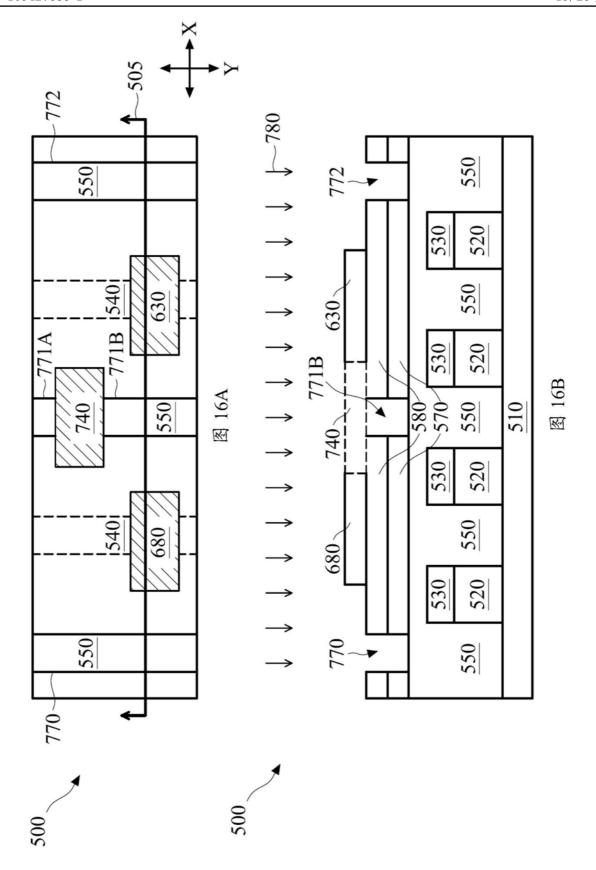

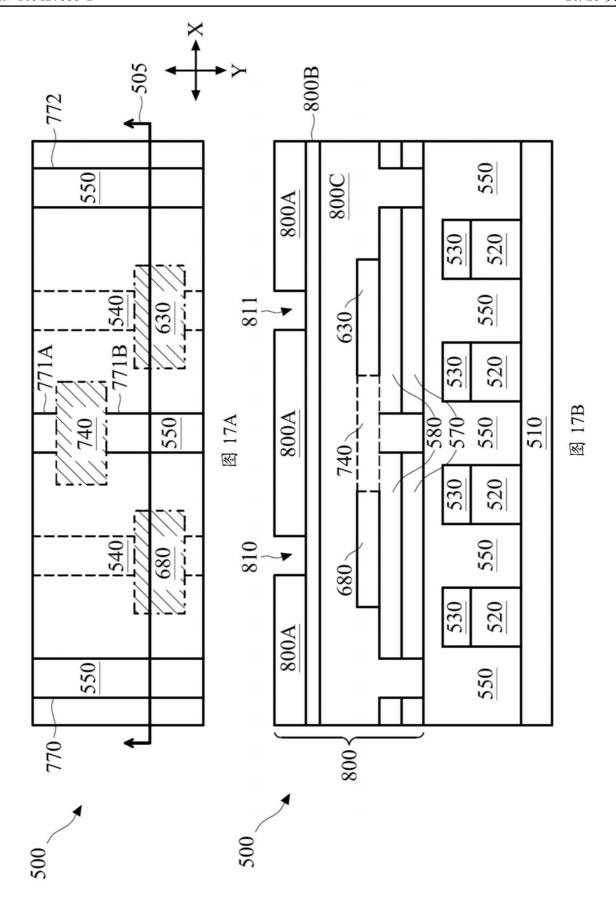

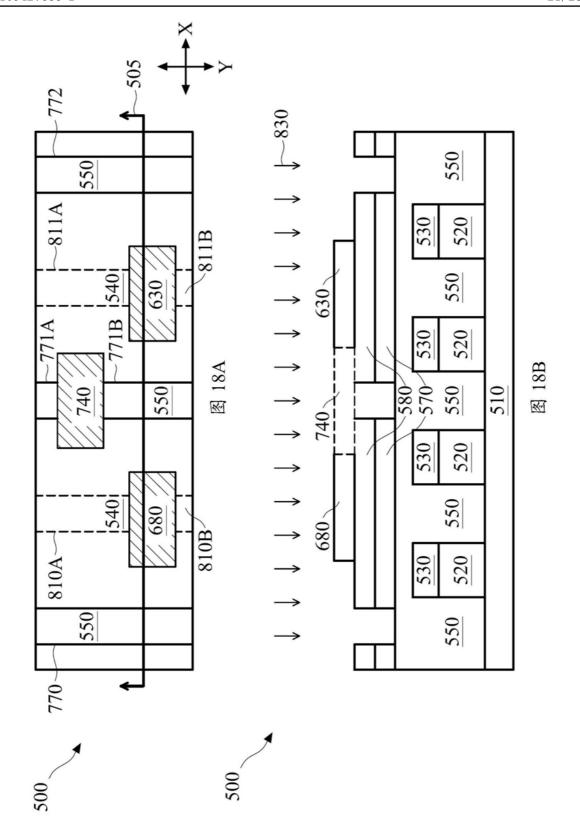

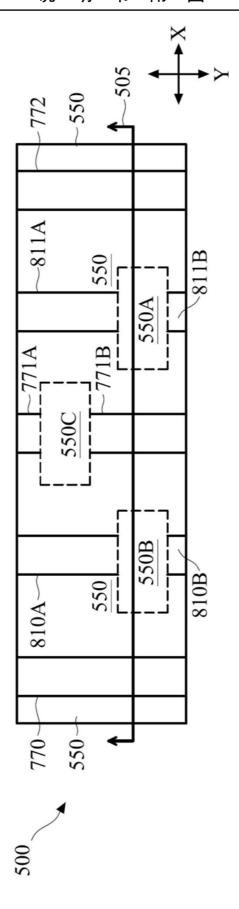

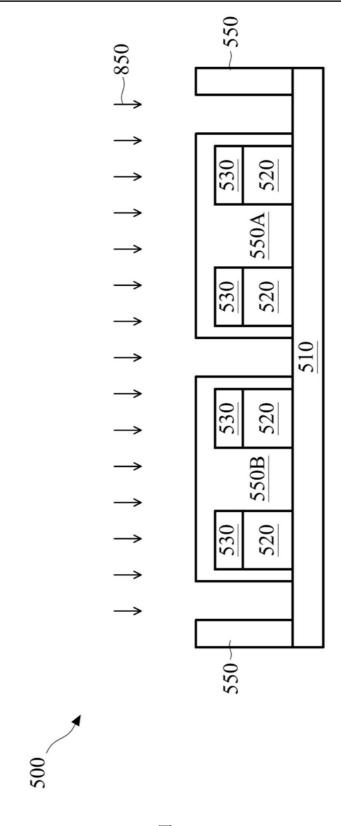

[0013] 图5A至图20A是根据本发明的实施例的各个制造阶段处的SRAM器件的示意性局部 顶视图。

[0014] 图5B至图20B是根据本发明的实施例的各个制造阶段处的SRAM器件的示意性局部截面侧视图。

[0015] 图21示出根据本发明的实施例的包括多个光刻掩模的光刻系统。

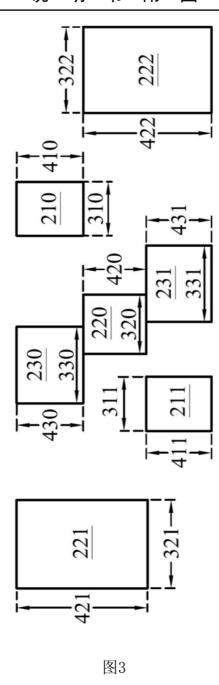

[0016] 图22是根据本发明的实施例示出的方法的流程图。

[0017] 图23是根据本发明的实施例示出的方法的流程图。

#### 具体实施方式

[0018] 以下公开内容提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件以直接接触的方式形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可在各个实例中重复参考标号和/或字符。该重复是为了简单和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

[0019] 而且,为了便于描述,在此可以使用诸如"在…下方"、"在…下面"、"下部"、"在… 之上"、"上部"等空间相对术语以描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。装置可以以其他方式定向(旋转90度或在其他方位上),并且在此使用的空间相对描述符可以同样地作出相应的解释。

[0020] 本发明涉及,但不以其他方式限制于,鳍式场效应晶体管(FinFET) 器件。例如,FinFET器件可以是包括P型金属氧化物半导体(PMOS)FinFET 器件和N型金属氧化物半导体(NMOS)FinFET器件的互补金属氧化物半导体(CMOS)器件。以下公开内容将继续结合一个或多个FinFET实例以示出本发明的各个实施例。然而,应当理解,除了权利要求中特别声明,本申请不应限制于特定类型的器件。

[0021] FinFET器件的使用在半导体产业中越来越受欢迎。参考图1,示出了示例性FinFET器件50的立体图。FinFET器件50是在衬底(诸如块状衬底)上方构建的非平面多栅极晶体管。薄的含硅"鳍式"结构(以下称为"鳍")形成FinFET器件50的主体。鳍在图1所示的X方向上延伸。鳍具有在与X方向正交的Y方向上测量的鳍宽度W<sub>fin</sub>。FinFET器件50的栅极60包裹在该鳍的周围,例如在鳍的顶面和相对的侧壁表面周围。因此,栅极60的部分在与X方向和Y方向两者正交的Z方向上位于鳍上方。

[0022]  $L_{\rm G}$ 表示在X方向上测量的栅极60的长度(或宽度,这取决于立体图)。栅极60可以包括栅电极组件60A和栅极介电组件60B。栅极介电组件60B 具有在Y方向上测量的厚度 $t_{\rm ox}$ 。栅极60的部分位于诸如浅沟槽隔离(STI)的介电隔离结构上方。在鳍的位于栅极60的相对两侧上的延伸件中形成 FinFET器件50的源极70和漏极80。鳍的由栅极60包裹在周围的部分用作FinFET器件50的沟道。通过鳍的尺寸确定FinFET器件50的有效沟道长度。

[0023] FinFET器件提供了超过传统的金属氧化物半导体场效应晶体管 (MOSFET)器件 (还称为平面晶体管器件)的几个优势。这些优势可包括较好的芯片区域效率、改进的载流子迁移率和与平面器件的制造工艺兼容的制造工艺。因此,期望将FinFET器件用作IC芯片的部分或整个IC芯片来设计集成电路 (IC) 芯片。这样的一个实例是利用FinFET器件制造SRAM单元。

[0024] 然而,由FinFET器件制造的传统的SRAM单元可能仍然存在缺陷。例如,现有的SRAM制造工艺流程可能涉及光刻图案化工艺以"分解"(break up)细长的接触线,从而形成用于SRAM单元的不同组件的各自的接触件。随着半导体特征尺寸的不断缩小,控制这些图案化工艺的工艺窗口变得更加困难。因此,可能会增加在SRAM单元接触件之间桥接的风险。此外,将接触件"置放"在其预定的鳍上可能更加困难。这些问题可能会劣化SRAM的性能,甚至会导致器件故障。本发明通过使用额外的掩模限定SRAM接触件来克服上面讨论的这些问题。还可以修改用于限定 SRAM接触件的掩模,以进一步提高SRAM接触件限定的准确度并降低接触件桥接的风险,如下面更详细讨论的。

[0025] 图2示出用于单端口SRAM单元(例如,1位SRAM单元)90的电路示意图。单端口SRAM单元90包括上拉晶体管PU1、PU2;下拉晶体管 PD1、PD2;和传输门晶体管PG1、PG2。如电路图所示,晶体管PU1和 PU2是诸如上述p型FinFET的p型晶体管,并且晶体管PG1、PG2、PD1 和PD2是上述n型FinFET。

[0026] 上拉晶体管PU1和下拉晶体管PD1的漏极连接在一起,并且上拉晶体管PU2和下拉晶体管PD2的漏极连接在一起。晶体管PU1和PD1与晶体管PU2和PD2交叉连接以形成第一数据锁存器。晶体管PU2和PD2的栅极连接在一起并且连接至晶体管PU1和PD1的漏极以形成第一存储节点 SN1,并且晶体管PU1和PD1的栅极连接在一起并且连接至晶体管PU2和 PD2的漏极以形成互补第一存储节点SNB1。上拉晶体管PU1和PU2的源极连接至电源电压Vcc (也称为Vdd),并且下拉晶体管PD1和PD2的源极连接至电压Vss (在一些实施例中,电压Vss可以是

电接地端)。

[0027] 第一数据锁存器的第一存储节点SN1通过传输门晶体管PG1连接至位线BL,并且互补第一存储节点SNB1通过传输门晶体管PG2连接至互补位线BLB。第一存储节点N1和互补第一存储节点SNB1是通常处于相对的逻辑等级(逻辑高或逻辑低)的互补节点。传输门晶体管PG1和PG2的栅极连接至字线WL。

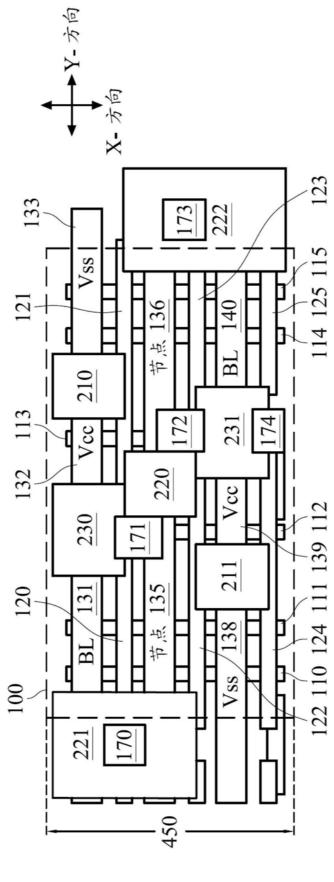

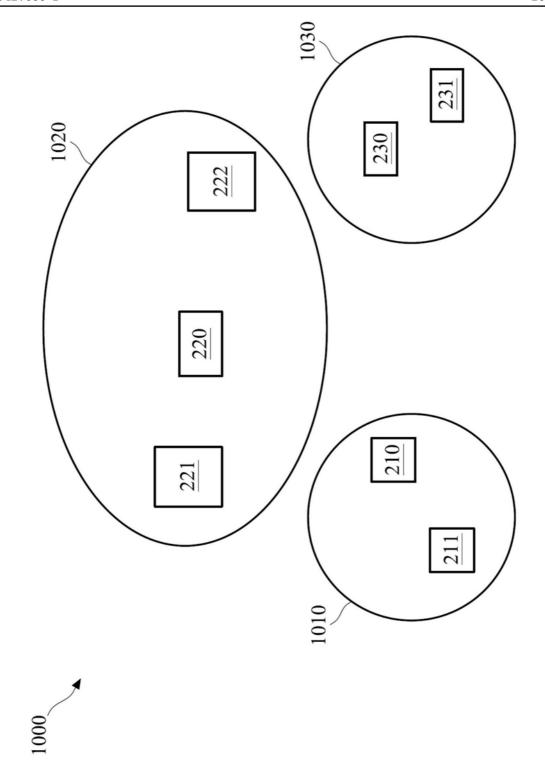

[0028] 现在参考图3至图4,图3示出用于限定SRAM单元的接触线的多个掩模图案,以及图 4示出根据本发明的实施例的图3的掩模图案叠加在其上的SRAM单元的局部顶视图。应当理解,图3的掩模图案属于不同的光刻掩模(下面更详细地讨论),但是为了清楚,在此叠加在一起。

[0029] 如图4所示,SRAM单元包括诸如1位SRAM单元100(在此作为实例示出)的多个单元,单元的电路示意图在图2中示出为SRAM单元90的电路示意图。在图4的顶视图中在具有虚线边界线的框内示出SRAM单元100的元件。

[0030] SRAM单元100包括多条鳍线110至115(还称为有源区或0D)。鳍线110至115均在X方向(与图1所示的X方向相同)上延伸,并且它们分别表示诸如图1所示的鳍结构的鳍结构。鳍线110至115可以包括诸如硅或硅锗的半导体材料。一些鳍线用作下拉晶体管的源极/漏极或沟道区,并且其他一些鳍线用作上拉晶体管的源极/漏极或沟道区。

[0031] SRAM单元100还包括均在Y方向(与图1所示的Y方向相同)上延伸的多个细长的栅极结构(还称为栅极线)120至125。栅极结构120至 125以上面参考图1所讨论的方式包裹在一条或多条鳍线110至115周围。栅极结构120至125以及鳍线110至115共同地形成至少六个晶体管器件,例如上文参考图2讨论的SRAM单元的PD1、PD2、PG1、PG2、PU1和 PU2晶体管器件。

[0032] 在图4的顶视图中还示出了多个导电接触件131至140(也称为接触线,因为它们每个都类似于线是细长的)。在SRAM单元100内(或至少部分地在SRAM单元100内)设置有位线(BL)接触件131、Vcc(还称为Vdd)接触件132、Vss(还称为接地)接触件133、节点接触件135、节点接触件136、Vss接触件138、Vcc接触件139和BL接触件140。还形成接触件170至175。接触件170至175是通孔-栅极接触件,并且均将相应的栅极结构与导电通孔连接在一起。这里没有详细讨论接触件170至175,因为它们不涉及本发明的中心方面。

[0033] 根据本发明的各个方面,在光刻和蚀刻工艺期间,通过接触线阻挡组件"分解"较长的接触线沟槽(例如,稍后将用金属填充以形成接触件的沟槽)而形成接触件131至140。

[0034] 例如,通过将本来是单个接触线分解为三个不同的部分来形成BL接触件131、Vcc接触件132和Vss接触件133。更详细地,掩模图案210和230限定了位于单个接触线的路径上方的"接触线阻挡组件"。这些接触线阻挡组件在稍后的蚀刻工艺期间用作蚀刻掩模,实施蚀刻工艺以形成是接触线的沟槽,其中,接触件131至133稍后将在沟槽中形成。由于由掩模图案210和230限定的接触线阻挡组件的存在,本来已经是长而连续的沟槽被分解成三个不同且分离的沟槽区段。然后用导电材料(例如,诸如钨、铝、铜或它们的组合的金属)填充这三个不同的沟槽区段以形成BL接触件131、Vcc接触件132和Vss接触件133。以这种方式,可以说掩模图案230和210将单个连续的接触线"分解"成三个不同且分离的接触件 131至133。以类似的方式,可以说通过使用掩模图案220来将单个连续的接触线"分解"成两个不同的区段来形成节点接触件135和136,并且通过使用掩模图案211和231来将单个连续的接

触线分解成三个不同的区段来形成Vss接触件138、Vcc接触件139和BL接触件140,。

[0035] 还应当理解,掩模图案221被配置为将接触线分解成形成BL接触件 131和相邻 SRAM单元(位于SRAM单元100的"左侧",但是为了简明,在此未示出)的VSS接触件的区段,以及将接触线分解成形成节点接触件 135和相邻SRAM单元的节点接触件的区段。类似地,掩模图案222被配置为将接触线分解成形成BL接触件140和相邻SRAM单元(位于SRAM 单元100的"右侧",但是为了简明,在此未示出)的VSS接触件的区段,以及将接触线分解成形成节点接触件136和相邻SRAM单元的节点接触件的区段。

[0036] 为了避免或减少SRAM接触件桥接风险,本发明应用了在至少三个不同的掩模上的掩模图案210至211、220至222以及230至231。根据本发明的一个实施例,在一个掩模上实施掩模图案210至211,在另一掩模上实施掩模图案220至222,并且在又一掩模上实施掩模图案230至231。当然,应当理解,将图案210至211、220至222和230至231布置到三个不同的掩模中仅仅是一个实例,并不旨在限制本发明,并且在可选实施例中可以将这些图案不同地布置到三个掩模上。此外,应当理解,在其他可选实施例中,可以使用多于三个的掩模(例如,四个掩模)来实施掩模图案 210至211、220至222和230至231。

[0037] 将掩模图案210至211、220至222以及230至231分布在至少三个掩模上为每个单独的掩模图案在其尺寸和形状方面提供了较大的调整自由,这可以用于减少SRAM接触桥接的风险并且改进接触件至鳍的置放。更详细地,随着半导体器件尺寸的不断缩小,控制掩模图案210至211、220至 222和230至231相对于接触线的精确定位和对准越来越困难。如上所述,掩模图案210至211、220至222以及230至231被用于"分解"SRAM接触件,并且这些掩模图案从其期望位置的偏移可能导致SRAM接触件的问题。

[0038] 例如,掩模图案210旨在将接触件"分解"成Vcc接触件132和Vss 接触件133。然而,如果掩模图案210的尺寸太小,则可能无法将Vcc接触件132和Vss接触件133充分分离,因为即使Vcc接触件132和Vss接触件133之间的小的连续性也可能导致这些两个接触件之间的桥接。如果掩模图案210的位置偏移,例如在图3至图4中在X方向上"向上"或"向下"偏移,则也可能发生Vcc接触件132和Vss接触件133之间的桥接。另一方面,如果掩模图案210的尺寸太大,则可能"吞没"(swallow up) Vcc接触件132的部分(或全部)。换言之,足够大的掩模图案210可能导致Vcc接触件132形成为太小,或者根本不会形成,因为大的掩模图案 210将"阻挡"Vcc接触件132的形成。在图3至图4中如果掩模图案210 在Y方向上向"左"移动得太多,也会发生这种情况。SRAM接触件之间的意外桥接可能会导致SRAM器件故障或性能下降。[0039] 掩模图案210至211、220至222和230至231的尺寸变化和/或位置偏移还可能导致

"接触件至鳍的置放"问题。例如,如果掩模图案220太小,或者在图3至图4中如果其在X方向上"向上"或"向下"移动,则可能导致节点接触件135与节点接触件136桥接。另一方面,如果掩模图案220太大,则可能导致节点接触件135没有"放置"在鳍线112上,或者导致节点接触件136没有"放置"在鳍线113上。在图3至图4中如果掩模图案220在Y方向上向"左"或"右"移动,则节点接触件135至136 也可能错过其期望的置放。如果接触件错过了"放置"在其期望的鳍上,则这意味着没有形成本应为给定的晶体管形成的电连接,并且这也可能导致SRAM器件故障或性能下降。

[0040] 如果将太多的掩模图案置于同一掩模上,则上面讨论的接触件桥接和/或鳍置放问题更加复杂。由于光刻中的限制(特别是随着器件尺寸变小),调整任何给定的掩模图案

的尺寸和/或位置都可能会导致该掩模上的其他掩模图案的不期望的变化(或桥接),这可能不利地影响SRAM单元的其他部分中的接触件桥接和/或鳍置放问题。作为实例,如果使用同一光刻掩模形成掩模图案210和231,然后在图3至图4中在X方向上放大或移动掩模图案210则可以导致掩模图案210和231相互桥接。掩模图案210和231的桥接可以"切断"节点接触件136的"左侧"部分,这可能导致节点接触件136错过其"置放"在鳍线113上。

[0041] 此外,由于光刻约束,彼此太靠近的掩模图案不应布置在同一掩模上。例如,如果掩模图案210和230布置在同一掩模上,则将它们分开的距离可能太小而不能被光刻来分辨,并且因此可能不能明确地限定掩模图案210 和230的边界。

[0042] 对光刻掩模设计的另一关注点是图案一致性。更详细地,如果这些图案在几何形状 (geographical shape) 和/或尺寸方面彼此相对一致,则光刻更容易分辨多个图案。因此,在不同图案中的一个图案远远大于其他图案的情况下,将这些不同图案实现在同一光刻掩模上是不期望的。

[0043] 本发明通过将掩模图案210至211、220至222和230至231分至三个掩模(或在可选实施例中的可以更多)来克服上面讨论的问题。这样做的一个益处是,调整任何一个掩模图案使得其不太可能影响其他图案。例如,可以在X方向上拉伸或放大掩模图案210。这有助于确保掩模图案210可以用于图案化接触线阻挡组件以"分解"Vcc接触件132和Vss接触件133的目的。换言之,由于掩模图案210在X方向上较大,所以它提供了较大的工艺裕度以容忍由光刻缺陷引起的尺寸变化或位置偏移。

[0044] 掩模图案210的放大或拉伸也不会增加与掩模图案231桥接的风险,因为如上所述,在不同的掩模上实现掩模图案210和231。这样,可以在不同的工艺步骤中使用掩模图案210和231,并且因此掩模图案210的拉伸将不会导致与掩模图案231的无意桥接。类似地,因为在不同的掩模上实现掩模图案211,所以可以在X方向上拉伸或放大掩模图案230,而不用担心导致与掩模图案211的无意桥接。

[0045] 掩模图案210(或230)的拉伸或放大是调整掩模图案的一个实例。应当理解,在其他实施例中,可以灵活地调整其他掩模图案以解决SRAM接触件桥接或接触件至鳍的置放问题,而不偏离本发明的精神或范围。

[0046] 如图3所示,掩模图案210至211、220至222和230至231的尺寸或大小被配置为便于分解SRAM接触线。例如,掩模图案210至211、220至222和230至231分别具有在图3的Y方向上测量的尺寸310至311、320至322以及330至331。掩模图案210至211、220至222和230至231分别具有在图3的X方向上测量的尺寸410至411、420至422和430至431。在一些实施例中,尺寸310至311配置为彼此类似,尺寸410至411配置为彼此类似,尺寸330至331配置为彼此类似,尺寸421至422配置为彼此类似。在一些实施例中,为了便于分解SRAM接触线,尺寸310至311配置为小于尺寸330至331,并且尺寸431至311配置为小于尺寸321至322。

[0047] 如上所述,可以拉伸或放大本文中的一些掩模图案以扩大工艺裕度。例如,在一些实施例中,虽然掩模图案210和230可以预先具有类似的尺寸410和430,但是掩模图案210现在可使其尺寸410在X方向上拉伸,从而使得尺寸410现在大于尺寸430。在一些实施例中,这同样可以适用于掩模图案211(拉伸的图案)和掩模图案231。

[0048] 还可根据SRAM单元100的大小或尺寸来配置掩模图案210至211、220至222和230

至231的尺寸。例如,如图4所示,SRAM单元100具有在X方向上测量的间距450。在一些实施例中,尺寸421至422均配置为大于间距450的1/2。

[0049] 掩模图案的尺寸也配置为确保布置在同一光刻掩模上的掩模图案之间的一致性。如上所述,在所示实施例中,掩模图案210至211布置在同一光刻掩模上,并且因此掩模图案210至211可以具有类似的尺寸310至311 以及类似的尺寸410至411。在所示实施例中,掩模图案220至222布置在另一光刻掩模上,并且因此掩模图案220至222可以具有类似的尺寸320 至322以及类似的尺寸420至422。在所示实施例中,掩模图案230至231 布置在同一光刻掩模上,并且因此,掩模图案230至231可以具有类似的尺寸330至331以及类似的尺寸430至431。在一些实施例中,如果上面讨论的这些各种尺寸在彼此的+50%或-50%之内变化,则可以认为它们是类似的。这样,位于同一掩模上的掩模图案的类似尺寸确保每个掩模提供良好的图案一致性。此外,掩模图案210至211、220至222和230至231 均实现为矩形(即使矩形具有不同的X尺寸与Y尺寸比率)。掩模图案的形状类似性(特别是在同一光刻掩模内)进一步改进了本发明的光刻掩模的图案一致性。

[0050] 还应当理解,本发明允许生成新的掩模布局方案。例如,可以接收传统的掩模布局方案。根据传统的掩模布局方案,用于限定接触线阻挡组件的所有掩模布局图案仅布置在一个(或两个)光刻掩模中。如上所述,这是不期望的,因为这会导致接触件桥接问题,接触件至鳍的置放困难等。根据本发明的方法,在接收传统的掩模布局方案之后,可以生成新的掩模布局方案,从而使得现在将传统的布局方案的掩模图案分至三个或多个光刻掩模上。在一些实施例中,在与接触线延伸方向垂直的方向上拉伸或放大至少一个掩模图案(例如,掩模图案210)。这减少了潜在的接触线桥接风险。

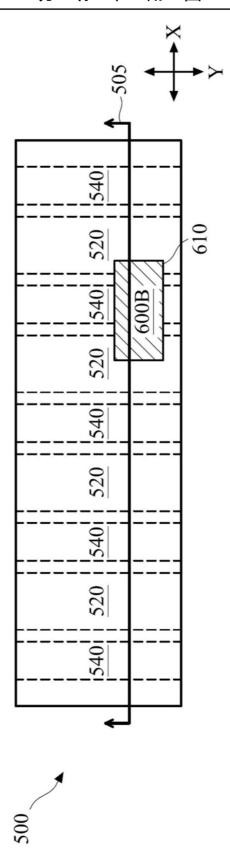

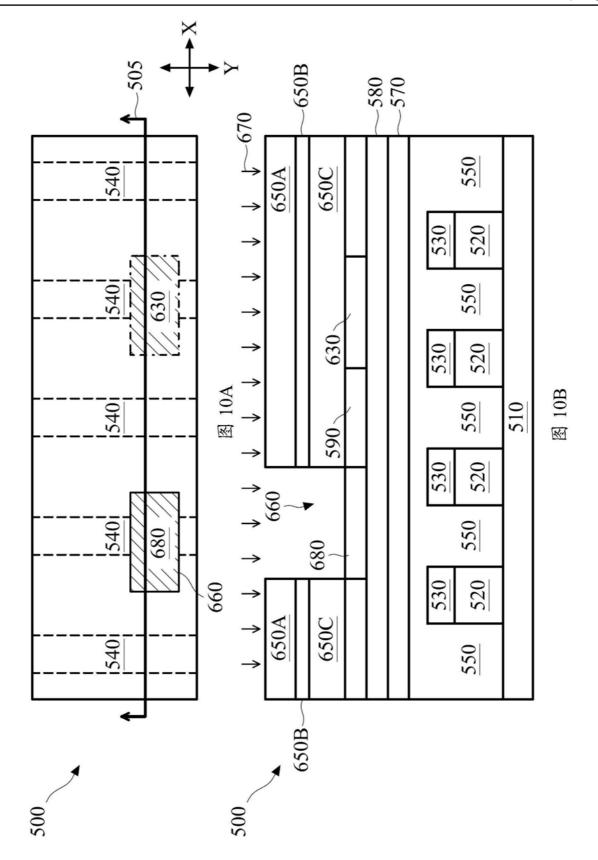

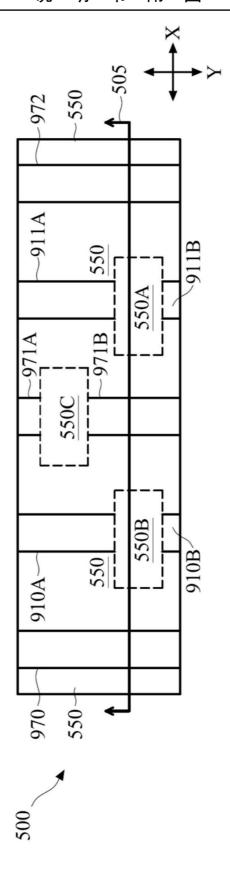

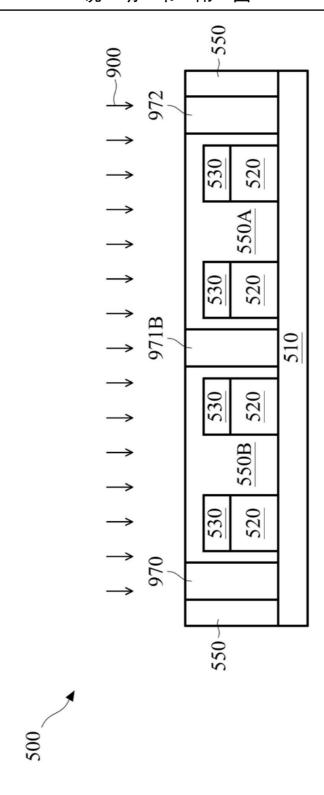

[0051] 现在将讨论使用这些掩模图案210至211、220至222和230至231来形成/限定接触件阻挡组件的制造工艺流程。更详细地,图5A至图20A是半导体器件500在不同制造阶段的示意性局部顶视图,以及图5B至图20B 是根据本发明的实施例的半导体器件500在不同制造阶段的示意性局部截面侧视图。应当理解,图5B至图20B的截面侧视图是通过X切割获得的,即根据图4中的X方向上的切割线获得的。这个切割线的实例在图5A至图20A中示出为切割线505。半导体器件500可以是上面参考图2和图4 讨论的SRAM单元100的实施例。

[0052] 现在参考图5A至图5B,半导体器件500包括形成在衬底上方的半导体层510。在实施例中,半导体层510包括诸如硅或硅锗的晶体硅材料。可以实施注入工艺以将多种掺杂剂离子注入到半导体层510。在一些实施例中,掺杂剂离子可以包括例如砷(As)或磷(P)的n型材料,或者在一些其他实施例中,它们可以包括例如硼(B)的p型材料,这取决于需要n型FET (NFET或NMOS)还是p型FET (PFET或PMOS)。例如,N阱可以形成为用于PFET,并且P阱可以形成为用于NFET。

[0053] 通过一个或多个光刻工艺图案化半导体层510来形成多个鳍结构。鳍结构可以用作半导体器件500的FinFET晶体管的源极、漏极或沟道区。可以以上面参考图4所讨论的方式来布置鳍结构,例如均在X方向上延伸的鳍线110至115。在图5B的截面图中,鳍结构不是直接可见的,因为X方向切割线取自SRAM单元的位于鳍结构外部的部分中。

[0054] 可以形成多个栅极堆叠件520。每个栅极堆叠件520均对应于上面参考图4讨论的栅极线120至125中的不同的一个。栅极堆叠件520可以通过使用硬掩模530的一个或多个图案化工艺形成,并且可以涉及栅极替换工艺,其中,高k金属栅极替换伪栅极。例如,栅极堆

叠件520均可以包括高k栅极电介质及金属栅电极。高k栅极电介质可以包括介电常数大于约为4的SiO<sub>2</sub>的介电常数的介电材料。在实施例中,高k栅极电介质包括具有在约18至约40的范围内的介电常数的氧化铪  $(HfO_2)$ 。在可选实施例中,高k栅极电介质可以包括ZrO<sub>2</sub>、 $Y_2O_3$ 、 $La_2O_5$ 、 $Gd_2O_5$ 、 $TiO_2$ 、 $Ta_2O_5$ 、HfErO、HfLaO、HfYO、HfGdO、HfAIO、HfZrO、HfTiO、HfTaO或 SrTiO。金属栅电极可以包括功函金属组件和填充金属组件。功函金属组件配置为调节其对应的FinFET的功函以实现期望的阈值电压Vt。在各个实施例中,功函金属组件可以包括 TiAI、TiAIN、TaCN、TiN、WN或W或它们的组合。填充金属组件配置为用作栅电极的主要导电部分。在各个实施例中,填充金属组件可以包括铝 (AI)、(AI) 、(AI) (AI) 、(AI) (AI) (AI)

[0055] 虽然栅极堆叠件520在该制造阶段在顶视图中不是直接可见的,但是在图5A的顶视图中示出栅极堆叠件520的轮廓(以虚线示出),以便于理解本发明。注意,与图4的顶视图相比,图5A的顶视图"旋转"了90度。换言之,X方向和Y方向分别在图4和图5A之间旋转90度。尽管如此,应当理解,在图4和图5A中,栅极堆叠件520仍在Y方向上延伸。

[0056] 在图5A的顶视图中还示出了接触线540的轮廓,本文用虚线示出接触线540。每个接触线540均对应于不同的接触线,其中,由这些接触线形成BL、Vcc、Vss和节点接触件(在图4中示出)。如图5A所示,接触线 540均在Y方向上延伸,并且不同的接触线540设置在每对栅极线520之间。应当理解,在图5A至图5B的制造阶段,还没有限定接触线540(即,它们还不存在),因此接触线540的轮廓的图示仅仅是为了便于理解本发明。

[0057] 如图5B所示,层间电介质(ILD)550围绕栅极堆叠件520或栅极堆叠件520嵌入到层间电介质(ILD)550中。可以通过沉积介电材料并且实施诸如化学机械抛光(CMP)的抛光工艺以平坦化ILD550的上表面来形成ILD550。ILD550为栅极堆叠件520提供电绝缘,并且可以包括诸如氧化硅的电绝缘材料。应当理解,可以在栅极堆叠件520之前形成ILD550。例如,可以在形成伪栅极结构(例如,包括多晶硅栅电极)之后形成ILD550。伪栅极结构的去除可以在ILD中创建开口或凹槽,然后可以用高k金属栅极结构(例如栅极堆叠件520)来填充这些开口或凹槽。

[0058] 在ILD 550上方形成层570。在一些实施例中,层570包括例如氮化钛的介电材料。然后在层570上方形成层580。在一些实施例中,层580包括与层570的介电材料不同的介电材料。例如,层580可以包括诸如氧化硅的氧化物材料。层570和580可以在后续的图案化工艺中共同用作硬掩模层以限定接触线沟槽。然后在层580上方形成层590。在一些实施例中,层590包括硅。在本文讨论的实施例中,层570、580和590可以用于图案化,例如以图案化与上面参考图4讨论的接触线相对应的沟槽。

[0059] 在层590上方形成图案化的光刻胶层600。在所示实施例中,光刻胶层600是三层光刻胶并且包括顶层600A、中间层600B和底层600C。以使得在顶层600A中形成开口610的方式来图案化光刻胶层600。通过包括上面参考图4讨论的掩模图案210至211、220至222和230至231中的一个的光刻掩模形成开口610。例如,可以通过掩模图案210限定开口610。图 5A中示出开口610的顶视图轮廓。

[0060] 如图5B的截面图所示,开口610的位置配置为使得其与接触线540(接触线540将在稍后形成)中的一个垂直对准。如图5A的顶视图所示,开口 610的尺寸也配置为导致在与其对准的接触线540中产生"断裂"(break)。更详细地,使用开口610实施的后续工艺导致将在ILD 550中形成阻挡组件。由于将在ILD 550中形成接触线沟槽,所以ILD 550中的阻挡部件

将防止形成连续的接触线。而且,由于由开口610限定接触线阻挡组件,接触线将形成为两个不同且分离的接触件(例如,Vcc接触件132和Vss接触件133)。基于下文中的详细讨论,这将变得更加明显。

[0061] 注意,如上所述,开口610也可以在X方向上"拉伸",以确保开口 610的位置移动或尺寸变化不会影响其"断开"接触线540,从而放宽工艺窗口和/或增加工艺裕度。在图5A的顶视图中,"拉伸"的开口610可以与附近的栅极堆叠件520重叠,但这不是问题,因为后续使用开口610的工艺将不会影响已经形成的栅极堆叠件520。

[0062] 现在参考图6A至图6B,开口610向下延伸到图案化的光刻胶600的层600B至600C中,并且去除光刻胶600的顶层600A。注意,在图6A的顶视图(以及后续的制造阶段的顶视图)中,仍然示出了将要形成的接触线540的轮廓以便于后续讨论,但是出于清楚和简单的原因未特别示出栅极堆叠件520的轮廓。在图6B中可以看出,开口610现在暴露层590的部分。

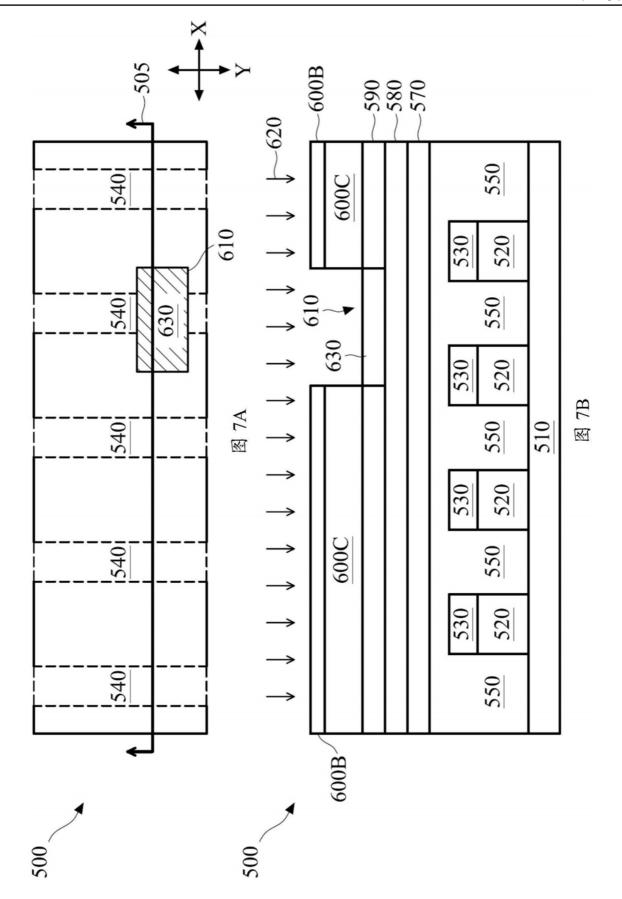

[0063] 现在参考图7A至图7B,通过开口610实施离子注入工艺620以将掺杂剂离子注入到层590中。在一些实施例中,注入的掺杂剂离子包括硼离子。作为离子注入工艺620的结果,通过层590的其中注入有掺杂剂离子的部分形成掺杂元件630。

[0064] 现在参考图8A至图8B所示,例如通过灰化或剥离工艺去除图案化的光刻胶层600。在层590上方形成另一图案化的光刻胶层650。同样,图案化的光刻胶层650可以是三层光刻胶层并且包括项层650A、中间层650B 和底层650C。以使得在项层650A中形成开口660的方式来图案化光刻胶层650。通过与上面参考图5B讨论的用于形成开口610的掩模不同的光刻掩模形成开口660。用于形成开口660的光刻掩模是不包括掩模图案210 的光刻掩模(其中掩模图案210对应于开口610)。在所示实施例中,通过包括掩模图案231的光刻掩模形成开口660。使用掩模图案231对开口660进行图案化。图8A中示出开口660的顶视图轮廓。

[0065] 如图8B的截面图所示,开口660的位置配置为使得其与接触线540 中的一个垂直对准。如图8A的顶视图所示,开口610的尺寸也配置为导致在与其对准的接触线540中产生"断裂"。更详细地,使用开口610实施的后续工艺导致在ILD 550中将形成阻挡组件,这将阻止在ILD中形成连续的接触线。而且,由于由开口660限定接触线阻挡组件,接触线将形成为两个不同且分离的接触件(例如,Vcc接触件139和BL接触件140)。基于下文中的详细讨论,这将变得更加明显。

[0066] 类似于开口610,可以在X方向上"拉伸"开口660,以确保开口660 的位置移动或尺寸变化不会影响其"断开"接触线540,从而放宽工艺窗口和/或增加工艺裕度。在顶视图中,"拉伸"的开口660可以与附近的栅极堆叠件520重叠,但这不是问题,因为使用开口660的后续工艺将不会影响已经形成的栅极堆叠件520。

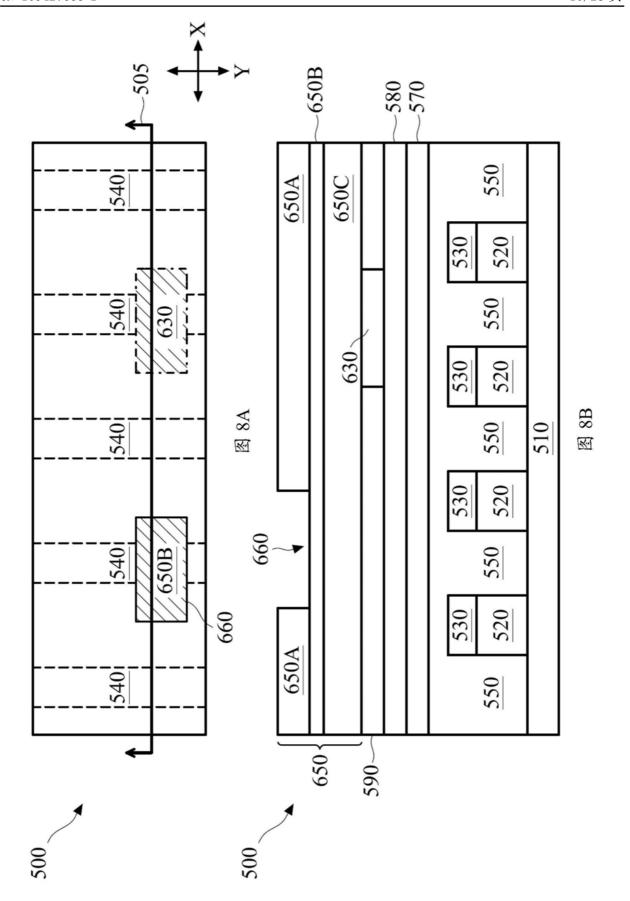

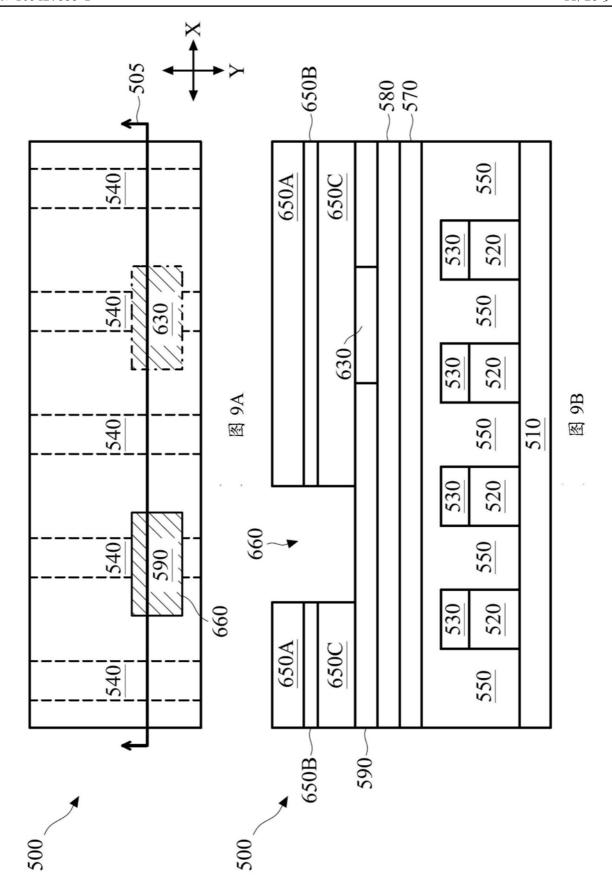

[0067] 现在参考图9A至图9B,开口660向下延伸到图案化的光刻胶650的层650B至650C中。在图9B中可以看出,现在开口660暴露层590的部分。

[0068] 现在参考图10A至图10B,通过开口660实施离子注入工艺670以将掺杂剂离子注入到层590中。在一些实施例中,注入的掺杂剂离子包括硼离子。作为离子注入工艺670的结果,通过层590的其中注入有掺杂剂离子的部分形成掺杂元件680。

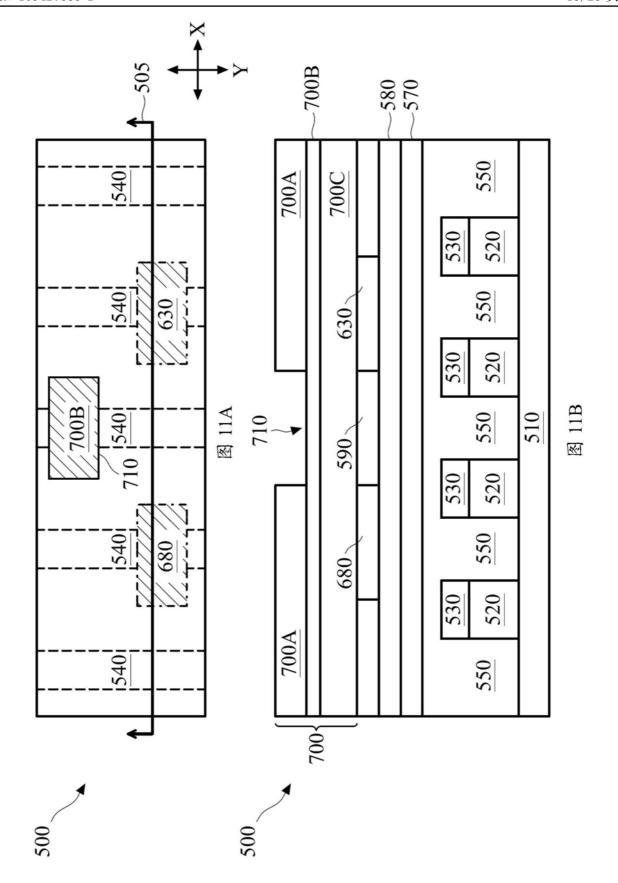

[0069] 现在参考图11A至图11B所示,例如通过灰化或剥离工艺去除图案化的光刻胶层650。在层590上方形成另一图案化的光刻胶层700。同样,图案化的光刻胶层700可以是三层

光刻胶层并且包括顶层700A、中间层700B 和底层700C。以使得在顶层700A中形成开口710的方式图案化光刻胶层 700。通过与用于形成开口610(图5B)的掩模和用于形成开口660(图8B)的掩模不同的光刻掩模形成开口710。用于形成开口710的光刻掩模是不包括掩模图案210(其中掩模图案210对应于开口610)并且不包括掩模图案231(其中掩模图案231对应于开口660)的光刻掩模。在所示实施例中,通过包括掩模图案220的光刻掩模形成开口710。使用掩模图案220对开口710进行图案化。图11A中示出开口710的顶视图轮廓。

[0070] 应当理解,开口710不与开口610和660对准,并且因此不与掺杂元件630和680对准。在图11A的顶视图中更清楚地示出了这种不对准,其中在Y方向上开口710与掺杂元件630和680之间存在位置偏移。同样,这种位置偏移(或不对准)与图3和图4一致,在掩模图案220(即,对应于开口710的掩模图案)与掩模图案210、231(即,对应于掺杂元件630和680的掩模图案)之间也存在相同的位置偏移(或不对准)。这样,如果仅在X方向上的单个切割线获取图11B的截面图,则开口710不应该与掺杂元件630和680同时示出。然而,为了便于理解本发明,图11B的截面图可以认为是两个不同的截面图的合成图(或者叠加图),其中,一个截面图是从与掺杂元件630和680相交的切割线(在X方向上)获取的,并且另一截面图从与开口710相交的切割线(在X方向上但是在不同的位置处)获取的。这同样适用于接下来的制造阶段的截面图图12A和图12B。

[0071] 如图11B的截面图所示,开口710的位置配置为使得其与接触线540中的一个垂直对准。如图11A的顶视图所示,开口710的尺寸也配置为导致在与其对准的接触线540中产生"断裂"。更详细地,使用开口710实施的后续工艺导致在ILD 550中将形成阻挡组件,这将阻止形成连续的接触线。而且,由于由开口710限定接触线阻挡组件,接触线将形成为两个不同且分离的接触件(例如,节点接触件135和节点接触件136)。基于下文中的详细讨论,这将变得更加明显。

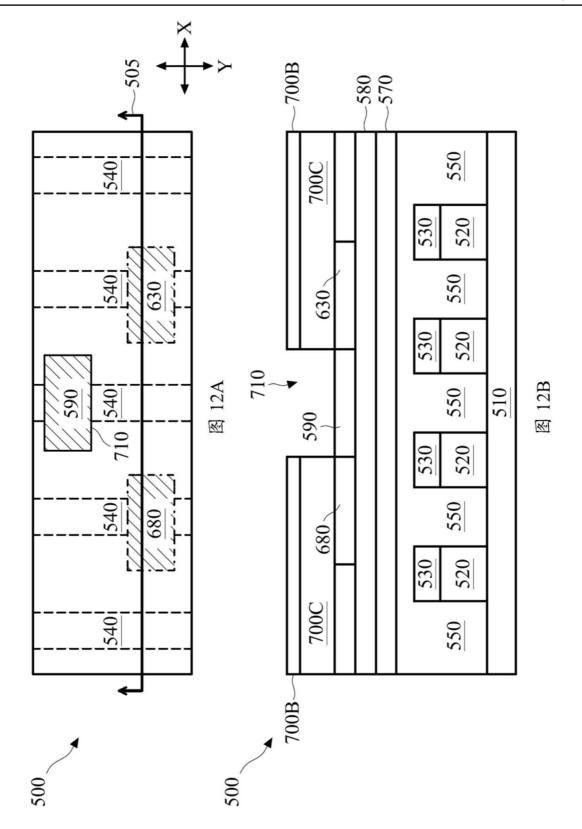

[0072] 类似于开口610,可以在X方向上"拉伸"开口710,以确保开口710 的位置偏移或尺寸变化不会影响其"断开"接触线540,从而放宽工艺窗口和/或增加工艺裕度。在顶视图中,"拉伸"的开口710可以与附近的栅极堆叠件520重叠,但这不是问题,因为使用开口710的后续工艺将不会影响已经形成的栅极堆叠件520。

[0073] 现在参考图12A至图12B,开口710向下延伸到图案化的光刻胶700 的层700B至700C中。在图12B中可以看出,开口710现在暴露层590的部分。

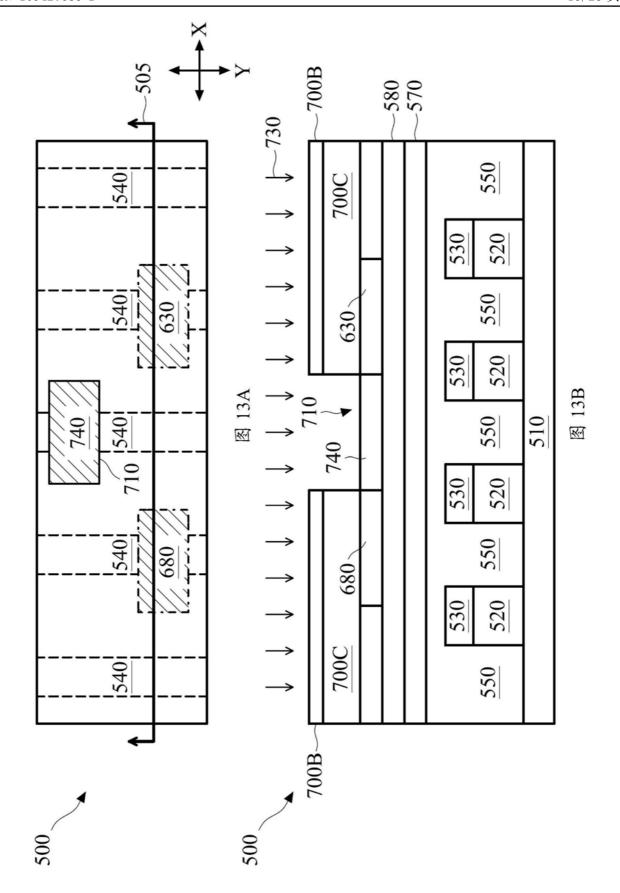

[0074] 现在参考图13A至图13B,通过开口710实施离子注入工艺730以将掺杂剂离子注入到层590中。在一些实施例中,注入的掺杂剂离子包括硼离子。作为离子注入工艺730的结果,通过层590的其中注入有掺杂剂离子的部分形成掺杂元件740。

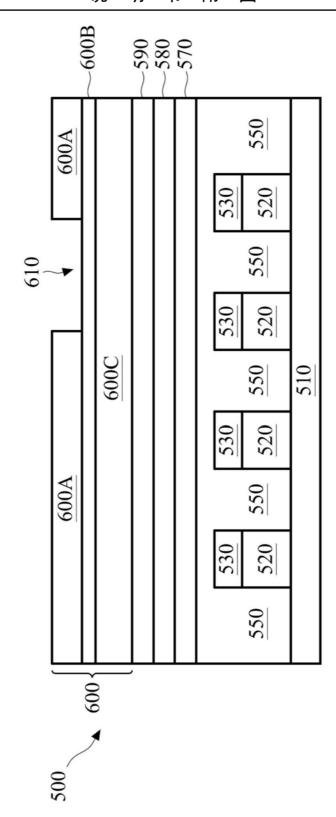

[0075] 现在参考图14A至图14B,例如通过灰化或剥离工艺去除图案化的光刻胶层700。结果,现在暴露掺杂元件630、680和740。掺杂元件630、680、740将用于图案化其下面的层570至580以形成接触线阻挡图案。然后这些接触线阻挡图案将用于在ILD 550中形成接触线阻挡组件以"阻挡"形成连续的接触线沟槽(即"分解"沟槽),如在下面更详细讨论的。

[0076] 现在参考图15A至图15B,在掺杂元件630、680和740上方形成图案化的光刻胶层750。同样,图案化的光刻胶层750可以是三层光刻胶层并且包括顶层750A、中间层750B和底层750C。以使得在顶层750A中形成诸如开口770、771和772的多个开口的方式来图案化光刻胶层750。开口770至772均限定了相应的接触线的位置,该接触线将在后续步骤中形成为

ILD 550中的沟槽。

[0077] 注意在所示实施例中,接触线的限定涉及双重图案化工艺。例如,如图15A至图15B 所示,由开口770至772限定接触线的子集,而将在稍后限定接触线的其余部分。双重图案化工艺可能有助于实现接触线之间较小的间距。应当理解,用于限定开口770至772的光刻掩模是与上面讨论的用于形成掺杂元件630、680、740的三个掩模不同的掩模。

[0078] 现在参考图16A至图16B,通过实施蚀刻工艺780,开口770至772 向下延伸到层570至580中。掺杂元件630、680和740在本文中还用作蚀刻掩模。注意,由于切割线505的位置,掺杂元件740在图16A中不应是直接可见的。尽管如此,掺杂元件740的轮廓在这里仍然以虚线示出,以帮助读者理解掺杂元件740的位置和方位,以及将在下面讨论它将如何影响图案化工艺。

[0079] 如图16A的顶视图所示,由于掺杂元件740(其与开口771的路径重叠)的存在,现在将开口771"分解"成两个区段771A和771B。换言之,掺杂元件740防止在蚀刻工艺780中层570至580中位于掺杂元件740下方的部分被蚀刻。结果,不是在层570至580中蚀刻连续的开口771,而是在层570至580中蚀刻开口的两个区段771A至771B。这样,可以说通过层570至580的位于掺杂元件740下面的部分"阻挡"或"中断"两个区段771A至771B。在所示实施例中,区段771A至771B将分别限定用于节点接触件135至136的沟槽。应当理解,参考图15A至图15B和图16A至图16B讨论的上述工艺对应于双重图案化工艺的第一部分。

[0080] 现在参考图17A至图17B,在掺杂元件630、680和740上方形成图案化的光刻胶层800。同样,图案化的光刻胶层800可以是三层光刻胶层并且包括顶层800A、中间层800B和底层800C。以使得在顶层800A中形成诸如开口810和811的多个开口的方式图案化光刻胶层800。开口810至811限定了未被图15A至图15B中的开口770至772限定的其余接触线的位置。应当理解,用于限定开口810至811的光刻掩模是与上面讨论的用于形成掺杂元件630、680、740的三个掩模不同的掩模。

[0081] 现在参考图18A至图18B,通过实施蚀刻工艺830,开口810至811 向下延伸到层570至580中。掺杂元件630、680和740在本文中还用作蚀刻掩模。如图18A的顶视图所示,由于掺杂元件630和680的存在(分别与开口810和811的路径重叠),现在将开口810"分解"成两个区段810A 和810B,并且现在将开口811"分解"成两个区段811A和811B。换言之,掺杂元件630和680防止在蚀刻工艺830中层570至580的位于掺杂元件630和680下方的部分被蚀刻。结果,不是在层570至580中蚀刻连续的开口810至811中,而是在层570至580中蚀刻开口的两个区段810A至810B和811A至811B。这样,可以说,层570至580中受掺杂元件630保护的部分将两个区段810A至810B"阻挡"或"中断",并且层570至580中受掺杂元件630保护的部分将两个区段811A至811B"阻挡"或"中断",

[0082] 在所示实施例中,区段810A至810B将分别限定用于Vcc接触件139 和位线接触件140(图4)的沟槽,并且区段811A至811B将分别限定用于Vcc接触件132和Vss接触件133的沟槽。应当理解,参考图17A至图 17B和图18A至图18B讨论的上述工艺对应于双重图案化工艺的第二部分。

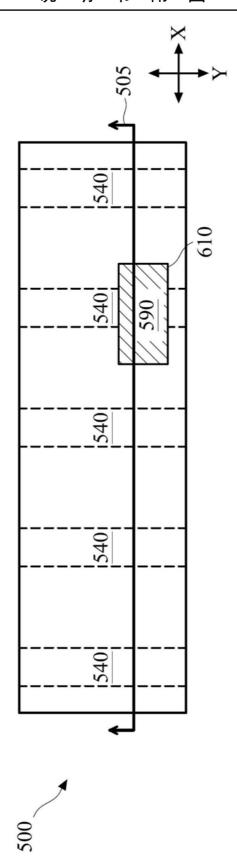

[0083] 应当理解,在这个制造阶段,已经在层570至580中限定用于所有 SRAM接触线的沟槽图案,即使由于X方向横切位于切割线505处它们在图19B的截面图中不是全部可见的。层570至580在此用作硬掩模层,并且形成在硬掩模层570至580中的开口将限定ILD 550中的

实际沟槽,以便在后续工艺中形成SRAM接触线。

[0084] 现在参考图19A至图19B,实施一个或多个蚀刻工艺850以将开口770、771A至771B、772、810A至810B和811A至811B蚀刻至ILD 550中。蚀刻至ILD 550中的开口770、771A至771B、772、810A至810B和811A 至811B形成接触线沟槽。硬掩模层570至580可以在蚀刻工艺850中用作蚀刻掩模,并且在将开口蚀刻至ILD 550中后被去除。在图19A的顶视图中可以看出,ILD层550A、550B、550C的部分分别对应于掺杂元件630、680、740。可以说,由包括分别限定掺杂元件630、680和740的掩模图案的三个光刻掩模来限定ILD层550A、550B、550C的这些部分。如图19A 所示,ILD层550A、550B、550C的部分用作接触线阻挡组件,因为它们有效地将接触线沟槽"分解"成沟槽区段810A至810B、771A至771B和 811A至811B。

[0085] 现在参考图20A至图20B,可以实施沉积工艺900以在接触线沟槽770、772、810A至810B、771A至771B和811A至811B中填充导电材料。在一些实施例中,导电材料可以包括诸如钨、铜、铝或它们的组合的金属。结果,形成了SRAM接触件910A至910B、911A至911B、970、971A、971B和972。在所示实施例中,接触件910A和910B对应于Vcc接触件 139和位线接触件140,接触件911A和911B对应于Vcc接触件132和Vss 接触件133,并且接触件971A和971B对应于节点接触件135和节点接触件136。同样,如图20A至图20B所示,ILD部分550A、550B和550C分别将接触线"分解"成接触件911A至911B、910A至910B和971A至971B。

[0086] 也可以说,ILD部分550A、550B和550C有效地限定了接触件911A 至911B、910A至910B和971A至971B的边界或边缘。例如,由于ILD 部分550A设置在接触件911A至911B之间,所以它限定了接触件911A 的边界和接触件911B的边界。由于ILD部分550B设置在接触件910A至910B之间,因此它限定了接触件910A的边界和接触件910B的边界。由于ILD部分550C设置在接触件971A至971B之间,因此它限定了接触件 971A的边界和接触件971B的边界。如上所述,通过将接触线阻挡掩模图案(以上参考图3至4所讨论的)分割成三个或多个光刻掩模,本发明降低了接触件911A和911B、910A和910B以及971A和971B之间桥接的风险,并且放宽了工艺裕度。此外,这些接触件911A至911B、910A至910B 和971A至971B的接触件至鳍的置放性能也得到了改进。

[0087] 图21示出光刻系统1000。根据本发明的各个方面,光刻系统1000包括至少三个光刻掩模1010、1020和1030。根据本发明的一个实施例,光刻掩模1010包括上面参考图3至图4讨论的掩模图案210和211,光刻掩模1020包括上面参考图3至图4讨论的掩模图案220和222,以及光刻掩模1030包括上面参考图3至图4讨论的掩模图案230和231。

[0088] 由于分别在三个单独的光刻掩模1010、1020、1030上实现了掩模图案 210至211、220至222以及230至231,所以在每个光刻掩模上调整掩模图案方面具有较大的自由度。如上所述,较大的调整自由度允许较灵活地调整(例如拉伸)掩模图案而没有与其他掩模图案桥接的风险或者没有以其他方式干扰其期望的图案化功能。此外,每个光刻掩模可以具有较好的掩模图案一致性,这也改进了光刻性能。掩模图案210至211、220至222 和230至231也均实施为矩形。掩模图案210至211、220至222和230至 231的矩形本质导致较好的图案化性能,因为图案的矩形几何形状不太可能引起破损,这与弯曲图案、曲折图案或其他不规则形状的图案相反。

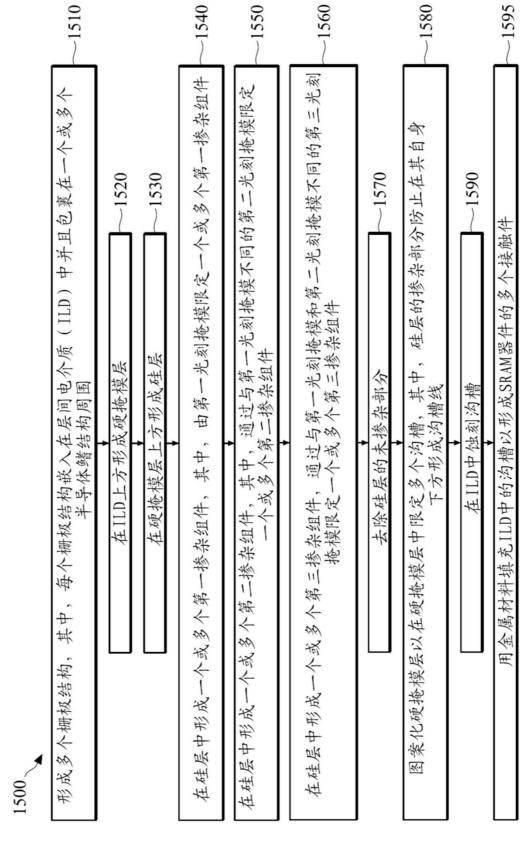

[0089] 图22是示出制造静态随机存取存储(SRAM)器件的方法1500的流程图。

[0090] 方法1500包括形成多个栅极结构的步骤1510。每个栅极结构嵌入在层间电介质

(ILD) 中并且包裹在一个或多个半导体鳍结构周围。

[0091] 方法1500包括在ILD上方形成硬掩模层的步骤1520。

[0092] 方法1500包括在硬掩模层上方形成硅层的步骤1530。

[0093] 方法1500包括在硅层中形成一个或多个第一掺杂组件的步骤1540。由第一光刻掩模限定一个或多个第一掺杂组件。

[0094] 方法1500包括在硅层中形成一个或多个第二掺杂组件的步骤1550。通过与第一光刻掩模不同的第二光刻掩模限定一个或多个第二掺杂组件。

[0095] 方法1500包括在硅层中形成一个或多个第三掺杂组件的步骤1560。通过与第一光刻掩模和第二光刻掩模不同的第三光刻掩模限定一个或多个第三掺杂组件。

[0096] 方法1500包括去除硅层的未掺杂部分的步骤1570。

[0097] 方法1500包括图案化硬掩模层以在硬掩模层中限定多个沟槽的步骤 1580。硅层的掺杂部分防止在其自身下方形成沟槽线。

[0098] 方法1500包括将在ILD中蚀刻沟槽步骤1590。

[0099] 方法1500包括用金属材料填充ILD中的沟槽以形成SRAM器件的多个接触件的步骤 1595。

[0100] 在一些实施例中,图案化包括限定至少第一不连续的沟槽、第二不连续的沟槽和第三不连续的沟槽,从而用于SRAM器件中的每个SRAM单元。在一些实施例中,第一不连续的沟槽包括沟槽区段,这些沟槽区段在蚀刻在ILD中并且用金属材料填充之后形成位线接触件、Vcc接触件和Vss接触件。在一些实施例中,第二不连续的沟槽包括沟槽区段,这些沟槽区段在蚀刻在ILD中并且用金属材料填充之后形成第一节点接触件和第二节点接触件。在一些实施例中,第三不连续的沟槽包括沟槽区段,这些沟槽区段在蚀刻在ILD中并且用金属材料填充之后,形成Vss接触件、Vcc接触件和位线接触件。

[0101] 在一些实施例中,通过分别位于第一光刻掩模、第二光刻掩模和第三光刻掩模上的矩形掩模图案来蚀刻一个或多个第一掺杂组件、一个或多个第二掺杂组件和一个或多个第三掺杂组件。

[0102] 在一些实施例中,在ILD中蚀刻沟槽包括双重图案化工艺。

[0103] 在一些实施例中,形成一个或多个第一掺杂组件包括使用第一光刻掩模以在第一 光刻胶层中形成一个或多个第一开口,并且通过一个或多个第一开口将离子注入到硅层 中。

[0104] 在一些实施例中,形成一个或多个第二掺杂组件包括使用第二光刻掩模以在第二 光刻胶层中形成一个或多个第二开口,并且通过一个或多个第二开口将离子注入到硅层 中。

[0105] 在一些实施例中,形成一个或多个第三掺杂组件包括使用第三光刻掩模以在第三光刻胶层中形成一个或多个第三开口,并且通过一个或多个第三开口将离子注入到硅层中。

[0106] 应当理解,可以在方法1500的步骤1510至1595之前、期间或之后实施额外的工艺。为了简单起见,本文不详细讨论其他额外的步骤。

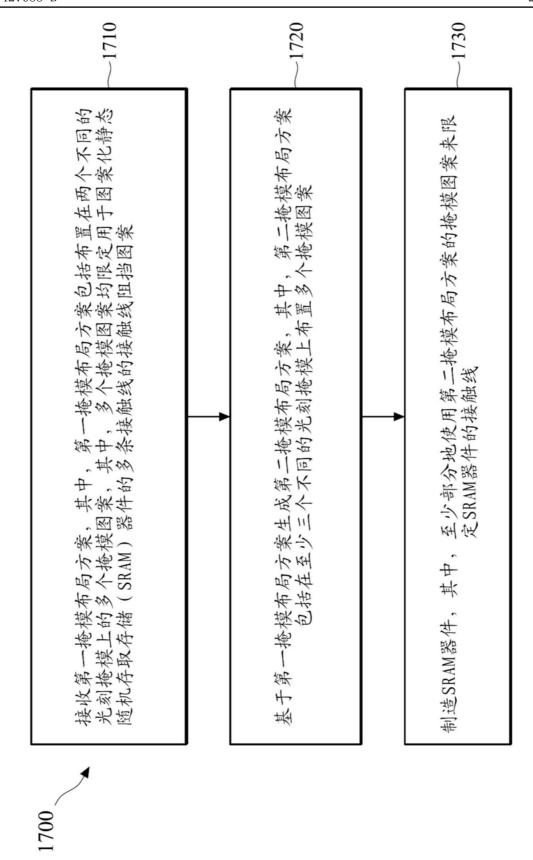

[0107] 图23是示出制造静态随机存取存储(SRAM)器件的方法1700的流程图。

[0108] 方法1700包括接收第一掩模布局方案的步骤1710。第一掩模布局方案包括布置在

两个不同的光刻掩模上多个掩模图案。多个掩模图案均限定了用于图案化静态随机存取存储(SRAM)器件的多条接触线的接触线阻挡图案。

[0109] 方法1700包括基于第一掩模布局方案生成第二掩模布局方案的步骤 1720。第二掩模布局方案包括布置在至少三个不同的光刻掩模上多个掩模图案。

[0110] 方法1700包括制造SRAM器件的步骤1730。至少部分地使用第二掩模布局方案的掩模图案来限定SRAM器件的接触线。在一些实施例中,制造SRAM器件包括:在介电层中蚀刻多个沟槽。通过介电层的由第二掩模布局图案的掩模图案限定的部分来中断至少一些沟槽。在一些实施例中,制造SRAM器件包括:填充沟槽以形成SRAM器件的接触线。

[0111] 在一些实施例中,接触线均在第一方向上延伸,并且生成步骤包括在与第一方向垂直的第二方向上放大至少一个掩模图案。

[0112] 应当理解,可以在方法1700的步骤1710至1730之前、期间或之后实施额外的工艺。 为了简单起见,本文不详细讨论其他额外的步骤。

[0113] 基于上述讨论,可以看出,本发明提供了优于传统的FinFET SRAM器件的制造的优势。然而,应当理解,其他实施例可以提供额外的优势,并不是所有优势都必须在此公开,并且没有特定优势是所有实施例都需要的。一个优势是本发明降低了接触件桥接的风险。通过将接触线阻挡掩模图案分布到三个或多个光刻掩模,现在在调整每个光刻掩模上的掩模图案方面具有更大的自由度。例如,可以在预定的方向上拉伸或放大一些图案,以便在后续的制造工艺中使分解SRAM接触件的可能性最大化。另一个优势是三个或多个光刻掩模均可以具有改进的图案一致性,因为掩模图案均可以成形为矩形和/或可以具有彼此类似的尺寸。改进的图案一致性又导致改进的光刻性能。其他优势包括与现有FinFET SRAM设计和制造的兼容性,因此本发明的实施是容易且经济实惠的。

本发明的一个方面涉及制造静态随机存取存储(SRAM)器件的方法。该方法包括: 在衬底上方形成多个栅极堆叠件,其中,介电结构围绕栅极堆叠件;在介电结构上方形成多 个接触线阻挡图案,其中,使用三个或多个光刻掩模形成接触线阻挡图案;在介电结构中形 成多个沟槽,其中,接触线阻挡图案用作介电结构的保护掩模,以防止在介电结构的位于接 触线阻挡图案下方的部分中形成沟槽:以及用导电材料填充沟槽以形成SRAM 器件的多条 接触线。在一些实施例中,形成接触线阻挡图案包括:使用包括第一掩模图案的第一光刻掩 模形成第一接触线阻挡图案;使用包括第二掩模图案的第二光刻掩模形成第二接触线阻挡 图案:以及使用包括第三掩模图案的第三光刻掩模形成第三接触线阻挡图案。在一些实施 例中,形成多个沟槽包括蚀刻用于第一Vcc接触件的第一沟槽和用于第一Vss接触件的第二 沟槽,并且其中,未蚀刻介电结构的设置在第一接触线阻挡图案下面且设置在第一沟槽和 第二沟槽之间的部分。在一些实施例中,形成多个沟槽包括蚀刻用于第二Vcc接触件的第三 沟槽和用于第一位线接触件的第四沟槽,并且其中,未蚀刻介电结构的设置在第二接触线 阻挡图案下面且设置在第三沟槽和第四沟槽之间的部分。在一些实施例中,形成多个沟槽 包括蚀刻用于第一节点接触件的第五沟槽和用于第二节点接触件的第六沟槽,并且其中, 未蚀刻介电结构的设置在第三接触线阻挡图案下面且设置在第五沟槽和第六沟槽之间的 部分。在一些实施例中,该方法还包括:在衬底上方形成多个鳍结构,并且其中,栅极堆叠件 均形成为包裹在鳍结构中的一个的周围。在一些实施例中,形成多个接触线阻挡图案包括: 将掺杂剂注入到硅层的形成在介电结构上方的多个部分中,从而形成硅层的多个掺杂部 分,其中,使用三个或多个光刻掩模中的一个来限定掺杂部分中的相应的一个。在一些实施例中,通过相应的矩形掩模图案限定每个接触线阻挡图案。

本发明的一个方面涉及制造静态随机存取存储(SRAM)器件的方法。该方法包括: 形成多个栅极结构,其中,每个栅极结构嵌入在层间电介质 (ILD) 中并且包裹在一个或多 个半导体鳍结构周围;在ILD上方形成硬掩模层;在硬掩模层上方形成硅层;在硅层中形成 一个或多个第一掺杂组件,其中,由第一光刻掩模限定一个或多个第一掺杂组件;在硅层中 形成一个或多个第二掺杂组件,其中,由与第一光刻掩模不同的第二光刻掩模限定一个或 多个第二掺杂组件:在硅层中形成一个或多个第三掺杂组件,其中,由与第一光刻掩模和第 二光刻掩模不同的第三光刻掩模限定一个或多个第三掺杂组件;去除硅层的未掺杂部分; 图案化硬掩模层以在硬掩模层中限定多个沟槽,其中,硅层的掺杂部分防止在其自身下方 形成沟槽线:在ILD中蚀刻沟槽:以及用金属材料填充ILD中的沟槽以形成SRAM器件的多个 接触件。在一些实施例中,图案化包括限定至少第一不连续的沟槽、第二不连续的沟槽和第 三不连续的沟槽,从而用于SRAM器件中的每个 SRAM单元。在一些实施例中,第一不连续的 沟槽包括沟槽区段,在ILD 中蚀刻沟槽并且用金属材料填充之后形成位线接触件、Vcc接触 件和Vss 接触件。在一些实施例中,第二不连续的沟槽包括沟槽区段,在ILD中蚀刻沟槽区 段并且用金属材料填充之后形成第一节点接触件和第二节点接触件;并且第三不连续的沟 槽包括沟槽区段,在ILD中蚀刻沟槽区段并且用金属材料填充之后形成Vss接触件、Vcc接触 件和位线接触件。

本发明的一个方面涉及一个系统。该系统包括至少三个彼此不同的光刻掩模,其 中,三个光刻掩模中的每个包括一个或多个相应的掩模图案,并且其中,每个掩模图案被配 置为限定相应的接触线阻挡图案,并且其中,接触线阻挡图案配置为图案化静态随机存取 存储(SRAM)器件的多条接触线。在一些实施例中,至少三个光刻掩模包括:第一光刻掩模, 包括第一图案和第二图案;第二光刻掩模,包括第三图案、第四图案和第五图案;以及第三 光刻掩模,包括第六图案和第七图案。在一些实施例中,第一图案配置为限定第一接触线阻 挡图案,其中,该第一接触线阻挡图案部分地限定用于第一Vcc接触件和第一Vss接触件的 边界;并且第二图案配置为限定第二接触线阻挡图案,其中,该第二接触线阻挡图案部分地 限定用于第二Vcc接触件和第一Vss接触件的边界。在一些实施例中,第三图案配置为限定 第三接触线阻挡图案,其中,第三接触线阻挡图案部分地限定用于第一节点接触件和第二 节点接触件的边界;第四图案配置为限定第四接触线阻挡图案,其中,第四接触线阻挡图案 部分地限定用于第一位线接触件和第一节点接触件的边界;并且第五图案配置为限定第五 接触线阻挡图案,其中,第五接触线阻挡图案部分地限定用于第二位线接触件和第二节点 接触件的边界。在一些实施例中,第六图案被配置为限定第六接触线阻挡图案,其中,第六 接触线阻挡图案部分地限定用于第一Vcc接触件和第一位线接触件的边界;并且第七图案 配置为限定第七接触线阻挡图案,其中,该第七接触线阻挡图案部分地限定用于第二Vcc接 触件和第二位线接触件的边界。在一些实施例中,接触线均在第一方向上延伸;第一图案具 有在与第一方向垂直的第二方向上测量的第一尺寸;第六图案具有在第二方向上测量的第 二尺寸;并且第一尺寸大于第二尺寸。在一些实施例中,接触线均在第一方向上延伸;SRAM 器件具有在与第一方向垂直的第二方向上测量的间距;并且在第二方向上测量的第四图案 的尺寸大于SRAM器件的间距的1/2。在一些实施例中,第一图案、第二图案、第三图案、第四

图案、第五图案、第六图案和第七图案中的每个成形为矩形。

[0117] 本发明的一个方面涉及一个系统。该系统包括:第一光刻掩模,包括一个或多个第一掩模图案,其中,一个或多个第一掩模图案配置为分解静态随机存取存储(SRAM)器件的至少第一接触线;第二光刻掩模,包括一个或多个第二掩模图案,其中,一个或多个第二掩模图案配置为分解 SRAM器件的至少第二接触线;以及第三光刻掩模,包括一个或多个第三掩模图案,其中,一个或多个第三掩模图案配置为分解SRAM器件的至少第三接触线。

[0118] 本发明的一个方面涉及一个系统。该系统包括:第一光刻掩模,包括一个或多个第一掩模图案,其中,一个或多个第一掩模图案配置为限定静态随机存取存储(SRAM)器件的接触线的第一子集的边界;第二光刻掩模,包括一个或多个第二掩模图案,其中,一个或多个第二掩模图案配置为限定SRAM器件的接触线的第二子集的边界;以及第三光刻掩模,包括一个或多个第三掩模图案,其中,一个或多个第三掩模图案配置为限定 SRAM器件的接触线的第三子集的边界。

[0119] 本发明的一个方面涉及一种方法。该方法包括:接收第一掩模布局方案,其中,第一掩模布局方案包括布置在两个不同的光刻掩模上的多个掩模图案,其中,多个掩模图案均限定接触线阻挡图案,从而用于图案化静态随机存取存储(SRAM)器件的多条接触线;以及基于第一掩模布局方案生成第二掩模布局方案,其中,第二掩模布局方案包括布置在至少三个不同的光刻掩模上的多个掩模图案。在一些实施例中,接触线均在第一方向上延伸;并且生成步骤包括在与第一方向垂直的第二方向上放大掩模图案中的至少一个。在一些实施例中,该方法还包括:制造SRAM器件,其中,至少部分地使用第二掩模布局方案中的掩模图案来限定SRAM器件的接触线。在一些实施例中,制造SRAM器件包括:在介电层中蚀刻多个沟槽,其中,由第二掩模布局方案的掩模图案限定的介电层的部分中断至少一些沟槽;并且填充沟槽以形成SRAM器件的接触线。

[0120] 上面概述了若干实施例的特征,使得本领域技术人员可以更好地理解本发明的各方面。本领域技术人员应该理解,他们可以容易地使用本发明作为基础来设计或修改用于实施与在此所介绍实施例相同的目的和/或实现相同优势的其他工艺和结构。本领域技术人员也应该意识到,这种等同构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,在此他们可以做出多种变化、替换以及改变。例如,通过实现位线导体和字线导体的不同厚度,可以实现导体的不同电阻。然而,还可以使用改变金属导体的电阻的其他技术。

图4

图5A

图5B

图6A

图6B

图14A

图14B

图19A

图19B

图20A

图20B

图21

图22

图23