### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6401588号 (P6401588)

(45) 発行日 平成30年10月10日(2018.10.10)

(24) 登録日 平成30年9月14日 (2018.9.14)

| (51) Int.Cl. |       |           | F I  |       |              |

|--------------|-------|-----------|------|-------|--------------|

| GO 1 N       | 27/00 | (2006.01) | GO1N | 27/00 | $\mathbf{Z}$ |

| GO 1 R       | 19/00 | (2006.01) | GO1R | 19/00 | C            |

| H03F         | 3/34  | (2006.01) | нозг | 3/34  | Z            |

|              |       |           | GO1R | 19/00 | E            |

請求項の数 3 (全 16 頁)

最終頁に続く

| (21) 出願番号<br>(22) 出願日 | 平成26年11月28日 (2014.11.28)      | (73) 特許権者         | 耸 390005175<br>株式会社アドバンテスト |  |

|-----------------------|-------------------------------|-------------------|----------------------------|--|

| (65) 公開番号             | 特開2016-102748 (P2016-102748A) | 東京都千代田区丸の内1丁目6番2号 |                            |  |

| (43) 公開日              | 平成28年6月2日(2016.6.2)           | (74) 代理人          | 100105924                  |  |

| 審査請求日                 | 平成29年3月31日 (2017.3.31)        |                   | 弁理士 森下 賢樹                  |  |

|                       |                               | (74) 代理人          | 100109047                  |  |

|                       |                               |                   | 弁理士 村田 雄祐                  |  |

|                       |                               | (74) 代理人          | 100109081                  |  |

|                       |                               |                   | 弁理士 三木 友由                  |  |

|                       |                               | (74) 代理人          | 100133215                  |  |

|                       |                               |                   | 弁理士 真家 大樹                  |  |

|                       |                               | (72) 発明者          | 倉持 泰秀                      |  |

|                       |                               |                   | 東京都練馬区旭町1丁目32番1号 株式        |  |

|                       |                               |                   | 会社アドバンテスト内                 |  |

|                       |                               |                   |                            |  |

|                       |                               | ll .              |                            |  |

(54) 【発明の名称】電流測定装置および塩基配列解析装置、測定用チップ

## (57)【特許請求の範囲】

## 【請求項1】

測定対象の電流信号が発生する電流発生部と、

前記電流信号を電圧信号に変換するトランスインピーダンスアンプと、

を備え、

前記トランスインピーダンスアンプは、

反転型の増幅回路と、

前記増幅回路の反転入力端子と出力端子の間に設けられる帰還抵抗と、

を含み.

前記増幅回路は、入力段と増幅段を含み、

\_\_前記増幅回路の前記入力段を含む一部が、前記電流発生部と同一の半導体チップに集積 化され、

前記半導体チップに形成され、前記増幅回路の前記反転入力端子と接続される第 1 コンタクト用パッドと、

前記半導体チップに形成され、前記入力段の出力端子と接続される第2コンタクト用パッドと、

前記第1、第2コンタクト用パッドと接触する第1、第2プローブを有するヘッドユニットと、

をさらに備え、

前記帰還抵抗および前記増幅段は前記ヘッドユニットに内蔵され、

前記増幅段の入力端子は、前記第2プローブと接続され、

前記帰還抵抗は、前記第1プローブと前記増幅段の出力端子の間に接続されることを特 徴とする電流測定装置。

### 【請求項2】

請求項1に記載の電流測定装置を備えることを特徴とする塩基配列解析装置。

#### 【請求項3】

第1電極および第2電極を含み、前記第1電極と前記第2電極の間に試料が通過可能に 構成される電極対と、

反転型の増幅回路の一部であって、その入力端子が前記第1電極と接続される入力段と

10

前記入力段の入力端子と接続される第1コンタクト用パッドと、

前記入力段の出力端子と接続される第2コンタクト用パッドと、

を備え、ひとつの半導体基板に一体集積化され、

使用において、前記第1コンタクト用パッドと前記第2コンタクト用パッドの間に、帰 還抵抗および前記増幅回路の増幅段が接続されることにより、トランスインピーダンスア ンプが構成可能となっていることを特徴とする測定用チップ。

【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は、電流測定装置に関する。

20

30

## 【背景技術】

#### [0002]

DNA(デオキシリボ核酸)やRNA(リボ核酸)などの塩基配列を解析するために、 塩基配列解析装置(シーケンサ)が用いられる。次世代(第4世代)のシーケンサとして さまざまな手法が研究機関や企業により模索されており、その中のひとつとして、ゲーテ ィングナノポアシーケンス技術が注目を集めている。

#### [0003]

ゲーティングナノポアシーケンス技術では、ナノメートルオーダーの1対の電極(ナノ 電極)の間をDNAやRNAが通過するときに電極間に流れるトンネル電流が、塩基の種 類(A,G,T,C)に応じて変化することを利用して、塩基配列を決定する。この手法 によれば、非常に安価でかつ小型な装置により、塩基配列の解析が可能となることが期待 されている。なお本明細書において、ナノ電極とは、それよりも大きなサブマイクロ電極 やマイクロ電極を包含するものとして用いる。

#### [0004]

またゲーティングナノポアシーケンス技術と同様にトンネル電流を利用する手法として 、MCBJ法(Mechanically Controllable Break Junction)が開発されている。MCB J法では、金属線を破断することによりナノ電極を形成する。

#### [0005]

これらのシーケンサにおいて重要な要素技術のひとつに、ナノ電極間に流れるトンネル 電流を十分な精度で測定可能な電流測定器が挙げられる。すなわちトンネル電流のオーダ 40 ーは数十pAであり、塩基の種類を判定するためには、数pSのオーダーのコンダクタン スの差を検出しなければならない。

#### 【先行技術文献】

## 【特許文献】

#### [0006]

【特許文献 1 】特開 2 0 0 3 - 2 4 0 7 4 7 号公報

【特許文献2】特開2009-133762号公報

【特許文献 3 】特開 2 0 1 3 - 2 5 7 3 3 4 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

#### [0007]

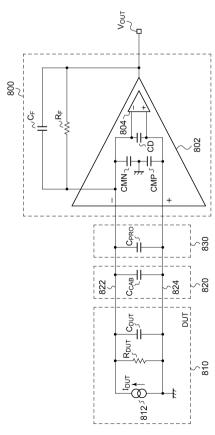

本発明者等は、微弱電流測定器として、トランスインピーダンスアンプを利用することを検討した。図 1 は、トランスインピーダンスアンプ 8 0 0 を備える電流測定装置 9 0 0 の回路図である。トランスインピーダンスアンプ 8 0 0 は、オペアンプ 8 0 2 と、オペアンプ 8 0 2 の反転入力(-)と出力の間に設けられた抵抗  $R_F$  と、を備える。オペアンプ 8 0 2 の非反転入力端子(+)には所定電位  $V_{R_F}$  (たとえば接地電圧)が入力される。キャパシタ  $C_F$  は、回路の安定性のために、抵抗  $R_F$  と並列に接続される。

## [0008]

DUT(被試験デバイス)810は、DNAやRNA(以下、DNAと総称する)などのサンプルと、サンプルを収容するチップを含む。チップには、サンプルから分離されたDNA分子が通過するナノ流路およびナノピラー、電極対などが形成される。ケーブル820は、DUT810とトランスインピーダンスアンプ800の間を接続する。

#### [0009]

図 2 は、図 1 の電流測定装置 9 0 0 の等価回路図である。 D U T 8 1 0 は、トンネル電流 I D U T を発生する電流源 8 1 2 と、寄生並列抵抗 R D U T 、寄生並列キャパシタ C D U T としてモデリングされる。

#### [0010]

ケーブル820は、DUT810の一端814とオペアンプ802の反転入力端子を接続する第1ライン822と、DUT810の他端816とオペアンプ802の非反転入力端子を接続する第2ライン824と、を含む。C<sub>CAB</sub>は、2つのライン822、824の間の寄生容量である。同軸ケーブルの場合、10cmあたりで10pFの寄生容量が発生する。

#### [0011]

トランスインピーダンスアンプ800の入力段には、様々な寄生容量が存在する。C<sub>PR</sub> o は、ESD用の保護素子、たとえばダイオードやESDサプレッサなどの寄生容量である。オペアンプに802は、理想アンプ804と、さまざまな寄生容量で表される。CMN、CMPは、コモン入力容量であり、CDは差動入力容量である。なお、図2に示される抵抗値や容量値は例示にすぎない。

## [0012]

このトランスインピーダンスアンプ800の直流トランスインピーダンスは、以下の式で与えられる。

$2.0 \times Log_{1.0}(R_F)$  (dB) ...(1)  $Log_{1.0}(R_F)$  (dB) ...(1)

## [0013]

DNAシーケンサは、数十億もの膨大な数の塩基対の種類を特定する必要がある。第4世代では1塩基1ms程度の測定時間が要求されるところ、1回の測定ではノイズの影響で塩基を特定することは難しい。そこで、1msの間に複数回、トンネル電流を測定し、その結果得られるヒストグラムにもとづいて塩基を特定するなど、統計的手法が用いられる。たとえば1msの間に100回、トンネル電流を測定するためには、サンプリングレートとして100kspsが要求され、この場合にトランスインピーダンスアンプに要求される帯域は、マージンを考慮すると数百kHz~数MHzとなる。

### [0014]

ここで図2のトランスインピーダンスアンプ800の周波数特性について検討する。カットオフ周波数f2は、式(2)で与えられる。

$f 2 = 1 / \{ 2 R_F \times (C_F + C_S / A_{OL}) \}$  ... (2)

ただし、 $C_S = C_{DUT} + C_{CAB} + C_{PRO} + C_{DB}$ り、 $A_{OL}$ は、オペアンプのオープンループゲインである。式(2)からカットオフ周波数 f2 を高めるためには、 $C_F$ を小さく、 $C_S$ を小さく、 $A_{OL}$ を高利得、広帯域にするアプローチが取り得ることがわかる。 $C_S$ を入力シャント容量と称する。オープンループゲイン $A_{OL}$ が十分に大きく、入力シャント容量  $C_S$ が小さい場合、式(2)は式(3)で近似できる。

10

20

40

30

10

20

30

40

50

$f 2 1 / \{ 2 R_F \times C_F \} \dots (3)$

たとえば $R_F = 1$  G 、 $C_F = 1$  0 f F とすると、式(3)から f 2 = 1 5 . 9 k H z となる。

## [ 0 0 1 5 ]

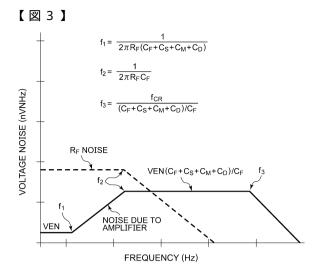

一方でトンネル電流は微弱であるため、測定系のノイズも問題となる。図 3 は、トランスインピーダンスアンプのノイズ特性を示す図である。微小電流を検出するためには、  $R_F$  として数十M から数 T のオーダーが必要となり、したがって低周波領域においては抵抗  $R_F$  による熱雑音が支配的となる。

$V_{NOTSF} = (4 \times k \times T \times R_F) [V/Hz]$

Tは温度、kはボルツマン定数である。この式は単位周波数当たりの電圧雑音密度を表す。

$R_F=1$  G 、 T=2 7 の場合、  $V_{NOISE}=4$  .  $1\mu V$  / Hz ( V/rtHz とも記す ) となる。

## [0016]

#### [0017]

特にトランスインピーダンスアンプは、オペアンプの入力インピーダンスが非常に高いことから、電界ノイズに敏感である。ノイズを低減するために、信号ラインをシールドで覆い、シールドの電位を制御する技術がある。ところが、高速化が要求されるトランスインピーダンスアンプに、シールドを追加すると、信号ラインの寄生容量が増加し、またシールドを駆動するアンプの容量が付加されることとなるため、帯域が狭くなり速度が低下する。

#### [0018]

本発明は係る課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、ノイズを低減した電流測定装置の提供にある。

## 【課題を解決するための手段】

## [0019]

本発明のある態様は、電流測定装置に関する。電流測定装置は、測定対象の電流信号が発生する電流発生部と、電流信号を電圧信号に変換するトランスインピーダンスアンプと、を備える。トランスインピーダンスアンプは、反転型の増幅回路と、増幅回路の反転入力端子と出力端子の間に設けられる帰還抵抗と、を含む。増幅回路は、電流発生部と同一の半導体チップに集積化される。

この態様によれば、電流発生部から増幅回路の反転入力端子に至る信号ラインを半導体基板上の配線で形成でき、その長さを短くして入力ラインの対接地容量を小さくできる。これによりトランスインピーダンスアンプのノイズゲインを低下させることができ、低ノイズな電流測定装置を提供できる。またトランスインピーダンスアンプは、入力インピーダンスが非常に高いため電界ノイズに敏感であるところ、干渉経路である信号ラインを短くできるため、電界ノイズの影響も低減することができる。また増幅回路を集積化することで、高抵抗なアンプ入力端が外部に露出しないことにより、電界ノイズ等の影響を低減できる。

### [0020]

ある態様の電流測定装置は、半導体チップに形成され、増幅回路の反転入力端子と接続

される第1コンタクト用パッドと、半導体チップに形成され、増幅回路の出力端子と接続される第2コンタクト用パッドと、第1、第2コンタクト用パッドと接触する第1、第2プローブを有するヘッドユニットと、をさらに備えてもよい。帰還抵抗は、ヘッドユニットに内蔵され、第1、第2プローブの間に接続されてもよい。

この態様では、帰還抵抗を半導体チップに集積化せずに、ヘッドユニットにチップ部品やSiP部品、抵抗モジュールを利用して帰還抵抗を構成することで、帰還抵抗の抵抗値はプロセスデザインルール等の制約を受けないため、大きくできる。ここで電流測定装置の利得(トランスインピーダンス)は、帰還抵抗に比例する一方、抵抗が発生する熱雑音は、 $V_{NOISE}=(4\times k\times T\times R_F)$  [V/Hz]で与えられ、帰還抵抗の平方根に比例するため、帰還抵抗の抵抗値が大きいほど、S/N比を高めることができる。また、帰還抵抗を半導体チップに集積化すると抵抗値がプロセスばらつきで変動し、トランスインピーダンス(利得)がばらつくという問題が生ずるが、この態様によれば、帰還抵抗をヘッドユニットに内蔵して使い回すことで、トランスインピーダンスのばらつきを抑制できる。

## [0021]

ある態様の電流測定装置は、半導体チップ上に形成される第3コンタクト用パッドと、 半導体チップ上に形成され、第3コンタクト用パッドと接続されるドライビングガードメ タルと、半導体チップ上に形成され、ドライビングガードメタルに増幅回路の非反転入力 端子の電圧を供給するガードアンプと、をさらに備えてもよい。ヘッドユニットは、第3 コンタクト用パッドと接触する第3プローブと、第1プローブから帰還抵抗に至る配線の 一部である芯線および第3プローブと接続されるシールドを有するケーブルと、をさらに 有してもよい。

この態様によれば、ドライビングガード機能を用いることで、アンプ入力から帰還抵抗の間を保護することにより、電界シールドとなると同時に、浮遊容量を削減できる。

#### [0022]

本発明の別の態様も、電流測定装置に関する。電流測定装置は、測定対象の電流信号が発生する電流発生部と、電流信号を電圧信号に変換するトランスインピーダンスアンプと、を備える。トランスインピーダンスアンプは、反転型の増幅回路と、増幅回路の反転入力端子と出力端子の間に設けられる帰還抵抗と、を含む。増幅回路は、入力段と増幅段を含む。増幅回路の入力段を含む一部が、電流発生部と同一の半導体チップに集積化される

## [0023]

この態様によれば、電流発生部から増幅回路の反転入力端子に至る信号ラインを半導体基板上の配線で形成でき、その長さを短くして入力ラインの対接地容量を小さくできる。これによりトランスインピーダンスアンプのノイズゲインを低下させることができ、低ノイズな電流測定装置を提供できる。またトランスインピーダンスアンプは、入力インピーダンスが非常に高いため電界ノイズに敏感であるところ、干渉経路である信号ラインを短くできるため、電界ノイズの影響も低減することができる。また増幅回路を集積化することで、高抵抗なアンプ入力端が外部に露出しないことにより、電界ノイズ等の影響を低減できる。

## [0024]

ある態様の電流測定装置は、半導体チップに形成され、増幅回路の反転入力端子と接続される第1コンタクト用パッドと、半導体チップに形成され、入力段の出力端子と接続される第2コンタクト用パッドと、第1、第2コンタクト用パッドと接触する第1、第2プローブを有するヘッドユニットと、をさらに備えてもよい。帰還抵抗および増幅段はヘッドユニットに内蔵され、増幅段の入力端子は、第2プローブと接続され、帰還抵抗は、第1プローブと増幅段の出力端子の間に接続されてもよい。

#### [0025]

本発明の別の態様は、塩基配列解析装置に関する。塩基配列解析装置は、上述のいずれかの電流測定装置を備える。

10

20

30

40

#### [0026]

本発明の別の態様は、測定用チップに関する。測定用チップは、第1電極および第2電極を含み、第1電極と第2電極の間に試料が通過可能に構成される電極対と、その反転入力端子が第1電極と接続される反転型の増幅回路と、増幅回路の反転入力端子と接続される第1コンタクト用パッドと、増幅回路の出力端子と接続される第2コンタクト用パッドと、を備え、ひとつの半導体基板に一体集積化される。測定用チップは、使用において、第1コンタクト用パッドと第2コンタクト用パッドの間に、帰還抵抗が接続されることにより、トランスインピーダンスアンプが構成可能となっている。

### [0027]

本発明の別の態様は、測定用チップに関する。測定用チップは、第1電極および第2電極を含み、第1電極と第2電極の間に試料が通過可能に構成される電極対と、反転型の増幅回路の一部であって、その入力端子が第1電極と接続される入力段と、入力段の入力端子と接続される第1コンタクト用パッドと、入力段の出力端子と接続される第2コンタクト用パッドと、を備え、ひとつの半導体基板に一体集積化される。使用において、第1コンタクト用パッドと第2コンタクト用パッドの間に、帰還抵抗および増幅回路の増幅段が接続されることにより、トランスインピーダンスアンプが構成可能となっている。

#### [0028]

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置などの間で相互に置換したものもまた、本発明の態様として有効である。

#### 【発明の効果】

[0029]

本発明のある態様によれば、ノイズを低減した電流測定装置を提供できる。

## 【図面の簡単な説明】

[0030]

- 【図1】トランスインピーダンスアンプを備える電流測定装置の回路図である。

- 【図2】図1の電流測定装置の等価回路図である。

- 【図3】トランスインピーダンスアンプのノイズ特性を示す図である。

- 【図4】第1の実施の形態に係る電流測定装置を示す図である。

- 【図5】図5(a)は、第2の実施の形態に係る電流測定装置を示す図であり、図5(b)は、増幅回路の別の構成例を示す回路図である。

- 【図6】第1変形例に係る電流測定装置を示す図である。

- 【図7】第2変形例に係る電流測定装置を示す図である。

- 【図8】第3変形例に係る電流測定装置を示す図である。

- 【図9】電流測定装置を備える塩基配列解析装置のブロック図である。

## 【発明を実施するための形態】

## [0031]

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

### [0032]

本明細書において、「部材 A が、部材 B と接続された状態」とは、部材 A と部材 B が物理的に直接的に接続される場合のほか、部材 A と部材 B が、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

同様に、「部材 C が、部材 A と部材 B の間に設けられた状態」とは、部材 A と部材 C 、あるいは部材 B と部材 C が直接的に接続される場合のほか、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合も含む。

#### [0033]

(第1の実施の形態)

10

20

30

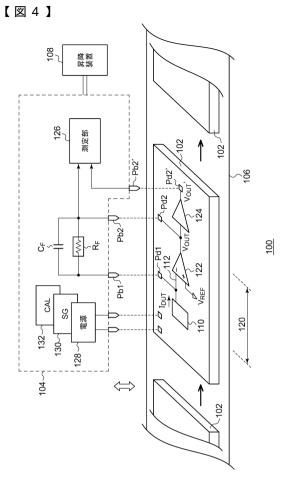

図4は、第1の実施の形態に係る電流測定装置100を示す図である。電流測定装置100は、トンネル電流やイオン電流などの微弱な電流信号I<sub>DUT</sub>を検出し、電圧信号V<sub>OUT</sub>に変換する。

### [0034]

電流測定装置 1 0 0 は、電流発生部 1 1 0 、トランスインピーダンスアンプ 1 2 0 を備える。電流発生部 1 1 0 には、測定対象の電流信号  $I_{DUT}$ が発生する。トランスインピーダンスアンプ 1 2 0 は、電流信号  $I_{DUT}$ を、電圧信号  $V_{DUT}$  に変換する。

## [0035]

トランスインピーダンスアンプ 1 2 0 は、反転型の増幅回路 1 2 2 、帰還抵抗 R  $_{\rm F}$  、帰還キャパシタ C  $_{\rm F}$  を含む。帰還抵抗 R  $_{\rm F}$  は、増幅回路 1 2 2 の反転入力端子( - ) と出力端子の間に設けられる。帰還キャパシタ C  $_{\rm F}$  は、帰還抵抗 R  $_{\rm F}$  と並列に接続される。

#### [0036]

本実施の形態において、電流発生部110およびトランスインピーダンスアンプ120 の構成部品は、測定用チップ102とヘッドユニット104に分けて実装されている。

#### [0037]

増幅回路122は、電流発生部110と同一の半導体チップ(測定用チップ)102に集積化される。測定用チップ102には、第1コンタクト用パッドPd1および第2コンタクト用パッドPd2が形成される。第1コンタクト用パッドPd1は、増幅回路122の反転入力端子と電気的に接続され、第2コンタクト用パッドPd2は、増幅回路122の出力端子と電気的に接続される。複数の測定用チップ102は、搬送装置106によって順次、ヘッドユニット104の直下に運び込まれ、測定後に運び出される。

#### [0038]

ヘッドユニット 1 0 4 は、第 1 プローブ P b 1、 P b 2 を備える。第 1 プローブ P b 1 、第 2 プローブ P b 2 はそれぞれ、第 1 コンタクト用パッド P d 1、第 2 コンタクト用パッド P d 2 と接触可能な箇所に配置されている。ヘッドユニット 1 0 4 は昇降装置 1 0 8 によって昇降可能となっている。

## [0039]

トランスインピーダンスアンプ120の帰還抵抗R<sub>F</sub>は、ヘッドユニット104に内蔵され、第1プローブPb1と第2プローブPb2の間に電気的に接続される。帰還キャパシタC<sub>F</sub>も、第1プローブPb1と第2プローブPb2の間に電気的に接続される。

#### [0040]

測定用チップ102には、コンタクト用パッドPd2′および出力バッファ124がさらに設けられる。出力バッファ124は、増幅回路122の出力を受ける。コンタクト用パッドPd2′は、出力バッファ124の出力端子と電気的に接続される。ヘッドユニット104は、プローブPb2′および測定部126、電源回路128、信号発生器130、校正器132をさらに備える。

## [0041]

プローブ P b 2 ' は、コンタクト用パッド P d 2 ' と接触可能な箇所に配置される。測定部 1 2 6 は、第 2 プローブ P b 2 およびプローブ P b 2 ' の電圧を測定可能に構成される。測定部 1 2 6 はたとえばデジタイザ(A / D コンバータ)などを含む。電源回路 1 2 8 は、ヘッドユニット 1 0 4 内の回路素子や測定用チップ 1 0 2 内の回路素子に供給すべき電源電圧等を生成する。信号発生器 1 3 0 は、測定やキャリブレーションに使用されるさまざまな信号を発生する。校正器 1 3 2 は、測定用チップ 1 0 2 の測定に先立って、測定用チップ 1 0 2 の増幅回路 1 2 2 の D C オフセットなどのキャリブレーションを行なう

## [0042]

なお増幅回路122の出力インピーダンスが十分小さい場合、出力バッファ124は省略してもよく、この場合、コンタクト用パッドPd2′、プローブPb2′は省略してもよい。また電源回路128、信号発生器130、校正器132は、ヘッドユニット104の外部に設けられてもよい。

10

20

30

40

#### [0043]

以上が電流測定装置100の構成である。

この電流測定装置 1 0 0 によれば、増幅回路 1 2 2 を測定用チップ 1 0 2 に集積化したことにより、電流発生部 1 1 0 から増幅回路 1 2 2 の反転入力端子に至る信号ライン 1 1 2 を測定用チップ 1 0 2 (半導体基板)上の配線で形成できる。これにより信号ライン 1 1 2 の長さを短くして信号ライン 1 1 2 の対接地容量(図 2 の  $_{\rm S}$  )を小さくできる。また信号ライン 1 1 2 が短くなることから、保護素子(ESD素子)を省略してもよく、この場合にはさらに対接地容量  $_{\rm S}$  を小さくできる。その結果、( $_{\rm F}$  +  $_{\rm C}$   $_{\rm S}$  + CM + CD)/  $_{\rm F}$  に応じたトランスインピーダンスアンプのノイズゲインを低下させることができ、低ノイズな電流測定装置を提供できる。

[0044]

またトランスインピーダンスアンプ120は、入力インピーダンスが非常に高いため電界ノイズに敏感であるところ、干渉経路である信号ライン112を短くできるため、電界ノイズの影響も低減することができる。また増幅回路122をSiP部品やDiP部品などを用いた場合、高抵抗なアンプ入力端が外部に露出することとなるが、増幅回路122を集積化することで、高抵抗なアンプ入力端が外部に露出しないことにより、電界ノイズ等の影響を低減できる。

[0045]

さらに図4の電流測定装置100では、帰還抵抗 $R_F$ を半導体チップ(測定用チップ)102に集積化せずに、ヘッドユニット104にチップ部品やSiP部品、抵抗モジュールを利用して帰還抵抗 $R_F$ を構成することとした。半導体基板上の抵抗素子は、数M程度が現実的な上限であり、数百 $M_F$ を外付け部品とすることで、測定用チップ102のチップサイズの増加を抑制つつも数百 $M_F$ を外ですることができる。

[0046]

ここで電流測定装置の利得(トランスインピーダンス)は、帰還抵抗  $R_F$  に比例する一方、抵抗が発生する熱雑音は、 $V_{NOISE} = (4 \times k \times T \times R_F)[V/Hz]$ で与えられ、帰還抵抗の平方根に比例するため、帰還抵抗の抵抗値が大きいほど、S/N比を高めることができる。

[0047]

また、帰還抵抗 R  $_F$  を半導体チップに集積化すると、抵抗値がプロセスばらつきで変動し、トランスインピーダンス(利得)がばらつくという問題が生ずるが、帰還抵抗 R  $_F$  をヘッドユニット 1 0 4 に内蔵して繰り返し使用することで、トランスインピーダンスのばらつきを抑制できる。これにより半導体チップごとのキャリブレーションが不要となる。

[0048]

トランスインピーダンスアンプの帯域について検討する。この電流測定装置 100では入力容量  $C_S$ が小さくなることで、トランスインピーダンスアンプの帯域(カットオフ周波数)は上述の式(3)で与えられ、帰還抵抗  $R_F$  と帰還キャパシタ  $C_F$  のみの関数となる。したがって、帰還抵抗  $R_F$  に加えて帰還キャパシタ  $C_F$  をヘッドユニット 104 に設けたことで、カットオフ周波数 f2 のばらつきを抑え、複数の測定用チップ 102 を同じ帯域で測定することができる。

[0049]

増幅回路 1 2 2 を構成するオペアンプで大きくばらつくパラメータとして、オープンループゲインが挙げられる。ここでカットオフ周波数 f 2 のオープンループゲインに対する感度は式(3)で与えられるが、これは対接地容量  $C_s$  が小さいことにより、十分に小さくできる。

[0050]

オペアンプのDCオフセットについては、以下の方法によりキャリブレーション可能である。測定対象である電流発生部 1 1 0 の出力インピーダンスが、帰還抵抗  $R_F$  より高いものとする。この場合、帰還抵抗  $R_F$  をコンタクトさせ、電流発生部 1 1 0 が電流を発生

10

20

30

40

しない状態とし、トランスインピーダンスアンプの出力電圧を測定部  $1\ 2\ 6$  によって測定することで、オペアンプ(増幅回路  $1\ 2\ 2$  )のD C オフセットを測定できる。こうして測定されたD C オフセットを保持しておき、電流信号  $I_{DUT}$  を測定するときには、測定値からD C オフセットを減算(加算)することで、D C オフセットの影響を除くことができる。

## [0051]

このように、製造バラツキによりオペアンプの特性が変動したとしても、実施の形態に係る電流測定装置 1 0 0 によれば、その変動の影響は無視しうるか、あるいは容易に対処することができ、したがってオペアンプへの性能要求は高くないと言える。オペアンプをCMOS (Complementary Metal Oxide Semiconductor)プロセスで構成する場合、CMOSはゲート入力抵抗が高いため,低リークな増幅器を構成できるという利点もある。

[0052]

また、測定用チップ102のみを可搬型としたことで、自動連続高感度測定が可能になる。

## [0053]

(第2の実施の形態)

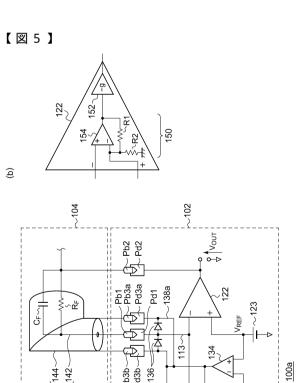

図5(a)は、第2の実施の形態に係る電流測定装置100aを示す図である。電流測定装置100aは、図4の電流測定装置100に加えて、ガードアンプ134、ESD保護素子136、ドライビングガードメタル138、同軸配線(ケーブル)140をさらに備える。

[0054]

ドライビングガードメタル 1 3 8 は、信号ライン 1 1 2 の近傍に配置される。たとえば信号ライン 1 1 2 と第 1 コンタクト用パッド P d 1 を結ぶフィードバックライン 1 1 3 を挟み込むように、 2 本のドライビングガードメタル 1 3 8 a 、 1 3 8 b を形成してもよい

[0055]

ドライビングガードメタル 1 3 8 a / b は、第 3 コンタクト用パッド P d 3 a / b と接続される。ヘッドユニット 1 0 4 は、第 3 コンタクト用パッド P d 3 a / b と対応する位置に設けられた第 3 プローブ P b 3 a / b を備える。第 3 プローブ P b 3 a / b は、同軸配線 1 4 0 のシールド 1 4 4 と接続される。第 1 プローブ P b 1 は、同軸配線 1 4 0 の芯線 1 4 2 と接続される。同軸配線 1 4 0 のシールド 1 4 4 は、帰還キャパシタ C  $_F$  および帰還抵抗 R  $_E$  の少なくとも一部を覆う。

[0056]

ガードアンプ134は、増幅回路122の非反転入力端子(+)の電圧 V<sub>REF</sub>を受け、ドライビングガードメタル138に印加する。基準電圧 V<sub>REF</sub>は、基準電圧源123により生成された電圧であってもよいし、接地電圧であってもよい。

[0057]

ESD保護素子136は、信号ライン112とドライビングガードメタル138の間に 設けられ、たとえばダイオードで構成される。

[0058]

以上が電流測定装置100aの構成である。

電流測定装置 1 0 0 a によれば、ドライビングガード機能を用いることで、アンプ入力から帰還抵抗の間を保護することにより、電界シールドとなると同時に、浮遊容量を削減できる。 E S D 保護素子 1 3 6 の寄生容量も低減される。浮遊容量を C  $_{STRAY}$  とした場合、実効的な容量は、 C  $_{STRAY}$  / A  $_{OL}$  に低減される。

[0059]

図5(b)は、増幅回路122の別の構成例を示す回路図である。増幅回路122は、単一のオペアンプで構成してもよいが、非反転アンプ150と反転アンプ152の組み合わせで構成される。非反転アンプ150は、たとえばオペアンプ154、抵抗R1、R2

10

20

30

40

を含む。反転アンプ152は、非反転アンプ150の出力を反転増幅する。オペアンプ154の非反転入力端子は、増幅回路122の反転入力端子に対応し、オペアンプ154の 反転入力端子は、増幅回路122の反転入力端子に対応する。

#### [0060]

この変形例によれば以下の効果を得ることができる。

増幅回路 1 2 2 は、非反転アンプ 1 5 0 と反転アンプ 1 5 2 の 2 段構成となっている。図 2 では、オペアンプ 8 0 2 の差動入力容量 C D が、ケーブル容量 C  $_{CAB}$ 等と並列に接続されて入力シャント容量 C  $_{S}$ の一部となり、トランスインピーダンスアンプ 8 0 0 のカットオフ周波数 f 2 を低下させる要因となっている。これに対して、図 5 (b)の構成では、オペアンプ 1 5 4 の差動入力容量は、図 2 のケーブル容量 C  $_{CAB}$  等とは並列に存在せず、したがってトランスインピーダンスアンプのカットオフ周波数 f 2 が、オペアンプ 1 5 4 の差動入力容量によって低下するのを防止できる。

#### [0061]

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、 それらの各構成要素や各処理プロセスの組み合わせにいるいろな変形例が可能なこと、ま たそうした変形例も本発明の範囲にあることは当業者に理解されるところである。以下、 こうした変形例について説明する。

#### [0062]

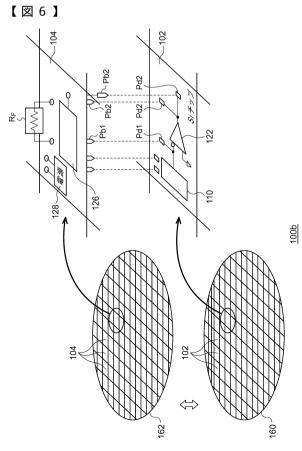

#### (第1変形例)

実施の形態では、測定用チップ102を搬送装置106によって搬送し、測定用チップ102を1個ずつ測定したが、本発明はそれには限定されない。図6は、第1変形例に係る電流測定装置100bを示す図である。この変形例では、電流測定装置100bは、ウェハ上のダイシング前のウェハ160上の複数の測定用チップ102の一部あるいは全部を同時に測定する。

#### [0063]

プローブカード162には、上述のヘッドユニット104が、複数個、ウェハ160上の複数の測定用チップ102と対応するように並べられている。ウェハ160は、図示しないハンドラによりヘッドユニット104の直下まで搬送される。そしてウェハ160とプローブカード162が近接し、各ヘッドユニット104のプローブPbとそれと対応する測定用チップ102のコンタクト用パッドPdが接触することにより、複数の測定用チップ102を一括測定することができ、あるいは測定用チップ102上の増幅回路122の良否・不良品を一括で判定することができる。

### [0064]

なおプローブカード162は、ウェハ160のすべての測定用チップ102を同時に測定する必要はなく、8個、16個など、複数の測定用チップ102を同時に測定できればよい。

## [0065]

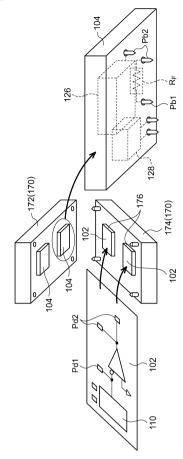

#### (第2変形例)

図7は、第2変形例に係る電流測定装置100cを示す図である。電流測定装置100cは、マニュアルハンドリング可能なケース型の測定装置である。治具170は、上部蓋部分であるプローブユニット172と、下部ベース部分であるマウンタ174を備える。マウンタ174には、ひとつあるいは複数のソケット176が設けられ、各ソケット176には測定用チップ102が装着可能となっている。プローブユニット172には、ひとつあるいは複数のヘッドユニット104が設けられる。

#### [0066]

ユーザは、手動で測定用チップ102をソケット176に置いた後に、プローブユニット172をマウンタ174に覆い被せ、ヘッドユニット104と測定用チップ102の対応するパッドとプローブを接触させる。

### [0067]

## (第3変形例)

40

10

20

30

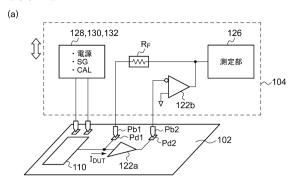

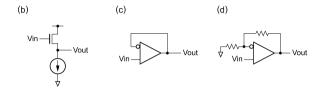

実施の形態では、増幅回路122全体が測定用チップ102に集積化される場合を説明したが、本発明はそれに限定されない。図8(a)~(d)は、第3変形例に係る電流測定装置を示す図である。図8(a)に示すように、増幅回路122は、入力段122aと増幅段122bを含み、入力段122aを含む一部が測定用チップ102に集積化され、増幅段122bは、ヘッドユニット104に内蔵される。図8(b)~(c)には、入力段122aの具体例が示される。図8(b)はソースフォロア回路であり、図8(c)はバッファ(ボルテージフォロア)であり、図8(d)は非反転増幅器である。

## [0068]

図8(a)に戻る。増幅回路122の入力段122aの入力端子、つまり増幅回路122の反転入力端子は、電流発生部110(図9の第1電極310a)と接続される。第1コンタクト用パッドPd1は、入力段122aの入力端子と接続される。第2コンタクト用パッドPd2は、入力段122aの出力端子と接続される。

#### [0069]

第1プローブ P b 1、第2プローブ P b 2 は、第1コンタクト用パッド P d 1、第2コンタクト用パッド P d 2 それぞれと接触可能に配置される。増幅段122bの入力端子は第2プローブ P b 2 と接続される。帰還抵抗 R F は、増幅段 p b 2 1 2 2 b の出力端子と第1プローブ P b 1 の間に設けられる。

## [0070]

つまり使用において、第 1 コンタクト用パッド P d 1 と第 2 コンタクト用パッド P d 2 の間に、帰還抵抗 R  $_F$  および増幅回路 1 2 2 の増幅段 1 2 2 b が接続されることにより、トランスインピーダンスアンプ 1 1 0 が構成可能となっている。

#### [0071]

この変形例によっても、実施の形態と同様の効果を得ることができる。

#### [0072]

#### (第4変形例)

実施の形態では、ヘッドユニット104にデジタイザ(A/Dコンバータ)を搭載する場合を説明したが、測定用チップ102に、デジタイザを集積化してもよい。この場合、測定用チップ102に、デジタルデータを伝送するためのインタフェース回路と、デジタルデータを出力するためのコンタクト用パッドをさらに形成する。ヘッドユニット104側には、プローブと、プローブを介したデジタルデータを受信するインタフェース回路と、を設ければよい。

## [0073]

#### (第5変形例)

実施の形態では、第1コンタクト用パッド P d 1 と信号ライン 1 1 2 を直接接続したが、回路保護のために、第1コンタクト用パッド P d 1 と信号ライン 1 1 2 の間に、抵抗を形成してもよい。同様に、第2コンタクト用パッド P d 2 と増幅回路 1 2 2 の出力の間に、抵抗を形成してもよい。

#### [0074]

## (用途)

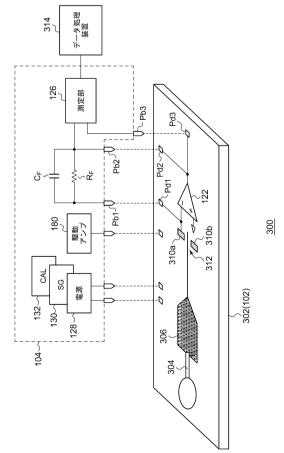

最後に、電流測定装置100の用途について説明する。実施の形態に係る電流測定装置 100は、塩基配列解析装置(DNAシーケンサあるいはRNAシーケンサ)300に用 いることができる。図9は、電流測定装置100を備える塩基配列解析装置300のブロ ック図である。ナノポアチップ302は、上述の測定用チップ102に対応する。なお図 9のチップは模式図であり、各部材のサイズは実際のそれとは異なることに留意されたい

## [0075]

ナノポアチップ302は、シリコンなどの半導体チップであり、その上にはナノ流路304、ナノピラー306、電極対310、ナノポア312、増幅回路122、第1コンタクト用パッドPd3が集積化される。そのほか、測定用チップ102には、電気泳動用電極(不図示)と、電気泳動用電極に電圧を供給するため

10

20

30

40

のコンタクト用パッド、電源回路 1 2 8 が生成した電源電圧を供給するためのコンタクト 用パッドなども形成される。

#### [0076]

ナノ流路304をDNAサンプルが通過することにより、1分子のDNAが分離、抽出される。このDNA分子がナノピラー306を通過すると、DNA分子が直線化される。

#### [0077]

ヘッドユニット 1 0 4 には、駆動アンプ 1 8 0 が設けられる。駆動アンプ 1 8 0 は、電気泳動用電極対に印加する電圧を制御し、電気泳動用電極対の間に発生する電界を制御する。この電界は、DNA分子に印加され、DNA分子がナノポア 3 1 2 に形成された電極対 3 1 0 の間を通過する。

## [0078]

#### [0079]

電圧信号  $V_{OUT}$  は、測定部(A / Dコンバータ) 1 2 6 によってデジタル値に変換される。デジタル値はデータ処理装置 3 1 4 に入力される。データ処理装置 3 1 4 は、メモリやプロセッサを含むコンピュータであり、信号処理により DNA分子の塩基配列を特定する。

## [0080]

抵抗 R  $_{\rm F}$  による電流換算の抵抗熱雑音は、 I  $_{\rm NOISE}$  = (  $4 \times k \times T /$  R  $_{\rm F}$  )となる。 R  $_{\rm F}$  = 1 M 、 2 7 の環境下で 1 2 9 f A / H z となり、トランスインピーダンスが 1 0 0 k H z の帯域を有する場合、 4 0 . 7 p A  $_{\rm RMS}$  の  $_{\rm J}$  イズが発生することとなる。 したがって高精度測定のためには、多数サンプリングを行い、統計的処理が必要となるであろう。 この観点において、実施の形態に係る電流測定装置 1 0 0 は、低  $_{\rm J}$  イズ特性および高速性を有するため、 1 塩基当たりのサンプリング回数を増やして精度を高め、あるいは単位時間当たりに解析する塩基の個数を増やすことができる。 あるいは電流測定装置 1 0 0 の  $_{\rm J}$  イズを低減できるため、 1 塩基当たりのサンプリング回数を減らすことができる。

#### [0081]

図9では、ゲーティングナノポア方式のシーケンサを説明したが、電流測定装置100 はMCBJ方式のシーケンサにも利用可能である。この場合、ナノポアチップ302に代えて、MCBJチップが使用される。MCBJチップには、ナノポア312に代えて、金線などの電極材料と、電極材料を破断するための破断機構などが集積化される。

#### [0082]

実施の形態にもとづき本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

#### 【符号の説明】

## [0083]

100…電流測定装置、102…測定用チップ、104…ヘッドユニット、106…搬送装置、108…昇降装置、110…電流発生部、112…信号ライン、120…トランスインピーダンスアンプ、122…増幅回路、124…出力バッファ、126…測定部、128…電源回路、130…信号発生器、132…校正器、134…ガードアンプ、136…ESD保護素子、138…ドライビングガードメタル、140…同軸配線、142…芯線、144…シールド、R<sub>F</sub>…帰還抵抗、C<sub>F</sub>…帰還キャパシタ、150…非反転アンプ、152…反転アンプ、154…オペアンプ、Pd1…第1コンタクト用パッド、Pd2

10

20

30

40

…第2コンタクト用パッド、Pd3…第3コンタクト用パッド、Pb1…第1プローブ、Pb2…第2プローブ、Pb3…第3プローブ、112…信号ライン、160…ウェハ、162…プローブカード、170…治具、172…プローブユニット、174…マウンタ、176…ソケット、180…駆動アンプ、300…塩基配列解析装置、302…ナノポアチップ、304…ナノ流路、306…ナノピラー、310…電極対、310a…第1電極、310b…第2電極、312…ナノポア。

【図 1】

900

DUT

NREF

RF

OUT

VREF

【図2】

(a)

# 【図7】

100c

# 【図8】

【図9】

#### フロントページの続き

## 審査官 小澤 瞬

```

(56)参考文献 米国特許出願公開第2013/0180867(US,A1)

特開2011-226886(JP,A)

特開平11-101807(JP,A)

特表2014-508300(JP,A)

特開2014-190891(JP,A)

特表2014-520568(JP,A)

国際公開第2013/109970(WO,A1)

国際公開第2014/123716(WO,A1)

国際公開第2012/164679(WO,A1)

特開2003-050192(JP,A)

特別2013-019853(JP,A)

特別2013-019853(JP,A)

```

国際公開第2014/066909(WO,A1)

## (58)調査した分野(Int.CI., DB名)

G 0 1 N 2 7 / 0 0 - 2 7 / 1 0 2 7 / 1 4 - 2 7 / 2 4 G 0 1 R 1 9 / 0 0 - 1 9 / 3 2 H 0 3 F 1 / 0 0 - 3 / 4 5 3 / 5 0 - 3 / 5 2 3 / 6 2 - 3 / 6 4 3 / 6 8 - 3 / 7 2