# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 111009572 B (45) 授权公告日 2023. 09. 01

(21)申请号 201910940618.9

(22)申请日 2019.09.30

(65) 同一申请的已公布的文献号 申请公布号 CN 111009572 A

(43) 申请公布日 2020.04.14

(30) 优先权数据 1859285 2018.10.08 FR

(73) 专利权人 意法半导体有限公司 地址 法国蒙鲁 专利权人 意法半导体(克洛尔2)公司

(72) 发明人 A·高蒂尔 P·舍瓦利耶

(74) **专利代理机构** 北京市金杜律师事务所 11256

专利代理师 董莘

(51) Int.CI.

H01L 29/06 (2006.01) H01L 21/331 (2006.01) H01L 29/73 (2006.01)

(56) 对比文件

CN 107644901 A,2018.01.30

US 2016093722 A1,2016.03.31

US 2011147892 A1,2011.06.23

CN 210723037 U,2020.06.09

US 4711017 A,1987.12.08

US 2015318384 A1,2015.11.05

JP 2004079719 A,2004.03.11

CN 1661811 A,2005.08.31

审查员 孙士博

权利要求书2页 说明书8页 附图12页

#### (54) 发明名称

双极晶体管

#### (57) 摘要

本公开的实施例涉及双极晶体管。一种双极晶体管包括集电极。集电极通过在腔体底部处形成第一基本均匀掺杂层的工艺来制造。然后,通过第一基本均匀掺杂层的掺杂剂的扩散来形成第二渐变掺杂层。

1.一种制造双极晶体管的方法,包括:

通过以下操作形成双极晶体管的集电极:

在设置在衬底中的腔体的底部处形成第一基本均匀掺杂层;

通过所述第一基本均匀掺杂层的掺杂剂到所述衬底中的扩散,形成第二渐变掺杂层, 以产生所述集电极的第一部分;

至少部分地去除所述第一基本均匀掺杂层,以形成延伸穿过所述第一基本均匀掺杂层以暴露所述第二渐变掺杂层的顶部的开口;以及

将所述集电极的第二部分放置在所述开口中,与所述第二渐变掺杂层的所述顶部接触。

- 2.根据权利要求1所述的方法,还包括:通过用绝缘材料填充所述腔体,形成绝缘沟槽。

- 3.根据权利要求2所述的方法,其中去除还包括形成在深度上完全延伸穿过所述绝缘沟槽的开口,并且其中放置包括在所述开口中形成所述集电极的所述第二部分以完全穿过所述绝缘沟槽。

- 4.根据权利要求2所述的方法,其中至少部分地去除所述第一基本均匀掺杂层在用所述绝缘材料填充所述腔体之后执行。

- 5.根据权利要求1所述的方法,其中至少部分地去除所述第一基本均匀掺杂层包括:完全去除所述第一基本均匀掺杂层。

- 6.根据权利要求1所述的方法,还包括:

在所述第一基本均匀掺杂层的被去除部分的位置处形成气穴。

- 7.根据权利要求1所述的方法,还包括:将掺杂剂注入与所述第二渐变掺杂层接触的区域中。

- 8.一种双极晶体管,包括:

集电极,所述集电极包括:

在设置在衬底中的腔体的底部处的第一基本均匀掺杂层;

在所述第一基本均匀掺杂层和所述衬底之间的第二渐变掺杂层,所述第二渐变掺杂层 形成所述集电极的第一部分;以及

在延伸穿过所述第一基本均匀掺杂层的开口中的所述集电极的第二部分,其中所述集 电极的所述第二部分与所述第二渐变掺杂层的顶部接触。

- 9.根据权利要求8所述的晶体管,其中所述第一基本均匀掺杂层与绝缘沟槽接触。

- 10.一种制造双极晶体管的方法,包括:

在半导体衬底中形成第一腔体;

在所述第一腔体中沉积第一半导体材料层,其中所述第一半导体材料层基本均匀地被掺杂;

用绝缘材料填充所述第一腔体,以在所述第一半导体材料层上方形成绝缘沟槽;

将掺杂剂从所述第一半导体材料层扩散到所述半导体衬底中,以形成渐变掺杂的半导体区域,所述半导体区域形成集电极的第一部分;以及

由穿过所述绝缘沟槽和所述第一半导体材料层的第二半导体材料层形成所述集电极的第二部分,其中所述集电极的所述第二部分的底部与用于所述集电极的所述第一部分的所述半导体区域的顶部物理接触。

11.根据权利要求10所述的方法,其中形成所述集电极的所述第二部分包括:刻蚀所述第一半导体材料层:以及

在所述集电极的所述第二部分和所述第一半导体材料层的区域之间形成第一气穴。

12.根据权利要求10所述的方法,其中形成所述集电极的所述第二部分包括:

通过刻蚀形成第二腔体,所述第二腔体在深度上延伸穿过所述绝缘沟槽和所述第一半导体材料层;以及

利用用于所述集电极的所述第二部分的所述第二半导体材料层填充所述第二腔体。

- 13.根据权利要求12所述的方法,其中所述集电极的所述第一部分的所述形成在所述第二腔体的所述刻蚀之前被执行。

- 14.根据权利要求10所述的方法,其中形成所述集电极的所述第二部分包括:

在所述绝缘沟槽上方形成导电元件;

刻蚀所述导电元件;以及

在所述集电极的所述第二部分和所述导电元件之间形成第二气穴。

- 15.根据权利要求12所述的方法,其中刻蚀还包括:去除在所述绝缘沟槽下方延伸的所述第一半导体材料层的部分。

- 16.根据权利要求15所述的方法,其中填充所述第二腔体不填充其中在所述绝缘沟槽下方延伸的所述第一半导体材料层的被去除的所述部分所位于的区域。

- 17.一种双极晶体管,包括:

半导体衬底,包括第一沟槽;

在所述第一沟槽中的第一半导体材料层,其中所述第一半导体材料层基本均匀地被掺杂:

绝缘材料,填充所述第一沟槽以在所述第一半导体材料层上方形成绝缘沟槽;

在所述半导体衬底内的半导体区域,所述半导体区域被渐变地掺杂,所述半导体区域位于所述沟槽中的所述第一半导体材料层下方,并且形成集电极的第一部分:以及

- 第二半导体材料层,穿过所述绝缘沟槽和所述第一半导体材料层,形成用于所述双极晶体管的所述集电极的第二部分,其中所述集电极的所述第二部分的底部与所述集电极的所述第一部分的顶部物理接触。

- 18.根据权利要求17所述的双极晶体管,进一步包括在所述集电极的所述第二部分和所述第一半导体材料层之间的第一气穴。

- 19.根据权利要求17所述的双极晶体管,还包括在所述绝缘沟槽上方的导电元件,其中 所述导电元件包括开口,所述开口形成在所述集电极的所述第二部分和所述导电元件之间 的第二气穴。

## 双极晶体管

## [0001] 优先权权益

[0002] 本申请要求2018年10月8日提交的法国专利申请第1859285号的优先权权益,其内容在法律允许的最大范围内通过整体引用并入本文。

## 技术领域

[0003] 本公开总体上涉及电子部件,更具体地,涉及双极晶体管及其制造方法。

## 背景技术

[0004] 双极晶体管是晶体管家族中基于半导体的电子器件。其工作原理是基于两个PN结:一个正向,一个反向。

### 发明内容

[0005] 一个实施例提供了一种制造双极晶体管的方法,其中形成集电极包括:在腔体的底部形成第一基本均匀掺杂层;以及通过第一层的掺杂剂的扩散形成第二渐变掺杂层。

[0006] 根据一个实施例,该方法还包括:通过用绝缘材料填充腔体来形成绝缘沟槽。

[0007] 根据一个实施例,该方法还包括:形成集电极的穿过绝缘沟槽的一部分。

[0008] 根据一个实施例,第一层至少部分地被去除。

[0009] 根据一个实施例,第一层被完全去除。

[0010] 根据一个实施例,在用绝缘材料填充腔体之后,第一层被去除。

[0011] 根据一个实施例,在第一层的被去除部分的位置处形成气穴。

[0012] 根据一个实施例,该方法包括:将掺杂剂注入与第二层接触的区域。

[0013] 另一实施例提供了一种双极晶体管,其具有的集电极包括与渐变掺杂层接触的基本均匀掺杂区域。

[0014] 根据一个实施例,该区域与绝缘沟槽接触。

[0015] 一个实施例提供了一种制造双极晶体管的方法,该方法包括:形成集电极的在绝缘沟槽下方延伸的第一部分;以及形成集电极的穿过绝缘沟槽的第二部分,集电极的第一和第二部分物理接触。

[0016] 根据一个实施例,第二部分的形成包括:在连续的绝缘沟槽中形成第一腔体。

[0017] 根据一个实施例,在第一腔体的刻蚀之前执行第一部分的形成。

[0018] 根据一个实施例,集电极的第一部分通过注入形成。

[0019] 根据一个实施例,集电极的第二部分的形成包括:刻蚀导电元件;以及在集电极的第二部分和导电元件之间形成第一气穴。

[0020] 根据一个实施例,集电极的第一部分的形成包括:形成第二腔体,该第二腔体具有在其中沉积的N型掺杂多晶硅层,并且该第二腔体随后用绝缘材料进行填充。

[0021] 根据一个实施例,集电极的第一部分的形成包括:扩散多晶硅层的掺杂剂。

[0022] 根据一个实施例,集电极的第二部分的形成包括:刻蚀多晶硅层;以及在集电极的

第二部分和集电极的第一部分的区域之间形成第二气穴。

[0023] 另一实施例提供了一种双极晶体管,该双极晶体管包括集电极的在绝缘沟槽下方延伸的第一部分以及集电极的穿过绝缘沟槽的第二部分,集电极的第一和第二部分物理接触。

[0024] 根据一个实施例,集电极的第二部分通过气穴来与导电元件分离。

[0025] 根据一个实施例,集电极的第二部分包括基本均匀的N掺杂区域和渐变N掺杂层,渐变N掺杂层至少部分地与所述区域接触。

[0026] 所公开的实施例克服了已知双极晶体管和/或已知双极晶体管制造方法的全部或部分缺点。

#### 附图说明

[0027] 将在以下结合附图对具体实施例的非限制性描述中详细讨论上述和其他特征和优点,其中:

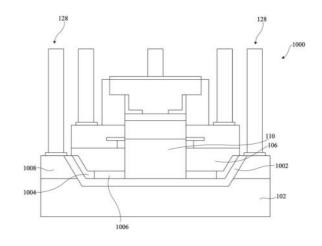

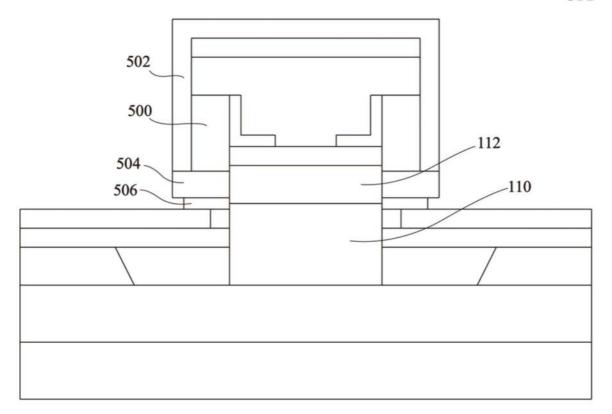

[0028] 图1示意性示出了双极晶体管的一个实施例;

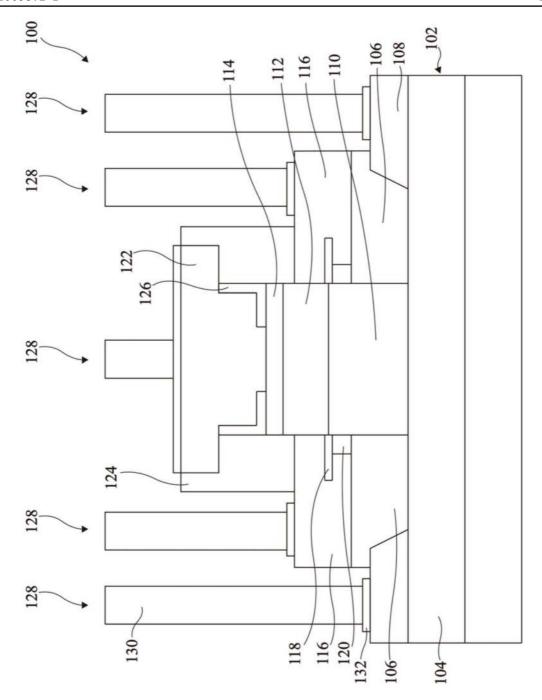

[0029] 图2示出了由图1的双极晶体管的制造方法的一个实施例的步骤产生的两个结构;

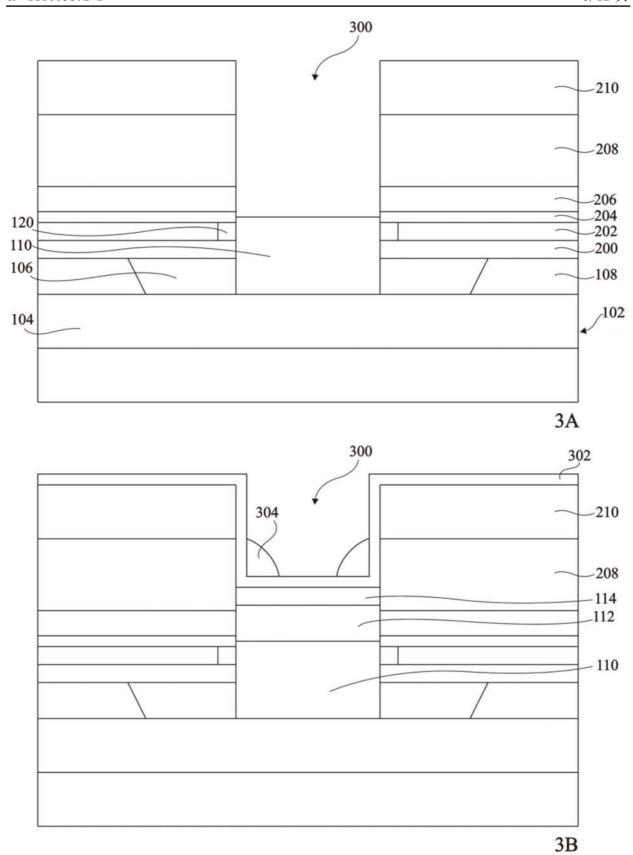

[0030] 图3示出了由图1的双极晶体管的制造方法的一个实施例的其他步骤产生的两个结构:

[0031] 图4示出了由图1的双极晶体管当制造方法的一个实施例的其他步骤产生的两个结构:

[0032] 图5示出了由图1的双极晶体管的制造方法的一个实施例的其他步骤产生的两个结构:

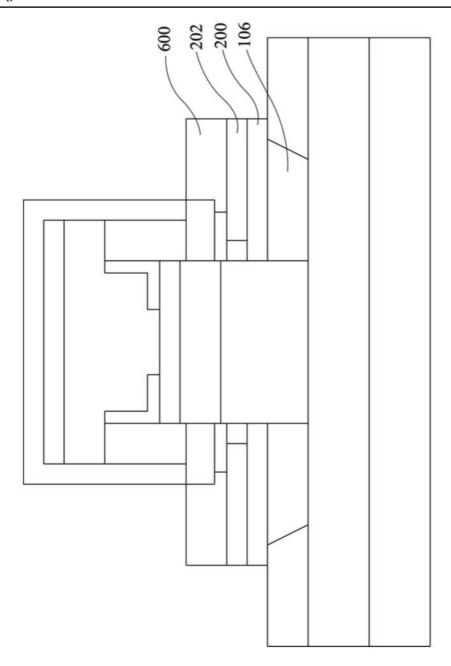

[0033] 图6示出了由图1的双极晶体管的制造方法的一个实施例的另一步骤产生的结构;

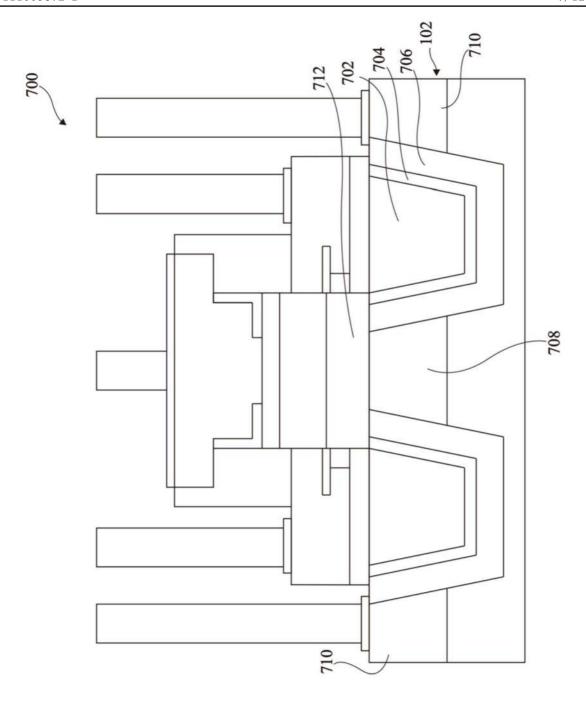

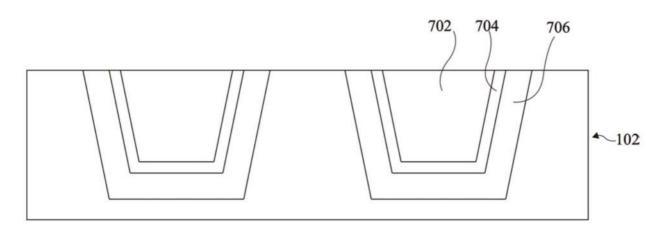

[0034] 图7示意性示出了双极晶体管的另一实施例;

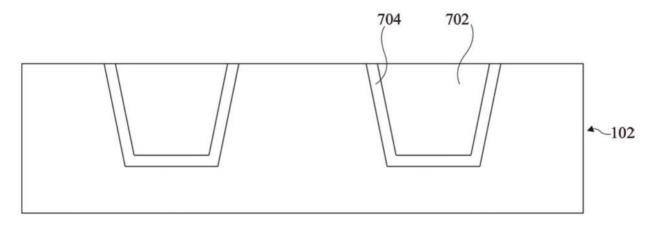

[0035] 图8示出了由图7的双极晶体管的制造方法的一个实施例的步骤产生的两个结构;

[0036] 图9示出了由图7的双极晶体管的制造方法的一个实施例的其他步骤产生的两个结构:

[0037] 图10示意性示出了双极晶体管的另一实施例:

[0038] 图11示出了由图10的双极晶体管的制造方法的一个实施例的步骤产生的两个结构:

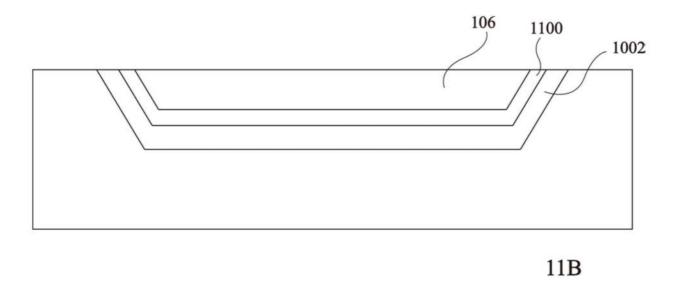

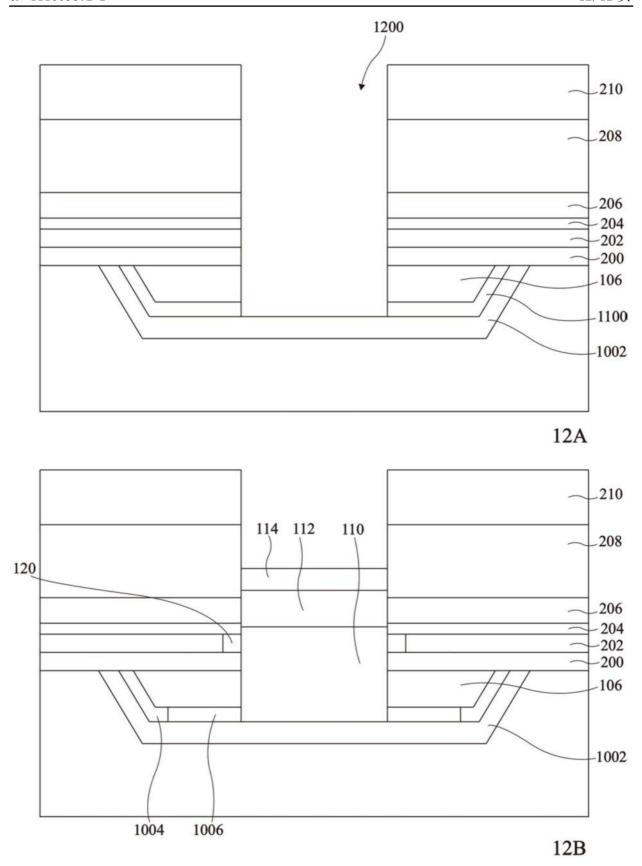

[0039] 图12示出了由图10的双极晶体管的制造方法的一个实施例的其他步骤产生的两个结构。

#### 具体实施方式

[0040] 在不同的附图中用相同的参考标号指定相同的元件。具体地,不同实施例共用的结构和/或功能元件可以用相同的参考标号来指定,并且可以具有相同的结构、尺寸和材料特性。

[0041] 为了清楚,仅示出并详细说明了那些有助于理解所述实施例的步骤和元件。

[0042] 贯穿本公开,术语"连接"用于指定除导体之外没有中间元件的电路元件之间的直接电气连接,而术语"耦合"用于指定电路元件之间的、可以是直接的或者可以经由一个或

多个中间元件的电气连接。

[0043] 在下面的描述中,当提及量化绝对位置的术语(诸如术语"前"、"后"、"上"、"下"、"左"、"右"等)或相对位置的术语(诸如术语"上方"、"下方"、"上部"、"下部"等)时或者提及限定方向的术语(诸如"水平"、"竖直"等)时,除非另有规定,否则是指附图的取向。

[0044] 这里使用术语"大约"、"基本"和"近似"来指定所提到的值的正负10%的公差,优选正负5%。

[0045] 图1示意性示出了双极晶体管100的一个实施例。

[0046] 晶体管100被形成于半导体衬底102的内部和上方,半导体衬底102优选由硅制成。晶体管100包括集电极。集电极包括衬底的第一部分104。第一部分104是埋置在衬底102中的N掺杂阱,即,在衬底102的部分108下方。例如,第一部分104掺杂有砷或磷原子。绝缘沟槽106位于阱104的一部分上。更具体地,绝缘沟槽106穿过衬底102的部分108以到达阱104。例如,绝缘沟槽是超浅沟槽隔离(SSTI)沟槽。

[0047] 例如,第一部分104被埋置在大约100nm到大约200nm的范围内的深度处。例如,沟槽106的高度在大约50nm到大约150nm的范围内。

[0048] 集电极还包括穿过绝缘沟槽106的第二部分110。因此,绝缘沟槽106在第二部分110周围形成环。集电极的第二部分110由N掺杂半导体材料制成。集电极的第二部分的高度使得第二部分从绝缘沟槽106向上突出(即,从绝缘沟槽的上表面上方突出)。

[0049] 集电极的第二部分110的下部(即,被绝缘沟槽106包围的部分)优选地在所有点处与绝缘沟槽106直接物理接触。优选地,集电极的第二部分110的下部和绝缘沟槽106不被另一材料分离。

[0050] 集电极的第二部分110覆盖有基底112和封装层114。第二部分110、基底112和层114具有基本相等的水平尺寸(即,俯视图中的尺寸)。基底由P掺杂半导体材料制成,例如由硅制成,例如由硼掺杂硅锗制成。例如,封装层114由本征硅制成。

[0051] 例如,由P掺杂半导体材料制成的导电元件116位于绝缘沟槽106上,并且与基底112物理接触。例如,通过绝缘元件118和气穴120,导电元件116与集电极的第二部分110绝缘。

[0052] 晶体管100还包括发射极122。发射极122由例如掺杂有砷和磷原子的N掺杂半导体材料制成。发射极122通过绝缘区域124来与导电元件116绝缘。发射极122和封装层114之间的界面的表面取决于绝缘元件126的尺寸。绝缘元件126包括在封装层114上延伸的下部。由此,发射极和封装层114之间的界面的表面更具体地取决于下部之间的距离。

[0053] 接触件128(例如,每个接触件都包括导电通孔130和接触焊盘132)允许晶体管100的不同部分和外部元件之间的电接触,例如经由互连网络。更具体地,接触件位于衬底的部分108上,以与集电极形成电接触。其他接触件形成在导电元件116上,以与基底形成电接触。其他接触件形成在发射极122上以与发射极形成电连接。

[0054] 图2A-图2B示出了由图1的晶体管的制造方法的一个实施例的步骤产生的两个结构。

[0055] 图2A所示的结构是在衬底102中形成绝缘沟槽106的步骤的结果。绝缘沟槽106是连续的,即,在该步骤中,其不包括开口,因此不形成环。优选地,绝缘沟槽对应于基本凸起(convex)的体积。例如,沟槽106通过在衬底102中刻蚀腔体并通过向其填充绝缘材料(例

如,氧化硅)而形成。

[0056] 然后,在衬底102中形成阱104。例如,阱104通过掺杂剂注入来形成。阱104在绝缘沟槽106下方延伸。更具体地,阱104从位于沟槽的一侧的部分108连续地延伸至位于沟槽106的另一侧的部分108。

[0057] 图2B所示的结构是在衬底102上形成叠层的步骤的结果。叠层包括:

[0058] -绝缘层200,优选由与绝缘沟槽106相同的材料制成,例如由氧化硅制成;

[0059] -导电层202,优选地由P掺杂半导体材料(例如,P掺杂多晶硅)制成;

[0060] -绝缘层204,例如由氧化硅制成;

[0061] -绝缘层206,例如由氮化硅制成;

[0062] -绝缘层208,例如由氧化硅制成;以及

[0063] -绝缘层210,例如由氮化硅制成。

[0064] 优选地,层204和208由相同的材料制成,并且层206和210由相同的材料制成。优选地,可以在层206和210的材料上方选择性地刻蚀层204和208的材料。

[0065] 例如,绝缘层200的厚度在大约20nm到大约30nm的范围内,优选为24nm。例如,导电层202的厚度在大约5nm到大约15nm的范围内,优选为10nm。例如,绝缘层204的厚度在大约8nm到大约15nm的范围内,优选为12nm。例如,绝缘层206的厚度在大约15nm到大约25nm的范围内,优选为20nm。例如,绝缘层208的厚度在大约25nm到大约37nm的范围内,优选为32nm。例如,绝缘层210的厚度在大约40nm到大约50nm的范围内,优选为44nm。

[0066] 图3A-图3B示出了由图1的晶体管的制造方法的一个实施例的其他步骤产生的两个结构。

[0067] 图3A所示的结构是形成腔体300的步骤的结果。腔体300穿过绝缘层210、208、206和204、导电层202、绝缘层200和绝缘沟槽106。阱104形成腔体300的底部。腔体的水平尺寸(即,俯视图中的尺寸)基本上对应于期望形成的晶体管的基底的尺寸。

[0068] 然后,例如通过外延在腔体300中形成集电极的第二部分110。优选地,第二部分110通过至少包括半导体材料的刻蚀和外延生长的方法形成。因此,在形成图3A所示结构的步骤期间,从腔体300部分地刻蚀层202,并且通过外延生长形成集电极的第二部分110。优选地,第二部分110从腔体300的底部延伸到绝缘层204。例如,第二部分110的厚度在约120nm到约180nm的范围内,优选为约150nm。通过外延的这种制造方法使得在层202被刻蚀的位置处形成气穴120。因此,导电层202通过气穴120与集电极的第二部分110绝缘。

[0069] 图3B中所示的结构是在集电极的第二部分110上、在腔体300中形成基底112的步骤的结果。基底112优选与第二部分110接触。例如,基底112通过外延形成。例如,基底112从集电极的第二部分110的上表面延伸到绝缘层208。然后,封装层114形成于基底112上。例如,基底112的厚度在约18nm至约26nm的范围内,优选为约22nm。例如,封装层的厚度在约10nm到约20nm的范围内,优选为约15nm。

[0070] 然后,在该结构上共形地形成绝缘层302。更具体地,层302在绝缘层210上方、在腔体300的壁上以及在封装层114上延伸。例如,由氮化硅制成的间隔件304形成于层302上的腔体300中。更具体地,间隔件部分地形成于腔体壁上,并且部分地形成于腔体底部上。在腔体底部层级处,间隔件之间的距离基本上等于绝缘元件126的下部之间的距离(图1)。

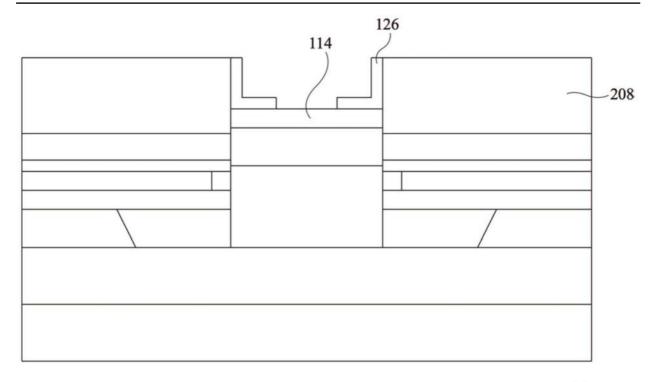

[0071] 图4A-图4B示出了由图1的晶体管的制造方法的一个实施例的其他步骤产生的两

个结构。

[0072] 图4A的结构是层302的未被间隔件304保护的部分被刻蚀的步骤的结果。由此形成绝缘元件126。然后,去除层210和间隔件304。

[0073] 图4B的结构是在该结构上形成由发射极122(图1)的材料制成的层400的步骤的结果。层400填充腔体300,并覆盖层208。然后,层400用例如由氧化硅制成的绝缘层402进行覆盖。

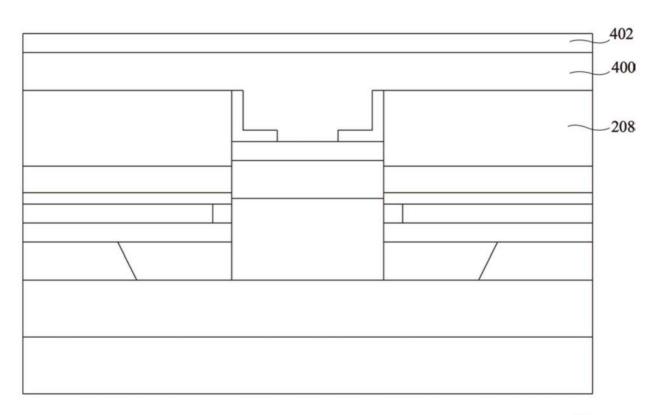

[0074] 图5A-图5B示出了由图1的晶体管的制造方法的一个实施例的其他步骤产生的两个结构。

[0075] 图5A的结构是层402、400和208被刻蚀以保持位于与集电极的第二部分110相对的部分(优选为相邻部分)的步骤的结果。因此,暴露层206的部分,尤其是位于与衬底的部分108相对的部分。保持源于绝缘层208的绝缘元件500,以使基底112和封装层114的侧面电绝缘。

[0076] 然后,在层402、400的侧壁上、绝缘元件500的侧壁上以及层402的上表面上共形地形成绝缘层502。

[0077] 图5B的结构是完全去除绝缘层206的步骤的结果,由此在绝缘元件500下方和层502的一部分下方形成腔体。腔体向下延伸到基底112。

[0078] 例如,通过外延在腔体中形成优选由P掺杂多晶硅制成的导电元件504。然后,刻蚀绝缘层204,除了位于导电元件504下方的部分506。部分506使得能够使导电元件504和集电极的第二部分110彼此电绝缘。

[0079] 图6示出了由图1的晶体管的制造方法的一个实施例的另一步骤产生的结构。

[0080] 在该步骤期间,例如通过外延在层202上形成优选由P型掺杂半导体材料制成的导电层600。层600、202和200被部分地刻蚀,优选地至少保持位于与绝缘沟槽106相对的部分。

[0081] 然后,可以执行后续步骤。在这些步骤期间,例如形成接触件128。

[0082] 图7示意性示出了双极晶体管700的另一实施例。晶体管700包括类似于晶体管100的元件。这些元件将用相同的参考标号指定,并且不再详细说明。

[0083] 与晶体管100类似,晶体管700形成于衬底102的内部和上方。绝缘沟槽702位于衬底102中。优选地,绝缘沟槽702是环形的。绝缘沟槽优选是浅沟槽绝缘(STI)沟槽。例如,沟槽的高度在大约250nm到大约350nm的范围内,例如大约为300nm。例如,沟槽702由氧化硅制成。

[0084] 由(例如,N掺杂的)半导体材料制成的层704和706位于绝缘沟槽702下方。更具体地,层704与绝缘沟槽702接触,并且层706与层704接触。层704和706共形地跟随(follow)绝缘沟槽702的侧壁和下表面。层704基本均匀地被掺杂,即,掺杂浓度在整个层中基本相等。例如,层704中的掺杂浓度在从大约3x10<sup>19</sup>掺杂剂/cm³到大约3x10<sup>20</sup>掺杂剂/cm³的范围内。层706被渐变掺杂,即,掺杂浓度随着与层704的距离的增加而逐渐降低。例如,层706中的掺杂浓度在从大约5x10<sup>18</sup>掺杂剂/cm³到大约5x10<sup>19</sup>掺杂剂/cm³的范围内。例如,层704和706掺杂有砷或磷原子。

[0085] 衬底102包括部分708以及部分710,部分708位于绝缘沟槽702之间,部分710位于绝缘沟槽的相对于部分708的另一侧。例如,部分710位于由沟槽702形成的环的外部。部分708和710是N掺杂的,例如掺有砷或磷原子。部分708与层706接触并与衬底102的上表面齐

平。每个部分710都与一个层706接触,并且与衬底102的上表面齐平。因此,部分710经由层704和706以及部分708电互连。

[0086] 与晶体管100的集电极的第二部分110类似的,部分708以及优选的层704和706的至少一部分被层712覆盖。层712、部分708和710以及层704和706形成晶体管700的集电极。例如,层712的厚度在从约35nm到约45nm的范围内,优选为40nm。

[0087] 图8A-图8B示出了由图7的晶体管的制造方法的一个实施例的步骤产生的两个结构。

[0088] 图8A所示的结构是基本在绝缘沟槽702的位置处在衬底102中形成腔体的步骤的结果。层704共形地形成在腔体的底部上。在该步骤中,掺杂浓度例如在大约4x1<sup>20</sup>原子/cm<sup>3</sup>到大约6x10<sup>20</sup>原子/cm<sup>3</sup>的范围内。然后,用例如由氧化硅制成的绝缘材料填充腔体以形成绝缘沟槽702。

[0089] 图8B所示的结构是层704的掺杂剂扩散到衬底102并由此形成层706的步骤的结果。当条件(例如,温度)允许时,扩散可以在制造过程期间进行。

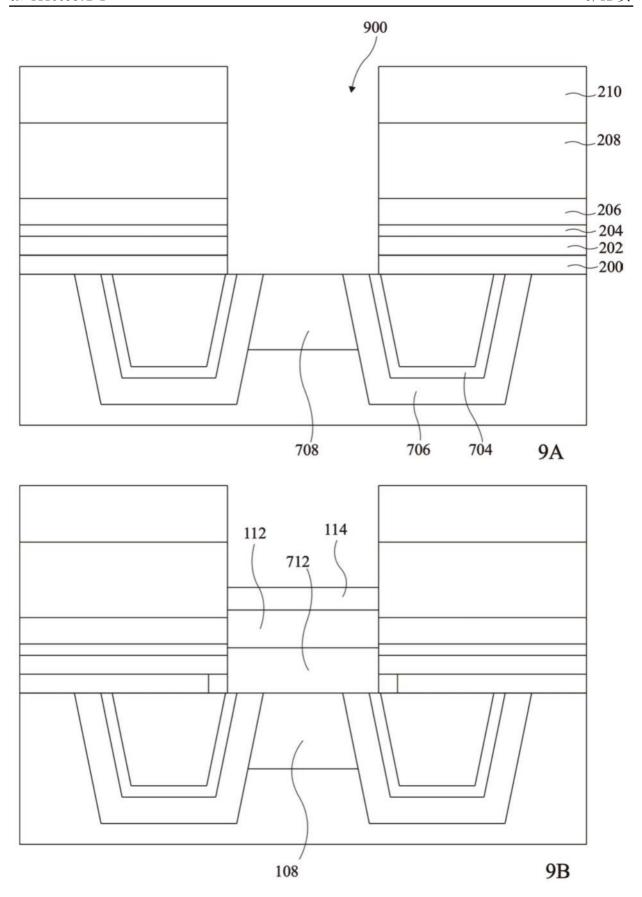

[0090] 图9A-图9B示出了由图7的晶体管的制造方法的一个实施例的其他步骤产生的两个结构。

[0091] 图9A的结构是形成先前描述的层200、202、204、206、208和210的步骤的结果。此外,腔体900被形成为与部分708相对,并且可能与层704和706的一部分相对。腔体900穿过层200、202、204、206、208和210。因此,腔体900的底部包括部分708以及层704和706的部分。

[0092] 图9B的结构是例如通过外延在腔体900中形成层712的步骤的结果。然后,例如通过外延在腔体900中形成基底112和封装层114。

[0093] 结合图3B的结构的形成来描述基底112和封装层114的形成。然后,晶体管700的制造方法包括与晶体管100的制造方法相同的步骤。更具体地,晶体管700的制造方法包括从形成基底112开始的所有步骤。因此,将不再详细描述这些步骤。

[0094] 晶体管700的制造方法还包括:通过掺杂剂注入形成部分708和710。区域708和710 位于衬底102的表面处,注入可以低功率执行,这使得与形成埋置阱相比形成更少的缺陷。

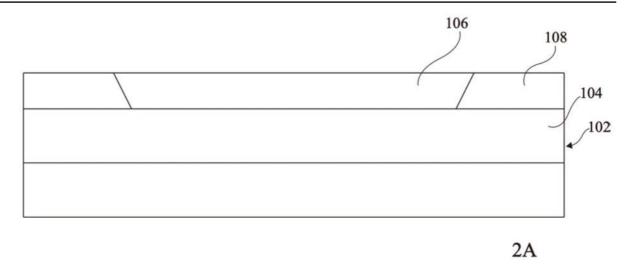

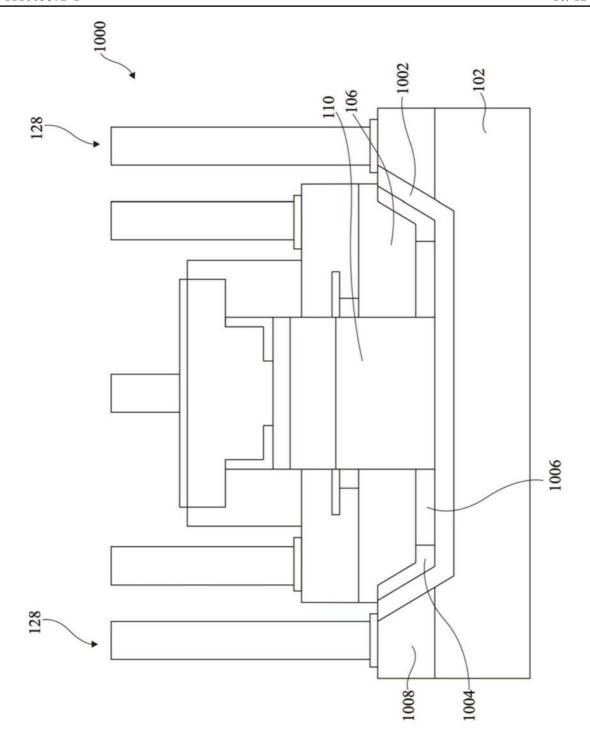

[0095] 图10示意性示出了双极晶体管1000的另一实施例。晶体管1000包括与晶体管100和700类似的元件。这些元件将用相同的参考标号指定,并且将不再详细描述。

[0096] 与晶体管100一样,晶体管1000包括被集电极的第二部分110穿过的绝缘沟槽106,第二部分110的下表面与集电极的第一部分接触。然而,在该实施例中,集电极的第一部分包括由N掺杂半导体材料(优选为硅)制成的层1002,其在绝缘沟槽106下方和集电极的第二部分110下方延伸。层1002中的掺杂浓度是渐变的,即,掺杂浓度随着与绝缘沟槽106的距离的增加而逐渐减小。例如,层1002的掺杂浓度在约5x10<sup>18</sup>掺杂剂/cm³到约5x10<sup>19</sup>掺杂剂/cm³的范围内。更具体地,在图10的截面中,层1002从绝缘沟槽106的一侧延伸到另一侧。层1002的端部与衬底102的上表面接触。层1002的端部通过由N掺杂半导体材料(例如,硅)制成的区域1004与绝缘沟槽106分离。区域1004基本均匀地掺杂,即,掺杂浓度在所有区域中基本相等。例如,区域1004中的掺杂浓度在约10<sup>19</sup>掺杂剂/cm³到约10<sup>20</sup>掺杂剂/cm³的范围内。层1002的不与区域1004或第二部分110接触的部分通过气穴1006来与绝缘沟槽106分离。

[0097] 村底102的N掺杂区域1008可以被定位为与层1002的端部接触。因此,位于村底102上的接触件128可以经由区域1008、区域1004和层1002连接。

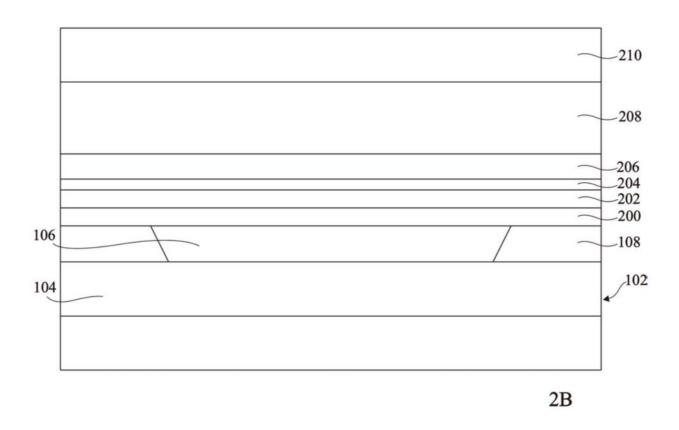

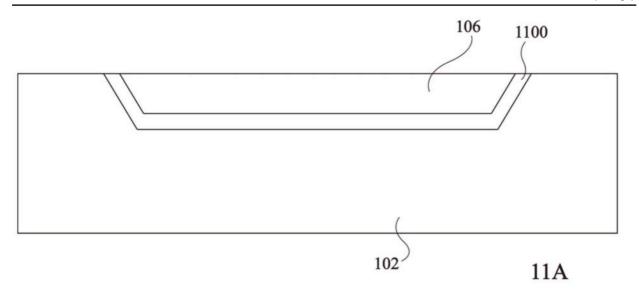

[0098] 图11A-图11B示出了由图10的晶体管的制造方法的一个实施例的步骤产生的两个结构。

[0099] 图11A的结构是在衬底102中形成腔体的步骤的结果。腔体是连续的,即,其形成基本凸起的体积。

[0100] 在腔体的壁和底部上形成层1100。层1100由N掺杂半导体材料制成,优选地由多晶硅制成。掺杂浓度在层1100中基本是均匀的。例如,掺杂浓度在约10<sup>19</sup>掺杂剂/cm³到约10<sup>20</sup>掺杂剂/cm³的范围内。然后,用绝缘材料填充腔体以形成绝缘沟槽106。

[0101] 图11B的结构是通过层1100的掺杂剂的扩散形成层1002的步骤的结果。当条件(例如,温度)允许时,可以在制造方法期间执行扩散。

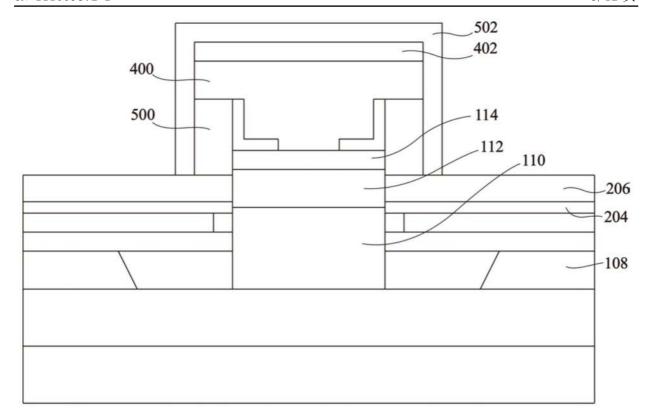

[0102] 图12A-图12B示出了由图10的晶体管的制造方法的一个实施例的其他步骤产生的两个结构。

[0103] 图12A的结构是形成先前描述的层200、202、204、206、208和210的步骤的结果。然后,腔体1200被形成为与绝缘沟槽106的一部分相对。腔体1200一直延伸到层1002,即,腔体1200穿过层210、208、206、204、202和200、绝缘沟槽106、层1100,并且可能穿过层1002的全部或部分。

[0104] 图12B的结构是例如通过诸如参照图3A的结构形成所描述的方法形成集电极的第二部分110的步骤的结果。

[0105] 优选地,第二部分110通过至少包括半导体材料的刻蚀和外延生长的方法形成。因此,在产生结构12B的步骤期间,从腔体1200部分地刻蚀层202和层1100,并且通过外延生长形成集电极的第二部分110。这种外延制造方法使得在层202和层1100被刻蚀的位置处形成气穴120和1006。作为变型,层1100可以被完全刻蚀并用气穴替换。

[0106] 如前所述,然后形成基底112和封装层114。然后,晶体管1000的制造方法包括与晶体管100的制造方法相同的步骤。更具体地,晶体管1000的制造方法包括从基底112的形成开始的所有步骤。因此,这些步骤将不再详细描述。

[0107] 晶体管1000的制造方法可以附加地包括将N型掺杂剂注入到衬底中以形成区域1008的步骤。这种注入例如类似于图1的实施例的部分708和710的掺杂剂的注入,并且因此是低功率注入。

[0108] 制造双极晶体管的另一种方法包括在衬底中形成环形绝缘沟槽,然后形成集电极的第一部分。集电极的第一部分是N型埋置阱,其在绝缘沟槽下方、位于由绝缘沟槽形成的环中的衬底部分下方以及在位于绝缘沟槽周围的衬底部分下方延伸。然后,集电极的第二部分将通过在衬底102上的、位于由绝缘沟槽形成的环中的衬底部分上方的外延来形成,并由此通过本征衬底区域来与集电极的第一部分分离。

[0109] 所述实施例的优点在于:集电极的第一和第二部分接触。特别地,集电极的第一和第二部分将不会诸如上述其他方法中的情况那样被由本征半导体材料制成的区域分离。因此,实施例的集电极的容量小于通过其他方法获得的晶体管的容量。

[0110] 图1的实施例的优点在于:集电极的第一部分104的掺杂在沟槽下方以及集电极的第二部分下方基本是均匀的,这与如其他制造方法中在掺杂期间沟槽是环形的情况不同。

[0111] 图1和图10的实施例的另一个优点在于:集电极的第二部分110的形成不会导致对准问题。实际上,在其他制造方法中,在衬底上形成的集电极的第二部分可能会与位于由绝

缘沟槽形成的环中的衬底部分不正确地对准。

[0112] 图7和图10的实施例的一个优点在于:集电极的第一部分比其他制造方法的情况相比包括较少的缺陷。事实上,与其他制造方法的形成埋置阱相比,通过扩散形成层706和1002以及通过低功率注入形成部分708、710和1008导致形成非常少的缺陷。

[0113] 已经描述了各种实施例和变型。本领域技术人员将理解,可以组合这些各种实施例和变型的特定特征,并且本领域技术人员将想到其他变型。

[0114] 最后,基于以上给出的功能指示,所述实施例和变型的实际实施在本领域技术人员的能力范围内。

图1

图3

4A

4B

5A

5B

图6

图7

8A

8B

图8

图9

图10

图11

图12