# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 111327323 A (43)申请公布日 2020.06.23

(21)申请号 202010096682.6

(22)申请日 2020.02.17

(71)申请人 西安交通大学 地址 710049 陕西省西安市咸宁西路28号

(72)发明人 张韩瑞 张鸿 焦子豪 金锴

(74)专利代理机构 北京中济纬天专利代理有限 公司 11429

代理人 覃婧婵

(51) Int.CI.

HO3M 1/38(2006.01)

权利要求书2页 说明书8页 附图4页

#### (54)发明名称

无源噪声整形过采样逐次逼近模数转换器 及控制方法

#### (57)摘要

公开了无源噪声整形过采样逐次逼近模数 转换器及控制方法,逐次逼近模数转换器中,电 容型数模转换器经由切换在其上极板产生余量 电压,无源环路滤波器配置成对所述余量电压噪 声整形,其中,用于存储余量电压的余量采集电 容相连用于实现无源增益的第一积分电容和第 二积分电容以构成无源积分器,余量采集电容与 电容型数模转换器的上极板相连,比较器输入端 连接所述无源环路滤波器的输出端以接收所述 无源环路滤波器的输出电压且将所述输出电压 与输入电压之和量化成数字码,逐次逼近逻辑数 V 字电路基于所述数字码控制电容型数模转换器 切换,以逐次逼近方式从高到低不断产生逐次逼 近模数转换器的每一位输出,直到整个量化结 東。

1.一种无源噪声整形过采样逐次逼近模数转换器,其包括,

电容型数模转换器,其经由切换在其上极板产生余量电压,

无源环路滤波器,其配置成对所述余量电压噪声整形,其中,用于存储余量电压的余量 采集电容相连用于实现无源增益的第一积分电容和第二积分电容以构成无源积分器,余量 采集电容与电容型数模转换器的上极板相连,

比较器,其输入端连接所述无源环路滤波器的输出端以接收所述无源环路滤波器的输出电压且将所述输出电压与输入电压之和量化成数字码,

逐次逼近逻辑数字电路,其输入端连接所述比较器的输出端,基于所述数字码控制电容型数模转换器切换,以逐次逼近方式从高到低不断产生逐次逼近模数转换器的每一位输出,直到整个量化结束。

- 2.如权利要求1所述的无源噪声整形过采样逐次逼近模数转换器,其中,优选的,无源环路滤波器的输出分别连接到比较器的输入端以及通过第二开关S<sub>2</sub>连接到电容型数模转换器的上极板,形成双反馈结构。

- 3. 如权利要求1所述的无源噪声整形过采样逐次逼近模数转换器,其中,电容型数模转换器包括电容阵列和采样开关 $S_1$ 。

- 4.如权利要求1所述的无源噪声整形过采样逐次逼近模数转换器,其中,无源环路积分器包括余量采集电容、第一积分电容和第二积分电容、控制信号为 $\Phi_r$ 的第二开关 $S_2$ 和第五开关 $S_5$ 、控制信号为 $\Phi_s$ 的第三开关 $S_3$ 、第四开关 $S_4$ 和第六开关 $S_6$ 。

- 5.如权利要求4所述的无源噪声整形过采样逐次逼近模数转换器,其中,第三开关S<sub>3</sub>分别连接余量采集电容、第一积分电容的上极板,第四开关S<sub>4</sub>分别连接第一积分电容和第二积分电容的上极板以构成一阶积分器,积分后得到的所述输出电压输入所述比较器的输入端完成反馈,所述输出电压通过余量采集电容在下个周期再次与电容型数模转换器的上极板相连以实现反馈。

- 6.如权利要求4所述的无源噪声整形过采样逐次逼近模数转换器,其中,第二开关S<sub>2</sub>左端连接电容型数模转换器的上极板,右端连接比较器的输入端和余量采集电容的上极板,第三开关S<sub>3</sub>左端连接余量采集电容的上极板,右端连接第一积分电容的上极板,第四开关S<sub>4</sub>左端连接余量采集电容的上极板,右端连接第二积分电容的上极板和比较器的输入端,第五开关S<sub>5</sub>左端连接第一积分电容的上极板,右端连接第二积分电容的下极板,第六开关S<sub>6</sub>左端连接共模电压,右端连接第二积分电容的下极板。

- 7.如权利要求1所述的无源噪声整形过采样逐次逼近模数转换器,其中,周期分为采样阶段  $\phi$  s 和转换阶段  $\phi$  r,在第n-1个周期时,当采样阶段为高时,电容型数模转换器作为采样电容对输入电压进行采样,采样结束后,采样阶段为低电平,转换阶段为高电平,电容型数模转换器开始第n-1次转换流程,通过比较器逐次量化采集差模输入电压,所有数字码转换完成后,电容型数模转换器和余量采集电容上极板剩余电压为 $V_{res}$  (n-1),之后进入第n个周期,当采样阶段为高电平时,电容型数模转换器进行第n次采样,此时余量采集电容相连第一积分电容和第二积分电容,第一积分电容和第二积分电容对余量采集电容上存储的上个周期的余量电压 $V_{res}$  (n-1)进行积分。

- 8. 如权利要求7所述的无源噪声整形过采样逐次逼近模数转换器,其中,转换阶段为高电平时,第一积分电容的上极板与第二积分电容的下极板相连,第二积分电容的上极板的

电压为2倍所述输出电压,通过比较器的kx端放大得到2k倍的输出电压。

- 9.如权利要求1所述的无源噪声整形过采样逐次逼近模数转换器,其中,比较器将最后一位的数字码反馈回逐次逼近逻辑数字电路控制电容型数模转换器多一次切换以在电容型数模转换器的上极板产生本周期的余量电压。

- 10.一种无源噪声整形过采样逐次逼近模数转换器的控制方法,其包括以下步骤,

- 电容型数模转换器进行开关切换,在其上极板产生余量电压,

- 无源环路滤波器对所述余量电压噪声整形产生输出电压,

- 比较器接收所述输出电压与输入电压之和量化成数字码,

逐次逼近逻辑数字电路基于所述数字码控制电容型数模转换器的切换,以逐次逼近方式从高到低不断产生逐次逼近模数转换器的每一位输出,直到整个量化结束。

# 无源噪声整形过采样逐次逼近模数转换器及控制方法

#### 技术领域

[0001] 本发明涉及集成电路技术领域,特别是一种余量反馈型的无源噪声整形过采样逐次逼近模数转换器及控制方法。

### 背景技术

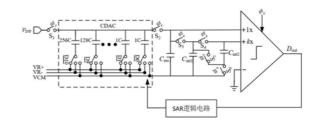

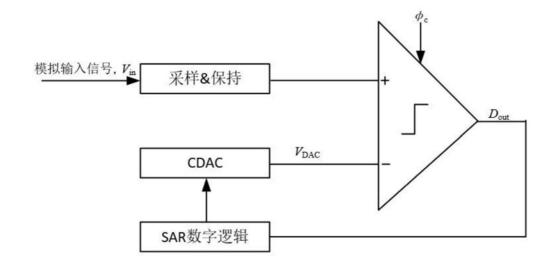

[0002] 模数转换器 (ADC) 用于将自然中的模拟信号转换为数字信号,按照采样频率与输入频率关系的可以分为两类:奈奎斯特率ADC和过采样ADC。奈奎斯特率ADC中应用最广泛的种类之一就是逐次逼近型 (Successive Approximation Register,SAR) ADC。经典的SAR ADC结构如图1所示,因为其结构简单且数字电路所占比重大,因此速度能随着工艺节点的进步而提高,同时功耗也随之降低。但是由于比较器噪声和DAC电容失配,SAR ADC在不加校准的情况下精度很难超过12位。因此SAR ADC广泛应用于中低速度和中等精度领域。过采样ADC应用最为广泛的是 $\Sigma$   $\triangle$  ADC,其结构框图如图2所示。 $\Sigma$   $\triangle$  ADC以远高于奈奎斯特频率的速率进行采样,然后利用噪声整形技术,通过牺牲带宽来降低信号通带内的噪声,从而实现高精度。但是,由于 $\Sigma$   $\triangle$  ADC中的环路滤波器需要通过一个或数个高性能的运算跨导放大器(0TA)来实现,先进工艺下由于晶体管的工作电压和本征增益越来越低,实现高性能0TA也越来越困难。因此0TA的存在不仅降低了 $\Sigma$   $\triangle$  ADC的系统的稳定性,还提高了系统的功耗限制了系统的整体转换速率。因此 $\Sigma$   $\triangle$  ADC广泛应用于低速、高精度领域。

[0003] 在SAR ADC中进行噪声整形的方法依靠有源积分器和无源积分器结合,将 \(\Sigma\) ADC 中的噪声整形技术和过采样技术应用在SAR ADC中,实现了一阶噪声整形。但是其依然使用的是基于运放的有源积分器因此功耗较高,而且运放的性能随PVT变化较大。现有的采用纯无源环路滤波器的结构采用纯电容构成的IIR滤波器大大降低了功耗。但是其在原有的SAR ADC的转换周期上额外增加两个周期,并且实现的噪声整形函数带内噪声抑制能力非常有限,仅为-3.5dB。

[0004] 在背景技术部分中公开的上述信息仅仅用于增强对本发明背景的理解,因此可能包含不构成本领域普通技术人员公知的现有技术的信息。

#### 发明内容

[0005] 鉴于上述问题,本发明的目的就是为了克服上述现有技术存在的缺陷而提供一种结无源噪声整形过采样逐次逼近模数转换器及控制方法,其能以较小的面积开销消除余量采集所需要的额外的时钟周期以加快ADC的工作速度,同时,它还能实现更优化的噪声传递函数,对比较器噪声以及ADC自身量化噪声进行一阶整形,从而有效提高SAR ADC的信噪比。

[0006] 本发明的目的是通过以下技术方案予以实现。

[0007] 一种无源噪声整形过采样逐次逼近模数转换器包括,

[0008] 电容型数模转换器,其经由切换在其上极板产生余量电压,

[0009] 无源环路滤波器,其配置成对所述余量电压噪声整形,其中,用于存储余量电压的 余量采集电容相连用于实现无源增益的第一积分电容和第二积分电容以构成无源积分器, 余量采集电容与电容型数模转换器的上极板相连,

[0010] 比较器,其输入端连接所述无源环路滤波器的输出端以接收所述无源环路滤波器的输出电压且将所述输出电压与输入电压之和量化成数字码,

[0011] 逐次逼近逻辑数字电路,其输入端连接所述比较器的输出端,基于所述数字码控制电容型数模转换器切换,以逐次逼近方式从高到低不断产生逐次逼近模数转换器的每一位输出,直到整个量化结束。

[0012] 所述的无源噪声整形过采样逐次逼近模数转换器中,无源环路滤波器的输出分别连接到比较器的输入端以及通过第二开关S<sub>2</sub>连接到电容型数模转换器的上极板,形成双反馈结构。

[0013] 所述的无源噪声整形过采样逐次逼近模数转换器中,电容型数模转换器包括电容阵列和采样开关S<sub>1</sub>。

[0014] 所述的无源噪声整形过采样逐次逼近模数转换器中,无源环路积分器包括余量采集电容 $C_{res}$ 、第一积分电容 $C_{int1}$ 和第二积分电容 $C_{int2}$ 、控制信号为 $\Phi_r$ 的第二开关 $S_2$ 和第五开关 $S_5$ 、控制信号为 $\Phi_s$ 的第三开关 $S_3$ 、第四开关 $S_4$ 和第六开关 $S_6$ 。

[0015] 所述的无源噪声整形过采样逐次逼近模数转换器中,第三开关S<sub>3</sub>分别连接余量采集电容、第一积分电容的上极板,第四开关S<sub>4</sub>分别连接第一积分电容和第二积分电容的上极板以构成一阶积分器,积分后得到的所述输出电压输入所述比较器的输入端完成反馈,所述输出电压通过余量采集电容在下个周期再次与电容型数模转换器的上极板相连以实现反馈。

[0016] 所述的无源噪声整形过采样逐次逼近模数转换器中,第二开关S<sub>2</sub>左端连接电容型数模转换器的上极板,右端连接比较器的输入端和余量采集电容的上极板,第三开关S<sub>3</sub>左端连接余量采集电容的上极板,右端连接第一积分电容的上极板,第四开关S<sub>4</sub>左端连接余量采集电容的上极板,右端连接第二积分电容的上极板和比较器的输入端,第五开关S<sub>5</sub>左端连接第一积分电容的上极板,右端连接第二积分电容的下极板,第六开关S<sub>6</sub>左端连接共模电压,右端连接第二积分电容的下极板。

[0017] 所述的无源噪声整形过采样逐次逼近模数转换器中,周期分为采样阶段和转换阶段,在第n-1个周期时,当采样阶段为高时,电容型数模转换器作为采样电容对输入电压进行采样,采样结束后,采样阶段为低电平,转换阶段为高电平,电容型数模转换器开始第n-1次转换流程,通过比较器逐次量化采集差模输入电压,所有数字码转换完成后,电容型数模转换器和余量采集电容上极板剩余电压为Vres(n-1),之后进入第n个周期,当采样阶段为高电平时,电容型数模转换器进行第n次采样,此时余量采集电容相连第一积分电容和第二积分电容,第一积分电容和第二积分电容对余量采集电容上存储的上个周期的余量电压Vres(n-1)进行积分。

[0018] 所述的无源噪声整形过采样逐次逼近模数转换器中,转换阶段为高电平时,第一积分电容的上极板与第二积分电容的下极板相连,第二积分电容的上极板的电压为2倍所述输出电压,通过比较器的kx端放大得到2k倍的输出电压。

[0019] 所述的无源噪声整形过采样逐次逼近模数转换器中,比较器将最后一位的数字码反馈回逐次逼近逻辑数字电路控制电容型数模转换器多一次切换以在电容型数模转换器的上极板产生本周期的余量电压。

[0020] 根据本发明另一方面,一种无源噪声整形过采样逐次逼近模数转换器的控制方法包括以下步骤,

[0021] 电容型数模转换器进行开关切换,在其上极板产生余量电压,

[0022] 无源环路滤波器对所述余量电压噪声整形产生输出电压,

[0023] 比较器接收所述输出电压与输入电压之和量化成数字码,

[0024] 逐次逼近逻辑数字电路基于所述数字码控制电容型数模转换器的切换,以逐次逼近方式从高到低不断产生逐次逼近模数转换器的每一位输出,直到整个量化结束。

[0025] 与现有技术相比,本发明的有益效果是:

[0026] 1、本发明利用电容型数模转换器CDAC与余量采集电容Cres直接相连的方式获取本周期余量电压Vres,不需要额外的开关周期来采集余量电压,从而加快了模数转换器ADC的工作速度;

[0027] 2、使用无源增益方式提供了2倍增益,减小了比较器所需要提供的增益,从而减小了比较器输入管的尺寸,使得比较器有更小的噪声电压和回踢噪声;

[0028] 3、本发明利用多回路反馈的方式,在不增加额外积分电容和开关的情况下,实现了更优化的噪声传递函数(NTF),大大提高了一阶噪声整形的效果,有效抑制了信号带内的量化噪声和比较器的噪声,明显提高了逐次逼近模数转换器的信噪比。

[0029] 上述说明仅是本发明技术方案的概述,为了能够使得本发明的技术手段更加清楚明白,达到本领域技术人员可依照说明书的内容予以实施的程度,并且为了能够让本发明的上述和其它目的、特征和优点能够更明显易懂,下面以本发明的具体实施方式进行举例说明。

#### 附图说明

[0030] 通过阅读下文优选的具体实施方式中的详细描述,本发明各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。说明书附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。显而易见地,下面描述的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。而且在整个附图中,用相同的附图标记表示相同的部件。

[0031] 在附图中:

[0032] 图1为现有技术的SAR ADC结构框图;

[0033] 图2为现有技术的 $\Sigma \triangle ADC$ 结构框图;

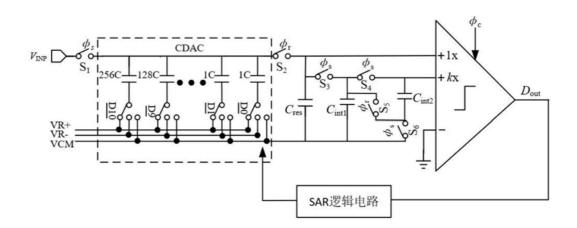

[0034] 图3为本发明的无源噪声整形SAR ADC结构示意图;

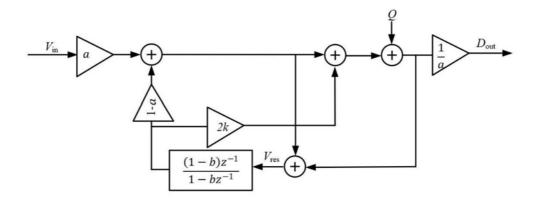

[0035] 图4为本发明的无源噪声整形SAR ADC的信号流图:

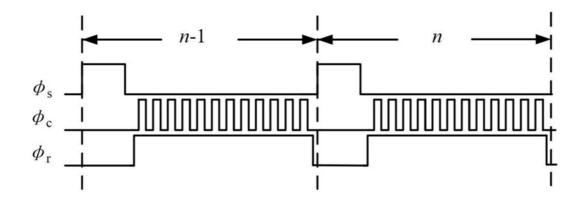

[0036] 图5为本发明的无源噪声整形SAR ADC的工作时序图;

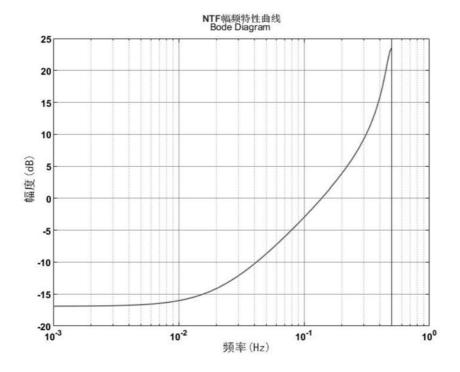

[0037] 图6为本发明的无源噪声整形SAR ADC噪声传递函数幅频特性曲线:

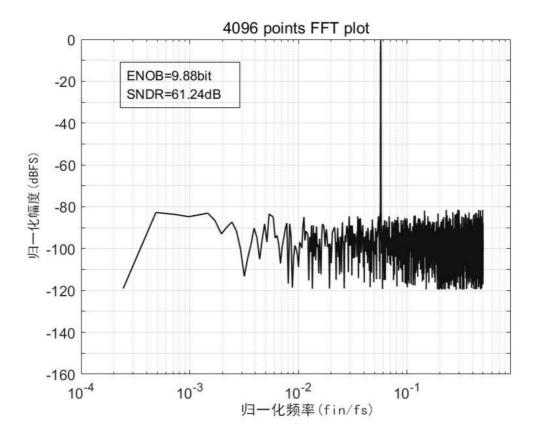

[0038] 图7为本发明的无源噪声整形SAR ADC无噪声整形时输出的FFT结果;

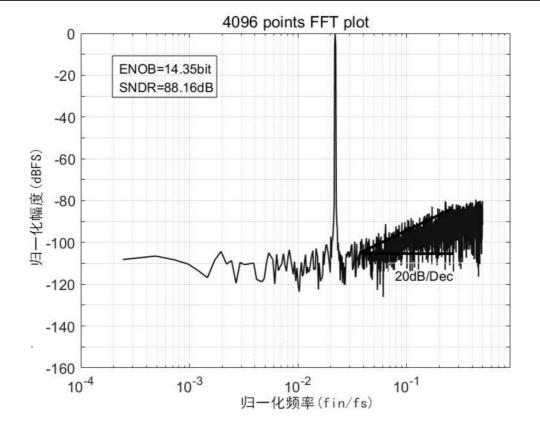

[0039] 图8为本发明的无源噪声整形SAR ADC有噪声整形时输出的FFT结果。

[0040] 以下结合附图和实施例对本发明作进一步的解释。

## 具体实施方式

[0041] 下面将参照附图1至图8更详细地描述本发明的具体实施例。虽然附图中显示了本发明的具体实施例,然而应当理解,可以以各种形式实现本发明而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本发明,并且能够将本发明的范围完整的传达给本领域的技术人员。

[0042] 需要说明的是,在说明书及权利要求当中使用了某些词汇来指称特定组件。本领域技术人员应可以理解,技术人员可能会用不同名词来称呼同一个组件。本说明书及权利要求并不以名词的差异来作为区分组件的方式,而是以组件在功能上的差异来作为区分的准则。如在通篇说明书及权利要求当中所提及的"包含"或"包括"为一开放式用语,故应解释成"包含但不限定于"。说明书后续描述为实施本发明的较佳实施方式,然所述描述乃以说明书的一般原则为目的,并非用以限定本发明的范围。本发明的保护范围当视所附权利要求所界定者为准。

[0043] 为便于对本发明实施例的理解,下面将结合附图以具体实施例为例做进一步的解释说明,且各个附图并不构成对本发明实施例的限定。

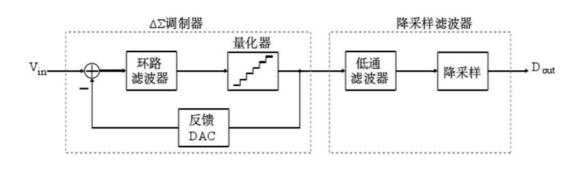

[0044] 为了更好地理解,如图3至图5所示,一种无源噪声整形过采样逐次逼近模数转换器包括,

[0045] 电容型数模转换器,其经由切换在其上极板产生余量电压,

[0046] 无源环路滤波器,其配置成对所述余量电压噪声整形,其中,用于存储余量电压的余量采集电容相连用于实现无源增益的第一积分电容和第二积分电容以构成无源积分器,余量采集电容与电容型数模转换器的上极板相连,

[0047] 比较器,其输入端连接所述无源环路滤波器的输出端以接收所述无源环路滤波器的输出电压且将所述输出电压与输入电压之和量化成数字码,

[0048] 逐次逼近逻辑数字电路,其输入端连接所述比较器的输出端,基于所述数字码控制电容型数模转换器切换,以逐次逼近方式从高到低不断产生逐次逼近模数转换器的每一位输出,直到整个量化结束。

[0049] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,无源环路滤波器的输出分别连接到比较器的输入端以及通过第二开关S<sub>2</sub>连接到电容型数模转换器的上极板,形成双反馈结构。

[0050] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,电容型数模转换器包括电容阵列和采样开关S<sub>1</sub>。

[0051] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,无源环路积分器包括余量采集电容、第一积分电容和第二积分电容、控制信号为 $\Phi_r$ 的第二开关 $S_2$ 和第五开关 $S_5$ 、控制信号为 $\Phi_s$ 的第三开关 $S_3$ 、第四开关 $S_4$ 和第六开关 $S_6$ 。

[0052] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,第三开关S<sub>3</sub>分别连接余量采集电容、第一积分电容的上极板,第四开关S<sub>4</sub>分别连接第一积分电容和第二积分电容的上极板以构成一阶积分器,积分后得到的所述输出电压输入所述比较器的输入端完成反馈,所述输出电压通过余量采集电容在下个周期再次与电容型数模转换器的上极板相连以实现反馈。

[0053] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,第二开关S<sub>2</sub>左

端连接电容型数模转换器的上极板,右端连接比较器的输入端和余量采集电容的上极板,第三开关S<sub>3</sub>左端连接余量采集电容的上极板,右端连接第一积分电容的上极板,第四开关S<sub>4</sub>左端连接余量采集电容的上极板,右端连接第二积分电容的上极板和比较器的输入端,第五开关S<sub>5</sub>左端连接第一积分电容的上极板,右端连接第二积分电容的下极板,第六开关S<sub>6</sub>左端连接共模电压,右端连接第二积分电容的下极板。

[0054] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,周期分为采样阶段和转换阶段,在第n-1个周期时,当采样阶段为高时,电容型数模转换器作为采样电容对输入电压进行采样,采样结束后,采样阶段为低电平,转换阶段为高电平,电容型数模转换器开始第n-1次转换流程,通过比较器逐次量化采集的输入电压,所有数字码转换完成后,电容型数模转换器和余量采集电容上极板剩余电压为Vres (n-1),之后进入第n个周期,当采样阶段为高电平时,电容型数模转换器进行第n次采样,此时余量采集电容相连第一积分电容和第二积分电容,第一积分电容和第二积分电容对余量采集电容上存储的上个周期的余量电压Vres (n-1)进行积分。

[0055] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,转换阶段为高电平时,第一积分电容的上极板与第二积分电容的下极板相连,第二积分电容的上极板的电压为2倍所述输出电压,通过比较器的kx端放大得到2k倍的输出电压。

[0056] 所述的无源噪声整形过采样逐次逼近模数转换器的优选实施例中,比较器将最后一位的数字码反馈回逐次逼近逻辑数字电路控制电容型数模转换器多一次切换以在电容型数模转换器的上极板产生本周期的余量电压。

[0057] 为了进一步理解本发明,在一个实施例中,本发明提供的基于余量反馈的无源噪声整形SAR ADC,包括电容型CDAC、无源环路滤波器、低回踢噪声比较器和逐次逼近逻辑数字电路。其中无源环路滤波器包括了一个用于存储上个周期余量电压的余量采集电容Cres和两个用于实现无源增益的积分电容。

[0058] 在一个实施例中,电容 $C_{res}$ 与CDAC电容的上极板相连,存储由CDAC产生的本周期的 余量电压 $V_{res}$  (n) 然后该电容与积分电容相连形成无源积分器作为无源环路滤波器,对余量电压进行噪声整形,无源环路滤波器的输出分别连接到比较器的输入端以及通过第二开关  $S_2$ 连接到CDAC的上极板,形成双反馈结构。比较器将无源环路滤波器输出电压与输入电压 之和量化成数字码,SAR逻辑控制电路根据该数字码来控制CDAC的切换,以逐次逼近方式从 高到低不断产生ADC的每一位输出,直到整个量化结束,一次完整转换输出的所有数字码即 为SAR ADC当前的量化结果。

[0059] 在一个实施例中,电容型CDAC包括电容阵列CDAC和采样开关 $S_1$ ,采样开关 $S_1$ 的控制信号为 $\phi_s$ 。

[0060] 在一个实施例中,无源环路积分器包括余量采集电容 $C_{res}$ 以及积分电容 $C_{int1}$ 和  $C_{int2}$ ,开关 $S_2$ 、 $S_5$ 的控制信号为 $\Phi_r$ 、开关 $S_3$ 、 $S_4$ 、 $S_6$ 的控制信号为 $\Phi_s$ 。无源环路滤波器的输入为 CDAC的上极板,输出连接在比较器的输入端。通过无源环路积分器对余量电压进行积分,再 通过反馈实现带内噪声的高通整形。

[0061] 噪声整形中,在SAR ADC完成最后一位的量化后,用该数字码控制CDAC额外进行一次开关切换,在CDAC上极板上得到本周期的余量电压V<sub>res</sub>,无源积分器接着对该电压进行一阶积分,同时分别使用比较器和C<sub>res</sub>电容将积分后的电压反馈回环路,从而实现噪声整形。

[0062] 其中,在SAR ADC转换期间,通过第二开关 $S_2$ 将电容 $C_{res}$ 和CDAC的上极板连接在一起实现无源采样。当CDAC完成最后一个周期的转换,CDAC和 $C_{res}$ 的上极板上剩余的电压即为余量电压 $V_{res}$ 。接下来,通过开关 $S_3$ 、 $S_4$ 将 $C_{res}$ 与 $C_{int1}$ 、 $C_{int2}$ 的上极板相连实现一阶积分器的效果。积分后得到的输出电压 $V_{int}$ 一方面送入比较器的输入端完成反馈,另一方面通过 $C_{res}$ 电容在下个周期再次与CDAC上极板相连,实现积分电压 $V_{int}$ 与 $V_{in}$ 信号求和,从而实现反馈。

[0063] 在一个实施例中,如图3所示,本发明提供的无源噪声整形SAR ADC包括电容型 CDAC、余量采集电容Cres、无源环路滤波器、无源增益单元、低回踢噪声比较器和逐次逼近逻辑数字电路。其中无源环路滤波器包括了一个用于存储上个周期余量电压的余量采集电容以及两个积分电容。

[0064] 电容 $C_{res}$ 与CDAC的上极板相连,存储由CDAC产生的本周期的余量电压 $V_{res}$ (n),然后该电容与积分电容相连形成无源积分器作为无源环路滤波器,对余量电压进行噪声整形。无源环路滤波器的输出分别连接到比较器的输入端以及通过开关 $S_2$ 连接到CDAC上极板,形成双反馈结构。比较器将无源环路滤波器输出的电压与输入电压量化成数字码,SAR逻辑控制电路根据该数字码来控制CDAC的切换,以逐次逼近方式从高到低不断产生ADC的每一位输出,直到整个量化结束,一次完整转换输出的所有数字码即为SAR ADC当此的量化结果。

[0065] 电容型CADC包括电容阵列CDAC和采样开关 $S_1$ ,采样开关 $S_1$ 的控制信号为 $\phi_s$ 。

[0066] 无源环路积分器包括余量采集电容 $C_{res}$ 以及积分电容 $C_{int1}$ 和 $C_{int2}$ ,开关 $S_2$ 、 $S_5$ 的控制信号为 $\Phi_r$ 、开关 $S_3$ 、 $S_4$ 、 $S_6$ 的控制信号为 $\Phi_s$ 。第二开关 $S_2$ 左端连接 $C_{DAC}$ 的上极板右端连接比较器的输入端和 $C_{res}$ 的上极板。第三开关 $S_3$ 左端连接 $C_{res}$ 电容上极板,右端连接 $C_{int1}$ 的上极板。第四开关 $S_4$ 左端连接 $C_{res}$ 上极板,右端连接 $C_{int2}$ 的上极板和比较器的输入端。第五开关 $S_5$ 左端连接 $C_{int1}$ 的上极板,右端连接 $C_{int2}$ 的下极板。第六开关 $S_6$ 左端连接共模电压,右端连接 $C_{int2}$ 的下极板。

[0067] 在噪声整形SAR ADC中,通过将最后一位的数字码反馈回SAR逻辑电路以此来控制 CDAC电容阵列多一次切换,这样可以在CDAC上极板得到本周期的余量电压V<sub>res</sub>。

[0068] 如图4所示为本文实现的噪声整形SAR ADC信号流图。在无源积分器中,积分电容首先对 $C_{res}$ 上的余量电压 $V_{res}$ (z)进行积分得到 $V_{int}$ (z),这种无源积分避免了使用有源积分器所带来的额外功耗,积分增益由电容的比例决定,受工艺、电源和温度 (PVT) 变化的影响很小。

[0069] 本发明的无源噪声整形SAR ADC的工作时序如图5所示。每个周期分为采样阶段  $\Phi_s$ 和转换阶段  $\Phi_r$ 。

[0070] 在第n-1个周期时,当  $\phi$  s为高时,CDAC作为采样电容对输入电压 $V_{\rm in}$ 进行采样。采样结束后, $\phi$  s为低电平, $\phi$  r为高电平,CDAC开始第n-1次的SAR ADC转换流程,通过比较器逐次量化采集到DAC上的差模输入电压。在所有数字码转换完成后,CDAC和 $C_{\rm res}$ 上极板剩余电压为 $V_{\rm res}$  (n-1)。之后进入第n个周期,当  $\phi$  s为高电平时,CDAC进行第n次采样,此时 $C_{\rm res}$ 和 $C_{\rm int}$ 相连, $C_{\rm int}$ 对 $C_{\rm res}$ 上存储的上个周期的余量电压 $V_{\rm res}$  (n-1)进行积分。使电容 $C_{\rm int}$ = $C_{\rm int1}$ + $C_{\rm int2}$ = $3C_{\rm res}$ =1.5 $C_{\rm DAC}$ (其中 $C_{\rm DAC}$ 为CDAC的总电容),那么,根据电荷守恒可以得到如下等式:

[0071]  $C_{res} \cdot V_{res} (n-1) + C_{int} \cdot V_{int} (n-1) = (C_{res} + C_{int}) \cdot V_{int} (n)$  (1)

[0072] 进一步转换到Z域中推导可得V<sub>int</sub>(z)为:

[0073]

$$V_{\text{int}}(z) = \frac{V_{\text{res}} \cdot z^{-1}}{1 - 0.75z^{-1}}$$

(2)

[0074] 之后 $\Phi_r$ 为高电平,一方面将该积分电压 $V_{int}$  (n) 与 $V_{in}$  (n) 进行相加操作,具体地,通过 $C_{res}$ 电容与CDAC电容直接相连,设CADC的总电容为 $C_{DAC}$ ,可计算得相连后CDAC上极板电压 $V_{DAC}$  (n) 的表达式:

[0075]

$$V_{in}(n) \cdot C_{DAC} + V_{int}(n) \cdot C_{res} = (C_{DAC} + C_{res}) \cdot V_{DAC}(n)$$

(3)

[0076]

$$\Leftrightarrow \frac{C_{\text{DAC}}}{C_{\text{DAC}} + C_{\text{res}}} = a$$

,

[0077] 则可进一步得到

[0078]

$$V_{DAC}(n) = a \cdot V_{in}(n) + (1-a) \cdot V_{int}(n)$$

(4)

[0079] 另一方面,  $\Phi_r$ 为高电平时, $C_{int1}$ 的上极板与 $C_{int2}$ 的下极板相连,此时 $C_{int2}$ 上极板的电压为 $2V_{int}$  (n),通过比较器kx端放大,即可得到2k倍的 $V_{int}$  (n)。具体地,通过让比较器kx端输入管的尺寸为1x端输入尺寸的k倍,即 (W/L) $_{kx}$ =k (W/L) $_{1x}$ ,即可实现k倍的放大。由此,得到系统的传递函数为:

[0080]

$$V_{in}(n) \cdot a + (1-a+k) \cdot V_{int}(n) + Q = D_{out}(n) \cdot a$$

(5)

[0081] 通过设计器件尺寸参数,使得a=0.5,k=3,则噪声传递函数NTF为

[0082] NTF=

$$\frac{2(1-0.875z^{-1})}{1+0.75z^{-1}}$$

(6)

[0083] 图6是本发明的无源噪声整形SAR ADC噪声传递函数NTF的幅频特性曲线,从图中可以看出当z=1时,NTF=1/7,即带内噪声抑制能力达到-17dB,这说明该结构有较强的噪声整形效果。

[0084] 在本发明的噪声整形SAR ADC (CDAC设计为10位) 不打开噪声整形功能时,对系统输出进行快速傅里叶变换 (FFT) 得到功率谱密度图,如图7所示。可以看出,整个噪底在带内非常平坦。且此时ADC的有效位数 (ENOB) 为9.88bit,信号噪声失真比 (SNDR) 为61.24dB。

[0085] 本发明的噪声整形SAR ADC (CDAC设计为10位) 在过采样率0SR=8情况下,对系统输出进行FFT得到功率谱密度图,如图8所示。可以看出,带内噪声底被明显压低,同时噪声功率谱在较高频处以20dB/Dec的速率在增加,一阶噪声整形效果明显。整个ADC的有效位数ENOB为14.35bit,SNDR为88.16dB。对比未打开噪声整形时,SNDR提高了26.92dB,有效位数增加了4.47位。

[0086] 综上,本发明提出的基于余量反馈的无源噪声整形技术能够有效抑制过采样SAR ADC带内的量化噪声和比较器噪声,并且在不增加额外时钟周期的条件下,有效提升SAR ADC的信噪比和有效位数。

[0087] 一种无源噪声整形过采样逐次逼近模数转换器的控制方法包括以下步骤,

[0088] 电容型数模转换器进行开关切换,在其上极板产生余量电压,

[0089] 无源环路滤波器对所述余量电压噪声整形产生输出电压,

[0090] 比较器接收所述输出电压与输入电压之和量化成数字码,

[0091] 逐次逼近逻辑数字电路基于所述数字码控制电容型数模转换器的切换,以逐次逼近方式从高到低不断产生逐次逼近模数转换器的每一位输出,直到整个量化结束。

[0092] 本发明通过复用余量采集电容来缩短转换周期,使整个噪声整形SAR ADC相较于传统SAR ADC并未增加额外的时钟周期。本发明能够实现一阶噪声整形效果,明显抑制信号通带内的量化噪声和比较器噪声,且结构简单,易于移植到更先进的集成电路工艺。

[0093] 工业实用性

[0094] 本发明所述的无源噪声整形过采样逐次逼近模数转换器及控制方法可以在集成电路领域制造并使用。

[0095] 以上结合具体实施例描述了本申请的基本原理,但是,需要指出的是,在本申请中提及的优点、优势、效果等仅是示例而非限制,不能认为这些优点、优势、效果等是本申请的各个实施例必须具备的。另外,上述公开的具体细节仅是为了示例的作用和便于理解的作用,而非限制,上述细节并不限制本申请为必须采用上述具体的细节来实现。

[0096] 为了例示和描述的目的已经给出了以上描述。此外,此描述不意图将本申请的实施例限制到在此公开的形式。尽管以上已经讨论了多个示例方面和实施例,但是本领域技术人员将认识到其某些变型、修改、改变、添加和子组合。

图1

图2

图3

图4

图5

图6

图7

图8