# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-33023 (P2005-33023A)

(43) 公開日 平成17年2月3日(2005. 2.3)

| (51) Int.C1. <sup>7</sup> | F 1                  |              | テーマコード                       | (参考)   |  |

|---------------------------|----------------------|--------------|------------------------------|--------|--|

| HO1L 21/768               | HO1 L 21,            | /90 <b>J</b> | 4 M 1 O 4                    |        |  |

| HO1L 21/308               | <b>5</b> HO1L 29,    | /44 S        | 5F004                        |        |  |

| HO1L 21/320               | <b>5</b> HO1L 29,    | /58 G        | 5F033                        |        |  |

| HO1L 21/336               | HO1L 21,             | /88 B        | 5 F 1 4 O                    |        |  |

| HO1L 29/41                | HO1L 29,             | /78 3 O 1 P  |                              |        |  |

|                           | 審査請求 未請求             | で 請求項の数 6    | O L (全 12 頁)                 | 最終頁に続く |  |

| (21) 出願番号<br>(22) 出願日     | 平成15年7月7日 (2003.7.7) | ソニー<br>東京都   | ソニー株式会社<br>東京都品川区北品川6丁目7番35号 |        |  |

弁理士 船橋 國則

(72) 発明者 菅野 道博

東京都品川区北品川6丁目7番35号 ソニー株式会社内

F ターム (参考) 4M104 AA01 BB01 CC05 DD80 DD84 DD91 EE09 EE12 EE16 EE17 FF06 FF14 GG08 HH13 5F004 AA11 EA12 EA37 EA38 EB03 EB08 FA02 FA06

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法および半導体装置

# (57)【要約】

【課題】狭い配線間における絶縁膜の埋め込み性を改善し、配線間に絶縁膜を埋め込んだ際にその絶縁膜にボイドを発生すること無く、信頼性の高い絶縁膜の形成を図る。

【解決手段】基板11上に配線14を形成した後に配線14の側部にスペーサ17を形成する工程と、基板11上に配線14間を埋め込むとともに配線14およびスペーサ17を被覆する絶縁膜21を形成する工程とを備えた半導体装置に製造方法において、スペーサ17を形成した後で絶縁膜21を形成する前に、スペーサ17の上部側面の曲率を大きくするようにスペーサ17の上部側面を除去する工程を備えた半導体装置の製造方法である

### 【特許請求の範囲】

# 【請求項1】

基 板 上 に 配 線 を 形 成 し た 後 に 前 記 配 線 の 側 部 に ス ペ ー サ を 形 成 す る 工 程 と 、 前 記 基 板 上 に 前 記 配 線 間 を 埋 め 込 む と と も に 前 記 配 線 お よ び 前 記 ス ペ ー サ を 被 覆 す る 絶 縁 膜 を 形 成 す る工程とを備えた半導体装置に製造方法において、

前 記 ス ペ ー サ を 形 成 し た 後 で 前 記 絶 縁 膜 を 形 成 す る 前 に 、 前 記 ス ペ ー サ の 上 部 側 面 の 曲 率を大きくするように前記スペーサの上部側面を除去する工程

を備えたことを特徴とする半導体装置の製造方法。

### 【請求項2】

前 記 配 線 間 に お け る 前 記 絶 縁 膜 が 埋 め 込 ま れ る 領 域 の ア ス ペ ク ト 比 を 1 以 下 と す る ことを特徴とする請求項1記載の半導体装置の製造方法。

### 【請求項3】

前記スペーサ側面の傾斜は90度未満とする ことを特徴とする請求項1記載の半導体装置の製造方法。

#### 【請求項4】

前記スペーサの上部側面を除去する工程は、

前記スペーサの上部側面にダメージ層を形成する工程と、

前記スペーサの上部側面に形成された前記ダメージ層を選択的に除去する工程と を備えたことを特徴とする請求項1記載の半導体装置の製造方法。

### 【請求項5】

前記ダメージ層を形成する工程は、

前記スペーサ上部の側部のみにイオン注入する、

ことを特徴とする請求項4記載の半導体装置の製造方法。

### 【請求項6】

基板上に形成された配線と、

前記配線の側部に形成されたスペーサと、

前記配線間を埋め込むとともに前記配線および前記スペーサを被覆するように前記基板 上に形成された絶縁膜とを備えた半導体装置において、

前記スペーサは、前記スペーサの上部側面の曲率を大きくするように前記スペーサの上 部側面が除去されたものからなり、

前 記 配 線 側 部 に 形 成 さ れ た ス ペ ー サ 間 の 前 記 絶 縁 膜 が 埋 め 込 ま れ る 領 域 は ア ス ペ ク ト が 1以下となるように形成されている

ことを特徴とする半導体装置。

# 【発明の詳細な説明】

# 【技術分野】

### [00001]

本 発 明 は 、 半 導 体 装 置 の 製 造 方 法 お よ び 半 導 体 装 置 に 関 し 、 詳 し く は 半 導 体 装 置 の 絶 縁 膜の形成に係わる半導体装置の製造方法およびその製造方法により形成される半導体装置 に関する。

### 【背景技術】

# [0002]

従来、半導体装置における金属配線形成工程前の層間絶縁膜の形成技術およびその層間 絶 縁 膜 の 平 坦 化 技 術 は 、 ホ ウ 素 や ヒ 素 を 入 れ て 流 動 化 さ せ る ホ ウ 素 リ ン シ リ ケ ー ト ガ ラ ス ( B P S G )を用いたリフロー技術や、全面エッチバック技術の組み合わせなどが主流で あった(例えば、特許文献1参照。)が、世代が進むにつれて高温処理によるトランジス 夕 特 性 や 信 頼 性 へ の 影 響 が 無 視 で き な く な っ て き た こ と や 、 リ ソ グ ラ フ ィ ー の 焦 点 深 度 ( DOF)マージン確保のためにはグローバル段差を極力抑える必要性が生じてきたことな どにより、低温でグローバル段差を小さくできるプロセス技術に変わってきた。

10

20

30

40

50

20

30

40

50

[0003]

熱的にはトランジスタに影響を及ぼさない温度限界から、 0 . 1 μ m 世代のトランジスタでは熱処理温度を 6 0 0 以下に抑える必要があり、局所(ローカル)段差のギャップフィル(Gap-fill)特性との兼ね合いからオゾン・ノンドープトシリケートガラス( O 3 N S G )膜や高密度プラズマ・ノンドープトシリケートガラス( H D P N S G )膜が埋め込みの絶縁膜として使われている。これらの膜のグローバル段差を低減する方法の主流としては化学的機械研磨(以下、 C M P という)があげられる。

[0004]

【特許文献1】特開平10-189518号公報(段落番号0002および段落番号00 13-0022、図1および3)

【発明の開示】

【発明が解決しようとする課題】

[0005]

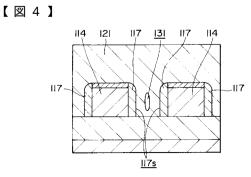

しかしながら、これら低温で埋め込み可能な膜種であっても、0.1μm世代のロジック部ゲート・ゲート間距離の設計値は0.2μm以下と小さくなり、さらに図4に示すように、ゲート配線114の側壁にスペーサ膜117が形成されるので、スペーサ117間の実質的なアスペクト比は1を大きく超えることになる。このため、埋め込み絶縁膜121によるこの部分の段差被覆が難しくなる。また、スペーサ膜117の側壁117sの傾斜が垂直になり、絶縁膜121の埋め込み性が悪化し、ゲート配線114、114間にボイド131を生じるようになる。さらに、図示はしないが、ソース・ドレイン領域となる拡散層上およびゲート上にサリサイド(Salicide)を形成する前のウエットエッチング処理やスペーサ膜厚のばらつきなどで、下地プロセスばらつきが悪化する方向になって埋め込み領域がオーバーハング状態となるとさらに埋め込みが厳しくなることがわかっている

[0006]

また、HDPNSGを用いて層間絶縁膜を形成する場合は、成膜プロセスがプラズマ中のため、プラズマダメージによるトランジスタ特性や信頼性への影響が、プラズマの影響が受けやすいアンテナ比の高いトランジスタにおいて顕著になる問題がある。それに比べてオゾンNSGはプラズマダメージの影響がないので、ダメージフリーであることにおいて優位である。

[0007]

したがって、埋め込みの膜そのものの能力向上だけでなく、下地プロセスのばらつき抑制や埋め込みのしやすい形状にするようなプロセスインテグレーレションによる改善が必要になっている。

【課題を解決するための手段】

[0008]

本発明の半導体装置の製造方法は、基板上に配線を形成した後に前記配線の側部にスペーサを形成する工程と、前記基板上に前記配線間を埋め込むとともに前記配線および前記スペーサを被覆する絶縁膜を形成する工程とを備えた半導体装置に製造方法において、前記スペーサを形成した後で前記絶縁膜を形成する前に、前記スペーサの上部側面の曲率を大きくするように前記スペーサ上部の側部を除去する工程を備えていることを最も主要な特徴とする。

[0009]

上記半導体装置の製造方法では、スペーサを形成した後で絶縁膜を形成する前に、スペーサの上部側面の曲率を大きくするようにスペーサの上部側面を除去することから、スペーサ側壁の急峻な傾斜面が緩く形成されることになり、絶縁膜の埋め込みが容易になる。よって、スペーサ間の絶縁膜の埋め込みに際し、ボイドの発生が防止される。

[0010]

本発明の半導体装置は、基板上に形成された配線と、前記配線の側部に形成されたスペーサと、前記配線間を埋め込むとともに前記配線および前記スペーサを被覆するように前

記基板上に形成された絶縁膜とを備えた半導体装置において、前記スペーサは、前記スペーサの上部側面の曲率を大きくするように前記スペーサの上部側面が除去されたものからなり、前記配線側部に形成されたスペーサ間の前記絶縁膜が埋め込まれる領域はアスペクトが1以下となるように形成されているものであることを最も主要な特徴とする。

### [0011]

上記半導体装置では、スペーサは、スペーサの上部側面の曲率を大きくするようにスペーサの上部側面が除去されたものからなることから、スペーサ側面の急峻な傾斜面が緩く形成されることになり、絶縁膜の埋め込みが容易になる。さらに、配線側部に形成されたスペーサ間の絶縁膜が埋め込まれる領域はアスペクトが1以下となるように形成されていることから、絶縁膜の埋め込みの容易性が高められる。よって、スペーサ間の絶縁膜の埋め込みに際し、ボイドの発生が防止される。

### 【発明の効果】

### [0012]

本発明の半導体装置の製造方法によれば、スペーサを形成した後で絶縁膜を形成する前に、スペーサの上部側面の曲率を大きくするようにスペーサの上部側面を除去することから、スペーサ側壁の急峻な傾斜面が緩く形成されることになり、絶縁膜の埋め込みが容易になる。よって、従来の絶縁膜材料による狭いスペーサ間の埋め込みに際し、ボイドの発生が防止される。このように、ボイドを発生することなく、絶縁膜を配線間に良好に埋め込むことが可能になることで、コンタクト・コンタクト間のショートがなくなり、コンタクトのショート起因によるデバイスの歩留まり低下をなくすことができる。またドライエッチング工程を追加するだけですみ、プロセスが簡単である。さらに、従来から適用されているデバイスのスペーサ構造を利用することができ、従来のプロセスから要求されるスペーサ構造との整合性がよいという利点がある。

### [0013]

本発明の半導体装置によれば、スペーサは、スペーサの上部側面の曲率を大きくするようにスペーサの上部側面が除去されたものからなることから、スペーサ側面の急峻な傾斜面が緩く形成されることになり、絶縁膜の埋め込みが容易になる。さらに、配線側部に形成されたスペーサ間の絶縁膜が埋め込まれる領域はアスペクトが1以下となるように形成されていることから、絶縁膜の埋め込みの容易性が高められる。よって、スペーサ間の絶縁膜の埋め込みに際し、ボイドの発生を防止することができるので、信頼性の高い絶縁膜構造をもつ半導体装置とすることができるという利点がある。

【発明を実施するための最良の形態】

### [0014]

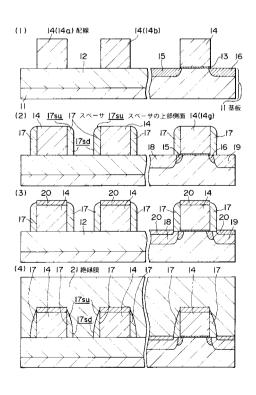

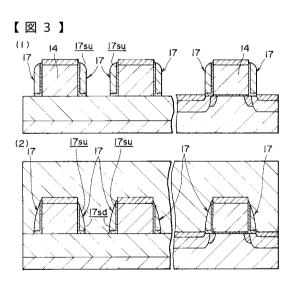

本発明の半導体装置の製造方法に係る第1実施の形態を、図1の製造工程断面図によって説明する。

# [0015]

図1(1)に示すように、通常のMOSトランジスタの形成技術によって、基板(半導体基板)11に対してアクティブ領域を分離する素子分離領域およびフィールド領域となるフィールド絶縁膜12を形成する。上記半導体基板には通常のシリコン基板を用いた。次いで、上記基板11上にゲート絶縁膜13を形成する。次いで、ゲート電極およびゲート配線で開いて導電膜をゲート電極およびゲート配線ではポリシリコンにで形成される。このポリシリコン膜の膜厚は、例えば200mmとし、フィールド絶縁膜12上の配線14(14a)とこの配線14aに隣接する配線14(14b)との間隔は、例えば設計値で200mmとする。ポリシリコン膜厚は、後に形成されるサリサイドのブリッジング(Bridging)や、ゲート絶縁膜13に与える影響から決められている。配線14間の間隔は配線14の加工限界から決まる。なお、配線14の間隔は実際には設計値よりもやなく形成される。

# [0016]

10

20

30

30

40

50

次に、アクティブ領域の半導体基板11に低濃度拡散層からなるエクステンション領域15、16を例えば配線14をマスクにしたイオン注入により形成する。したがって、エクステンション領域15、16は、配線14の側方におけるアクティブ領域の半導体基板11に形成される。またMOSFETの短チャネル効果を抑制するための斜めイオン注入を行う。

### [0017]

その後、図1(2)に示すように、配線14の側部にスペーサ17を形成する。スペーサ17は、配線14を被覆するように、スペーサを形成するための絶縁膜を形成した後、エッチバックによりその絶縁膜をエッチングして配線14の側壁にのみ残すことにより形成される。ここでは、スペーサ17を形成する絶縁膜に窒化シリコン膜を用い、その膜厚は一例として100mmとした。その結果、スペーサ17は、配線14の配設方向に沿った厚さwはおよそ80mmになった。このとき、スペーサ17の上部側面17suは小さな曲率の曲面となっており、スペーサ17の下部側面17sd(垂直面)におけるスペーサ17間のアスペクト比は1以下であり、この状態では絶縁膜を埋め込んだ際にボイドを発生するような形状となっていた。

### [0018]

次に、配線14およびスペーサ17をマスクにしたイオン注入法によって、アクティブ領域の半導体基板11に上記低濃度拡散層よりも濃度の濃い(高濃度拡散層からなる)ソース・ドレイン領域18、19を形成する。このソース・ドレイン領域18、19は、配線14側方のアクティブ領域の半導体基板11にスペーサ17の厚さ分、すなわちエクステンション領域15、16を介して形成される。ここでスペーサ17は、ソース・ドレイン領域18、19のゲート電極となる配線14(14g)側にエクステンション領域15、16というオフセットをつけることでMOSFETのホットキャリア耐性向上を図るとともに、前記斜めイオン注入によって行われたMOSFETの短チャネル効果抑制領域を残す役割を成す。

# [0019]

次いで、図1(3)に示すように、サリサイド形成を行う。サリサイド形成は、スパッタリングにより、配線14が形成されている側の全面に高融点金属膜を被覆形成した後、急速加熱処理(以下、RTAという、RTAはRapid Thermal Annealingの略)によって、シリコンの露出している部分において高融点金属膜とシリコンとをシリサイド反応させて、自己整合的にサリサイド層20を形成する技術である。このサリサイド形成では、アクティブ領域の半導体基板11(ソース・ドレイン領域18、19)上と配線14上に同時に形成される。なお、絶縁膜であるフィールド絶縁膜12上、スペーサ17表面ではシリサイド化反応は起こらない。その後、シリサイド化反応に寄与しない余剰な高融点金属膜を除去する。

# [0020]

次に、図1(4)に示すように、上記スペーサ17の上部側面17suの曲率を大きくするようにスペーサ17の上部側面の曲率が小さな部分〔前記図1の(2)のスペーサの上部側面17su参照〕を例えばエッチングにより除去するとともに、このエッチングによりスペーサ17の下部側面17sdから垂直面を無くしてスペーサ17の側面全体を90度未満の傾斜面、例えば88度程度の傾斜面とする。これによって、スペーサ17の側面間のアスペクト比を1未満とする。このように、スペーサ17の側面をエッチングすることにより、スペーサ17によるテーパー形状が顕著になるようにする。

# [0021]

上記スペーサ 1 7 の側面の除去加工は、具体的には、平行平板型ドライエッチング装置を用い、エッチングガスには、一例としてトリフルオロメタン( $CHF_3$ )と酸素( $O_2$ )とを用い、それぞれのガスの流量は標準状態において、 $CHF_3$ が 4 5 c m  $^3$  / m i n に設定され、エッチング雰囲気の圧力は 5 . 3 k P a 、基板温度は 2 0 に設定され、スペーサ 1 7 の膜厚換算で 3 n m 程度のエッチングを行うことにより成

30

50

される。上記スペーサ17のエッチングは一例であって、上記エッチング装置およびエッチング条件に限定されるものではなく、スペーサ17を上記所望の形状にエッチングする条件であり、下地との選択比が高い条件であれば如何なる装置、条件であってもよい。

# [0022]

また、上記スペーサ17の側壁を上記説明したごとくエッチング加工することによりテーパー形状にするだけでなく、エッチング量を大目にすることで、スペーサ17の高さを低くして配線14間のアスペクト比を小さくすることもできる。

## [ 0 0 2 3 ]

次いで、上記配線14、スペーサ17等を埋め込むように、半導体基板11上に絶縁膜21を形成する。その際、配線14間はスペーサ17を介して絶縁膜(層間絶縁膜)21によって完全に埋め込む。この絶縁膜21は600 以下の成膜温度で成膜可能なオゾン・ノンドープトガラス(〇3・NSG)を用いることができる。前述した通り、〇3・NSGの成膜はプラズマCVDによる成膜と異なってダメージフリーの優位性があるが、埋め込み領域の形状が少しでもオーバーハング状態に形成されていると完全な埋め込みが原理的にできなくなる特徴を有する。しかさいながら、本実施の形態では、スペーサ17の側面は基板表面に対して90度未満の傾斜面に形成されていることから、また、スペーサ17間のアスペクト比が1未満となっていることから、〇3・NSGの成膜においても配線14間にボイドを発生することなく、完全なる埋め込みができる。

### [0024]

上記製造方法によれば、スペーサ17を形成した後で絶縁膜21を形成する前に、スペーサ17の上部側面17suの曲率を大きくするようにスペーサ17上部の側部を除去することから、スペーサ17の側壁の急峻な傾斜面が緩く形成されることになり、絶縁膜21の埋め込みが容易になる。よって、スペーサ17間の絶縁膜21の埋め込みに際し、ボイドの発生が防止される。

## [0025]

また、上記スペーサ17を形成し、スペーサ17の側面の形状を90度未満の傾斜面に加工した後、配線14間の領域を埋め込む上記絶縁膜21を形成する前に、配線14間の領域を埋め込むことなく配線14およびスペーサ17を被覆する絶縁膜(図示せず)を形成した場合には、配線14間におけるスペーサ17および被覆絶縁膜(図示せず)を介した領域のアスペクト比が1未満であればよい。

### [0026]

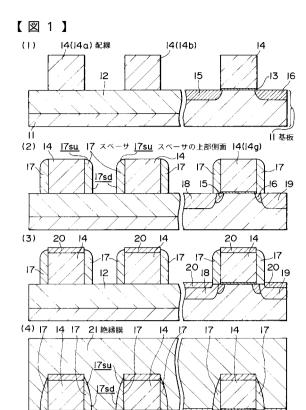

次に、本発明の半導体装置の製造方法に係る第2実施の形態を、図2の製造工程断面図によって説明する。この第2実施の形態では前記第1実施の形態で説明したのと同様なる構成部品には、前記第1実施の形態と同一の符号を付与して説明する。

# [0027]

前記第1実施の形態と同様にして、図2(1)に示すように、通常のMOSトランジスタの形成技術によって、基板(半導体基板)11に対してアクティブ領域を分離する素子分離領域およびフィールド領域となるフィールド絶縁膜12を形成する。上記半導体本をは通常のシリコン基板を用いた。次いで、上記アクティブ領域の基板11上にゲート絶縁膜13を形成する。次いで、ゲート電極およびゲート配線を形成するための導電膜を形成した後、リソグラフィー技術およびゲート配線を配線14という)に加工する。上記半導体を形成した後、リソグラフィー技術およびゲート配線を配線14という)に加工する。上記等で、一下配線(以下、ゲート電極およびゲート配線を配線14という)に加工する。上記等電膜は、例えばポリシリコンにて形成される。このポリシリコン膜の膜厚は、例えば200mmとし、フィールド絶縁膜12上の配線14(14a)とこの配線14aに隣接する配線14(14b)との間隔は、例えば200mmとする。ポリシリコン膜厚は、後に形成されるサリサイドのブリッジング(Bridging)や、ゲート絶縁膜13に与える影響から決められている。配線14間の間隔は配線14の加工限界から決まる。なお、配線14の間隔は実際には設計値よりもやや広く形成される。

### [0028]

次に、アクティブ領域の半導体基板11に低濃度拡散層からなるエクステンション領域

30

40

50

15、16を例えば配線14をマスクにしたイオン注入により形成する。したがって、エクステンション領域15、16は、配線14の側方におけるアクティブ領域の半導体基板11に形成される。またMOSFETの短チャネル効果を抑制するための斜めイオン注入を行う。

# [0029]

その後、図2(2)に示すように、配線14の側部にスペーサ17を形成する。スペーサ17は、配線14を被覆するように、スペーサを形成するための絶縁膜を形成した後、エッチバックによりその絶縁膜をエッチングして配線14の側壁にのみ残すことにより形成される。ここでは、スペーサ17を形成する絶縁膜に窒化シリコン膜171と酸化シリコン膜171と酸化シリコン膜171と酸化シリコン膜171と酸に多のに変化シリコン膜171と酸化シリコン膜171と酸では、スペーサ17の下の膜厚は一例として、窒化シリコン膜171は小さな曲率の曲面となっており、スペーサ17の下部側面17suは小さな曲率の曲面となっており、スペーサ17の下部側一サ17を形成する絶縁膜を2層構造にすることで、第1実施の形態のように変化シリコン膜171をストッパーとして酸化シリコン膜172をエッチング時のまり、窒化シリコン膜171をストッパーとして酸化シリコン膜171をエッチング時にはフィールド絶縁膜12のフィールド酸化膜をできるだけ削らないようにしている。

#### [0030]

また、酸化シリコン膜 / 窒化シリコン膜 / 酸化シリコン膜のように窒化シリコン膜を酸化シリコン膜で挟む構造とすることもできる。この場合には、例えば、上層の酸化シリコン膜を 7 0 n m、中間層の窒化シリコン膜を 2 0 n m、下層の酸化シリコン膜を 1 0 n mの厚さに形成する。これは先に説明した 2 層構造のスペーサと比較すると窒化シリコン膜が配線 1 4 (ゲート電極)に直接に触れることがないため、界面準位の発生を抑えることができ、トランジスタ特性や信頼性的に優位な構造となる。また、窒化シリコン膜のストレスを酸化シリコン膜で緩和させることにもなり、ゲート電極への窒化シリコン膜の応力によるストレスを低減することもできる。

### [ 0 0 3 1 ]

その後は、前記第1実施の形態で説明したのと同様に、ソース・ドレイン領域形成以降の工程を行う。すなわち、配線14およびスペーサ17をマスクにしたイオン注入法によって、アクティブ領域の半導体基板11に上記低濃度拡散層よりも濃度の濃い(高濃度拡散層からなる)ソース・ドレイン領域18、19を形成する。このソース・ドレイン領域18、19を形成する。このソース・ドレイン領域18、19を形成する。このソース・ドレイン領域18、19を介して形成される。ここでスペーサ17は、ソース・ドレイン領域18、19のゲート電極となる配線14(14g)側にエクステンション領域15、16というオフセットをつけることでMOSFETのホットキャリア耐性向上を図るとともに、前記斜めイオン注入によって行われたMOSFETの短チャネル効果抑制領域を残す役割を成す。

# [0032]

次いで、図2(3)に示すように、サリサイド形成を行う。サリサイド形成は、スパッタリングにより配線14が形成されている側の全面に高融点金属膜を被覆形成した後、急速加熱処理(以下、RTAという、RTAはRapid Thermal Annealingの略)によって、シリコンの露出している部分において高融点金属膜とシリコンとをシリサイド反応させて、自己整合的にサリサイド層20を形成する技術である。このサリサイド形成では、アクティブ領域の半導体基板11(ソース・ドレイン領域18、19)上と配線14上に同時に形成される。その後、シリサイド化反応に寄与しない余剰な高融点金属膜を除去する。

### [0033]

次に、図2(4)に示すように、上記スペーサ17の上部側面17suの曲率を大きくするようにスペーサ17の上部側面の曲率が小さな部分〔前記図1の(2)のスペーサの上部側面17su参照〕を例えばエッチングにより除去するとともに、このエッチングに

20

30

40

50

よりスペーサ 1 7 の下部側面 1 7 s d から垂直面を無くしてスペーサの側面 1 7 s 全体を 9 0 度未満の傾斜面、例えば 8 8 度程度の傾斜面とするとともに、スペーサの側面 1 7 s 間のアスペクト比を 1 未満とする。このように、スペーサ 1 7 の側面をエッチングすることにより、スペーサ 1 7 によるテーパー形状が顕著になるようにする。

[0034]

上記スペーサ17の側面の除去加工は、スペーサ17を上記所望の形状にエッチングする条件であり、下地との選択比が高い条件であれば如何なる装置、条件であってもよい。また、上記スペーサ17の側壁を上記説明したごとくエッチング加工することによりテーパー形状にするだけでなく、エッチング量を大目にすることで、スペーサ17の高さを低くして配線14間のアスペクト比を小さくすることもできる。

[0035]

次いで、上記配線14、スペーサ17等を埋め込むように、半導体基板11上に絶縁膜21を形成する。その際、配線14間はスペーサ17を介して絶縁膜(層間絶縁膜)21によって完全に埋め込む。この絶縁膜21は600 以下の成膜温度で成膜可能なオゾン・ノンドープトガラス(〇₃・NSG)を用いることができる。前述した通り、〇₃・NSGの成膜はプラズマCVDによる成膜と異なってダメージフリーの優位性があるが、埋め込み領域の形状が少しでもオーバーハング状態に形成されていると完全な埋め込みが原理的にできなくなる特徴を有する。しかさいながら、本実施の形態では、スペーサ17の側面は基板表面に対して90度未満の傾斜面に形成されていることから、また、スペーサ17間のアスペクト比が1未満となっていることから、〇₃・NSGの成膜においても配線14間にボイドを発生することなく、完全なる埋め込みができる。

[0036]

上記製造方法によれば、スペーサ17を形成した後で絶縁膜21を形成する前に、スペーサ17の上部側面17suの曲率を大きくするようにスペーサ17上部の側部を除去することから、スペーサ17の側壁の急峻な傾斜面が緩く形成されることになり、絶縁膜21の埋め込みが容易になる。よって、スペーサ17間の絶縁膜21の埋め込みに際し、ボイドの発生が防止される。

[0037]

また、上記スペーサ17を形成し、スペーサ17の側面の形状を90度未満の傾斜面に加工した後、配線14間の領域を埋め込む上記絶縁膜21を形成する前に、配線14間の領域を埋め込むことなく配線14およびスペーサ17を被覆する絶縁膜(図示せず)を形成した場合には、配線14間におけるスペーサ17および被覆絶縁膜(図示せず)を介した領域のアスペクト比が1未満であればよい。

[0038]

実際のデバイス作製に適用する場合には、上記説明した第1実施の形態もしくは第2実施の形態を適宜選択して実施することになる。現状では、第2実施の形態のほうが第1実施の形態よりも実際のデバイス形成にあったプロセスにも対応した絶縁膜の埋め込みが可能になる。

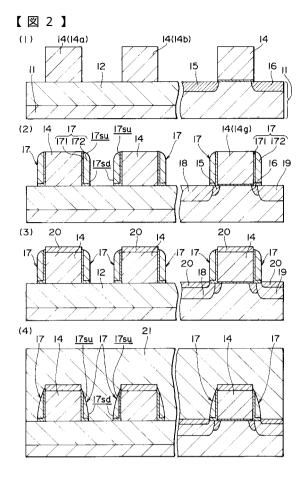

[0039]

次に、本発明の半導体装置の製造方法に係る第3実施の形態を図3の製造工程断面図によって説明する。この第3実施の形態では前記第1実施の形態で説明したのと同様なる構成部品には、前記第1実施の形態と同一の符号を付与して説明する。

[0040]

第3実施の形態は、スペーサ17の側面のエッチング加工を行う前に、イオン注入によりダメージ層を形成することを特徴としている。その他の工程は、前記第1、第2実施の形態で説明したのと同様である。したがって、ここでは、ダメージ層の形成方法について、以下に説明する。なお、スペーサ17は、前記第2実施の形態の構成を用いたが前記第1実施の形態の構成であってもよい。

[ 0 0 4 1 ]

図3(1)に示すように、配線14の側部にスペーサ17を形成し、サリサイドプロセ

20

30

40

50

スを行った後、全面にイオン注入を行ってスペーサ17の表面にダメージ層(図示せず)を形成する。このイオン注入では、シリコンまたはゲルマニウムなどのN型、P型どちらにもならない比較的重いイオンを1×10<sup>15</sup>以上の高いドーズ量でスペーサ17表面のおよそ20nmぐらいの深さの領域に注入する。このように注入するには、例えばイオン注入の注入エネルギーを20keV程度とすればよい。上記ダメージ層の形成によって、スペーサ17の上部側面の曲率が小さな部分のエッチングレートが高くなり、それによって他の部分とのエッチング選択比が高まるので、スペーサ17の上部側面の曲率が小さな部分を制御性よくエッチングすることが可能となり、プロセス的なマージンを広げることができる。

[0042]

その後、図3(2)に示すように、前記第1、第2実施の形態で説明したのと同様にして、上記スペーサ17の上部側面17suの曲率を大きくするようにスペーサ17の上部側面の曲率が小さな部分〔前記図3の(1)のスペーサの上部側面17su参照〕を例えばエッチングにより除去するとともに、このエッチングによりスペーサ17の下部側面17sdから垂直面を無くしてスペーサ17の側面全体を90度未満の傾斜面とする。これによって、スペーサ17の側面間のアスペクト比を1未満とする。このように、スペーサ17の側面をエッチングすることにより、スペーサ17によるテーパー形状が顕著になるようにする。

[0043]

その後、前記第1、第2実施の形態と同様にして、配線14間にスペーサ17を介して 絶縁膜21を埋め込むように形成する。

[0044]

上記各実施の形態で説明したスペーサ17のエッチングは、ドライエッチングの他にスパッタエッチングもしくはウエットエッチングで行うことができる。

[0045]

スパッタエッチングで行う場合には、スパッタエッチング装置を用い、プロセスガスにアルゴン(Ar)を用い、スパッタ出力を300W、エッチング雰囲気の圧力を5.3kPa、基板温度を25 として、スペーサ17の膜厚換算で3nm程度エッチングを行う。このように、アルゴン(Ar)によるスパッタエッチングによって、スペーサ17の上部側面を削り取る。このスパッタエッチングでは、ドライエッチングよりも異方性が高くなり、パワーによっては強力なエッチングが可能となる。

[0046]

ウエットエッチングで行う場合には、ウエットエッチング装置を用い、エッチング液に希フッ酸(HF:H₂〇=1:200の0.5%希フッ酸)を用い、エッチング液温度を25として3nm/min程度の遅いエッチング速度でスペーサ17の膜厚換算で3nm程度エッチングを行ってもよい。なお、上記エッチング液はスペーサ17が酸化シリコン膜で形成されている場合である。また、スペーサ17が窒化シリコン膜の場合には熱リン酸をエッチング液に用いることができる。

[ 0 0 4 7 ]

上記各エッチング技術によって、スペーサ 1 7 の側面の傾斜を 9 0 度未満にしている。この傾斜面は、例えば 8 8 度程度でも絶縁膜 2 1 の埋め込みがボイドを発生することなく良好に行えることが本発明者の実験により確認されている。

[0048]

また、上記説明したように、イオン注入によるダメージ層を形成することにより、ウエットエッチングのような等方性のエッチングでありながらスペーサ17の上部側面のみエッチングレートを早めてエッチングを行うことができる。この場合、先のスパッタエッチングやドライエッチングのようなプラズマもしくはスパッタ雰囲気に下地がさらされることがないため、ゲート酸化膜へのダメージが無い点で有利となる。

[0049]

上記説明した製造方法により、前記図1(4)および前記図2(4)に示したように、

基板 1 1 上に形成された配線 1 4 と、この配線 1 4 の側部に形成されたスペーサ 1 7 と、配線 1 4 間を埋め込むとともに配線 1 4 およびスペーサ 1 7 を被覆するように基板 1 1 上に形成された絶縁膜 2 1 とを備えた半導体装置において、スペーサ 1 7 は、このスペーサ 1 7 の上部側面 1 7 s u の曲率を大きくするようにスペーサ 1 7 の上部側部 1 7 s u が除去されたものからなり、配線 1 4 側部に形成されたスペーサ 1 7 間の絶縁膜 2 1 が埋め込まれる領域はアスペクトが 1 以下となるように形成されている半導体装置を構成することができる。

[0050]

このような半導体装置では、スペーサ17は、スペーサ17の上部側面17suの曲率を大きくするようにスペーサ17上部の側部が除去されたものからなることから、スペーサ17側面の急峻な傾斜面が緩く形成されることになり、絶縁膜21の埋め込みが容易になる。さらに、配線14側部に形成されたスペーサ17間の絶縁膜21が埋め込まれる領域はアスペクトが1以下となるように形成されていることから、絶縁膜21の埋め込みの容易性が高められる。よって、スペーサ17間の絶縁膜21の埋め込みに際し、ボイドの発生が防止されるので、信頼性の高い半導体装置となる。

【産業上の利用可能性】

[0051]

本発明の半導体装置の製造方法および半導体装置は、配線間の絶縁膜の埋め込みを伴う半導体装置に適用でき、例えば半導体メモリ素子、半導体ロジック素子等の半導体装置に適用できる。

【図面の簡単な説明】

[ 0 0 5 2 ]

【図1】本発明の半導体装置の製造方法に係る第1実施の形態を示す製造工程断面図である。

【 図 2 】 本 発 明 の 半 導 体 装 置 の 製 造 方 法 に 係 る 第 2 実 施 の 形 態 を 示 す 製 造 工 程 断 面 図 で ある。

【図3】本発明の半導体装置の製造方法に係る第3実施の形態を示す製造工程断面図である。

【図4】従来の半導体装置の製造方法に係る課題を示す製断面図である。

【符号の説明】

[0053]

1 1 ... 基 板 、 1 4 ... 配 線 、 1 7 ... スペーサ、 1 7 s u ... スペーサの上部側面、 2 1 ... 絶縁膜

20

10

30

# フロントページの続き

(51) Int.CI.<sup>7</sup> F I テーマコード (参考)

H 0 1 L 29/423 H 0 1 L 21/302 1 0 5 B

H 0 1 L 29/49 H 0 1 L 29/78

F ターム(参考) 5F033 HH04 HH25 MM07 QQ09 QQ11 QQ19 QQ25 QQ31 QQ34 QQ35

QQ58 QQ70 QQ82 RR04 RR06 SS04 SS11 TT02 TT08 VV06

WW00 XX02 XX19 XX31 XX33

5F140 AA00 AA08 BA01 BF04 BF11 BF18 BG08 BG09 BG10 BG12

BG14 BG30 BG34 BG37 BG53 BG54 BG56 BG58 BH14 BJ01

BJ08 BK02 BK13 BK22 BK29 BK34 CB01 CC03