### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5066996号 (P5066996)

(45) 発行日 平成24年11月7日(2012.11.7)

(24) 登録日 平成24年8月24日 (2012.8.24)

| (51) Int.Cl. |               |           | FΙ   |       |     |

|--------------|---------------|-----------|------|-------|-----|

| HO4N         | <i>5/3</i> 57 | (2011.01) | HO4N | 5/335 | 570 |

| HO4N         | 5/374         | (2011.01) | HO4N | 5/335 | 740 |

| HO4N         | 5/378         | (2011.01) | HO4N | 5/335 | 780 |

| HO1L         | 27/146        | (2006.01) | HO1L | 27/14 | A   |

請求項の数 17 (全 34 頁)

(21) 出願番号 特願2007-112650 (P2007-112650) (22) 出願日 平成19年4月23日 (2007. 4. 23) (65) 公開番号 特開2008-271278 (P2008-271278A) (43) 公開日 平成20年11月6日 (2008. 11. 6) 審査請求日 平成22年3月8日 (2010. 3. 8)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

|(74)代理人 110000925

特許業務法人信友国際特許事務所

(72)発明者 大池 祐輔

東京都港区港南1丁目7番1号 ソニー株

式会社内

審査官 鈴木 肇

最終頁に続く

(54) [発明の名称] 固体撮像装置、固体撮像装置の信号処理方法および撮像装置

## (57)【特許請求の範囲】

### 【請求項1】

光信号を信号電荷に変換する光電変換部と、当該光電変換部で光電変換された信号電荷を転送する転送素子と、当該転送素子によって転送された信号電荷を出力する出力手段とを含む単位画素が行列状に配置された画素アレイ部と、

一単位の蓄積期間中に前記光電変換部に蓄積された信号電荷を前記転送素子によって少なくとも2回に分割して前記出力手段を介して読み出す駆動手段と、

前記単位画素から分割して読み出された複数の出力信号に対して加算処理を行なう信号処理手段と、

前記<u>複数の出力信号の各々を読み出す度に当該</u>複数の出力信号の各信号レベルを参照レベルと比較するレベル判定手段と、

前記レベル判定手段の判定結果に基づいて、前記複数の出力信号のうち、前記参照レベル以上の信号レベルの出力信号に対して前記加算処理を実行させる制御手段と

を備えた固体撮像装置。

#### 【請求項2】

前記制御手段は、前記複数の出力信号の各信号レベルが前記参照レベルを下回るとき前記加算処理を停止する

請求項1記載の固体撮像装置。

## 【請求項3】

前記制御手段は、前記複数の出力信号の各信号レベルが前記参照レベルを下回るとき、

20

前記出力手段での分割転送による次以降の出力信号に対する前記加算処理を少なくとも 1回停止する

請求項2記載の固体撮像装置。

### 【請求項4】

前記制御手段は、前記複数の出力信号の各信号レベルが前記参照レベル以上になったとき前記加算処理を開始する

請求項1記載の固体撮像装置。

### 【請求項5】

前記制御手段は、前記複数の出力信号の各信号レベルが前記参照レベル以上になったとき、それ以前に読み出された出力信号あるいはその加算結果をリセットする

10

請求項4記載の固体撮像装置。

#### 【請求項6】

前記信号処理手段は、前記複数の出力信号に対してアナログ - デジタル変換処理を行な うアナログ - デジタル変換手段を有する

請求項1記載の固体撮像装置。

#### 【請求項7】

前記制御手段は、前記複数の出力信号の各信号レベルが前記参照レベルを下回るとき前記アナログ・デジタル変換処理を停止する

請求項6記載の固体撮像装置。

## 【請求項8】

20

前記制御手段は、前記複数の出力信号の各信号レベルが前記参照レベル以上になったと き前記アナログ・デジタル変換処理を開始する

請求項6記載の固体撮像装置。

#### 【請求項9】

前記アナログ - デジタル変換手段は、

前記複数の出力信号を参照信号と比較する比較手段と、

前記比較手段の比較結果に応じたカウント値だけカウント動作を行うカウント手段とを 有する

請求項6記載の固体撮像装置。

## 【請求項10】

30

前記アナログ・デジタル変換手段は、前記カウント手段によるカウント動作により、前記アナログ・デジタル変換処理と前記加算処理を並行して実行する

請求項9記載の固体撮像装置。

## 【請求項11】

前記カウント手段は、前記比較手段の比較結果に応じたカウント値だけアップカウント またはダウンカウントする

請求項9記載の固体撮像装置。

### 【請求項12】

前記アナログ・デジタル変換手段は、前記カウント手段によるアップカウントまたはダウンカウントにより、前記単位画素から得られるリセットレベルと信号レベルの差分をとる

40

50

請求項11記載の固体撮像装置。

### 【請求項13】

前記出力手段は、前記転送素子によって転送された信号電荷を電圧に変換する電荷電圧 変換部を有し、

前記電荷電圧変換部は、当該電荷電圧変換部が扱える最大電荷量が前記光電変換部に蓄 積可能な最大電荷量よりも小さくなるように寄生容量が小さく設定されている

請求項1記載の固体撮像装置。

## 【請求項14】

光信号を信号電荷に変換する光電変換部と、当該光電変換部で光電変換された信号電荷

を転送する転送素子と、当該転送素子によって転送された信号電荷を出力する出力手段と を含む単位画素が行列状に配置された画素アレイ部と、

一単位の蓄積期間中に前記光電変換部に蓄積された信号電荷を前記転送素子によって少なくとも2回に分割して前記出力手段を介して読み出す駆動手段とを備え、

前記単位画素から分割して読み出された複数の出力信号に対して加算処理を行なう固体撮像装置の信号処理にあたって、

前記<u>複数の出力信号の各々を読み出す度に当該</u>複数の出力信号の各信号レベルを参照レベルと比較し、

その比較結果に基づいて、前記複数の出力信号のうち、前記参照レベル以上の信号レベルの出力信号に対して前記加算処理を実行する

固体撮像装置の信号処理方法。

#### 【請求項15】

前記複数の出力信号の各信号レベルが前記参照レベルを下回るとき前記加算処理を停止する

請求項14記載の固体撮像装置の信号処理方法。

#### 【請求項16】

前記複数の出力信号の各信号レベルが前記参照レベル以上になったとき前記加算処理を 開始する

請求項14記載の固体撮像装置の信号処理方法。

## 【請求項17】

光信号を信号電荷に変換する光電変換部と、当該光電変換部で光電変換された信号電荷を転送する転送素子と、当該転送素子によって転送された信号電荷を出力する出力手段とを含む単位画素が行列状に配置されてなる固体撮像装置と、

入射光を前記固体撮像装置の撮像面上に結像する光学系とを具備し、

前記固体撮像装置は、

一単位の蓄積期間中に前記光電変換部に蓄積された信号電荷を前記転送素子によって少なくとも2回に分割して前記出力手段を介して読み出す駆動手段と、

前記単位画素から分割して読み出された複数の出力信号に対して加算処理を行なう信号 処理手段と、

前記<u>複数の出力信号の各々を読み出す度に当該</u>複数の出力信号の各信号レベルを参照レベルと比較するレベル判定手段と、

前記レベル判定手段の判定結果に基づいて、前記複数の出力信号のうち、前記参照レベル以上の信号レベルの出力信号に対して前記加算処理を実行させる制御手段とを備えた 撮像装置。

【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、固体撮像装置、固体撮像装置の信号処理方法および撮像装置に関する。

### 【背景技術】

## [0002]

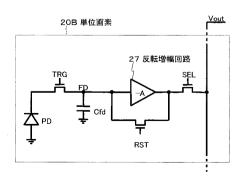

図36に、固体撮像装置の単位画素100の構成の一例を示す。本例のように、光電変換素子101で光電変換された信号電荷を転送する転送トランジスタ102を有する単位画素100では、画素の浮遊拡散容量(FD; Floating Diffusion)106に転送できる最大蓄積電荷量Qfd.maxを、受光部である光電変換素子101の最大蓄積電荷量Qpd.maxよりも十分に大きくすることで、光電変換素子101での電荷残留をなくし完全転送を実現している。

#### [0003]

このようにして、光電変換素子101で光電変換された信号電荷について、完全転送を 実現することで、画像撮影時の残像を防ぎ、また入射光の輝度とセンサ出力信号の良好な 線形性を実現することができる。因みに、本例に係る単位画素100は、転送トランジス 10

20

30

40

タ 1 0 2 に加えて、リセットトランジスタ 1 0 3 、増幅トランジスタ 1 0 4 および画素選択トランジスタ 1 0 5 を有する構成となっている。

### [0004]

しかし、図36に示す単位画素100では、下記の問題点が挙げられる。

(1) 浮遊拡散容量 106の最大蓄積電荷量 Qfd.maxが光電変換素子 101の最大蓄積電荷量 Qpd.maxを上回っている必要があるため、電荷電圧変換効率を高めるための浮遊拡散容量 106を小さくすることに制限がある。

(2) 同様の理由から、浮遊拡散容量 106のリセット電圧として用いられる電源電圧 V d d が下がると浮遊拡散容量 106の最大蓄積電荷量 Q f d.maxが小さくなるため、電源電圧 V d d の低電圧化に制限がある。

[0005]

そこで、従来は、上記(1)~(2)の問題点を次のようにして解決している。すなわち、電荷電圧変換効率を高めるため浮遊拡散容量106を小さくすることで最大蓄積電荷量Qfd.maxが小さいとき、あるいはリセット電圧(電源電圧)Vdddを低電圧化することで最大蓄積電荷量Qfd.maxが小さいときに、電荷転送と、信号の読み出しと、浮遊拡散容量106のリセットを実行した後、光電変換素子101から転送しきれずに残留した電荷を、再度電荷転送して信号を読み出すことで、光電変換素子101に蓄積された電荷を分割して全て読み出すようにしている(例えば、特許文献1参照)。

[0006]

【特許文献 1 】特開 2 0 0 1 - 1 7 7 7 7 5 号公報

【発明の開示】

【発明が解決しようとする課題】

[0007]

しかしながら、上記従来技術のように、電荷を分割して転送し、各々分割転送された信号電荷を出力して無条件に加算するようにしたのでは、特に入射光輝度が低いときに、信号レベルが小さいにもかかわらず、ランダムノイズや固定パターンノイズについては信号レベルが大きいときと同じように加算されることになるため、ランダムノイズや固定パターンノイズが、分割せずに読み出した場合よりも増加し、画質が劣化する。

[0008]

例えば、1回の読み出しにおけるランダムノイズを $N_{RN}$ 、1回の読み出しにおける固定パターンノイズを $N_{FPN}$  とした場合、n回に分割して読み出し、これらを加算したときのノイズは、固定パターンノイズを $N_{FPN}$  のn倍と、ランダムノイズを $N_{RN}$ の n6を、2乗平均したものになる。

[0009]

そこで、本発明は、全ての蓄積電荷を1回の読み出しで出力できない場合に分割して電荷転送および信号出力を行なう構成において、特に入射光輝度が低い領域(低輝度領域)にて高いS/Nを実現可能な固体撮像装置、固体撮像装置の信号処理方法および撮像装置を提供することを目的とする。

【課題を解決するための手段】

[0010]

上記目的を達成するために、本発明は、光信号を信号電荷に変換する光電変換部と、当該光電変換部で光電変換された信号電荷を転送する転送素子と、当該転送素子によって転送された信号電荷を出力する出力手段とを含む単位画素が行列状に配置された画素アレイ部と、一単位の蓄積期間中に前記光電変換部に蓄積された信号電荷を前記転送素子によって少なくとも2回に分割して前記出力手段を介して読み出す駆動手段とを備え、前記単位画素から分割して読み出された複数の出力信号に対して加算処理を行なう固体撮像装置において、前記複数の出力信号の各信号レベルを参照レベルと比較し、その比較結果に基づいて、前記複数の出力信号のうち、前記参照レベル以上の信号レベルの出力信号に対して前記加算処理を実行することを特徴としている。

[0011]

10

20

30

40

光電変換部の全ての蓄積電荷を1回の読み出しで出力できない場合に、蓄積電荷を分割して転送する分割転送による駆動法を用いた固体撮像装置において、分割転送によって単位画素から出力される複数の出力信号の各信号レベルが参照レベルを下回るときは、光電変換部からの電荷転送によって光電変換部が空の状態(あるいは、残りの電荷が少ない状態)にあるか、または、光電変換部にまだ電荷が蓄積されていない状態(あるいは、蓄積電荷が少ない状態)にある。このような状態では、加算処理を停止し、複数の出力信号の各信号レベルが参照レベル以上のときに加算処理を実行することで、特に入射光輝度が低いときに、信号レベルが小さいにもかかわらず、固定パターンノイズやランダムノイズが積算されてしまうようなことがなくなる。

## 【発明の効果】

[0012]

本発明によれば、1回の読み出しで出力できない蓄積電荷を分割して転送する場合において、入射光輝度が低いときに、固定パターンノイズやランダムノイズが積算されてしまわないようにしたことで、特に低輝度側で高いS/Nを実現できるため撮像画像の画質を向上できる。

【発明を実施するための最良の形態】

[0013]

以下、本発明の実施の形態について図面を参照して詳細に説明する。

[0014]

[第1実施形態]

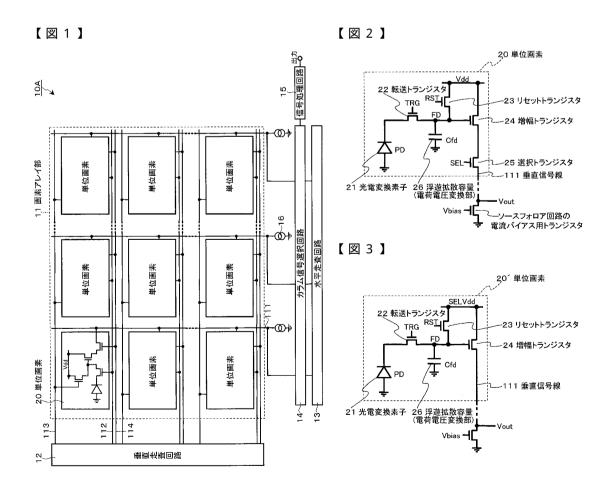

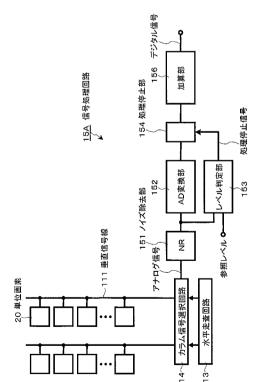

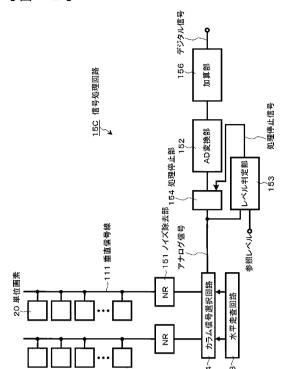

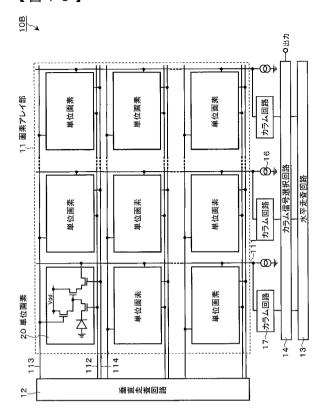

図1は、本発明の第1実施形態に係る固体撮像装置、例えばCMOSイメージセンサの構成を示すシステム構成図である。

[0015]

図1に示すように、本実施形態に係るCMOSイメージセンサ10Aは、光電変換部を含む単位画素(以下、単に「画素」と記述する場合もある)20が行列状に2次元配置されてなる画素アレイ部11と、その周辺回路とを有する構成となっている。画素アレイ部11の周辺回路としては、例えば、垂直走査回路12、水平走査回路13、カラム信号選択回路14および信号処理回路15などが設けられている。

[0016]

画素アレイ部11の画素20の行列状配列に対して、画素列毎に垂直信号線111が配線され、画素行毎に駆動制御線、例えば転送制御線112、リセット制御線113および選択制御線114が配線されている。

[0017]

垂直信号線111の各一端には、定電流源16が接続されている。定電流源16に代えて、例えばバイアス電圧Vbiasでゲートがバイアスされ、後述する増幅トランジスタ24とソースフォロア回路を構成する電流バイアス用トランジスタを用いることも可能である(図2参照)。

[0018]

垂直走査回路12は、シフトレジスタあるいはアドレスデコーダ等によって構成され、画素アレイ部11の各画素20を電子シャッタ行と読み出し行それぞれについて行単位で垂直方向(上下方向)に走査しつつ、電子シャッタ行に対してはその行の画素20の信号掃き捨てを行うための電子シャッタ動作を行うとともに、読み出し行に対してはその行の画素20の信号読み出しを行うための読み出し動作を行う。

[0019]

ここでは、図示を省略するが、垂直走査回路12は、画素20を行単位で順に選択しつつ、読み出し行の各画素20の信号を読み出す読み出し動作を行うための読み出し走査系と、当該読み出し走査系による読み出し走査よりもシャッタ速度に対応した時間分だけ前に同じ行(電子シャッタ行)に対して電子シャッタ動作を行うための電子シャッタ走査系とを有する構成となっている。

[0020]

10

20

40

30

そして、電子シャッタ走査系によるシャッタ走査によって光電変換部の不要な電荷がリセットされたタイミングから、読み出し走査系による読み出し走査によって画素20の信号が読み出されるタイミングまでの期間が、画素20における信号電荷の一単位の蓄積期間(露光期間)となる。すなわち、電子シャッタ動作とは、光電変換部に蓄積された信号電荷のリセット(掃き捨て)を行い、そのリセット後から新たに信号電荷の蓄積を開始する動作である。

#### [0021]

水平走査回路13は、シフトレジスタあるいはアドレスデコーダ等によって構成され、画素アレイ部11の各画素列を順に水平走査する。カラム信号選択回路14は、水平選択スイッチや水平信号線等によって構成され、画素アレイ部11から画素行毎に垂直信号線111を通して出力される画素20の信号を、水平走査回路13による水平走査に同期して順次出力する。

#### [0022]

信号処理回路15は、カラム信号選択回路14から画素単位で出力される画素20の信号に対して、ノイズ除去、AD(アナログ・デジタル)変換、加算処理などの各種の信号処理を実行する。本実施形態では、この信号処理回路15の構成および動作を特徴としており、その詳細については後述する。

#### [0023]

なお、垂直走査回路 1 2、水平走査回路 1 3 および信号処理回路 1 5 等の動作の基準となるタイミング信号や制御信号は、図示せぬタイミング制御回路で生成される。

#### [0024]

### (画素回路)

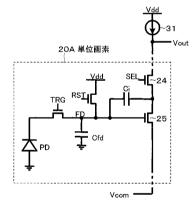

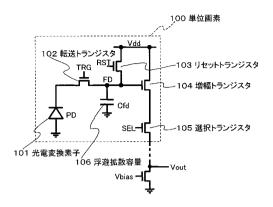

図2は、単位画素20の回路構成の一例を示す回路図である。本回路例に係る単位画素20は、埋め込み型フォトダイオード等の光電変換素子(光電変換部)21に加えて、例えば転送トランジスタ(転送素子)22、リセットトランジスタ23、増幅トランジスタ24および選択トランジスタ25の4つのトランジスタを有する画素回路となっている。ここでは、これらトランジスタ22~25として、例えばNチャネルのMOSトランジスタを用いているが、これに限られるものではない。

### [0025]

転送トランジスタ22は、光電変換素子21のカソード電極と浮遊拡散容量(FD)26との間に接続され、光電変換素子21で光電変換され、ここに蓄積された信号電荷(ここでは、電子)を、ゲート電極(制御電極)に転送パルスTRGが与えられることによって浮遊拡散容量26に転送する。浮遊拡散容量26は、信号電荷を電圧信号に変換する電荷電圧変換部として機能する

# [0026]

リセットトランジスタ23は、電源電圧Vddの画素電源にドレイン電極が、浮遊拡散容量26にソース電極がそれぞれ接続され、光電変換素子21から浮遊拡散容量26への信号電荷の転送に先立って、ゲート電極にリセットパルスRSTが与えられることによって浮遊拡散容量26の電位をリセット電圧Vrstにリセットする。

#### [0027]

増幅トランジスタ24は、浮遊拡散容量26にゲート電極が、電源電圧Vddの画素電源にドレイン電極がそれぞれ接続され、リセットトランジスタ23によってリセットされた後の浮遊拡散容量26の電位をリセットレベルとして出力し、さらに転送トランジスタ22によって信号電荷が転送された後の浮遊拡散容量26の電位を信号レベルとして出力する。

# [0028]

選択トランジスタ25は、例えば、ドレイン電極が増幅トランジスタ24のソース電極に、ソース電極が垂直信号線111にそれぞれ接続され、ゲート電極に選択パルスSELが与えられることによってオン状態となり、画素20を選択状態として増幅トランジスタ24から出力される信号を垂直信号線111に出力する。選択トランジスタ25について

10

20

30

40

は、画素電源(Vdd)と増幅トランジスタ24のドレイン電極との間に接続した構成を採ることも可能である。

### [0029]

なお、ここでは、転送トランジスタ22、リセットトランジスタ23、増幅トランジスタ24および選択トランジスタ25を有する4トランジスタ構成の単位画素20を有するCMOSイメージセンサに適用する場合を例に挙げたが、この適用例に限られるものではない。

## [0030]

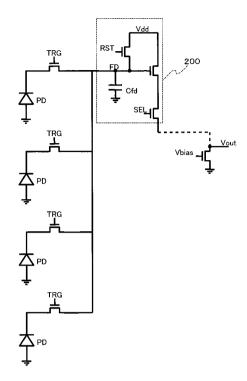

具体的には、図3に示すように、選択トランジスタ25を省略し、電源電圧SELVddを可変とすることにより、増幅トランジスタ24に選択トランジスタ25の機能を持たせた3トランジスタ構成の単位画素20を有するCMOSイメージセンサや、図4に示すように、浮遊拡散容量FDや読み出し回路200を複数の画素で共有した構成を採るCMOSイメージセンサなどにも適用可能である。

## [0031]

上記構成の C M O S イメージセンサ 1 0 A において、単位画素 2 0 の各構成素子(転送トランジスタ 2 2、リセットトランジスタ 2 3 および選択トランジスタ 2 5 ) を駆動する垂直走査回路 1 2 は、一単位の蓄積期間中に光電変換素子 2 1 に蓄積された信号電荷を転送トランジスタ 2 2 によって少なくとも 2 回に分割して、出力手段(リセットトランジスタ 2 3、浮遊拡散容量 2 6、増幅トランジスタ 2 4 および選択トランジスタ 2 5 )を介して読み出す駆動手段を構成している。

#### [0032]

### (分割転送)

上記構成のCMOSイメージセンサ10Aでは、垂直走査回路12から適宜出力される転送パルスTRG、リセットパルスRSTおよび選択パルスSELによる駆動の下に、一単位の蓄積期間中に光電変換素子21に蓄積された光電荷を少なくとも2回に分割して浮遊拡散容量26に転送(分割転送)し、増幅トランジスタ24を通して垂直信号線111に読み出す動作が画素行単位で行われる。そして、分割転送にて単位画素20から読み出された複数の信号は、後段の信号処理回路15において加算処理される。

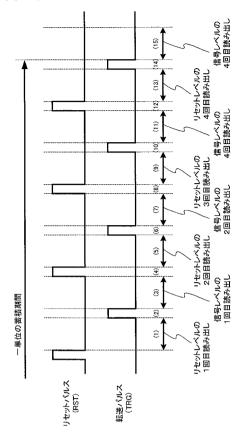

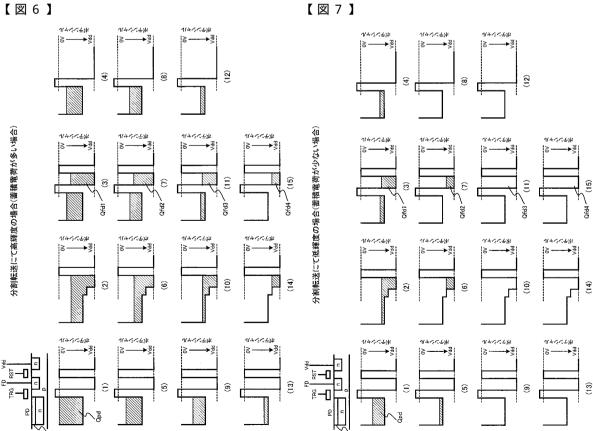

### [0033]

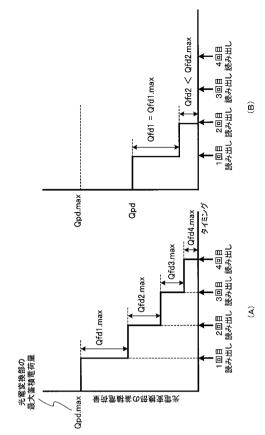

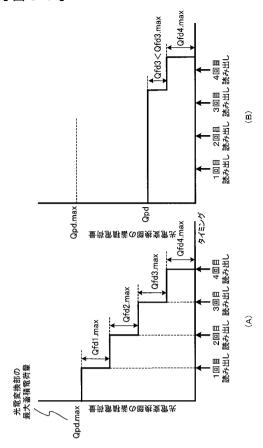

ここで、一例として、4分割にて分割転送を行なう場合のリセットパルスRSTおよび 転送パルスTRGのタイミング関係を図5に示す。また、図6に入射光輝度が高い場合の 動作説明図を、図7に入射光輝度が低い場合の動作説明図をそれぞれ示す。図6および図 7において、各動作(1)~(15)は図5の各期間(1)~(15)に対応している。

#### [0034]

4分割にて電荷転送を行い、それぞれの電荷転送で読み出された電荷 Q f d 1 , Q f d 2 , Q f d 3 , Q f d 4 を加算して、蓄積電荷 Q p d (= Q f d 1 + Q f d 2 + Q f d 3 + Q f d 4)を得るとき、入射光輝度が高く、光電変換素子 2 1 の蓄積電荷が多い画素においては、図 6 に示すように、4分割して加算することで全蓄積電荷 Q p dを読み出すことが可能である。

## [0035]

### <分割転送での問題点>

一方で、入射光輝度が低く、光電変換素子21の蓄積電荷が少ない画素においては、図7に示すように、最初の数回(本例では、2回)の転送で全蓄積電荷Qpdが読み出されてしまい、残りの転送(本例では、2回)においては、出力すべき信号電荷がない状態となっている。

## [0036]

その結果、特に入射光輝度が低い(低輝度<u>の)</u>場合に、信号レベルが小さいにもかかわらず、ランダムノイズや固定パターンノイズについては信号レベルが大きいときと同じように加算されることになるため、ランダムノイズや固定パターンノイズが、分割せずに読み出した場合よりも増加し、画質が劣化する。

## [0037]

50

40

20

10

30

### < 本実施形態の特徴部分 >

これに対して、本実施形態に係るCMOSイメージセンサ10Aでは、参照レベル以上のときに加算処理あるいはAD変換処理を実行し、分割された各々の転送の最大値、即ち1回目で転送できる最大電荷量Qfd1.max、2回目で転送できる最大電荷量Qfd2.max、……を下回る出力が得られたときに、全ての蓄積電荷Qpdの読み出しが完了したと判定して、次以降の加算処理あるいはAD変換処理を停止する制御を行なうことを特徴としている。

## [0038]

各々の最大値Qfd.maxは、図8(A)に示すように、光電変換部(光電変換素子21)が扱える最大電荷量Qpd.maxを分割転送した際に転送される電荷量となる。

[0039]

例えば、Qpd > Qfd1.max 、かつ、Qpd < Qfd1.max + Qfd2.max であった場合、図 8 (B)に示すように、1回目の読み出しにてQfd1 (= Qfd1.max)の電荷が読み出され、2回目の読み出しにて残りのQfd2 (= Qpd - QQfd1)の電荷が読み出される。

#### [0040]

Qfd2 < Qfd2.maxであることを後述するレベル判定部にて判定し、次以降の3回目、4回目の加算処理あるいはAD変換処理を停止する。これにより、Qfd1 + Qfd2 が加算されたQpdを読み出すことができ、かつ、3回目、4回目にてノイズ成分が加算されてしまうのを回避することができる。

## [0041]

< 本実施形態の作用効果 >

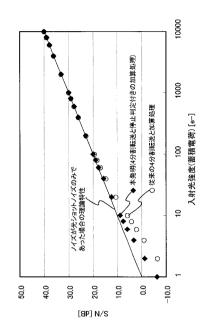

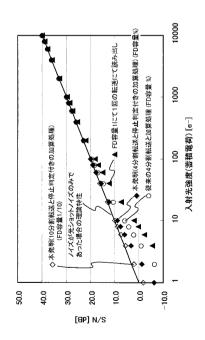

図9に、本実施形態の効果例を示す。光電変換部の最大蓄積電荷量を10,000電子とした場合の蓄積電荷とS/N(dB)の関係を示している。なお、一般的に、最大蓄積電荷量に達するまでは蓄積電荷は入射光強度に比例する。

#### [0042]

ここでは、読み出しの固定パターンノイズを 2 e - 相当、読み出しのランダムノイズを 7 e - 相当、そして蓄積電荷に応じた光ショットノイズをノイズ成分として含めている。 光ショットノイズは蓄積電荷の平方根で発生すると一般的に知られている。また、図 9 には、ノイズ成分が光ショットノイズのみであった場合の理論特性を直線で示している。

## [0043]

従来の4分割転送と加算処理においては、蓄積電荷が小さくても読み出しの固定パターンノイズとランダムノイズが分割数に応じて加算されるため、図9に示すように特性劣化が著しい。

## [0044]

一方で、本実施形態に係るCMOSイメージセンサ10Aにおいては、低輝度であった場合には読み出しに必要な回数分のみの加算処理しか実行されないため、読み出しの固定パターンノイズやランダムノイズの影響が小さく、特に低輝度側で高いS/Nを実現し、画質を向上できる。

## [0045]

以下に、1回目で転送できる最大電荷量Qfd1.max、2回目で転送できる最大電荷量Qfd2.max、……を下回る出力が得られたときに、全ての蓄積電荷Qpdの読み出しが完了したと判定し、次以降の加算処理あるいはAD変換処理を停止する制御を行なう信号処理回路15の具体的な実施例について説明する。

## [0046]

### (実施例1)

図10は、実施例1に係る信号処理回路15Aの構成の一例を示すブロック図である。本実施例1に係る信号処理回路15Aは、ノイズ除去部151、AD変換部152、レベル判定部153、処理停止部154および加算部156を有する構成となっている。

### [0047]

ノイズ除去部151は、例えばCDS(Correlated Double Sampling;相関二重サンプリ

20

10

30

30

50

ング) 回路からなり、単位画素 2 0 から順次供給されるリセットレベルと信号レベルの差分を順にとることにより、リセットノイズや増幅トランジスタ 2 4 の閾値ばらつき等の画素固有の固定パターンノイズを除去する。

#### [0048]

分割して転送され、ノイズ除去部151でノイズ除去されたアナログの出力信号は、AD変換部152およびレベル判定部153に供給される。AD変換部152は、アナログの出力信号をデジタル信号にAD変換する。

### [0049]

レベル判定部 1 5 3 は、ノイズ除去後の信号レベルを参照レベルと比較し、信号レベルが参照レベルを下回るときに判定結果を出力し、当該判定結果を処理停止信号として処理停止部 1 5 4 に与える。レベル判定部 1 5 3 の具体的な構成については後述する。参照レベルは、1回目で転送できる最大電荷量 Q fd1.max 、 2 回目で転送できる最大電荷量 Q fd 2.max 、 ......に対応して設定される。

## [0050]

処理停止部154は、レベル判定部153から判定結果が与えられたときに、AD変換部152から出力される分割転送に伴うデジタル信号に対する加算部156での加算処理を停止する。処理停止部154による加算処理の停止手法としては、加算部156への入力を0とする、加算部156の制御信号あるいはクロックを止める、加算部156がイネーブル信号に応答して加算処理を行なう構成の場合は当該イネーブル信号の供給を停止する、などの手法が考えられる。

#### [0051]

加算部 1 5 6 は、処理停止部 1 5 4 によって加算処理が停止されているときは加算処理を停止する(0 を加算する場合も加算処理の停止の概念に含むものとする)が、それ以外は、分割転送に伴って A D 変換部 1 5 2 から順次供給されるデジタル信号を加算処理して1 画素の画素信号として出力する。

### [0052]

上記構成の信号処理回路15Aにおいて、ノイズ除去部151、AD変換部152、レベル判定部153、処理停止部154および加算部156は、例えば、画素アレイ部11と同じ半導体基板に集積される。

## [0053]

ただし、ノイズ除去部151、AD変換部152、レベル判定部153、処理停止部154および加算部156の全てが画素アレイ部11と同じ半導体基板に集積されている必要はなく、いずれか、あるいは全てが別の半導体基板に集積されていても構わない。

## [0054]

### (実施例2)

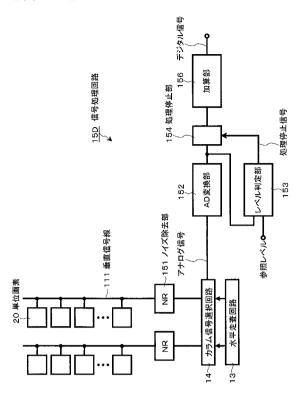

図11は、実施例2に係る信号処理回路15Bの構成の一例を示すブロック図であり、図中、図10と同等部分には同一符号を付して示している。

### [0055]

本実施例2に係る信号処理回路15Bは、AD変換部152、レベル判定部153、処理停止部154および加算部156を有する構成となっている。そして、本実施例2においては、ノイズ除去部151については、画素アレイ部11の画素列毎に並列に搭載した構成を採っている。

### [0056]

ここでは、ノイズ除去部 1 5 1 を画素列毎に並列に搭載するとしたが、AD変換部 1 5 2、レベル判定部 1 5 3、処理停止部 1 5 4 および加算部 1 5 6 のいずれかあるいは全てを画素列毎に並列に搭載する構成を採ることも可能である。

#### [0057]

## (実施例3)

図12は、実施例3に係る信号処理回路15Cの構成の一例を示すブロック図であり、 図中、図10と同等部分には同一符号を付して示している。 10

20

30

40

#### [0058]

本実施例3に係る信号処理回路15Cは、処理停止部154をAD変換部152の前段側に配置し、レベル判定部153からその判定結果が処理停止信号として処理停止部154に与えられたときに、当該処理停止部154によってAD変換部152のAD変換処理を停止する構成を採っている。

#### [0059]

処理停止部154によるAD変換処理の停止手法としては、AD変換部152への入力を0とする、AD変換部152の制御信号あるいはクロックを止める、AD変換部152がイネーブル信号に応答して加算処理を行なう構成の場合は当該イネーブル信号の供給を停止する、などの手法が考えられる。

[0060]

なお、実施例1の場合と同様に、ノイズ除去部151を信号処理回路15C内に配置する構成を採っても良いことは勿論である。

[0061]

(実施例4)

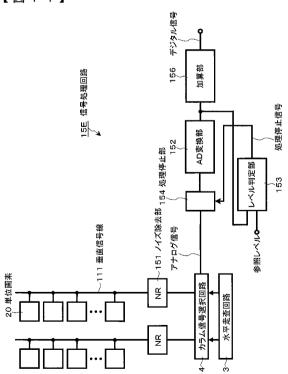

図13は、実施例4に係る信号処理回路15Dの構成の一例を示すブロック図であり、 図中、図10と同等部分には同一符号を付して示している。

[0062]

本実施例4に係る信号処理回路15Dは、AD変換部152によるAD変換後のデジタル値に対してレベル判定部153が参照レベルと比較する構成を採っている。そして、実施例1の場合と同様に、レベル判定部153からその判定結果が処理停止信号として処理停止部154に与えられたときに、当該処理停止部154によって加算部156での加算処理を停止するようにしている。

[0063]

処理停止部154による加算処理の停止手法としては、実施例1の場合と同様に、加算部156への入力を0とする、加算部156の制御信号あるいはクロックを止める、加算部156がイネーブル信号に応答して加算処理を行なう構成の場合は当該イネーブル信号の供給を停止する、などの手法が考えられる。

[0064]

なお、実施例1の場合と同様に、ノイズ除去部151を信号処理回路15C内に配置する構成を採っても良いことは勿論である。

[0065]

(実施例5)

図14は、実施例5に係る信号処理回路15Eの構成の一例を示すブロック図であり、図中、図10と同等部分には同一符号を付して示している。

[0066]

本実施例 5 に係る信号処理回路 1 5 E は、レベル判定部 1 5 3 が A D 変換部 1 5 2 による A D 変換後のデジタル値を参照レベルと比較するとともに、処理停止部 1 5 4 を A D 変換部 1 5 2 の前段側に配置し、レベル判定部 1 5 3 からその判定結果が処理停止信号として処理停止部 1 5 4 に与えられたときに、分割転送されて読み出される次以降のいずれかあるいは全ての出力信号に対して、処理停止部 1 5 4 によって A D 変換部 1 5 2 の A D 変換処理を停止する構成を採っている。

[0067]

処理停止部 1 5 4 による A D 変換処理の停止手法としては、実施例 3 の場合と同様に、A D 変換部 1 5 2 への入力を 0 とする、A D 変換部 1 5 2 の制御信号あるいはクロックを止める、A D 変換部 1 5 2 がイネーブル信号に応答して加算処理を行なう構成の場合は当該イネーブル信号の供給を停止する、などの手法が考えられる。

[0068]

なお、実施例1の場合と同様に、ノイズ除去部151を信号処理回路15C内に配置する構成を採っても良いことは勿論である。

10

20

30

40

#### [0069]

上述したように、光電変換素子21の全ての蓄積電荷を1回の読み出しで出力できない場合に、分割して電荷転送および信号出力を行なうCMOSイメージセンサ10Aにおいて、分割転送によって単位画素20から出力される信号を加算する際に、参照レベル以上のときに加算処理を実行し、参照レベルを下回ったときには光電変換素子21の蓄積電荷が全て読み出されている状態(あるいは、残りの電荷が少ない状態)にあることから、それ以降の読み出しにおいて加算処理を停止することで、特に入射光輝度が低いときに、読み出しに必要な回数分のみの加算処理しか実行されず、読み出しの固定パターンノイズやランダムノイズが積算されることがないため、固定パターンノイズやランダムノイズの影響が小さく、特に低輝度側で高いS/Nを実現し、撮像画像の画質を向上できる。

[0070]

また、参照レベルについては、先述したとおり、該当するn回目の読み出しにおいて転送できる最大電荷量 Q f dn.max であり、出力信号が最大電荷量 Q f dn.max 以下であれば処理停止信号が発生する。ただし、画素の特性ばらつきなどを考慮して、あるマージン Q を設定し、最大電荷量 Q f dn.max よりも低い Q f dn.max - Q を参照レベルとして設定することが好ましい。

### [0071]

上記実施例1乃至実施例5に係る信号処理回路15A乃至15Eにおいて、処理停止部154は、レベル判定部153の判定結果に基づいて、分割転送によって単位画素20から読み出される複数の出力信号のうち、参照レベル以上の信号レベルの出力信号に対して加算処理を実行させる、具体的には、複数の出力信号の各信号レベルが参照レベル以上のときに加算処理を実行させ、参照レベルを下回るとき加算処理を停止する制御手段を構成している。

[0072]

なお、上記実施例1乃至実施例5では、複数の出力信号の各信号レベルが参照レベルを下回るとき、次以降の出力信号に対する加算処理を全て停止する場合を例に挙げて説明したが、次以降の出力信号に対する加算処理を少なくとも1回停止するだけでも、そのときの固定パターンノイズやランダムノイズが積算されないことになるため、固定パターンノイズやランダムノイズの影響を抑えることができる。

[0073]

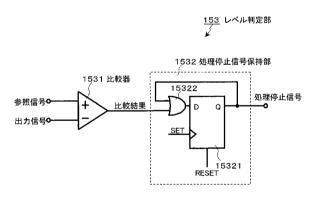

(レベル判定部)

図15は、レベル判定部153の構成の一例を示すブロック図である。ここでは、アナログ信号に対するレベル判定の場合を例に挙げている。

[0074]

本例に係るレベル判定部 1 5 3 は、レベル比較器 1 5 3 1 と処理停止信号保持部 1 5 3 2 によって構成されている。

[0075]

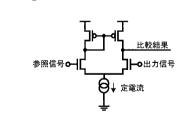

レベル比較器 1 5 3 1 は、例えば図 1 6 に示すような差動増幅回路によって構成され、分割して転送された出力信号を反転 ( - )入力、参照信号を非反転 ( + )入力とし、出力信号と参照信号の大小比較を実行し、その比較結果を処理停止信号として出力する。

[0076]

処理停止信号保持部 1 5 3 2 は、 D型フリップフロップからなるラッチ回路 1 5 3 2 1 と、レベル比較器 1 5 3 1 の比較結果である処理停止信号とラッチ回路 1 5 3 2 1 の Q 出力とを 2 入力とし、その出力をラッチ回路 1 5 3 2 1 の D 入力とする論理輪回路 1 5 3 2 2 によって構成されている。

[0077]

このレベル判定部 1 5 3 は、レベル比較器 1 5 3 1 での比較によって処理停止信号が発生した次以降の読み出しにおいても引き続き処理停止をしたい場合に対応した回路構成となっている。次以降の読み出しでは、処理停止を行なわない場合には、処理停止信号を保持する処理停止信号保持部 1 5 3 2 を省略すればよいことになる。

10

20

30

40

#### [0078]

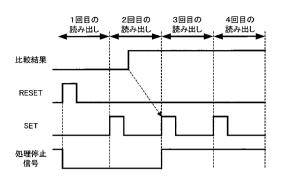

上記構成のレベル判定部 1 5 3 の回路動作について、図 1 7 のタイミングチャートを用いて説明する。

#### [0079]

リセット信号RESETによりラッチ回路15321がリセットされることで、そのQ出力である処理停止信号が低レベル(以下、"L"レベルと記す)になる。次に、レベル比較器1531の比較結果が高レベル(以下、"H"レベルと記す)になると、ラッチ回路15321は次のセット信号SETによって"H"レベルの比較結果を保持し、リセット信号RESETが入力されるまで比較結果によらず保持し続ける。

#### [0800]

図15の回路例の場合、2回目の読み出しで処理停止信号が"H"レベルとなっているため、3回目や4回目読み出しでのレベル比較器1531の比較結果が"L"レベルであっても、処理停止信号は"H"レベルのままとなる。

## [0081]

また、レベル比較器1531の比較結果が"H"レベルとなる2回目の読み出しから加算を停止させるような即時反映としたい場合は、比較結果と処理停止信号の論理和をとってもよい。

#### [0082]

なお、ここでは、アナログ信号に対するレベル判定の場合を例に挙げて説明したが、デジタル信号に対するレベル判定の場合は、単純な引き算を実行する方法や、デジタル信号の bit幅のある桁が 1 あるいは 0 である、といった判定方法や、AD変換中にある桁が 1 または 0 となる、といった判定方法など、参照レベルの分解能によって大小比較できるものであればいずれでも構わない。

#### [0083]

#### 「第2実施形態]

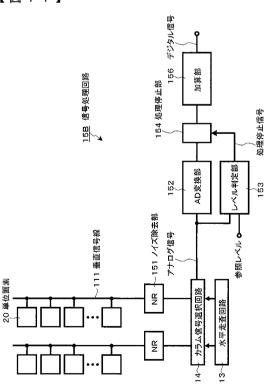

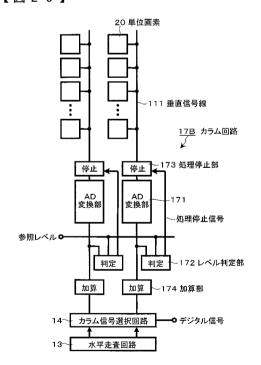

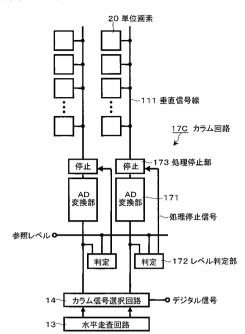

図18は、本発明の第2実施形態に係る固体撮像装置、例えばCMOSイメージセンサの構成を示すシステム構成図であり、図中、図1と同等部分には同一符号を付して示している。

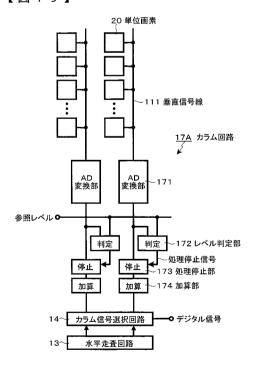

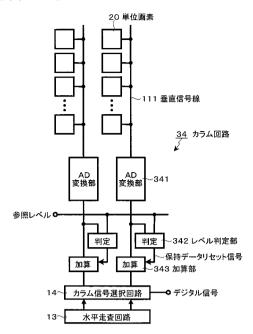

### [0084]

図18に示すように、本実施形態に係るCMOSイメージセンサ10Bは、画素アレイ部11、垂直走査回路12、水平走査回路13およびカラム信号選択回路14に加えて、画素アレイ部11の画素列毎に配置された複数のカラム回路17を有し、当該カラム回路17において、画素アレイ部11から垂直信号線111を通して画素単位で出力される画素20の信号に対して、ノイズ除去、AD変換、加算処理などの各種の信号処理を実行する構成となっており、それ以外の構成については第1実施形態に係るCMOSイメージセンサ10Aと基本的に同じである。

## [0085]

本実施形態に係るCMOSイメージセンサ10Bにおいても、第1実施形態に係るCMOSイメージセンサ10Aと同様に、参照レベル以上のときに加算処理あるいはAD変換処理を実行し、分割された各々の転送の最大値、即ち1回目で転送できる最大電荷量Qfd1.max、2回目で転送できる最大電荷量Qfd2.max、.....を下回る出力が得られたときに、全ての蓄積電荷Qpdの読み出しが完了したと判定して、次以降の加算処理あるいはAD変換処理を停止する制御が行なわれる。この制御は、カラム回路17で実行される。

## [0086]

以下に、1回目で転送できる最大電荷量Qfd1.max、2回目で転送できる最大電荷量Qfd2.max、……を下回る出力が得られたときに、全ての蓄積電荷Qpdの読み出しが完了したと判定し、次以降の加算処理あるいはAD変換処理を停止する制御を行なうカラム回路17の具体的な実施例について説明する。

### [0087]

(実施例1)

10

30

20

40

図19は、実施例1に係るカラム回路17Aの構成の一例を示すブロック図である。本実施例1に係るカラム回路17Aは、AD変換部171、レベル判定部172、処理停止部(制御手段)173および加算部174を有する構成となっている。ここでは図示を省略するが、AD変換部171の前段側に、図10のノイズ除去部151に相当するノイズ除去部を設けた構成を採ることも可能である。

#### [0088]

A D 変換部 1 7 1 は、画素アレイ部 1 1 から垂直信号線 1 1 1 を通して供給される、分割して転送されたアナログの出力信号をデジタル信号に A D 変換する。レベル判定部 1 7 2 は、 A D 変換部 1 7 1 による A D 変換後のデジタル値を参照レベルと比較し、当該デジタル値が参照レベルを下回るときに判定結果を出力し、当該判定結果を処理停止信号として処理停止部 1 5 4 に与える。参照レベルは、1回目で転送できる最大電荷量 Q fd1.max、2回目で転送できる最大電荷量 O fd2.max、……に対応して設定される。

#### [0089]

処理停止部173は、レベル判定部172から判定結果が与えられたときに、AD変換部171から出力される分割転送に伴うデジタル信号に対する加算部174での加算処理を停止する。処理停止部173による加算処理の停止手法としては、加算部174への入力を0とする、加算部174の制御信号あるいはクロックを止める、加算部174がイネーブル信号に応答して加算処理を行なう構成の場合は当該イネーブル信号の供給を停止する、などの手法が考えられる。

### [0090]

加算部174は、処理停止部173によって加算処理が停止されているときは加算処理を停止する(0を加算する場合も加算処理の停止の概念に含むものとする)が、それ以外は、分割転送に伴ってAD変換部171から順次供給されるデジタル信号を加算処理して1画素の画素信号として出力する。

#### [0091]

### (実施例2)

図 2 0 は、実施例 2 に係るカラム回路 1 7 B の構成の一例を示すブロック図であり、図中、図 1 9 と同等部分には同一符号を付して示している。

### [0092]

本実施例 2 に係るカラム回路 1 7 B は、レベル判定部 1 5 3 が A D 変換部 1 5 2 による A D 変換後のデジタル値を参照レベルと比較するとともに、処理停止部 1 7 3 を A D 変換部 1 7 1 の前段側に配置し、レベル判定部 1 7 2 からその判定結果が処理停止信号として処理停止部 1 7 3 に与えられたときに、分割転送されて読み出される次以降のいずれかあるいは全ての出力信号に対して、処理停止部 1 7 3 によって A D 変換部 1 7 1 の A D 変換処理を停止する構成を採っている。

### [0093]

処理停止部 1 7 3 による A D 変換処理の停止手法としては、 A D 変換部 1 7 1 への入力を 0 とする、 A D 変換部 1 7 1 の制御信号あるいはクロックを止める、 A D 変換部 1 7 1 がイネーブル信号に応答して加算処理を行なう構成の場合は当該イネーブル信号の供給を停止する、などの手法が考えられる。

## [0094]

#### (実施例3)

図 2 1 は、実施例 3 に係るカラム回路 1 7 C の構成の一例を示すブロック図であり、図中、図 1 9 と同等部分には同一符号を付して示している。

#### [0095]

本実施例3に係るカラム回路17Cは、実施例2に係るカラム回路17Bにおいて、AD変換部171がAD変換機能に加えて、ノイズ除去(CDS)機能と加算機能を持つ構成となっている。

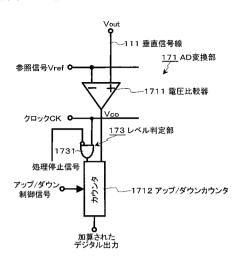

### [0096]

< A D 変換部および処理停止部 >

20

10

30

40

図 2 2 は、 A D 変換部 1 7 1 および処理停止部 1 7 3 の具体的な構成の一例を示すプロック図である。

#### [0097]

図22に示すように、本例に係るAD変換部171は、電圧比較器1711とカウンタ1712によって構成されている。また、本例に係る処理停止部173は、論理積回路1731によって構成されている。

#### [0098]

電圧比較器1711は、ランプ(RAMP)波形の参照信号Vrefを反転(・)入力とし、垂直信号線111を通して供給される単位画素20の出力信号Voutを非反転(+)とし、出力信号Voutが参照信号Vrefよりも大きいときに比較結果Vcoを出力する。

#### [0099]

カウンタ1712はアップ / ダウンカウンタからなり、電圧比較器1711の比較結果 Vcoが遷移するまでの期間、アップ / ダウン制御信号による制御の下に、クロックCK に同期してアップカウント / ダウンカウントのカウント動作を行なうことにより、カウント値を増減する。

#### [0100]

より具体的には、リセットレベルを読み出すときはダウンカウントによってカウント値を減じ、信号レベルを読み出すときはアップカウントによってカウント値を増やす。これにより、リセットレベルと信号レベルの差分を得るノイズ除去処理をAD変換と同時に実行することができる。

#### [0101]

さらに、1回目のAD変換結果から引き続き、2回目のリセットレベル、信号レベルのAD変換を同様に実行すると、カウント値は1回目と2回目の和となり、よって加算処理も同時に実行することができる。

### [0102]

なお、カウンタ1712においては、必ずしもリセットレベルをダウンカウントする必要はなく、リセットレベルをアップカウントしておき、信号レベルの読み出し直前に1を加えて反転させて負の値として扱い、信号レベルも同様にアップカウントするようにしても構わない。

### [0103]

他にも、リセットレベルの読み出しにおける総カウント値がN、リセットレベルの値に相当するカウント値がNsig のとき、比較結果Vcoが遷移してから総カウント値Nが終わるまでのカウント値N・Nsig をカウントし、さらに信号レベルの値に相当するカウント値Msig をカウントし、N・Nsig ・Msig として出力した上で、最終的に既知である総カウント値Nを引き算して、ノイズ除去後の信号出力Msig・Nsig を得るようにしても構わない。

### [0104]

論理積回路1731は、クロックCKを一方の入力とし、レベル判定部172から出力される処理停止信号を負論理の他方の入力とし、レベル判定部172から処理停止信号が与えられているときは、カウンタ1712へのクロックCKの入力を停止することで、カウンタ1712のカウント動作、即ちAD変換部171のAD変換処理、ノイズ除去処理および加算処理を停止させる。

## [0105]

続いて、上記構成のAD変換部341、即ちノイズ除去機能と加算機能を持つAD変換部341の動作タイミングについて、図23のタイミングチャートを用いて説明する。ここでは、図8(B)に示すように、最初の2回で全電荷が読み出される場合を例に挙げて説明するものとする。

### [0106]

レベル判定部172でのレベル判定はAD変換および加算処理が為された信号に対して

10

20

30

50

実行される。したがって、参照レベルについては、各分割された読み出し転送の最大電荷量 Qfd1.max, Qfd2.max,……を累積加算したものを、それぞれの読み出しにおける参照レベルとする。

### [0107]

図 2 3 の例では、前述したとおり、画素の特性バラツキなどに対する余裕として Q のマージンを取り、1 回目の読み出しに対する参照レベルを Q fd1.max - Q 、 2 回目の読み出しに対する参照レベルを Q fd1.max + Q fd2.max - Q 、以降同様としている。

### [0108]

信号レベルの読み出しが完了したタイミングで参照レベルとの比較を実行し、2回目の読み出しにて処理停止信号が発生し、3回目の読み出し以降のAD変換が停止している。そのため、1回目の読み出し結果と2回目の読み出し結果のみを加算した値がAD変換および加算処理の出力として得られる。

#### [0109]

なお、上記実施例 1 , 2 , 3 では、レベル判定部 1 7 2 が A D 変換器 1 7 1 の後段側においてデジタル値を参照レベルと比較するとしたが、D 変換器 1 7 1 の前段側において、アナログ値を参照レベルと比較する構成を採ることも可能である。

### [0110]

また、上記実施例1,2,3に係るレベル判定部172としては、図15に示したレベル判定部153と同じ構成のものを用いることが可能である。

### [0111]

上述したように、分割転送による駆動法を用いた C M O S イメージセンサ 1 0 B では、参照レベル以上のときに加算処理あるいは A D 変換処理を実行し、信号レベルが参照レベルを下回ったときに、それ以降の読み出しにおいて加算処理あるいは A D 変換処理を停止することで、特に低輝度の場合に、読み出しに必要な回数分のみの加算処理または A D 変換処理しか実行されず、読み出しの固定パターンノイズやランダムノイズが積算されることがないため、固定パターンノイズやランダムノイズの影響が小さく、特に低輝度側で高い S / N を実現し、撮像画像の画質を向上できる。

#### [0112]

上記実施例1乃至実施例3に係るカラム回路17A乃至17Eにおいて、処理停止部173は、レベル判定部172の判定結果に基づいて、分割転送によって単位画素20から読み出される複数の出力信号のうち、参照レベル以上の信号レベルの出力信号に対して加算処理を実行させる、具体的には、複数の出力信号の各信号レベルが参照レベル以上のときに加算処理を実行させ、参照レベルを下回るとき加算処理を停止する制御手段を構成している。

## [0113]

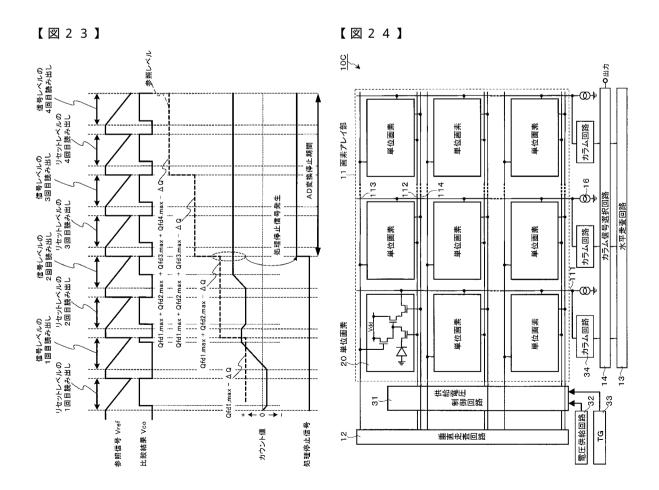

## 「第3実施形態]

図24は、本発明の第3実施形態に係る固体撮像装置、例えばCMOSイメージセンサの構成を示すシステム構成図であり、図中、図1と同等部分には同一符号を付して示している。

### [0114]

図24に示すように、本実施形態に係るCMOSイメージセンサ10Cは、画素アレイ部11、垂直走査回路12、水平走査回路13、複数のカラム回路17およびカラム信号選択回路14および複数に加えて、供給電圧制御回路31、電圧供給回路32およびタイミング発生回路(TG)33を有するとともに、画素アレイ部11の画素列毎に配置された複数のカラム回路34を有する構成となっており、それ以外の構成については第2実施形態に係るCMOSイメージセンサ10Bと基本的に同じである。

#### [0115]

供給電圧制御回路31は、単位画素20内の転送トランジスタ(転送素子)22のゲート電極(制御電極)に印加する転送パルスTRGの電圧値(波高値)を制御する。この供給電圧制御回路31の具体的な構成については後述する。

10

20

30

40

10

20

30

40

50

#### [0116]

電圧供給回路32は、供給電圧制御回路31に対して電圧値が異なる複数の制御電圧を供給する。この複数の制御電圧は、電圧値が異なる転送パルスTRGとして転送トランジスタ22のゲート電極に供給される。この異なる電圧値の転送パルスTRGの詳細については後述する。

#### [0117]

タイミング発生回路(TG)33は、供給電圧制御回路31が転送トランジスタ22のゲート電極に異なる電圧値の転送パルスTRGを供給する際のタイミングを決めるタイミング信号PTRGを発生する。

### [0118]

カラム回路34は、画素アレイ部11から垂直信号線111を通して画素単位で出力される画素20の信号に対して、ノイズ除去、AD変換、加算処理などの各種の信号処理を実行する。カラム回路34の具体的な構成および動作については後述する。

## [0119]

### (供給電圧制御回路)

供給電圧制御回路31は、垂直走査回路12で選択走査された行を駆動するアドレス信号ADRを入力とし、電圧供給回路32から与えられる複数の電圧のうちの1つを選択して転送パルスTRGとして単位画素20内の転送トランジスタ22のゲート電極に供給する。

## [0120]

複数の電圧としては、転送トランジスタ22をオン(導通)状態にするオン電圧Vonと、転送トランジスタ22をオフ(非導通)状態にするオフ電圧Voffと、オン電圧Vonとオフ電圧Voffの間の中間電圧Vmidが電圧供給回路32から供給される。ここで、中間電圧Vmidとは、光電変換素子21の蓄積電荷の一部を保持したまま、残りの蓄積電荷を部分的に浮遊拡散容量26へ転送できる電圧である。

### [0121]

上述した画素回路では、転送トランジスタ22がNチャネルであることから、オン電圧Vonを電源電圧Vddとし、オフ電圧Voffを接地電圧、好ましくは接地電圧よりも低い電圧とする。また、本例では、中間電圧Vmidとして、電圧値が異なる2つの中間電圧Vmid0,Vmid1を用いるものとする。

#### [0122]

これにより、電圧供給回路32から供給電圧制御回路31に対して、オン電圧Von、中間電圧Vmid0,Vmid1およびオフ電圧Voffの4つの電圧が供給される。これら4つの電圧の電圧値は、Voff<Vmid0<Vmid1<Vonの関係にある。そして、4つの電圧のうち、中間電圧Vmid0,Vmid1およびオン電圧Vonが転送パルスTRGとして用いられる。

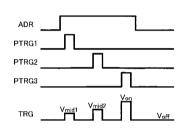

## [0123]

中間電圧Vmid 0 , Vmid 1 およびオン電圧Vonの供給タイミングを制御するために、タイミング発生回路 3 3 から 3 つのタイミング信号PTRG 1 , PTRG 2 , PTRG 3 が供給電圧制御回路 3 1 に与えられる。供給電圧制御回路 3 1 は、中間電圧Vmid 0 , Vmid 1 およびオン電圧Vonのうちの1 つを、タイミング信号PTRG 1 , PTRG 2 , PTRG 3 を基に選択して転送トランジスタ 2 2 のゲート電極に中間電圧Vmid として供給する。

## [0124]

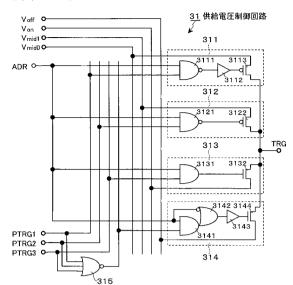

図25は、供給電圧制御回路31の回路構成の一例を示す回路図である。図25に示すように、本例に係る供給電圧制御回路31は、4つの電圧、即ち中間電圧Vmid0,Vmid1、オン電圧Vonおよびオフ電圧Voffに対応した4つの回路プロック311~314と3入力のNOR回路315とを有する構成となっている。

### [0125]

回路ブロック 3 1 1 ~ 3 1 4 には、垂直走査回路 1 2 からアドレス信号 A D R が共通に

与えられる。 N O R 回路 3 1 5 には、タイミング発生回路 3 3 からタイミング信号 P T R G 1 , P T R G 2 , P T R G 3 が 3 入力として与えられる。

### [0126]

回路ブロック311は、アドレス信号ADRとタイミング信号PTRG1とを2入力とするNAND回路3111、レベルシフタ3112およびPチャネルの駆動トランジスタ3113によって構成され、中間電圧Vmid0を選択して転送トランジスタ22のゲート電極に供給する。

## [0127]

回路ブロック312は、アドレス信号ADRとタイミング信号PTRG2とを2入力とするAND回路3121およびPチャネルの駆動トランジスタ3122によって構成され、中間電圧Vmid1を選択して転送トランジスタ22のゲート電極に供給する。

#### [0128]

回路ブロック313は、アドレス信号ADRとタイミング信号PTRG3とを2入力とするNAND回路3131およびNチャネルの駆動トランジスタ3132によって構成され、オン電圧Vonを選択して転送トランジスタ22のゲート電極に供給する。

#### [0129]

回路ブロック314は、アドレス信号ADRとNOR回路315の出力信号とを2入力とするAND回路3141、アドレス信号ADRを一方の(否定)入力とし、AND回路3141の出力信号を他方の入力とするOR回路3142、レベルシフタ3143およびNチャネルの駆動トランジスタ3144によって構成され、オフ電圧Voffを選択して転送トランジスタ22のゲート電極に供給する。

#### [ 0 1 3 0 ]

この回路ブロック314では、転送トランジスタ22をオフするためのオフ電圧Voffとして、接地電圧よりも低い電圧、例えば-1.0Vを供給するために、NOR回路315の作用により他の回路ブロック311,312,313とは排他的に動作する回路構成となっている。

## [0131]

図26に、供給電圧制御回路31の入出力のタイミング関係を示す。転送トランジスタ22のゲート電極に供給する電圧を中間電圧Vmid0,Vmid1、オン電圧Vonおよびオフ電圧Voffとした場合において、アドレス信号ADRによって行が選択された際に、タイミング信号PTRG1,PTRG2,PTRG3によって、それぞれに対応する電圧Vmid0,Vmid1,Vonを供給し、それ以外は電圧Voffを供給する。

#### [0132]

このようにして、供給電圧制御回路 3 1 による制御の下に、垂直走査回路 1 2 による垂直走査に同期して画素行ごとに、中間電圧 V m i d 0 , V m i d 1 およびオン電圧 V o n をその順番で順次転送トランジスタ 2 2 のゲート電極に供給することにより、光電変換素子 2 1 に蓄積された信号電荷を例えば 3 回に分割して浮遊拡散容量 2 6 へ転送する 3 分割転送を実現できる。

## [0133]

### < 3 分割転送 >

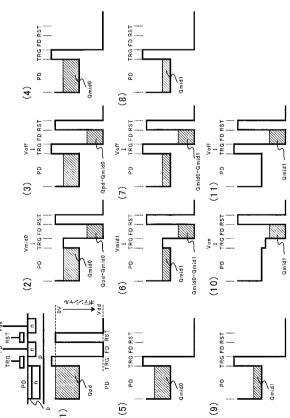

以下に、ある画素行における3分割転送の場合の具体的な動作について、図27のタイミングチャートおよび図28の動作説明図を用いて説明する。図28において、各動作(1)~(11)は図27の各期間(1)~(11)に対応している。

## [0134]

ある画素行の一単位の蓄積期間中において、3分割転送を行なう場合は、垂直走査回路 12からリセットトランジスタ23のゲート電極に対してリセットパルスRTSが一定の 間隔で3回与えられることで、浮遊拡散容量26のリセット動作が3回実行される。この リセット動作に同期して供給電圧制御回路31から、各リセット動作の一定時間後に中間 電圧 V mid 0、中間電圧 V mid 1 およびオン電圧 V onがこの順番で転送トランジスタ22のゲート電極に与えられる。

10

20

30

40

#### [0135]

期間(1)では、光電変換素子21に電荷Qpdが蓄積している。このとき、転送トランジスタ22のゲート電極にオフ電圧Voffが印加されており、また浮遊拡散容量26が1回目のリセットパルスRSTによってリセット済みであり、そのリセットレベルが1回目のリセットレベルとして増幅トランジスタ24および選択トランジスタ25を通して垂直信号線111に読み出される。

#### [ 0 1 3 6 ]

リセットレベルの1回目の読み出し後、期間(2)で中間電圧Vmid 0が転送トランジスタ22のゲート電極に印加される。この中間電圧Vmid 0の印加により、光電変換素子21の蓄積電荷Qpdの一部の電荷Qmid 0を残し、(Qpd-Qmid 0)の電荷が浮遊拡散容量26へ転送される。

#### [0137]

次に、期間(3)で、転送トランジスタ22のゲート電極にオフ電圧Voffが印加され、浮遊拡散容量26に転送された電荷(Qpd-Qmid0)に応じた信号が1回目の信号レベルとして垂直信号線111に読み出される。

### [0138]

次に、期間(4)では、2回目のリセットパルスRSTがリセットトランジスタ23のゲート電極に印加されることで浮遊拡散容量26がリセットされる。次いで、期間(5)で、そのリセットレベルが2回目のリセットレベルとして垂直信号線111に読み出される。

#### [0139]

次に、期間(6)で、中間電圧Vmid1が転送トランジスタ22のゲート電極に印加される。この中間電圧Vmid1の印加により、光電変換素子21に残っている電荷Qmid0の一部の電荷Qmid1を残し、(Qpd0-Qmid1)の電荷が浮遊拡散容量26へ転送される。

## [0140]

次に、期間(7)で、転送トランジスタ22のゲート電極にオフ電圧Voffが印加され、浮遊拡散容量26に転送された電荷(Qpd0-Qmid1)に応じた信号が2回目の信号レベルとして垂直信号線111に読み出される。

## [0141]

次に、期間(8)では、3回目のリセットパルスRSTがリセットトランジスタ23のゲート電極に印加されることで浮遊拡散容量26がリセットされる。次いで、期間(9)で、そのリセットレベルが3回目のリセットレベルとして垂直信号線111に読み出される。

# [0142]

次に、期間(10)で、オン電圧Vonが転送トランジスタ22のゲート電極に印加される。このオン電圧Vonの印加により、光電変換素子21の残りの電荷Qmid1が浮遊拡散容量26へ転送される。

### [0143]

次に、期間(11)で、転送トランジスタ22のゲート電極にオフ電圧Voffが印加され、浮遊拡散容量26に転送された電荷Qmid1に応じた信号が3回目の信号レベルとして垂直信号線111に読み出される。

### [0144]

3分割転送の場合には、中間電圧 V m i d 0 , V m i d 1 が第1制御電圧となり、オン電圧 V o n が第2制御電圧となる。

## [0145]

#### < n 分割転送 >

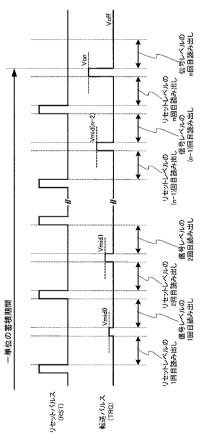

ここでは、3分割転送の場合を例に挙げて説明したが、転送動作の分割数は任意に設定可能である。そして、n分割(nは2以上の整数)の転送を実行する場合は、図29に示すように、n-1個の中間電圧Vmid0,Vmid1,.....,Vmid(n-2)と、

20

10

30

40

オン電圧 V o n とを供給電圧制御回路 1 3 から転送トランジスタ 2 2 のゲート電極に印加して当該転送トランジスタ 2 2 を駆動するようにすればよい。

#### [0146]

n分割転送の場合には、中間電圧Vmid0~Vmid(n-2)が第1制御電圧となり、オン電圧Vonが第2制御電圧となる。

### [0147]

上述したn分割転送による駆動の下に、画素行ごとに電荷の転送、リセット、画素選択が実行されることで、単位画素 2 0 からリセットレベルおよび信号レベルの各信号(単位画素 2 0 の出力信号)が列並列に、即ち画素列単位で並列的に垂直信号線 1 1 1 に読み出され、当該垂直信号線 1 1 1 を通してカラム回路 3 4 に供給される。

### [0148]

分割転送による駆動法が、図27に示すように、転送トランジスタ22に中間電圧Vmid0,Vmid1を印加して任意の電荷量単位で分割転送する方式である場合、第1,第2実施形態に係る分割転送による駆動法の場合とは逆に、高輝度の画素において最初に電荷転送および出力が発生し、低輝度の画素においては最初に電荷転送および出力が発生しない。

### [0149]

図28に示す分割転送による駆動法では、図27に示すように、転送トランジスタ22の駆動電圧によって光電変換部(受光部)で保持できる電荷量が異なることを利用して分割転送を実行する。例えば、図27に記載した例では、転送トランジスタ22の駆動電圧として中間電圧Vmid0,Vmid1を用いることで、電荷Qmid0,Qmid1を光電変換部に保持し、それを超えた電荷を順次転送して読み出すことができる。

### [0150]

### < 本実施形態の特徴部分 >

上述したように、中間電圧Vmid0,Vmid1およびオン電圧Vonをその順番で順次転送トランジスタ22のゲート電極に転送パルスTRGとして供給し、一単位の蓄積期間中に光電変換部に蓄積された信号電荷を例えば3分割転送にて浮遊拡散容量26へ転送し、これら分割転送された信号電荷を読み出す構成を採るCMOSイメージセンサ10Cでは、分割された各々の転送の最大値以上の出力が得られたときに、それ以前に読み出された結果あるいはその加算結果をリセットして、次以降の加算処理あるいはAD変換処理を開始することを特徴としている。

## [0151]

#### < 本実施形態の作用効果 >

第1,第2実施形態では、参照レベル以上のときに加算処理あるいはAD変換処理を実行し、信号レベルが参照レベルを下回ったときに、光電変換部の蓄積電荷が全て読み出されているものとし、次以降の加算処理あるいはAD変換処理を停止するようにしている。これに対して、本実施形態では、光電変換部に蓄積電荷が無い状態から電荷が蓄積され、信号レベルが参照レベル以上になったとき、それ以前に読み出された結果あるいはその加算結果をリセットするとともに、次以降の加算処理あるいはAD変換処理を開始することで、特に低輝度時に出力の無い読み出しのノイズ成分を加算することなく、第1,第2実施形態の場合と同様の作用効果を得ることができる。

#### [0152]

例えば、図30(A)に示すように、転送可能な最大電荷量が決まる。そして、図30(B)の例のように、例えば蓄積電荷QpdがQpd>Qfd4.max、かつ、Qpd<Qfd4.max+Qfd3.maxの場合、1回目、2回目にて電荷転送が発生せず出力がなく、3回目にてQfd3(=Qpd-Qfd4.max)が転送されて出力され、4回目でQfd4.max が出力される。

#### [0153]

そして、3回目と4回目で読み出された出力信号を加算することで全蓄積電荷Qpdが得られる。この場合、3回目にてQfd3 < Qfd3.max のレベル判定により保持データリセット信号が発生し、それまでにAD変換し保持されている1回目と1回目のデータ、あるい

10

20

30

40

は、それらを加算されて保持されているデータをリセットし、3回目と4回目のみを加算 することで、ノイズ成分を抑えることができる。

### [0154]

以下に、分割された各々の転送の最大値を上回る出力が得られたときに、それ以前に読み出された結果あるいはその加算結果をリセットし、次以降の加算処理あるいはAD変換処理を開始する制御を行なうカラム回路34の具体的な実施例について説明する。

#### [0155]

## (カラム回路)

図31は、カラム回路34の構成の一例を示すブロック図である。図31に締め治すように、カラム回路34Aは、AD変換部341、レベル判定部342および加算部343 を有する構成となっている。

#### [0156]

AD変換部341は、画素アレイ部11から垂直信号線111を通して供給される、分割して転送されたアナログの出力信号をデジタル信号にAD変換する。レベル判定部342は、AD変換部341によるAD変換後のデジタル値を参照レベルと比較し、当該デジタル値が参照レベルを上回るときに判定結果を出力し、当該判定結果を保持データリセット信号として加算部343に与える。

### [0157]

加算部343は、分割転送に伴ってAD変換部341から順次供給されるデジタル信号を加算処理してその加算結果を保持し、レベル判定部342から保持データリセット信号が与えられたときは、それまで加算して保持した保持データをリセットし、分割転送に伴ってAD変換部341から順次供給されるデジタル信号について再び加算処理を開始し、最終的な保持データを1画素の画素信号として出力する。

#### [0158]

レベル判定部342の判定結果を保持データリセット信号として用いる場合、保持データのリセットは1回実行されればよいので、レベル判定部342は、図15に示したレベル判定部153の場合のように、保持データリセット信号を保持し続ける構成でなくても構わない。

### [0159]

なお、ここでは図示を省略するが、AD変換部341の前段側に、図10のノイズ除去部151に相当するノイズ除去部を設ける構成を採ることも可能である。

## [0160]

上記実施例に係るカラム回路34において、加算部343は、レベル判定部34の判定結果に基づいて、分割転送によって単位画素20から読み出される複数の出力信号のうち、参照レベル以上の信号レベルの出力信号に対して加算処理を実行させる、具体的には、複数の出力信号の各信号レベルが参照レベル以上になったとき、それ以前に読み出された出力信号あるいはその加算結果をリセットし、算処理を開始する制御手段としての機能をも併せ持っている。

## [0161]

### 「高変換効率 ]

以上説明した第1~第3実施形態に係るCMOSイメージセンサ10A~10Cにおいて、浮遊拡散容量26での電荷電圧変換効率を高めるべく、光電変換素子21から信号電荷が転送される浮遊拡散容量(電荷電圧変換部)26の寄生容量(FD容量)を微小化、具体的には、浮遊拡散容量26が扱える最大電荷量が光電変換素子21に蓄積可能な最大電荷量よりも小さくなるように寄生容量を小さくすることで、より高い効果を得ることができる。

#### [0162]

光電変換素子21の最大蓄積電荷量を10,000e-とした場合に、全ての蓄積電荷を1回の転送にて読み出し可能なFD容量を1とする。この場合の読み出し時ランダムノイズを7e-、読み出し時の固定パターンノイズを2e-、光ショットノイズを蓄積電荷

10

20

30

40

の平方根とした場合の、蓄積電荷に対する信号ノイズ比S/N(dB)を図32に示す。

## [0163]

図32にはさらに、同じ条件にて、FD容量を1/4として、従来の分割転送と加算処理をした場合、本発明の停止判定付きで4分割転送と加算処理をした場合をそれぞれ示している。

### [0164]

図32から明らかなように、高変換効率として光ショットノイズ以外のノイズ成分を相対的に小さくし、全蓄積電荷を分割転送で読み出した上で、低輝度の場合にはノイズ成分のみを加算しないようにできるため、高い画質を実現できることがわかる。

### [0165]

また、同様にFD容量を1/10にして10分割転送して本発明による加算処理を実行した場合のように、FD容量を微小化し、分割転送の分割数を増やすことで光ショットノイズ以外のノイズ成分を小さくすることができる。

### [0166]

上述したように、浮遊拡散容量 2 6 の寄生容量を小さくするなどして電荷電圧変換効率を高めることで、出力信号の信号レベルに対するラインダムノイズや固定パターンノイズを相対的に小さくし、かつ、電荷電圧変換効率を高めたことによって1回の読み出しで出力できない蓄積電荷を分割転送する C M O S イメージセンサ 1 0 A ~ 1 0 C において、分割転送によって単位画素 2 0 から出力される信号を加算する際に、入射光輝度または蓄積電荷によって加算する必要の無い読み出しを検知して加算しないようにすることで、不要なランダムノイズや固定パターンノイズを加算結果に含まないようにすることができるため、特に低輝度領域にて高い S / N を実現できる。

### [0167]

### 「変形例 ]

上記各実施形態では、信号処理回路15(15A,15B,15C,15D,15E)およびカラム回路17(17A,17B,17C),34がAD変換機能を持つ場合を例に挙げた説明したが、AD変換機能は必須の構成要素ではなく、信号処理回路15およびカラム回路17,34としては、少なくとも加算機能を持つ構成のものであれば所期の目的を達成することができる。

## [0168]

また、上記各実施形態では、光電変換素子21の電荷を1つの転送トランジスタ22によって共通の浮遊拡散容量26に分割転送し、共通の垂直信号線111に順次読み出す構成の単位画素20を有するCMOSイメージセンサに適用した場合を例に挙げて説明したが、これに限られるものではなく、種々の変形例が可能である。

## [0169]

## (変形例1)

図33は、変形例1に係る単位画素20Bの画素回路を示す回路図であり、図中、図2と同等部分には同一符号を付して示している。

### [0170]

図33に示すように、本変形例1に係る単位画素20Aは、増幅トランジスタ24に対して直列に接続された選択トランジスタ25のドレイン電極と電源Vddとの間に電流源31を接続し、選択トランジスタ25のドレインノードから出力信号Voutを導出する構成となっている。

## [0171]

この単位画素 2 0 A において、浮遊拡散容量 2 6 での電荷電圧変換の変換効率は、浮遊拡散容量 2 6 と垂直信号線 1 1 1 の間の寄生容量の容量値 C i で決まり、この寄生容量の容量値 C i を浮遊拡散容量 2 6 の容量値 C f d よりも小さくすることで、変換効率を上げることができる。

### [0172]

ここで、浮遊拡散容量 2 6 の最大蓄積電荷量を Q fd.max、寄生容量 C i の最大蓄積電荷

10

20

30

40

量をQi.maxとした場合、高変換効率の効果を得るには、

Qi.max < Qfd.max

が条件となる。このため、最大蓄積電荷量 Qfd.maxよりも小さい最大蓄積電荷量 Qi.max を単位として光電変換素子 2 1 の蓄積電荷 Qpdを分割転送する必要がある。

### [0173]

このように、電荷電圧変換効率が高い、あるいは、電圧増幅率が高い単位画素 2 0 A を有する C M O S イメージセンサは、 S / N において有利である一方で、 1 回の読み出しで出力できる電荷量に制限が発生する場合がある。

### [0174]

この単位画素 2 0 A を有する C M O S イメージセンサに対して、先述した分割転送を適用し、光電変換素子 2 1 の電荷を任意に分割して転送することにより、光電変換素子 2 1 で発生した全ての電荷を、読み出し回路の出力範囲に応じて効率よく出力することができる。

## [0175]

また、図33に示す単位画素22Aの例では、リセット時の電荷電圧変換部(浮遊拡散容量26)の電圧を読み出し回路の動作点に設定する必要があるが、先述した分割転送を適用することにより、電荷電圧変換部の電位に依らず分割転送量を制御できる。

## [0176]

## (変形例2)

図34は、変形例2に係る単位画素20Bの画素回路を示す回路図であり、図中、図2と同等部分には同一符号を付して示している。

#### [0177]

図34に示すように、本変形例2に係る単位画素20Bは、増幅トランジスタ24に代えて、浮遊拡散容量26と選択トランジスタ25の間に反転増幅回路27を接続するとともに、当該反転増幅回路27に対してリセットトランジスタ23を並列に接続した構成となっている。このように、反転増幅回路27を画素内に持つことにより、信号レベルを増幅し、S/Nの改善を図ることができる。

#### [0178]

このように、反転増幅回路27を画素内に持つ単位画素20Cを有するCMOSイメージセンサでは、反転増幅回路27の増幅率を-Aとすると、浮遊拡散容量26に最大蓄積電荷量Qfd.maxが転送されたときの出力電圧Voutの振幅-A・Qfd.max/Cfdが、出力電圧Voutの出力可能範囲 Vout.ppを超える場合がある。

#### [0179]

この場合、全ての電荷を信号出力するために、浮遊拡散容量 2 6 の最大蓄積電荷量 Q fd.maxよりも小さい電荷 Q mid ( < Q fd.max)を最大とした電荷量の単位で分割転送する必要がある。

## [0180]

この単位画素 2 0 B を有する C M O S イメージセンサに対して、先述した分割転送を適用し、光電変換素子 2 1 の電荷を任意に分割して転送することにより、光電変換素子 2 1 で発生した全ての電荷を、出力電圧 V o u t の出力可能範囲 V o u t . p p に応じて効率よく出力することができる。

## [0181]

なお、上記各実施形態では、可視光の光量に応じた信号電荷を物理量として検知する単位画素が行列状に配置されてなるCMOSイメージセンサに適用した場合を例に挙げて説明したが、本発明はCMOSイメージセンサへの適用に限られるものではなく、画素アレイ部の画素列ごとにカラム回路を配置してなるカラム方式の固体撮像装置全般に対して適用可能である。

## [0182]

また、本発明は、可視光の入射光量の分布を検知して画像として撮像する固体撮像装置への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する

10

30

20

40

固体撮像装置や、広義の意味として、圧力や静電容量など、他の物理量の分布を検知して 画像として撮像する指紋検出センサ等の固体撮像装置(物理量分布検知装置)全般に対し て適用可能である。

#### [0183]

さらに、本発明は、画素アレイ部の各単位画素を行単位で順に走査して各単位画素から 画素信号を読み出す固体撮像装置に限らず、画素単位で任意の画素を選択して、当該選択 画素から画素単位で信号を読み出す X - Y アドレス型の固体撮像装置に対しても適用可能 である。

### [0184]

なお、固体撮像装置はワンチップとして形成された形態であってもよいし、撮像部と、 信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール 状の形態であってもよい。

#### [0185]

また、本発明は、固体撮像装置への適用に限られるものではなく、撮像装置にも適用可能である。ここで、撮像装置とは、デジタルスチルカメラやビデオカメラ等のカメラシステムや、携帯電話機などの撮像機能を有する電子機器のことを言う。なお、電子機器に搭載される上記モジュール状の形態、即ちカメラモジュールを撮像装置とする場合もある。

#### [0186]

#### 「撮像装置 ]

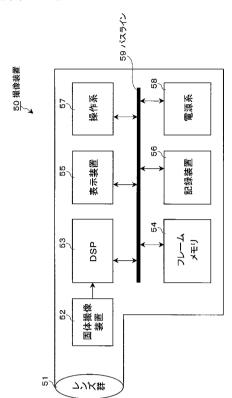

図35は、本発明に係る撮像装置の構成の一例を示すブロック図である。図35に示すように、本発明に係る撮像装置50は、レンズ群51を含む光学系、固体撮像装置52、カメラ信号処理回路であるDSP回路53、フレームメモリ54、表示装置55、記録装置56、操作系57および電源系58等を有し、DSP回路53、フレームメモリ54、表示装置55、記録装置56、操作系57および電源系58がバスライン59を介して相互に接続された構成となっている。

#### [0187]

レンズ群 5 1 は、被写体からの入射光(像光)を取り込んで固体撮像装置 5 2 の撮像面上に結像する。固体撮像装置 5 2 は、レンズ群 5 1 によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この固体撮像装置 5 2 として、先述した実施形態に係る C M O S イメージセンサ 1 0 が用いられる。

### [0188]

表示装置55は、液晶表示装置や有機 EL(electro luminescence)表示装置等のパネル型表示装置からなり、固体撮像装置52で撮像された動画または静止画を表示する。記録装置56は、固体撮像装置52で撮像された動画または静止画を、ビデオテープやDVD(Digital Versatile Disk)等の記録媒体に記録する。

#### [0189]

操作系57は、ユーザによる操作の下に、本撮像装置が持つ様々な機能について操作指令を発する。電源系58は、DSP回路53、フレームメモリ54、表示装置55、記録装置56および操作系57の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

## [0190]

上述したように、ビデオカメラやデジタルスチルカメラ、さらには携帯電話機等のモバイル機器向けカメラモジュールなどの撮像装置において、その固体撮像装置52として先述した第1~第3実施形態に係るСMOSイメージセンサ10A~10Cを用いることにより、これらCMOSイメージセンサ10A~10Cでは、全ての蓄積電荷を1回の読み出しで出力できない場合に分割して電荷転送し、その分割転送による各出力信号を加算する際に、不要なランダムノイズや固定パターンノイズを加算結果に含まないようにすることができるため、特に低輝度領域にて高いS/Nを実現できる。

### 【図面の簡単な説明】

## [0191]

10

20

30

- 【図1】本発明の第1実施形態に係るCMOSイメージセンサの構成を示すシステム構成図である。

- 【図2】単位画素の回路構成の一例を示す回路図である。

- 【図3】画素回路の構成の他の例を示す回路図である。

- 【図4】画素回路の構成のさらに他の例を示す回路図である。

- 【図5】4分割にて分割転送を行なう場合のリセットパルスRSTおよび転送パルスTRGのタイミング関係を示すタイミングチャートである。

- 【図6】4分割転送における入射光輝度が高い場合の動作説明図である。

- 【図7】4分割転送における入射光輝度が低い場合の動作説明図である。

- 【図8】光電変換部が扱える最大電荷量 Q pd . maxと分割転送の各々の最大値 Q fd . maxの関係を示す図である。

- 【図9】光電変換部の最大蓄積電荷量を10,000電子とした場合の蓄積電荷とS/N(dB)の関係を示す図である。

- 【図10】実施例1に係る信号処理回路の構成の一例を示すブロック図である。

- 【図11】実施例2に係る信号処理回路の構成の一例を示すブロック図である。

- 【図12】実施例3に係る信号処理回路の構成の一例を示すブロック図である。

- 【図13】実施例4に係る信号処理回路の構成の一例を示すブロック図である。

- 【図14】実施例5に係る信号処理回路の構成の一例を示すブロック図である。

- 【図15】レベル判定部の構成の一例を示すブロック図である。

- 【図16】レベル比較器の構成の一例を示す回路図である。

- 【図17】レベル判定部の動作説明のためのタイミングチャートである。

- 【図18】本発明の第2実施形態に係るCMOSイメージセンサの構成を示すシステム構成図である。

- 【図19】実施例1に係るカラム回路の構成の一例を示すブロック図である。

- 【図20】実施例2に係るカラム回路の構成の一例を示すブロック図である。

- 【図21】実施例3に係るカラム回路の構成の一例を示すブロック図である。

- 【図22】AD変換部および処理停止部の具体的な構成の一例を示すブロック図である。

- 【図23】ノイズ除去機能と加算機能を持つAD変換部の動作タイミングを示すタイミングチャートである。

- 【図 2 4 】本発明の第 3 実施形態に係る C M O S イメージセンサの構成を示すシステム構 30 成図である。

- 【図25】供給電圧制御回路の回路構成の一例を示す回路図である。

- 【図26】供給電圧制御回路の入出力のタイミング関係を示すタイミングチャートである

- 【図27】3分割転送の場合の駆動タイミング例を示すタイミングチャートである。

- 【図28】3分割転送の場合の動作説明図である。

- 【図29】n分割転送の場合の駆動タイミング例を示すタイミングチャートである。

- 【図30】光電変換部が扱える最大電荷量 Q pd.maxと分割転送の各々の最大値 Q fd.maxの関係を示す図である。

- 【図31】カラム回路の構成の一例を示すブロック図である。

- 【図32】電荷電圧変換効率を高めた場合の入射光強度 S / N の特性についての本発明と従来技術の比較例を示す図である。

- 【図33】変形例1に係る単位画素の画素回路を示す回路図である。

- 【図34】変形例2に係る単位画素の画素回路を示す回路図である。

- 【図35】本発明に係る撮像装置の構成の一例を示すブロック図である。

- 【図36】単位画素の構成の一例を示す回路図である。

【符号の説明】

[0192]

1 0 A , 1 0 B , 1 0 C ... C M O S イメージセンサ、1 1 ... 画素アレイ部、1 2 ... 垂直 走査回路、1 3 ... 水平走査回路、1 4 ... カラム信号選択回路、1 5 ( 1 5 A , 1 5 B , 1

10

20

40

5 C , 1 5 D , 1 5 E ) ...信号処理回路、17 ( 1 7 A , 1 7 B , 1 7 C ) , 3 4 ...カラム回路、2 0 ( 2 0 A , 2 0 B ) ...単位画素、2 1 ...光電変換素子、2 2 ...転送トランジスタ、2 3 ...リセットトランジスタ、2 4 ...増幅トランジスタ、2 5 ...選択トランジスタ、3 1 ...供給電圧制御回路、3 2 ...電圧供給回路、3 3 ...タイミング発生回路(T G )

【図4】

# 【図5】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

# 【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図25】

【図27】

【図26】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

## フロントページの続き

## (56)参考文献 特開2001-177775(JP,A)

特開2006-086845(JP,A)

特開平01-147972(JP,A)

特開2006-148328(JP,A)

特開平09-154065(JP,A)

特開2005-278135(JP,A)

特開2006-217548(JP,A)

# (58)調査した分野(Int.CI., DB名)

H04N 5/30 - 5/378

H 0 4 N 5 / 2 2 2 - 5 / 2 5 7

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762