# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(11) 공개번호 10-2010-0051555 (43) 공개일자 2010년05월17일

(51) Int. Cl.

H01L 27/146 (2006.01)

(21) 출원번호 **10-2009-0106408**

(22) 출원일자2009년11월05일심사청구일자없음

(30) 우선권주장 JP-P-2008-287010 2008년11월07일 일본(JP) (뒷면에 계속) (71) 출원인

소니 주식회사

일본국 도쿄도 미나토쿠 코난 1-7-1

(72) 발명자

타카하시 히로시

일본국 도쿄도 미나토쿠 코난 1-7-1 소니 가부시 끼 가이샤 내

(74) 대리인 **최달용**

전체 청구항 수 : 총 14 항

# (54) 고체 촬상 장치, 고체 촬상 장치의 제조 방법, 및 전자 기기

## (57) 요 약

고체 촬상 장치는 기판과; 상기 기판의 깊이 방향으로 적층된 복수의 포토 다이오드와; 상기 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된 종형의 판독 게이트 전극과; 상기 판독 게이트 전극의 저부 및 측면을 피복하여 형성되고, 상기 판독 게이트 전극 측면에는 균일폭으로 형성된 제 1 도전형의 반도체 영역으로 이루어지는 암전류 억제 영역과; 상기 제 1 도전형의 반도체 영역과, 상기 포토 다이오드사이에, 제 2 도전형의 반도체 영역으로 형성된 판독 채널 영역을 포함한다.

## 대 표 도 - 도2

공개특허 10-2010-0051555

(30) 우선권주장

JP-P-2008-287011 2008년11월07일 일본(JP)

JP-P-2008-287012 2008년11월07일 일본(JP)

## 특허청구의 범위

#### 청구항 1

기판과,

상기 기판의 깊이 방향으로 적층된 복수의 포토 다이오드와,

상기 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된 종형의 판독 게이트 전극과.

상기 판독 게이트 전극의 저부 및 측면을 피복하여 형성되고, 상기 판독 게이트 전극 측면에는 균일폭으로 형성 된 제 1 도전형의 반도체 영역으로 이루어지는 암전류 억제 영역과

상기 제 1 도전형의 반도체 영역과, 상기 포토 다이오드 사이에, 제 2 도전형의 반도체 영역으로 형성된 판독채널 영역을 포함하여 구성된 것을 특징으로 하는 고체 촬상 장치.

# 청구항 2

제 1항에 있어서,

상기 판독 채널 영역은, 상기 판독 게이트 전극의 측면을 피복하여 형성된 상기 암전류 억제 영역의 주위를 피복하도록 형성되어 있는 것을 특징으로 하는 고체 촬상 장치.

#### 청구항 3

기판의 깊이 방향으로 적층한 복수의 포토 다이오드를 형성하는 공정,

상기 기판 상부에 마스크층 및 포토레지스트막을 형성하는 공정,

포토 리소그래피법에 의해 포토레지스트막을 패턴 형성하고, 패턴 형성된 상기 포토레지스트막을 마스크로 하여, 상기 마스크층을 에칭하고, 상기 기판 표면에 달하는 개구부를 형성하는 공정,

상기 개구부를 통하여, 상기 기판에 제 1 도전형의 불순물을 이온 주입하는 공정,

상기 개구부를 통하여, 상기 기판의 제 1 도전형의 불순물이 이온 주입된 영역보다도 기판 표면측의 영역에 제 2 도전형의 불순물을 이온 주입하는 공정,

상기 레지스트막을 제거하는 공정,

상기 개구부를 포함하는 마스크층 표면에 제 1의 측벽 스페이서를 형성하고, 상기 개구부의 지름을 축소하는 공 정,

상기 축소된 개구부를 통하여, 제 1 도전형의 불순물을 이온 주입하는 공정,

상기 축소된 개구부의 측벽에 제 2의 측벽 스페이서를 형성하고, 상기 개구부의 지름을 더욱 축소하는 공정,

상기 축소된 개구부를 마스크로 하여, 상기 기판을 에칭하고, 상기 포토 다이오드에 인접하는 홈부를 형성하는 공정,

상기 홈부의 저부 및 측면을 피복하여 게이트 절연막을 형성하는 공정,

상기 게이트 절연막이 형성된 상기 홈부에 전극 재료를 매입하여 판독 게이트 전극을 형성하는 공정을 포함하는 것을 특징으로 하는 고체 촬상 장치의 제조 방법.

# 청구항 4

광학 렌즈와,

기판과; 기판의 깊이 방향으로 적충된 복수의 포토 다이오드와; 상기 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된 종형의 판독 게이트 전극과; 판독 게이트 전극의 저부 및 측면을 피복하여 형성되고, 상기 판독 게이트 전극 측면에는 균일폭으로 형성된 제 1 도전형의 반도체 영역으로 이루어지는 암전류 억제 영역과; 상기 제 1 도전형의 반도체 영역과 상기 포토 다이오드 사이에, 제 2 도전형의

반도체 영역으로 형성된 판독 채널 영역을 포함하는 고체 촬상 장치와,

상기 고체 활상 장치의 출력 신호를 처리하는 신호 처리 회로를 포함하여 구성되는 것을 특징으로 하는 전자 기.

## 청구항 5

기판과,

상기 기판의 깊이 방향으로 적충된 복수의 포토 다이오드와; 상기 복수의 포토 다이오드중 기판 표면측의 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판 표면에 형성된 평면형 게이트 전극과; 상기 복수의 포토 다이오드중 기판 표면부터 깊이 방향의 깊은 위치의 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된 상기 종형 게이트 전극을 포함하여 구성된 화소와,

상기 복수의 포토 다이오드를 분리하는 포토 다이오드 분리 영역을 포함하여 구성된 것을 특징으로 하는 고체 활상 장치.

#### 청구항 6

제 5항에 있어서,

상기 평면형 게이트 전극에 의해 판독된 신호 전하를 축적하기 위해, 상기 평면형 게이트 전극에 인접하여 형성 된 플로팅 디퓨전 영역 및

상기 종형 게이트 전극에 의해 판독된 신호 전하를 축적하기 위해, 상기 종형 게이트 전극에 인접하여 형성된 플로팅 디퓨전 영역을 가지며,

상기 플로팅 디퓨전 영역은, 인접하는 화소 사이에서 공유되는 것을 특징으로 하는 고체 촬상 장치.

#### 청구항 7

광학 렌즈와,

기판과, 화소와, 복수의 포토 다이오드를 분리하는 포토 다이오드 분리 영역을 포함하는 고체 촬상 장치, 및 상기 고체 촬상 장치의 출력 신호를 처리하는 신호 처리 회로를 포함하며,

상기 화소는, 상기 기판의 깊이 방향으로 적충된 복수의 포토 다이오드와; 상기 복수의 포토 다이오드중 기판 표면측의 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판 표면에 형성된 평면형 게이트 전극과; 상기 복수의 포토 다이오드중 기판 표면부터 깊이 방향의 깊은 위치의 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된 상기 종형 게이트 전극을 포함하여 구성되는 것을 특징으로 하는 전자 기기.

# 청구항 8

기판과,

상기 기판 내에 매입된 포토 다이오드와,

상기 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된, 전하 판독 트랜 지스터의 종형의 게이트 전극과,

상기 종형의 게이트 전극과는 다른 전극 재료로 형성된, 다른 트랜지스터의 평면형의 게이트 전극을 갖는 것을 특징으로 하는 고체 촬상 장치.

#### 청구항 9

제 8항에 있어서,

상기 종형의 게이트 전극이 불순물 혼합 가스를 사용하여 퇴적되는 불순물 도입 실리콘으로 형성되고,

상기 평면형의 게이트 전극이 언도프 실리콘에 이온 주입으로 불순물을 도입한 불순물 도입 실리콘으로 형성되어 있는 것을 특징으로 하는 고체 촬상 장치.

#### 청구항 10

제 9항에 있어서,

상기 종형의 게이트 전극이 제 1 도전형 또는 제 2 도전형의 불순물을 도입한 불순물 도입 실리콘으로 형성되어 있는 것을 특징으로 하는 고체 촬상 장치.

# 청구항 11

제 8항에 있어서,

상기 종형의 게이트 전극이 불순물 혼합 가스를 사용하여 퇴적되는 제 1 도전형 또는 제 2 도전형의 불순물을 도입한 불순물 도입 실리콘으로 형성되고,

상기 평면형의 게이트 전극이, 하층에 고유전률 게이트 절연막을 갖는 메탈 재료로 형성되어 있는 것을 특징으로 하는 고체 촬상 장치.

#### 청구항 12

기판의 표면상의 제 1의 연마 스토퍼막에 홈을 형성하여 소자 분리 영역을 형성하는 공정과,

상기 제 1의 연마 스토퍼막상에 제 2의 연마 스토퍼막을 형성하는 공정과,

상기 제 1, 제 2의 연마 스토퍼막에 홈을 형성하고, 평면형의 게이트 전극 재료와 홈의 내벽 사이에 게이트 절 연막이 삽입되도록 종형 게이트를 포함하는 트랜지스터 이외의 트랜지스터에 대한 평면형 게이트 전극 재료로 홈을 채우는 공정과,

제 1 및 제 2의 연마 스토퍼막에서 다른 홈이 형성된 위치 이외의 위치에서 제 1 및 제 2의 연마 스토퍼막에 형성된 홈을 통해 기판에서 세로홈을 형성하고, 상기 평면형 게이트 전극 재료는 서로 다른 특성을 갖는 종형 게이트 전극 재료와 세로 홈의 내벽 사이에 게이트 절연막이 삽입되도록 전하 판독 트랜지스터에 대한 종형 게이트 전극 재료로 세로홈을 채우는 공정과,

상기 제 2의 연마 스토퍼막까지 상기 평면형의 게이트 전극 재료와 상기 종형의 게이트 전극 재료를 일괄하여 평탄화하는 공정과,

상기 제 1, 제 2의 연마 스토퍼막을 제거하고, 종형의 게이트 전극과 평면형의 게이트 전극을 형성하는 공정과,

상기 기판에 매입하도록 이온 주입법으로 포토 다이오드를 형성하는 공정을 갖는 것을 특징으로 하는 고체 촬상 장치의 제조 방법.

# 청구항 13

제 12항에 있어서.

상기 제 1, 제 2의 연마 스토퍼막에서 다른 홈이 형성된 위치 이외의 위치에서 상기 제 1 및 제 2의 연마 스토퍼막에 상기 홈을 형성한 후, 상기 제 1, 제 2의 연마 스토퍼막을 마스크로 상기 기판 내에 암전류 억제를 위한 불순물 영역을 형성하고, 다음에, 상기 제 1, 제 2의 연마 스토퍼막의 상기 홈의 내벽에 상기 기판에 세로홈을 형성할 때 마스크로서 사용되는 측벽을 형성하는 것을 특징으로 하는 고체 촬상 장치의 제조 방법.

#### 청구항 14

광학 렌즈와,

고체 촬상 장치와,

상기 고체 촬상 장치의 출력 신호를 처리하는 신호 처리 회로를 구비하고,

상기 고체 촬상 장치는,

기판과,

상기 기판 내에 매입된 포토 다이오드와,

상기 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된, 전하 판독 트랜

지스터의 종형의 게이트 전극과,

상기 종형의 판독 게이트 전극과는 다른 전극 재료로 형성된, 다른 트랜지스터의 평면형의 게이트 전극을 갖는 것을 특징으로 하는 전자 기기.

# 명 세 서

#### 발명의 상세한 설명

# 기술분야

[0001] 본 발명은, 고체 촬상 장치, 고체 촬상 장치의 제조 방법, 및 해당 고체 촬상 장치를 구비한 전자 기기에 관한 것이다. 본 발명은, 고체 촬상 장치, 및 해당 고체 촬상 장치를 구비한 전자 기기에 관한 것이다.

## 배경기술

- [0002] 고체 활상 장치로서, CMOS형의 고체 활상 장치가 알려져 있다. 이 CMOS형의 고체 활상 장치는, 포토 다이오드와, 복수의 트랜지스터, 이른바 MOS 트랜지스터에 의해, 2화소를 형성하고, 복수의 화소를 소요되는 패턴으로 배열하여 구성되어 있다. 이 포토 다이오드는, 수광량에 응한 신호 전하를 생성하고, 축적하는 광전 변환 소자이고, 복수의 MOS 트랜지스터는, 포토 다이오드로부터의 신호 전하를 전송하기 위한 소자이다.

- [0003] 도 1에, 이미지 센서에 적용한 종래의 CMOS형의 고체 촬상 장치(하기 일본특개평 11-122532호 기재)의 주요부의 개략 단면 구성을 도시한다. 도 1은, 고체 촬상 장치(216)의 화소부에 있어서의 단면 구성이다.

- [0004] 도 1에 도시하는 종래의 고체 촬상 장치(216)는, 실리콘으로 이루어지는 p형의 기판(201)의 표면측에, 화소 분리 영역(208)을 가지며, 각 구분 영역에 포토 다이오드(PD)와 복수의 MOS 트랜지스터로 이루어지는 화소(200)를 갖는다. 복수의 MOS 트랜지스터는, 각각, 전하 판독 트랜지스터(Tr1), 리셋 트랜지스터(Tr2), 앰프 트랜지스터 (Tr3) 및 수직 선택 트랜지스터(도시 생략)이다. 이 4개의 MOS 트랜지스터와, 포토 다이오드(PD)로 구성되는 화소 영역이 단위 화소가 된다. 이 단위 화소는, 복수개, 2차원 매트릭스형상으로 배열된다.

- [0005] 포토 다이오드(PD)는, p형의 기판(201)의 표면부터 소요되는 깊이 방향으로 차례로 형성한 n+형 불순물 영역 (203)과, 및 n형 불순물 영역(202)와, 이 n+형 불순물 영역(203)의 표면에 형성한 고불순물 농도의 p형 불순물 영역(204)에 의해 구성되어 있다.

- [0006] 전하 판독 트랜지스터(Tr1)는, 포토 다이오드(PD)가 형성된 영역에 인접하는 기판상에 게이트 절연막(217)을 통하여 형성된 평면형의 게이트 전극(209)과, 기판 표면에 형성된 n+불순물 영역으로 구성되는 소스·드레인 영역(205)으로 구성된다. 이 소스·드레인 영역(205)은, 플로팅 디퓨전 영역을 구성하는 것이다.

- [0007] 앰프 트랜지스터(Tr3)는, 소스·드레인 영역(206)과, 소스·드레인 영역(206)이 형성된 영역에 인접하는 기판상에 게이트 절연막(217)을 통하여 형성된 평면형의 게이트 전극(211)과, 기판 표면에 형성된 n+불순물 영역으로 구성되는 소스·드레인 영역(207)으로 구성된다.

- [0008] 리셋 트랜지스터(Tr2)는, 소스·드레인 영역(205)과, 소스·드레인 영역(205)이 형성된 영역에 인접하는 기판 (201)상에 게이트 절연막(217)을 통하여 형성된 평면형의 게이트 전극(210)과, 기판(201) 표면에 형성된 n+불순물 영역으로 구성되는 소스·드레인 영역(206)으로 구성된다.

- [0009] 소스·드레인 영역(206)은, 기판(201)상에 층간 절연막(215)을 통하여 형성되는 전원 배선(213)에 콘택트부 (212)를 통하여 접속된다.

- [0010] 또한, 층간 절연막(215) 내에는, 소망하는 배선(214)이 형성되어 있다.

- [0011] 이와 같이, 종래의 고체 촬상 장치(216)의 기판(201) 표면에는, 단위 화소(200)마다, 포토 다이오드(PD)와, 복수의 MOS 트랜지스터가 각각 배치된다.

- [0012] 그런데, 근래, 고체 촬상 장치에서는, 다수의 화소를 고집적하기 위해, 화소 사이즈의 미세화가 행하여지고 있다. 특히, 도 1에 도시하는 바와 같은 종래의 고체 촬상 장치(216)의 각 화소 영역에서는, 기판(201)의 동일 평면상에, 포토 다이오드(PD)나, 복수의 MOS 트랜지스터가 배치되어 있기 때문에, 단위 화소(200)를 구성하는 기판(201) 표면에는, 그들을 구성하는 면적이 필요해진다. 이 때문에, 1화소의 면적이 증대하여 버리는 경향이 있다. 이와 같은 구성에서는, 화소 사이즈를 미세화한 경우에는, 포토 다이오드(PD)의 면적이 축소하여 버리게 되

어.

- [0013] 포화 전하량(Qs)의 저하나 감도의 저하를 초래하는 등의 문제가 있다.

- [0014] 이 문제에 대해, 화소 내의 MOS 트랜지스터를, 인접하는 복수의 화소로 공유한 것으로, 화소 사이즈를 축소하는 방법이 몇가지 제안되어 있다.

- [0015] 이 대책으로서, 화소 내의 화소 트랜지스터를, 인접하는 복수의 화소로 공유한 것으로, 포토 다이오드(PD)의 면적을 유지하면서 화소 사이즈를 축소하는 방법이, 이미 몇가지 제안되어 있다. 예를 들면, 일반적인 CMOS 고체 촬상 장치에서는, 4화소로 1조(組)의 화소 트랜지스터를 공유하는 방법이 취해지고 있다.

- [0016] 또한, 화소 사이즈의 미세화에 수반하는 포화 전하량(Qs)의 저하나, 감도의 저하를 막는 방법에 대한 전혀 다른 어프로치로서, 일본 특개2002-513145호에서는, 매입형의 게이트 전극을 이용한 고체 촬상 장치가 제안되어 있다. 도 4에, 매입형의 게이트 전극으로 한 종형의 전하 판독 트랜지스터를 갖는 CMOS 고체 촬상 장치를 도시한다.

- [0017] 이 CMOS 고체 촬상 장치(111)는, 기판 이면에서 광을 조사하는 이면 조사형의 고체 촬상 소자이다. 도면은, 화소부의 주요부을 도시한다. 이 CMOS 고체 촬상 장치(231)에서는, 반도체 기판(232)의 표면측에, 각 화소를 구성하는 화소 트랜지스터, 본 예에서는 전하 판독 트랜지스터(Tr1), 리셋 트랜지스터(Tr2) 및 앰프 트랜지스터(Tr3)가 형성된다. 이들 화소 트랜지스터의 하부에 포토 다이오드(PD)가 형성된다. 포토 다이오드(PD)는, 기판(112)의 내부에 전하 축적 영역이 되는 고불순물 영역(n+영역)(233A)과 저불순물 영역(n영역)(233B)으로 이루어지는 n형 반도체 영역(233)과, 그 표면측의 고불순물 농도의 p형 반도체 영역(p+영역)(241)에 의해 구성된다.

- [0018] 종형 전하 판독 트랜지스터(Tr1)는, 기판(232)의 표면부터 깊이 방향으로 포토 다이오드(PD)의 n형의 고농도 불순물 영역(n+영역)(233A) 내에 달하는 홈부(234) 내에 게이트 절연막(235)을 통하여 매입한 주상(柱狀)의 판독 게이트 전극(236)을 갖고서 구성된다. 기판(232)의 표면에는 게이트 절연막(235)에 접하도록 플로팅 디퓨전(FD) 영역이 되는 n형의 소스·드레인 영역(237)이 형성된다. 종형의 전하 판독 트랜지스터(Tr1)의 종형의 게이트 전극(236)은, 단위 화소(251)의 중심, 즉 포토 다이오드(PD)의 중심에 상당하는 위치에 형성된다. 포토 다이오드(PD)의 고불순물 농도 영역(n+영역)(233A) 내에 형성된 게이트 절연막(235)를 둘러싸도록, 고불순물 농도의 p형 반도체 영역(p+영역)(241)이 형성된다.

- [0019] 리셋 트랜지스터(Tr2)는, 기판(232)의 표면측의 한 쌍의 n형의 소스·드레인 영역(237 및 238)과 게이트 절연막을 통하여 형성된 평면형의 리셋 게이트 전극(243)에 의해 구성된다. 앰프 트랜지스터(Tr3)는, 기판(232)의 표면측의 한 쌍의 n형의 소스·드레인 영역(238 및 239)과, 게이트 절연막을 통하여 형성된 평면형의 게이트 전극(240)에 의해 구성된다. 또한, 이들 화소 트랜지스터(Tr1, Tr2, Tr3)가 형성된 기판(232)의 위에, 층간 절연막(245)을 통하여 복수층의 배선(246)을 형성한 다층 배선층이 형성된다. 또한, 도시하지 않지만, 기판(232)의 이면에는, 컬러 필터 및 그 위의 각 화소에 대응한 위치에 온 칩 마이크로 렌즈 등이 형성된다. 도 4에서, 부호 250은 화소 분리 영역을 나타낸다.

- [0020] 또한, 도시하지 않지만, 주변 회로부에서는, CMOS 트랜지스터로 이루어지는 신호 처리 회로 등이 형성된다. 이들의 CMOS 트랜지스터는, 평면형의 게이트 전극을 갖고서 구성된다.

- [0021] 또한, 화소 사이즈의 미세화에 수반하는 포화 전하량(Qs)의 저하나, 감도의 저하를 막는 방법에 대한 전혀 다른 어프로치로서, 일본 특개2005-223084서는, 매입형의 게이트 전극을 이용한 고체 촬상 장치가 제안되어 있다.

- [0022] 고체 촬상 장치로서, CMOS형의 고체 촬상 장치가 알려져 있다. 이 CMOS형의 고체 촬상 장치는, 포토 다이오드와, 복수의 트랜지스터, 이른바 MOS 트랜지스터에 의해, 2화소를 형성하고, 복수의 화소를 소요되는 패턴으로 배열하여 구성되어 있다. 이 포토 다이오드는, 수광량에 응한 신호 전하를 생성하고, 축적하는 광전 변환 소자이고, 복수의 MOS 트랜지스터는, 포토 다이오드로부터의 신호 전하를 전송하기 위한 소자이다.

- [0023] 또한, 화소 사이즈의 미세화에 수반하는 포화 전하량(Qs)의 저하나, 감도의 저하를 막는 방법에 대한 전혀 다른 어프로치로서, 하기 특허 문헌 4에는, 1화소에 있어서, 기판 내의 깊이 방향으로 복수의 포토 다이오드를 형성함으로서, 분광하는 방법이 기재되어 있다.

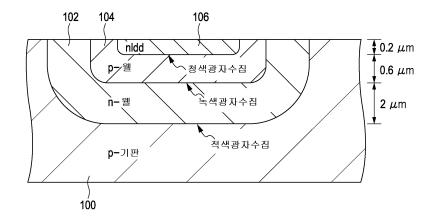

- [0024] 일본 특개2002-513145호에서는, 예를 들면, 도 2에 도시하는 바와 같이, p형의 Si 기판(100)중에, n형 반도체층 (102)/p형 반도체층(104)/n형 반도체층(106)의 3층 구조를 형성하고, 깊이 방향으로 얕은 쪽부터, 청, 녹, 적의 광을 광전 변환하여 취출하는 색 분리 방법이 기재되어 있다. 이 방법에서는, Si 기판(100) 표면에서, 각각의 층에 접속된 각각의 단자에 의해, 청, 녹, 적의 신호가 외부에 출력된다. 이것은, 파장의 길이와, 깊이 방향에

있어서의 광의 흡수의 성질을 이용한 것이다. 이로써, 1화소에서의 색 분광이 가능해지고, 위색(僞色)의 발생을 억제하는 것이 가능해진다. 따라서, 로우패스 필터가 불필요하게 된다. 또한, 컬러 필터를 사용하지 않기 때문에, 적, 녹, 청의 과장이 다른 색이 단위 화소 내에 입사한다. 이 때문에 광량의 손실도 적어진다. 그러나, 과장이 긴 적색의 광을 광전 변환하고, 전하를 축적하는 포토 다이오드는, 실리콘 기판 표면부터, 2μm 정도의 깊이에 형성되기 때문에, 기판 표면의 출력 단자와의 거리가 길고, 포토 다이오드에 축적된 신호 전하를 완전히 전송하는 것이 곤란하였다.

- [0025] 이와 같은 문제점을 개선하기 위해, 하기 일본 특개 2007-36202호에서는, 깊이 방향으로 적층한 복수의 포토 다이오드 사이에, 전위의 배리어를 배치하는 구성이 기재되어 있다. 이와 같이, 전위의 배리어를 배치함에 의해, 기판에 깊게 형성된 포토 다이오드에 축적된 신호 전하의 플로팅 디퓨전 영역으로의 판독을 용이하게 한 것이 가능하게 되어 있다. 그러나, 기판 표면부터 깊이 방향으로 떨어진 영역에 축적된 전하는, 기판 표면에 형성된 게이트 전극으로부터 주어지는 전계로는 충분한 포텐셜 변동을 주는 것은 곤란하고, 잔상이 발생하여 버린다.

- [0026] 도 3에, 상기 단위 화소(200)의 등가 회로를 도시한다. 포토 다이오드(PD)가 전하 판독 트랜지스터(Tr1)의 소스에 접속되고, 전하 판독 트랜지스터(Tr1)의 드레인이 리셋 트랜지스터(Tr2)의 소스에 접속된다. 리셋 트랜지스터(Tr2)의 드레인이 앰프 트랜지스터(Tr3)의 드레인에 접속된다. 앰프 트랜지스터(Tr3)의 소스가 수직 선택 트랜지스터(Tr4)의 드레인에 접속된다. 또한, 전하 판독 트랜지스터(Tr1)와 리셋 트랜지스터(Tr2)의 접속 중점에 대응하는 플로팅 디퓨전(FD)이 앰프 트랜지스터(Tr3)의 게이트에 접속된다. 또한 수직 선택 트랜지스터(Tr4)의 소스가 수직 신호선 221에 접속된다.

- [0027] 전하 판독 트랜지스터(Tr1)의 게이트에는, 수직 판독 펄스(φTG)가 인가되고, 리셋 트랜지스터(Tr2)의 게이트에 리셋 펄스(φR)가 인가되고, 수직 선택 트랜지스터(TR4)의 게이트에는 수직 선택 펄스(φSEL)가 인가된다.

#### 발명의 내용

- [0028] 이상과 같이, 고체 촬상 장치에 있어서, 화소 사이즈의 축소화에 수반하는 포화 전하량의 감소나, 감도의 저하를 방지하기 위해, 다양한 제안이 이루어지고 있다. 그러나, 근래의 화소 사이즈의 축소화가 급격하게 진행됨에 따라 충분한 포화 전하량을 얻는 것은 곤란하게 되고 있다.

- [0029] 또한, 일본 특개 2005-223084과 같은 매입형의 게이트 전극을 이용한 경우, 매입형의 게이트 전극을 형성하기 위해, 실리콘의 반도체 기관을 선택 에칭한다. 이 때문에, 선택 에칭에 의해 생기는 데미지에 기인한 결함으로 부터 발생하는 암전류를 억제할 필요가 있다.

- [0030] 상술한 점을 감안하여, 본 발명은, 포화 전하량(Qs)을 증가하고, 암전류의 억제를 도모한 고체 촬상 장치와 그 제조 방법을 제공하는 것이다.

- [0031] 또한, 본 발명은, 상기 고체 촬상 장치를 구비한 전자 기기를 제공하는 것이다.

- [0032] 상술한 점을 감안하여, 본 발명은, 신호 전하의 전송 효율을 향상시키고, 또한, 실효적인 화소 수의 향상을 도 모한 고체 촬상 장치를 제공하는 것이다. 또한, 그 고체 촬상 장치를 이용한 전자 기기를 제공하는 것이다.

- [0033] 근래, 화소 사이즈의 축소화가 급격하게 진행됨에 따라, 충분한 포화 전하량을 얻는 것이 곤란해지고 있다. 한편, 종형의 전하 판독 트랜지스터 구성의 고체 활상 장치에서도, 그 종형의 게이트 전극을 통상의 언도프 폴리실리콘을 퇴적한 후, 이온 주입으로 불순물을 도입하여 형성하는 경우에는, 양호한 게이트 전극이 얻기 어렵다. 즉, 불순물은 주로 언도프 폴리실리콘의 표면측에 이온 주입되고, 깊이 방향으로 균일하게 도입하는 것이 곤란해진다. 이 때문에, 이 종형의 판독 게이트 전극에 게이트 전압을 인가한 때에, 깊은 곳의 언도프 폴리실리콘이 공핍화(空乏化)하여, 깊이 방향의 채널 영역의 전위 컨트롤을 할 수가 어렵게 된다. 깊은 위치까지 불순물을 도입하기 위해, 고타입(高打入) 에너지로 불순물을 이온 주입한 경우에는, 게이트 전극 이외의 타부(他部)까지 불순물이 도입되어, 부적합함이 생긴다.

- [0034] 또한, 예를 들면, 종형의 게이트 전극을 메탈로 형성할 때는, 다른 주변 회로부의 MOS 트랜지스터의 게이트 전 극도 메탈로 형성하게 되고, 특히 p채널 MOS 트랜지스터의 게이트 전극으로서 바람직하지 않다. 화소 트랜지스터, 주변 회로부의 CMOS 트랜지스터에서는, 각각 임계치 전압 제어가 행하여지고 있고, 통상, n채널·트랜지스터는 n형 불순물 도프의 폴리실리콘의 게이트 전극이 사용된다. p채널·트랜지스터에서는 p형 불순물 도프의 폴리실리콘의 게이트 전극이 사용된다.

- [0035] 본 발명은, 상술한 점을 감안하여, 전하 판독 트랜지스터의 게이트 전극을 종형 구성으로 하여 화소 사이즈의

미세화를 가능하게 하면서, 각 트랜지스터에서의 채널 영역의 전위 컨트롤을 용이하게 하는 고체 촬상 장치 및 그 제조 방법을 제공하는 것이다.

- [0036] 또한, 본 발명은 해당 고체 촬상 장치를 구비한 카메라 등의 전자 기기를 제공하는 것이다

- [0037] 상기 과제를 해결하고, 본 발명의 목적을 달성하기 위해, 본 발명의 고체 촬상 장치는, 기판과, 포토 다이오드 와, 판독 게이트 전극과, 암전류 억제 영역과, 판독 채널 영역을 갖는다.

- [0038] 포토 다이오드는, 기판의 깊이 방향으로 복수 적충되어 형성되어 있다. 또한, 판독 게이트 전극은, 종형의 판독 게이트 전극이고, 기판의 깊이 방향으로 복수 적충된 포토 다이오드의 신호 전하를 판독하기 위해, 기판의 깊이 방향으로 매입되어 형성되어 있다.

- [0039] 암전류 억제 영역은, 제 1 도전형의 반도체 영역에 의해 판독 게이트 전극의 저부, 및 측면을 피복하여 형성되어 있고, 판독 게이트 측면에는 균일한 폭으로 형성되어 있다.

- [0040] 판독 채널 영역은, 판독 게이트 전극의 측면에 형성된 암전류 억제 영역과 포토 다이오드 사이의 영역에, 제 2 도전형의 반도체 영역에 의해 형성되어 있다.

- [0041] 본 발명의 고체 촬상 장치에서는, 기판의 깊이 방향으로 복수 적충된 포토 다이오드에 의해, 신호 전하가 축적된다. 이로써, 포화 전하량이 증가한다. 또한, 종형의 판독 게이트 전극으로 그 신호 전하를 판독하기 때문에, 신호 전하의 전송 남겨짐을 막을 수 있다. 또한, 판독 게이트 전극 측면에 형성된 암전류 억제 영역은, 균일한폭으로 형성되기 때문에, 판독 특성의 편차가 저감된다.

- [0042] 또한, 본 발명의 고체 촬상 장치의 제조 방법은, 기판의 깊이 방향으로 적충한 복수의 포토 다이오드를 형성하는 공정, 기판 상부에 마스크층 및 포토레지스트막을 형성하는 공정을 갖는다. 다음에, 포토 리소그래피법에 의해 포토레지스트막을 패턴 형성하고, 패턴 형성된 상기 포토레지스트막을 마스크로 하여, 마스크층을 에칭하고, 기판 표면에 달하는 개구부를 형성하는 공정을 갖는다. 다음에, 개구부를 통하여, 기판에 제 1 도전형의 불순물을 이온 주입하는 공정, 개구부를 통하여, 기판의 제 1 도전형의 불순물이 이온 주입된 영역보다도 기판 표면측의 영역에 제 2 도전형의 불순물을 이온 주입하는 공정을 갖는다. 다음에, 레지스트막을 제거하는 공정, 개구부를 포함하는 마스크층 표면에 제 1의 측벽 스페이서를 형성하고, 개구부의 지름을 축소하는 공정, 축소된 개구부를 통하여, 제 1 도전형의 불순물을 이온 주입하는 공정을 갖는다. 다음에, 축소된 개구부의 측벽에 제 2의 측벽 스페이서를 형성하고, 개구부의 지름을 더욱 축소하는 공정, 축소된 개구부를 마스크로 하여, 기판을 에칭하고, 포토 다이오드에 인접하는 홈부를 형성하는 공정을 갖는다. 다음에, 홈부의 저부 및 측면을 피복하여 게이트 절연막을 형성하는 공정, 게이트 절연막이 형성된 홈부에 전극 재료를 매입하여 판독 게이트 전극을 형성하는 공정을 갖는다.

- [0043] 본 발명의 고체 촬상 장치의 제조 방법에서는, 개구부의 지름을 단계적으로 축소하면서, 소망하는 불순물이 이 온 주입되는 영역이나, 홈부를 형성하여 있기 때문에, 이들의 이온 주입되는 영역이나, 홈부는, 셀프 얼라인으로 형성된다. 이로써, 소정의 영역에 이온 주입하기 위해서나, 홈부를 형성하기 위해 마스크 맞춤을 행할 필요가 없고, 정밀도 좋게 판독 게이트 전극이나, 그 주변의 반도체 영역을 형성할 수 있다.

- [0044] 또한, 본 발명의 전자 기기는, 광학 렌즈와, 고체 촬상 장치와, 신호 처리 회로를 포함하여 구성된다. 그리고, 고체 촬상 장치는, 기판과, 포토 다이오드와, 판독 게이트 전극과, 암전류 억제 영역과, 판독 채널 영역을 갖는다.

- [0045] 포토 다이오드는, 기판의 깊이 방향으로 복수 적충되어 형성되어 있다. 또한, 판독 게이트 전극은, 종형의 판독 게이트 전극이고, 기판의 깊이 방향으로 복수 적충된 포토 다이오드의 신호 전하를 판독하기 위해, 기판의 깊이 방향으로 매입되어 형성되어 있다.

- [0046] 암전류 억제 영역은, 제 1 도전형의 반도체 영역에 의해 판독 게이트 전극의 저부, 및 측면을 피복하여 형성되어 있고, 판독 게이트 측면에는 균일한 폭으로 형성되어 있다.

- [0047] 판독 채널 영역은, 판독 게이트 전극의 측면에 형성된 암전류 억제 영역과 포토 다이오드 사이의 영역에, 제 2 도전형의 반도체 영역에 의해 형성되어 있다.

- [0048] 본 발명의 전자 기기에서는, 광학 렌즈로부터 입사된 광은, 고체 촬상 장치에서 신호 전하로 변환되고, 신호 처리 회로를 통하여, 영상 신호로서 출력된다. 또한, 고체 촬상 장치에서는, 기판의 깊이 방향으로 복수 적충된 포토 다이오드에 의해, 신호 전하가 축적된다. 이로써, 포화 전하량이 증가한다. 또한, 종형의 판독 게이트 전

극으로 그 신호 전하를 판독하기 때문에, 신호 전하의 전송 남겨짐을 막을 수 있다. 또한, 판독 게이트 전극 측면에 형성된 암전류 억제 영역은, 균일한 폭으로 형성되기 때문에, 판독 특성의 편차가 저감된다.

- [0049] 상기 과제를 해결하고, 본 발명의 목적을 달성하기 위해, 본 발명의 고체 촬상 장치는 이하의 구성을 갖는다. 기판과, 기판의 깊이 방향으로 적충된 복수의 포토 다이오드와, 평면형 게이트 전극과, 종형 게이트 전극을 포함하여 구성되는 화소를 갖는다. 평면형 게이트 전극이란, 복수의 포토 다이오드중 기판 표면측의 포토 다이오드의 신호 전하를 판독하기 위해 기판 표면에 형성된 게이트 전극이다. 종형 게이트 전극이란, 복수의 포토 다이오드중 기판 표면부터 깊이 방향의 깊은 위치의 포토 다이오드의 신호 전하를 판독하기 위해 기판의 깊이 방향으로 매입되어 형성된 게이트 전극이다. 또한, 복수의 포토 다이오드 사이에는, 복수의 포토 다이오드 사이를 분리하는 포토 다이오드 분리 영역을 갖는다.

- [0050] 본 발명의 고체 촬상 장치에서는, 기판의 깊이 방향으로 형성된 복수의 포토 다이오드중, 표면측에 형성된 포토 다이오드에 축적된 신호 전하는, 평면형 게이트 전극에 의해 판독된다. 또한, 기판 표면부터 깊이 방향으로 깊은 위치의 포토 다이오드에 축적된 신호 전하는, 종형 게이트 전극에 판독된다.

- [0051] 또한, 본 발명의 전자 기기는, 광학 렌즈와, 고체 촬상 장치와, 신호 처리 회로를 포함하여 구성된다. 그리고, 고체 촬상 장치는, 기판과, 기판의 깊이 방향으로 적충된 복수의 포토 다이오드와, 평면형 게이트 전극과, 종형 게이트 전극을 포함하여 구성되는 화소를 갖는다. 평면형 게이트 전극이란, 복수의 포토 다이오드중 기판 표면 측의 포토 다이오드의 신호 전하를 판독하기 위해 기판 표면에 형성되는 게이트 전극이다. 종형 게이트 전극이란, 복수의 포토 다이오드중 기판 표면부터 깊이 방향의 깊은 위치의 포토 다이오드의 신호 전하를 판독하기 위해 기판의 깊이 방향으로 매입되어 형성된 게이트 전극이다. 또한, 고체 촬상 장치는, 복수의 포토 다이오드 사이에는, 복수의 포토 다이오드 사이를 분리하는 포토 다이오드 분리 영역을 갖는다.

- [0052] 본 발명의 전자 기기에서는, 광학 렌즈로부터 입사된 광은, 고체 촬상 장치에서 신호 전하로 변환되고, 신호 처리 회로를 통하여, 영상 신호로서 출력된다. 그리고, 본 발명의 전자 기기에 사용되는 고체 촬상 장치에서는, 기판의 깊이 방향으로 형성된 복수의 포토 다이오드중, 표면측에 형성된 포토 다이오드에 축적된 신호 전하는, 평면형 게이트 전극에 의해 판독된다. 또한, 기판 표면부터 깊이 방향으로 깊은 위치의 포토 다이오드에 축적된 신호 전하는, 종형 게이트 전극에 판독된다.

- [0053] 본 발명에 관한 고체 촬상 장치는, 기판과, 기판 내에 매입된 포토 다이오드와, 포토 다이오드의 신호 전하를 판독하기 위해 상기 기판의 깊이 방향으로 매입되어 형성된, 전하 판독 트랜지스터의 종형의 게이트 전극과, 종형의 판독 게이트 전극과는 다른 전극 재료로 형성된, 다른 트랜지스터의 평면형의 게이트 전극을 갖는다.

- [0054] 본 발명의 고체 촬상 장치에서는, 전하 판독의 종형의 게이트 전극과, 다른 트랜지스터의 평면형의 게이트 전극과 전극 재료를 달리 하고 있다. 이 때문에, 전하 판독 트랜지스터에 있어서, 깊이 방향으로 균일한 종형의 게이트 전극을 형성할 수 있다. 한편, 다른 트랜지스터의 평면형의 게이트 전극에서는, 종형의 게이트 전극 재료에 제약된 일 없이, 필요한 성질을 갖는 게이트 전극을 형성할 수 있다.

- [0055] 본 발명에 관한 고체 촬상 장치의 제조 방법은, 기판의 표면상 제 1의 연마 스토퍼막에 홈을 형성하여 소자 분리 영역을 형성하는 제 1 공정과, 제 1의 연마 스토퍼막상에 제 2의 연마 스토퍼막을 형성하는 제 2 공정과, 제 1, 제 2의 연마 스토퍼막에 홈을 형성하고, 해당 홈 내를 매입하도록 게이트 절연막을 통하여, 다른 트랜지스터의 평면형의 게이트 전국 재료를 형성하는 제 3 공정을 갖는다. 또한, 제 1, 제 2의 연마 스토퍼막의타부(他部)에 형성한 홈을 통하여 기판 내에 세로 홈을 형성하고, 해당 세로 홈 내를 매입하도록 게이트 절연막을 통하여 평면형의 게이트 전국 재료와는 다른 재질의, 전하 판독 트랜지스터의 종형의 게이트 전국 재료를 형성하는 제 4 공정을 갖는다. 또한, 제 2의 연마 스토퍼막까지 평면형의 게이트 전국 재료와 종형의 게이트 전국 재료를 일괄하여 평탄화하는 제 5의 공정과, 제 1, 제 2의 연마 스토퍼막을 제거하고, 종형의 게이트 전국과 평면형의 게이트 전국을 형성하는 제 6 공정을 갖는다. 또한, 기판에 포토 다이오드를 매입하도록 이온 주입법으로 형성하는 제 7 공정을 갖는다.

- [0056] 본 발명의 고체 촬상 장치의 제조 방법에서는, 전하 판독 트랜지스터와, 다른 트랜지스터를, 서로의 종형의 게이트 전극 재료, 평면형의 게이트 전극 재료에 제약되는 일 없고, 각각 필요한 성질을 갖는 게이트 전극을 형성할 수 있다.

- [0057] 본 발명에 관한 전자 기기는, 광학 렌즈와, 고체 촬상 장치와, 고체 촬상 장치의 출력 신호를 처리하는 신호 처리 회로를 구비한다. 고체 촬상 장치는, 기판과, 기판 내에 매입된 포토 다이오드와, 포토 다이오드의 신호 전하를 판독하기 위해 기판의 깊이 방향으로 매입되어 형성된, 전하 판독 트랜지스터의 종형의 게이트 전극과, 종

형의 판독 게이트 전극과는 다른 전극 재료로 형성된, 다른 트랜지스터의 평면형의 게이트 전극을 갖는다.

- [0058] 본 발명의 전자 기기에서는, 상기 고체 활상 장치를 구비하기 때문에, 고체 활상 장치에서의 전하 판독 트랜지스터, 다른 트랜지스터가, 서로의 게이트 전극 재료에 제약되는 일 없이, 각각 양호한 게이트 전극을 갖고서 구성된다.

- [0059] 본 발명에 관한 고체 촬상 장치에 의하면, 단위 화소의 포화 전하량(Qs)이 증가하고, 암전류의 발생을 억제하여 백상(白傷)의 발생이 억제된 고체 촬상 장치를 제공할 수 있다.

- [0060] 본 발명의 고체 촬상 장치의 제조 방법에 의하면, 암전류 억제 영역이나, 판독 채널 영역을 정밀도 좋게 형성하고, 암전류의 발생을 억제하여 백상(白傷)의 발생이 억제된 고체 촬상 장치를 제조할 수 있다.

- [0061] 본 발명에 관한 전자 기기에 의하면, 상기 본 발명의 고체 촬상 장치를 구비함에 의해, 감도의 향상, 고화질화 된 전자 기기를 제공할 수 있다.

- [0062] 본 발명에 의하면, 고체 촬상 장치에 있어서, 기판 내에 형성된 복수층의 포토 다이오드에 축적된 신호 전하를 각각의 깊이에 대응한 게이트 전극에서 판독할 수 있기 때문에, 신호 전하의 전송 남겨짐을 저감할 수 있다. 즉, 전송 효율이 향상한다. 또한, 기판 내에 복수층의 포토 다이오드를 가지며, 또한, 그 포토 다이오드를 분리함으로써, 1화소 내에서 복수의 색이 검출된다. 이로써, 실효적인 화소 수가 향상한다.

- [0063] 본 발명에 의할 수 있다면, 고체 촬상 장치에 있어서, 전하 판독 트랜지스터의 게이트 전극을 종형 구성으로 하여 화소 사이즈의 미세화를 가능하게 하면서, 각 트랜지스터에서의 채널 영역의 전위 컨트롤을 용이하게 한다.

# 발명의 실시를 위한 구체적인 내용

- [0064] 이하, 도 5 내지 도 35를 참조하여 본 발명의 실시의 형태를 설명한다.

- [0065] <제 1의 실시 형태>

- [0066] [고체 촬상 장치의 전체 구조]

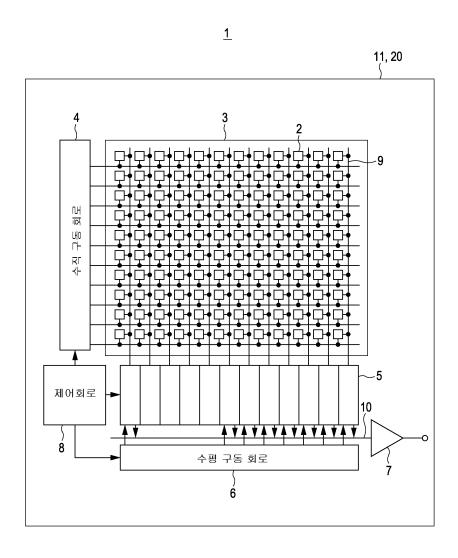

- [0067] 우선, 도 5를 이용하여, 본 발명의 제 1의 실시 형태의 CMOS형의 고체 촬상 장치, 즉, CMOS 이미지 센서의 전체 구조에 관해 설명한다.

- [0068] 이하, 1, 101 은 고체 촬상 장치, 2는 화소, 2a는 제 1의 화소, 2b는 제 2의 화소, 3는 촬상 영역(화소부), 4는 수직 구동 회로, 5는 칼럼 신호 처리 회로, 6은 수평 구동 회로, 7은 출력 회로, 8은 제어 회로, 9는 수직 신호 선, 10은 수평 신호선, 11, 20은 기판, 21은 p+형 반도체 영역, 22는 n+형 반도체 영역, 23은 p+형 반도체 영역, 24는 n+형 반도체 영역, 25는 n형 반도체 영역, 26은 종형의 판독 게이트 전국, 27은 게이트 절연막, 28은 판독 채널 영역, 29, 30은 암전류 억제 영역, 31은 리셋 전국, 32, 34는 소스·드레인 영역, 33은 앰프 게이트 전국, 35는 화소 분리 영역을 나타낸다.

- [0069] 31, 33, 87, 88은 평면형의 게이트 전극을 나타낸다.

- [0070] 도 5에 도시하는 고체 촬상 장치(1)는, Si로 이루어지는 기판(11)상에 배열된 복수의 화소(2)로 구성된 촬상 영역(3)과, 촬상 영역(3)의 주변 회로로서의 수직 구동 회로(4)와, 칼럼 신호 처리 회로(5)와, 수평 구동 회로(6)와, 출력 회로(7)와, 제어 회로(8) 등을 갖고서 구성된다.

- [0071] 화소(2)는, 광전 변환 소자인 포토 다이오드와, 복수의 MOS 트랜지스터로 구성되고, 기판(11)상에, 2차원 어레이형상으로 규칙적으로 복수 배열되어 형성되어 있다.

- [0072] 활상 영역(3)은, 2차원 어레이형상으로 규칙적으로 복수 배열된 화소(2)로 구성된다. 그리고, 활상 영역(3)은, 실제로 광을 수광하고, 광전 변환에 의해 생성된 신호 전하를 축적할 수 있는 유효 화소 영역과, 유효 화소 영역의 주위에 형성되고, 흑 레벨의 기준이 되는 광학적 흑을 출력하기 위한 흑 기준 화소 영역으로 구성된다.

- [0073] 본 예의 고체 촬상 장치(1)는, 반도체 기판(20) 예를 들면 실리콘 기판에 복수의 광전 변환 소자를 포함하는 화소(2)가 규칙적으로 2차원적으로 배열된 화소부(이른바 촬상 영역)(3)와, 주변 회로부를 갖고서 구성된다. 화소(2)는, 광전 변환 소자가 되는 예를 들면 포토 다이오드와, 복수의 화소 트랜지스터(이른바 MOS 트랜지스터)를 갖고서 이루어진다. 복수의 화소 트랜지스터는, 예를 들면 전하 판독 트랜지스터, 리셋 트랜지스터 및 증폭 트랜지스터의 3개의 트랜지스터로 구성할 수 있다. 그 밖에, 선택 트랜지스터 추가하여 4개의 트랜지스터로 구성

할 수도 있다. 나아가서는, 복수의 화소를 1조의 화소 트랜지스터로 공유하는 구성으로 할 수도 있다. 이 공유 화소 구성의 경우는, 전하 판독 트랜지스터는 화소 수에 대응하여 복수 마련하고, 다른 리셋 트랜지스터, 앰프 트랜지스터, 수직 선택 트랜지스터를 각 하나 갖는다.

- [0074] 주변 회로부는, 수직 구동 회로(4)와, 칼럼 신호 처리 회로(5)와, 수평 구동 회로(6)와, 출력 회로(7)와, 제어 회로(8) 등을 갖고서 구성된다.

- [0075] 제어 회로(8)는, 수직 동기 신호, 수평 동기 신호 및 마스터 클록에 의거하여, 수직 구동 회로(4), 칼럼 신호 처리 회로(5), 및 수평 구동 회로(6) 등의 동작의 기준이 되는 클록 신호나 제어 신호 등을 생성한다. 그리고, 제어 회로(8)에서 생성된 클록 신호나 제어 신호 등은, 수직 구동 회로(4), 칼럼 신호 처리 회로(5) 및 수평 구 동 회로(6) 등에 입력된다.

- [0076] 수직 구동 회로(4)는, 예를 들면 시프트 레지스터에 의해 구성되고, 촬상 영역(3)의 각 화소(2)를 행 단위로 순 차적으로 수직 방향에 선택 주사한다. 그리고, 각 화소(2)의 포토 다이오드에서 수광량에 응하여 생성한 신호 전하에 의거한 화소 신호를, 수직 신호선을 통하여 칼럼 신호 처리 회로(5)에 공급한다.

- [0077] 칼럼 신호 처리 회로(5)는, 예를 들면, 화소(2)의 열마다 배치되어 있고, 1행분의 화소(2)로부터 출력되는 신호를 화소열마다 흑 기준 화소 영역(도시하지 않지만, 유효 화소 영역의 주위에 형성된다)으로부터의 신호에 의해, 노이즈 제거나 신호 증폭 등의 신호 처리를 행한다. 칼럼 신호 처리 회로(5)의 출력단(出力端)에는, 수평 선택 스위치(도시 생략)가 수평 신호선(10)과의 사이에 마련되어 있다.

- [0078] 수평 구동 회로(6)는, 예를 들면 시프트 레지스터에 의해 구성되고, 수평 주사 펄스를 순차적으로 출력함에 의해, 칼럼 신호 처리 회로(5)의 각각을 순번대로 선택하고, 칼럼 신호 처리 회로(5)의 각각으로부터 화소 신호를 수평 신호선(10)에 출력시킨다.

- [0079] 출력 회로(7)는, 칼럼 신호 처리 회로(5)의 각각으로부터 수평 신호선(10)을 통하여, 순차적으로 공급되는 신호 에 대해, 신호 처리를 행하여 출력한다.

- [0080] 이하에 설명한 제 1 내지 제 5의 실시 형태에서의 고체 촬상 장치는, 도 5에서의 고체 촬상 장치(1)를 구성하는 것이고, 특히 유효 촬상 영역에서의 화소(2)의 단면 구성을 도시하는 것이다.

- [0081] 상술한 고체 촬상 장치에 있어서, 광을 기판 이면측부터 입사시키는 이면 조사형으로 구성할 때는, 화소부(3) 및 주변 회로부가 형성된 반도체 기판의 표면측의 상에, 층간 절연막을 통하여 다층 배선층이 형성되고, 이면측이 광 입사면(이른바 수광면)이 된다. 이면측의 화소부(3)상에 평탄화막을 통하여 온 칩 컬러 필터, 또한 그 위에 온 칩 마이크로 렌즈가 형성된다.

- [0082] 상술한 고체 촬상 장치에 있어서, 광을 기판 표면측부터 입사시키는 표면 조사형으로 구성할 때는, 화소부(3) 및 주변 회로부가 형성된 기판의 표면측의 상방에, 층간 절연막을 통하여 다층 배선층이 형성된다. 화소부(3)에 서는, 다층 배선층의 위에 평탄화막을 통하여 온 칩 컬러 필터, 또한 그 위에 온 칩 마이크로 렌즈가 형성된다.

- [0083] [고체 촬상 장치의 구성]

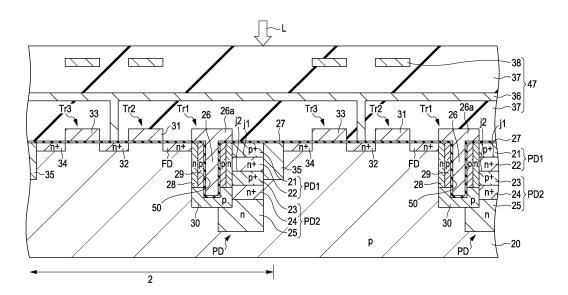

- [0084] 도 6에, 본 발명에 관한 고체 촬상 장치의 제 1 실시의 형태를 도시한다.

- [0085] 도 6에 본 실시 형태 예에 관한 고체 촬상 장치(1)의 촬상 영역(3)의 개략 단면 구성을 도시한다.

- [0086] Tr1은 전하 판독 트랜지스터, Tr2는 리셋 트랜지스터, Tr3은 앰프 트랜지스터, PD[PD1, PD2]는 포토 다이오드이다. 본 실시 형태 예의 고체 촬상 장치(1)는, 기판(20)과, 기판(20)에 형성된 포토 다이오드(PD)와, 포토 다이오드(PD)에서 얻어지는 신호 전하를 판독하기 위한 복수의 화소 트랜지스터와, 그 화소 트랜지스터를 구동하기위한 배선층(47)을 갖는다.

- [0087] 이하의 설명에서는, 본 발명의 제 1 도전형의 반도체 영역으로서 p형 반도체 영역을 이용하고, 제 2 도전형으로 서 n형 반도체 영역을 이용한다. 또한, n형 불순물 농도가 엷은 순서로, n형, n+형으로 표기하고, p형 불순물 농도가 엷은 순서로, p형, p+형으로 표기한다. 또한, 본 실시 형태 예에서는, 기판(20)의 표면측부터 광(L)이 조사되는, 표면 조사형의 고체 촬상 장치로서 설명한다.

- [0088] 기판(20)은, p형 반도체로 이루어지는 실리콘으로 구성되어 있다.

- [0089] 포토 다이오드(PD)는, 도 5에 도시하는 화소(2)에 대응하여, 기판(20) 내의 수직 방향 및 수평 방향으로, 매트 릭스형상으로 복수개 형성되어 있다. 이 포토 다이오드(PD)는 화소(2)에서, 광을 수광하는 수광부를 구성하는

것이다. 포토 다이오드(PD)는, p형의 반도체 영역과, n형의 반도체 영역의 접합부인 pn접합(j1, j2)을 갖고서, 깊이 방향으로 형성된 복수개의 포토 다이오드, 본 실시 형태 예에서는 제 1의 포토 다이오드(PD1)와 제 2의 포토 다이오드(PD2)로 구성되어 있다. 구체적으로는, 기판(20) 표면부터 차례로 형성된 p+형 반도체 영역(21), n+형 반도체 영역(22), p+형 반도체 영역(23), n+형 반도체 영역(24), n형 반도체 영역(25)이 형성되어 있고, p+형 반도체 영역(21)과 n+형 반도체 영역(22)과 pn접합(j1)에 의해 제 1의 포토 다이오드(PD1)가 구성되어 있다. 또한, 그 제 1의 포토 다이오드(PD1)의 하방에 연속하여 형성된 p+형 반도체 영역(23)과 n+형 반도체 영역(24)와의 pn접합(j2)에 의해 제 2의 포토 다이오드(PD2)가 구성되어 있다.

- [0090] 이와 같은 구성을 갖는 포토 다이오드(PD)에서는, 수광부인 포토 다이오드(PD)에 입사된 광(L)은, 이곳에서 광전 변환되고, 광전 변환에 의해 얻어진 신호 전하는, pn접합(j1)에 의해 형성되어 있는 각각의 전위의 우물(井戶)에 축적된다.

- [0091] 화소 트랜지스터는, 전하 판독 트랜지스터(Tr1)와, 리셋 트랜지스터(Tr2)와, 앰프 트랜지스터(Tr3)에 의해 구성되어 있다.

- [0092] 우선, 전하 판독 트랜지스터(Tr1)는, 화소(2)마다 형성된 포토 다이오드(PD)에 인접하여 형성된 판독 게이트 전 극(26)과, 플로팅 디퓨전 영역(FD)으로 구성되어 있다.

- [0093] 판독 게이트 전극(26)은, 기판(20)의 표면부터 깊이 방향으로 형성된 홈부(50)에, 게이트 절연막(27)를 통하여 전극 재료가 매입됨에 의해 형성된 주상(柱狀)의 종형 게이트 전극이다. 또한, 이 종형 게이트 전극으로 구성되는 판독 게이트 전극(26)의 상부는, 배선 인출용의 평면형 전극부(26a)가 형성되어 있다. 판독 게이트 전극(26) 저부는, 제 2의 포토 다이오드(PD2)를 구성하는 pn접합(j2)의 깊이보다도 깊은 위치에 달하도록, 기판(20) 내에 종형으로 형성되어 있다.

- [0094] 그리고, 게이트 절연막(27)을 포함하는 판독 게이트 전극(26)의 저부, 및 측면은, p형 반도체 영역으로 이루어지는 암전류 억제 영역(30, 29)에 의해 피복되어 있다. 특히, 판독 게이트 전극(26)의 측면에 형성된 암전류 억제 영역(29)은, 판독 게이트 전극(26)의 측면 일주(一周)에 있어서, 균일한 폭이 되도록 형성되어 있다. 그리고, 판독 게이트 전극(26)의 측면에 형성된 암전류 억제 영역(29)의 주위에는, n형 반도체 영역으로 이루어지는 판독 채널 영역(28)이 형성되어 있다. 본 실시 형태 예에 있어서, 이 판독 채널 영역(28)은 판독 게이트 전극(26)의 측면에 형성된 암전류 억제 영역(29)의 주위 전체를 피복하도록 형성되어 있다. 그리고, 이 판독 채널 영역(28)의 한쪽의 측면은, 제 1의 포토 다이오드(PD1) 및 제 2의 포토 다이오드(PD2)를 구성하는 pn접합(j1, j2)에 접하도록 형성되어 있다. 또한, 판독 채널 영역(28)의 다른쪽의 측면은, 기판(20) 표면에 형성된 플로팅 디퓨전 영역(FD)에 접하도록 형성되어 있다.

- [0095] 플로팅 디퓨전 영역(FD)은, 종형의 판독 게이트 전극(26)의, 포토 다이오드(PD)에 접하는 측과는 반대측의 측면에 형성된 판독 채널 영역(28)에 접하는 위치의, 기판(20) 표면측에, 고농도 불순물 농도의 n+형 반도체 영역에의해 형성되어 있다. 이 플로팅 디퓨전 영역(FD)은, 포토 다이오드(PD)에 축적된 신호 전하가 판독되어 오는 영역이다.

- [0096] 전하 판독 트랜지스터(Tr1)에서는, 판독 게이트 전극(26)에 정의 전압이 인가된 경우에는, 판독 채널 영역(28)의 전위가 변동하고, 포토 다이오드(PD)와 플로팅 디퓨전 영역(FD)이 전기적으로 접속된다.

- [0097] 본 실시의 형태에 관한 고체 촬상 장치(101)는, 제 1 도전형, 예를 들면 p형의 실리콘 반도체 기판(20)에 화소 분리 영역(35)이 형성되고, 이 화소 분리 영역(35)에서 구획된 영역에 포토 다이오드(PD)와 화소 트랜지스터로 이루어지는 단위 화소(2)가 형성된다.

- [0098] 단위 화소(2)에서는, 반도체 기판(20) 내에, 복수의 광전 변환 소자가 되는 포토 다이오드(PD)[PD1, PD2]를 층 상(層狀)으로 형성하고, 전하 판독 트랜지스터(Tr1)를 종형 트랜지스터로 형성하여 구성된다. 즉, 복수층의 포토 다이오드(PD)[PD1, PD2]는, 반도체 기판(20)의 깊이 방향으로 제 2 도전형인 n형의 반도체 영역과, 제 1 도 전형인 p형의 반도체 영역이 교대로 적층되어 구성된다.

- [0099] 화소 분리 영역(35)은, 도 6에서는 예를 들면 p형 반도체 영역으로 형성할 수 있다. 그 밖에, 후술하는 제조 방법에서 도시하는 바와 같이 기판(20)상에 게이트 절연막보다 두꺼운 절연층과 그 바로 아래의 p형 반도체 영역으로 형성할 수도 있다. 화소 내의 소자 분리 영역도, 도시하지 않지만, 화소 분리 영역과 같은 구성을 취한다.

- [0100] 종형의 전하 판독 트랜지스터(Tr1)에서는, 반도체 기판(20)에 깊이 방향으로 수직으로 늘어나는 세로 홈부(50) 가 형성되고, 세로 홈부(50)에 게이트 절연막(27)을 통하여 주상의 판독 게이트 전극(26)이 매입되도록 형성된

다. 판독 게이트 전극(26)은, 그 상부의 인출 전극부(26a)가 반도체 기판(20)의 표면에 따르도록 내달아(張出) 형성되고, 그 인출 전극부(26a)의 내달은(張出) 부분에 근접하도록, 기판 표면에 n형 반도체 영역에 의한 플로팅 디퓨전 영역(FD)이 형성된다. 전하 판독 트랜지스터(Tr1)는, 포토 다이오드(PD)[PD1 내지 PD2]의 단(端)에 형성된다.

- [0101] 즉, 종형의 전하 판독 트랜지스터(Tr1)는, 포토 다이오드(PD)와, 플로팅 디퓨전 영역(FD)과, 양 영역(PD 및 FD)의 사이의 기판상에 게이트 절연막(27)을 통하여 형성된 종형의 판독 게이트 전극(26)을 갖고서 구성된다.

- [0102] 제 1 포토 다이오드(PD1)는, 반도체 기판(20)의 표면측의 위치에 pn접합이 형성되도록, p+반도체 영역(21)과 그 아래의 n+반도체 영역(22)을 갖고서 구성된다. 제 2 포토 다이오드(PD2)는, 제 1 포토 다이오드(PD1)의 하층에 pn접합이 형성되도록, p+반도체 영역(23)과 그 아래의 n+형 반도체 영역(24)과 또한 그 아래의 n반도체 영역(25)을 갖고서 구성된다.

- [0103] 판독 게이트 전극(26)은, 그 저부가 제 2 포토 다이오드(PD2)를 구성하는 pn접합의 깊이보다도 깊은 위치에 달하도록 종형으로 형성된다.

- [0104] 그리고, 게이트 절연막(27)을 포함하는 판독 게이트 전극(26)의 저부, 및 측면은, p형 반도체 영역으로 이루어지는 암전류 억제 영역(30, 29)에 의해 피복되어 있다. 특히, 판독 게이트 전극(26)의 측면에 형성된 암전류 억제 영역(29)은, 판독 게이트 전극(26)의 측면 일주에 있어서, 균일한 폭이 되도록 형성되어 있다. 그리고, 판독 게이트 전극(26)의 측면에 형성된 암전류 억제 영역(29)의 주위에는, n형 반도체 영역으로 이루어지는 채널 영역(28)이 형성되어 있다. 본 실시 형태 예에서, 이 채널 영역(28)은 판독 게이트 전극(26)의 측면에 형성된 암전류 억제 영역(29)의 주위 전체를 피복하도록 형성되어 있다. 그리고, 이 채널 영역(28)의 한쪽의 측면은, 제 1의 포토 다이오드(PD1) 및 제 2의 포토 다이오드(PD2)를 구성하는 pn접합에 접하도록 형성되어 있다. 또한, 채널 영역(28)의 다른쪽의 측면은, 기판(20) 표면에 형성된 플로팅 디퓨전 영역(FD)에 접하도록 형성되어 있다.

- [0105] 플로팅 디퓨전 영역(FD)은, 종형의 판독 게이트 전극(26)의, 포토 다이오드(PD)에 접하는 측과는 반대측의 측면 에 형성된 채널 영역(28)에 접하는 위치의, 기판(20) 표면측에, 고농도 불순물 농도의 n+반도체 영역에 의해 형성되어 있다.

- [0106] 리셋 트랜지스터(Tr2)는, 플로팅 디퓨전 영역(FD)과, n형의 소스·드레인 영역(32)과, 양 영역(FD 및 32)와의 사이의 기판상에 게이트 절연막(27)을 통하여 형성된 평면형의 리셋 게이트 전극(31)을 갖고서 구성된다.

- [0107] 앰프 트랜지스터(Tr3)는, 한 쌍의 n형의 소스·드레인 영역(32 및 34)과, 양 영역(32 및 34)의 사이의 기판상에 게이트 절연막(27)을 통하여 형성된 평면형의 앰프 게이트 전극(33)을 갖고서 구성된다.

- [0108] 그 밖에, 도시하지 않지만, 필요에 응하여, 수직 선택 트랜지스터 등이 형성된다.

- [0109] 또한, 도시하지 않지만, 화소부의 주변에 배치되는 주변 회로부에서는, 예를 들면 로직 회로를 구성하는 CMOS 트랜지스터가 형성된다. n채널 MOS 트랜지스터는, p형 반도체 영역에 한 쌍의 n형의 소스·드레인 영역과, 양 영역의 사이의 기판상에 게이트 절연막을 통하여 형성된 평면형의 게이트 전극을 갖고서 구성된다. 또한, p채널 MOS 트랜지스터는, n형 반도체 영역에 한 쌍의 p형의 소스·드레인 영역과, 양 영역의 사이의 기판상에 게이트 절연막을 통하여 형성된 평면형의 게이트 전극을 갖고서 구성된다.

- [0110] 이상과 같이, 포토 다이오드(PD) 및, 전하 판독 트랜지스터(Tr1), 리셋 트랜지스터(Tr2), 앰프 트랜지스터(Tr3) 등의 소망하는 화소 트랜지스터에 의해, 각 화소(2)가 구성되고, 기판(20)에 형성된 화소(2)는 화소 분리 영역 (35)에 의해 인접하는 화소(2)와 분리되어 있다. 그리고, 화소부에서의 포토 다이오드(PD)나, 소망하는 화소 트랜지스터가 형성된 기판(20) 상부, 및 주변 회로부에서의 기판(20) 상부에는, 전원 배선(36)을 포함하는 다층의 배선(38)이 층간 절연막(37)을 통하여 형성된 배선층(47)이 형성되어 있다.

- [0111] 상술한 고체 촬상 장치(101)에서는, 기판(20)의 표면측부터 광(L)을 조사하고, 이 광(L)을 포토 다이오드(PD)에서 수광하는 구성으로 한다. 이 때문에, 도시하지 않지만, 기판(20) 상부의 배선층(47) 상부에는, 온 칩 컬러 필터나, 각 화소(2)에 대응한 위치에 온 칩 렌즈가 형성되어 있다.

- [0112] 또한, 본 실시의 형태에서는, 전하 판독 트랜지스터(Tr1)의 종형의 판독 게이트 전극(26)과, 다른 게이트 전극을 서로 다른 재질의 전극 재료로 형성된다. 즉, 종형의 판독 게이트 전극(26)과, 화소 트랜지스터(Tr2 및 Tr 3)의 평면형의 리셋 게이트 전극(31) 및 앰프 게이트 전극(33), 또한 주변 회로부의 CMOS 트랜지스터의 평면형의 게이트 전극을, 다른 전극 재료로 형성된다.

- [0113] 또한, 종형의 판독 게이트 전극(26)과, 다른 평면형의 게이트 전극은, 서로 일함수가 다른 전극 재료로 형성할수 있다.

- [0114] 특히, 종형의 판독 게이트 전극(26)은, 매입된 전극 재료의 공핍화를 억제하기 위해, 도펀트 가스를 소스 가스에 혼합한 가스, 이른바 불순물 혼합 가스를 사용한 CVD법에 의해 퇴적되는 불순물 도입(도핑) 실리콘으로 형성된다. 예를 들면, 종형의 판독 게이트 전극(26)의 전극 재료는, 인사이츠(insitu)로 n형 불순물인 인(P)을 도핑한 어모퍼스 실리콘 또는 폴리실리콘을 사용할 수 있다.

- [0115] 한편, 다른 평면형의 게이트 전극은, 언도프의 어모퍼스 실리콘 또는 폴리실리콘을 성막한 후, 소요되는 도전형의 불순물을 도핑하여 형성된다. 예를 들면, n채널 형 트랜지스터의 게이트 전극이라면, 이 언도프 실리콘에 n형 불순물을 도핑하고, p채널형 트랜지스터의 게이트 전극이라면, 이 언도프 실리콘에 p형 불순물을 도핑하여, 각각의 평면형의 게이트 전극이 형성된다.

- [0116] 한편, 종형의 판독 게이트 전극(26) 이외의 다른 평면형의 게이트 전극은, 고속 동작을 실현하기 위해, ±0.3V 이내로 낮은 임계치 전압으로 제어할 것이 필요해진다. 이 때문에, 다른 평면형의 게이트 전극은, 종형의 판독 게이트 전극(26)과는 다른 일함수를 갖은 게이트 전극 재료, 즉 보론 도프 실리콘이나, TiN, HfSi, W 등의 메탈 재료 등으로 형성할 수 있다. 즉, 이들의 전극 재료 등, n채널/p채널의 MOS 트랜지스터마다의 임계치 전극 제어나, AlO나 HfO, TaO라는 고유전률 게이트 절연막의 일함수 차(差)를 상쇄한 전극 재료로 형성할 수 있다.

- [0117] 종형의 판독 게이트 전극(26)은, 제 1 도전형 또는 제 2 도전형의 불순물을 도핑한 불순물 도입 실리콘으로 형성할 수 있다. 예를 들면, 판독 게이트 전극(26)은, 인(P) 또는 보론(B)을 도핑한 어모퍼스 실리콘 또는 폴리실리콘으로 형성할 수 있다.

- [0118] 종형의 판독 게이트 전극(26)으로서, 상기 인사이츠로 보론을 도핑한 어모퍼스 실리콘이나, 그 밖의 p형 상당한 일함수를 갖은 메탈로 형성할 수 있다. 이 경우, 자기 정합적으로 종형의 판독 게이트 전극의 표면에 전자 밀도 가 내려가기 때문에, 암전류 발생 방지의 효과가 있다. 이와 같은 구성에서는, 판독 게이트 전극(26)은, 게이트 절연막(27)을 통하여 직접 n형 반도체의 채널 영역에 접촉하여도 문제 없기 때문에, 암전류 억제 영역(29, 30)을 생략할 수 있다.

- [0119] 또한, 종형의 판독 게이트 전극(26)상의 이른바 인출 전극부(26a)와, 평면형의 다른 게이트 전극(31, 33, 87, 88)과, 게이트 전극 배선(도시 생략)은, 각각의 윗면이, 서로 동일 평면에 형성된다. 게이트 전극 배선은, 평면형의 다른 게이트 전극(31, 33, 87, 88)의 각각과 연속하여 형성한 구성으로 할 수도 있다.

- [0120] [고체 촬상 장치의 동작]

- [0121] 다음에, 고체 촬상 장치(101)의 동작을 설명한다.

- [0122] 우선, 도 2에서 도시하는 고체 촬상 장치(101)의 표면측, 즉, 도시하지 않은 온 칩 렌즈측에서 광(L)을 조사한다. 온 칩 렌즈에 의해 집광된 광(L)은, 도시하지 않은 컬러 필터를 통하여, 포토 다이오드(PD)에 입사한다.

- [0123] 포토 다이오드(PD)에 입사한 광은, 제 1 포토 다이오드(PD1)나, 제 2 포토 다이오드(PD2)에서 광전 변환하고, 그곳에서, 신호 전하가 생성된다. 생성된 신호 전하는, 제 1 포토 다이오드(PD1)를 구성하는 n+반도체 영역(22), 또는 제 2 포토 다이오드(PD2)를 구성하는 n+반도체 영역(24)에 축적된다.

- [0124] 또한, 판독 게이트 전극(26)의 저부, 및 측면이, 게이트 절연막(27)을 통하여 암전류 억제 영역(29, 30)에 접촉하도록 구성되고, 신호 전하의 축적시에, 판독 게이트 전극(26)에, 부전압이 인가된다. 이로써, 채널 영역(29)의 계면은 홀 피닝되고, 신호 전하의 축적시에 있어서, 판독 게이트 전극(26)으로부터 들어가는 암전류 노이즈를, 암전류 억제 영역(29, 30) 내에 가둘 수 있다. 따라서, 제 1의 포토 다이오드(PD1), 제 2의 포토 다이오드(PD2)에 도달하는 암전류를 저감할 수 있다.

- [0125] 또한, 신호 전하의 축적시에, 예를 들면 제 1 포토 다이오드(PD1)의 포화 전하량(Qs)을 초과하여 넘친 신호 전하는, 채널 영역(29)를 통과하여, 인접하는 제 2 포토 다이오드(PD2)로 이동한다. 또한, 그 반대로, 제 2 포토 다이오드(PD2)에서 넘친 신호 전하는, 제 1 포토 다이오드(PD1)로 이동한다. 즉, 한쪽의 포토 다이오드의 포화 전하량을 초과한 신호 전하는, 다른쪽의 포토 다이오드에 오버플로된다. 이로써, 포토 다이오드(PD) 전체의 포화 전하량(Qs)을 증가시키는 것이 가능해진다. 여기서, 제 1 포토 다이오드(PD1)와 제 2 포토 다이오드(PD2) 사이의 채널 영역(28)에서는, 오버플로 배리어 영역을 겸하여 형성된다.

- [0126] 신호 전하의 축적 후, 판독 게이트 전극(28)에, 정전압을 인가한다. 채널 영역(28)의 전위가 깊어짐에 의해, 제

- 1 포토 다이오드(PD1), 제 2 포토 다이오드(PD2)에 축적된 신호 전하는, 채널 영역(28)을 통하여 플로팅 디퓨전 영역(FD)에 동시에 판독된다.

- [0127] 그 후의 구동 방법은, 통상의 고체 촬상 장치의 구동과 마찬가지이다. 즉, 플로팅 디퓨전 영역(FD)에 신호 전하 가 전송되고, 그 플로팅 디퓨전 영역(FD)의 전압 변화에 의해, 앰프 트랜지스터(Tr3)의 앰프 게이트 전극(33)에 전압이 인가된다. 이로써, 신호 전하에 의한 신호 출력이 증폭되어 출력된다.

- [0128] 또한, 리셋 게이트 전극(31)에 정의 전압이 인가됨에 의해, 리셋 트랜지스터(Tr2)가 온 하여, 플로팅 디퓨전 영역(FD)은, 소스·드레인 영역(32)에 인가되어 있는 전원 전압과 동(同) 전압이 되도록 리셋된다.

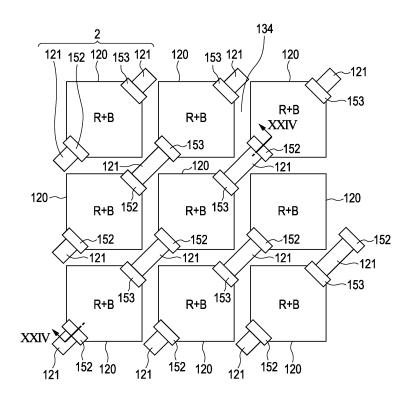

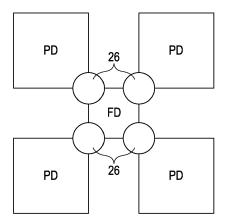

- [0129] 도 7에, 본 실시 형태 예의 고체 촬상 장치(1)의 화소(2)의 평면 레이아웃 구성을 도시한다. 도 7에 도시하는 바와 같이, 본 실시 형태 예의 고체 촬상 장치(1)에서는, 전하 판독 트랜지스터(Tr1)는, 1화소를 구성하는 포토 다이오드(PD1)에 대해 1하나 형성되어 있다. 또한, 플로팅 디퓨전 영역(FD)은, 인접하는 4개의 화소(2) 사이에서 공유되어 있다.

- [0130] 리셋 트랜지스터(Tr2)는, 플로팅 디퓨전 영역(FD)과, 소스·드레인 영역(32)과, 리셋 게이트 전극(31)으로 구성되어 있다.

- [0131] 플로팅 디퓨전 영역(FD)의 구성은 전술한 바와 같다.

- [0132] 소스·드레인 영역(32)은, 플로팅 디퓨전 영역(FD)과 이간하여, 기판(20) 표면에 n+형 반도체 영역에 의해 형성되어 있다. 이 소스·드레인 영역(32)은, 전원 전압을 공급하는 전원 배선(36)에 접속되어 있다.

- [0133] 리셋 게이트 전극(31)은, 플로팅 디퓨전 영역(FD)과, 소스·드레인 영역(32) 사이의 기판(20) 윗면에, 게이트 절연막(27)을 통하여 형성되어 있다. 이 리셋 게이트 전극(31)의 한쪽의 단부는, 플로팅 디퓨전 영역(FD)과 인접하고, 다른쪽의 단부는, 소스·드레인 영역(32)과 인접하도록 형성되어 있다.

- [0134] 이 리셋 트랜지스터(Tr2)에서는, 리셋 게이트 전극(31)에 정의 전압이 인가된 경우에는, 리셋 게이트 전극(31) 하부의 기판(20) 영역에 채널 영역이 형성된다. 이 채널 영역에 의해, 플로팅 디퓨전 영역(FD)과 소스·드레인 영역(32)이 전기적으로 접속된다.

- [0135] 앰프 트랜지스터(Tr3)는, 소스·드레인 영역(32, 34)과, 앰프 게이트 전극(33)으로 구성되어 있다.

- [0136] 소스 · 드레인 영역(32)의 구성은 전술한 바와 같다.

- [0137] 소스·드레인 영역(34)은, 전술한 소스·드레인 영역(32)과 이간하여, 기판(20) 표면에 n+형 반도체 영역에 의해 형성되어 있다.

- [0138] 앰프 게이트 전극(33)은, 소스·드레인 영역(32)과 소스·드레인 영역(34) 사이의 기판(20) 윗면에, 게이트 절 연막(27)을 통하여 형성되어 있다. 이 앰프 게이트 전극(33)의 한쪽의 단부는, 소스·드레인 영역(32)과 인접하고, 다른쪽의 단부는, 소스·드레인 영역(34)과 인접하도록 형성되어 있다.

- [0139] 이 앰프 트랜지스터(Tr3)에서는, 앰프 게이트 전극(33)은, 플로팅 디퓨전 영역(FD)에 신호 전하가 판독됨에 의한 플로팅 디퓨전 영역(FD)의 전압 변화에 대응하여 전압이 인가된다. 그리고, 앰프 게이트 전극(33)에 전압이 인가됨에 의해, 앰프 게이트 전극(33) 하부의 기판(20) 영역에 채널 영역이 형성되고, 이 채널 영역에 의해, 소스·드레인 영역(32, 34) 사이가 전기적으로 접속된다.

- [0140] 그 밖에, 도시하지 않지만, 필요에 응하여, 선택 트랜지스터 등이 형성된다.

- [0141] 이상과 같이, 포토 다이오드(PD) 및, 전하 판독 트랜지스터(Tr1), 리셋 트랜지스터(Tr2), 앰프 트랜지스터(Tr3) 등의 소망하는 화소 트랜지스터에 의해, 각 화소(2)가 구성되고, 기판(20)에 형성된 화소(2)는 화소 분리 영역 (35)에 의해 인접하는 화소(2)와 분리되어 있다. 그리고, 포토 다이오드(PD)나, 소망하는 화소 트랜지스터가 형성된 기판(20) 상부에는, 전원 배선(36)을 포함하는 다층의 배선(38)이 층간 절연막(37)을 통하여 형성된 배선 층(47)이 형성되어 있다.

- [0142] 상술한 고체 촬상 장치(1)에서는, 기판(20)의 표면측부터 광(L)을 조사하고, 이 광(L)을 포토 다이오드(PD)에서 수광하는 구성으로 한다. 이 때문에, 도시하지 않지만, 기판(20) 상부의 배선층(47) 상부에는, 온 칩 컬러 필터나, 각 화소(2)에 대응한 위치에 온 칩 렌즈가 형성되어 있다.

- [0143] <고체 촬상 장치의 제조 방법>

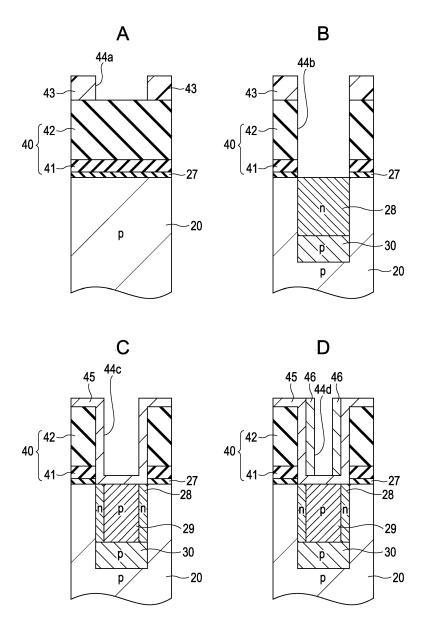

- [0144] 다음에, 본 실시 형태 예의 고체 활상 장치(1)의 제조 방법에 관해 도 8, 도 9를 이용하여 설명한다. 여기서는, 화소 사이즈가, 예를 들면, 0.9ょm인 경우에 관해 설명하고, 특히 판독 게이트 전극(26)의 부분의 제조 공정에 주목하여 설명한다. 판독 게이트 전극(26)의 부분 이외는, 종래의 고체 활상 장치의 제조 방법을 적용할 수 있다. 또한, 판독 게이트 전극(26)의 제조 공정은, 통상, 포토 다이오드(PD)의 제조 공정 후에 행하는 것이고, 본실시 형태 예에서는, 포토 다이오드(PD)를 구성하는 기판(20) 표면의 p+형 반도체 영역(21)을 형성하기 전단계에서 행하고 있다. 또한, 본실시 형태 예의 제조 공정은, 제 1의 포토 다이오드(PD)의 pn접합(j1)이, 기판(20) 표면부터 0.1ょm 정도의 깊이에 형성되고, 제 2의 포토 다이오드(PD2)의 pn접합(j2)가, 기판(20) 표면부터 0.5ょm 정도의 깊이에 형성되는 것을 상정한 것이다.

- [0145] 우선, 도 8A에 도시하는 바와 같이, 기판(20)상에 게이트 절연막(27)이 되는 실리콘 산화막(SiO<sub>2</sub>)을 5mm의 두께로 형성한다.

- [0146] 다음에, 게이트 절연막(27)상에 실리콘 질화막(SiN)(41)을 100nm의 두께로 형성하고, 실리콘 질화막(41)상에, 실리콘 산화막(SiO2)(42)을 1/m의 두께로 형성한다. 이 실리콘 질화막(41) 및 실리콘 산화막(42)는, 기판(20)에 의 이온 주입에 이용되는 마스크층(40)을 구성하는 것이다.

- [0147] 계속해서, 실리콘 산화막(42)상에, 포토레지스트막(43)을 0.6μm의 두께로 형성한다. 그리고, 이 포토레지스트막(43)을 리소그래피법에 의해 노광, 현상함에 의해, 포토레지스트막(43)을 패턴 형성한다. 본 실시 형태 예에서는, 포토레지스트막(43)에, 직경이 0.3μm의 원형의 개구부(44a)를 패턴 형성한다. 또한, 이 개구부(44a)의 직경은, 화소 사이즈에 따라 다른 것이고, 본 실시 형태 예에서 이용하고 있는 수치는, 그 한 예이다.

- [0148] 다음에, 개구부(44a)가 형성된 포토레지스트막(43)을 마스크로 하여, 기판(20) 표면이 노출할 때까지, 마스크층 (40), 및 게이트 절연막(27)을 에칭하고, 개구부(44b)를 형성한다.

- [0149] 다음에, 도 8B에 도시하는 바와 같이, 게이트 절연막(27), 마스크층(40), 포토레지스트막(43)에 개구부(44b)를 통하여, 기판(20) 표면부터의 깊이가 0.6 내지 0.8μm 이상, 1 내지 1.5μm 이하의 영역에, p형 반도체 영역의 불순물인 보론을 이온 주입한다. 즉, pn접합(j2)보다도 깊은 위치에, 보론을 이온 주입한다. 이로써, 판독 게이트 전극(26) 저부를 피복하는 암전류 억제 영역(30)이 형성된다.

- [0150] 계속해서, 마찬가지로 개구부(44b)를 통하여, 기판(20) 표면부터의 깊이가, 0.6 내지 0.8㎞ 이하의 영역에, n형 반도체 영역의 불순물인 인을 이온 주입한다. 즉, 기판(20) 표면부터, pn접합(j2)보다도 깊은 위치에 걸쳐진 영역에 형성한다. 이 n형 반도체 영역은, 판독 채널 영역(28)이 되는 것이다.

- [0151] 이들의 보론이나 인의 불순물의 이온 주입 깊이는, 포토레지스트막(43)과, 실리콘 산화막(42) 및 실리콘 질화막(41)으로 이루어지는 마스크층(40)의 합계의 막두께보다 충분히 얕게 할 필요가 있다. 또한, 인의 불순물 농도는, 기판(20)의 깊은 영역부터, 표면에 향하여 높아지도록 설계하는 것이 바람직하다.

- [0152] 다음에, 포토레지스트막(43)을 제거한다. 그리고, 도 8C에 도시하는 바와 같이, 마스크층(40) 표면에, 실리콘 산화막을 50nm의 두께로 형성하고, 제 1의 측벽 스페이서(45)를 형성한다. 이 제 1의 측벽 스페이서(45)는, 마스크층(40)에 형성된 개구부(44b)의 지름을 축소하는 것이고, 제 1의 측벽 스페이서(45)에 의해 축소된 개구부 (44c)의 지름은, 0.2µm이 된다.

- [0153] 계속해서, 제 1의 측벽 스페이서(45)에 의해 축소된 개구부(44c)를 통하여, 기판(20) 표면부터의 깊이가, 0.8 내지 1년 이하의 영역에, p형 반도체 영역의 불순물인 보론을 이온 주입한다. 이 때, 보론의 불순물 농도는, 기판(20) 표면부터 깊이 방향으로 가능한 한 균일하게 되도록 한다. 이 p형 반도체 영역은, 판독 게이트 전극(26)의 측면에 형성되는 암전류 억제 영역(29)이 되는 것이다.

- [0154] 다음에, 도 8D에 도시하는 바와 같이, 제 1의 측벽 스페이서(45)에 의해 축소된 개구부(44c)의 측벽에, 또한, 실리콘 산화막을 50mm의 두께로 형성하고, 제 2의 측벽 스페이서(46)를 형성한다. 이 제 2의 측벽 스페이서(46)는, 제 1의 측벽 스페이서(45)에 의해 축소된 개구부(44c)의 지름을 더욱 축소하는 것이고, 제 2의 측벽 스페이서(46)에 의해 축소된 개구부(44d)의 직경은, 0.1/mm이 된다.

- [0155] 그리고, 도 9E에 도시하는 바와 같이, 제 2의 측벽 스페이서(46)에 의해 축소된 개구부(44d)를 통하여, 개구부 (44d) 저부에 형성되어 있는, 제 1의 측벽 스페이서(45)를 구성하는 실리콘 산화막을 드라이 에칭에 의해 제거하고, 기판(20) 표면을 노출시킨다.

- [0156] 그 후, 도 9F에 도시하는 바와 같이, 제 1의 측벽 스페이서(45), 제 2의 측벽 스페이서(46)에 의해 축소된 개구

부(44d)를 갖는 마스크층(40)을 마스크로 하여, 기판(20)을 1 $\mu$ m 정도의 깊이까지 에칭하여 파들어간다. 이로써, 판독 게이트 전극(26)을 형성하기 위한 홈부(50)를 형성한다.

- [0157] 다음에, 도 9G에 도시하는 바와 같이, 데미지 제거를 위한 열산화의 전처리로서, 불산으로, 마스크층(40), 제 1 의 측벽 스페이서(45), 제 2의 측벽 스페이서(46)를 구성하는 실리콘 산화막을 제거한다.

- [0158] 그리고, 도 9H에 도시하는 바와 같이, 홈부(50) 표면에, 실리콘 산화막으로 이루어지는 게이트 절연막(27)을 형성한다. 여기서 형성되는 게이트 절연막(27)은, 판독 게이트 전극(26)에 대응하는 것이다.

- [0159] 그리고, 도 9I에 도시하는 바와 같이, 게이트 절연막(27)을 통하여, 홈부(50) 내, 및 실리콘 질화막(41)에 형성되어 있는 개구부(44b)에, 인(燐) 도프의 게이트 전극재를 매입한다. 그리고, CMP(Chemical Mechanical Polishing)에 의해, 실리콘 질화막(41)상의 게이트 전극재를 제거한다.

- [0160] 그 후, 도 9J에 도시하는 바와 같이, 실리콘 질화막(41)을 열(熱) 인산으로 제거함에 의해, 소망하는 형상의 판독 게이트 전극(26)을 얻는다. 이와 같이 하여 형성된 본 실시 형태 예의 판독 게이트 전극(26)은, 홈부(50)에 형성된 종형 게이트 전극과, 실리콘 질화막(41)의 개구부(4b)에 형성된 평면형 전극부(26a)를 갖고서 구성된다. 이 평면형 전극부(26a)에서, 배선의 인출이 행하여진다.

- [0161] 또한, 도시하지 않지만, 판독 게이트 전극(26) 성형시에, 리셋 게이트 전극(31)이나 앰프 게이트 전극(33) 등의 소망하는 게이트 전극이 형성된다.

- [0162] 이상과 같이 하여 판독 게이트 전극(26)이 완성된다. 그 후, 예를 들면, 포토 다이오드(PD)를 구성하는 기판 (20)의 최표면측의 p+형 반도체 영역(21)을 형성하는 공정 등이 있다.

- [0163] 본 실시 형태 예의 고체 촬상 장치(1)의 제조 방법에서는, 판독 게이트 전극(26)의 제조 공정에서, 포토레지스 트막(43)을 패턴 형성하기 위한 노광·현상 공정에서만, 노광 마스크가 사용된다. 그리고, 이 포토레지스트막(43)을 이용하여 에칭된 마스크층(40)의 개구부(44b)를 제 1의 측벽 스페이서(45)나 제 2의 측벽 스페이서(46)로 축소하고, 이 축소된 개구부(44c, 44d)를 통하여 암전류 억제 영역(29), 판독 채널 영역(28), 홈부(50) 등을 형성할 수 있다. 즉, 본 실시 형태 예에서는, 판독 게이트 전극(26) 형성시에 있어서, 1장의 노광 마스크밖에 사용하고 있지 않고, 암전류 억제 영역(29), 판독 채널 영역(28), 홈부(50) 등은, 셀프 얼라인으로 형성되기 때문에, 마스크의 맞춤 어긋남의 영향이 없다.

- [0164] 암전류 억제 영역(29)은, 포토 다이오드(PD)에의 전하의 축적시에, 불필요한 전하가, 포토 다이오드(PD)에 침입하여, 암전류가 되는 것을 막기 위한 것이다. 이 때문에, 암전류 억제 영역(29)은, 판독 게이트 전극(26) 측면에는, 보다 균일한 폭으로, 및 균일한 농도로 형성되는 것이 바람직하다. 구체적으로 말하면, 암전류 억제 영역(29)이 너무 두꺼우면, 게이트 바이어스의 제어가 잘 듣지 않고, 이른바 전송 남겨짐이 생긴다. 역으로 암전류억제 영역(29)가 너무 얇으면, 암전류 발생의 원인이 된다. 통상 이들의 제어는 ±20 내지 30mm로 행하여지는 것이 바람직하다. 이 때문에, 맞춤 정밀도를 내기 어려운 종래의 후막 레지스트를 통하는 이온 주입으로 암전류억제 영역(29)의 폭을 정하여 버리는 것은 특성 편차의 점에서 심각한 문제를 일으킬 가능성이 있다. 또한, 판독채널 영역(28)에 대해서도, 신호 전하의 전송 남겨짐을 방지하기 위해서는, 균일한 층으로 할 필요가 있다.

- [0165] 본 실시 형태 예에서는, 암전류 억제 영역(29)은, 셀프 얼라인으로 형성되기 때문에 마스크가 맞춤 어긋남의 영향이 없고, 균일한 폭으로 할 수 있기 때문에, 암전류의 발생을 억제하면서도, 전송 남겨짐이 생기지 않는 구성이 된다.

- [0166] 또한, 본 실시 형태 예에서는, 판독 채널 영역(28)도, 셀프 얼라인으로 형성되기 때문에, 마스크가 맞춤 어긋남의 영향이 없고, 균일한 폭으로 할 수 있기 때문에, 신호 전하의 전송 남겨짐을 방지할 수 있다.

- [0167] 또한, 본 실시 형태 예에서는, 포토레지스트막(43)이 형성되어 있는 상태에서, 판독 게이트 전극(26)의 저부에 형성되는 암전류 억제 영역(30)을 형성한다. 이로써, 암전류 억제 영역(30)을 형성하기 위한 불순물을, 기판 (20)의 깊은 영역이고, 또한, 판독 게이트 전극(26)의 저부를 피복하는 영역에 정밀도 좋게 이온 주입할 수 있다.

- [0168] 또한, 본 실시 형태 예에서는, 마스크층(40)을, 불산에 대한 선택비를 갖는 실리콘 질화막(41)과 실리콘 산화막 (42)의 2층 구조로 하고, 도 5G에서의 공정에서, 실리콘 산화막(42)만을 제거한다. 이로써, 셀프 얼라인으로, 홈부(50)과 홈부(50)보다 지름의 큰 개구부(44a)를 얻을 수 있고, 이 홈부(50)과 개구부(44a)를 전극 재료에 의해 매입함에 의해, 판독 게이트 전극(26)을 형성하고 있다. 이로써, 배선 인출용의 평면형 전극부(26a)가, 주상

으로 형성된 종형 게이트 전극의 상부에 정밀도 좋게 형성된다.

- [0169] 본 실시 형태 예에서는, 판독 게이트 전극(26), 암전류 억제 영역(29), 판독 채널 영역(28)이 각각 셀프 얼라인으로 형성되기 때문에, 맞춤 어긋남에 의한 특성 편차를 막고, 불필요한 맞춤 마진을 만들 필요가 없어진다. 이때문에 화소 사이즈를 축소한 경우라도, 판독 게이트 전극(26)을 정밀도 좋게 형성하는 것이 가능해진다.

- [0170] <고체 촬상 장치의 구동 방법>

- [0171] 다음에, 이상과 같이 하여 형성된 고체 촬상 장치(1)의 구동 방법에서의 설명을 한다.

- [0172] 우선, 도 6에서 도시하는 고체 촬상 장치(1)의 표면측, 즉, 도시하지 않은 온 칩 렌즈측에서 광(L)을 조사한다. 그러면, 온 칩 렌즈에 의해 집광된 광(L)은, 도시하지 않은 컬러 필터를 통하여, 포토 다이오드(PD)에 입사한다.

- [0173] 그리고, 포토 다이오드(PD)에 입사한 광은, 제 1의 포토 다이오드(PD1)나, 제 2의 포토 다이오드(PD2)에서 광전 변환하고, 그곳에서, 신호 전하가 생성된다. 생성된 신호 전하는, 제 1의 포토 다이오드(PD1)를 구성하는 pn접합(j1), 또는, 제 2의 포토 다이오드(PD2)를 구성하는 pn접합(j2)에 의해 형성된 전위의 우물에 축적된다.

- [0174] 또한, 본 실시 형태 예의 고체 촬상 장치(1)에서는, 판독 게이트 전극(26)의 저부, 및 측면을, 게이트 절연막 (27)을 통하여 암전류 억제 영역(29, 30)에 접촉하도록 구성하고, 신호 전하의 축적시에, 판독 게이트 전극(26)에, 부전압을 인가하여 둔다. 그렇게 함에 의해, 게이트 절연막(27)을 통한 판독 게이트 전극(26)의 저부 및 측면에는, 홀이 핀 고정된다. 이와 같이, 홀이 핀 고정되는, 홀 피닝이 일어남에 의해, 신호 전하의 축적시에 있어서, 판독 게이트 전극(26)으로부터 들어가는 암전류 노이즈를, 암전류 억제 영역(29, 30) 내에 가둘 수 있다. 이로써, 제 1의 포토 다이오드(PD1), 제 2의 포토 다이오드(PD2)에 도달하는 암전류를 저감할 수 있다.

- [0175] 또한, 본 실시 형태 예에서는, 신호 전하의 축적시에, 예를 들면 제 1의 포토 다이오드(PD1)의 포화 전하량(Qs)을 초과하여 넘친 신호 전하는, 판독 채널 영역을 통과하여, 인접하는 제 2의 포토 다이오드(PD2)로 이동한다. 또한, 그 반대로, 제 2의 포토 다이오드(PD2)에서 넘친 신호 전하는, 제 1의 포토 다이오드(PD1)로 이동한다. 즉, 본 실시 형태 예에서는, 한쪽의 포토 다이오드의 포화 전하량을 초과한 신호 전하는, 다른쪽의 포토 다이오드에 오버플로된다. 이로써, 포토 다이오드(PD) 전체의 포화 전하량(Qs)을 증가시키는 것이 가능해 진다.

- [0176] 신호 전하의 축적 후, 판독 게이트 전극(26)에, 정전압을 인가한다. 그러면, 판독 채널 영역(28)의 전위가 깊어 진다. 이로써, 제 1의 포토 다이오드(PD1), 제 2의 포토 다이오드(PD2)에 축적된 신호 전하는, 판독 채널 영역 (28)을 전송되어 플로팅 디퓨전 영역(FD)에 동시에 판독된다.

- [0177] 그 후의 구동 방법은, 통상의 고체 촬상 장치의 구동과 마찬가지이다. 즉, 플로팅 디퓨전 영역(FD)에 신호 전하 가 전송되고, 그 플로팅 디퓨전 영역(FD)의 전압 변화에 의해, 앰프 트랜지스터(Tr3)의 앰프 게이트 전극(33)에 전압이 인가된다. 이로써, 신호 전하에 의한 신호 출력이 증폭되어 출력된다.

- [0178] 또한, 리셋 게이트 전극(31)에 정의 전압이 인가됨에 의해, 플로팅 디퓨전 영역(FD)과, 소스·드레인 영역(32)가 접속되기 때문에, 플로팅 디퓨전 영역(FD)은, 소스·드레인 영역(32)에 인가되어 있는 전원 전압과 동 전압이 되도록 리셋된다.

- [0179] 본 실시 형태 예의 고체 촬상 장치(1)에서는, 기판(20)의 깊이 방향에, 제 1 및 제 2의 포토 다이오드(PD1, PD2)로 이루어지는 포토 다이오드(PD)가 형성되어 있다. 이와 같은 구성에 의해, 포토 다이오드(PD) 전체의 포화 전하량(Qs)이 증가한다. 이 때문에, 고체 촬상 장치의 감도를 향상시키는 것이 가능해진다.

- [0180] 그리고, 본 실시 형태 예의 고체 촬상 장치(1)에서는, 포토 다이오드(PD)의 깊이 방향으로 매입된 종형의 판독 게이트 전극(26)을 갖는, 전하 판독 트랜지스터(Tr1)가 구성되어 있다. 이로써, 기판(20)의 깊이 방향으로 형성 된 제 1 및 제 2의 포토 다이오드(PD1, PD2)에 축적된 신호 전하를, 플로팅 디퓨전 영역(FD)에 완전 전송하는 것이 가능해진다.

- [0181] 본 실시 형태 예의 고체 촬상 장치에서는, 제 1의 포토 다이오드(PD1) 및 제 2의 포토 다이오드(PD2)로 이루어 지는 2개의 포토 다이오드에 의해 구성된 예로 하였지만, 2개 이상의 포토 다이오드를, 소망하는 수만큼, 복수 적층시키는 것이 가능하다. 화소 사이즈를 축소화한 경우에도, 복수의 포토 다이오드를 적층시킴에 의해, 포화 전하량(Qs)을 증가시킬 수 있고, 감도를 향상시킬 수 있다. 이 때문에, 포화 전하량의 증가나, 감도를 향상시키 면서도, 화소 사이즈의 축소화가 용이하고, 본 실시 형태 예의 구조는, 화소 사이즈의 미세화에 유리하다.

또한, 포화 전하량의 증가가 가능하고, 다이내믹 레인지를 크게할 수 있기 때문에, 콘트라스트의 향상이 도모된다.

- [0182] 본 실시 형태 예의 고체 촬상 장치(1)에서는, 제 1 도전형을 p형으로 하고, 제 2 도전형을 n형으로서 구성하였지만, 제 1 도전형을 n형으로 하고, 제 2 도전형을 p형으로 하여도 좋다. 그 경우에, 상술한 구동 방법에 있어서, 각 화소 트랜지스터에 인가하는 전압은, 정을 부, 부를 정으로 바꾸어 읽는다.

- [0183] 또한, 본 실시 형태 예의 고체 촬상 장치(1)에서는, 표면 조사형의 고체 촬상 장치로서 설명하였지만, 이면 조사형의 고체 촬상 장치로 하여도 좋다. 본 실시 형태 예의 고체 촬상 장치(1)를, 광을 기판 이면측부터 입사시키는 이면 조사형으로 구성할 때는, 촬상 영역(3) 및 주변 회로부가 형성된 반도체 기판의 표면측의 상방에, 충간 절연막을 통하여 다층 배선층이 형성되고, 이면측이 광 입사면(이른바 수광면)이 된다. 이면측의 촬상 영역(3)의 화소(2)상에 평탄화막을 통하여 온 칩 컬러 필터, 또한 그 위에 온 칩 마이크로 렌즈가 형성된다.

- [0184] 또한, 본 실시 형태 예의 고체 촬상 장치(1)에서는, 판독 채널 영역(28)은, n형의 불순물이 이온 주입됨에 의해 형성되는 예로 하였지만, 암전류 억제 영역(29)보다도 2자릿수 정도 낮은 농도라면, 언도프의 영역에서 구성할 수 있다.

- [0185] <제 2의 실시 형태>

- [0186] [전자 기기]

- [0187] 이하에, 상술한 본 발명의 고체 촬상 장치를, 전자 기기에 이용한 경우의 실시 형태를 나타낸다. 이하의 설명에 서는, 한 예로서, 카메라에, 제 1의 실시 형태의 고체 촬상 장치(1)를 이용하는 예를 설명한다.

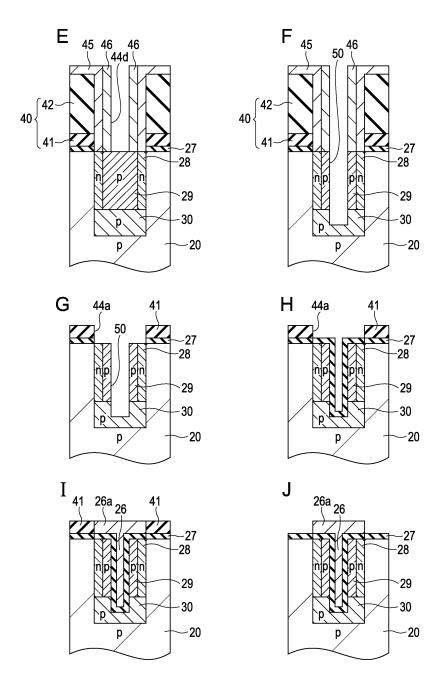

- [0188] 도 10에, 본 발명의 제 2의 실시 형태에 관한 카메라의 개략 단면 구성을 도시한다. 본 실시 형태에 관한 카메라는, 정지화 촬영 또는 동화 촬영 가능한 비디오 카메라를 예로 한 것이다.

- [0189] 본 실시 형태에 관한 카메라는, 고체 촬상 장치(1)와, 광학 렌즈(110)와, 셔터 장치(111)와, 구동 회로(112)와, 신호 처리 회로(113)를 갖는다.

- [0190] 광학 렌즈(110)는, 피사체로부터의 상광(像光)(입사광)을 고체 촬상 장치(1)의 촬상면상에 결상시킨다. 이로써 고체 촬상 장치(1) 내에 일정 기간 해당 신호 전하가 축적된다. 이 광학 렌즈(110)는, 복수의 광학 렌즈로 구성되는 광학 렌즈계로 하여도 좋다.

- [0191] 셔터 장치(111)는, 고체 촬상 장치(1)에의 광조사 기간 및 차광 기간을 제어한다.

- [0192] 구동 회로(112)는, 고체 촬상 장치(1)의 전송 동작 및 셔터 장치(111)의 셔터 동작을 제어하는 구동 신호를 공급한다. 구동 회로(112)로부터 공급되는 구동 신호(타이밍 신호)에 의해, 고체 촬상 장치(1)의 신호 전송을 행한다. 신호 처리 회로(113)는, 각종의 신호 처리를 행한다. 신호 처리가 행하여진 영상 신호는, 메모리등의 기억 매체에 기억되고, 또는 모니터에 출력된다.

- [0193] 본 실시 형태 예의 카메라에 사용된 고체 촬상 장치(1)에서는, 기판 내에 적층한 포토 다이오드를 이용하여, 1 화소로부터 복수의 색 신호를 검출할 수 있고, 실효적인 화소 수의 향상이나, 포화 전하량(Qs), 감도의 향상이도모된다. 이 때문에, 본 실시 형태 예의 카메라에서는, 카메라의 소형화가 가능하고, 또한, 보다 고화질화된 카메라를 얻을 수 있다. 즉, 전자 기기의 소형화, 고해상도화, 고화질화가 가능하게된다.

- [0194] 이하에 설명하는 제 3 내지 제 7의 실시 형태에서의 고체 촬상 장치는, 도 5에서의 고체 촬상 장치(1)를 구성하는 것이고, 특히 유효 촬상 영역에서의 화소(2)의 단면 구성을 나타내는 것이다.

- [0195] 120은 수광부, 120a는 제 1의 수광부, 120b는 제 2의 수광부, 121, 121a, 121b, 121c는 플로팅 디퓨전 영역, 122는 제 3의 게이트 전극, 123은 제 2의 게이트 전극, 124는 제 1의 게이트 전극, 125는 화소 트랜지스터 영역, 142는 마젠더 필터, 143은 청색 필터, 144는 옐로 필터, 145는 녹색 필터, 146은 적색 필터, 147은 시안 필터를 나타낸다.

- [0196] <제 3의 실시 형태>

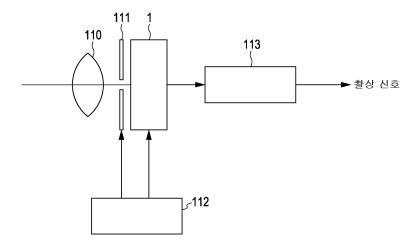

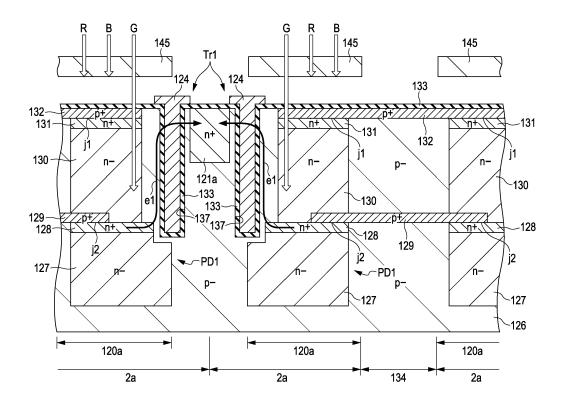

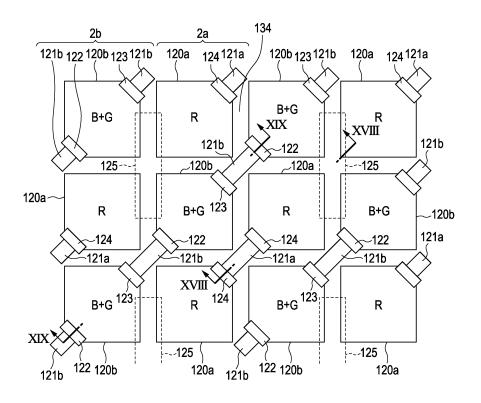

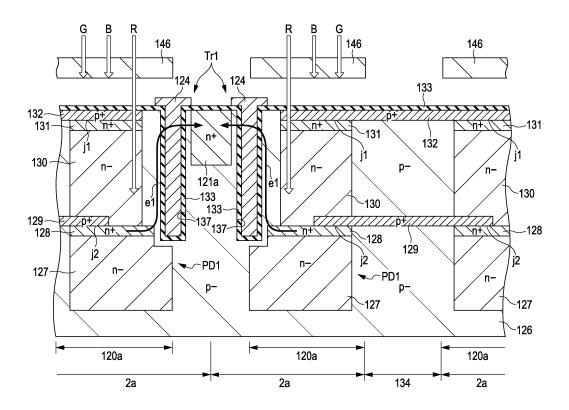

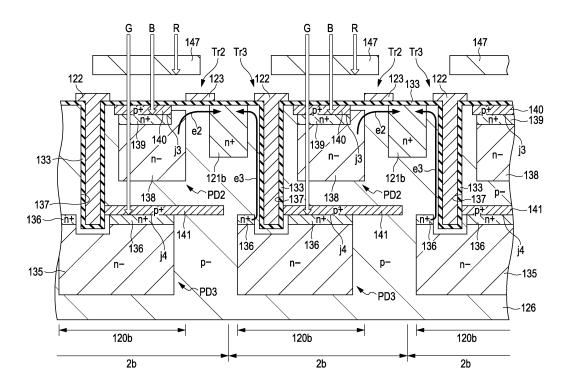

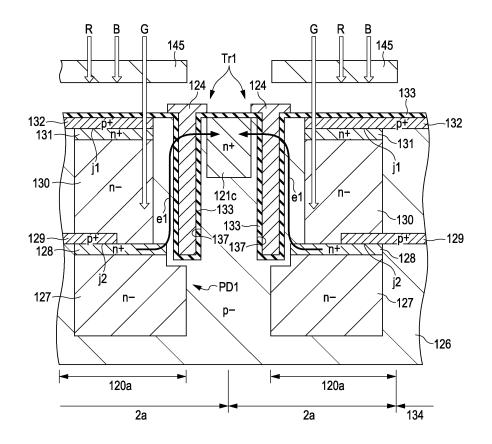

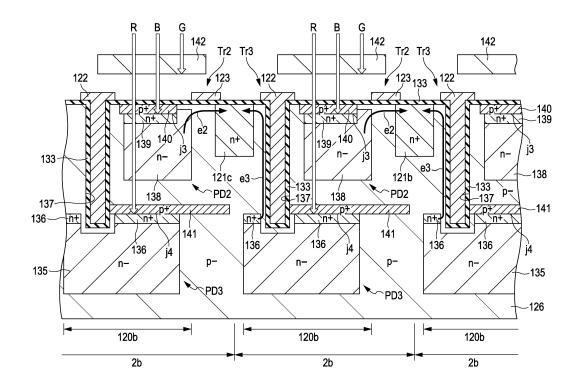

- [0197] 도 11에 본 발명의 제 3의 실시 형태에 관한 고체 촬상 장치의 주요부의 개략 평면 구성을 도시한다. 도 11은, 본 실시 형태 예의 고체 촬상 장치의 촬상 영역에서의 복수의 화소(2)(본 실시 형태 예에서는, 제 1의 화소(2a), 제 2의 화소(2b))의 평면 레이아웃을 도시하는 것이다. 또한, 도 12에는, 도 11의 XII-XII선상에 따른 단면 구성을 도시하고, 도 13에는, 도 11의 XIII-XIII선상에 따른 단면 구성을 도시한다. 본 실시 형태 예의 고체

촬상 장치는, 기판의 표면측부터 광조사가 되는 표면 조사형의 고체 촬상 장치이다.

- [0198] [구성의 설명]

- [0199] 본 실시 형태 예의 고체 촬상 장치는, 제 1의 화소(2a)와 제 2의 화소(2b)로 구성되어 있다. 제 1의 화소(2a)는, 제 1의 수광부(120a)와, 제 1의 게이트 전극(124)과, 플로팅 디퓨전 영역(121a)을 포함하여 구성되어 있다. 또한, 제 2의 화소(2b)는, 제 2의 수광부(120b)와, 제 2 및 제 3의 게이트 전극(122, 123)과, 플로팅 디퓨전 영역(121b)을 포함하여 구성되어 있다.

- [0200] 도 12에 도시하는 바와 같이, 제 1의 수광부(120a)는, 기판(126) 내에 형성된 제 1의 포토 다이오드(PD1)에 의해 구성되어 있다. 제 1의 포토 다이오드(PD1)에서는, 제 1의 파장역의 광이 광전 변환에 의해 신호 전하로 변환된다.

- [0201] 도 13에 도시하는 바와 같이, 제 2의 수광부(120b)는, 기판(126) 내의 깊이 방향으로 차례로 형성된 제 2의 포토 다이오드(PD2)와 제 3의 포토 다이오드(PD3)에 의해 구성되어 있다. 제 2 및 제 3의 포토 다이오드(PD2, PD3)에서는, 제 1의 파장역과 보색 관계에 있는 제 2의 파장역 및 제 3의 파장역의 광이, 광전 변환에 의해 각각의 신호 전하로 변환된다.

- [0202] 본 실시 형태 예는, 제 1의 파장역의 광을 녹색(G)으로 하고, 제 2의 파장역의 광을 청색(B)으로 하고, 제 3의 파장역의 광을 적색(R)으로 하는 예이다.

- [0203] 그리고, 도 11에 도시하는 바와 같이, 제 1의 수광부(120a)와, 제 2의 수광부(120b)는, 기판(126) 내에 서로 지 그재그 모양으로 배치되어 있다. 즉, 제 1의 수광부(120a)의 수직 방향 및 수평 방향에는, 제 2의 수광부(120b)가 인접하여 형성되어 있다. 또한, 제 2의 수광부(120b)의 수직 방향 및 수평 방향에는, 제 1의 수광부(120a)가 인접하여 형성되어 있다.

- [0204] 여기서, 제 1 내지 제 3의 포토 다이오드(PD1 내지 PD3)는, 제 1 도전형의 p형(여기서는, p-불순물 농도) 반도 체로 이루어지는 기판(126)에 형성된 p+불순물 영역과, 제 2 도전형의 n+불순물 영역의 pn접합을 갖고서 구성된 것이다. 이하에 상세히 기술한다.

- [0205] 우선, 제 1의 화소(2a)에 관해 설명한다.

- [0206] 도 12에 도시하는 바와 같이, 제 1의 수광부(120a)를 구성하는 제 1의 포토 다이오드(PD1)는, 기판(126)의 표면 부터 깊이 방향으로 차례로 형성된 p+불순물 영역(132), n+불순물 영역(130), n-불순물 영역(131), p+불순물 영역(129), n+불순물 영역(128), n-불순물 영역(127)으로 이루어지는 2층의 포토 다이오드를 갖는다. 즉, 기판 (126) 표면측의 p+불순물 영역(132)과 n+불순물 영역(130)의 pn접합(j1)에 의해 상층의 포토 다이오드가 구성되고, 기판(126)의 깊이 방향으로 깊은 위치에 형성된 p+불순물 영역(129)과 n+불순물 영역(128)의 pn접합(j2)에 의해 하층의 포토 다이오드가 구성되어 있다. 그리고, 상층의 포토 다이오드를 구성하는 pn접합(j1)은, 기판 (126)의 표면부터 0.1 내지 0.24㎞ 정도의 깊이에 형성되고, 하층의 포토 다이오드를 구성하는 pn접합(j2)은, 기판(126)의 표면부터 0.54㎞ 내지 0.84㎞ 정도의 깊이에 형성되어 있다.

- [0207] 제 1의 포토 다이오드(PD1)에 있어서, 상층 및, 하층의 포토 다이오드를 구성하는 p+불순물 영역(132, 129)은, 비스듬히 인접하는 2개의 제 1의 수광부(120a) 사이에 연재되어 형성되어 있다. 또한, 하층의 포토 다이오드를 구성하는 n+불순물 영역(128)과, 상층의 포토 다이오드를 구성하는 n-불순물 영역(131)은, 신호 전하가 판독되는 측, 즉, 제 1의 게이트 전극(124)이 형성되는측에서 전기적으로 접속되어 있다.

- [0208] 제 1의 게이트 전극(124)은, p+불순물 영역(132, 129)이 연재되어 형성되는 측과는 반대측의 제 1의 수광부 (120a)의 외주부에 형성되어 있다. 제 1의 게이트 전극(124)은, 기판(126)의 표면측부터, 깊이 방향으로 형성된 홈부(137)에, 게이트 절연막(133)을 통하여 전극 재료가 매입됨에 의해 형성된 종형 게이트 전극이다. 이 홈부 (137)는, 기판(126)의 표면부터 0.7㎞ 내지 1.0㎞ 정도의 깊이까지 파고들어가 형성되어 있다. 그리고, 제 1의 게이트 전극(124) 및, 제 1의 게이트 전극(124) 저부에 위치하는 게이트 절연막(133)은, 제 1의 포토 다이오드 (PD1)중, 하층의 포토 다이오드를 구성하는 pn접합(j2)보다도 깊은 위치가 되도록 형성되어 있다.

- [0209] 플로팅 디퓨전 영역(121a)은, 제 1의 게이트 전극(124)에 인접하는 기판(126)의 표면에, n+불순물 영역에 의해 형성되어 있다. 이 플로팅 디퓨전 영역(121a)은, p+불순물 영역(132, 129)이 연재되어 형성되는 측과는 반대측 에 인접하는 2개의 제 1의 화소(2a) 사이에서 공유되어 있다.

- [0210] 제 1의 화소(2a)에서는, 제 1의 게이트 전극(124)과 플로팅 디퓨전 영역(121a)에 의해, 제 1의 포토 다이오드

(PD1)의 신호 전하(e1)를 판독하기 위한 전하 판독 트랜지스터(Tr1)가 구성된다.

- [0211] 그리고, 제 1의 수광부(120a)가 형성된 기판(126)의 광조사측인 상부에는, 도시하지 않은 소망하는 배선층을 통하여, 녹색의 광(G)만을 투과하는 단색 필터인 녹색 필터(145)가 배치되어 있다.

- [0212] 다음에, 제 2의 화소(2b)에 관해 설명한다.

- [0213] 도 13에 도시하는 바와 같이, 제 2의 수광부(120b)는, 깊이 방향으로 적충된 제 2의 포토 다이오드(PD2)와 제 3의 포토 다이오드(PD3)를 갖는다.

- [0214] 제 2의 포토 다이오드(PD2)는, 기판(126)의 표면부터 깊이 방향으로 차례로 형성된 p+불순물 영역(140), n+불순물 영역(139), n-불순물 영역(138)에 의해 구성되고, 주로, p+불순물 영역(140)과 n+불순물 영역(139)의 pn접합 (j3)에 의해 구성되어 있다. 그리고, 제 2의 게이트 전극(123)에 인접하는측의 제 2의 포토 다이오드(PD2)를 구성하는 n-불순물 영역(138)은, p+불순물 영역(140)의 도중까지 피복하도록 형성되어 있다.

- [0215] 또한, 제 3의 포토 다이오드(PD3)는, 기판(126)의 제 2의 포토 다이오드(PD2)보다도 깊은 위치로부터 깊이 방향으로 형성된 p+불순물 영역(141), n+불순물 영역(136), n-불순물 영역(135)에 의해 구성되어 있다. 이 제 3의 포토 다이오드(PD3)는, 주로, p+불순물 영역(141)과 n+불순물 영역(136)의 pn접합(j4)에 의해 구성되어 있다.

- [0216] 제 2의 포토 다이오드(PD2)를 구성하는 pn접합(j3)은, 제 1의 포토 다이오드(PD1)의 pn접합(j1)과 마찬가지로, 기판(126)의 표면부터 0.1 내지 0.2㎞ 정도의 깊이에 형성된다. 또한, 제 3의 포토 다이오드(PD3)를 구성하는 pn접합(j4)은, 제 1의 포토 다이오드(PD1)의 pn접합(j2)과 마찬가지로, 기판(126)의 표면부터 0.5㎞ 내지 0.8㎞ 정도의 깊이에 형성된다.

- [0217] 제 2의 게이트 전극(123)은, 제 2의 수광부(120b)의 외주부의, 제 2의 포토 다이오드(PD2)에 인접한 기판(136) 윗면에 형성되어 있다. 제 2의 게이트 전극(123)은, 기판(126)의 표면에, 게이트 절연막(133)을 통하여 형성된 평면형 게이트 전극이다.

- [0218] 제 3의 게이트 전극(122)은, 제 2의 수광부(120b)의, 제 2의 게이트 전극(123)이 형성되어 있는 측과는 반대측의 외주부에, 제 3의 포토 다이오드(PD3)에 인접하여 형성되어 있다. 제 3의 게이트 전극(122)은, 기판(126)의 표면측부터, 깊이 방향으로 형성된 홈부(137)에, 게이트 절연막(133)을 통하여 전극 재료가 매입됨에 의해 형성된 종형 게이트 전극이다. 이 홈부(137)는, 기판(126)의 표면부터 0.7μm 내지 1.0μm 정도의 깊이까지 파고들어가 형성되어 있다. 그리고, 제 3의 게이트 전극(122) 저부 및, 제 3의 게이트 전극(122) 저부에 위치하는 게이트 절연막(133)은, 제 3의 포토 다이오드(PD3)를 구성하는 pn접합(j4)보다도 깊은 위치에 달하도록 형성되어 있다.

- [0219] 또한, 제 3의 게이트 전극(122) 저부 및 제 3의 게이트 전극(122) 저부에 위치하는 게이트 절연막(133)은, 제 3의 포토 다이오드(PD3)를 구성하는 n+불순물 영역(136) 및 n-불순물 영역(135)에, 기판(126)을 구성하는 p-불순물 영역을 통하여 피복되어 있다. 또한, 이 때, 제 2의 포토 다이오드(PD2)를 구성하는 p+불순물 영역(140)은, 제 3의 게이트 전극(122)의, 제 2의 수광부(120b)에 면하는 측에는, 제 3의 게이트 전극(122)에 접하여 형성되어 있고, 제 2의 수광부(120b)에 면하는 측과는 반대측에는 형성되어 있지 않다. 그리고, 제 3의 포토 다이오드(PD3)를 구성하는 p+불순물 영역(141)은, 인접하는 제 2의 화소(2b)를 구성하는 제 2의 수광부(120b) 경계 위치까지 연재되어 있다. 이 제 3의 포토 다이오드(PD3)를 구성하는 p+불순물 영역(141)은, 제 2의 수광부(120b) 내에서, 제 2의 포토 다이오드(PD2)와 제 3의 포토 다이오드(PD3)를 전기적으로 분리하기 위한 포토 다이오드 분리 영역을 겸하는 것이다.

- [0220] 플로팅 디퓨전 영역(121b)은, 제 2의 게이트 전극(123)에 인접하는 기판(126)의 표면, 및 제 3의 게이트 전극 (122)에 인접하는 기판의 표면에, n+불순물 영역에 의해 형성되어 있다. 이 플로팅 디퓨전 영역(121b)은, 비스듬히 인접하는 모든 제 2의 화소(2b)에서 공유되어 있다. 하나의 제 2의 화소(2b)에 주목하면, 제 2의 게이트 전극(123)에 인접하는 플로팅 디퓨전 영역(121b)은, 인접하는 제 2의 화소(2b)의 제 3의 게이트 전극(122)에 인접하여 있다. 또한, 제 3의 게이트 전극(122)에 인접하는 플로팅 디퓨전 영역(121b)은, 인접하는 제 2의 화소 (2b)의 제 2의 게이트 전극(123)에 인접하여 있다.

- [0221] 제 2의 화소(2b)에서는, 제 2의 게이트 전극(123)과, 제 2의 게이트 전극(123)에 인접하는 플로팅 디퓨전 영역 (121b)에 의해, 제 2의 포토 다이오드(PD2)의 신호 전하(e2)를 판독하는 전하 판독 트랜지스터(Tr2)가 구성되어 있다. 또한, 제 3의 게이트 전극(122)과 플로팅 디퓨전 영역(121b)에 의해, 제 3의 포토 다이오드(PD3)의 신호 전하(e3)를 판독하는 전하 판독 트랜지스터(Tr3)가 구성되어 있다.

- [0222] 그리고, 제 2의 수광부(120b)가 형성된 기판(126) 상부의 광조사측에는, 도시하지 않은 소망하는 배선층을 통하여, 녹색과 보색 관계에 있는 적색의 광(R) 및 청색의 광(B)을 투과하는 보색 필터인, 마젠더 필터(142)가 배치되어 있다.

- [0223] 제 1의 수광부(120a), 제 2의 수광부(120b) 사이의 소망하는 위치에는, 제 1의 화소(2a), 및 제 2의 화소(2b)를 구성하는, 앰프 트랜지스터, 리셋 트랜지스터, 선택 트랜지스터 등의 소망하는 화소 트랜지스터 영역(125)이 형성되어 있다.

- [0224] [동작의 설명]

- [0225] 이상의 구성을 갖는 고체 촬상 장치의 동작에 관해, 하나의 제 1의 화소(2a)와, 하나의 제 2의 화소(2b)에 주목 하여 설명한다.

- [0226] 우선, 기판(126)의 표면측부터 제 1의 수광부(120a) 및 제 2의 수광부(120b)에 광을 조사한다.

- [0227] 그러면, 녹색 필터(145)에서는, 녹색의 광(G)만이 투과하기 때문에, 제 1의 수광부(120a)에는, 제 1의 파장역의 광으로서, 녹색의 광(G)이 입사한다. 제 1의 수광부(120a)에 입사한 녹색의 광(G)은, 제 1의 포토 다이오드 (PD1)에서 광전 변환에 의해 신호 전하로 변환된다. 이 때, 녹색의 광(G)은, 상층의 포토 다이오드 및 하층의 포토 다이오드에서 광전 변되기 때문에, 제 1의 포토 다이오드(PD1)의 포화 전하량(Qs)을 증가시킬 수 있다. 그리고, 제 1의 포토 다이오드(PD1)에서 광전 변환에 의해 발생한 신호 전하는, pn접합(j1, j2)에 의해 형성된 전위의 우물에 축적된다.

- [0228] 한편, 마젠더 필터(42)에서는, 청색 및 적색의 광만이 투과하기 때문에, 제 2의 수광부(120b)에는, 제 2 및 제 3의 파장역의 광으로서, 청색의 광(B)과 적색의 광(R)이 입사한다. 제 2의 수광부(120b)에 입사한 광중, 청색의 광(B)은, 파장이 적색의 광(R)보다도 짧기 때문에, 그 대부분이 기판(126) 표면측에 형성된 제 2의 포토 다이오드(PD2)에서 광전 변환된다. 그리고, 제 2의 포토 다이오드(PD2)에서 광전 변환되어 발생한 신호 전하(e2)는, pn접합(j3)에 의해 형성된 전위의 우물에 축적된다. 또한, 제 2의 수광부(120b)에 입사한 광중, 적색의 광(R)은, 파장이 청색의 광(B)보다도 길다. 이 때문에, 적색의 광(R)중, 제 2의 포토 다이오드(PD2)에서 광전 변환되지 않은 광은, 기판(126)의 표면부터 깊은 위치에 형성된 제 3의 포토 다이오드(PD3)에 달하고, 제 3의 포토 다이오드(PD3)에서 광전 변환되어 발생한 신호 전하(e3)는, pn접합(j4)에 의해 형성된 전위의 우물에 축적된다.

- [0229] 다음에, 축적된 각각의 신호 전하(e1 내지 e3)를, 플로팅 디퓨전 영역(121a, 121b)에 판독한다.

- [0230] 우선, 제 1의 화소(2a)에 관해 보면, 제 1의 화소(2a)에서는, 제 1의 게이트 전극(124)이 온 됨에 의해, 종형의 제 1의 게이트 전극(124) 주위의 전위가 변동한다. 이로써, 제 1의 포토 다이오드(PD1)에 축적된 신호 전하(e 1)는, 제 1의 게이트 전극(124)에 인접하여 형성된 플로팅 디퓨전 영역(121a)에 판독된다.

- [0231] 그리고, 플로팅 디퓨전 영역(121a)에 신호 전하(e1)가 판독됨에 의해, 플로팅 디퓨전 영역(121a)의 전압이 변화한다. 이 전압 변화가 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 제 1의 포토 다이오드(PD1)의 신호 출력(S1)으로서 출력된다. 이 신호 출력(S1)은, 녹색의 광(G)에 의한 신호 출력(Gs)이다.

- [0232] 다음에, 제 2의 화소(2b)에 관해 보면, 제 2의 화소(2b)에서는, 제 2의 게이트 전극(123)이 온 됨에 의해, 평면형의 제 2의 게이트 전극(123) 하부의 기판(126) 내의 전위가 변동한다. 이로써, 제 2의 포토 다이오드(PD2)에 축적된 신호 전하(e2)는, 제 2의 게이트 전극(123)에 인접하여 형성된 플로팅 디퓨전 영역(121b)에 판독된다. 또한, 제 3의 게이트 전극(22)이 온 됨에 의해, 종형의 제 3의 게이트 전극(122) 주위의 전위가 변동한다. 이로써, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)는, 제 3의 게이트 전극(122)에 인접하여 형성된 플로팅디퓨전 영역(121b)에 판독된다.

- [0233] 그런데, 제 3의 게이트 전극(22) 저부 및 제 3의 게이트 전극(122) 저부에 위치하는 게이트 절연막(133)은, 제 3의 포토 다이오드(PD3)를 구성하는 n+불순물 영역(136) 및 n-불순물 영역(135)에, 기판(126)을 구성하는 p-불 순물 영역을 통하여 피복되어 있다. 그리고, 제 2의 포토 다이오드(PD2)를 구성하는 p+불순물 영역(141)은, 제 3의 게이트 전극(122)의, 제 2의 수광부(120b)에 면하는 측에는, 제 3의 게이트 전극(122)에 접하여 형성되어 있고, 제 2의 수광부(120b)에 면하는 측과는 반대측에는 형성되어 있지 않다. 이 때문에, 제 3의 게이트 전극(122)의, p+불순 물 영역(141)이 형성되어 있지 않은측의 면에 따라 플로팅 디퓨전 영역(121b)에 판독된다. 즉, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)의, 제 2의 수광부(120b)에 면하

는 측과는 반대측의 면에 따라 형성된다.

- [0234] 또한, 이 때, 제 3의 포토 다이오드(PD3)를 구성하는 p+불순물 영역(141)은 인접하는 제 2의 화소(2b)를 구성하는 제 2의 수광부(120b) 경계 위치까지 연재되어 형성되어 있다. 그리고, 이 p+불순물 영역(141)은, 제 2의 포토 다이오드(PD2)와 제 3의 포토 다이오드(PD3)를 분리하는 포토 다이오드 분리 영역으로 되어 있다. 이때문에, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)가, 제 2의 게이트 전극(23)에 인접하는 플로팅 디퓨전 영역(121b)에 판독되는 것을 막을 수 있다.

- [0235] 그리고, 제 2의 포토 다이오드(PD2) 및 제 3의 포토 다이오드(PD3)에 인접하는 각각의 플로팅 디퓨전 영역 (121b)에 신호 전하(e2, e3)가 판독됨에 의해, 각각의 플로팅 디퓨전 영역(121b)의 전압이 변화한다. 그리고, 이 제 2의 포토 다이오드(PD2)에 인접하는 플로팅 디퓨전 영역(121b)의 전압 변화는, 그 플로팅 디퓨전 영역 (121b)에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 출력 신호(S2)로서 출력된다. 또한 제 3의 포토 다이오드(PD3)에 인접하는 플로팅 디퓨전 영역(121b)의 전압 변화는, 그 플로팅 디퓨전 영역(121b)에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 신호 출력(S3)으로서 출력된다.

- [0236] 제 2의 수광부(120b)에는, 청색의 광(B)과 적색의 광(R)이 입사되기 때문에, 신호 출력(S2 및 S3)으로부터, 청색의 신호 출력(Bs)과, 적색의 신호 출력(Rs)을 연산 처리에 의해 구할 수 있다. 본 실시 형태 예에서는, 제 2의 수광부(120b)에 의해 흡수되는 청색의 광(B)과, 적색의 광(R)은, 그 파장역의 중복이 적기 때문에, 서로, 기판(126) 내에서의 흡수계수 차가 크다. 이 때문에, 제 3의 포토 다이오드(PD3)의 pn접합(j4) 깊이를, 청색의 광(B)이 거의 도달하지 않는 깊이로 설정함에 의해, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)는, 적색의 광(R)에 의해 광전 변환된 신호 전하만으로 할 수 있다. 제 3의 포토 다이오드(PD3)의 pn접합(j4)의 깊이가, 0.5µm 내지 0.8µm 정도로 한 경우, 청색의 광(B)은, 제 3의 포토 다이오드(PD3)에 거의 도달하지 않기 때문에, 신호 출력(S1, S2) 및 신호 출력(Bs, Rs)의 관계는,

- [0237] S2=Bs+Rs/2

- [0238] S3=2Rs/3

- [0239] 이 된다. 그리고, 이 연산식으로부터, 신호 출력(Bs, Rs)을, 각각

- [0240] Bs=S2-S3/2

- [0241]  $Rs=3/2\times S3$

- [0242] 로 구할 수 있다.

- [0243] 이와 같이, 본 실시 형태 예에서는, 제 2의 화소(2b)에서 검출되는 광을, 파장역의 중복이 적은 청색의 광(B)과 적색의 광(R)으로 함에 의해, 제 3의 포토 다이오드(PD3)에서 광전 변환되는 광을 적색의 광(R)만으로 할 수 있고, 실효적인 혼색을 막을 수 있다.

- [0244] 본 실시 형태 예에서는, 제 1의 화소(2a)를 구성하는 제 1의 수광부(20a)에 있어서, 기판(26)의 깊이 방향으로 적충된 2층의 포토 다이오드를 이용함으로써, 제 1의 수광부(20a)의 포화 전하량(Qs)을 2배로 할 수 있다. 그리고, 포화 전하량(Qs)의 향상에 수반하여, 감도를 향상시킬 수 있다.

- [0245] 또한, 제 2의 화소(2b)를 구성하는 제 2의 수광부(120b)에서는, 기판(26)의 깊이 방향으로 적충되고, 상하로 분리된 2층의 포토 다이오드를 이용함으로써, 청색의 광(B)과, 적색의 광(R)으로부터 각각 신호 전하를 얻을 수있다. 이로써, 1화소 내에서, 청색의 광(B)과 적색의 광(R)으로부터의 신호 출력(Bs, Rs)을 얻을 수 있기 때문에, 청색과, 적색의 화소 수는 2배로 증가하고, 포화 전하량(Qs)이나, 감도를 향상시킬 수 있다. 그리고, 깊은쪽에 위치하는 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)은, 종형의 제 3의 게이트 전극(22)에 의해플로팅 디퓨전 영역(121b)에 전송하고 있다. 이로써, 기판(26)의 깊이 방향의 포텐셜 변위를 충분히 행할 수 있고, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)의 전송 누설을 방지할 수 있다.

- [0246] 또한, 제 2의 화소(2b)에 있어서, 상측에 형성된 제 2의 포토 다이오드(PD2)를 평면형으로 형성된 제 2의 게이트 전극(123)에서 판독하고, 하측에 형성된 제 3의 포토 다이오드(PD3)을 종형으로 형성된 제 3의 게이트 전극(122)에서 판독하고 있다. 또한, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)의 판독 경로는, 제 3의 게이트 전극(122)의, 제 2의 수광부(120b)에 면하는 측과는 반대측의 측면에 따라 형성된다. 또한, 포토 다이오드 분리 영역을 겸하는 p+불순물 영역(141)이, 제 2의 포토 다이오드(PD2)에 축적된 신호 전하(e2)가 판독되는 플로팅 디퓨전 영역(121b)의 하방까지 연재되어 있다. 이로써, 제 2의 포토 다이오드(PD2)에서 축적된 신호 전하

- (e2)와, 제 3의 포토 다이오드(PD3)에서 축적된 신호 전하(e3)는 섞이지 않는 상태로, 각각의 플로팅 디퓨전 영역(121b)에 판독된다.

- [0247] 또한, 본 실시 형태 예에서는, 플로팅 디퓨전 영역(121a, 121b)이, 인접하는 화소 사이에서 공유되기 때문에, 화소 사이즈의 축소화가 도모된다.

- [0248] 그리고, 본 실시 형태 예의 고체 촬상 장치에서는, 제 1의 화소(2a)와 제 2의 화소(2b)를 구성하는 각각의 포토 다이오드나, 게이트 전극을 공통의 프로세스 스텝에 의해 형성할 수 있기 때문에, 공정 수의 증가는 없다.

- [0249] <제 4의 실시 형태>

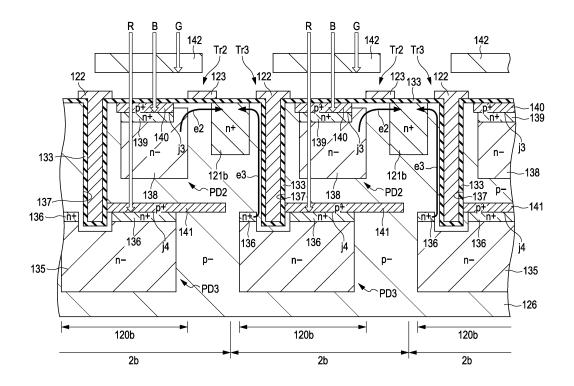

- [0250] 도 14에 본 발명의 제 4의 실시 형태에 관한 고체 촬상 장치의 주요부의 개략 평면 구성을 도시한다. 도 14는, 본 실시 형태 예의 고체 촬상 장치의 촬상 영역에서의 복수의 화소(2)의 평면 레이아웃을 도시하는 것이다. 또한, 도 15에는, 도 14의 XV-XV선상에 따른 단면 구성을 도시하고, 도 16에는, 도 14의 XVI-XVI선상에 따른 단면 구성을 도시하고, 도 16에는, 도 14의 XVI-XVI선상에 따른 단면 구성을 도시한다. 도 14 내지 16에 있어서, 도 11 내지 13에 대응하는 부분에는 동일 부호를 붙이고, 중복 설명을 생략한다.

- [0251] [구성의 설명]

- [0252] 본 실시 형태 예는, 제 1의 파장역의 광을 청색(B)으로 하고, 제 2의 파장역의 광을 녹색(G)으로 하고, 제 3의 파장역의 광을 적색(R)으로 하는 예이다. 즉, 도 14에 도시하는 바와 같이, 청색의 광(B)을 광전 변환하는 제 1의 수광부(120a)와, 녹색의 광(G)과 적색의 광을 광전 변환하는 제 2의 수광부(120b)가 각각 지그재그 모양으로 교대로 형성되어 있다.

- [0253] 이 때문에, 본 실시 형태 예에서는, 도 15에 도시하는 바와 같이, 제 1의 수광부(120a)가 형성된 기판(126)상에 배치되는 단색 필터로서, 청색 필터(143)를 이용한다. 또한, 도 16에 도시하는 바와 같이, 제 2의 수광부(120b)가 형성된 기판(126)상에 배치되는 보색 필터로서, 청색의 보색인 옐로 필터(144)를 이용한다.

- [0254] 기판(126) 내부의 구성은, 제 3의 실시 형태와 마찬가지이다.

- [0255] [동작의 설명]

- [0256] 이상의 구성을 갖는 고체 촬상 장치의 동작에 관해, 하나의 제 1의 화소(2a)와, 하나의 제 2의 화소(2b)에 주목 하여 설명한다.

- [0257] 우선, 기판(126)의 표면측부터 제 1의 수광부(120a) 및 제 2의 수광부(120b)에 광을 조사한다.

- [0258] 그러면, 청색 필터(143)에서는, 청색의 광(B)만이 투과하기 때문에, 제 1의 수광부(120a)에는, 제 1의 파장역의 광으로서, 청색의 광(B)이 입사한다. 제 1의 수광부(120a)에 입사한 청색의 광(B)은, 제 1의 포토 다이오드 (PD1)에서 광전 변환한다. 이 때, 청색의 광(B)은, 상층의 포토 다이오드 및 하층의 포토 다이오드에서 광전 변되기 때문에, 제 1의 포토 다이오드(PD1)의 포화 전하량(Qs)을 증가시킬 수 있다. 그리고, 제 1의 포토 다이오드(PD1)에서 광전 변환되어 발생한 신호 전하(e1)는, pn접합(j1, j2)에 의해 형성된 전위의 우물에 축적된다.

- [0259] 한편, 옐로 필터(144)에서는, 녹색의 광(G) 및 적색의 광(R)만이 투과하기 때문에, 제 2의 수광부(120b)에는, 제 2 및 제 3의 파장역의 광으로서, 녹색의 광(G) 및 적색의 광(R)이 입사한다. 제 2의 수광부(120b)에 입사한 광중, 녹색의 광(G)은, 파장이 적색의 광(R)보다도 짧기 때문에, 그 대부분이 기판(126) 표면측에 형성된 제 2의 포토 다이오드(PD2)에서 광전 변환되어 발생한 신호 전하(e2)는, pn접합(j3)에 의해 형성된 전위의 우물에 축적된다. 또한, 제 2의 수광부(120b)에 입사한 광중, 적색의 광(R)은, 파장이 녹색의 광(G)보다도 길다. 이 때문에, 적색의 광(R)중, 제 2의 포토 다이오드(PD2)에서 흡수되지 않은 광은, 기판(126) 표면부터 깊은 위치에 형성된 제 3의 포토 다이오드(PD3)에 달하고, 제 3의 포토 다이오드(PD3)에서 광전 변환된다. 또한, 녹색의 광(G)중 제 2의 포토 다이오드(PD2)에서 흡수되지 않은 광도 제 3의 포토 다이오드(PD3)에서 광전 변환된다. 그리고, 제 3의 포토 다이오드(PD3)에서 광전 변환된다.

- [0260] 다음에, 축적된 각각의 신호 전하(e1 내지 e3)를, 플로팅 디퓨전 영역(21a, 21b)에 판독한다.

- [0261] 우선, 제 1의 화소(2a)에 관해 보면, 제 1의 화소(2a)에서는, 제 1의 게이트 전극(124)가 온 됨에 의해, 종형의 제 1의 게이트 전극(124) 주위의 전위가 변동한다. 이로써, 제 1의 포토 다이오드(PD1)에 축적된 신호 전하(e 1)는, 제 1의 게이트 전극(124)에 인접하여 형성된 플로팅 디퓨전 영역(21a)에 판독된다.

- [0262] 그리고, 플로팅 디퓨전 영역(121a)에 신호 전하(e1)가 판독됨에 의해, 플로팅 디퓨전 영역(121a)의 전압이 변화한다. 이 전압 변화가 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 제 1의 포토 다이오드(PD1)의 신호 출력(S1)으로서 출력된다. 이 신호 출력(S1)은, 청색의 광(B)에 의해 얻어진 것이다.

- [0263] 다음에, 제 2의 화소(2b)에 관해 보면, 제 2의 화소(2b)에서는, 제 2의 게이트 전극(123)이 온 됨에 의해, 평면 형의 제 2의 게이트 전극(123) 하부의 기판(126) 내의 전위가 변동한다. 이로써, 제 2의 포토 다이오드(PD2)에 축적된 신호 전하(e2)는, 제 2의 게이트 전극(123)에 인접하여 형성된 플로팅 디퓨전 영역(121b)에 판독된다. 또한, 제 3의 게이트 전극(122)이 온 됨에 의해, 종형의 제 3의 게이트 전극(122) 주위의 전위가 변동한다. 이로써, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)는, 제 3의 게이트 전극(122)에 인접하여 형성된 플로팅 디퓨전 영역(121b)에 판독된다.

- [0264] 그런데, 제 3의 게이트 전극(122) 저부 및 제 3의 게이트 전극(122) 저부에 위치하는 게이트 절연막(133)은, 제 3의 포토 다이오드(PD3)를 구성하는 n+불순물 영역(136) 및 n-불순물 영역(135)에, 기판(126)을 구성하는 p-불순물 영역을 통하여 피복되어 있다. 그리고, 제 2의 포토 다이오드(PD2)를 구성하는 p+불순물 영역(141)은, 제 3의 게이트 전극(122)의, 제 2의 수광부(120b)에 면하는 측에는, 제 3의 게이트 전극(122)에 접하여 형성되어 있고, 제 2의 수광부(120b)에 면하는 측과는 반대측에는 형성되어 있지 않다. 이 때문에, 제 3의 게이트 전극(122)이 온 된 때, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)는, 제 3의 게이트 전극(122)의, p+불순물 영역이 형성되지 않은측의 면에 따라 플로팅 디퓨전 영역(121b)에 판독된다.

- [0265] 또한, 이 때, 제 3의 포토 다이오드(PD3)를 구성하는 p+불순물 영역(141)은 인접하는 제 2의 화소(2b)를 구성하는 제 2의 수광부(120b) 경계 위치까지 연재되어 형성되어 있다. 그리고, 이 p+불순물 영역(141)은, 제 2의 포토 다이오드(PD2)와 제 3의 포토 다이오드(PD3)를 분리하는 포토 다이오드 분리 영역으로 되어 있다. 이 때문에, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)가, 제 2의 게이트 전극(123)에 인접하는 플로팅 디퓨전 영역(121b)에 판독되는 것을 막을 수 있다.

- [0266] 그리고, 제 2의 포토 다이오드(PD2) 및 제 3의 포토 다이오드(PD3)에 인접하는 각각의 플로팅 디퓨전 영역 (121b)에 신호 전하(e2, e3)가 판독됨에 의해, 각각의 플로팅 디퓨전 영역(121b)의 전압이 변화한다. 제 2의 포토 다이오드(PD2)에 인접하는 플로팅 디퓨전 영역(121b)의 전압 변화는, 그 플로팅 디퓨전 영역(121b)에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 출력 신호(S2)로서 출력된다. 또한 제 3의 포토 다이오드 (PD3)에 인접하는 플로팅 디퓨전 영역(121b)의 전압 변화는, 그 플로팅 디퓨전 영역(121b)에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 신호 출력(S3)으로서 출력된다.

- [0267] 제 2의 수광부(120b)에는, 녹색의 광(G)과 적색의 광(R)이 입사되기 때문에, 신호 출력(S2 및 S3)으로부터, 녹색의 신호 출력(Gs)과, 적색의 신호 출력(Rs)이 연산 처리에 의해 구하여진다. 신호 출력(S1, S2) 및 신호 출력(Bs, Rs)의 관계는,

- [0268]  $S2=\alpha \cdot Bs+\beta \cdot Rs$

- [0269]  $S3=y \cdot Bs + \delta \cdot Rs$

- [0270] 가 된다. α, β, γ, δ는, 기판(126)의 깊이에 대한 광의 흡수계수나, 옐로 필터(144)의 특성으로부터 결정되는 정수이다. 그리고, 이 연산식으로부터, 신호 출력(Bs, Rs)을, 각각 구할 수 있다.

- [0271] <제 5의 실시 형태>

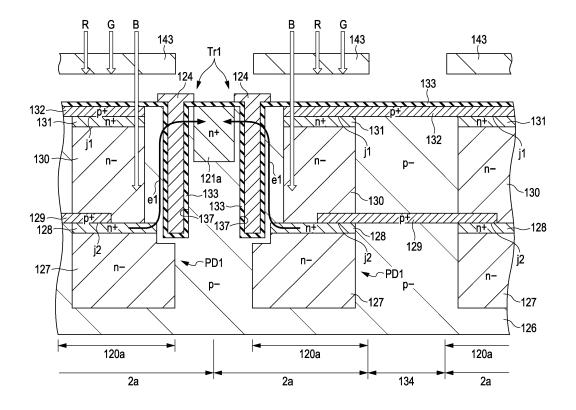

- [0272] 도 17에 본 발명의 제 5의 실시 형태에 관한 고체 촬상 장치의 주요부의 개략 평면 구성을 도시한다. 도 17은, 본 실시 형태 예의 고체 촬상 장치의 촬상 영역에서의 복수의 화소(2)의 평면 레이아웃을 도시하는 것이다. 또한, 도 18에는, 도 17의 XVIII-XVIII선상에 따른 단면 구성을 도시하고, 도 19에는, 도 17의 XIX-XIX선상에 따른 단면 구성을 도시한다. 도 17 내지 19에서, 도 11 내지 13에 대응하는 부분에는 동일 부호를 붙이고, 중복설명을 생략한다.

- [0273] [구성의 설명]

- [0274] 본 실시 형태 예는, 제 1의 파장역의 광을 적색(R)으로 하고, 제 2의 파장역의 광을 청색(B)으로 하고, 제 3의 파장역의 광을 녹색(G)으로 하는 예이다. 즉, 도 17에 도시하는 바와 같이, 적색의 광(R)을 광전 변환하는 제 1의 수광부(120a)와, 청색의 광(B)과 녹색의 광(G)를 광전 변환하는 제 2의 수광부(120b)가 각각 지그재그 모양으로 교대로 형성되어 있다.

- [0275] 이 때문에, 본 실시 형태 예에서는, 도 18에 도시하는 바와 같이, 제 1의 수광부(120a)가 형성된 기판(126)상에 배치되는 단색 필터로서, 적색 필터(146)를 이용한다. 또한, 제 2의 수광부(120b)가 형성된 기판(126)상에 배치되는 보색 필터로서, 적색의 보색인 시안 필터(147)를 이용한다.

- [0276] [동작의 설명]

- [0277] 이상의 구성을 갖는 고체 촬상 장치의 동작에 관해, 하나의 제 1의 화소(2a)와, 하나의 제 2의 화소(2b)에 주목 하여 설명한다.

- [0278] 우선, 기판(126)의 표면측부터 제 1의 수광부(120a) 및 제 2의 수광부(120b)에 광을 조사한다.

- [0279] 그러면, 적색 필터(146)에서는, 적색의 광(R)만이 투과하기 때문에, 제 1의 수광부(120a)에는, 제 1의 파장역의 광으로서, 적색의 광(R)이 입사한다. 제 1의 수광부(120a)에 입사한 적색의 광(R)은, 제 1의 포토 다이오드 (PD1)에서 광전 변환된다. 이 때, 적색의 광(R)은, 상층의 포토 다이오드 및 하층의 포토 다이오드에서 광전 변되기 때문에, 제 1의 포토 다이오드(PD1)의 포화 전하량(Qs)을 증가시킬 수 있다. 그리고, 제 1의 포토 다이오드(PD1)에서 광전 변환되어 발생한 신호 전하(e1)는, pn접합(j1, j2)에 의해 형성된 전위의 우물에 축적된다.

- [0280] 한편, 시안 필터(147)에서는, 청색의 광(B) 및 녹색의 광(G)만이 투과하기 때문에, 제 2의 수광부(120b)에는, 제 2 및 제 3의 파장역의 광으로서, 청색의 광(B) 및 녹색의 광(G)가 입사한다. 제 2의 수광부(120b)에 입사한 광중, 청색의 광(B)은, 파장이 녹색의 광(G)보다도 짧기 때문에, 그 대부분이 기판(126) 표면측에 형성된 제 2의 포토 다이오드(PD2)에서 광전 변환된다. 그리고, 제 2의 포토 다이오드(PD2)에서 광전 변환되어 발생한 신호전하(e2)는, pn접합(j3)에 의해 형성된 전위의 우물에 축적된다. 또한, 제 2의 수광부(120b)에 입사한 광중, 녹색의 광(G)은, 파장이 청색의 광(B)보다도 길다. 이 때문에, 녹색의 광(G)중, 제 2의 포토 다이오드(PD2)에서 흡수되지 않은 광은, 기판(126) 표면부터 깊은 위치에 형성된 제 3의 포토 다이오드(PD3)에 달하고, 제 3의 포토 다이오드(PD3)에서 광전 변환된다. 그리고, 제 3의 포토 다이오드(PD3)에서 광전 변환되어 발생한 신호전하(e3)는, pn접합(j4)에 의해 형성된 전위의 우물에 축적된다.

- [0281] 다음에, 축적된 각각의 신호 전하를, 플로팅 디퓨전 영역(121a, 121b)에 판독한다.

- [0282] 우선, 제 1의 화소(2a)에 관해 보면, 제 1의 화소(2a)에서는, 제 1의 게이트 전극(124)이 온 됨에 의해, 종형의 제 1의 게이트 전극(124) 주위의 전위가 변동한다. 이로써, 제 1의 포토 다이오드(PD1)에 축적된 신호 전하(e 1)는, 제 1의 게이트 전극(124)에 인접하여 형성된 플로팅 디퓨전 영역(121a)에 판독된다.

- [0283] 그리고, 플로팅 디퓨전 영역(121a)에 신호 전하(e1)가 판독됨에 의해, 플로팅 디퓨전 영역(121a)의 전압이 변화한다. 이 전압 변화가 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 제 1의 포토 다이오드(PD1)의 신호 출력(S1)으로서 출력된다. 이 신호 출력(S1)은, 적색의 광(R)에 의해 얻어진 것이다.

- [0284] 다음에, 제 2의 화소(2b)에 관해 보면, 제 2의 화소(2b)에서는, 제 2의 게이트 전극(123)이 온 됨에 의해, 평면형의 제 2의 게이트 전극(123) 하부의 기판(126) 내의 전위가 변동한다. 이로써, 제 2의 포토 다이오드(PD2)에 축적된 신호 전하(e2)는, 제 2의 게이트 전극(123)에 인접하여 형성된 플로팅 디퓨전 영역(121b)에 판독된다. 또한, 제 3의 게이트 전극(122)이 온 됨에 의해, 종형의 제 3의 게이트 전극(122) 주위의 전위가 변동한다. 이로써, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)는, 제 3의 게이트 전극(122)에 인접하여 형성된 플로팅 디퓨전 영역(121b)에 판독된다.

- [0285] 그런데, 제 3의 게이트 전극(122) 저부 및 제 3의 게이트 전극(122) 저부에 위치하는 게이트 절연막(133)은, 제 3의 포토 다이오드(PD3)를 구성하는 n+불순물 영역(136) 및 n-불순물 영역(135)에, 기판(126)을 구성하는 p-불순물 영역을 통하여 피복되어 있다. 그리고, 제 3의 포토 다이오드(PD3)를 구성하는 p+불순물 영역(141)은, 제 3의 게이트 전극(122)의, 제 2의 수광부(120b)에 면하는 측에는, 제 3의 게이트 전극(122)에 접하여 형성되어 있고, 제 2의 수광부(120b)에 면하는 측과는 반대측에는 형성되어 있지 않다. 이 때문에, 제 3의 게이트 전극(122)의, p+불순물 영역(141)이 형성되지 않은측의 면에 따라 플로팅 디퓨전 영역(121b)에 판독된다.

- [0286] 또한, 이 때, 제 3의 포토 다이오드(PD3)를 구성하는 p+불순물 영역(141)은 인접하는 제 2의 화소(2b)를 구성하는 제 2의 수광부(120b) 경계 위치까지 연재되어 형성되어 있다. 그리고, 이 p+불순물 영역(141)은, 제 2의 포토 다이오드(PD2)와 제 3의 포토 다이오드(PD3)를 분리하는 포토 다이오드 분리 영역으로 되어 있다. 이 때문에, 제 3의 포토 다이오드(PD3)에 축적된 신호 전하(e3)가, 제 2의 게이트 전극(123)에 인접하는 플로팅 디퓨전 영역(121b)에 판독되는 것을 막을 수 있다.

- [0287] 그리고, 제 2의 포토 다이오드(PD2) 및 제 3의 포토 다이오드(PD3)에 인접하는 각각의 플로팅 디퓨전 영역 (121b)에 신호 전하(e2, e3)가 판독됨에 의해, 각각의 플로팅 디퓨전 영역(121b)의 전압이 변화한다. 그리고, 이 제 2의 포토 다이오드(PD2)에 인접하는 플로팅 디퓨전 영역(121b)의 전압 변화는, 그 플로팅 디퓨전 영역 (121b)에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 출력 신호(S2)로서 출력된다. 또한 제 3의 포토 다이오드(PD3)에 인접하는 플로팅 디퓨전 영역(121b)의 전압 변화는, 그 플로팅 디퓨전 영역(121b)에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 신호 출력(S3)으로서 출력된다.

- [0288] 제 2의 수광부(120b)에는, 청색의 광(B)과 녹색의 광(G)이 입사되기 때문에, 신호 출력(S2 및 S3)으로부터, 청색의 신호 출력(Bs)과, 녹색의 신호 출력(Gs)이 연산 처리에 의해 구하여진다. 신호 출력(S1, S2) 및 신호 출력(Bs, Gs)의 관계는,

- [0289]  $S2= \alpha \cdot Bs + \beta \cdot Gs$

- [0290] S3=  $y \cdot Bs + \delta \cdot Gs$

- [0291] 가 된다. α, β, γ, δ는, 기판(126)의 깊이에 대하는 광의 흡수계수나, 시안 필터(147)의 특성으로부터 결정되는 계수이다. 그리고, 이 연산식으로부터, 신호 출력(Bs, Gs)을, 각각 구할 수 있다.

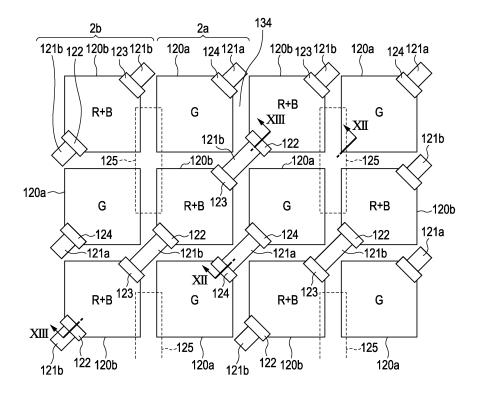

- [0292] <제 6의 실시 형태>

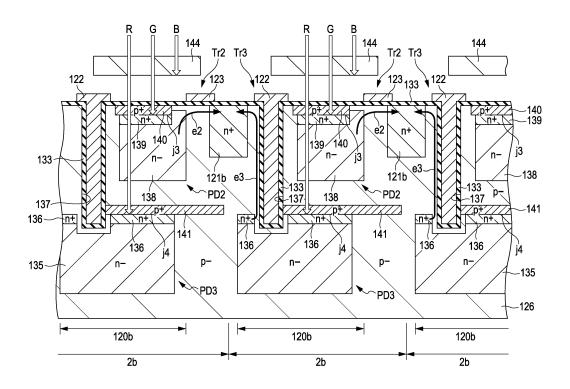

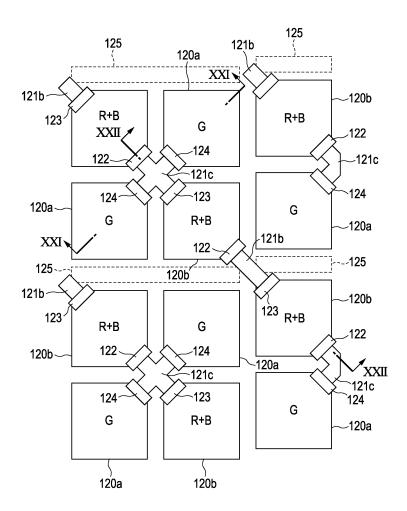

- [0293] 도 20에 본 발명의 제 6의 실시 형태에 관한 고체 촬상 장치의 주요부의 개략 평면 구성을 도시한다. 도 20은, 본 실시 형태 예의 고체 촬상 장치의 촬상 영역에서의 복수의 화소(2)의 평면 레이아웃을 도시하는 것이다. 또한, 도 21에는, 도 20의 XXI-XXI선상에 따른 단면 구성을 도시하고, 도 22에는, 도 20의 XXII-XXII선상에 따른 단면 구성을 도시하고, 도 22에는, 도 20의 XXII-XXII선상에 따른 단면 구성을 도시한다. 도 20 내지 22에서, 도 11 내지 13에 대응하는 부분에는 동일 부호를 붙이고, 중복 설명을 생략한다.

- [0294] [구성의 설명]

- [0295] 본 실시 형태 예의 고체 활상 장치는, 제 1의 실시 형태 예에서 고체 활상 장치와는, 플로팅 디퓨전 영역의 공유 방법과, 제 2의 게이트 전극(123) 및 제 3의 게이트 전극(122)의 배치 방법이 다른 예이다.

- [0296] 도 20에 도시하는 바와 같이, 비스듬히 인접하는 제 1의 화소(2a) 사이에서 공유되는 플로팅 디퓨전 영역(121 c)은, 비스듬히 인접하는 제 2의 화소(2b) 사이에서도 공유된다. 즉, 이 플로팅 디퓨전 영역(121c)은 인접하는 4개의 화소 사이에서 공유되어 있다. 그리고, 이 플로팅 디퓨전 영역(121c)을 공유하는 4개의 화소를 단위 화소 군으로 하면, 수직 방향으로 인접하는 단위 화소군의 사이에는, 리셋 트랜지스터, 앰프 트랜지스터, 선택 트랜지스터 등이 형성되는 화소 트랜지스터 영역(125)이 마련되어 있다. 그리고, 단위 화소군중, 제 2의 화소(2b)와, 이 단위 화소군에 인접하는 단위 화소군의 제 2의 화소(2b) 사이에서는, 플로팅 디퓨전 영역(121 b)이 공유되어 있다. 이 때문에, 단위 화소군과 수평 방향으로 인접하는 단위 화소군은, 화소 트랜지스터 영역(125)의 영역분만큼 빗나가도록 형성되어 있다.

- [0297] 본 실시 형태 예의 고체 촬상 장치에서의 제 1의 수광부(120a), 제 2의 수광부(120b)로부터의 신호 판독의 동작은, 제 1의 실시 형태와 마찬가지이기 때문에, 중복 설명을 생략한다.

- [0298] 본 실시 형태 예에 의하면, 인접하는 4개의 화소를 단위 화소군으로 하여, 하나의 플로팅 디퓨전 영역(121c)를 공유함에 의해, 기판(126) 표면에 있어서 전하 판독 트랜지스터(Tr1 내지 Tr3)가 차지하는 비율이 감소한다. 이로써, 다른 화소 트랜지스터 영역(125)을 형성한 스페이스를 충분히 확보하는 것이 가능해진다.

- [0299] <제 7의 실시 형태>

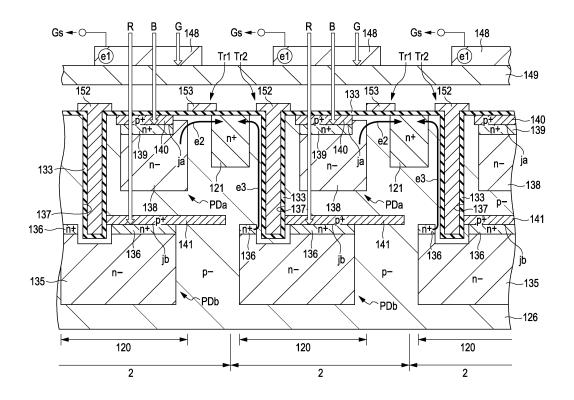

- [0300] 도 23에 본 발명의 제 7의 실시 형태에 관한 고체 촬상 장치의 주요부의 개략 평면 구성을 도시한다. 도 23은, 본 실시 형태 예의 고체 촬상 장치의 촬상 영역에서의 복수의 화소(2)의 평면 레이아웃을 도시하는 것이다. 또한, 도 24에는, 도 23의 XXIV-XXIV선상에 따른 단면 구성을 도시한다. 도 23 및 도 24에서, 도 11 및 도 13에 대응하는 부분에는 동일 부호를 붙이고, 중복 설명을 생략한다.

- [0301] [구성의 설명]

- [0302] 본 실시 형태 예의 고체 촬상 장치의 화소(2)는, 수광부(120)와, 종형 게이트 전극(152)과, 평면형 게이트 전극 (153)과, 플로팅 디퓨전 영역(121)을 포함하여 구성되어 있다. 그리고, 화소(2) 상부에는, 유기 광전 변환막 (148)을 갖는다. 본원의 모든 실시 형태 예에서는, 유기 광전 변환막(148)을 화소(2) 상부에 배설하는 대신에,

유기가 아니라, 무기의 광전 변환막이나, 적충된 광전 변환막, 적외선을 흡수하는 Si나 Ge, 또는 유기 광전 변환막과 그들의 일부 또는 전부와의 조합을 화소(2) 상부에 배설하여도 좋다.

- [0303] 수광부(120)는, 기판(126)의 수평 방향 및 수직 방향으로 복수, 매트릭스형상으로 형성되어 있고, 기판(126)의 깊이 방향으로 적충된 상측 포토 다이오드(PDa)와 하측 포토 다이오드(PDb)를 갖는다.

- [0304] 도 24에 도시하는 바와 같이, 상측 포토 다이오드(PDa)는, 기판(126)의 표면부터 깊이 방향으로 차례로 형성된 p+불순물 영역, n+불순물 영역, n-불순물 영역에 의해 구성되고, 주로, p+불순물 영역과 n+불순물 영역의 pn접합(ja)에 의해 구성되어 있다.

- [0305] 또한, 하측 포토 다이오드(PDb)는, 상측 포토 다이오드(PDa)보다도 깊은 위치로부터 깊이 방향으로 형성된 p+불 순물 영역, n+불순물 영역, n-불순물 영역에 의해 구성되고, 주로, p+불순물 영역과 n+불순물 영역의 pn접합 (jb)에 의해 구성되어 있다.

- [0306] 본 실시 형태 예의 상측 포토 다이오드(PDa)는, 제 1의 실시 형태에서의 제 2의 포토 다이오드(PD2)에 상당하는 것이고, 하측 포토 다이오드(PDb)는, 제 1의 실시 형태에서의 제 3의 포토 다이오드(PD3)에 상당하는 것이다. 또한, 평면형 게이트 전극(153)은, 제 1의 실시 형태에서의 제 2의 게이트 전극(123)에 상당하는 것이고, 종형 게이트 전극(152)은, 제 1의 실시 형태에서의 제 3의 게이트 전극(122)에 상당하는 것이다. 또한, 플로팅 디퓨전 영역(121)은, 제 1의 실시 형태의 플로팅 디퓨전 영역(121b)에 상당하는 것이다.

- [0307] 화소(2)에서는, 평면형 게이트 전극(153)과, 평면형 게이트 전극(153)에 인접하는 플로팅 디퓨전 영역(121)에 의해, 상측 포토 다이오드(PDa)의 신호 전하(e2)를 판독하는 전하 판독 트랜지스터(Tr1)가 구성되어 있다. 또한, 종형 게이트 전극(152)과 플로팅 디퓨전 영역(121)에 의해, 하측 포토 다이오드(PDb)의 신호 전하(e3)를 판독하는 전하 판독 트랜지스터(Tr3)가 구성되어 있다.

- [0308] 수광부(120)가 형성된 기판(126) 상부의 광조사측에는, 도시하지 않은 소망하는 배선층을 통하여, 녹색과 보색 관계에 있는 적색의 광(R) 및 청색의 광(B)을 투과하는 보색 필터인, 마젠더 필터(149)가 전면(全面)에 배치되어 있다.

- [0309] 그리고, 이 마젠더 필터(149)의 상부에는, 녹색의 광(G)만을 흡수하고 광전 변환하는, 유기 광전 변환막(148)이 형성되어 있다.

- [0310] 유기 광전 변환막(148)은, 각 수광부(120)에 대응하는 기판(126)상에, 화소(2)마다 분리하여 배치되어 있다.

- [0311] [동작의 설명]

- [0312] 이상의 구성을 갖는 고체 촬상 장치의 동작에 관해 설명한다.

- [0313] 우선, 기판(126) 표면측부터 광을 조사한다.

- [0314] 그러면, 유기 광전 변환막(148)에서는, 녹색의 광(G)만이 흡수된다. 그리고, 유기 광전 변환막(148)에 흡수된 녹색의 광(G)은, 유기 광전 변환막(148) 내에서 광전 변환되고, 신호 전하(e1)가 발생한다. 녹색의 광(G)에 의해 발생한 신호 전하(e1)는, 출력 단자를 통하여, 녹색의 신호 출력(Gs)으로서 출력된다.

- [0315] 한편, 유기 광전 변환막(148)에 흡수되지 않은 광은, 마젠더 필터(149)를 통하여, 기판(126) 내의 수광부(120)에 입사한다. 마젠더 필터(149)에서는, 청색의 광(B) 및 적색의 광(R)만이 투과하기 때문에, 수광부(120)에는, 청색의 광(B), 및 적색의 광(R)이 입사한다. 수광부(120)에 입사한 광중, 청색의 광(B)은, 파장이 적색의 광(R)보다도 짧기 때문에, 그 대부분이 기판(126) 표면측에 형성된 상측 포토 다이오드(PDa)에서 광전 변환된다. 그리고, 상측 포토 다이오드(PDa)에서 광전 변환되어 발생한 신호 전하(e2)는, pn접합(ja)에 의해 형성된 전위의 우물에 축적된다.

- [0316] 또한, 수광부(120)에 입사한 광중, 적색의 광(R)은, 파장이 청색의 광(B)보다도 길다. 이 때문에, 적색의 광(R)중, 상측 포토 다이오드(PDa)에서 광전 변환되지 않은 광은, 기판(126)의 표면부터 깊은 위치에 형성된 하측 포토 다이오드(PDb)에 달하고, 하측 포토 다이오드(PDb)에서 광전 변된다. 그리고, 하측 포토 다이오드(PDb)에서 광전 변환되어 발생한 신호 전하(e3)는, pn접합(jb)에 의해 형성된 전위의 우물에 축적된다.

- [0317] 다음에, 축적된 각각의 신호 전하(e2, e3)를, 플로팅 디퓨전 영역(121)에 판독한다.

- [0318] 우선, 평면형 게이트 전극(153)이 온 됨에 의해, 평면형 게이트 전극(153) 하부의 기판(126) 내의 전위가 변동한다. 이로써, 상측 포토 다이오드(PDa)에 축적된 신호 전하(e2)는, 평면형 게이트 전극(153)에 인접하여 형성

된 플로팅 디퓨전 영역(121)에 판독된다. 또한, 종형 게이트 전극(152)이 온 됨에 의해, 종형 게이트 전극(152) 주위의 전위가 변동한다. 이로써, 하측 포토 다이오드(PDb)에 축적된 신호 전하(e3)는, 종형 게이트 전극(152) 에 인접하여 형성된 플로팅 디퓨전 영역(121)에 판독된다.

- [0319] 그런데, 종형 게이트 전극(152) 저부 및 종형 게이트 전극(152) 저부에 위치하는 게이트 절연막(133)은, 하측 포토 다이오드(PDb)를 구성하는 n+불순물 영역 및 n-불순물 영역에, 기판을 구성하는 p-불순물 영역을 통하여 피복되어 있다. 그리고, 제 2의 포토 다이오드를 구성하는 p+불순물 영역은, 종형 게이트 전극(152)의, 수광부 (120)에 면하는 측에는, 종형 게이트 전극(152)에 접하여 형성되어 있고, 수광부(120)에 면하는 측과는 반대측에는 형성되어 있지 않다. 이 때문에, 종형 게이트 전극(152)이 온 된 때, 상측 포토 다이오드(PDa)에 축적된 신호 전하(e3)는, 종형 게이트 전극(152)의, p+불순물 영역이 형성되지 않은측의 면에 따라 플로팅 디퓨전 영역 (121)에 판독된다.

- [0320] 또한, 이 때, 하측 포토 다이오드(PDb)를 구성하는 p+불순물 영역은 인접하는 수광부(120) 경계 위치까지 연재되어 형성되어 있고, 상측 포토 다이오드(PDa)와 하측 포토 다이오드(PDb)를 분리하는 포토 다이오드 분리 영역으로 되어 있다. 이 때문에, 하측 포토 다이오드(PDb)에 축적된 신호 전하(e3)가, 평면형 게이트 전극(153)에 인접하는 플로팅 디퓨전 영역(121)에 판독되는 것을 막을 수 있다.

- [0321] 그리고, 상측 포토 다이오드(PDa) 및 하측 포토 다이오드(PDb)에 인접하는 각각의 플로팅 디퓨전 영역(121)에 신호 전하(e2, e3)이 판독됨에 의해, 각각의 플로팅 디퓨전 영역(121)의 전압이 변화한다. 그리고, 이 상측 포토 다이오드(PDa)에 인접하는 플로팅 디퓨전 영역(121)의 전압 변화는, 그 플로팅 디퓨전 영역(121)에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 출력 신호(S2)로서 출력된다. 또한 하측 포토 다이오드에 인접하는 플로팅 디퓨전 영역의 전압 변화는, 그 플로팅 디퓨전 영역에 접속된 도시하지 않은 앰프 트랜지스터에 의해 증폭되고, 신호 출력(S3)으로서 출력된다.

- [0322] 수광부(120)에는, 청색의 광(B)과 적색의 광(R)이 입사되기 때문에, 신호 출력(S2 및 S3)으로부터, 청색의 신호 출력(Bs)과, 적색의 신호 출력(Rs)을 연산 처리에 의해 구할 수 있다. 이 연산 방법은, 제 3의 실시 형태와 마찬가지이다.

- [0323] 이와 같이, 본 실시 형태 예에서는, 1화소로, 청색의 광(B), 녹색의 광(G), 적색의 광(R)을 동시에 검출할 수 있다. 이 때문에, 입사광량의 손실을 저감할 수 있다. 또한, 1화소로, 청색의 광(B), 녹색의 광(G), 적색의 광(R)을 검출할 수 있기 때문에, 실효적인 화소 수를 늘릴 수 있다.

- [0324] 또한, 녹색의 광(G)은, 유기 광전 변환막(148)에 의해 검출하고, 광흡수계수의 차가 큰 청색의 광(B)과 적색의 광(R)을, 기판(126) 내의 깊이 방향으로 적충된 상측 포토 다이오드(PDa), 하측 포토 다이오드(PDb)에서 검출한 다. 이로써, 하측 포토 다이오드(PDb)에서 광전 변환된 광의 색을 적색만으로 할 수 있고, 기판(126) 내에서의 분광 특성을 향상시킬 수 있다.

- [0325] 본 실시 형태 예에서는, 유기 광전 변환막(148)으로서, 녹색의 광(G)을 흡수하는 재료를 사용하였지만, 청색의 광(B)를 흡수하는 재료를 사용하여도 좋다. 이 경우는, 마젠더 필터(149) 대신에, 옐로 필터를 사용하고, 기판 (126) 내의 수광부(120)에서는, 녹색의 광(G)과, 적색의 광(R)을 광전 변환한다. 또한, 유기 광전 변환막(148)으로서, 적색의 광(R)을 흡수하는 재료를 사용하여도 좋다. 이 경우는, 마젠더 필터(149) 대신에, 시안 필터를 사용하고, 기판(126) 내의 수광부(120)에서는, 청색의 광(B)과, 녹색의 광(G)을 광전 변환한다.

- [0326] 상술한 제 3 내지 제 7의 실시 형태에서는, 기판의 표면측부터 광을 조사하는 표면 조사형의 고체 촬상 장치를 예로 하여 설명하였지만, 기판의 이면측부터 광을 조사하는 이면 조사형의 고체 촬상 장치로 하여도 좋다. 이경우는, 기판의 이면측에, 단색 필터, 보색 필터, 유기 광전 변환막을 구성하고, 기판 내부의 포토 다이오드의 구성을 역으로 하면 좋다.

- [0327] 상술한 제 3 내지 제 7의 실시 형태에 관한 고체 촬상 장치에서는, 가시광의 광량에 응한 신호 전하를 물리량으로서 검지하는 단위 화소가 행렬형상으로 배치되어 이루어지는 이미지 센서에 적용한 경우를 예에 들어 설명하였다. 그러나, 본 발명은 이미지 센서에의 적용으로 한정되는 것이 아니고, 화소 어레이부의 화소열마다 칼럼 회로를 배치하여 이루어지는 칼럼 방식의 고체 촬상 장치 전반에 대해 적용 가능하다.

- [0328] 또한, 본 발명은, 가시광의 입사광량의 분포를 검지하여 화상으로서 촬상하는 고체 촬상 장치에의 적용으로 한하지 않고, 적외선이나 X선, 또는 입자 등의 입사량의 분포를 화상으로서 촬상하는 고체 촬상 장치에 적용 가능하다. 또한, 광의의 의미로서, 압력이나 정전용량 등, 다른 물리량의 분포를 검지하여 화상으로서 촬상하는 지

- 문 검출 센서 등의 고체 촬상 장치(물리량 분포 검지 장치) 전반에 대해 적용 가능하다.

- [0329] 또한, 본 발명은, 화소 어레이부의 각 단위 화소를 행 단위로 차례로 주사하여 각 단위 화소로부터 화소 신호를 판독하는 고체 촬상 장치로 한하지 않는다. 예를 들면, 화소 단위로 임의의 화소를 선택하여, 해당 선택 화소로 부터 화소 단위로 신호를 판독하는 X-Y어드레스형의 고체 촬상 장치에 대해서도 적용 가능하다.

- [0330] 또한, 고체 촬상 장치는 원 칩으로서 형성된 형태라도 좋고, 촬상부와, 신호 처리부 또는 광학계가 통함하여 팩 키징된 촬상 기능을 갖는 모듈형상의 형태라도 좋다.

- [0331] 또한, 본 발명은, 고체 촬상 장치에의 적용으로 한정되는 것이 아니고, 촬상 장치에도 적용 가능하다. 여기서, 촬상 장치란, 디지털 스틸 카메라나 비디오 카메라 등의 카메라 시스템이나, 휴대 전화기 등의 촬상 기능을 갖는 전자 기기인 것을 말한다. 또한, 전자 기기에 탑재되는 상기 모듈형상의 형태, 즉 카메라 모듈을 촬상 장치로 하는 경우도 있다.

- [0332] [전자 기기]

- [0333] 이하에, 상술한 본 발명의 고체 촬상 장치를, 전자 기기에 이용한 경우의 실시 형태를 나타낸다. 이하의 설명에 서는, 한 예로서, 카메라에, 제 3 내지 제 7의 실시 형태의 어느 하나를 적용한 고체 촬상 장치(1)를 이용하는 예를 설명한다.

- [0334] 도 10에, 본 발명에 관한 카메라의 개략 단면 구성을 도시한다. 본 실시 형태에 관한 카메라는, 정지화 촬영 또는 동화 촬영 가능한 비디오 카메라를 예로 한 것이다.

- [0335] 본 실시 형태에 관한 카메라는, 고체 촬상 장치(1)와, 광학 렌즈(110)와, 셔터 장치(111)와, 구동 회로(112)와, 신호 처리 회로(113)를 갖는다. 그리고, 이 고체 촬상 장치(1)에는, 제 3 내지 제 7의 실시 형태의 고체 촬상 장치를 적용할 수 있다.

- [0336] 광학 렌즈(110)는, 피사체로부터의 상광(입사광)을 고체 촬상 장치(1)의 촬상면상에 결상시킨다. 이로써 고체 촬상 장치(1) 내에 일정 기간 해당 신호 전하가 축적된다. 이 광학 렌즈(110)는, 복수의 광학 렌즈로 구성된 광학 렌즈계로 하여도 좋다.

- [0337] 셔터 장치(111)는, 고체 촬상 장치(1)에의 광조사 기간 및 차광 기간을 제어한다.

- [0338] 구동 회로(112)는, 고체 촬상 장치(1)의 전송 동작 및 셔터 장치(111)의 셔터 동작을 제어한 구동 신호를 공급한다. 구동 회로(112)로부터 공급되는 구동 신호(타이밍 신호)에 의해, 고체 촬상 장치(1)의 신호 전송을 행한다. 신호 처리 회로(113)는, 각종의 신호 처리를 행한다. 신호 처리가 행하여진 영상 신호는, 메모리 등의 기억매체에 기억되고, 또는 모니터에 출력된다.

- [0339] 본 실시 형태 예의 카메라에 이용되는 고체 촬상 장치(1)에서는, 기판 내에 적충한 포토 다이오드를 이용하고, 1화소로부터 복수의 색 신호를 검출할 수 있고, 실효적인 화소 수의 향상이나, 포화 전하량(Qs), 감도의 향상이 도모된다. 이 때문에, 본 실시 형태 예의 카메라에서는, 카메라의 소형화가 가능하고, 또한, 보다 고화질화된 카메라를 얻을 수 있다. 즉, 전자 기기의 소형화, 고해상도화, 고화질화가 가능하게 된다.

- [0340] <제 8 실시의 형태>

- [0341] <고체 촬상 장치의 제조 방법의 실시의 형태>

- [0342] 다음에, 도 25 내지 도 32를 이용하여 본 발명에 관한 고체 촬상 장치의 제조 방법의 한 예를 설명한다.

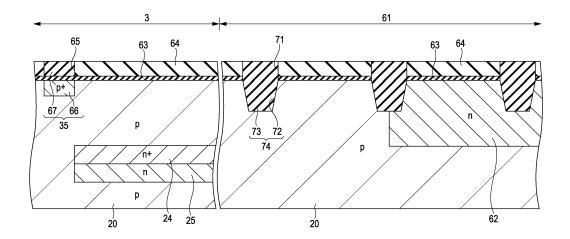

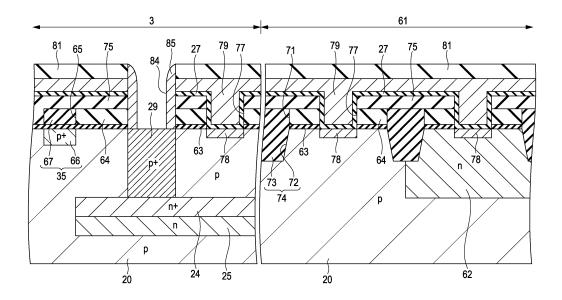

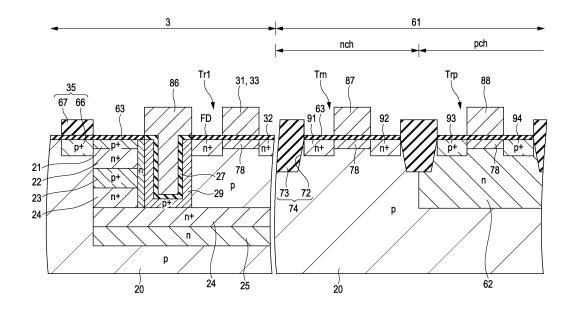

- [0343] 우선, 도 25에 도시하는 바와 같이, p형의 반도체 기판(20)의 화소부(3)측에 제 2 포토 다이오드(PD2)의 일부를 구성하는 n반도체 영역(25) 및 n+반도체 영역(24)을 이온 주입법으로 형성한다. 이 양 영역(25 및 24)은, 단위 화소 내의 화소 트랜지스터의 하부로 연장하도록 형성된다. 또한, 주변 회로부(61)측에서는, p채널 MOS 트랜지스터를 형성하여야 할 영역에 n형 반도체 웰 영역(62)을 형성한다.

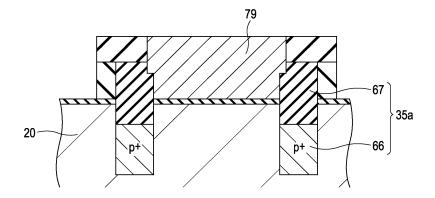

- [0344] 그리고, 반도체 기판(20)상에, 실리콘 산화막(63)을 통하여 소요되는 막두께의 제 1 연마 스톱막이 되는 예를 들면 실리콘 질화막(64)을 성막한다. 이 실리콘 질화막(64)은, 예를 들면 100nm 정도의 막두께를 갖는다. 화소부(3)측에서는, 화소 분리 영역 및 화소 내의 소자 분리 영역에 대응하는 부분의 제 1의 실리콘 질화막(64)에 개구(65)를 형성하고, 이 개구(65)를 통하여 p형 불순물을 이온 주입하여 p형의 채널 스톱 영역(66)을 형성한다.

- [0345] 그리고, 개구(65) 내에 실리콘 산화막(67)을 매입하여, 실리콘 산화막(67)을 평탄화한다. 평탄화는, 예를 들면

CMP(화학 기계 연마)법이 이용된다. 이 실리콘 산화막(67)과 p형의 채널 스톱 영역(66)에 의한 화소 분리 영역 (35)(소자 분리 영역(35a)도 포함한다)을 형성한다. 또한, 화소 분리 영역 및 소자 분리 영역은, 형성 소자의 종류에 의해, 예를 들면 실리콘 기판에 홈을 형성하고, 이 홈 내에도 실리콘 산화막(67)을 매입한 구성으로 할수도 있다.

- [0346] 한편, 주변 회로부(61)측에서는, 소자 분리 영역에 대응하는 부분의 제 1의 실리콘 질화막(64)에 개구(71)를 형성하고, 이 개구(71) 아래의 반도체 기판(20)에 소요되는 깊이의 홈(72)을 형성한다. 이 홈(72) 내 및 제 1의 실리콘 질화막(64)의 개구(71) 내에 실리콘 산화막(73)을 매입하여, STI 구조로 소자 분리 영역(74)을 형성한다.

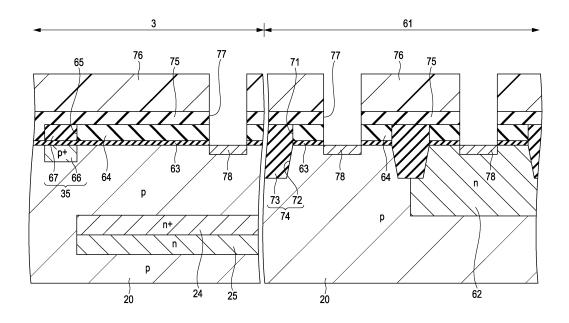

- [0347] 다음에, 도 26에 도시하는 바와 같이, 평탄화 후의, 제 1 연마 스토퍼가 되는 실리콘 질화막(64)상에 제 2 연마 스토퍼가 되는 실리콘 질화막(75)을 소요되는 막두께로 성막한다. 예를 들면, 평탄화 후의, 제 1의 실리콘 질화막(64)의 나머지의 막두께 80mm에 100mm 두께의 제 2의 실리콘 질화막(75)을 성막하고, 토탈 두께가 평면형의 게이트 전극의 두께 상당인 180mm 정도로 한다.

- [0348] 그리고, 화소부(3) 및 주변 회로부(61)측의 각각에서, 평면형 게이트 전극을 형성하여야 할 부분에 대응하는 위치에, 레지스트 마스크(76)를 통하여, 제 1, 제 2의 실리콘 질화막(64, 75) 및 실리콘 산화막(63)을 선택적으로 에칭 제거하여 홈(77)을 형성한다. 이 홈(77)은, 평면형의 게이트 전극 폭에 상당하는 홈 폭을 갖고서 형성된다. 이 홈(77)을 통과하여 임계치 전압이 조정되도록, 각각 n채널, p채널의 트랜지스터에 대응하여, 소요되는 채널 영역을 형성한다. 또한, 도시하지 않지만, 홈(77)을 형성할 때에, 게이트 전극 배선용의 홈을 형성할수가 있다. 예를 들면, 홈(77)에 연속하도록, 평면형 게이트 전극의 게이트 전극 배선을 형성하기 위한 홈도 동시에 형성할수 있다. 상기 채널 영역은, 평면형 게이트 전극에 대응하는 영역에 선택적으로 형성한다.

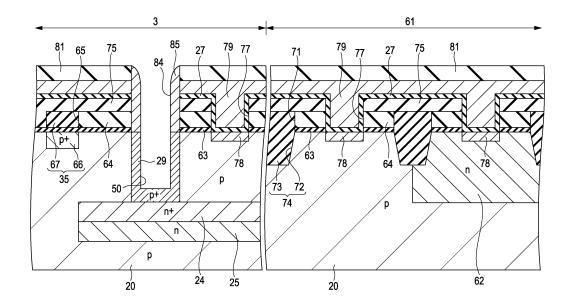

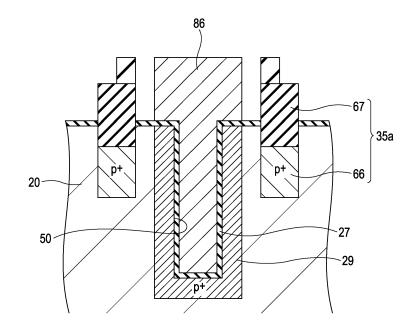

- [0349] 다음에, 도 27에 도시하는 바와 같이, 홈(77) 내에 게이트 절연막(27)을 통하여 언도프의 어모퍼스 실리콘 또는 폴리실리콘, 본 예에서는 언도프의 폴리실리콘막(79)을 매입하도록 형성한다. 언도프 실리콘막(79)은, 평면형 게이트 전극, 게이트 전극 배선에 상당하는 것이다. 폴리실리콘막(79)은, 실리콘 질화막(75)상에도 형성된다.

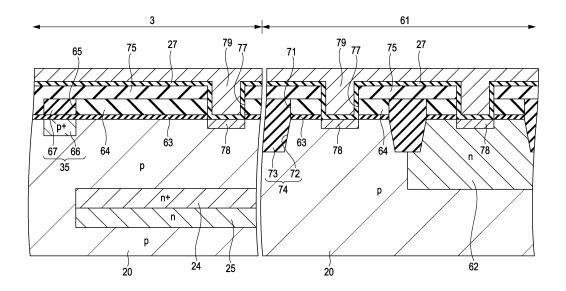

- [0350] 다음에, 도 28에 도시하는 바와 같이, 언도프의 폴리실리콘막(79)상에 실리콘 산화막(81)을 성막한다. 이 실리콘 산화막(81)상에 레지스트 마스크(82)를 형성한다. 레지스트 마스크(82)의 개구(83)를 통하여, 종형의 판독게이트 전극을 형성하여야 할 영역상의 실리콘 산화막(63), 제 1, 제 2의 실리콘 질화막(64, 75), 언도프의 폴리실리콘막(79), 및 실리콘 산화막(81)을 선택 에칭하여 개구부(84)를 형성한다.

- [0351] 이 개구부(84)를 통과하여, p형 불순물인 예를 들면 보론을 이온 주입하여, n+반도체 영역(24)에 달하는 p형 반도체 영역(29)을 형성한다. 이 p형 반도체 영역(29)의 형성에 즈음하여서는, 종형의 판독 게이트 전극에 대응하는 영역에만, 선택적으로 형성한다. 이 p형 반도체 영역(29)은, 암전류 억제를 위한 영역이다.

- [0352] 다음에, 도 29에 도시하는 바와 같이, 실리콘 산화막(63)부터 실리콘 산화막(81)에 이르는 다층막의 개구부(8 4)의 측벽에, 예를 들면 실리콘 산화막에 의한 측벽(85)을 형성한다. 이 측벽(85)은, 통상과 같이 홈부(84)의 내벽면을 포함하는 전면(全面)에 예를 들면 막두께 50nm 정도의 실리콘 산화막을 성막한 후, 실리콘 표면까지 드라이 에칭(에치백)하여 형성할 수 있다.

- [0353] 다음에, 도 30에 도시하는 바와 같이, 측벽을 마스크로, p형 반도체 영역(29)을 저부 및 주벽(周壁) 부분을 남겨 두도록 선택 에칭하여 세로 홈(50)을 형성한다. 이 세로 홈(50)은, 예를 들면 1년 정도의 깊이로 형성한다. 그 후, 에칭 데미지를 제거하기 위해 열산화(熱酸化)하고, 그 열산화막과 측벽 산화막(85) 및 실리콘 산화막(81)을 불산으로 제거한다. 이 불산으로 제거된 세로 홈(50) 상부의 넓은 개구부(84)는, 판독 게이트 전극의 인출 전극부가 형성되는 개구부가 된다.

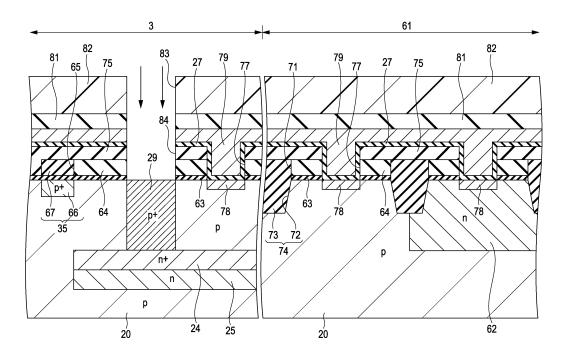

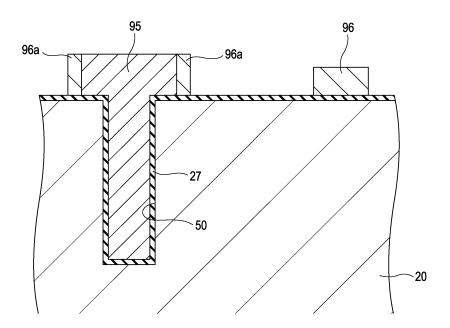

- [0354] 다음에, 도 31에 도시하는 바와 같이, 개구부(84) 및 세로 홈(50) 내에 게이트 절연막(27)이 되는 예를 들면 실리콘 산화막(27)을 통하여, 인 도프의 어모퍼스 실리콘 또는 폴리실리콘의 게이트 전극 재료(86)를 매입한다. 이 게이트 전극 재료(86)는, 인(P) 함유의 도펀트 가스와 실란의 소스 가스에 혼합한 혼합 가스를 사용한 CVD법으로 성막된다.

- [0355] 그 후, CMP법에 의해, 제 2의 실리콘 질화막(75)까지 일괄하여 평탄화 처리를 행한다. 즉, 언도프의 폴리실리콘막(79) 및 인 도프 실리콘의 게이트 전극 재료(86)를 일괄 평탄화 처리한다. 이로써, 세로 홈 및 개구부에 매입된 인 모프 실리콘에 의한 종형의 판독 게이트 전극(26) 및 그 상부의 인출 전극부(26a)와, 홈(77)에 매입된 평면형의 게이트 전극, 게이트 전극 배선으로 이루어지는 언도프의 폴리실리콘막(79)을 형성한다.

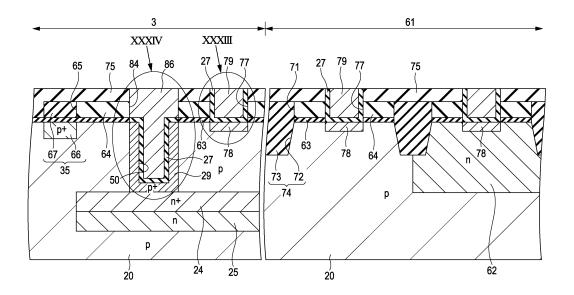

- [0356] 도 31에서의 언도프의 폴리실리콘막(79)을 포함하는 영역(A)의 도 31과 직교하는 방향의 단면 구조를 도 33에 도시한다. 도 26의 공정에서, 레지스트 마스크(76)의 개구가 소자 분리 영역(35a)을 타고넘는 크기로 형성되고, 이 레지스트 마스크(76)을 통하여 제 1, 제 2의 실리콘 질화막(75, 64)이 에칭 제거된다. 이 에칭 제거에서는, 소자 분리 영역(35a)의 실리콘 산화층(67) 일부 표면도 제거된다. 이로써, 언도프의 폴리실리콘막(79)은, 소자 분리 영역(35a)의 실리콘 산화층(67)의 단차(段差) 부분에 매입되도록 하여, 전체로서 T자형으로 형성된다. 최종적으로, 평면형의 게이트 전극은, 실리콘 산화층(67)의 단차 부분에 매입되도록, 전체로서 T자형으로 형성된다.

- [0357] 도 31에서의 종형의 판독 게이트 전극(26)을 포함하는 영역(B)의 도 31과 직교하는 방향의 단면 구조를 도 34에 도시한다.

- [0358] 다음에, 도 32에 도시하는 바와 같이, 제 1, 제 2의 실리콘 질화막(64, 75)를 열인산으로 제거한다. 그 후, 다른 화소 트랜지스터의 게이트 전극, 본 예에서는 리셋 게이트 전극, 앰프 게이트 전극, 및 주변 회로부(61)의 n 채널 MOS 트랜지스터의 게이트 전극에 대응하는 언도프의 폴리실리콘막(79)에 n형 불순물의 예를 들면 인(P)을 이온 주입한다. 또한, 주변 회로부(61)의 p채널 MOS 트랜지스터의 게이트 전극에 대응하는 언도프의 폴리실리콘막(79)에 p형 불순물인 예를 들면 보론(B)을 이온 주입한다. 이와 같이 하여, 화소 트랜지스터의 평면형의 게이트 전극(31, 33) 및 게이트 전극 배선과, CMOS 트랜지스터의 평면형의 게이트 전극(87, 88) 및 게이트 배선을 형성한다.

- [0359] 언도프의 폴리실리콘막(79)에 대한 불순물의 이온 주입은, 예를 들면 도 9의 공정의 후에, 선택적으로 n형, p형 의 불순물을 이온 주입할 수도 있다.

- [0360] 또한, 제 1, 제 2의 포토 다이오드(PD1, PD2)를 구성하는 n+반도체 영역(24), p+반도체 영역(23), n+반도체 영역(22), p+반도체 영역(21)을 이온 주입으로 형성한다. 또한, 화소 트랜지스터의 n형 반도체 영역에 의한 플로팅 디퓨전 영역(FD), 각 소스·드레인 영역(32, 34), 주변 회로부(61)측의 n채널 MOS 트랜지스터의 n형 반도체 영역에 의한 소스·드레인 영역(91, 92)을 형성한다. 또한, 주변 회로부(61)측의 p채널 MOS 트랜지스터의 p형 반도체 영역에 의한 소스·드레인 영역(93, 94)을 형성한다.

- [0361] 이와 같이 하여, 평면형의 게이트 전극(31, 33, 87, 88), 및 상부에 인출 전극부(26a)를 갖는 종형 판독 게이트 전극(26)이 형성된다. 동시에 게이트 전극 배선이 형성된다. 또한, 화소 트랜지스터, CMOS 트랜지스터의 n채널 MOS 트랜지스터(Trn), p채널 MOS 트랜지스터(Trp)가 형성된다.

- [0362] 평면형의 게이트 전극과 소스·드레인 영역은, 같은 도전형의 불순물을 동시에 이온 주입하여 형성할 수도 있다.

- [0363] 이 이후는, 도시하지 않지만, 다층 배선층, 컬러 필터, 온 칩 마이크로 렌즈 등을 형성하여, 목적하는 고체 촬상 장치를 얻는다.

- [0364] 또한, 도시하지 않지만, 종형의 판독 게이트 전극(26)을 보론 도프의 어모퍼스 실리콘 또는 폴리실리콘으로 형성하고, 평면형의 게이트 전극을 언도프의 어모퍼스 실리콘 또는 폴리실리콘을 성막한 후, 불순물을 이온 주입하여 형성할 수도 있다. 또한, 평면형의 게이트 전극을 갖는 트랜지스터의 형성에 있어서, 게이트 절연막을 전술한 고유전률 게이트 절연막으로 하고, 이 위에 고유전률 게이트 절연막과의 일함수 차를 상쇄하는 일함수를 갖는 전극 재료, 예를 들면 메탈로 평면형의 게이트 전극을 형성할 수도 있다.