(19) **日本国特許庁(JP)**

## (12)特許公報(B2)

(11)特許番号 特許第7183434号 (P7183434)

(45)発行日 令和4年12月5日(2022.12.5)

(24)登録日 令和4年11月25日(2022.11.25)

(51)国際特許分類 F I

**B41J 2/14 (2006.01)** B41J 2/14 611

**B 4 1 J 2/135(2006.01)** B 4 1 J 2/135

請求項の数 13 (全15頁)

(21)出願番号 特願2021-543387(P2021-543387) (

(86)(22)出願日 平成31年2月6日(2019.2.6)

(65)公表番号 特表2022-520333(P2022-520333

A)

(87)国際公開番号 WO2020/162921 (87)国際公開日 令和2年8月13日(2020.8.13)

審査請求日 令和3年7月27日(2021.7.27)

(73)特許権者 511076424

ヒューレット・パッカード デベロップ メント カンパニー エル・ピー・ Hewlett Packard De

velopment Company,

L . P .

アメリカ合衆国 テキサス州 77389

スプリング エナジー ドライブ 103

0 0

(74)代理人 100087642

弁理士 古谷 聡

(74)代理人 100082946

弁理士 大西 昭広

(74)代理人 100195693 弁理士 細井 玲

最終頁に続く

(54) 【発明の名称】 流体ダイ用のアドレスドライバを有する集積回路

## (57)【特許請求の範囲】

#### 【請求項1】

流体ダイの一部を形成する集積回路であって、

一組のアドレスを伝えるためのアドレスバスと、

前記一組のアドレスのうちのアドレスの第1の部分を前記アドレスバス上に<u>載せ</u>るための第1のアドレスドライバを含むダイ構成機能<u>回路</u>の第1のグループと、

前記一組のアドレスのうちのアドレスの第2の部分を前記アドレスバス上に<u>載せ</u>るための第2のアドレスドライバを含むダイ構成機能回路の第2のグループと、

流体付勢デバイスのアレイとを含み、前記流体付勢デバイスのそれぞれは、前記第1のアドレスドライバ及び前記第2のアドレスドライバにより前記アドレスバス上に載せられた前記一組のアドレスにおけるそれぞれのアドレスによりアドレス指定されることになり、前記第1の部分および前記第2の部分は合わさって、前記一組のアドレスのうちのアドレスを表す、集積回路。

## 【請求項2】

前記流体<u>付勢</u>デバイスのアレイは、前記ダイ構成機能<u>回路</u>の第1のグループと第2のグループとの間に長手方向に延在する流体付勢デバイスの列として構成される、請求項<u>1に</u>記載の集積回路。

## 【請求項3】

メモリ素子のアレイを含み、前記メモリ素子のアレイは、

前記ダイ構成機能回路の第1のグループに対応するメモリ素子の第1の部分と、

前記ダイ構成機能回路の第2のグループに対応するメモリ素子の第2の部分と、

前記流体付勢デバイスのアレイに対応するメモリ素子の第3の部分とを含み、

前記メモリ素子のアレイは、データセグメントを直列的にロードし、その結果、データセグメントをロードすることの完了時に、前記メモリ素子の第1の部分は、前記一組のアドレスのうちのアドレスの第1の部分を表す第1の組のアドレスビットを格納し、前記メモリ素子の第2の部分は、前記一組のアドレスのうちのアドレスの第2の部分を表す第2の組のアドレスビットを格納する、請求項1又は2に記載の集積回路。

## 【請求項4】

前記メモリ素子のアレイは、直列・並列データ変換器として機能するためのメモリ素子のチェーンを含み、この場合、前記メモリ素子の第1の部分は、前記ダイ構成機能回路の第1のグループに近接して配置され、前記メモリ素子の第2の部分は、前記ダイ構成機能回路の第2のグループに近接して配置され、前記メモリ素子の第3の部分は、前記メモリ素子の第1の部分と第2の部分との間に延在し且つ流体付勢デバイスのアレイに近接して配置される、請求項3に記載の集積回路。

#### 【請求項5】

前記第1<u>のアドレスドライバ</u>及び<u>前記</u>第2のアドレスドライバに加えて、前記ダイ構成機能<u>回路</u>は、噴射パルス制御<u>回路</u>およびセンサ<u>制御回路</u>を含む、請求項1~<u>4</u>の何れか1項に記載の集積回路。

#### 【請求項6】

流体ダイであって、

<u>流体付勢デバイスの列であって、前記流体付勢デバイスのそれぞれが、</u>一組のアドレス<u>の</u> <u>それぞれのアドレス</u>によりアドレス指定<u>されることになる、</u>流体付勢デバイスの列と、

第1の組のアドレスビットに基づいて、前記一組のアドレスのうちのアドレスの第1の 部分を供給するための第1のアドレスドライバと、

第2の組のアドレスビットに基づいて、前記一組のアドレスのうちのアドレスの残りの 部分を供給するための第2のアドレスドライバと、

前記第1の組のアドレスビットを前記第1のアドレスドライバに提供する、前記第1のアドレスドライバに対応するメモリ素子の第1の部分、及び前記第2の組のアドレスビットを前記第2のアドレスドライバに提供する、前記第2のアドレスドライバに対応するメモリ素子の第2の部分を含むメモリ素子のアレイとを含み、前記メモリ素子のアレイは、データセグメントを直列的にロードし、その結果、データセグメントをロードすることの完了時に、前記第1の部分のメモリ素子は、前記第1の組のアドレスビットを格納する、流体ダイ。

## 【請求項7】

前記メモリ素子のアレイは、前記流体付勢デバイスの列に対応するメモリ素子の第3の部分を含む、請求項6に記載の流体ダイ。

#### 【請求項8】

前記流体付勢デバイスの列は、前記第1のアドレスドライバと前記第2のアドレスドライバとの間に長手方向に延在する、請求項<u>6</u>又は<u>7</u>に記載の流体ダイ。

## 【請求項9】

前記流体付勢デバイスの列の流体付勢デバイスは、多数のプリミティブを形成するように構成され、各プリミティブの流体付勢デバイスは、前記一組のアドレスによりアドレス指定可能であり、各流体付勢デバイスは前記一組のアドレスのうちのアドレスの異なる1つに対応し、前記メモリ素子の第3の部分の各メモリ素子は、前記プリミティブの異なる1つに対応する、請求項6~8の何れか1項に記載の流体ダイ。

## 【請求項10】

前記メモリ素子のアレイは、直列 - 並列データ変換器として機能するためのメモリ素子のチェーンを含み、前記メモリ素子のチェーンは、前記流体付勢デバイスの列と平行に延在し、前記メモリ素子の第1の部分は、前記第1のアドレスドライバに近接して配置され、前記メモリ素子の第2の部分は、前記第2のアドレスドライバに近接して配置され、前

10

20

30

30

40

記メモリ素子の第3の部分は、前記メモリ素子の第1の部分と第2の部分との間に延在し且つ流体付勢デバイスの列に近接して配置される、請求項<u>6~9</u>の何れか1項に記載の流体ダイ。

#### 【請求項11】

流体ダイを動作させる方法であって、

データセグメントを受け取ることであって、各データセグメントは、

多数の構成データビットを含<u>み、且つ第1の組のアドレスビットを含む</u>ヘッド部分と、 多数の構成データビットを含<u>み、且つ第2の組のアドレスビットを含む</u>テール部分と、 前記ヘッド部分と前記テール部分との間に延在し且つ多数の付勢データビットを含む ボディ部分とを含む、データセグメントを受け取ること、

<u>前記流体ダイの</u>メモリ素子のアレイへ各データセグメントを直列的にロードすることであって、前記メモリ素子のアレイは、<u>前記流体ダイの</u>構成機能回路の第1のグループに対応するメモリ素子の第1の部分、<u>前記流体ダイの</u>構成機能回路の第2のグループに対応するメモリ素子の第2の部分、及び<u>前記流体ダイの</u>流体アクチュエータのアレイに対応するメモリ素子の第3の部分を含み、その結果、前記メモリ素子のアレイへデータセグメントをロードする際、前記ヘッド部分の前記構成データビットは、前記メモリ素子の第1の部分に格納され、前記テール部分の前記構成データビットは、前記メモリ素子の前記第2の部分に格納され、前記ボディ部分の前記付勢データビットは、前記メモリ素子の前記第3の部分に格納される、前記流体ダイのメモリ素子のアレイへ各データセグメントを直列的にロードすること、

一組のアドレスの各アドレスにより前記流体アクチュエータのそれぞれをアドレス指定するために、アドレスバスを介して、前記一組のアドレスを前記流体アクチュエータのアレイに伝えることを含み、その伝えることは、

前記構成機能回路の第1のグループの第1のアドレスドライバでもって、前記第1の組の アドレスビットに基づいて、前記一組のアドレスのうちのアドレスの第1の部分をアドレ スバス上へ載せ、

前記構成機能回路の第2のグループの第2のアドレスドライバでもって、前記第2の組の アドレスビットに基づいて、前記一組のアドレスのうちのアドレスの残りの部分を前記ア ドレスバス上へ載せることを含む、方法。

## 【請求項12】

直列 - 並列データ変換器として具現化される一連のメモリ素子として前記メモリ素子のアレイを構成することを含み、前記構成することは、前記一連のメモリ素子を長手方向に配置することを含み、前記メモリ素子の第 3 の部分は、前記メモリ素子の第 1 の部分と第 2 の部分との間に延在する、請求項<u>1 1</u> に記載の方法。

## 【請求項13】

前記メモリ素子の第1の部分に近接して前記構成機能回路の第1のグループを配置し、前記メモリ素子の第2の部分に近接して前記構成機能回路の第2のグループを配置し、前記構成機能回路の第1のグループと第2のグループとの間に長手方向に延在する列に且つ前記メモリ素子の第3の部分に近接して前記流体アクチュエータのアレイを配置することを含む、請求項11又は12に記載の方法。

【発明の詳細な説明】

## 【背景技術】

## [0001]

幾つかの印刷構成要素は、ノズルのアレイ及び/又はポンプを含むことができ、それらの各々が流体チャンバ及び流体アクチュエータを含み、この場合、流体アクチュエータは、チャンバ内の流体の変位をもたらすように付勢され得る。幾つかの例示的な流体ダイは、プリントヘッドであることができ、この場合、流体は、インク又は印刷薬剤に対応することができる。印刷構成要素は、2 D及び3 D印刷システム及び/又は他の高精度流体分注システムのプリントヘッドを含む。

## 【図面の簡単な説明】

10

20

30

#### [0002]

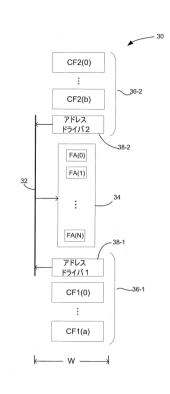

- 【図1】一例による、流体ダイ用の集積回路を示す略ブロック図である。

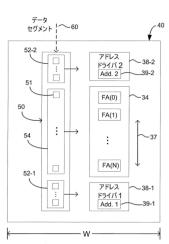

- 【図2】一例による、流体ダイを示す略ブロック図である。

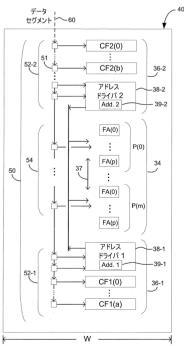

- 【図3】一例による、流体ダイを示す略ブロック図である。

- 【図4】一例による、データセグメントを一般的に示す略図である。

- 【図5】一例による、プリミティブ構成の部分を一般的に示す略ブロック図である。

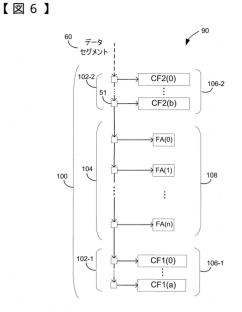

- 【図6】一例による、流体ダイ用の集積回路を示す略ブロック図である。

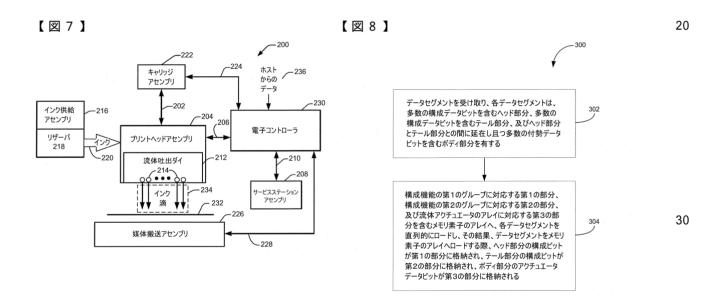

- 【図7】流体吐出システムの一例を示すブロック図を示す略図である。

- 【図8】一例による流体ダイを動作させる方法を示す流れ図である。

【発明を実施するための形態】

## [0003]

図面の全体にわたって、同じ参照番号は、類似するが、必ずしも全く同じでない要素を 示す。図面は、必ずしも一律の縮尺に従っておらず、幾つかの部分のサイズは、図示され た例をより明確に示すために誇張され得る。更に、図面は、説明と一致した例および/ま たは具現化形態を提供するが、当該説明は、図面に提供された当該例および/または具現 化形態に制限されない。

### [0004]

## 詳細な説明

以下の詳細な説明において、その一部を形成する添付図面が参照され、添付図面には、 本開示が実施され得る特定の例が実例として示される。理解されるべきは、他の例が利用 されることができ、構造的または論理的変更が本開示の範囲から逸脱せずに行われ得る。 従って、以下の詳細な説明は、制限の意味で解釈されるべきではなく、本開示の範囲は、 添付の特許請求の範囲により定義される。理解されるべきは、本明細書で説明される様々 な例の特徴要素は、特に断りのない限り、部分的に又は全体的に互いに組み合わされ得る。

[0005]

流体ダイの例は、流体アクチュエータを含むことができる。流体アクチュエータは、電 気的付勢に応答して流体の変位をもたらすことができる、熱抵抗器ベースのアクチュエー 夕(例えば、流体を噴射または再循環するための)、圧電膜ベースのアクチュエータ、静 電膜アクチュエータ、機械的/インパクト駆動型膜アクチュエータ、磁歪駆動アクチュエ ータ、又は他の適切なデバイスを含むことができる。本明細書で説明される流体ダイは、 流体アクチュエータのアレイと呼ばれ得る、複数の流体アクチュエータを含むことができ る。付勢は、流体変位をもたらすために流体ダイの流体アクチュエータの単一の又は同時 の付勢を意味することができる。付勢イベントの一例は、流体噴射イベントであり、それ により、流体がノズルを介して噴出される。

#### [0006]

例示的な流体ダイにおいて、流体アクチュエータのアレイは、流体アクチュエータのセ ット(組)へ配列(構成)されることができ、この場合、係る流体アクチュエータのセッ トのそれぞれは、「プリミティブ」又は「噴射プリミティブ」と呼ばれ得る。プリミティ ブにおける流体アクチュエータの数は、プリミティブのサイズと呼ばれ得る。幾つかの例 において、各プリミティブの流体アクチュエータは、付勢アドレスの同じセットを用いて アドレス指定可能であり、この場合、プリミティブの各流体アクチュエータは、付勢アド レスのセットの異なる付勢アドレスに対応する。例において、アドレスのセットは、各プ リミティブにより共用されるアドレスバスを介して、各プリミティブに伝えられる。

## [0007]

一例において、アドレスデータに加えて、各プリミティブは、対応するデータ線を介し て付勢データ(時として、噴射データ又はノズルデータと呼ばれる)を、及び噴射信号線 を介して噴射信号(噴射パルスるとも呼ばれる)を受け取る。一例において、付勢イベン ト又は噴射イベント中に、各プリミティブにおいて、噴射信号線に存在する噴射信号に応 答して、アドレス線を介して伝えられたアドレスに対応する流体アクチュエータが、プリ ミティブに対応する付勢データに基づいて付勢(例えば、噴射)される。

10

20

30

40

## [0008]

場合によっては、流体ダイの電気的および流体的な動作制約は、各プリミティブのどの 流体アクチュエータが所与の付勢イベントに対して同時に(並行して)付勢され得るかを 制限する場合がある。プリミティブは、係る動作制約に従う所与の付勢イベントに関して 同時に付勢され得る流体アクチュエータのサブセットの付勢を容易にする。

(5)

## [0009]

一例として示すために、流体ダイが4個のプリミティブを含み、各プリミティブが、8個の流体アクチュエータ(この場合、各流体アクチュエータは、一組のアドレス0~7の異なるアドレスに対応する)を含む場合、電気的および流体的な制約は、付勢をプリミティブ毎に1個の流体アクチュエータに制限し、総計4個の流体アクチュエータ(各プリミティブから1個)が所与の付勢イベントに関して同時に付勢され得る。例えば、第1の付勢イベントに関して、アドレス「0」に対応する各プリミティブの個々の流体アクチュエータが付勢され得る。第2の付勢イベントに関して、アドレス「5」に対応する各プリミティブの個々の流体アクチュエータが付勢され得る。理解されるように、係る例は、例示のために単に提供されており、本明細書で企図された流体ダイは、プリミティブ毎により多い又はより少ない流体アクチュエータ、及びダイ毎により多い又はより少ないプリミティブを含むことができる。

#### [0010]

例示的な流体ダイは、エッチング、微細加工(例えば、フォトリソグラフィー)、マイクロマシニングプロセス、又は他の適切なプロセス、或いはそれらの組み合わせにより、流体ダイの基板に製作された表面により画定され得る流体チャンバ、オリフィス、及び/又は他の特徴要素を含むことができる。幾つかの例示的な基板は、シリコンベースの基板、ガラスベースの基板、ガリウムヒ素ベースの基板、及び/又は微細加工されるデバイス及び構造用の他の係る適切なタイプの基板を含むことができる。本明細書で使用される限り、流体チャンバは、流体が吐出され得るノズルオリフィスと流体連絡する吐出チャンに、及び流体が運ばれ得る流体チャネルを含むことができる。幾つかの例において、流体チャネルは、微小流体チャネルであることができ、この場合、本明細書で使用される限り、微小流体チャネルは、少量の流体(例えば、ピコリットルのスケール、ナノリットルのスケール、マイクロリットルのスケール、ミリリットルのスケール、マイクロメートのスケール、ミリメートルサイズのスケール、マイクロメートルサイズのスケール、ミリメートルサイズのスケールに対応することができる。

## [0011]

幾つかの例において、流体アクチュエータは、ノズルの一部として配置(配列)されることができ、この場合、流体アクチュエータに加えて、ノズルは、ノズルオリフィスと流体連絡する吐出チャンバを含む。流体アクチュエータの付勢が、ノズルオリフィスを介して流体チャンバから流体滴の吐出をもたらすことができる流体チャンバ内の流体の変位を生じさせるように、流体アクチュエータは流体チャンバに対して配置される。従って、ノズルの一部として配置された流体アクチュエータは、時として、流体吐出器または吐出アクチュエータと呼ばれ得る。

#### [0012]

幾つかの例において、流体アクチュエータは、ポンプの一部として配置(配列)されることができ、この場合、流体アクチュエータに加えて、ポンプは、流体チャネルを含む。流体アクチュエータの付勢が、例えば流体供給部とノズルとの間のような、流体ダイ内で流体を輸送するために流体チャネル(例えば、微小流体チャネル)において流体変位を生じるように、流体アクチュエータは、流体チャネルに対して配置される。ダイ内の流体変位 / ポンピングの一例は、時として、微小再循環とも呼ばれる。流体チャネル内で流体を輸送するように構成された流体アクチュエータは、時として、非吐出アクチュエータ又は微小再循環アクチュエータと呼ばれ得る。1つの例示的なノズルにおいて、流体アクチュエータは、サーマルアクチュエータからなることができ、この場合、流体アクチュエータ

10

20

30

40

20

30

40

50

の付勢(時として、「噴射」と呼ばれる)は、流体滴がノズルオリフィスから吐出され得る流体チャンバ内にガス状駆動気泡を形成するために流体を加熱する。上述されたように、流体アクチュエータは、アレイ(例えば、列のような)に配列されることができ、この場合、アクチュエータは、流体吐出器および/またはポンプとして具現化されることができ、流体吐出器の選択的な動作は、流体滴の吐出をもたらし、ポンプの選択的な動作は、流体ダイ内で流体の変位をもたらす。幾つかの例において、流体アクチュエータの係るアレイは、プリミティブへ構成され得る。

#### [0013]

幾つかの流体ダイは、時として、噴射パルスグループ又は噴射パルスグループデータパケットと呼ばれる、データパケットの形態でデータを受け取り、この場合、各噴射パルスグループは、ヘッド部分とボディ部分を含む。幾つかの例において、ヘッド部分は、例えば、アドレスドライバ用のアドレスデータ(付勢アドレスのセットのアドレスを表す)、噴射パルス制御回路用の噴射パルスデータ、及びセンサ制御回路用のセンサデータ(例えば、熱センサを選択および構成する)のようなオンダイ構成機能の構成データを含む。一例において、各噴射パルスグループのボディ部分は、噴射パルスに応答して付勢される当該ヘッド部分のアドレスデータにより表されたアドレスにどのノズルが対応するかを選択する付勢データを含む。

#### [0014]

幾つかの流体ダイにおいて、アドレスドライバが、各噴射パルスグループのヘッド部分からアドレスデータビットを受け取り、当該データビットにより表されたアドレスをアドレスバス上へ駆動し、この場合、アドレスバスは、アドレスを流体アクチュエータのアレイに伝える。噴射パルスグループのアドレスビットにより表されたアドレスをアドレスバス上へ駆動することに加えて、場合によっては、アドレスドライバは、アドレスバス上へアドレスの相補信号も駆動する。

#### [0015]

アドレスドライバ回路は、流体ダイ上で比較的大量のシリコン面積を消費し、それによりダイのサイズとコストが増加する。本明細書でより詳細に説明されるように、本開示の例に従って、アドレスドライバ回路は、複数の部分へ分割され、この場合、各部分は、アドレスの異なる部分をアドレスバス上へ駆動する。一例において、アドレスドライバは、2つの部分へ分割され、アドレスドライバ回路のそれぞれは、付勢アドレスの異なる部分をアドレスバス上へ駆動する。アドレスドライバを複数の部分へ分割することにより、幅のような、少なくとも1つの寸法において必要とされるシリコン面積の量は、それにより少なくとも1つの寸法においてシリコンを節約し、流体ダイが少なくとも1つの寸法において、より小さくなることを可能にする。

## [0016]

図1は、本開示の一例による、流体アクチュエータのアレイ用の集積回路30を一般的に示す略ブロック図である。一例において、集積回路30は、より詳細に後述される流体ダイの一部である。集積回路30は、流体付勢デバイスFA(0)~FA(n)で示された流体付勢デバイス34のアレイに一組のアドレスを伝えるためのアドレスバス32を含み、この場合、流体付勢デバイスFA(0)~FA(n)は、当該一組のアドレスを用いてアドレス指定可能である。一例において、各流体付勢デバイスFA(0)~FA(n)は、当該一組のアドレスのアドレスうちの異なる1つに対応する。一例において、アレイ34の流体付勢デバイスFA(0)~FA(n)は、列を形成するように構成される。

#### [0017]

一例において、集積回路 3 0 は、第 1 のアドレスドライバ 3 8 - 1 及び C F 1 (0) ~ C F 1 (a) として示された多数の更なる機能を含む構成機能の第 1 のグループ 3 6 - 1 、及び第 2 のアドレスドライバ 3 8 - 2 及び C F 2 (0) ~ C F 2 (b) として示された多数の更なる構成機能を含む構成機能の第 2 のグループ 3 6 - 2 を含む。場合によっては、アドレスドライバ 3 8 - 1 及び 3 8 - 2 に加えて、構成機能の第 1 及び第 2 のグループ 3 6 - 1 及び 3 6 - 2 の更なる構成機能 C F 1 (0) ~ C F 1 (a) 及び C F 2 (0) ~

20

30

40

50

CF2(b)は、数ある中で、例えば、噴射パルス制御構成機能(例えば、ウォーミング、先行するもの、及び噴射パルス構成を調整するために)、及びセンサ構成機能(例えば、熱センサ構成を選択および制御するために)を含む。

#### [0018]

動作中、第1のアドレスドライバ38-1は、一組のアドレスのうちのアドレスの第1の部分をアドレスバス32上へ駆動し、第2のアドレスドライバ38-2は、一組のアドレスのうちのアドレスの残りの部分をアドレスバス32上へ駆動し、この場合、流体付勢デバイスのアレイ34の流体付勢デバイスの少なくとも1つは、第1及び第2のアドレスドライバ38-1及び38-2によりアドレスバス32上に駆動されたアドレスに対応する。図1により示されたように、アドレスドライバを複数の部分(例えば、アドレスドライバ38-1及び38-2)へ分割することにより、幅寸法Wのような少なくとも1つの寸法においてアドレスドライバ回路に必要なシリコンのスペースの量が減少し、これにより、集積回路30が一部を形成することができる流体ダイが少なくとも1つの寸法においてより小さくなることを可能にする。

#### [0019]

図2は、本開示の一例による、流体ダイ40の一例を示す略ブロック図である。図示された例に従って、上述されたように、一組のアドレスによりアドレス指定可能である流体アクチュエータ34のアレイに加えて、流体ダイ40は、第1の組のアドレスビット39-1に基づいて一組のアドレスのうちのアドレスの第1の部分を提供する第1のアドレスドライバ38-1、及び第2の組のアドレスビット39-2に基づいて一組のアドレスのうちのアドレスの第2の部分を提供する第2のアドレスドライバ38-2を含む。一例において、第1及び第2の組のアドレスビットは共に、一組のアドレスの1つのアドレスを提供する。

#### [0020]

流体ダイ40は更に、メモリ素子51により示されたようなメモリ素子のアレイ50を含む。一例に従って、メモリ素子のアレイ50は、第1のアドレスドライバ38-1に対応するメモリ素子の第1の部分52-1、第2のアドレスドライバ38-2に対応するメモリ素子の第2の部分52-2、及び流体アクチュエータのアレイ34に対応するメモリ素子の第3の部分54を含む。一例において、メモリ素子のアレイ50は、データセグメント60を直列的(シリアル)にロードすることができ、各データセグメントは一連のデータビットを含み、その結果、データセグメント60をロードすることの完了時に、メモリ素子の第1の部分52-1のメモリ素子は、第1の組のアドレスビット39-1を格納し、メモリ素子の第2の部分52-2のメモリ素子は、第2の組のアドレスビット39-2を格納する。例に従って、第1及び第2のアドレスドライバ38-1及び38-2はそれぞれ、第1及び第2の組のアドレスビット39-1及び第2の部分52-1及び52-2から受け取って、一組のアドレスのうちのアドレスの第1及び第2の部分を流体アクチュエータのアレイ34に供給する。

## [0021]

一例において、流体アクチュエータのアレイ34の流体アクチュエータは、長手方向37に延在する列を形成するように配列される。一配列において、図示されたように、第1及び第2のアドレスドライバ38-1及び38-2は、流体アクチュエータ(FA)のアレイ34の列の両端に配置される。一例において、メモリ素子のアレイ50のメモリ素子51は、直列・並列データ変換器として具現化されるメモリ素子のチェーン又は一連のメモリ素子として構成され、この場合、一連のメモリ素子は、流体アクチュエータのアレイ34の長手方向37に延在するように配置され、その結果、メモリ素子の第1及び第2の部分52-1及び52-2はそれぞれ、第1及び第2のアドレスドライバ38-1及び38-2に近接して配置され、メモリ素子の第3の部分54は、流体アクチュエータのアレイ34に近接して配置される。

#### [0022]

第1及び第2のアドレスドライバ38-1及び38-2を流体アクチュエータのアレイ

20

30

40

50

3 4 の流体アクチュエータFA(0)~FA(n)の列の両端に配置することにより、及び長手方向 3 7 に延在するメモリ素子のチェーンとしてメモリ素子のアレイ 5 0 を配列することにより、幅寸法Wのような流体ダイ 4 0 の少なくとも 1 つの寸法に必要なシリコンスペースの量が減少し、それにより流体ダイ 4 0 の幅が低減されることが可能になる。

#### [0023]

図3は、本開示による、流体ダイ40の一例を示す略ブロック図である。一例において、図示されたように、流体アクチュエータのアレイ34は、長手方向37に延在する流体アクチュエータの列として具現化され、この場合、流体アクチュエータの列は、プリミティブP(0)~プリミティブP(m)として示された多数のプリミティブを形成するように構成される。一例において、各プリミティブP(0)~P(m)は、流体アクチュエータFA(0)~FA(p)として示された多数の流体アクチュエータを有する。一例において、各プリミティブP(0)~P(m)は、同じ組のアドレスを使用し、この場合、各プリミティブの各流体アクチュエータFA(0)~FA(p)は、例えば、一組のアドレスの異なる1つに対応する。

#### [0024]

構成機能の第1のグループ36-1は、第1のアドレスドライバ38-1、及び多数の追加の構成機能CF1(0)~CF1(a)を含み、構成機能の第2のグループ36-2は、第2のアドレスドライバ38-2、及び多数の追加の構成機能CF2(0)~CF2(b)を含む。第1のアドレスドライバ38-1は、第1の組のアドレスビット39-1に基づいて、一組のアドレスのうちのアドレスの第1の部分をアドレスバス32上に駆動し、第2のアドレスドライバ38-2は、第2の組のアドレスビット39-2に基づいて、一組のアドレスのうちのアドレスの残りの部分をアドレスバス32で駆動し、次いで、アドレスを各プリミティブP(0)~P(m)に伝える。一例において、図示されたように、構成機能の第1及び第2のグループ36-1及び36-2は、流体アクチュエータのアレイ34の両端において長手方向37に配置される。

## [0025]

一例において、図示されたように、メモリ素子のアレイ50は、直列・並列データ変換器として具現化される一連のメモリ素子51又はメモリ素子51のチェーンからなり、この場合、メモリ素子51の第1の部分52-1は、構成機能の第1のグループ36-1に対応し、メモリ素子の第2の部分52-2は、構成機能の第2のグループ36-2に対応し、メモリ素子の第3の部分54は、流体アクチュエータのアレイ34に対応し、この場合、第3の部分54の各メモリ素子51は、プリミティブP(0)~P(m)の異なる1つに対応する。一例において、メモリ素子のアレイ50は、順序論理回路(例えば、フリップフロップのアレイ、ラッチアレイなど)を含む。一例において、順序論理回路は、直列入力並列出力シフトレジスタとして機能するように適合される。

## [0026]

一例において、メモリ素子51のアレイ50のチェーンは、長手方向37に延在し、この場合、メモリセルの第1の部分52-1は、構成機能の第1のグループ36-1に近接して配置され、メモリセルの第2の部分52-2は、構成機能の第2のグループ36-2に近接して配置され、メモリセルの第3のグループ54は、メモリセルの第1の部分52-1と第2の部分52-2との間に且つ流体アクチュエータ(FA)のアレイ34の列に近接して延在する。

#### [0027]

図3により示されたような、流体ダイ40の動作の一例は、図4及び図5に関連して後述される。図4は、流体ダイ40のメモリ素子のアレイ50により受け取られるデータセグメント60の一例を一般的に示すブロック図である。図示されたように、データセグメント60は、データビット61により示されたような一連のデータビットを含み、係る一連のデータビットは、時として「ヘッド」と呼ばれるデータビットの第1の部分62・1、時として「テール」と呼ばれるデータビットの第2の部分62・2、及び時として「ボ

ディ」と呼ばれるデータビットの第3の部分64を含む。総合して、データビットの第1、第2及び第3の部分62-1、62-2及び64は、ひとまとめにして噴射パルスグループと呼ばれる。

#### [0028]

データビットの第1の部分62-1は、構成機能の第1のグループ36-1用のデータビットを含み、第1のアドレスドライバ38-1用の第1の組のアドレスデータビット39-1を含む。データビットの第2の部分62-2は、構成機能の第2のグループ36-2用のデータビットを含み、第2のアドレスドライバ38-2用の第2の組のアドレスデータビット39-2を含む。データビットの第3の部分64は、流体アクチュエータのアレイ34用の付勢データビットを含み、この場合、データビットの第3の部分64の各データビット61は、プリミティブP(0)~P(m)の異なる1つに対応する。データビットの第3の部分64のデータビットは、時としてプリミティブデータと呼ばれる。

#### [0029]

図3(及び図2)に関連して、一連の係るデータセグメントの各データセグメント60はメモリ素子のアレイ50へ直列的にロードされ、ヘッド部分62-1の最初のビットから始まり、テール部分62-2の最後のビットで終了する。メモリ素子のアレイ50へ直列的にロード又はシフトされた後、データセグメント60のヘッド部分62-1のデータビット61はメモリ素子の第1の部分52-1に格納され、この場合、第1の組のアドレスビット39-1は、第1のアドレスドライバ38-1に対応する。同様に、データセグメント60のテール部分62-2のデータビット61は、メモリ素子の第2の部分52-2に格納され、この場合、第2の組のアドレスビット39-2は、第2のアドレスドライバ38-2に対応する。データセグメント60の第3の部分64のデータビット61は、メモリ素子のアレイ50の第3の部分54に格納される。

#### [0030]

図5は、図3のプリミティブP(0)のような、プリミティブ構成の一部を一般的に示す略ブロック図である。一例において、各流体アクチュエータFAは、図5において熱抵抗器として示され、電源VPPと、FET70により示されたような対応する制御可能なスイッチを介して基準電位(例えば、接地)との間に接続可能である。

## [0031]

一例に従って、プリミティブP(0)を含む、各プリミティブは、メモリ素子のアレイ50のメモリ素子の第3のグループ54の対応するメモリ素子51からプリミティブP(0)用のプリミティブデータ(例えば、付勢データ)を第1の入力において受け取るANDゲート72を含む。第2の入力において、ANDゲート72は、噴射信号74(例えば、噴射パルス)を受け取り、当該噴射信号74は、流体アクチュエータFA(0)のような、流体アクチュエータの付勢または噴射の持続時間を制御する。一例において、噴射信号74は、遅延素子76により遅延され、この場合、噴射アクチュエータの噴射がプリミティブP(0)~P(m)の間で同時に生じないように、各プリミティブは異なる遅延を有する。

## [0032]

一例において、各流体アクチュエータ(FA)は、第1及び第2のアドレスドライバ38-1及び38-2によりアドレスバス32上に駆動されたアドレスを受け取る対応するアドレス復号器78、及びFET70のゲートを制御するための対応するANDゲート80を有する。ANDゲート80は、第1の入力において、対応するアドレス復号器78の出力を受け取り、第2の入力において、ANDゲート72の出力を受け取る。留意される点は、アドレス復号器78及びANDゲート80は、各流体アクチュエータFAに対して繰り返されるが、ANDゲート72及び遅延素子76は、各プリミティブに対して繰り返される。

## [0033]

一例において、メモリ素子のアレイ 5 0 ヘロードされた後、データセグメント 6 0 のヘッド部分 6 2 - 1、テール部分 6 2 - 2 及びボディ部分 6 4 のデータビット 6 1 により表

10

20

30

40

された噴射パルスグループデータ(図4を参照)は、流体を循環する又は流体滴を吐出するように、選択された流体アクチュエータ(FA)を動作させるために、構成機能の対応するグループ38-1と38-2及びプリミティブP(0)~P(m)により、処理される。例えば、図5に関連して、一例において、プリミティブP(0)に対応するメモリ素子51に格納されたアクチュエータデータが論理ハイ(例えば、「1」)を有し、且力は、論理「ハイ」に設定される。メモリ素子の第1及び第2の部分54-1と54-2の対応するメモリ素子から受け取ったアドレスビットの組39-1と39-2に応答して、第1及び第2のアドレスドライバ38-1と38-2によりアドレスバス32上に駆動理「ハイ」に設定される。この場合、ANDゲート72の出力およびアドレス「0」復号器78の出力は、流下ドレスが、アドレス「0」を表す場合、アドレス「0」復号器78の出力に設定される。この場合、ANDゲート80の出力も論理「ハイ」に設定される。この場合、ANDゲート80の出力も論理「ハイ」に設定されていた。

#### [0034]

図6は、本開示の一例による、流体アクチュエータのアレイ用の集積回路90を一般的に示す略プロック図である。一例において、集積回路90は、流体ダイの一部として具現化される。集積回路90は、ダイ構成機能の第1のグループ106-1に対応するメモリ素子の第1の部分102-1、ダイ構成機能の第2のグループ106-2に対応するメモリ素子の第2の部分102-2、及び流体アクチュエータのアレイ108に対応するメモリ素子の第3の部分104を含む一連のメモリ素子100を含み、この場合、メモリ素子の第3の部分104のメモリ素子は、メモリ素子の第1の部分102-1と第2の部分102-2との間に延在する。

## [0035]

一例において、流体アクチュエータのアレイ108は、流体アクチュエータFA(0)~FA(n)として示された多数の流体アクチュエータを含む。一例において、構成機能の第1のグループ106-1は、CF1(0)~CF1(a)として示された多数の構成機能を含み、構成機能の第2のグループ106-2は、CF2(0)~CF2(b)として示された多数の構成機能を含む。例において、ダイ構成機能は、流体アクチュエータのアレイ108と関連付けられたアドレスを駆動するためのアドレスドライバ、噴射信号を介して、流体アクチュエータのアレイ108の流体アクチュエータの付勢時間または噴射時間を調整するための噴射パルス制御回路、及びセンサ回路を構成する(例えば、熱センサを選択および構成する)ためのセンサ制御回路のような、機能を含むことができる。

## [0036]

例において、一連のメモリ素子100は、図4により示されたデータセグメント60のような、一連のデータビットを含むデータセグメントを直列的にロードし、その結果、データセグメントをロードすることの完了時に、メモリ素子の第1の部分102-1のメモリ素子は、ダイ構成機能の第1のグループ106-1用のデータビットを格納し、メモリ素子の第2の部分102-2は、ダイ構成機能の第2のグループ106-2用のデータビットを格納し、メモリ素子の第3の部分104は、流体アクチュエータのアレイ108用のデータビットを格納する。

## [0037]

図7は、流体吐出システム200の一例を示すブロック図である。流体吐出システム200は、プリントヘッドアセンブリ204のような流体吐出アセンブリ、及びインク供給アセンブリ216のような流体供給アセンブリを含む。図示された例において、流体吐出システム200は、サービスステーションアセンブリ208、キャリッジアセンブリ222、印刷媒体搬送アセンブリ226、及び電子コントローラ230も含む。以下の説明はインクに関して取り扱う流体に対するシステム及びアセンブリの例を提供するが、開示されたシステム及びアセンブリは、インク以外の流体の取り扱いにも適用可能である。

10

20

30

## [0038]

プリントへッドアセンブリ204は、複数のオリフィス又はノズル214を介してインク又は流体の小滴を吐出する少なくとも1つのプリントへッド212を含み、この場合、プリントへッド212は、一例において、例えば、図1により本明細書で前述されたように、ノズル214として具現化された流体アクチュエータFA(0)~FA(n)を有する集積回路30を用いて、具現化され得る。一例において、小滴は、印刷媒体232上へ印刷するように、印刷媒体232のような媒体へ向けて送られる。一例において、印刷媒体232は、用紙、カード用紙、透明媒体、マイラー(登録商標)、生地、及び同類ののような、任意のタイプの適切なシート材料を含む。別の例において、印刷媒体232は、粉末ベッドのような三次元(3D)印刷用の媒体、或いはリザーバ又は容器のようなバイオプリンティング及び/又は創薬試験用の媒体を含む。一例において、プリントへッドアセンブリ204及び印刷媒体232が互いに対して移動する際に、ノズル214からの適切に順序付けられたインクの吐出により、文字、記号および/または他のグラフィックス又はイメージが印刷媒体232上に印刷されるように、ノズル214は、少なくとも1つの列またはアレイに配列される。

## [0039]

インク供給アセンブリ216は、インクをプリントヘッドアセンブリ204に供給し、インクを貯蔵するためのリザーバ218を含む。そのため、一例において、インクはリザーバ218からプリントヘッドアセンブリ204に流れる。一例において、プリントヘッドアセンブリ204及びインク供給アセンブリ216は、インクジェット又は流体ジェット印刷カートリッジ又はペンに一緒になるように収容される。別の例において、インク供給アセンブリ216は、プリントヘッドアセンブリ204から分離し、供給管および/またはバルブのようなインターフェース接続220を介して、インクをプリントヘッドアセンブリ204に供給する。

#### [0040]

キャリッジアセンブリ222は、プリントヘッドアセンブリ204を印刷媒体搬送アセンブリ226に対して位置決めし、印刷媒体搬送アセンブリ226は、印刷媒体232をプリントヘッドアセンブリ204に対して位置決めする。かくして、印刷区域234が、プリントヘッドアセンブリ204と印刷媒体232との間の領域において、ノズル214に隣接して画定される。一例において、プリントヘッドアセンブリ204は、キャリッジアセンブリ222が印刷媒体搬送アセンブリ226に対してプリントヘッドアセンブリ204を移動させるような、走査型プリントヘッドアセンブリ222が印刷媒体搬送アセンブリ226に対して所定の位置にプリントヘッドアセンブリ204を固定するような、非走査型プリントヘッドアセンブリである。

## [0041]

サービスステーションアセンブリ208は、プリントヘッドアセンブリ204、より具体的にはノズル214の機能性を維持するために、プリントヘッドアセンブリ204のスピッティング(吐き出し)、ワイピング、キャッピング及び / 又はプライミングを行う。例えば、サービスステーションアセンブリ208は、ノズル214から余分なインクを拭き取る又は取り除くためにプリントヘッドアセンブリ204上を周期的に通過するゴム製ブレード又はワイパを含むことができる。更に、サービスステーションアセンブリ208は、使用していない期間中にノズル214を乾燥から保護するためにプリントヘッドアセンブリ208は、リザーバ218が適切なレベルの圧力および流動性を確実に維持するためにリンスル214が詰まっていない又は垂らさないことを保証するために、プリントヘッドアセンブリ208の機能は、サービスステーションアセンブリ208の機能は、サービスステーションアセンブリ208の機能は、サービスステーションアセンブリ208の機能は、サービスステーションアセンブリ208の機能は、サービスステーションアセンブリ208の機能は、サービスステーションアセンブリ208の機能は、サービスステーションアセンブリ208080日の相対運動を含むことができる。

## [0042]

50

40

10

20

電子コントローラ230は、通信経路206を介してプリントへッドアセンブリ204と通信し、通信経路210を介してサービスステーションアセンブリ208と通信し、通信経路224を介してキャリッジアセンブリ222と通信し、及び通信経路228を介して印刷媒体搬送アセンブリ226と通信する。一例において、プリントへッドアセンブリ204がキャリッジアセンブリ222に取り付けられる場合、電子コントローラ230とプリントへッドアセンブリ204は、通信経路202を介してキャリッジアセンブリ222を経由して通信することができる。また、電子コントローラ230は、一具現化形態において、新たな(又は使用済み)インク供給品が検出され得るように、インク供給アセンブリ216と通信することもできる。

#### [0043]

電子コントローラ 2 3 0 は、コンピュータのようなホストシステムからデータ 2 3 6 を受け取り、一時的にデータ 2 3 6 を格納するためのメモリを含むことができる。データ 2 3 6 は、電子経路、赤外線経路、光学的経路または他の情報伝達経路に沿って、流体吐出システム 2 0 0 に送信され得る。データ 2 3 6 は例えば、印刷されるべき文章(書類)及び/又はファイルを表す。そのため、データ 2 3 6 は、流体吐出システム 2 0 0 用の印刷ジョブを形成し、少なくとも 1 つの印刷ジョブコマンド及び/又はコマンドパラメータを含む。

#### [0044]

一例において、電子コントローラ230は、プリントへッドアセンブリ204の制御を行い、当該制御には、ノズル214からのインク滴の吐出に関するタイミング制御が含まれる。そのため、電子コントローラ230は、文字、記号および/または他のグラフィックス又はイメージを印刷媒体232上に形成する、吐出されるインク滴のパターンを定義する。タイミング制御、それ故に吐出されるインク滴のパターンは、印刷ジョブコマンド及び/又はコマンドパラメータにより決定される。一例において、電子コントローラ230の一部を形成する論理回路および駆動回路は、プリントへッドアセンブリ204上に位置する。別の例において、電子コントローラ230の一部を形成する論理回路および駆動回路は、プリントへッドアセンブリ204から離れて位置する。一例において、データセグメント33-1~33-n、間欠クロック信号35、噴射信号72、及びモード信号79は、電子コントローラ230により印刷構成要素30に供給されることができる。

## [0045]

図8は、本開示の一例による、例えば、図3の流体ダイ40のような流体ダイを動作させる方法300を一般的に示す流れ図である。302において、方法300は、データセグメントを受け取ることを含み、各データセグメントは、ヘッド部分62-1、テール部分62-2及びボディ部分64を含む図4のデータセグメント60のような、多数の構成データビットを含むヘッド部分、多数の構成データビットを含むテール部分、及びヘッド部分とテール部分との間に延在し且つ多数の付勢データビットを含むボディ部分を有する。【0046】

304において、方法300は、構成機能の第1のグループに対応するメモリ素子の第1の部分、構成機能の第2のグループに対応するメモリ素子の第2の部分、及び流体アクチュエータのアレイに対応するメモリ素子の第3の部分を含むメモリ素子のアレイへ各データセグメントを直列的にロードすることを含み、その結果、データセグメントをメモリ素子のアレイへロードする時に、ヘッド部分の構成ビットは、メモリ素子の第1の部分に格納され、ボディ部分のアクチュエータデータビットは、メモリ素子の第3の部分に格納され、そのため、構成機能の第1のグループ36-1に対応するメモリ素子の第1の部分52-1、構成機能の第2のグループ36-2に対応するメモリ素子の第2の部分52-2及び流体付勢デバイスのアレイ34に対応するメモリ素子の第3の部分54を有するメモリ素子のアレイ50ヘデータセグメント60が直列的にロードされる。

## [0047]

10

20

30

本明細書において、特定の例が図示および説明されたが、様々な代替および/または等価な具現化形態が、本開示の範囲から逸脱せずに、図示および説明された特定の例と置き換えられ得る。本明細書は、本明細書で説明された特定の例の任意の改作物または変化形態を網羅することが意図されている。従って、本開示は、特許請求の範囲およびその等価物によってのみ制限されることが意図されている。

## 【図面】

## 【図1】

【図2】

20

10

## 【図3】

3 ]

30

40

## フロントページの続き

(72)発明者 リン,スコット,エイ

アメリカ合衆国オレゴン州 9 7 3 3 0 - 4 2 4 1 , コーバリス , ノースイースト・サークル・ブールバード・1 0 7 0

(72)発明者 ガードナー,ジェイムズ,マイケル

アメリカ合衆国オレゴン州 9 7 3 3 0 - 4 2 4 1 , コーバリス , ノースイースト・サークル・ブールバード・1 0 7 0

(72)発明者 カンビー,マイケル,ダブリュー

アメリカ合衆国オレゴン州 9 7 3 3 0 - 4 2 4 1 , コーバリス , ノースイースト・サークル・ブールバード・1 0 7 0

審査官 大浜 登世子

(56)参考文献 国際公開第2001/010647(WO,A1)

米国特許出願公開第2004/0104973 (US,A1)

(58)調査した分野 (Int.Cl., DB名)

B41J 2/01 - 2/215