#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5537078号 (P5537078)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

| (51) Int.Cl. |               | F I            |                    |              |          |        |

|--------------|---------------|----------------|--------------------|--------------|----------|--------|

| HO1L 21/82   | (2006.01)     | HO1L           | 21/82              | D            |          |        |

| HO1L 21/8234 | 4 (2006.01)   | HO1L           | 27/08 1            | O 2 B        |          |        |

| HO1L 27/088  | (2006.01)     | HO1L           | 27/04              | A            |          |        |

| HO1L 21/822  | (2006.01)     | HO1L           | 21/76              | S            |          |        |

| HO1L 27/04   | (2006.01)     |                |                    |              |          |        |

|              |               |                |                    | 請求項の数 9      | (全 12 頁) | 最終頁に続く |

| (21) 出願番号    | 特願2009-172516 | (P2009-172516) | (73) 特許権者          | \$ 302062931 |          |        |

| (22) 出願日     | 平成21年7月23日    | (2009. 7. 23)  |                    | ルネサスエレク      | トロニクス株   | 式会社    |

| (65) 公開番号    | 特開2011-29345( | P2011-29345A)  |                    | 神奈川県川崎市中     | 中原区下沼部   | 1753番地 |

| (43) 公開日     | 平成23年2月10日    | (2011. 2. 10)  | (74) 代理人           | 100102864    |          |        |

| 審査請求日        | 平成24年2月16日    | (2012. 2. 16)  |                    | 弁理士 工藤 男     | 実        |        |

|              |               |                | (72) 発明者           | 山口 俊英        |          |        |

| 神务           |               | 神奈川県川崎市中       | 奈川県川崎市中原区下沼部1753番地 |              |          |        |

|              |               |                | NECエレクト            | トロニクス株       | 式会社内     |        |

|              |               |                |                    |              |          |        |

|              |               |                | 審査官                | 須原 宏光        |          |        |

|              |               |                |                    |              |          |        |

最終頁に続く

# (54) 【発明の名称】半導体装置

### (57)【特許請求の範囲】

# 【請求項1】

半導体基板の主面に設けられた素子分離領域と、

前記主面に設けられ、前記素子分離領域によって囲まれる素子形成領域と、

## を具備し、

前記主面内において、第1方向と、前記第1方向に直交する第2方向とが定義され、前記素子形成領域の外周形状は、前記第1方向に沿って延びる第1辺を有しており、前記素子形成領域は、

第1トランジスタ領域と、

前記第2方向において前記第1辺と前記第1トランジスタ領域との間にあたる位置に配置された第2トランジスタ領域と、

前記第1方向における前記第2トランジスタ領域の側方に配置されたダミー領域と を備え、

前記第1トランジスタ領域は、前記第1辺に対向するように伸びる第1チャネル形成領域を有し、

前記第2トランジスタ領域は、前記第1辺に対向するように伸びる第2チャネル形成領域を有し、

前記第1チャネル形成領域は、前記第2チャネル形成領域と非対向である非対向領域を有し、

前記ダミー領域は、前記第2方向において前記非対向領域と対向するような位置に配置

されており、

前記第1チャネル形成領域の前記非対向領域と前記素子分離領域との間の前記第2方向 における距離と、前記第1チャネル形成領域の前記第2チャネル形成領域と対向する対向 領域と前記素子分離領域との間の前記第2方向における距離は等しい

半導体装置。

#### 【請求項2】

請求項1に記載された半導体装置であって、

前記素子形成領域は、前記第2トランジスタ領域と前記ダミー領域とを分離する分離領 域を含んでおり、

前記分離領域は絶縁性材料により形成されている

半導体装置。

#### 【請求項3】

請求項2に記載された半導体装置であって、

前記素子分離領域は、絶縁性の第1材料により形成され、

前記第1トランジスタ領域、第2トランジスタ領域および前記ダミー領域は、半導体材 料である第2材料により形成され、

前記第1トランジスタ領域と前記第2トランジスタ領域とが前記第2方向において隣接 している場合に、前記第1トランジスタ領域と前記第2トランジスタ領域との間では前記 第2材料が連続している

半導体装置。

【請求項4】

請求項3に記載された半導体装置であって、

前記第1トランジスタ領域と前記ダミー領域とが前記第2方向において隣接している場 合に、前記第1トランジスタ領域と前記ダミー領域との間では、前記第2材料が連続して いる

半導体装置。

#### 【請求項5】

請求項1乃至4のいずれか一項に記載された半導体装置であって、

前記ダミー領域には、前記第1方向に沿って伸び、前記ダミー領域を2つのダミー拡散 領域に分割する第1ダミーゲート形成領域が形成され、前記第1ダミーゲート形成領域上 に第1ダミーゲートが形成される

半導体装置。

#### 【請求項6】

請求項5に記載された半導体装置であって、

前記第1ダミーゲートには、前記2つのダミー拡散領域が電気的に遮断されるような電 圧が供給される

半導体装置。

#### 【請求項7】

請求項5に記載された半導体装置であって、

前記第1トランジスタ領域は、前記第1チャネル形成領域により2つの第1拡散領域に 40 分割されており、

前記第2トランジスタ領域は、前記第2チャネル形成領域により2つの第2拡散領域に 分割されており、

前記2つの第1拡散領域のうちの一方は、前記2つのダミー拡散領域のうちの一方と隣 接しており、

前記素子形成領域には、前記一方の第1拡散領域と前記一方のダミー拡散領域との間を 分割するように、第2ダミーゲート形成領域が設けられ、前記第2ダミーゲート形成領域 上に第2ダミーゲートが形成される

半導体装置。

### 【請求項8】

10

20

30

請求項7に記載された半導体装置であって、

前記一方の第1拡散領域と、前記2つの第2拡散領域のうちの一方と隣接しており、

前記第2ダミーゲート形成領域は、前記一方の第1拡散領域と前記一方の第2拡散領域とを分割するように伸びており、

前記第2ダミーゲート形成領域により、前記一方の第1拡散領域と前記一方の第2拡散 領域とが電気的に遮断される

半導体装置。

### 【請求項9】

請求項7に記載された半導体装置であって、

前記第2ダミーゲートには、前記一方の第1拡散領域と前記一方のダミー拡散領域とが電気的に遮断されるような電圧が供給される

半導体装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、半導体装置に関する。

【背景技術】

[0002]

半導体装置は、半導体基板と、半導体基板の主面に形成されるトランジスタとを含んでいる。半導体基板の主面には、素子形成領域及び素子分離領域が設けられる。素子形成領域は、トランジスタなどの素子が形成される領域である。素子形成領域は、半導体材料(例えばシリコン膜など)により、形成される。一方、素子分離領域は、素子形成領域を他の領域から電気的に分離するための領域である。素子分離領域は、絶縁性材料(例えば、酸化シリコン膜など)により形成される。素子形成領域は、素子分離領域によって囲まれる。

[0003]

素子形成領域には、トランジスタが形成されるトランジスタ形成領域が設けられる。トランジスタ形成領域は、拡散領域(ソース及びドレイン領域)、及びチャネル形成領域を含んでいる。

[0004]

素子形成領域と素子分離領域とは、通常、別の材料により形成される。この場合、熱膨 張率の違いなどから、チャネル形成領域が素子分離領域からストレス(応力)を受けるこ とがある。チャネル形成領域が受けるストレスは、チャネル形成領域におけるキャリア( 電子又は正孔)の移動度に影響を与える。

[0005]

関連技術として、特許文献1(特開2007-311491号公報)に記載された半導体集積回路が挙げられる。この半導体集積回路は、NチャネルトランジスタとPチャネルトランジスタを用いたCMOS回路を搭載した半導体集積回路である。この半導体集積回路は、NチャネルトランジスタとPチャネルトランジスタのいずれか一方がゲートアイソレーション構造、他方がシャロートレンチアイソレーション構造により素子分離されていることを特徴とする。この半導体集積回路によれば、一方のトランジスタはSTIストレスを受けず、他方のトランジスタはSTIストレスによってトランジスタ性能が変化する。これにより、Pチャネルトランジスタ及びNチャネルトランジスタの性能を効率的に向上させることができる。

[0006]

チャネル形成領域が素子分離領域から受けるストレスは、チャネル形成領域と素子分離領域との間の距離に関係している。従って、チャネル形成領域におけるキャリアの移動度は、チャネル形成領域と素子分離領域との間の距離に依存する。関連して、特許文献2(特開2007-272号公報)には、ドレイン電流Idrが、チャネル領域からSTI領域までの距離Gate-STI(X)に依存することが記載されている。

10

20

30

40

#### 【先行技術文献】

【特許文献】

[0007]

【特許文献1】特開2007-311491号公報

【特許文献2】特開2007-272号公報

【発明の概要】

【発明が解決しようとする課題】

[0008]

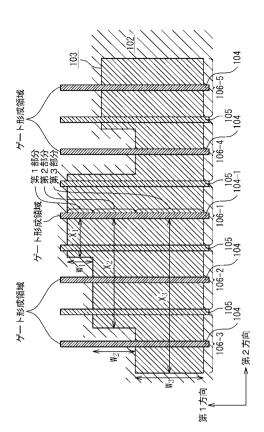

ところで、素子形成領域には、複数のトランジスタ形成領域が設けられることがある。 加えて、複数のトランジスタ形成領域間において、チャネル幅が異なっていることがある 。図1は、そのような素子形成領域のレイアウトの一例を示す図である。

[0009]

図1には、半導体基板の主面内における方向として、第1方向及び第2方向が定義されている。第1方向と第2方向とは直交している。素子形成領域103は、素子分離領域102に囲まれている。素子形成領域103内には、複数(図1では5個)のトランジスタ形成領域106(106・1~106・5)が、第2方向に沿って並んでいる。隣接する2つのトランジスタ形成領域106の間には、ダミーゲート形成領域105が設けられている。ダミーゲート形成領域105が不活性になるような電圧が印加される。ダミーゲート形成領域105では、隣接する2つのトランジスタ形成領域106間が、電気的に分離されている。

[0010]

半導体基板には、複数のトランジスタ形成領域106に対応して、複数のゲート形成領域が設けられている。各ゲート形成領域は、基板上にゲート電極が形成される領域である。ゲート形成領域は、第1方向に沿って伸びている。各トランジスタ形成領域106では、ゲート形成領域に対応する位置に、チャネルが形成される。各トランジスタ形成領域106においてチャネルが形成される領域が、以下、チャネル形成領域104として示される。

[0011]

ここで、複数のトランジスタ形成領域106間では、第1方向に沿う幅が、異なっている。その結果、複数のトランジスタ形成領域106間では、チャネル形成領域104の幅(チャネル幅)が異なっている。

[0012]

上述のようなレイアウトが採用された場合、1つのチャネル形成領域104において、素子分離領域102との間の第2方向に沿う距離が、チャネル幅方向(第1方向)における位置により異なってしまう。一例として、トランジスタ形成領域106-1に含まれるチャネル形成領域104-1は、素子分離領域102との間の距離がX1である第1部分、その距離がX2である第2部分、及びその距離がX3である第3部分に分けられる。チャネル形成領域104-1が素子分離領域102から受けるストレスは、第1部分乃至第3部分の間で異なっている。

[0013]

図1に示されるように、第1部分の第1方向に沿う長さが、W1と定義される。第2部分の第1方向に沿う長さが、W2と定義される。第3部分の第1方向に沿う長さが、W3と定義される。「BSIM4.4.0 MOSFET MODEL - User's Manual"中のChapter.13」を参考にすれば、トランジスタ形成領域106-1に設けられるトランジスタのドレイン電流は、次の式1に示される移動度係数に依存する。

[0014]

20

10

30

20

30

40

50

$$\frac{W1}{W1+W2+W3} \times \frac{1}{X1} + \frac{W2}{W1+W2+W3} \times \frac{1}{X2} + \frac{W3}{W1+W2+W3} \times \frac{1}{X3} \quad \cdots (1)$$

(5)

#### [0015]

尚、上式1では、トランジスタ形成領域106-1が第2方向における一方の側から受けるストレスだけが考慮されている。

#### [0016]

チャネル形成領域が受けるストレスがチャネル幅方向において不均一である場合、トラ 10 ンジスタの特性が劣化してしまう、という問題点があった。

【課題を解決するための手段】

#### [0017]

本発明に係る半導体装置は、半導体基板の主面に設けられた素子分離領域と、前記主面に設けられ、前記素子分離領域によって囲まれる、素子形成領域とを具備する。前記素子形成領域の外周形状は、前記第1方向に直交する第2方向とが定義される。前記素子形成領域の外周形状は、前記第1方向に沿って延びる第1辺を有している。前記素子形成領域は、第1トランジスタ領域と、前記第2方向において前記第1辺と前記第1トランジスタ領域と、前記第1方向において前記第2トランジスタ領域の側方にあたる位置に配置された、ダミー領域とを備える。前記第1トランジスタ領域は、前記第1辺に対向するように伸びる第1チャネル形成領域を有している。前記第1チャネル形成領域は、前記第2チャネル形成領域と対向領域を有している。前記ダミー領域は、前記第2方向において前記非対向領域と対向するような位置に配置されている。

### [0018]

このような構成によれば、ダミー領域を設けることにより、第1トランジスタ形成領域と素子分離領域との間の距離を、チャネル幅方向(第1方向)において揃えることができる。その結果、第1トランジスタ形成領域が素子分離領域から受けるストレスを、チャネル幅方向において均一化させることができる。ストレスが均一化されるため、第1トランジスタ形成領域に形成されるトランジスタの特性劣化が防止される。

【発明の効果】

### [0019]

本発明によれば、素子分離領域から受けるストレスの量がチャネル幅方向で異なっていても、トランジスタの特性が劣化しない、半導体装置が提供される。

【図面の簡単な説明】

[0020]

【図1】素子形成領域の一例を示すレイアウト図である。

【図2】第1の実施形態に係る半導体装置のパターンレイアウトを示す図である。

【図3】第2の実施形態に係る半導体装置のパターンレイアウトを示す図である。

【図4】第3の実施形態に係る半導体装置のパターンレイアウトを示す図である。

【発明を実施するための形態】

[0021]

以下に、図面を参照しつつ、本発明の実施形態について説明する。

[0022]

(第1の実施形態)

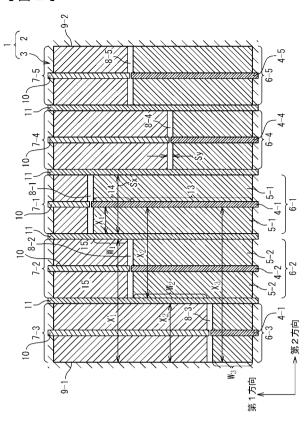

図 2 は、本実施形態に係る半導体装置のパターンレイアウトを示す図である。図 2 に示されるパターンは、半導体基板の主面に設けられるパターンである。

[0023]

図2に示されるように、半導体基板の主面において、第1方向(ゲート幅方向)と第2

方向(ゲート長方向)とが定義されている。第1方向と第2方向とは、直交している。半 導体装置1は、半導体基板の主面に設けられた、素子形成領域3及び素子分離領域2を備 えている。

# [0024]

素子形成領域3は、トランジスタなどの素子が形成される領域である。素子形成領域3 は、矩形状である。素子形成領域3の外周形状の2辺(9-1及び9-2)は、第1方向 に沿って伸びている。

### [0025]

素子分離領域2は、素子形成領域3を他の領域から分離するために設けられている。素子分離領域3では、半導体基板の主面に、酸化シリコン膜などの絶縁性材料が埋め込まれている。

[0026]

以下に、素子形成領域3について詳述する。

### [0027]

素子形成領域3には、複数のトランジスタ領域6(6-1~6-5)、ダミー領域7(7-1~7-5;ダミートランジスタ領域)、分離領域8(8-1~8-5)、第1ダミーゲート形成領域10、及び第2ダミーゲート形成領域11が設けられている。素子形成領域3のうち、分離領域8以外の領域は、半導体材料(例えばシリコン膜)により形成されている。分離領域8は、素子分離領域2と同一の材料(例えば酸化シリコン膜)により形成されている。

#### [0028]

複数のトランジスタ領域6の各々は、トランジスタが形成される領域である。複数のトランジスタ領域6は、第2方向に沿って並んでいる。各トランジスタ領域6は、2つの拡散領域5、及びチャネル形成領域4(4-1~4-5)を備えている。チャネル形成領域4は、第1方向に沿って伸びている。チャネル形成領域4は、辺9-1及び辺9-2に対向している。各トランジスタ領域6内において、2つの拡散領域5は、チャネル形成領域4によって分けられている。チャネル形成領域4では、半導体基板の主面上に、ゲート電極が形成される。

### [0029]

本実施形態に係る半導体装置では、複数のトランジスタ領域6の間において、第1方向におけるチャネル形成領域4の長さが異なっている。隣接する2つのトランジスタ領域6の間では、トランジスタ領域に含まれる拡散領域のゲート長方向における一方の端部(拡散層端)が、揃っている。すなわち、複数のトランジスタ領域6間では、チャネル幅が異なっている。その結果、複数のトランジスタ6のうちのいずれかは、他のトランジスタ領域6と第2方向において非対向である部分(非対向領域)を有している。一例として、トランジスタ領域6・1に着目する。トランジスタ領域6・1に含まれるチャネル形成領域4・1は、トランジスタ領域6・2に含まれるチャネル形成領域4・2よりも長い。そのため、チャネル形成領域4・1は、チャネル形成領域4・2に対向する領域(対向領域13)と、チャネル形成領域4・2に対向しない領域(非対向領域14)とを有している。

[ 0 0 3 0 ]

ダミー領域7(7・1~7・5)は、チャネル形成領域4と素子分離領域2との間の距離を調節するために、配置されている。ダミー領域7は、各トランジスタ領域6と同じ材料(例えばシリコン膜)により形成されている。

# [0031]

ダミー領域7は、各トランジスタ領域6の第1方向における側方に配置されている。また、ダミー領域7の少なくとも一部は、チャネル形成領域に含まれる非対向領域と第2方向で対向するような位置に、配置されている。この点について具体的に説明するため、トランジスタ領域6・2の第1方向における側方に配置されたダミー領域7・2について着目する。仮に、トランジスタ領域6・1が、第1トランジスタ領域6・1として定義される。辺9・1が、第1辺9・1として定義される。第1トランジスタ領域6・1と第1辺

20

10

30

40

9 - 1 との間に配置されたトランジスタ領域 6 が、第 2 トランジスタ領域として定義される。第 1 トランジスタ領域 6 - 1 と第 1 辺 9 - 1 との間には、トランジスタ領域 6 - 2 及びトランジスタ6 - 3 が配置されている。そこで、仮に、トランジスタ領域 6 - 2 が第 2 トランジスタ領域 6 - 2 として定義される。第 2 トランジスタ領域 6 - 2 の第 1 方向における側方には、ダミー領域 7 - 2 の少なくとも一部は、第 1 トランジスタ領域 6 - 1 における非対向領域 1 4 と、第 2 方向において対向している。

### [0032]

トランジスタ領域 6 - 3 が第 2 トランジスタ領域として定義された場合も、同様である。すなわち、トランジスタ領域 6 - 3 (第 2 トランジスタ領域)の第 1 方向における側方には、ダミー領域 7 - 3 が配置されている。ダミー領域 7 - 3 の少なくとも一部は、第 1 トランジスタ領域 6 - 3 と非対向である領域と、対向している。

# [0033]

上述の第1トランジスタ領域、第2トランジスタ領域、及びダミー領域7の関係は、トランジスタ領域6-1とは別のトランジスタ領域を第1トランジスタ領域として定義した場合にも、同様に成り立つ。また、辺9-1ではなく辺9-2を第1辺として考えた場合にも、同様に成り立つ。

#### [0034]

言い換えれば、ダミー領域7は、素子形成領域3が、辺9-1と辺9-2との間に形成される矩形状の領域を含んだ形状となるように、配置されている。

#### [0035]

第1ダミーゲート形成領域10は、ダミー領域7を不活性にするために設けられている。第1ダミーゲート形成領域10は、第1方向に沿って伸びている。第1ダミーゲート形成領域10は、チャネル形成領域4の延長上に設けられている。第1ダミーゲート形成領域10は、ダミー領域7を、2つのダミー拡散領域15に分割している。第1ダミーゲート形成領域10上には、第1ダミーゲートが形成される。第1ダミーゲートには、第1ダミーゲート形成領域10が不活性になるような電圧が印加される。例えば、ダミー領域7にNチャネル型トランジスタが形成される場合には、第1ダミーゲート及び2つのダミー拡散領域15は、それぞれ接地電位が供給されるように構成される。

#### [0036]

第2ダミーゲート形成領域11は、第1方向に沿って伸びており、隣接するトランジスタ領域6間を分離している。第2ダミーゲート形成領域11は、第2ダミーゲートが形成される領域である。第2ダミーゲートには、第2ダミーゲート形成領域11が不活性になるように、電源電圧又は接地電圧が印加される。これにより、主面において、隣接するトランジスタ領域6間は、電気的に分離されている。また、第2ダミーゲート形成領域11は、第2方向において、ダミー領域7と各トランジスタ領域6との間を分離している。

### [0037]

分離領域8は、ダミー領域7と各トランジスタ領域6とを第1方向において分離する領域である。分離領域8は、第2方向に沿って伸びている。分離領域8は絶縁性であり、素子分離領域2と同じ材料により形成される。分離領域8の幅(第1方向に沿う幅)は、一定である。

### [0038]

次いで、本実施形態に係る半導体装置1の作用について説明する。本実施形態に係る半導体装置によれば、ダミー領域7が設けられているため、チャネル形成領域4と素子分離領域2との間の距離を、チャネル幅方向において均一にすることができる。その結果、チャネル形成領域4が受けるストレスが、分離領域8に対応する位置を除き、均一化される。これにより、各トランジスタ領域6に形成されるトランジスタの特性劣化が抑制される

[0039]

50

40

30

10

20

30

40

50

尚、トランジスタ領域 6 - 1 に着目すると、チャネル形成領域 4 - 1 におけるキャリアの移動度係数は、以下の式 2 によって示される。但し、下記式 2 では、チャネル形成領域 4 - 1 が辺 9 - 1 側から受けるストレスだけが考慮されている。

[0040]

【数2】

$$\frac{W1}{W1+W2+W3} \times \frac{1}{X1} + \frac{W2}{W1+W2+W3} \times \frac{1}{X2} + \frac{W3}{W1+W2+W3} \times \frac{1}{X3} + \frac{W1-Sy}{W1+W2+W3} \times \frac{1}{X1'} + \frac{W2-Sy}{W1+W2+W3} \times \frac{1}{X2'} \qquad \cdots (2) \qquad ^{10}$$

# [0041]

数式 2 中、W 1 は、分離領域 8 - 1 と分離領域 8 - 2 との間の第 1 方向における距離を示す。W 2 は、分離領域 8 - 2 と分離領域 8 - 3 との間の第 1 方向における距離を示す。W 3 は、チャネル形成領域 4 - 3 の第 1 方向における長さを示す。X 1 は、チャネル形成領域 4 - 1 と、トランジスタ形成領域 6 - 1 及びトランジスタ形成領域 6 - 2 の間に設けられた第 2 ダミーゲート形成領域 1 1 との間の距離を示す。X 2 は、チャネル形成領域 4 - 1 と、トランジスタ形成領域 6 - 2 及びトランジスタ形成領域 6 - 3 の間に設けられた第 2 ダミーゲート形成領域 1 1 との間の距離を示す。X 3 は、チャネル形成領域 4 - 1 と辺 9 - 1 との間の距離を示す。X 1 ' は、トランジスタ形成領域 6 - 1 及びトランジスタ形成領域 6 - 2 及びトランジスタ形成領域 6 - 3 の間に設けられた第 2 ダミーゲート形成領域 1 1 と、辺 9 - 1 との間の距離を示す。S x は、分離領域 8 の第 2 方向に沿う長さを示す。S y は、分離領域 8 の第 1 方向における幅を示す。

### [0042]

数式 2 より、本実施形態に係る半導体装置では、チャネル形成領域 4 - 1 における移動 度係数が、チャネル形成領域 4 - 1 と辺 9 - 1 との間の距離が一定である場合の移動度係 数に近いことがわかる。すなわち、トランジスタの特性劣化が抑制されることがわかる。 【 0 0 4 3 】

尚、本実施形態では、第1ダミーゲートが、チャネル形成領域4上に形成されるゲート電極とは分離されている場合について説明した。但し、第1ダミーゲートは、必ずしもゲート電極から分離されている必要はなく、ゲート電極と連続していてもよい。特に、本実施形態では、第2ダミーゲートによりダミー拡散領域が分離されているため、第1ダミーゲートとゲート電極とが連続していても問題はない。但し、第1ダミーゲートとゲート電極とが分離されていれば、ゲート電極と第1ダミーゲートとを異なる電位で制御することができ、第1ダミーゲート形成領域による電気的分離をより確実にすることができる。また、ゲート電極におけるゲート容量に第1ダミーゲートのゲート容量が付加されない。これら観点から、第1ダミーゲートとゲート電極とは、分離されていることが好ましい。

#### [0044]

また、本実施形態では、複数のトランジスタ領域6間で、チャネル幅が異なっている場合について説明した。但し、複数のトランジスタ領域6間においてチャネル幅が同じであったとしても、チャネル形成領域4の位置がずれていれば、非対向領域14が形成される。このような場合であっても、ダミー領域7を設けることにより、チャネル形成領域4が受けるストレスを均一化させることが可能である。

### [0045]

以上説明したように、本実施形態によれば、ダミー領域 7 が設けられている。これにより、隣接するトランジスタ領域 6 間でチャネル幅が異なっているのにもかかわらず、チャネル形成領域 4 が素子分離領域 2 から受けるストレスのばらつきを低減することができる

。その結果、トランジスタの特性劣化を抑制することができる。

#### [0046]

(第2の実施形態)

次いで、第2の実施形態について説明する。

#### [0047]

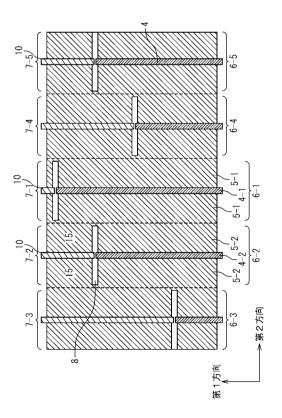

図3は、本実施形態に係る半導体装置のパターンレイアウトを示す図である。本実施形態では、第2ダミーゲート形成領域11が形成されていない。その他の点については、第1の実施形態と同様とすることができるので、詳細な説明は省略する。

#### [0048]

本実施形態では、隣接する各トランジスタ領域6間において、拡散領域5同士が区切られていない。すなわち、隣接する2つのトランジスタ領域6間では、拡散領域5同士が同電位となるように接続されている。尚、図3では、説明の便宜上、隣接するトランジスタ領域6間に、点線が描かれている。しかし実際には、隣接するトランジスタ領域6間において、拡散領域5同士を区別する構成は存在しない。

#### [0049]

第2ダミーゲート形成領域11が設けられていないため、トランジスタ領域6-1の拡散領域5-1は、ダミー領域7(7-1~7-5)に含まれる拡散領域15と、電気的に接続されている。但し、ダミー領域7には第1ダミーゲート形成領域10が設けられている。従って、トランジスタ領域6-1に含まれる2つの拡散領域5-1同士が、ダミー領域7を介してショートすることはない。

#### [0050]

本実施形態に示される構成を採用しても、第1の実施形態と同様に、チャネル形成領域4が受けるストレスのばらつきを無くすことができ、トランジスタの特性劣化を抑制できる。

### [0051]

また、隣接する2つのトランジスタ領域6の拡散領域5同士を電気的に接続するために、金属配線を使用することが考えられる。しかし、この場合には、金属配線の寄生抵抗及び容量が、各トランジスタの動作特性に影響を与えることがある。これに対し、本実施形態では、隣接する2つのトランジスタ領域6間において拡散領域5同士が連続している。従って、隣接するトランジスタ領域6間に生じる寄生抵抗及び容量を、低減できる。

#### [0052]

尚、本実施形態においても、第1の実施形態と同様に、第1ダミーゲートとチャネル形成領域上に形成されるゲート電極とは、分離されていても連続していてもよい。

### [0053]

(第3の実施形態)

次いで、第3の実施形態について説明する。

# [0054]

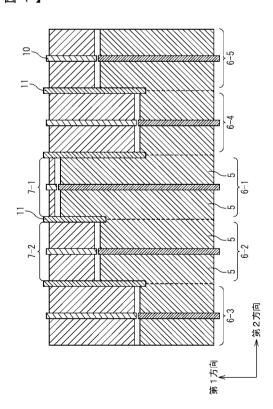

図4は、本実施形態に係る半導体装置のパターンレイアウトを示す図である。本実施形態では、第1の実施形態に対して、第2ダミーゲート形成領域11が変更されている。その他の点については、第1の実施形態と同様とすることができるので、詳細な説明は省略する。

#### [0055]

図4に示されるように、第2ダミーゲート形成領域11は、ダミー領域7と各トランジスタ形成領域6とを第2方向において分割するように延びている。但し、隣接する2つのトランジスタ形成領域6間には、第2ダミーゲート形成領域11が設けられていない。従って、隣接する2つのトランジスタ形成領域6間では、拡散領域5同士が同電位となるように、接続されている。すなわち、第2の実施形態と同様に、隣接する2つのトランジスタ領域6間では、拡散領域5同士が同電位となるように、連続している。

#### [0056]

本実施形態に示される構成を採用しても、既述の実施形態と同様に、チャネル形成領域

20

10

30

40

4 が受けるストレスのばらつきを無くすことができ、トランジスタの特性劣化を抑制できる。

### [0057]

また、本実施形態では、各トランジスタ形成領域6とダミー領域7との間が、第2ダミーゲート形成領域11によって区切られている。ソース・ドレイン間(2つの拡散領域5間)に生じるリーク電流が、より確実に防止される。

#### [0058]

尚、本実施形態においても、第1の実施形態と同様に、第1ダミーゲートとチャネル形成領域上に形成されるゲート電極とは、分離されていても連続していてもよい。

### [0059]

以上、本発明について、第1~第3の実施形態を用いて説明した。但し、これらの実施 形態は互いに独立するものではなく、矛盾のない範囲内で組み合わせることも可能である

# 【符号の説明】

### [0060]

- 1 半導体装置

- 2 素子分離領域

- 3 素子形成領域

- 4 1 第 1 チャネル形成領域

- 4 2 第 2 チャネル形成領域

- 5 1 第 1 拡散領域

- 5 2 第 2 拡散領域

- 5 1 第1トランジスタ領域

- 6 2 第 2 トランジスタ領域

- 7 ダミー領域

- 8 分離領域

- 9-1、9-2 辺

- 1 0 第 1 ダミーゲート形成領域

- 1 1 第 2 ダミーゲート形成領域

- 13 対向領域

- 14 非対向領域

- 15 ダミー拡散領域

- 102 素子分離領域

- 103 素子形成領域

- 104 チャネル形成領域

- 105 ダミーゲート形成領域

- 106 トランジスタ形成領域

10

20

【図1】

【図2】

【図3】

【図4】

# フロントページの続き

(51)Int.CI. F I

H 0 1 L 21/76 (2006.01)

(56)参考文献 特開2002-026125(JP,A)

特開2007-311587(JP,A)

特開2006-253393(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 1 L 2 1 / 8 2

H01L 27/04