### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-232475 (P2010-232475A)

(43) 公開日 平成22年10月14日(2010.10.14)

| (51) Int.Cl. |         |           | F 1    |       |     | テーマコード (参考) |

|--------------|---------|-----------|--------|-------|-----|-------------|

| HO1L         | 21/8246 | (2006.01) | HO1L 2 | 27/10 | 447 | 4M119       |

| HO1L         | 27/105  | (2006.01) | HO1L 4 | 43/08 | Z   | 5FO92       |

| HO1L         | 43/08   | (2006.01) | G11C 1 | 11/15 | 110 |             |

| G 1 1 C      | 11/15   | (2006.01) | G11C 1 | 11/15 | 120 |             |

|           |                            | 審査請求               | 未請求              | 請求項 | で数 8          | OL | (全 20 頁) |  |

|-----------|----------------------------|--------------------|------------------|-----|---------------|----|----------|--|

| (21) 出願番号 | 特願2009-79229 (P2009-79229) | (71) 出願人           | 頂人 302062931     |     |               |    |          |  |

| (22) 出願日  | 平成21年3月27日 (2009.3.27)     |                    | ルネサスエレクトロニクス株式会社 |     |               |    |          |  |

|           | 神奈川県川崎市                    |                    |                  |     | 5中原区下沼部1753番地 |    |          |  |

|           |                            | (74) 代理人           | 10006474         | 46  |               |    |          |  |

|           |                            |                    | 弁理士              | 深見  | 久郎            |    |          |  |

|           |                            | (74) 代理人           | 10008513         | 32  |               |    |          |  |

|           |                            |                    | 弁理士              | 森田  | 俊雄            |    |          |  |

|           |                            | (74) 代理人 100083703 |                  |     |               |    |          |  |

|           |                            |                    | 弁理士              | 仲村  | 義平            |    |          |  |

|           |                            | (74) 代理人           | 100096781        |     |               |    |          |  |

|           |                            |                    | 弁理士              | 堀井  | 豊             |    |          |  |

|           |                            | (74) 代理人           | 10010916         | 62  |               |    |          |  |

|           |                            |                    | 弁理士              | 酒井  | 將行            |    |          |  |

|           |                            | (74) 代理人           | 100111246        |     |               |    |          |  |

|           |                            |                    | 弁理士              | 荒川  | 伸夫            |    |          |  |

|           |                            |                    |                  |     |               | 最  | 終頁に続く    |  |

(54) 【発明の名称】磁気記憶装置およびその製造方法

## (57)【要約】

【課題】磁気記憶素子の機能低下を抑制することのできる磁気記憶装置およびその製造方法を提供する。

【解決手段】磁気記憶装置は、磁化状態に基づいたデータを保持可能な磁気記憶素子MMと、発生する磁界により磁気記憶素子の磁化状態を変化させることが可能なディジット線DLおよびビット線BLとを備えている。磁気記憶素子MMは、ディジット線DLとビット線BLとの交差部分において、ディジット線DLの上であってビット線BLの下に配置されている。ディジット線DLはこの交差部分において幅WDLを有しており、かつビット線BLはこの交差部分において幅WBLを有している。幅WDLは磁気記憶素子MMの幅WMM1よりも大きく、かつ幅WBLは磁気記憶素子MMの幅WMM1よりも大き

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

磁化状態に基づいたデータを保持可能な磁気記憶素子と、

発生する磁界により前記磁化状態を変化させることが可能な第1および第2の導体とを備え、

前記磁気記憶素子は、第1の方向に延在する前記第1の導体と第2の方向に延在する前記第2の導体との交差部分において、前記第1の導体の上であって前記第2の導体の下に配置され、

前記第1の導体は前記交差部分において、平面的に見て前記第1の方向に対して垂直な方向に第1の幅を有し、かつ前記第2の導体は前記交差部分において、平面的に見て前記第2の方向に対して垂直な方向に第2の幅を有し、

前記磁気記憶素子は平面的に見て前記第1の方向に対して垂直な方向に第3の幅を有し、かつ平面的に見て前記第2の方向に対して垂直な方向に第4の幅を有し、

前記第1の幅は前記第3の幅よりも大きく、かつ前記第2の幅は前記第4の幅よりも小さい、磁気記憶装置。

#### 【請求項2】

磁化状態に基づいたデータを保持可能な磁気記憶素子と、

発生する磁界により前記磁化状態を変化させることが可能な第1および第2の導体とを 備え.

前記磁気記憶素子は、第1の方向に延在する前記第1の導体と第2の方向に延在する前記第2の導体との交差部分において、前記第1の導体の上であって前記第2の導体の下に配置され、

前記磁気記憶素子は、磁化の向きが固着された磁化固定層と磁化の向きが可変の磁化自由層との間に設けられた中間層を有し、

前記第1の導体の上面から前記中間層の下面までの距離は、前記中間層の上面から前記第2の導体の下面までの距離よりも小さい、磁気記憶装置。

#### 【請求項3】

前記第1の導体は前記交差部分において、平面的に見て前記第1の方向に対して垂直な方向に第1の幅を有し、かつ前記第2の導体は前記交差部分において、平面的に見て前記第2の方向に対して垂直な方向に第2の幅を有し、

前記磁気記憶素子は平面的に見て前記第1の方向に対して垂直な方向に第3の幅を有し、かつ平面的に見て前記第2の方向に対して垂直な方向に第4の幅を有し、

前記第1の幅は前記第3の幅よりも大きく、かつ前記第2の幅は前記第4の幅よりも小さい、請求項2に記載の磁気記憶装置。

## 【請求項4】

前記第1および前記第2の導体のうち少なくともいずれか一方は、導体本体と、前記導体本体に電流を流した際に前記電流から発生する磁界を前記磁気記憶素子に向かって増大させるためのクラッド層とを含む、請求項1~3のいずれかに記載の磁気記憶装置。

#### 【請求項5】

磁化状態に基づいたデータを保持可能な磁気記憶素子を形成する工程と、

発生する磁界により前記磁化状態を変化させることが可能な第1および第2の導体を形成する工程とを備え、

前記磁気記憶素子は、第1の方向に延在する前記第1の導体と第2の方向に延在する前記第2の導体との交差部分において、前記第1の導体の上であって前記第2の導体の下に配置され、

前記第1の導体は前記交差部分において、平面的に見て前記第1の方向に対して垂直な方向に第1の幅を有し、かつ前記第2の導体は前記交差部分において、平面的に見て前記第2の方向に対して垂直な方向に第2の幅を有し、

前記磁気記憶素子は平面的に見て前記第1の方向に対して垂直な方向に第3の幅を有し、かつ平面的に見て前記第2の方向に対して垂直な方向に第4の幅を有し、

10

20

30

40

前記第1の幅は前記第3の幅よりも大きく、かつ前記第2の幅は前記第4の幅よりも小さい、磁気記憶装置の製造方法。

#### 【請求項6】

磁化状態に基づいたデータを保持可能な磁気記憶素子を形成する工程と、

発生する磁界により前記磁化状態を変化させることが可能な第1および第2の導体を形成する工程とを備え、

前記磁気記憶素子は、第1の方向に延在する前記第1の導体と第2の方向に延在する前記第2の導体との交差部分において、前記第1の導体の上であって前記第2の導体の下に配置され、

前記磁気記憶素子を形成する工程は、磁化の向きが固定された固定層と磁化の向きが可変の磁化自由層との間に中間層を設ける工程を含み、

前記第1の導体の上面から前記中間層の下面までの距離は、前記中間層の上面から前記第2の導体の下面までの距離よりも小さい、磁気記憶装置の製造方法。

## 【請求項7】

前記第1の導体は前記交差部分において、平面的に見て前記第1の方向に対して垂直な方向に第1の幅を有し、かつ前記第2の導体は前記交差部分において、平面的に見て前記第2の方向に対して垂直な方向に第2の幅を有し、

前記磁気記憶素子は平面的に見て前記第1の方向に対して垂直な方向に第3の幅を有し、かつ平面的に見て前記第2の方向に対して垂直な方向に第4の幅を有し、

前記第1の幅は前記第3の幅よりも大きく、かつ前記第2の幅は前記第4の幅よりも小さい、請求項6に記載の磁気記憶装置の製造方法。

#### 【請求項8】

前記第1の導体を形成する工程または前記第2の導体を形成する工程は、導体本体を形成する工程と、前記導体本体に電流を流した際に前記導体本体から発生する磁界を前記磁気記憶素子に向かって増大させるためのクラッド層を形成する工程とを含む、請求項5~7のいずれかに記載の磁気記憶装置の製造方法。

【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は半導体記憶装置に関し、より特定的には、MRAM (Magnetoresistive Rand om Access Memory)を含む磁気記憶装置およびその製造方法に関する。

#### 【背景技術】

## [0002]

MRAMは、磁気によって情報を記憶するデバイスであり、高速動作、書換え耐性、不揮発性などの点で、他のメモリ技術と比較し優れた特長を有している。代表的なMRAMは、書き込み導体であるビット線およびワード線と、磁気抵抗効果素子のメモリセルとを含んでいる。

## [0003]

従来のMRAMにおける書き込み導体のレイアウト構造は、たとえば特開2002-118239号公報(特許文献1)に開示されている。特許文献1の書き込み導体のレイアウト構造は、第1の幅を有する第1の導体と、第2の幅を有する第2の導体と、データ記憶層とを含んでいる。第1の導体と第2の導体とは互いに直交しており、データ記憶層は第1の導体および第2の導体の交点において、第1の導体上であって第2の導体の下に配置されている。データ記憶層は第1の層幅と第2の層幅とを有している。第1の導体の第1の幅はデータ記憶層の第1の層幅よりも小さくなっており、第2の導体の第2の幅はデータ記憶層の第2の層幅よりも小さくなっており、第2の導体の第2の幅はデータ記憶層の第2の層幅よりも小さくなっている。データ記憶層に書き込みを行なう際には、第1の導体および第2の導体に電流を流し、それにより生成される磁界によってデータ記憶層の磁化方向を変化させる。

## 【先行技術文献】

#### 【特許文献】

20

10

40

30

20

30

40

50

[0004]

【特許文献1】特開2002-118239号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

従来のMRAMにおいては、磁気記憶素子の機能が低いという問題があった。たとえば特許文献1の構造においては、第1の導体の形状に起因して第1の導体の上層に凹凸が形成され、この凹凸が磁気記憶素子(データ記憶層)の平坦性に悪影響を及ぼし、磁気記憶素子の機能が低下していた。また、第2の導体の形成前に磁気記憶素子の上層を平坦化する際に、磁気記憶素子まで削られることがあり、磁気記憶素子の機能が低下していた。

[0006]

従って、本発明の目的は、磁気記憶素子の機能低下を抑制することのできる磁気記憶装置およびその製造方法を提供することである。

【課題を解決するための手段】

[0007]

本発明の一実施例における磁気記憶装置は、磁化状態に基づいたデータを保持可能な磁気記憶素子と、発生する磁界により磁化状態を変化させることが可能な第1および第2の導体とを備えている。磁気記憶素子は、第1の方向に延在する第1の導体と第2の方向に延在する第2の導体との交差部分において、第1の導体の上であって第2の導体の下に配置されている。第1の導体は交差部分において、平面的に見て第1の方向に対して垂直な方向に第1の幅を有しており、かつ第2の導体は交差部分において、平面的に見て第2の方向に対して垂直な方向に第2の幅を有しており、かつ平面的に見て第2の方向に対して垂直な方向に第3の幅を有しており、かつ平面的に見て第2の方向に対して垂直な方向に第3の幅を有しており、かつ平面的に見て第2の方向に対して垂直な方向に第4の幅を有している。第1の幅は第3の幅よりも大きく、かつ第2の幅は第4の幅よりも小さい。

[0008]

また、本発明の他の実施例における磁気記憶装置は、磁化状態に基づいたデータを保持可能な磁気記憶素子と、発生する磁界により磁化状態を変化させることが可能な第1および第2の導体とを備えている。磁気記憶素子は、第1の方向に延在する第1の導体と第2の方向に延在する第2の導体との交差部分において、第1の導体の上であって第2の導体の下に配置されている。磁気記憶素子は、磁化の向きが固着された磁化固定層と磁化の向きが可変の磁化自由層との間に設けられた中間層を有している。第1の導体の上面から中間層の下面までの距離は、中間層の上面から第2の導体の下面までの距離よりも小さい。

[0009]

本発明の一実施例における磁気記憶装置の製造方法は、以下の工程を備えている。磁化状態に基づいたデータを保持可能な磁気記憶素子を形成する。発生する磁界により磁化状態を変化させることが可能な第1および第2の導体を形成する。磁気記憶素子は、第1の方向に延在する第1の導体との交差部分において、第1の導体の上であって第2の導体の下に配置される。第1の導体は交差部分において、平面的に見て第1の方向に対して垂直な方向に第1の幅を有しており、かつ第2の導体は交差部分において、平面的に見て第2の方向に対して垂直な方向に第2の幅を有しており、かつ平面的に見て第2の方向に対して垂直な方向に第3の幅を有しており、かつ平面的に見て第2の方向に対して垂直な方向に第3の幅を有している。第1の幅は第3の幅よりも大きく、かつ第2の幅は第4の幅よりも小さい。

[0010]

本発明の他の実施例における磁気記憶装置の製造方法は、以下の工程を備えている。磁化状態に基づいたデータを保持可能な磁気記憶素子を形成する。発生する磁界により磁化状態を変化させることが可能な第1および第2の導体を形成する。磁気記憶素子は、第1の方向に延在する第1の導体と第2の存体の下に配置される。磁気記憶素子を形成する工程は、

20

30

40

50

磁化の向きが固定された固定層と磁化の向きが可変の磁化自由層との間に中間層を設ける 工程を含んでいる。第1の導体の上面から中間層の下面までの距離は、中間層の上面から 第2の導体の下面までの距離よりも小さい。

## 【発明の効果】

[0011]

本発明の一実施例および他の実施例における磁気記憶装置およびその製造方法によれば、磁気記憶素子の機能低下を抑制することができる。

【図面の簡単な説明】

[0012]

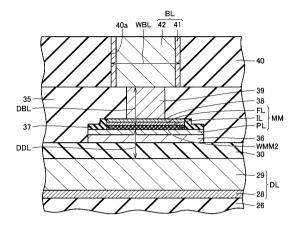

- 【図1】本発明の一実施の形態における磁気記憶装置のレイアウト構成を示す概略平面図である。

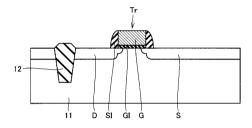

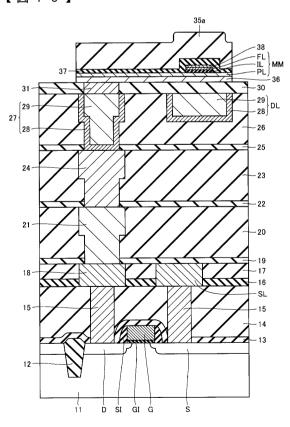

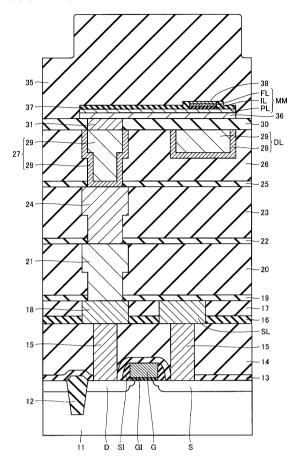

- 【図2】本発明の一実施の形態における磁気記憶装置のメモリセルの構成を示す概略断面図であり、図1のII-II線に沿った断面図である。

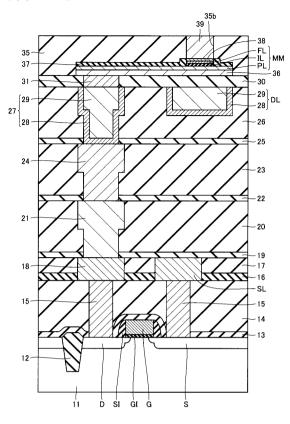

- 【図3】図2における磁気記憶素子付近の拡大断面図である。

- 【図4】図3のIV-IV線に沿った断面図である。

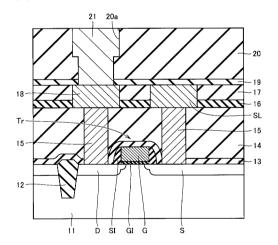

- 【図 5 】本発明の一実施の形態における磁気記憶装置の製造方法の第 1 工程を示す概略断面図である。

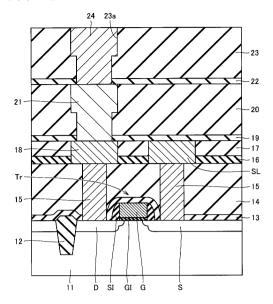

- 【図6】本発明の一実施の形態における磁気記憶装置の製造方法の第2工程を示す概略断面図である。

- 【図7】本発明の一実施の形態における磁気記憶装置の製造方法の第3工程を示す概略断面図である。

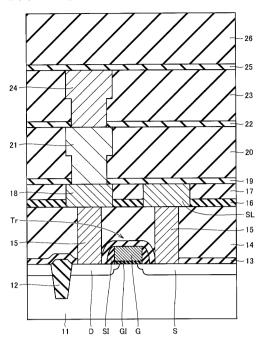

- 【図8】本発明の一実施の形態における磁気記憶装置の製造方法の第4工程を示す概略断面図である。

- 【図9】本発明の一実施の形態における磁気記憶装置の製造方法の第5工程を示す概略断面図である。

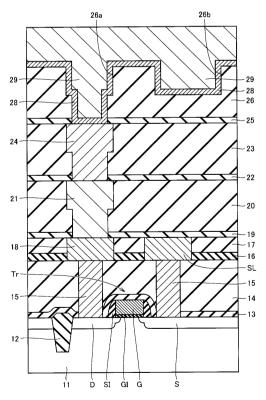

- 【図10】本発明の一実施の形態における磁気記憶装置の製造方法の第6工程を示す概略断面図である。

- 【図11】本発明の一実施の形態における磁気記憶装置の製造方法の第7工程を示す概略断面図である。

- 【図12】本発明の一実施の形態における磁気記憶装置の製造方法の第8工程を示す概略断面図である。

- 【図13】本発明の一実施の形態における磁気記憶装置の製造方法の第9工程を示す概略断面図である。

- 【図14】本発明の一実施の形態における磁気記憶装置の製造方法の第10工程を示す概略断面図である。

- 【図15】本発明の一実施の形態における磁気記憶装置の製造方法の第11工程を示す概略断面図である。

- 【図16】本発明の一実施の形態における磁気記憶装置の製造方法の第12工程を示す概略断面図である。

- 【図17】本発明の一実施の形態における磁気記憶装置の製造方法の第13工程を示す概略断面図である。

- 【図18】本発明の一実施の形態における磁気記憶装置の製造方法の第14工程を示す概略断面図である。

- 【図19】本発明の比較例として、ディジット線の幅が磁気記憶素子の幅以下である場合の一の問題点を説明するための概略断面図である。

- 【図 2 0 】本発明の比較例として、ディジット線の幅が磁気記憶素子の幅以下である場合の他の問題点を説明するための概略断面図である。

- 【図 2 1 】本発明の比較例として、ビット線の幅が磁気記憶素子の幅以上である場合の磁気記憶装置のレイアウト構成を示す概略平面図である。

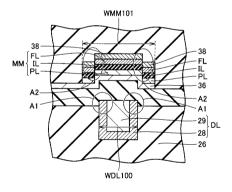

- 【図22】図17におけるディジット線、磁気記憶素子ユニット、およびビット線の位置

関係を模式的に示す図である。

【発明を実施するための形態】

#### [ 0 0 1 3 ]

以下、本発明の一実施の形態について、図面に基づいて説明する。なお、本実施の形態において、「下」という文言は半導体基板側を意味しており、「上」という文言は半導体 基板の反対側(ビット線側)を意味している。

#### [0014]

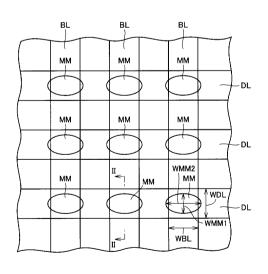

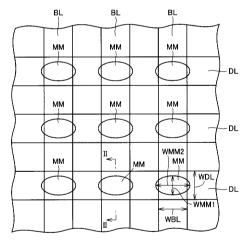

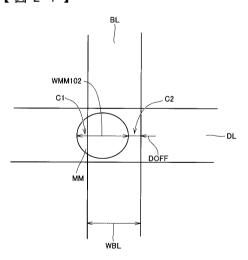

始めに、本実施の形態における磁気記憶装置の平面レイアウトについて、図1を用いて説明する。図1は、本発明の一実施の形態における磁気記憶装置のレイアウト構成を示す概略平面図である。図1を参照して、本実施の形態における磁気記憶装置は、複数のディジット線DL(第1の導体)と、複数のビット線BL(第2の導体)と、複数の磁気記憶素子MMとを備えている。複数のディジット線DLの各々は、図中横方向(第1の方向)に延在しており、複数のビット線BLの各々は、図中縦方向(第2の方向)に延在しており、での各交差部分には、たとえば正交しており、ディジット線DLとビット線BLとはたとえば直交しており、ディジット線DLとビット線BLとの各交差部分には、たとえば平面的に見て楕円形状を有する磁気記憶素子MMが配置されている。磁気記憶素子MMの各々は、磁化状態に基づいたデータを保持可能である。複数のディジット線DLおよび複数のビット線BLの各々は、発生する磁界により磁気記憶素子MMの磁化状態を変化させることが可能である。

## [0015]

次に、本実施の形態における磁気記憶装置のメモリセルの構成について、図2~図4を用いて説明する。

#### [0016]

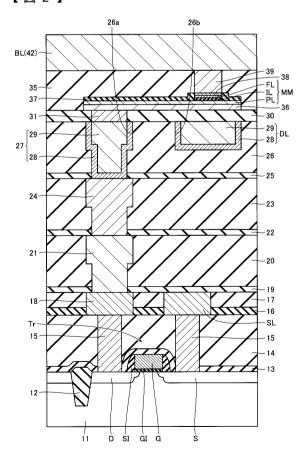

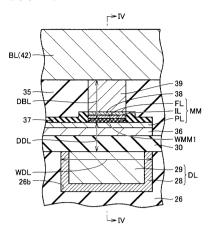

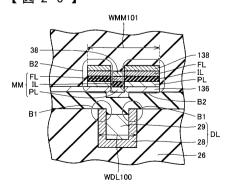

図2は、本発明の一実施の形態における磁気記憶装置のメモリセルの構成を示す概略断面図であり、図1のII-II線に沿った断面図である。図3は図2における磁気記憶素子付近の拡大断面図であり、図4は図3のIV-IV線に沿った断面図である。

## [0017]

特に図2を参照して、半導体基板11におけるメモリセル領域では、素子分離絶縁膜1 2によって区切られた素子形成領域の表面(半導体基板11の表面)に素子選択用トランジスタTrが形成されている。素子選択用トランジスタTrは、ドレイン領域Dと、ソース領域Sと、ゲート電極本体Gとを主に有している。ドレイン領域Dおよびソース領域Sは、互いに所定導電型の不純物領域から形成されている。ゲート電極本体Gは、ドレイン領域Dおよびソース領域Sに挟まれる領域上にゲート絶縁膜GIを介在して形成されている。ゲート電極本体Gの側壁は、サイドウォール状の側壁絶縁膜SIによって覆われている。

### [0018]

素子選択用トランジスタTrを覆うように層間絶縁膜13および14が形成されている。層間絶縁膜13および14には層間絶縁膜14の上面からドレイン領域Dおよびソース領域Sの各々に達する孔が設けられている。これらの孔内には導電層15が形成されている。層間絶縁膜14上には、層間絶縁膜16および17が形成されている。層間絶縁膜16および17には層間絶縁膜17の上面から導電層15の各々に達する孔が形成されている。これらの孔内のうち図中左側の孔内には導電層18が形成されており、図中右側の孔内にはソース線SLが形成されている。これにより、ソース線SLはソース領域Sと電気的に接続されている。

## [0019]

導電層18およびソース線SLを覆うように、層間絶縁膜17上に層間絶縁膜19および20が形成されている。層間絶縁膜19および20には層間絶縁膜20の上面から導電層18に達する孔が設けられている。この孔内には導電層21が形成されている。導電層21を覆うように、層間絶縁膜20上に層間絶縁膜22および23が形成されている。層間絶縁膜22および23には層間絶縁膜23の上面から導電層21に達する孔が設けられ

10

20

30

40

ている。この孔内には導電層24が形成されている。

#### [0020]

導電層24を覆うように、層間絶縁膜23上に層間絶縁膜25および26が形成されている。層間絶縁膜25および26には層間絶縁膜26の上面から導電層24に達する孔26aが設けられている。この孔26a内には導電層27が形成されている。また、層間には導電層27が形成されている。この溝26b内にはディジット線DLが形成されている。導電層27およびディジット線DLの各々は、導電層27およびディジット線DLの各々は、導電層27およびディジット線DLの各々は、連電層28(クラッド層)と、導電層29(導体本体)とを有している。導電層28は、孔26aおよび溝26bの各々における底面および側面に形成されており、導電層29における底面および内部に形成されており、導電層29におけるでれている。このような機の内部に形成されている。このような機の側における導電層29よりも磁気記憶素子MM側にある部分以外に形成することにより、ディジット線DLの導電層29はにを流を有する部分以外に形成することにより、ディジット線DLの導電層29に電流を流したこの電流から磁気記憶素子MMの方向(図中上方向)に発生する磁界を増大させることができる。なお、導電層28は形成されていなくてもよい。また、導電層28は形成されていなくてもよい。また、導電層28は形成されていなくてもよい。

## [0021]

導電層 2 7 およびディジット線 D L を覆うように、層間絶縁膜 2 6 上に層間絶縁膜 3 0 が形成されている。層間絶縁膜 3 0 にはその上面から導電層 2 7 に達する孔が設けられている。この孔内には導電層 3 1 が形成されている。

#### [0022]

特に図3および図4を参照して、層間絶縁膜30上には電極層36が形成されており、電極層36上には磁気記憶素子MMが形成されている。磁気記憶素子MMは、たとえばトンネル磁気抵抗(TMR)素子であり、磁化の向きが固着された磁化固定層PLと、磁化の向きが可変の磁化自由層FLと、磁化固定層PLと磁化自由層FLとの間に設けられたトンネル絶縁膜IL(中間層)とを有している。磁化固定層PLは電極層36上に形成されており、トンネル絶縁膜ILは磁化固定層PLの一部上に形成されており、磁化自由層FLは上に形成されている。磁化固定層PLは電極層36、導電層27、導電層24、導電層21、導電層18、および導電層15を介してドレイン領域Dと電気的に接続されている。なお、磁化固定層PLの代わりに磁化自由層FLが電極層36上に形成され、かつ磁化自由層FLの代わりに磁化固定層PLがトンネル絶縁膜IL上に形成され、かつ磁化自由層FLの代わりに磁化固定層PLがトンネル絶縁膜IL上に形成されてもよい。

## [ 0 0 2 3 ]

磁気記憶素子MM上には電極層38が形成されている。磁化固定層PL上におけるトンネル絶縁膜IL、磁化自由層FL、および電極層38が形成されていない領域には、絶縁膜37が形成されている。層間絶縁膜30および絶縁膜37上には、磁気記憶素子MMを覆うように層間絶縁膜35が形成されている。層間絶縁膜35にはその上面から電極層38に達する孔が設けられており、この孔内には導電層39が形成されている。

#### [0024]

特に図4を参照して、導電層39を覆うように、層間絶縁膜35上に層間絶縁膜40が形成されている。層間絶縁膜40にはその上面から導電層39に達する孔40aが設けられている。孔40a内にはビット線BLが形成されている。ビット線BLは、導電層41(クラッド層)と、導電層42(導体本体)とを有している。導電層41は、孔40aの側面に形成されており、導電層42は、導電層41に接触するように孔40aの内部に形成されている。導電層41は、たとえばNiFe合金(パーマロイ)などの磁性体よりなっている。導電層41は、導電層29と同様に、導電層42を流れる電流から発生する磁界の外部への漏洩を抑制する機能を有している。これにより、ビット線BLの導電層42に電流を流した際に、この電流から磁気記憶素子MMの方向(図中下方向)に発生する磁界を増大させることができる。なお、導電層41は、導電層42の周囲における導電層4

10

20

30

40

2よりも磁気記憶素子MM側にある部分以外に形成されていればよい。また、導電層41 は形成されていなくてもよい。

### [0025]

図1~図4を参照して、磁気記憶素子MMはディジット線DLの上であってビット線BLの下に配置されている。ディジット線DLはビット線BLとの交差部分において、平面的に見て延在方向に対して垂直な方向(図中縦方向)に幅WDL(第1の幅)を有している。ビット線BLはディジット線DLとの交差部分において、平面的に見て延在方向に対して垂直な方向(図1中横方向)に幅WBL(第2の幅)を有している。磁気記憶素子MMは、平面的に見てディジット線の延在方向に対して垂直な方向(図1中縦方向)に幅WMM1(第3の幅)を有しており、かつ平面的に見てビット線BLの延在方向に対して垂直な方向(図1中横方向)に幅WMM2(第4の幅)を有している。幅WDLは幅WMM1よりも大きく、かつ幅WBLは幅WMM2よりも小さい。

[0026]

また、特に図3および図4を参照して、ディジット線DLの上面からトンネル絶縁膜ILの下面までの距離DDLは、トンネル絶縁膜ILの上面からビット線BLの下面までの距離DBLよりも小さい。

[0027]

次に、本実施の形態の磁気記憶装置におけるメモリセルの動作について説明する。

図2を参照して、読み出しの際には、特定のメモリセルの磁気記憶素子MMに所定の電流を流し、磁化の向きによる抵抗値の違いを検知する。まず、特定のメモリセルの素子選択用トランジスタTrがON状態とされて、所定のセンス信号がビット線BLから特定の磁気記憶素子MMを経て、電極層36、導電層31、導電層27、導電層24、導電層21、導電層18、導電層15、素子選択用トランジスタTr、および導電層15を介してソース線SLに伝わる。

[0028]

このとき、磁気記憶素子MMにおける磁化固定層PLと磁化自由層FLとの磁化の向きが同じ向き(平行)の場合では抵抗値が相対的に低く、磁化固定層PLと磁化自由層FLとの磁化の向きが互いに反対向き(反平行)の場合では抵抗値が相対的に高くなる。その結果、磁化固定層PLと磁化自由層FLとの各磁化方向が平行の場合にはトンネル電流が大きくなり、磁化固定層PLと磁化自由層FLとの各磁化方向が反平行の場合にはトンネル電流が小さくなる。

[0029]

これにより、磁気記憶素子MMの磁化の向きが平行の場合では、ソース線SLに流れるセンス信号の強度は所定の参照メモリセルの信号強度より大きくなる。一方、磁気記憶素子MMの磁化の向きが反平行の場合では、センス信号の強度は所定の参照メモリセルの信号強度より小さくなる。こうして、センス信号の強度が所定の参照メモリセルの信号強度よりも大きいか小さいかによって、特定のメモリセルに書き込まれた情報が「0」であるか「1」であるかが判定される。

[0030]

書き込み(書き換え)の際には、ビット線BLおよびディジット線DLに所定の電流を流し、磁気記憶素子MMを磁化(磁化反転)する。まず、選択されたビット線BLとディジット線DLとの各々に所定の電流を流すことによってビット線BLとディジット線DLのまわりにはそれぞれ電流の流れの方向に対応した磁界が生じる。選択されたビット線BLとディジット線DLとが交差する領域に位置する磁気記憶素子MMには、ビット線BLを流れる電流によって生じた磁界との合成磁界が作用する。

[0031]

このとき、その合成磁界によって、磁気記憶素子MMの磁化自由層FLが磁化固定層PLの磁化の方向と同じ向きに磁化される態様と、磁化自由層FLが磁化固定層PLの磁化の方向とは反対の向きに磁化される態様とがある。こうして、磁化固定層PLと磁化自由

10

20

30

40

20

30

40

50

層 F L との磁化の向きが同じ向き(平行)の場合と互いに反対向き(反平行)の場合とが 実現されて、この磁化の向きが「 0 」または「 1 」に対応する情報として記録される。

#### [0032]

次に、本実施の形態における磁気記憶装置の製造方法の一例について説明する。

図5~図18は、本発明の一実施の形態における磁気記憶装置の製造方法を工程順に示す概略断面図である。図5を参照して、半導体基板11の主表面における所定の領域に素子分離絶縁膜12を形成することによって、メモリセル領域が形成される。次に、そのメモリセル領域に位置する半導体基板11の表面にゲート絶縁膜GIを介してゲート電極本体Gが形成される。そのゲート電極本体Gなどをマスクとして半導体基板11の表面に所定導電型の不純物を導入することにより、不純物領域からなるドレイン領域Dおよびソース領域Sが形成される。次に、ゲート電極本体Gを覆うように半導体基板11上に絶縁層を形成し、この絶縁層をエッチバックすることにより、ゲート電極本体Gの側部に側壁絶縁膜SIが形成される。こうして、メモリセル領域における半導体基板11の表面に素子選択用トランジスタTrが形成される。

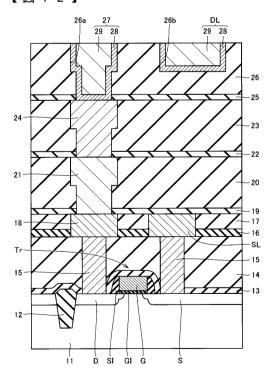

#### [0033]

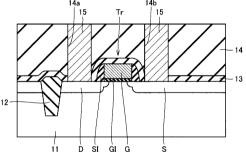

図6を参照して、素子選択用トランジスタTrを覆うように、たとえばCVD(Chemic al Vapor Deposition)法により層間絶縁膜13および14が形成される。層間絶縁膜13および14に対して所定の写真製版およびエッチングを施すことによって、半導体基板11の表面を露出する孔14a、14bが形成される。孔14a、14bを充填するように層間絶縁膜14上に導電層が形成される。その導電層に対してCMP(Chemical Me chanical Polishing)処理を施すことによって、層間絶縁膜13の上面上に位置する導電層の部分が除去される。その結果、孔14a、14b内の各々に導電層15が形成される。

## [0034]

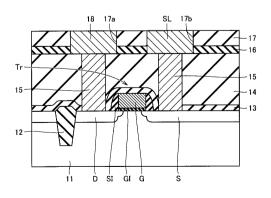

図7を参照して、2つの導電層15を覆うように、たとえばCVD法により層間絶縁膜14上に層間絶縁膜16および17が形成される。層間絶縁膜16および17に所定の写真製版およびエッチングを施すことによって、2つの導電層15に達する孔17a、17bが形成される。孔17a、17b内にたとえばメッキ法を用いて銅よりなる導電層18およびソース線SLが形成される。

## [ 0 0 3 5 ]

図8を参照して、導電層18およびソース線SLを覆うように、たとえばCVD法により層間絶縁膜17上にさらに層間絶縁膜19および20が形成される。層間絶縁膜19および20に所定の写真製版およびエッチングを施すことによって、導電層18に達する孔20aが形成される。孔20a内にたとえばメッキ法を用いて銅よりなる導電層21が形成される。

### [0036]

図9を参照して、導電層21を覆うように、たとえばCVD法により層間絶縁膜20上に層間絶縁膜22および23が形成される。層間絶縁膜22および23に所定の写真製版およびエッチングを施すことによって、導電層21に達する孔23aが形成される。孔23a内にたとえばメッキ法を用いて銅よりなる導電層24が形成される。

## [0037]

図 1 0 を参照して、導電層 2 4 を覆うように、たとえば C V D 法により層間絶縁膜 2 3 上に層間絶縁膜 2 5 および 2 6 が形成される。

## [0038]

図11を参照して、層間絶縁膜25および26に所定の写真製版およびエッチングを施すことによって、導電層24に達する孔26aが形成される。また、層間絶縁膜26の上部に所定の深さを有する溝26bが形成される。溝26bの形成の際には、溝26bはディジット線DLの幅WDL(図3)に対応する幅とされる。次に、たとえばスパッタ法を用いて、孔26aおよび溝26bの各々の側面上および底面上と、層間絶縁膜26上とに導電層28(クラッド層)が形成される。この導電層28上にたとえばメッキ法を用いて

導電層29(導体本体)が形成される。

### [0039]

図12を参照して、導電層28および29に平坦化処理(たとえばCMP処理)を施すことによって、層間絶縁膜26の上面上に位置する導電層28および29の部分が除去される。その結果、孔26a内に導電層27が形成され、溝26b内にディジット線DL(第1の導体)が形成される。

#### [0040]

図13を参照して、導電層27およびディジット線DLを覆うように、たとえばCVD法により層間絶縁膜26上に層間絶縁膜30が形成される。層間絶縁膜30に所定の写真製版およびエッチングを施すことによって、導電層27に達する孔30aが形成される。孔30a内にたとえばCVD法を用いて導電層31が形成される。

#### [0041]

図14を参照して、導電層31を覆うように、たとえばスパッタ法により層間絶縁膜30上に電極層36、磁化固定層PL、トンネル絶縁膜IL(中間層)、磁化自由層FL、および電極層38が形成される。層間絶縁膜30、電極層36、および磁化固定層PLを合わせた厚みは距離DDL(図3)に対応する厚みとされる。次に、所定の写真製版およびエッチングを施すことによって、トンネル絶縁膜IL、磁化自由層FL、および電極層38がパターニングされる。なお、このパターニングの際には、トンネル絶縁膜IL、磁化自由層FL、および電極層38の幅は磁気記憶素子MMの幅WMM1(図3)および幅MM2(図4)とされる。これにより、磁気記憶素子MMが得られる。

#### [0042]

図 1 5 を参照して、電極層 3 8 を覆うように、たとえば C V D 法により磁化固定層 P L 上に絶縁膜 3 7 および絶縁膜 3 5 a が形成される。

#### [ 0 0 4 3 ]

図16を参照して、所定の写真製版およびエッチングを施すことによって、絶縁膜35a、絶縁膜37、磁化固定層PL、および電極層36がパターニングされる。その結果、層間絶縁膜30の一部が露出する。

### [0044]

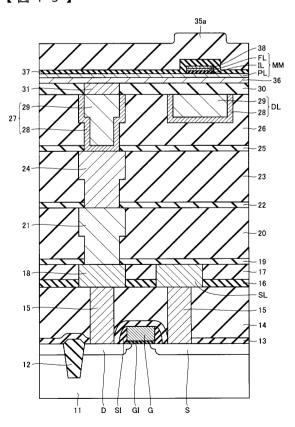

図17を参照して、絶縁膜35aを覆うように、たとえばCVD法により層間絶縁膜3 0上に絶縁膜35aと同一の材料よりなる絶縁膜を形成する。その結果、絶縁膜35aは 新たに形成された絶縁膜とともに層間絶縁膜35を構成する。

#### [0045]

図18を参照して、層間絶縁膜35に対してCMP処理を施すことによって、層間絶縁膜13の上面を平坦化する。この平坦化の際には、磁化自由層FL、電極層38、および電極層38上における層間絶縁膜35を合わせた厚みは距離DBL(図4)に対応する厚みとされる。次に、層間絶縁膜35に所定の写真製版およびエッチングを施すことによって、電極層38に達する孔35bが形成される。孔35b内にたとえばメッキ法を用いて銅よりなる導電層39が形成される。

### [0046]

図2~図4を参照して、導電層39を覆うように、たとえばスパッタ法により層間絶縁膜35上に層間絶縁膜40が形成される。層間絶縁膜35に所定の写真製版およびエッチングを施すことによって、導電層39に達する孔40aが形成される。孔40aの側面および底面と、層間絶縁膜35上とにたとえばスパッタ法を用いて導電層41(クラッド層)が形成され、導電層41に所定の写真製版およびエッチングを施すことによって、孔40aの側面以外の部分の導電層41が除去される。次に、孔40aを埋めるように層間絶縁膜40上にたとえばメッキ法を用いて導電層42(導体本体)が形成される。そして、導電層42にCMP処理を施すことによって、層間絶縁膜40の上面上に位置する導電層42の部分が除去される。その結果、孔40a内にビット線BL(第2の導体)が形成される。以上の工程により、本実施の形態における磁気記憶装置が完成する。

10

20

30

40

#### [0047]

なお、本実施の形態の磁気記憶装置では、導電層としてタングステン、シリコン、銅、チタン、あるいはタンタルなどの金属が用いられてもよい。さらに、このような金属の合金やこのような金属の窒化物などが用いられてもよい。特に導電層として銅を用いる場合には、いわゆるダマシン法を適用することができ、導電層と並行して配線層を形成することもできる。さらに、デュアルダマシン法を適用することもできる。また、ソース線、ビット線、およびディジット線などの配線としては、シリコン、タングステン、アルミニウム、チタンなどの金属、そのような金属の合金あるいはそのような金属の化合物が用いられてもよい。

### [0048]

また、トンネル絶縁膜ILとして、アルミニウム酸化物などの非磁性材料が用いられてもよい。また、トンネル絶縁膜ILとしてアルミニウム、シリコン、タンタル、マグネシウムなどの金属の酸化物、その金属の窒化物、シリケートなどに代表されるその金属の合金酸化物、あるいはその合金の窒化物などが用いられてもよい。なお、トンネル絶縁膜ILに換えて非磁性金属材料を用いることにより、磁気記憶素子MMを巨大磁気抵抗(GMR)素子としてもよい。

### [0049]

また、層間絶縁膜としてTEOS(Tetra Ethyl Ortho silicate)、SiO $_2$ 、あるいはSiNなどが用いられてもよい。

## [0050]

また、磁化固定層PLおよび磁化自由層FLとしては、たとえばニッケル、鉄およびバノまたはコバルトを主成分とする強磁性材料が好ましい。さらに、その強磁性材料の磁気特性向上と熱的安定性のため、それら強磁性材料にホウ素、窒素、シリコン、モリブーとに交流ができるでは、磁化固定層PLの磁気特性を改善する体心立方型、ルチル型、塩化ナトリウム型、ルテニの磁型の結晶構造を有する結晶性材料薄膜を積層する、および、安定化を図ること呼ばれるののなどの酸化防止膜を積層するなび破化自由層FLとして、ハーフメタルと呼ばれる。さらに、磁化固定層PLおよび磁化自由層FLとして、カーフメタルでは一方のスピンバンドにエネルギギャカを存るできる。磁化固定層PLおよび磁化自由層FLとして、対かの積層構造が用いられてもよい。できる。磁化固定層PLおよび磁化自由層FLとしてニッケル鉄合金膜が用いられてもよい。

## [0051]

また、本実施の形態においては、磁気記憶素子が単層の磁化固定層と単層の磁化自由層とにより構成される場合について示したが、2層以上の磁化固定層および2層以上の磁化自由層により構成されていてもよい。この構成においては、トンネル絶縁膜に対応する膜が本発明の中間層に対応する。

### [0052]

さらに、本実施の形態においては、第2の導体(ビット線)が磁気記憶素子の読み出しに用いられているが、第1および第2の導体は少なくとも磁気記憶素子の磁化状態を変化させるためのものであればよく、磁気記憶素子の読み出しの際に第2の導体以外の導体を用いてもよい。

## [ 0 0 5 3 ]

次に、本実施の形態における磁気記憶装置およびその製造方法の作用効果について説明する。

## [0054]

本実施の形態における磁気記憶装置およびその製造方法によれば、ディジット線 D L の幅W D L が磁気記憶素子 M M の幅 W M M 1 よりも大きく、かつビット線 B L の幅W B L が

10

20

30

40

20

30

40

50

磁気記憶素子MMの幅WMM2よりも小さいことにより、磁気記憶素子MMの機能低下を 抑止することができる。これについて以下に説明する。

#### [0055]

図19および図20は、本発明の比較例として、ディジット線の幅が磁気記憶素子の幅以下である場合の磁気記憶装置のメモリセルの構成を示す概略断面図である。図19を参照して、図12に示す平坦化処理を導電層28および29に対して施す際には、導電層28および29に対して施す際には、導電層28および29と、層間絶縁膜26とのエッチング速度の差に起因して、ディジット線DLの上面と層間絶縁膜26の上面との間に、ディジット線DLの形状に起因した段差A1が生じることがある。ディジット線DLの幅WDL100(図3に示す幅WDLに対応)が磁気記憶素子MMの幅WMM101(図3に示す幅WMMに対応)よりも小さいと、段差A1の真上に磁気記憶素子MMが形成されるため、磁気記憶素子MMにも段差A2が形成される。その結果、磁気記憶素子MMにおける磁化固定層および磁化自由層の磁区が段差A2において不連続となり、磁化固定層および磁化自由層の単磁区部分が減少する。これにより、磁気記憶素子MMの機能が低下する。

#### [0056]

また図19を参照して、図12に示す平坦化処理を導電層28および29に対して施す際には、導電層28と導電層29とのエッチング速度の差に起因して、導電層28の上面と導電層29の上面との間に、ディジット線DLの形状に起因した段差B1が生じることがある。ディジット線DLの幅WDL100が磁気記憶素子MMの幅WMM101よりも小さいと、段差A1の真上に磁気記憶素子MMが形成されるため、磁気記憶素子MMにも段差B2が形成される。その結果、磁気記憶素子MMにおける磁化固定層および磁化自由層の磁区が段差B2において不連続となり、磁化固定層および磁化自由層の単磁区部分が減少する。これにより、磁気記憶素子MMの機能が低下する。

#### [0057]

一方、図3に示すように、本実施の形態における磁気記憶装置においては、ディジット線DLの幅WDLが磁気記憶素子MMの幅WMM1よりも大きいので、図18に示す段差A1や図19に示す段差B1が仮に生じたとしても、段差A1や段差B1の真上に磁気記憶素子MMが形成され難くなる。これにより、磁気記憶素子MMに段差が生じ難くなり、磁化固定層および磁化自由層の単磁区部分の減少を防ぐことができる。その結果、磁気記憶素子MMの機能低下を抑止することができる。

#### [0058]

図21は、本発明の比較例として、ビット線の幅が磁気記憶素子の幅以上である場合の磁気記憶装置のレイアウト構成を示す概略平面図である。ビット線BLの形成時には記憶素子MMに対するビット線BLの位置ずれに起因して、ビット線BLが磁気記憶素子MMの真上の位置からはみ出して形成される可能性がある。この位置がれは、140a(図4)を形成する際の写真製版が不正確であることに起因するものである。図21をにいて、ビット線BLは、距離DOFFだけ磁気記憶素子MMの真上の位置がれている。ビット線BLが磁気記憶素子MMの幅WMM2にが生じた場合に、領域C1や領域C2が生じやすい。領域C1の磁気記憶素子MMはビット線BLが磁気記でが変化しならなるおそれがある。また、領域C2ではビット線BLが磁気記憶素子MMの外側に位置している。このため、領域C2にあるビット線BLにより生成る磁界は、磁気記憶素子の機能が低下する。

## [0059]

一方、図1および図3に示すように、本実施の形態における磁気記憶装置においては、ビット線BLの幅WBLが磁気記憶素子MMの幅WMM2よりも小さいので、磁気記憶素子MMに対するビット線BLの位置にずれが生じても、ビット線BLが磁気記憶素子の真上の位置からはみ出ることが抑止される。これにより、磁化方向が変化しない部分が磁気

記憶素子MMに生じることが抑止され、また磁気記憶素子MMの磁化方向の変化に寄与しない磁界が生じることが抑止される。その結果、磁気記憶素子の機能低下を抑制することができる。

#### [0060]

また、本実施の形態における磁気記憶装置およびその製造方法によれば、ディジット線 DLの上面からトンネル絶縁膜ILの下面までの距離DDLが、トンネル絶縁膜ILの上面からビット線BLの下面までの距離DBLよりも小さいことにより、磁気記憶素子MMの機能低下を抑止することができる。これについて以下に説明する。

### [0061]

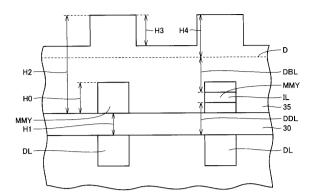

図 2 2 は、図 1 7 におけるディジット線、磁気記憶素子ユニット、およびビット線の位 置関係を模式的に示す図である。図22における磁気記憶素子ユニットMMYは、図17 における電極層36、磁化固定層PL、トンネル絶縁膜IL、磁化自由層FL、および電 極 層 3 8 を 合 わ せ た 構 造 に 対 応 す る 。 図 2 2 を 参 照 し て 、 層 間 絶 縁 膜 3 5 の 形 成 直 後 に お ける層間絶縁膜35の上面には、層間絶縁膜30と磁気記憶素子ユニットMMYとの段差 ( 高さ H 0 ) に起因して、高さ H 3 で示す段差が生じる。高さ H 3 はたとえば約 1 0 0 n mである。また、磁気記憶素子ユニットMMY同士の間隔(図22中横方向の長さ)はた とえば約200nmである。層間絶縁膜35上に形成されるビット線BLの各々と磁気記 憶 素 子 M M と の 距 離 を 均 一 に す る た め に 、 層 間 絶 縁 膜 3 5 の 上 面 は 平 坦 化 さ れ る 必 要 が あ る。層間絶縁膜35の上面の平坦化の際には、高さH3の1.5倍以上である高さH4( たとえば 1 5 0 n m ~ 2 0 0 n m ) だけ層間絶縁膜 3 5 が除去される。層間絶縁膜 3 5 の 除去の際には、磁気記憶素子における磁化層まで除去されるのを防ぐために、層間絶縁膜 35は、高さH0の少なくとも4倍の高さである高さH2(たとえば400nm)で形成 されることが望ましい。したがって、トンネル絶縁膜ILの上面からビット線BLの下面 までの距離DBLを大きくすることにより、その結果、層間絶縁膜35上に形成されるビ ット線BLの各々と磁気記憶素子MMとの距離が均一になる。一方、層間絶縁膜30には 磁気記憶素子ユニットMMYに起因する段差が生じないので、層間絶縁膜35に比べて平 坦性 が 高 い 。 こ の た め 、 デ ィ ジ ッ ト 線 D L か ら 生 じ る 磁 界 の 影 響 を 磁 気 記 憶 素 子 M M に 対 して効果的に及ぼすために、層間絶縁膜30は薄い(距離DDLが小さい)ことが望まし い。従って、距離DDLを距離DBLよりも小さくすることにより、磁気記憶素子の性能 低下を抑制することができる。

#### [0062]

なお、本実施の形態においては、幅WDLが幅WMM1よりも大きく、かつ幅WBLが幅WMM2よりも小さい第1の構成と、距離DDLが距離DBLよりも小さい第2の構成との両方を具備する場合について示したが、本発明の磁気記憶装置およびその製造方法においては、第1の構成および第2の構成のうち少なくとも一方を具備していればよい。しかし、第1の構成と第2の構成との両方を具備することにより、さらに磁気記憶素子MMの制御性を向上することができる。これについて以下に説明する。

### [0063]

ビット線またはディジット線からの電流ノイズによる磁気記憶素子MMの機能不良を防ぐためには、磁気記憶素子MMの磁化反転臨界値を示すアステロイド曲線において、ディジット線DLが磁気記憶素子MMに対して及ぼす磁場の大きさと、ビット線BLが磁気にに素子MMに対して及ぼす磁場の大きさとのバランスを取る必要がある。本実施の形態においては、ディジット線DLの幅WDLが大きくかつビット線BLの幅WBLがいたが、ビット線BLがら発生する磁場の大きさはディジット線DLから発生する磁場よりも大きいの発生する磁場が磁気記憶素子MMへ及ぼす影響は、ビット線BLから発生する磁場が磁気記憶素子MMへ及ぼす影響は、ビット線BLが磁気記憶素子MMに対して及ぼす磁場の大きさと、ビット線BLが磁気記憶素子MMに対して及ぼす磁場の大きさとのバランスを取り易くなり、磁気記憶素子MMの制御性を向上することができる

10

20

30

40

## [0064]

以上に開示された実施の形態はすべての点で例示であって制限的なものではないと考慮 されるべきである。本発明の範囲は、以上の実施の形態ではなく、特許請求の範囲によっ て示され、特許請求の範囲と均等の意味および範囲内でのすべての修正や変形を含むもの と意図される。

#### 【産業上の利用可能性】

### [0065]

本発明は、発生する磁界により磁気記憶素子の磁化状態を変化させることが可能な2つ の導体を備える磁気記憶装置およびその製造方法に適している。

## 【符号の説明】

#### [0066]

11 半導体基板、12 素子分離絶縁膜、13,14,16,17,19,20,2 2,23,25,26,30,35,40 層間絶縁膜、14a,17a,20a,23 a, 2 6 a, 3 0 a, 3 5 b, 4 0 a 孔、1 5, 1 8, 2 1, 2 4, 2 7 ~ 2 9, 3 1 , 3 9 , 4 1 , 4 2 導電層、 2 6 b 溝、 3 5 a , 3 7 絶縁膜、 3 6 , 3 8 電極層 、D ドレイン領域、DL ディジット線、FL 磁化自由層、G ゲート電極本体、G ゲート絶縁膜、IL トンネル絶縁膜、MM 磁気記憶素子、MMY 磁気記憶素子 ユニット、PL 磁化固定層、S ソース領域、SI 側壁絶縁膜、SL ソース線、T r 素子選択用トランジスタ。

20

10

## 【図1】

## 【図2】

【図3】

【図4】

【図5】

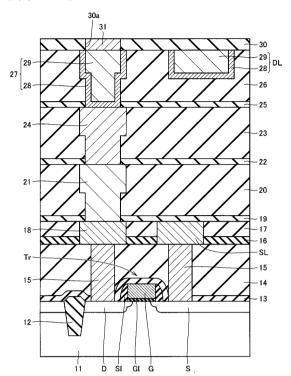

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

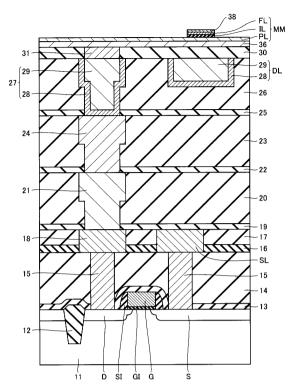

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図21】

【図20】

# 【図22】

## フロントページの続き

(74)代理人 100124523

弁理士 佐々木 眞人

(74)代理人 100098316

弁理士 野田 久登

(72)発明者 芦田 基

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

F ターム(参考) 4M119 AA20 BB01 CC02 DD25 DD33 DD55 EE03 EE23 EE27 FF05

FF13 FF14 FF15 FF17 JJ15 JJ16 KK18

5F092 AB08 AC08 AC12 BB17 BB22 BB23 BB30 BB33 BB34 BB35

BB36 BB37 BB42 BB43 BC04 BE13