#### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4084539号 (P4084539)

(45) 発行日 平成20年4月30日(2008.4.30)

(24) 登録日 平成20年2月22日 (2008.2.22)

| (51) Int.Cl. |        |            | FΙ   |        |   |

|--------------|--------|------------|------|--------|---|

| СЗОВ         | 29/38  | (2006.01)  | C30B | 29/38  | D |

| HO1L         | 21/205 | (2006.01)  | HO1L | 21/205 |   |

| HO1L         | 33/00  | (2006, 01) | HO1L | 33/00  | С |

請求項の数 3 (全 7 頁)

| (21) 出願番号<br>(22) 出願日<br>(65) 公開番号<br>(43) 公開日<br>審査請求日 | 特願2001-2723 (P2001-2723)<br>平成13年1月10日 (2001.1.10)<br>特開2002-211999 (P2002-211999A)<br>平成14年7月31日 (2002.7.31)<br>平成16年7月20日 (2004.7.20) | (73) 特許権者 000241463<br>豊田合成株式会社<br>愛知県西春日井郡春日町大字落合字長畑1<br>番地<br>(73) 特許権者 000003609<br>株式会社豊田中央研究所<br>愛知県愛知郡長久手町大字長湫字横道41<br>番地の1<br>(74) 代理人 100087723 |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                                         | 弁理士 藤谷 修<br>(72)発明者 永井 誠二<br>愛知県西春日井郡春日町大字落合字長畑 1<br>番地 豊田合成株式会社内                                                                                       |

|                                                         |                                                                                                                                         | 最終頁に続く                                                                                                                                                  |

(54) 【発明の名称】 1 1 1 族窒化物系化合物半導体の結晶成長基板の製造方法

### (57)【特許請求の範囲】

### 【請求項1】

結晶成長基板の下地となる下地基板としてシリコン(Si<u>)を</u>用いた、III族窒化物系化合物半導体の結晶成長基板の製造方法であって、

前記下地基板の上にIII族窒化物系化合物半導体より成る基板層を<u>前記下地基板の厚さ</u>以上に成長させ、

その後前記下地基板と前記基板層を<u>50/min以下の冷却速度で</u>冷却する際に、<u>前</u>記基板層の前記下地基板側の界面への応力により前記下地基板を前記基板層から剥離させることにより、残った前記基板層を前記結晶成長基板とする

ことを特徴とするII族窒化物系化合物半導体の結晶成長基板の製造方法。

#### 【請求項2】

前記基板層を 5 0 μ m 以上成長させることを特徴とする請求項 1 に記載のIII族窒化物系化合物半導体の結晶成長基板の製造方法。

### 【請求項3】

前記下地基板を50µm以上、300µm以下に形成することを特徴とする請求項1又は請求項2に記載のIII族窒化物系化合物半導体の結晶成長基板の製造方法。

### 【発明の詳細な説明】

#### 【発明の属する技術分野】

本発明は、結晶成長基板の下地となる下地基板としてシリコン(Si<u>)を</u>用いた、III 族窒化物系化合物半導体の結晶成長基板の製造方法に関する。

#### [0001]

### 【従来の技術】

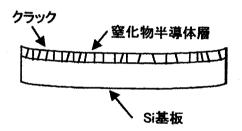

図3に例示する様に、シリコン基板上に窒化ガリウム(GaN)を結晶成長させ、その後常温まで冷却すると、GaN成長層に転位やクラックが多数入ることが一般に知られている。

#### [00002]

#### 【発明が解決しようとする課題】

この様に、成長層に転位やクラックが多数入ると、その上にデバイスを作製した場合に、デバイス中に格子欠陥や転位、変形、クラック等が多数生じる結果となり、デバイス特性の劣化を引き起こす原因となる。

また、シリコン(Si)基板を除去し、成長層のみを残して、独立した基板を得ようとする場合、上記の転位やクラック等の作用により、大面積(1 cm²以上)のものが得られない。

### [0003]

本発明は、上記の課題を解決するために成されたものであり、その目的は、転位やクラックの密度が低い高品質の結晶成長基板を得ることである。

#### [0004]

#### 【課題を解決するための手段】

上記の課題を解決するためには、以下の手段が有効である。

即ち、第1の手段は、結晶成長基板の下地となる下地基板としてシリコン(Si<u>)を</u>用いた、III族窒化物系化合物半導体の結晶成長基板の製造工程において、下地基板の上にII族窒化物系化合物半導体より成る基板層を<u>下地基板の厚さ以上に</u>成長させ、その後下地基板と基板層を<u>50 / min以下の冷却速度で</u>冷却する際に、<u>基板層の下地基板側の界面への応力により</u>下地基板を基板層から剥離させることにより、残った基板層を結晶成長基板とすることである。

#### [0005]

また、第2の手段は、上記の第1の手段において、基板層を50μm以上成長させることである。

#### [0006]

また、第3の手段は、上記の第1又は第2の手段において、下地基板を50 $\mu$ m以上、300 $\mu$ m以下に形成することである。

### [0007]

以上の手段により、前記の課題を解決することができる。

### [0008]

### 【作用及び発明の効果】

下地基板(Si基<u>板)</u>の上にIII族窒化物系化合物半導体より成る基板層を成長させる際、基板層(III族窒化物系化合物半導体)の結晶成長温度では、歪の少ない状態で結晶成長が進む。しかし、シリコンとGaN等のIII族窒化物系化合物半導体とでは熱膨張係数が大きく異なるため、結晶成長完了後に基板が略常温まで冷却される際には基板に大きな歪が生じ、例えば図3に例示した様に基板層に転位やクラックが発生する。

### [0009]

しかしながら、本発明の手段によれば、下地基板(Si基<u>板)</u>に対して、従来よりも比較的厚く基板層(III族窒化物系化合物半導体)が形成されるため、下地基板(Si基<u>板</u>)に対して相対的に基板層が強固となり、基板層の転位やクラックの発生密度が減少する

# [0010]

この時、従来は比較的薄く形成されていた基板層(III族窒化物系化合物半導体)の略全体に略均等に働いていた引っ張り応力は、厚く強固に形成された基板層の下地基板側の界面に集中し易くなり、また、厚く強固に形成された基板層には転位やクラックが発生し難くなっているため、これらの作用により、下地基板と基板層を略常温まで冷却すると、

10

20

30

40

10

20

30

40

50

圧縮応力を受ける下地基板は、引っ張り応力を受ける基板層の界面から剥離する。

#### [0011]

また、これらの作用は熱膨張係数差に基づくものであるので、より一般には、下地基板を基板層との界面より剥離させる応力は、加熱等による温度変化によっても得ることができる。

#### [0012]

結晶成長させる基板層(III族窒化物系化合物半導体)の厚さは、50 μ m 以上が望ましい。この厚さが厚い程、基板層に対する引っ張り応力が緩和されて、基板層の転位やクラックの発生密度を減少でき、同時に基板層を強固にできるため、上記の応力を基板層と下地基板との界面に集中させ易くなる。

### [0013]

また、下地基板(Si基<u>板)</u>の厚さは、300μm以下が望ましい。この厚さが薄い程、基板層に対する引っ張り応力が緩和されて、基板層の転位やクラックの発生密度が減少する。ただし、下地基板(Si基<u>板)</u>の厚さを50μm未満とすると、下地基板自身の絶対的な強度に問題が生じ、高い生産性を維持することが難しくなる。したがって、製造する結晶成長基板の品質と生産性を確保するためには、下地基板(Si基<u>板)</u>の厚さは、50μm以上300μm以下が望ましい。

#### [0014]

また、相対的には、結晶成長させる基板層(III族窒化物系化合物半導体)の厚さは、下地基板(Si基板)の厚さと同等とするか、或いはそれ以上とすることが望ましい。この様な設定により、基板層に対する引っ張り応力が緩和され易くなり、基板層の転位やクラックの発生を従来よりも大幅に抑制することが可能となる。この効果は、相対的に基板層を厚くする程大きくなる。

#### [0015]

尚、結晶成長させる基板層(III族窒化物系化合物半導体)と下地基板(Si基<u>板)</u>との間には、或いは、結晶成長後の基板層の上には、例えば、炭化シリコン(SiC)や、任意の混晶比のIII族窒化物系化合物半導体より成るバッファ層等を形成しても良い。これらの基板層やバッファ層は、GaNやAlN、SiCの他、<math>GaNやAlN、SiCに対してその組成比に殆ど影響しない程度のインジウム(<math>In)を添加したものや、或いは、InN,  $Al_xGa_{1-x}N$ (0 < x < 1),  $In_xGa_{1-x}N$ (0 < x < 1),  $Al_xIn_1$ -xN(0 < x < 1),  $Al_xGa_yIn_{1-x-y}N$ (0 < x < 1, 0 < y < 1, 0 < x + y < 1)等から形成しても良く、その他、一般式が $Al_xGa_yIn_{1-x-y}N$ (0 x 1, 0 x + y 1)成る $2\pi$ 、3元、若しくは $4\pi$ のIII族窒化物系半導体において、III族元素のうちの一部をボロン(III)等で置換したり、或いは、窒素の一部をリン(III)等で置換したり、で置換したりした半導体等から形成しても良い。

### [0016]

また、これらの基板層やバッファ層をはじめとする、積層される任意のIII族窒化物系化合物半導体層には、Si等のn型ドーパント、或いは、カルシウム(Ca)やMg等のp型ドーパントを添加しても良い。これらの添加物(ドーパント)は、一つの層に対して、n型、p型の両方を好適な比率で添加しても良い。また、これらの各半導体層は、2種以上の半導体の接合から成る超格子構造としても良い。

#### [0017]

また、バッファ層は、下地基板上に成長させるIII族窒化物系化合物半導体、例えば、GaNから成る基板層中に多重に繰り返して形成しても良い。この層を中間層といい、多重に繰り返して形成された複数の中間層を多重中間層という。これらの中間層には、バッファ層と同じ組成を用いることができる。即ち、例えば、A1N、GaN、その他、上記の2元、3元、4元のA1GaInN等を用いることができる。

#### [0018]

尚、これらのバッファ層は、900~1200 で形成するものの他、300~9

00 の低温で形成しても良い。この温度範囲は、1000 ~ 1150 が望ましく、 更に望ましくは、1050 ~ 1100 である。

#### [0019]

或いは、バッファ層は、MOCVD法の他、HVPE法やMBE法等が使用できる。又、スパッタリングを使用することも可能である。

また、DCマグネトロンスパッタ装置を用いて、高純度金属アルミニウムと窒素ガスを原材料として、リアクティブスパッタ法によりA1Nから成るバッファ層を形成することもできる。

#### [0020]

その他、金属アルミニウム、金属ガリウム、金属インジウム、窒素ガス又はアンモニアガスを用いて、一般式  $A_1$  、 $G_2$  の  $G_3$   $G_4$  の  $G_4$  の  $G_5$  の  $G_5$  の  $G_6$  の  $G_6$  の  $G_7$  の  $G_8$  の  $G_8$

#### [0021]

これらのスパッタリング法等の物理蒸着法を用いた場合には、バッファ層の厚さは、100~3000 が望ましい。更に望ましくは、100~2000 が望ましく、最も望ましくは、100~300 である。

### [0022]

また、Si基板の下地基板の上に成長させる任意の半導体層の結晶成長には、横方向成長(ELO)法等を用いることが可能である。これらの横方向成長(ELO)法としては、エッチング等により基板やバッファ層等を部分的に露出させ、エッチングされたバッファ層等の層の上に半導体結晶を横方向成長させる、保護膜を用いない方法と、基板やバッファ層等の上に保護膜層を形成し、露出している基板やバッファ層等の上に半導体結晶を横方向成長させる、保護膜を用いる方法とがある。

#### [0023]

また、ELOに使用する保護膜としては、III族窒化物系化合物半導体が成長し難い材料が有用である。具体的には、例えば、酸化硅素( $SiO_X$ )、窒化硅素( $Si_XN_Y$ )、酸化チタン( $TiO_X$ )、酸化ジルコニウム( $ZrO_X$ )等の酸化物、窒化物、これらの多層膜、或いは、1200 以上の融点を有する金属等である。

### [0024]

即ち、ELOに使用する保護膜としては、600~1100 におけるIII族室化物の成長温度にも耐えることができ、且つ、その上にはIII族窒化物系化合物半導体が成長しないか成長し難いものであることが必要である。また、成膜は、蒸着、CVD等の気相成長法、或いは、スパッタリング等により成膜することができる。

ELOに関するこれらの手段により、更にクラックの発生数を低減できる。

#### [0025]

### 【発明の実施の形態】

以下、本発明を具体的な実施例に基づいて説明する。ただし、本発明は以下に示す実施 例に限定されるものではない。

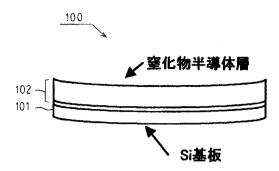

図1は、シリコン(Si)より形成された直径約10cmの略円形の下地基板101の上に、有機金属化合物気相成長法(MOVPE)により、窒化ガリウム(GaN)より成る基板層(窒化物半導体層)102を結晶成長させて得られたサンプル(基板100)の模式的な断面図であり、本実施例における結晶成長基板の製造過程(1工程)を例示している。

#### [0026]

本気相成長では、アンモニア( $\mathsf{NH}_3$ )ガス、キャリアガス( $\mathsf{H}_2$ , $\mathsf{N}_2$ )、トリメチルガリウム( $\mathsf{G}$  a( $\mathsf{CH}_3$ ) $_3$ )ガス(以下「 $\mathsf{TMG}$ 」と記す)、及びトリメチルアルミニウム( $\mathsf{AI}$ ( $\mathsf{CH}_3$ ) $_3$ )ガス(以下「 $\mathsf{TMA}$ 」と記す)を用いた。以下、その製造手順の概要を示す。

20

10

30

40

まず、シリコン(Si)より成る単結晶の下地基板101を有機洗浄及び熱処理により洗浄し、MOVPE装置の反応室に載置されたサセプタに装着した。ただし、装着した下地基板101の厚さは、約50 $\mu$ m、約100 $\mu$ m、約200 $\mu$ m、約500 $\mu$ mの4種類とした。

次に、常圧で $H_2$ を反応室に流しながら温度1100 で下地基板101をベーキングした。

### [0027]

その後、 $H_2$ ,  $NH_3$ , TMG, TMAを供給して、A1GaN層を形成し、下地基板 1 0 1 の温度を 1 1 0 0 に保持し、 $H_2$ 、 $NH_3$ 及び TMGを供給して、窒化ガリウム(GaN)より成る基板層 1 0 2 を結晶成長させ、その後、下地基板 1 0 1 と基板層 1 0 2 を 5 0 /min以下の冷却速度で冷却する。

[0028]

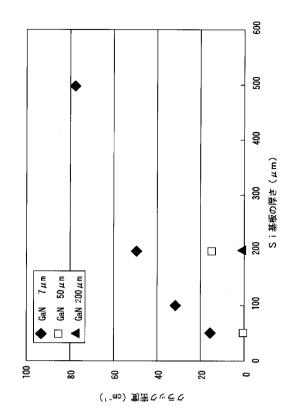

以上の手順により得られたGaN成長層のクラック密度を測定した。図2は、本実施例におけるこの結晶成長基板のクラック密度と、下地基板(Si基板)の厚さとの関係を例示するグラフである。

#### [0029]

例えば、本図 2 には基板層(GaN成長層)の膜厚を略  $7\mum$ に決めたサンプルに関する測定結果( $\pi$ 0)を例示しているが、本図からも判る様に、 $\pi$ 2 基板の厚さを薄くする程、その減少に伴ってクラック密度は著しく減少する。また、本図より、膜厚 2 0 0  $\mu$ 0 の基板層( $\pi$ 0)ではクラック密度が 1 cm<sup>-1</sup>以下となり、よって 1 cm<sup>2</sup>以上の  $\pi$ 0 a N 基板がえられることが判る。

[0030]

また、例えば、本図2には、基板層(GaN成長層)の膜厚を7μm,50μm、及び200μmに設定し、約200μmの下地基板(Si基板)を使用した際の各サンプルのクラック密度の測定結果を例示しているが、本図からも判る様に、同じSi基板の厚さに対して、基板層(GaN成長層)の厚さを厚くする程、その増加に伴ってクラック密度は著しく減少することが判る。

#### [0031]

即ち、基板層の厚さを  $50\mu$  m以上にした場合には、有用な大面積の GaN 基板を得ることが可能である。

また、逆に、基板層の厚さを例えば 7 μ m 程度に留めた実験では、基板層は一部が剥離するが、小面積のものしか得られなかった。

更に、従来の様に、基板層の厚さを 2 ~ 3 μ m 程度に留めた場合には、基板層は下地基板から殆ど剥離しなかった。

### [0032]

尚、上記の実施例では、有機金属化合物気相成長法(MOVPE)により、下地基板(Si基板)に窒化ガリウム(GaN)より成る基板層(窒化物半導体層)102を結晶成長させて得られたサンプル(基板100)について、その測定結果を例示したが、例えば液相成長法(LPE)や、ハライド気相成長法(HVPE)等の結晶成長法も、厚い基板層を形成する上で有効である。

例えばこれらに代表されるその他の結晶成長法によって得られる基板についても、上記 の実施例と略同様に、本発明の手段による本発明の作用・効果を得ることができる。

【図面の簡単な説明】

【図1】 本発明の結晶成長基板の製造過程を例示する基板の模式的な断面図。

【図2】 基板層(GaN成長層)のクラック密度と、下地基板(Si基板)の厚さとの 関係を例示するグラフ。

【図3】 従来の結晶成長基板の製造過程を例示する基板の模式的な断面図。

#### 【符号の説明】

100 ... 基板

101 ... 下地基板(Si基板)

102 ... 基板層(窒化物半導体層)

20

10

30

【図1】

【図2】

【図3】

### フロントページの続き

# (72)発明者 冨田 一義

愛知県愛知郡長久手町大字長湫字横道41番地の1 株式会社豊田中央研究所内

審査官 鮎沢 輝万

(56)参考文献 特開平11-001399(JP,A)

特開2001-253794(JP,A)

特開2002-050585(JP,A)

(58)調査した分野(Int.CI., DB名)

C30B 1/00-35/00

H01L 21/205

H01L 33/00