(19) **日本国特許庁(JP)**

(21) 出願番号

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5723821号 (P5723821)

(45) 発行日 平成27年5月27日 (2015.5.27)

(24) 登録日 平成27年4月3日(2015.4.3)

| (51) Int.Cl. |              |           | F 1  |       |      |

|--------------|--------------|-----------|------|-------|------|

| G09G         | 3/30         | (2006.01) | GO9G | 3/30  | J    |

| G09G         | 3/20         | (2006.01) | GO9G | 3/20  | 621J |

| HO1L         | <i>51/50</i> | (2006.01) | HO5B | 33/14 | Α    |

特願2012-89310 (P2012-89310)

請求項の数 6 (全 77 頁)

(22) 出願日 平成24年4月10日 (2012.4.10) (62) 分割の表示 特願2006-115825 (P2006-115825) の分割 平成18年4月19日(2006.4.19) 原出願日 (65) 公開番号 特開2012-150511 (P2012-150511A) (43) 公開日 平成24年8月9日(2012.8.9) 審査請求日 平成24年5月2日(2012.5.2) (31) 優先権主張番号 特願2005-121917 (P2005-121917) (32) 優先日 平成17年4月20日 (2005.4.20) (33) 優先権主張国 日本国(JP)

(73)特許権者 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 山崎 仁之

(56) 参考文献 特開2005-099764 (JP, A ) 特開2006-323376 (JP, A

最終頁に続く

(54) 【発明の名称】半導体装置、表示モジュール、及び電子機器

## (57)【特許請求の範囲】

## 【請求項1】

第 1 のトランジスタ、第 2 のトランジスタ、第 3 のトランジスタ及び第 4 のトランジスタと、

第1の配線、第2の配線、第3の配線及び第4の配線と、

画素電極と、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の配線と電気的に接続され、

前記第1のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第3の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記画素電極と電気的に接続

前記第4のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第3のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第4の配線と電気的に接

#### 続され、

前記第3のトランジスタのゲートは、前記第3の配線と電気的に接続され、

前記第4のトランジスタのゲートは、前記第4の配線と電気的に接続され、

前記第3のトランジスタは、前記第4のトランジスタと、異なる極性を有し、

前記第1の配線は、映像信号を伝えることができる機能を有し、

前記第2の配線は、第1の信号を伝えることができる機能を有し、

前記第3の配線は、前記画素電極に電流を伝えることができる機能を有し、

前記第4の配線は、第2の信号を伝えることができる機能を有し、

前記第1のトランジスタは、前記第1の信号に応じて、前記第2のトランジスタのゲートに、前記映像信号を供給することができる機能を有し、

前記第2のトランジスタは、前記画素電極に伝える前記電流の電流量を制御することができる機能を有し、

前記第3のトランジスタ又は前記第4のトランジスタは、前記第2のトランジスタに前記第2の信号を伝えるか否かを制御することができる機能を有することを特徴とする半導体装置。

#### 【請求項2】

請求項1において、

前記第4のトランジスタの極性は、Nチャネル型であることを特徴とする半導体装置。

#### 【請求項3】

請求項1または請求項2において、

前記第3のトランジスタの極性は、Pチャネル型であることを特徴とする半導体装置。

#### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記画素電極を含む表示素子を有することを特徴とする半導体装置。

#### 【請求項5】

FPC又はハウジングと、

請求項1乃至請求項4のいずれか一項に記載の半導体装置と、

を有する表示モジュール。

## 【請求項6】

アンテナ、操作キー、音声入力部、又は、外部接続ポートと、

請求項<u>5</u>に記載の表示モジュール、又は、請求項1乃至請求項<u>4</u>のいずれか一項に記載の半導体装置と、

を有する電子機器。

【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明は負荷に供給する電流をトランジスタで制御する機能を設けた半導体装置に係り、特に電流によって輝度が変化する電流駆動型発光素子で形成された画素や、その走査線駆動回路や信号線駆動回路を含む表示装置に関する。また、その駆動方法に関する。また、その表示装置を表示部に有する電子機器に関する。

#### 【背景技術】

## [0002]

近年、画素を発光ダイオード(LED)などの発光素子で形成した、いわゆる自発光型の表示装置が注目を浴びている。このような自発光型の表示装置に用いられる発光素子としては、有機発光ダイオード(OLED(Organic Light Emitting Diode)、有機EL素子、エレクトロルミネッセンス(Electro Luminescence:EL)素子などとも言う)が注目を集めており、ELディスプレイなどに用いられるようになってきている。OLEDなどの発光素子は自発光型であるため、液晶ディスプレイに比べて画素の視認性が高く、バックライトが不要で応答速度が速い等の利点がある。なお、発光素子の輝度は、そこを流れる電流値によって制御される。

10

20

30

40

#### [00003]

このような表示装置の階調を表現する駆動方式として、アナログ階調方式とデジタル階調方式がある。アナログ方式には、発光素子の発光強度をアナログ制御する方式と発光素子の発光時間をアナログ制御する方式がある。アナログ階調方式においては発光素子の発光強度をアナログ制御する方式がよく用いられている。しかし、発光強度をアナログ制御する方式は、画素毎の薄膜トランジスタ(以下TFTともいう)の特性のバラツキの影響を受けやすく、画素毎の発光にもバラツキが生じてしまう。一方、デジタル階調方式はデジタル制御で発光素子をオンオフさせ、階調を表現している。デジタル階調方式の場合で、2 階調しか表現できない。そこで、別の手法を組み合わせて、多階調化を図ることが行われている。多階調化のための手法としては、画素の発光面積に重みをつけてその選択により階調表示を行う時間階調方式とがある。そして、デジタル階調方式の場合には、高精細化にも適している時間階調法が用いられることが多い。

【先行技術文献】

【特許文献】

[0004]

【特許文献 1 】特開 2 0 0 1 - 3 4 3 9 3 3 号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

時間階調方式を採用する場合には、発光素子を駆動するトランジスタはデジタル式にオンオフさせればよいため、画素を構成するトランジスタの特性のばらつきによる画素間の輝度のばらつきの影響はあまりない。

[0006]

通常、トランジスタをオンさせる場合、Pチャネル型トランジスタのときには、ゲート端子にLow(以下Lレベルともいう)の電位を入力して行う。このLレベルの電位はPチャネル型トランジスタのソース端子の電位よりも低い電位であり、Lレベルの電位とPチャネル型トランジスタのソース端子の電位との電位差がPチャネル型トランジスタのいース端子の電位との電位差がPチャネル型トランジスタのときにはHigh(以下Hレベルともいう)の電位を入力して行う。このHレベルの電位はNチャネル型のトランジスタのソース端子の電位よりも高い電位であり、Hレベルの電位とNチャネル型のトランジスタのしきい値電圧以上となる電位である。なお、通常のPチャネル型トランジスタのしきい値電圧は、0Vより小さい電圧である。また、通常のNチャネル型のトランジスタのしきい値電には、10Vより大きい電圧である。よって、トランジスタのゲートソース間電圧が0Vのときには、トランジスタはオフし、電流は流れない。このようなトランジスタをエンハンスメント型トランジスタ(ノーマリーオフともいう)という。

[0007]

一方、トランジスタのゲートソース間電圧が 0 V であっても、トランジスタに電流が流れてしまうものがある。なお、このようなトランジスタをディプレション型トランジスタ(ノーマリーオンともいう) という。

[0008]

通常、ノーマリーオフの状態になるようにトランジスタを作製する。しかし製造ばらつきによって、ノーマリーオンになってしまう場合がある。駆動トランジスタがノーマリーオンになってしまうと、画素を非点灯とすべきときにも駆動トランジスタに電流が流れてしまい、発光素子へも電流が流れてしまうことがある。すると、正しく表示をすることができなくなってしまう。

[0009]

そこで、駆動トランジスタのソース領域やドレイン領域に添加する不純物とは逆の導電型

10

20

30

40

20

30

40

50

の不純物をチャネル形成領域に添加し、駆動トランジスタをより完全にノーマリーオフにする場合がある。つまり、駆動トランジスタをより完全にエンハンスメント型トランジスタにすることが行われる場合がある。これは、チャネルドープと一般に呼ばれている。または、駆動トランジスタがPチャネル型のトランジスタの場合、駆動トランジスタをオフさせるビデオ信号の電位(駆動トランジスタのゲート端子に入力する電位)を、駆動トランジスタのソース端子に入力する電位よりも高く設定することにより駆動トランジスタの場合、駆動トランジスタをオフさせるビデオ信号の電位(駆動トランジスタのゲート端子に入力する電位)を、駆動トランジスタのソース端子に設定する電位よりも低く設定することにより駆動トランジスタをオフさせる場合がある。

[0010]

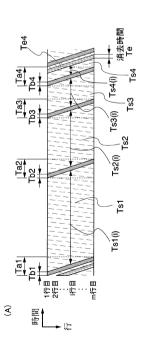

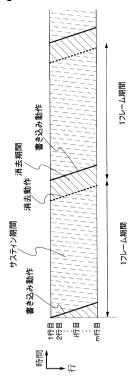

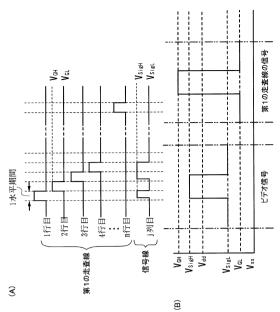

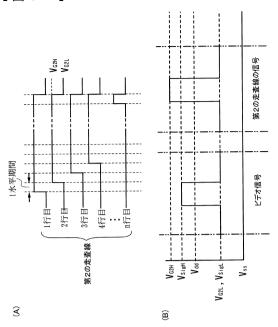

ここで、デジタル時間階調において、高精細化及び高階調表示を実現するために、画素への信号の書き込み動作と、画素への信号の消去動作を同時に行う技術が用いられている。つまり、画素への信号の書き込みが行われると、その画素は直ぐに発光期間(サスティン期間)となるような駆動方法において、画素への信号の書き込み期間(アドレス期間)より短い発光時間を設けるため、次に画素への信号書き込みが行われる前に、画素へ書き込まれた信号の消去を行うものである。このような駆動方法について図8を用いて説明する

[0011]

図8は時間経過に伴った1フレーム期間の動作について説明する図である。図8において、横方向は時間経過を表し、縦方向は走査線の走査行数を表している。

[0012]

画像表示を行うとき、書き込み動作と発光動作とが繰り返し行われる。一画面(1フレーム)分の書き込み動作と発光動作を行う期間を1フレーム期間という。1フレーム分の信号の処理について特に限定はないが、画像をみる人がちらつき(フリッカ)を感じないように少なくとも1秒間に60回程度とすることが好ましい。

[0013]

1フレーム期間は、図8に示すように、アドレス期間Ta1、Ta2、Ta3、Ta4とサスティン期間Ts1、Ts2、Ts3、Ts4とを含む4つのサブフレーム期間に時分割されている。つまり、それぞれの画素行については、書き込み時間Tb1、Tb2、Tb3、Tb4と発光時間Ts1(i)、Ts2(i)、Ts3(i)、Ts4(i)とに時分割されている。発光するための信号が入力された画素の発光素子は、サスティン期間において発光状態となっている。各々のサブフレーム期間における発光時間の長さの比は、Ts1(i):Ts2(i):Ts3(i):Ts4(i)=2 $^3$ :2 $^1$ :2 $^0$ =8:4:2:1となっている。これによって4ビット階調を表現することができる。但し、ビット数及び階調数はここに記すものに限定されず、例えば8つのサブフレーム期間を設け8ビット階調を行えるようにしてもよい。

[0014]

1フレーム期間における動作について説明する。まず、アドレス期間Ta1において、1行目から最終行まで、それぞれの行の書き込み時間Tb1に書き込み動作が行われる。つまり、1行目から順に走査線に走査信号が入力され、画素が選択される。そして、画素が選択されているときに、信号線から画素へビデオ信号が入力され、その電位によってサスティン期間Ts1における各画素の点灯、非点灯が制御される。従って、行によって画素の書き込み動作の開始時間が異なる。書き込み動作が終了した行から順にサスティン期間Ts1へと移る。当該サスティン期間において、発光するための信号が入力されていりの産業の発光素子は発光状態となっている。また、サスティン期間Ts1が終了した行から順に次のサブフレーム期間の信号書き込み動作に移り、それぞれの信号書き込み時間Tb2において、同様に1行目から最終行まで順に書き込み動作が行われる。このように、同様にアドレス期間Ta2、Ta3、Ta4において画素へビデオ信号が入力され、その電位によってサスティン期間Ts2、Ts3、Ts4における各画素の点灯、非点灯が制御

される。以上のような動作を繰り返し、サスティン期間Ts4迄終了する。

## [0015]

サスティン期間Ts4のように、最終行目までの書込動作が終了する前に、既に発光時間を終えた行におけるサスティン期間を強制的に終了させたいときは、消去時間Teにより画素に書き込まれたビデオ信号を消去し、強制的に非発光の状態となるように制御する。そして、強制的に非発光状態にした行については、一定期間、非発光の状態を保つ(この期間を非発光期間Te4とする。)。そして、最終行目の書き込み期間が終了したら直ちに、一行目から順に次のフレーム期間(またはサブフレーム期間)のアドレス期間に移行する。これによって、発光時間がアドレス期間より短いサブフレーム期間を設けることができる。

[0016]

このように、各サブフレーム期間において発光した時間の積算時間が、1フレーム期間における各々の画素の発光時間となり、これによって階調が表現される。

[0017]

なお、1フレーム期間において、サブフレーム期間はサスティン期間の長いものから順に並んでいるが、必ずしもこのような並びにする必要はなく、例えばサスティン期間の短いサブフレーム期間から順に並べられていてもよいし、またはサスティン期間の長いものと短いものとがランダムに並んでいてもよい。

[0018]

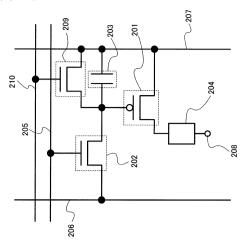

このような駆動方法を実現する従来の表示装置の画素構成を図2に示す。駆動トランジスタ201と、スイッチングトランジスタ202と、容量素子203と、発光素子204と、第1の走査線205と、信号線206と、電源線207と、消去用トランジスタ209と、第2の走査線210と、を有する。なお、駆動トランジスタ201はPチャネル型トランジスタであり、スイッチングトランジスタ202はNチャネル型トランジスタであり、消去用トランジスタ209はNチャネル型トランジスタである。

[0019]

スイッチングトランジスタ202は、ゲート端子が第1の走査線205に接続され、第1端子(ソース端子又はドレイン端子)が信号線206に接続され、第2端子(ソース端子又はドレイン端子)が駆動トランジスタ201のゲート端子と接続されている。また、スイッチングトランジスタ202の第2端子は容量素子203を介して電源線207と接続されている。さらに、駆動トランジスタ201は第1端子(ソース端子又はドレイン端子)が電源線207に接続され、第2端子(ソース端子又はドレイン端子)が発光素子204の第1電極(画素電極)と接続されている。発光素子204の第2の電極(対向電源線207に設定される高電源電位Vssが設定されている。なお、低電源電位Vssとは、電源線207に設定される高電源電位Vdddを基準にしてVss<Vddを満たす電位であり、低電源電位Vssとしては例えばGND、0Vなどが設定されていても良い。この高電源にでVdddと低電源電位Vssとの電位差を発光素子204に印加して、発光素子204に電流を流すことにより発光素子204を発光させるため、高電源電位Vdddと低電源電位Vssとの電位差が発光素子204の順方向しきい値電圧となるようにそれぞれの電位を設定する。

[0020]

また、容量素子203と並列に消去用トランジスタが設けられている。つまり、消去用トランジスタ209の第1端子(ソース端子又はドレイン端子)が駆動トランジスタ201のゲート端子に接続され、第2端子(ソース端子又はドレイン端子)が電源線207に接続されている。また、消去用トランジスタ209のゲート端子は第2の走査線210に接続されている。なお、容量素子203は駆動トランジスタ201のゲート容量を代用して削除しても良い。

[0021]

次に、上述した駆動方法を実現するための画素の動作について説明する。なお、本画素を 有する表示装置は、電圧データによるビデオ信号を画素に書き込むことにより画素の点灯 10

20

30

40

又は非点灯を制御し、点灯の際には画素の発光素子へ電圧を印加することによりその電圧に従った輝度を得る電圧入力電圧駆動方式である。よって、駆動トランジスタ 2 0 1 をスイッチとして動作させることにより、発光素子 2 0 4 に電圧を印加することができる。

## [0022]

まず、画素への信号の書き込み動作について説明する。第1の走査線205で画素が選択されているとき、つまりスイッチングトランジスタ202がオンになっているときに信号線206から画素にビデオ信号を入力する。そして、ビデオ信号に相当する電圧分の電荷が容量素子203に蓄積され、スイッチングトランジスタ202がオフすると容量素子203はその電圧を保持する。この電圧は駆動トランジスタ201のゲート端子と第1端子間の電圧であり、駆動トランジスタ201のゲートソース間電圧Vgsに相当する。

# [0023]

なお、一般に、トランジスタ(ここでは簡単のため、Nチャネル型のトランジスタであるとする)の動作領域は、線形領域と飽和領域とに分けることが出来る。その境目は、ドレインソース間電圧をVds、ゲートソース間電圧をVgs、しきい値電圧をVthとすると、(Vgs・Vth)=Vdsの時になる。 (Vgs・Vth)<Vdsの場合は飽和領域になり、理想的には、Vdsが変化しても、電流値はほとんど変わらない。つまり、Vgsの大きさだけによって電流値が決まる。一方、(Vgs・Vth)>Vdsの場合は、線形領域であり、Vds、Vgsの大きさによって電流値が決まる。そして、線形領域の場合には、Vgsが大きいため、Vdsを小さくすることができる。つまり、ソース端子とドレイン端子の電位をほぼ等しくできる。よって、トランジスタを線形領域で動作させると、トランジスタをスイッチとして機能させることができる。

#### [0024]

よって、本画素のように電圧入力電圧駆動方式場合には、駆動トランジスタ201をスイッチとして機能させるためゲート端子には、駆動トランジスタ201が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を入力する。

## [0025]

よって、画素が点灯するときには、駆動トランジスタ201が線形領域でオンするビデオ信号を信号線206から入力する。すると、駆動トランジスタ201は、ほぼスイッチとして機能するので、理想的には電源線207に設定されている電源電位Vddがそのまま発光素子204の第1の電極に加わるようになる。一方、画素が非点灯であるときには、駆動トランジスタ201が十分にオフするビデオ信号を信号線206から入力する。

# [0026]

つまり、理想的には発光素子204に印加する電圧を一定にし、発光素子204から得られる輝度を一定にする。そして、1フレーム期間内に複数のサブフレーム期間を設け、各サブフレーム期間の信号書き込み期間(アドレス期間)に各画素へのビデオ信号の書き込みを行い、発光期間(サスティン期間)の間、各画素はそのビデオ信号を保持する。そして、ビデオ信号に応じて画素が点灯又は非点灯するようになる。なお、発光時間がアドレス期間より短いサブフレームにおいては、消去期間に各画素に保持された信号を消去する。そして、サブフレーム期間毎に画素の点灯非点灯を制御し、1フレーム期間のうち、点灯している時間の合計によって、階調を表現する。

# [0027]

次に、消去期間における画素へ書き込まれたビデオ信号の消去動作について説明する。第2の走査線210で画素を選択し、消去用トランジスタ209をオンさせることにより、容量素子203に保持された電圧を消去する。つまり、容量素子203に蓄積された電荷を放電し、容量素子203の両電極間の電位を等しくする。こうして、駆動トランジスタ201をオフさせている

## [0028]

しかし、このとき、駆動トランジスタ 2 0 1 が製造ばらつきなどの要因によりノーマリーオン(つまり、ディプレション型トランジスタ)である場合、駆動トランジスタ 2 0 1 の

10

20

30

40

ゲートソース間電圧を等しくしても駆動トランジスタ201に電流が流れてしまい、発光素子204が発光してしまう。よって、画素を非点灯にすることができないため正しく表示を行うことができなくなってしまう。よって、歩留まりの低下を招いてしまうことになる。

## [0029]

ビデオ信号で画素を非点灯にする場合には、ビデオ信号の電位により Vgs>0にすることができるので、駆動トランジスタ 201がノーマリーオンでも対処できる。しかし、図2の画素構成の場合、消去で画素を非点灯にする場合には、Vgs=0としかできない。よって、駆動トランジスタ 201に電流が流れてしまい、発光素子 204が発光してしまう。よって、表示不良を起こしてしまい歩留まりが低下してしまう。

[0030]

そこで、本発明は、製造コストの増加を抑制しつつ、歩留まりの向上を図った表示装置を 提供することを課題とする。

【課題を解決するための手段】

### [0031]

本発明の原理は、消去用の走査線の電位を上げたら、それに応じて駆動トランジスタのゲート端子の電位も上がるようにする。または、走査線の電位を下げたら、それに応じて駆動トランジスタのゲート電位も下がるようにする。例えば、走査線と駆動トランジスタのゲート端子とを整流素子を介して接続する。

[0032]

また、本発明に用いる整流素子は、抵抗素子、PN接合ダイオード、PIN接合ダイオード、ショットキー型のダイオード、ダイオード接続したトランジスタ、カーボンナノチューブで形成されたダイオードのいずれか一又はそれらの組み合わせである。

[0033]

また、整流素子の代わりに、電位伝達素子を用いることもできる。電位伝達素子としては、ゲート端子、第 1 端子及び第 2 端子を有するトランジスタや、該トランジスタと、電流電圧変換素子と、を有し、該トランジスタが、ゲート端子と第 2 端子とが電流電圧変換素子を介して接続されているものであってもいい。

[0034]

また、本発明の半導体装置は、ゲート端子、第1端子及び第2端子をそれぞれ備える第1のトランジスタ、第2のトランジスタ並びに第3のトランジスタと、電流電圧変換素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、電極とを有し、該第1のトランジスタは、第1端子が第1の配線と接続され、ゲート端子が第2の配線と接続され、第2端子が該第2のトランジスタのゲート端子と接続され、該第2のトランジスタは、第1端子が第3の配線と接続され、第2の端子が該電極と接続され、第3のトランジスタは、第1端子が該第2のトランジスタのゲート端子と接続され、ゲート端子が該第4の配線と接続され、第2端子が該電流電圧変換素子を介して該第4の配線と接続されている。

また、本発明の半導体装置は、上記構成において、該電流電圧変換素子は、抵抗素子、PN接合ダイオード、PIN接合ダイオード、ショットキー型のダイオード、トランジスタ、若しくはダイオード接続トランジスタ又はその組み合わせである。

[0036]

[0035]

また、本発明の半導体装置は、上記構成において、該第1のトランジスタ及び該第3のトランジスタはNチャネル型トランジスタであり、該第2のトランジスタはPチャネル型トランジスタである。

# [0037]

また、本発明の表示装置は、ゲート端子、第1端子及び第2端子をそれぞれ備える第1のトランジスタ、第2のトランジスタ並びに第3のトランジスタと、電流電圧変換素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、発光層が画素電極と対向電極で挟み込まれた発光素子と、を有し、該第1のトランジスタは、第1端子が第1の配線

10

20

30

40

20

30

40

50

と接続され、ゲート端子が第2の配線と接続され、第2端子が該第2のトランジスタのゲート端子と接続され、該第2のトランジスタは、第1端子が第3の配線と接続され、第2の端子が該発光素子の画素電極と接続され、第3のトランジスタは、第1端子が該第2のトランジスタのゲート端子と接続され、ゲート端子が該第4の配線と接続され、第2端子が該電流電圧変換素子を介して該第4の配線と接続されている。

### [0038]

また、本発明の表示装置は、上記構成において、該電流電圧変換素子は、抵抗素子、PN接合ダイオード、PIN接合ダイオード、ショットキー型のダイオード、トランジスタ、若しくはダイオード接続トランジスタ又はその組み合わせである。

#### [0039]

また、本発明の表示装置は、上記構成において、該第1のトランジスタ及び該第3のトランジスタはNチャネル型トランジスタであり、該第2のトランジスタはPチャネル型トランジスタである。

## [0040]

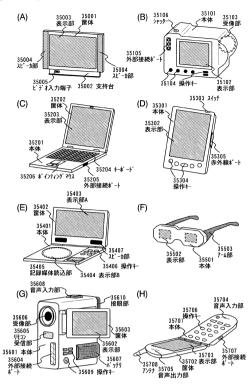

また、本発明の電子機器は、上記構成の表示装置を表示部に有する。

#### [0041]

なお、本発明に示すスイッチは、様々な形態のものを用いることができ、一例として、 電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるもので あればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トラ ンジスタでもよいし、ダイオード (PNダイオード、PINダイオード、ショットキーダ イオード、ダイオード接続のトランジスタなど)でもよいし、それらを組み合わせた論理 回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは 、単なるスイッチとして動作するため、トランジスタの極性(導電型)は特に限定されな い。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジ スタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設 けているものやマルチゲート構造にしているもの等がある。また、スイッチとして動作さ せるトランジスタのソース端子の電位が、低電位側電源(Vss、GND、0Vなど)に 近い状態で動作する場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源 (Vddなど)に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜ なら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして、動作しやすい からである。なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチ にしてもよい。CMOS型のスイッチにすると、スイッチを介して出力する電圧(つまり 入力電圧)が、出力電圧に対して、高かったり、低かったりして、状況が変化する場合に おいても、適切に動作を行うことが出来る。

## [0042]

なお、本発明において、接続されているとは、電気的に接続されている場合と直接接続されている場合とを含むものとする。したがって、本発明が開示する構成において、所定の接続関係に加え、その間に電気的な接続を可能とする他の素子(例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど)が配置されていてもよい。あるいは、間に他の素子を挟まずに、配置されていてもよい。なお、電気的な接続を可能とする他の素子を間に介さずに接続されていて、直接接続されている場合のみを含む場合であって、電気的に接続されている場合を含まない場合には、直接接続されている、あるいは、直接的に接続されている、と記載するものとする。なお、電気的に接続されている、と記載する場合は、電気的に接続されている場合と直接接続されている場合とを含むものとする。

# [0043]

なお、発光素子は、様々な形態を用いることが出来る。例えば、EL素子(有機EL素子、無機EL素子又は有機物材料及び無機材料を含むEL素子)、電子放出素子、液晶素子、電子インク、光回折素子、放電素子、微小鏡面素子(DMD:Digital Micromirror Device)、圧電素子、カーボンナノチューブなど、電気磁気的

20

30

40

50

作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いたELパネル方式の表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッションディスプレイ(FED:Field Emission Display)やSED方式平面型ディスプレイ(SED:Surface‐conduction Electron‐emitter Disply)など、液晶である。でのは、たっぱでレーティンであれては電子ペーパー、光回折素子を用いた表示装置としては電子ペーパー、光回折素子を用いた表示装置としてはグレーティンでライトバルブ(GLV)方式のディスプレイ、放電素子を用いたDMDパネル方式の表示装置としてはデジタル・フィスプレイ、微小鏡面素子を用いたDMDパネル方式の表示装置としてはデジタル・フィスプレイ、微小鏡面素子を用いたDMDパネル方式の表示装置としてはナノ放射ディスプレイ(NED:Nano Emissive Display)、などがある。

[0044]

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(接合型トランジスタ、接合型トランジスタ、接合型トランジスタを適用でおいて形成されるMOS型トランジスタ、接合型トランジスタを適用であるでは、できる。なができる。なができる。なお、非単結晶半導体膜には水素またはののトランジスタを適用することができる。なお、非単結晶半導体膜には水素または、かったのでき、特定のものに限定されることはない。従って例えば、単結晶をのを用いることができ、特定のものに限定されることはない。従って例えば、単結晶をあることができる。また、ある基板でトランジスタを形成し、その後、別の基板とに配置することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板とにシンジスタを移動させて、別の基板上に配置するようにしてもよい。

[0045]

なお、すでに述べたように、本発明におけるトランジスタは、様々なタイプを用いること ができ、様々な基板上に形成させることができる。したがって、回路の全てが、ガラス基 板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし、単結晶基 板に形成されていてもよいし、SOI基板上に形成されていてもよいし、どのような基板 上に形成されていてもよい。回路の全てが形成されていることにより、部品点数を減らし てコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすること ができる。あるいは、回路の一部が、ある基板に形成されており、回路の別の一部が、別 の基板に形成されていてもよい。つまり、回路の全てが同じ基板上に形成されていなくて もよい。例えば、回路の一部は、ガラス基板上にトランジスタを用いて形成し、回路の別 の一部は、単結晶基板上に形成し、そのICチップをCOG(Chip On Glas s ) で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB(T ape Auto Bonding)やプリント基板を用いてガラス基板と接続してもよ い。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らし てコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすること ができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなっ てしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力の向上を 防ぐことができる。

[0046]

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート本数が2本以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても

20

30

40

50

、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造でもより、電流値を大きくしたり、空乏層ができやすくなってS値(サブスレッショルド係数)をよくしたりもることができる。また、チャネルの上にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、正スタガ構造であってもよいし、近スタガ構造でもよいし、チャネル領域が複数の領域に分かれていてもよいし、はその一分にソース電極やドレイン電極が重なっていてもよい。チャネル(もしくはその一部)にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域を設けることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

#### [0047]

なお、本発明においては、一画素とは、明るさを制御できる要素一つ分を示すものとする 。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで 明るさを表現する。従って、そのときは、R(赤)G(緑)B(青)の色要素からなるカ ラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素 から構成されるものとする。なお、色要素は、三色に限定されず、それ以上でもよく、例 えば、RGBW(Wは白)がある。また、別の例としては、1つの色要素について、複数 の領域を用いて明るさを制御する場合は、その領域一つ分を一画素とする。よって、一例 としては、面積階調を行う場合、一つの色要素につき、明るさを制御する領域が複数あり 、その全体で階調を表現するわけであるが、明るさを制御する領域の一つ分を一画素とす る。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。また、 その場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。また 、一つの色要素につき複数ある、明るさを制御する領域において、つまり、一つの色要素 を構成する複数の画素において、各々に供給する信号を僅かに異ならせるようにして、視 野角を広げるようにしてもよい。なお、一画素(三色分)と記載する場合は、RとGとB の三画素分を一画素と考える場合であるとする。一画素(一色分)と記載する場合は、・ つの色要素につき、複数の画素がある場合、それらをまとめて一画素と考える場合である とする。

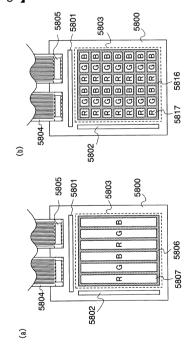

### [0048]

なお、本発明において、画素がマトリクスに配置されているとは、ドットが縦縞と横縞を組み合わせたいわゆる格子状に配置され、色要素毎にストライプ配置されている場合はもちろんのこと、三色の色要素(例えばRGB)でフルカラー表示を行う場合に、三つの色要素のドットがいわゆるデルタ配置されている場合も含むものとする。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW(Wは白)がある。また、色要素のドット毎にその発光領域の大きさが異なっていてもよい。

# [0049]

また、トランジスタとは、少なくとも三端子を有する素子である。例えば、トランジスタはそれぞれ、ゲート電極と、ドレイン領域と、ソース領域とを含む少なくとも三端子の素子であり、ドレイン領域とソース領域の間にチャネル領域を有する。ここで、ソース領域とドレイン領域とは、トランジスタの構造や動作条件等によって変わるため、いずれがソース領域またはドレイン領域であるかを限定することが困難である。そこで、本明細書においては、ゲート電極をゲート端子、ソースまたはドレインとして機能する領域を、それぞれ第1端子、第2端子と表記する。

#### [0050]

なお、ゲートとは、ゲート電極とゲート配線 (ゲート線またはゲート信号線等とも言う)

20

30

40

50

とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域やLDD(Lightly Doped Drain)領域などを形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。ゲート配線とは、各画素のゲート電極の間を接続したり、ゲート電極と別の配線とを接続したりするための配線のことを言う。

# [0051]

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

## [0052]

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル領域とオーバーラップしていなかったり、別のゲート電極と接続させる機能を有してなかったりする場合がある。しかし、製造マージンなどの関係で、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線とつながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んでも良い。

#### [0053]

また、例えば、マルチゲートのトランジスタにおいて、1つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。

また、例えば、ゲート電極とゲート配線とを接続してさせている部分の導電膜も、ゲート 電極と呼んでも良いし、ゲート配線と呼んでも良い。

### [0054]

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域 について、その一部分のことを言う。

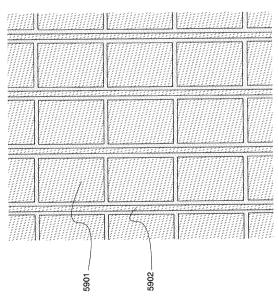

## [0055]

なお、ソースとは、ソース領域とソース電極とソース配線(ソース線またはソース信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物(ボロンやガリウムなど)やN型不純物(リンやヒ素など)が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD(Lightly Doped Drain)領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間を接続したり、ソース電極と別の配線とを接続したりするための配線のことを言う。

# [0056]

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能していることになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い

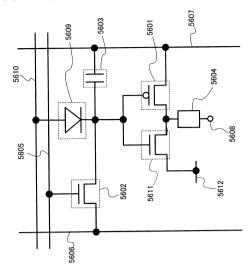

## [0057]

また、ソース電極と同じ材料で形成され、ソース電極とつながっている部分や、あるソース電極と別のソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしており、ソース電極とつながっている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、以ース配線と呼んでも良い。このような領域は、厳密な意味では、あるソース電極と別のソース電極とを接続させる機能を有していない場合がある。しかし、このような領域は、製造マージンなどの関係で、ソース電極やソース配線と同じ材料で形成され、いずれかのソース電極やソース配線とつながっている。よって、そのような領域もソース電極やソース配線と呼んでも良い。

10

### [0058]

また、例えば、ソース電極とソース配線とを接続してさせている部分の導電膜も、ソース 電極と呼んでも良いし、ソース配線と呼んでも良い。

#### [0059]

なお、ソース端子とは、ソース領域の領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。

#### [0060]

なお、ドレインについては、ソースと同様である。

[0061]

20

なお、本発明において、半導体装置とは半導体素子(トランジスタやダイオードなど)を含む回路を有する装置をいう。また、半導体特性を利用することで機能しうる装置全般でもよい。また、表示装置とは、表示素子(液晶素子や発光素子など)を有する装置のことを言う。なお、基板上に液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が形成された表示パネル本体のことでもよい。さらに、フレキシブルプリントサーキット(FPC)やプリント配線基盤(PWB)が取り付けられたものも含んでもよい。また、発光装置とは、特にEL素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。

[0062]

30

なお、本明細書において、トランジスタをオフにしたときにわずかに流れてしまう電流や 、整流素子の逆方向電流を併せてオフ電流ともいう。

#### 【発明の効果】

## [0063]

本発明により、整流素子や、トランジスタに流れるオフ電流を低減することができる。よて、非点灯(黒表示)にする信号が入力されている画素の発光素子が、わずかに光ってしまうのを防ぐことができる。

## [0064]

また、製造工程を増加することなく、トランジスタや整流素子のオフ電流を低減ため、製造コストの増加を抑制しつつ、歩留まりの向上を図った表示装置を提供することができる

40

#### [0065]

また、その表示装置を表示部に有する電子機器を提供することが可能となる。

# 【図面の簡単な説明】

#### [0066]

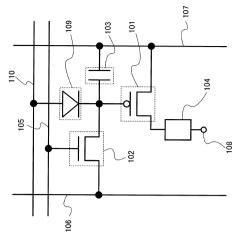

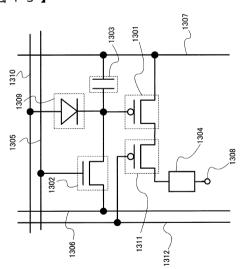

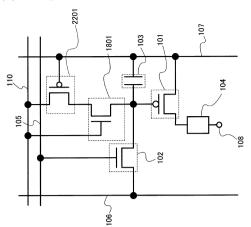

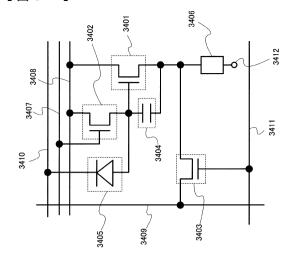

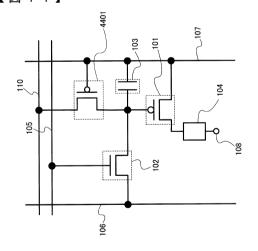

【図1】本発明の画素構成を示す図。

【図2】従来の画素構成を説明する図。

【図3】本発明の画素構成を示す図。

【図4】本発明の画素構成を示す図。

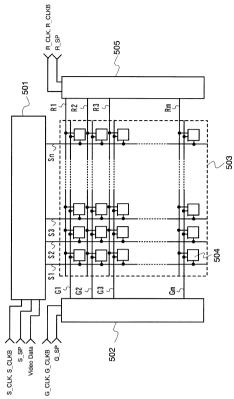

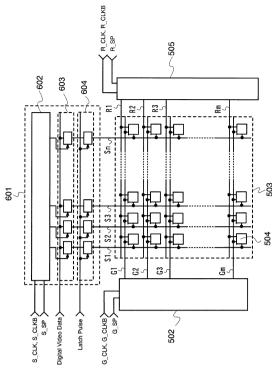

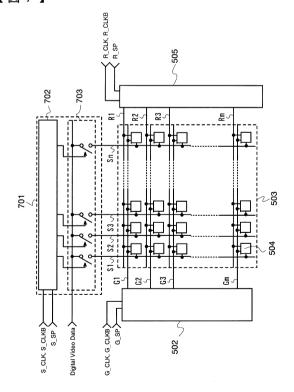

【図5】本発明の画素構成を有する表示装置を示す図。

20

30

40

```

【図6】本発明の画素構成を有する表示装置を示す図。

```

- 【図7】本発明の画素構成を有する表示装置を示す図。

- 【図8】タイミングチャートを示す図。

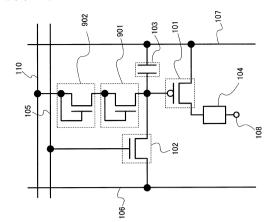

- 【図9】本発明の画素構成を示す図。

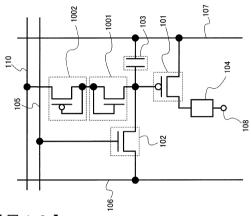

- 【図10】本発明の画素構成を示す図。

- 【図11】本発明の画素構成を示す図。

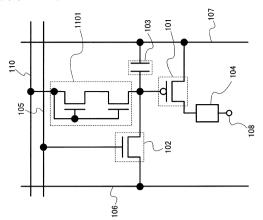

- 【図12】本発明の画素構成を示す図。

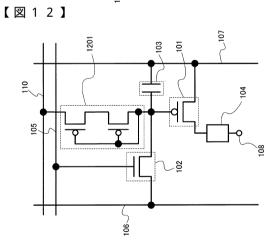

- 【図13】本発明の画素構成を示す図。

- 【図14】画素のレイアウトを説明する図。

- 【図15】本発明の画素の部分断面図。

- 【図16】本発明の画素構成を示す図。

- 【図17】本発明の画素構成を示す図。

- 【図18】本発明の画素構成を示す図。

- 【図19】本発明の画素構成を示す図。 【図19】本発明の画素構成を示す図。

- 【図20】本発明の画素構成を示す図。

- 【図21】本発明の画素構成を示す図。

- 【図22】本発明の画素構成を示す図。

- 【図23】画素のレイアウトを説明する図。

- 【図24】画素のレイアウトを説明する図。

- 【図25】本発明の画素の動作を説明する図。

- 【図26】(a)本発明の画素の部分断面図、(b)画素レイアウトの部分拡大図。

- 【図27】(a)本発明の画素の部分断面図、(b)画素レイアウトの部分拡大図。

- 【図28】発光素子を説明する図。

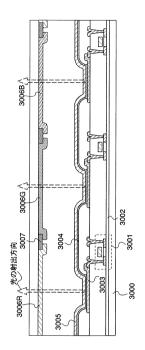

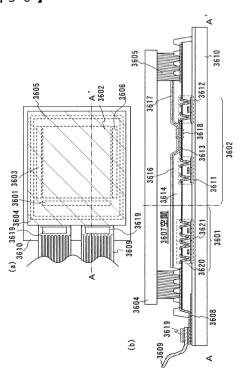

- 【図29】表示パネルの部分断面図。

- 【図30】表示パネルの部分断面図。

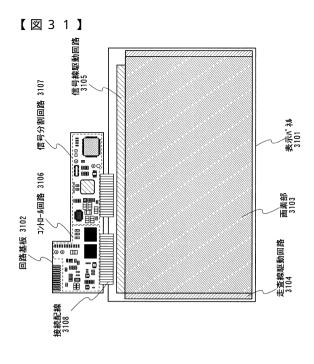

- 【図31】ELモジュールを示す図。

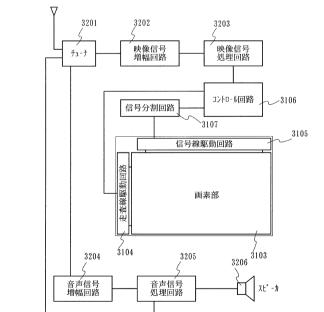

- 【図32】ELテレビ受像機の主要な構成を示す図。

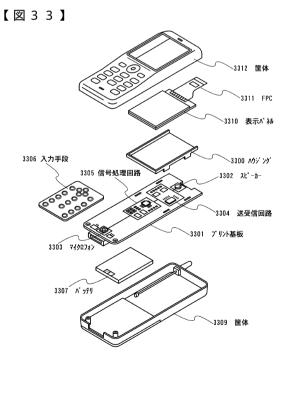

- 【図33】携帯電話機の構成例を示す図。

- 【図34】本発明の画素構成を示す図。

- 【図35】本発明の適用可能な電子機器の例。

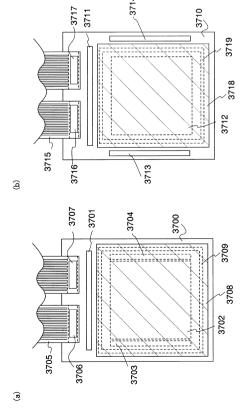

- 【図36】本発明の表示パネルの例。

- 【図37】本発明の表示パネルの例。

- 【図38】本発明の表示装置の例。

- 【図39】(a)本発明の表示パネルの例、(b)本発明の表示装置の例。

- 【図40】本発明の画素構成を示す図。

- 【図41】本発明の画素構成を示す図。

- 【図42】本発明の画素構成を示す図。

- 【図43】本発明の画素構成を示す図。

- 【図44】本発明の画素構成を示す図。

- 【図45】本発明の画素構成を示す図。 【図46】本発明の画素構成を示す図。

- 【図47】本発明の画素構成を示す図。

- 【図48】タイミングチャートを示す図。

- 【図49】本発明の画素構成を示す図。

- 【図50】本発明の画素構成を示す図。

- 【図51】本発明の画素構成を示す図。

- 【図52】第1の走査線の信号とビデオ信号の電位を説明する図。

- 【図53】本発明の画素構成を示す図。

- 【図54】本発明の画素構成を示す図。

- 【図55】本発明の画素構成を示す図。

- 【図56】本発明の画素構成を示す図。

- 【図57】本発明の画素構成の部分断面を示す図。

- 【図58】(a)本発明の表示パネルの構成を示す模式図、(b)本発明の表示パネルの構成を示す模式図。

- 【図59】本発明の表示パネルの画素部の模式図。

- 【図60】本発明の表示パネルの画素部の模式図。

- 【図61】第2の走査線の信号とビデオ信号の電位を説明する図。

- 【図62】第1の走査線の信号と第2の走査線の信号とビデオ信号の電位を説明する図。

【発明を実施するための形態】

[0067]

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

[0068]

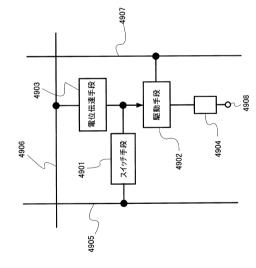

本発明の画素の基本構成について、図49を用いて説明する。

[0069]

図49に示す画素は、スイッチ手段4901、駆動手段4902、電位伝達手段4903、発光素子4904、信号線4905、走査線4906、電源線4907を有している。スイッチ手段4901は、信号線4905と駆動手段4902の制御端子との導通又は非導通を制御する。駆動手段4902は、制御端子に入力される信号にしたがって、発光素子4904の駆動を制御する。つまり、駆動手段4902の制御端子に画素を点灯させる信号が入力されているときには、電源線4907から発光素子4904へ電源を供給する。また、駆動手段4902の制御端子に画素を非点灯とする信号が入力されているときには、電源線4907から発光素子4904の対向電極4908には所定の電位が供給されている。

[0070]

また、電位伝達手段 4 9 0 3 は走査線 4 9 0 6 と駆動手段 4 9 0 2 の制御端子との間に接続され、走査線 4 9 0 6 に入力される信号(電位)に従って、駆動手段 4 9 0 2 の制御端子への電位の供給を制御する。そして、この走査線 4 9 0 6 に入力される電位の大きさにより、駆動手段 4 9 0 2 の制御端子に入力される電位の大きさも変化する。

[0071]

続いて画素の動作について説明する。

[0072]

画素への信号の書き込みの際には、スイッチ手段4901が導通し、信号線4905に入力されるビデオ信号(電位)が駆動手段4902の制御端子に入力される。こうして、画素への信号の書き込みが終了する。そして、駆動手段4902は制御端子に入力された信号を保持する。

[0073]

そして、駆動手段4902の制御端子に入力された信号にしたがって、発光素子4904 は、発光状態又は非発光状態となる。つまり、画素が点灯状態又は非点灯状態となる。

[0074]

画素の消去動作の際には、走査線4906に信号が入力される。この信号は電位情報の信号であり、駆動手段4902が電源線4907から発光素子4904へ電源を供給しないようにするために、十分な電位を駆動手段4902の制御端子に入力する。こうして、駆動手段4902から漏れて電源が発光素子4904へ供給されないようにする。

[0075]

(実施の形態1)

本実施の形態では、電位伝達手段として整流素子を適用した場合の画素構成と、その画素を有する表示装置について説明する。

10

20

30

40

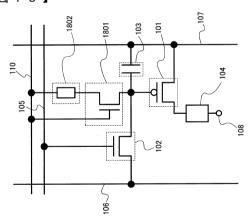

#### [0076]

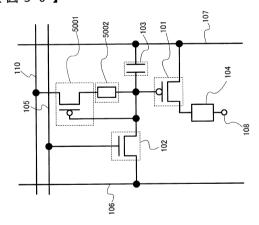

まず、本実施の形態の基本的な画素構成について図1を用いて説明する。ここでは、一画素のみを図示しているが、表示装置の画素部には行方向と列方向にマトリクスに複数の画素が配置されている。

## [0077]

図1に示す画素は、駆動トランジスタ101、スイッチングトランジスタ102、容量素 子103、発光素子104、第1の走査線105、信号線106、電源線107、整流素 子109、第2の走査線110を有している。なお、駆動トランジスタ101はPチャネ ル型トランジスタであり、スイッチングトランジスタ102はNチャネル型トランジスタ である。スイッチングトランジスタ102は、ゲート端子が第1の走査線105に接続さ れ、第1端子(ソース端子又はドレイン端子)が信号線106に接続され、第2端子(ソ 一ス端子又はドレイン端子)が駆動トランジスタ101のゲート端子と接続されている。 さらに、駆動トランジスタ101のゲート端子は整流素子109を介して第2の走査線1 10と接続されている。また、スイッチングトランジスタ102の第2端子は容量素子1 03を介して電源線107と接続されている。また、駆動トランジスタ101は、第1端 子(ソース端子又はドレイン端子)が電源線107に接続され、第2端子(ソース端子又 はドレイン端子)が発光素子104の第1の電極(画素電極)と接続されている。発光素 子104の第2の電極(対向電極)108には低電源電位が設定されている。なお、低電 源電位とは、電源線107に設定される高電源電位を基準にして低電源電位<高電源電位 を満たす電位であり、低電源電位としては例えばGND、0Vなどが設定されていても良 い。この高電源電位と低電源電位との電位差を発光素子104に印加して、発光素子10 4に電流を流して発光素子104を発光させるため、高電源電位と低電源電位との電位差 が発光素子104の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

#### [0078]

なお、容量素子103は、駆動トランジスタ101のゲート電位を保持できる場所に接続すればよく、例えば、容量素子103は、一方の電極を駆動トランジスタ101のゲート端子、他方の電極を電源線107とは異なる別の配線に接続してもよい。また、容量素子103は駆動トランジスタ101のゲート容量を代用して削除しても良い。

## [0079]

続いて、画素の動作について説明する。

### [0800]

画素への信号の書き込みの際には、第1の走査線105にスイッチングトランジスタ102がオンするHレベルの信号を入力する。すると、スイッチングトランジスタ102がオンし、信号の書き込みを行う画素が選択される。そして、信号線106から画素にビデオ信号が書き込まれる。つまり、ビデオ信号に相当する電圧分の電荷が容量素子103に蓄積される。そして、第1の走査線105をLレベルにし、スイッチングトランジスタ102がオフすると容量素子103はその電圧を保持する。なお、駆動トランジスタ101のゲート端子と第1端子との間の電圧が、駆動トランジスタ101のゲートソース間電圧Vgsに相当する。

## [0081]

ここで、電圧入力電圧駆動方式の場合には、駆動トランジスタ101のゲート端子には、駆動トランジスタ101が十分にオンするか、オフするかの二つの状態となるようなビデオ信号(オンするときVsig(L)、オフするときVsig(H))を入力する。つまり、駆動トランジスタ101は線形領域で動作させる。つまり、スイッチとして動作させる。

# [0082]

# [0083]

10

20

30

20

30

40

50

なお、第1の走査線105のHレベルの信号は、画素を非点灯にするビデオ信号(駆動トランジスタ101をオフにするゲート電位Vsig(H))よりもスイッチングトランジスタ102のしきい値電圧Vth分以上高い電位V1とすることが望ましい。なぜなら、スイッチングトランジスタ102はNチャネル型のトランジスタであるため、信号線106にVsig(H)が入力されると、第1端子がドレイン端子となる。したがって、スイッチングトランジスタ102は、第2端子(このときにはソース端子)がゲート端子の電位より、スイッチングトランジスタ102のしきい値電圧Vth分低い電位でオフしてしまう。つまり、スイッチングトランジスタ102のゲート電位がV1より小さいと、信号線106に入力されたVsig(H)を駆動トランジスタ101のゲート端子に入力することができなくなってしまうからである。すると、駆動トランジスタ101を完全にオフにすることができず、発光素子104がわずかに発光してしまうことがある。

[0084]

また、第1の走査線105のLレベルの信号は、Vsig(L)よりも低い電位とすることが望ましい。例えば、第1の走査線105のLレベルの信号が、画素を点灯にするビデオ信号(駆動トランジスタ101がオンするゲート電位Vsig(L))と等しい電位である場合、Vsig(H)が書き込まれている画素は、他の行の画素への信号書き込みのために信号線106にVsig(L)が入力されると、スイッチングトランジスタ102のゲートソース間電圧は0Vとなる。すると、スイッチングトランジスタ102がノーマリーオンとなってしまっているときにはオフ電流が流れてしまう。したがって、容量素子103に蓄積された電荷が放電し、駆動トランジスタ101のゲート電位が低くなることにより、駆動トランジスタ101に電流が流れ、発光素子104がわずかに発光してしまうことがある。

[0085]

次に、消去動作について説明する。消去動作時には、第2の走査線110にHレベルの信号を入力する。すると、整流素子109に電流が流れ、容量素子103によって保持されていた駆動トランジスタ101のゲート電位がある所定の電位になるようにすることができる。つまり、駆動トランジスタ101のゲート端子の電位が、所定の電位になるようにし、信号書き込み期間に画素へ書き込まれたビデオ信号に関わらず、駆動トランジスタ101を強制的にオフさせることができる。なお、駆動トランジスタ101のゲート端子の電位は第2の走査線110よりも整流素子109のしきい値電圧分低い電位となる。

[0086]

このとき、第2の走査線110に入力するHレベルの信号は、電源線107に入力される高電源電位以上の電位とすることが望ましい。このHレベルの信号の電位を適宜設定することにより、消去期間において駆動トランジスタ101を強制的にオフさせる場合に、駆動トランジスタ101のゲート端子の電位をソース端子の電位よりも高くすることができる。したがって、駆動トランジスタ101がノーマリーオンの場合でも駆動トランジスタ101をオフにし、発光素子104がわずかに発光してしまうのを防ぐことができる。

[0087]

なお、第2の走査線110のHレベルは、第1の走査線105のHレベルと同じでもよい。その結果、電源数を削減することができる。

[ 0 0 8 8 ]

なお、消去動作時以外は、第2の走査線110はLレベルの信号とする。このLレベルの信号の電位は、画素を点灯とするビデオ信号(駆動トランジスタ101をオンにするゲート電位Vsig(L))以下の電位とすることが望ましい。しかし、このLレベルの電位を低くし過ぎると、画素に非点灯のビデオ信号(駆動トランジスタ101をオフにするゲート電位Vsig(H))が書き込まれていた場合に、整流素子109に印加される逆バイアス電圧が大きくなってしまうことにより、整流素子109へ流れるオフ電流(逆方向電流ともいう)が大きくなってしまい、容量素子103に保持した電荷が漏れてしまう。そして、駆動トランジスタ101のゲート電位が低くなり、駆動トランジスタ101のオフ電流が大きくなってしまう。よって、好ましくは、このLレベルの信号の電位は、画素

20

30

40

50

を点灯にするビデオ信号(駆動トランジスタ101をオンにするゲート電位Vsig(L))と等しくするとよい。

## [0089]

なお、消去動作時とは、その画素に書き込まれたビデオ信号を消去するときのことであり、図 8 で示したタイミングチャートにおいての消去時間Teに相当する。また、消去期間とは、その画素への消去動作後から次にその画素へ信号の書き込みを行うまでの期間であり、図 8 で示したタイミングチャートにおいての消去期間Te4に相当する期間である。

## [0090]

また、本発明の画素は、図40に示すように、容量素子103の一方の電極を駆動トランジスタ101のゲート端子と接続し、他方の電極を第2の走査線110に接続してもよい。画素にビデオ信号の書き込みを行い、画素がその信号を保持する間は、第2の走査線110はLレベルに保たれている。よって、駆動トランジスタ101のゲート電位を保持することができる。そして、消去動作時には、第2の走査線110をHレベルにする。第2の走査線110をHレベルにすると、容量素子103の一方の電極の電位も高くなる。そのため、すばやく駆動トランジスタ101をオフにし易くすることができる。そして、駆動トランジスタ101をオフにする所定の電位となるまで整流素子109に電流が流れる。つまり、画素に書き込まれたビデオ信号を消去することができる。そして、消去期間の間ずっと第2の走査線110をHレベルにしておく。

## [0091]

また、図1でも、消去期間の間ずっと第2の走査線110をHレベルにしていてもよい。ずっと、Hレベルにしておくと、電荷の漏れにより駆動トランジスタ101のゲート電位が下がってしまうということを避けることができる。

# [0092]

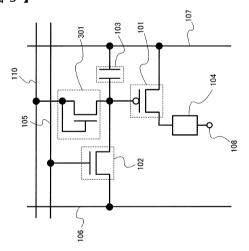

なお、整流素子109には、ダイオード接続したトランジスタを用いることが可能である。さらに、ダイオード接続したトランジスタの他にも、PN接合やPIN接合のダイオードやショットキー型のダイオードやカーボンナノチューブで形成されたダイオードなどを用いてもよい。

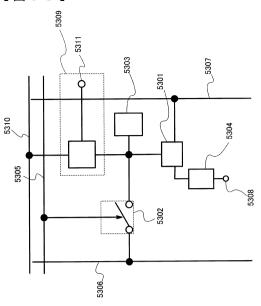

#### [0093]

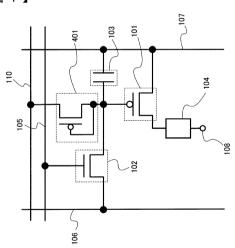

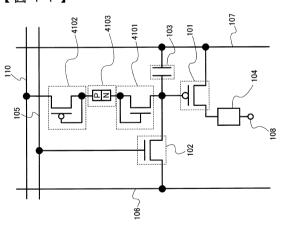

また、整流素子109へダイオード接続したNチャネル型のトランジスタを適用した場合の画素構成を図3に示す。ダイオード接続トランジスタ301の第1端子(ソース端子又はドレイン端子)を駆動トランジスタ101のゲート端子と接続する。また、ダイオード接続トランジスタ301の第2端子(ソース端子又はドレイン端子)をゲート端子と接続するとともに、第2の走査線110に接続する。すると、第2の走査線110がLレベルのときにはダイオード接続トランジスタ301の第2端子はソース端子となり、ゲート端子とソース端子が接続されているため電流が流れないが、第2の走査線110にHレベルの信号を入力したときにダイオード接続トランジスタ301の第2端子はドレイン端子となるためダイオード接続トランジスタ301に電流が流れる。よって、ダイオード接続トランジスタ301は整流作用を奏する。

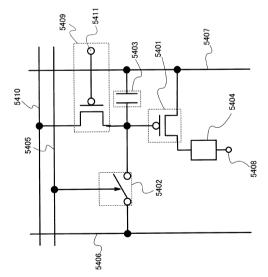

## [0094]

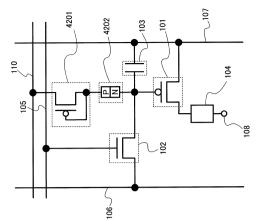

また、ダイオード接続した P チャネル型トランジスタを適用した場合の画素構成を図4に示す。ダイオード接続トランジスタ401の第1端子(ソース端子又はドレイン端子)を第2の走査線110に接続する。また、ダイオード接続トランジスタ401は、第2端子(ソース端子又はドレイン端子)をゲート端子と接続するとともに、駆動トランジスタ101のゲート端子と接続する。すると、第2の走査線110がLレベルのときにはダイオード接続トランジスタ401はゲート端子とソース端子が接続されているため電流が流れないが、第2の走査線110にHレベルの信号を入力したときにダイオード接続トランジスタ401の第2端子はドレイン端子となるため電流が流れる。よって、ダイオード接続トランジスタ401は整流作用を奏する。

## [0095]

なお、このとき、第2の走査線110に入力するHレベルの信号の電位は、電源線107

20

30

40

50

の電位よりも高い電位とすることが望ましい。すると、駆動トランジスタ101のオフ電流を小さくすることができる。また、第2の走査線110に入力するLレベルの信号の電位は、画素を点灯とするビデオ信号(駆動トランジスタ101をオンにするゲート電位Vsig(L))以下の電位とすることが望ましい。しかし、このLレベルの電位をあまり低くし過ぎると画素に非点灯のビデオ信号(駆動トランジスタ101をオフにする電位Vsig(H))が書き込まれていた場合に、ダイオード接続トランジスタ301、401のドレインソース間電圧が大きくなってしまいオフ電流が大きくなってしまう。よって、好ましくは、このLレベルの電位は、画素を非点灯にするビデオ信号(駆動トランジスタ101をオンにするゲート電位Vsig(L))と等しくするとよい。

## [0096]

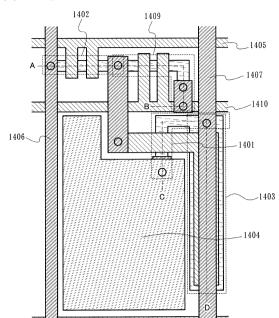

ここで、図3の画素のレイアウトの一例を図14に示す。画素は、駆動トランジスタ14 0 1 、スイッチングトランジスタ1 4 0 2 、容量素子1 4 0 3 、画素電極1 4 0 4 、第1 の走査線 1 4 0 5 、信号線 1 4 0 6 、電源線 1 4 0 7 、ダイオード接続トランジスタ 1 4 09、第2の走査線1410を有している。スイッチングトランジスタ1402は、ゲー ト端子が第1の走査線1405の一部分で構成され、第1端子(ソース端子又はドレイン 端子)が信号線1406に接続され、第2端子(ソース端子又はドレイン端子)が駆動ト ランジスタ1401のゲート端子と接続されている。また、ダイオード接続トランジスタ 1409は、ゲート端子が第2の走査線1410の一部で構成され、第1端子(ソース端 子又はドレイン端子)が駆動トランジスタ1401のゲート端子と接続され、第2端子( ソース端子又はドレイン端子)が第2の走査線1410と接続されている。また、駆動ト ランジスタ1401は、第1端子(ソース端子又はドレイン端子)が電源線1407に接 続され、第2端子(ソース端子又はドレイン端子)が画素電極1404と接続されている 。また、駆動トランジスタ1401のゲート端子を構成する電極の一部を第1の電極とし 駆動トランジスタ1401の第1端子となる不純物領域(ソース領域又はドレイン領域 )と同じ層の半導体層と電源線1407の一部とで第2の電極とする、容量素子1403 が形成されている。なお、図14の画素レイアウトは、図3の画素におけるレイアウトの 一例であってこれに限定されない。図14の駆動トランジスタ1401、スイッチングト ランジスタ1402、容量素子1403、第1の走査線1405、信号線1406、電源 線1407、ダイオード接続トランジスタ1409、第2の走査線1410は、それぞれ 図3の駆動トランジスタ101、スイッチングトランジスタ102、容量素子103、第 1 の走査線 1 0 5 、信号線 1 0 6 、電源線 1 0 7 、ダイオード接続トランジスタ 3 0 1 、 第2の走査線110に相当する。また、画素電極1404上に発光層と対向電極が形成さ れることにより、図3に示す発光素子104が完成する。

# [0097]

なお、画素の構造をより詳しく説明するため、破線 A B 間の断面図を図 1 5 ( a )、破線 C D 間の断面図を図 1 5 ( b )に示す。

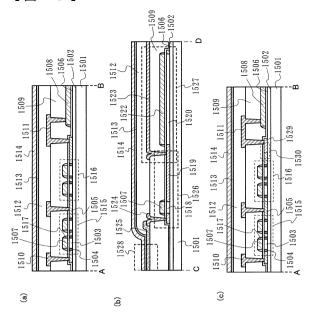

# [0098]

図15(a)、(b)の断面図について説明する。基板1501上に下地膜1502を有している。基板1501としてはガラス基板、石英基板、プラスチック基板、セラミックス基板等の絶縁性基板、金属基板、半導体基板等を用いることができる。下地膜1502はCVD法やスパッタ法により形成することができる。例えばSiH $_4$ 、N $_2$ О、NH $_3$ を原料に用いたCVD法により形成した酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を適用することができる。また、これらの積層を用いても良い。なお、下地膜1502は基板1501から不純物が半導体層に拡散することを防ぐために設けるものであり、基板1501にガラス基板や石英基板を用いている場合には下地膜1502は設けなくてもよい。

# [0099]

下地膜1502上に島状の半導体層を有する。半導体層にはN型のチャネルが形成されるチャネル形成領域1503、N型のトランジスタのソース領域又はドレイン領域となる不純物領域1505、低濃度不純物領域(LDD領域)1504、P型のチャネルが形成されるチャネル形成領域1518、P型のトランジスタのソース領域又はドレイン領域とな

20

30

40

50

る不純物領域1519、容量素子1527の第1電極の一部を構成する半導体層1520が形成されている。そして、チャネル形成領域1503、チャネル形成領域1518及び半導体層1520上にゲート絶縁膜1506を介してゲート電極1507及び第1の配線1508及び第2の配線1522を有している。ゲート絶縁膜1506としてはCVD法やスパッタ法により形成される酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を用いることができる。また、ゲート電極1507、第1の配線1508及び第2の配線1522としてはアルミニウム(A1)膜、銅(Cu)膜、アルミニウム又は銅を主成分とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル(TaN)膜、チタン(Ti)膜、タングステン(W)膜、モリブデン(Mo)膜等を用いることができる。

## [0100]

ゲート電極 1 5 0 7 の脇にはサイドウォール 1 5 1 7 が形成されている。ゲート電極 1 5 0 7 を覆うようにシリコン化合物、例えば、酸化シリコン膜、窒化シリコン膜若しくは酸化窒化シリコン膜を形成した後、エッチバックしてサイドウォール 1 5 1 7 を形成することができる。

## [0101]

なお、 L D D 領域 1 5 0 4 はサイドウォール 1 5 1 7 の下部に位置している。つまり、自己整合的に L D D 領域 1 5 0 4 が形成されている。

## [0102]

ゲート電極1507、第1の配線1508、第2の配線1522、サイドウォール1517およびゲート絶縁膜1506上には層間絶縁膜1509を有している。層間絶縁膜1509は下層に無機絶縁膜、上層に樹脂膜を有している。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

#### [0103]

また、層間絶縁膜1509上には、第3の配線1510と第4の配線1511と第5の配 線 1 5 2 4 と第 6 の配線 1 5 2 3 と画素電極 1 5 2 5 を有している。なお、第 3 の配線 1 510はコンタクトホールを介して不純物領域1505と電気的に接続されている。また 、第4の配線1511は、コンタクトホールを介して、不純物領域1505と第1の配線 1508と接続されている。また、第5の配線1524はコンタクトホールを介して不純 物領域1519と接続されている。また、第3の配線1510や第4の配線1511や第 5 の配線 1 5 2 4 や第 6 の配線 1 5 2 3 としては、チタン(Ti)膜やアルミニウム(A 1)膜や銅(Cu)膜やTiを含むアルミニウム膜などを用いることができる。なお、第 3 の配線 1 5 1 0 や第 4 の配線 1 5 1 1 や第 5 の配線 1 5 2 4 や第 6 の配線 1 5 2 3 と同 じ層に信号線などの配線を設ける場合には低抵抗な銅を用いるとよい。また、画素電極 1 5 2 5 に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、 窒化チタン(TiN)膜、クロム(Cr)膜、タングステン(W)膜、亜鉛(Zn)膜、 プラチナ(Pt)膜などの単層膜の他、窒化チタン膜とアルミニウムを主成分とする膜と の積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を 用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミ ックコンタクトがとれ、さらに陽極として機能させることができる。光を反射する金属膜 を用いることで光を透過させない陽極を形成することができる。

## [0104]

第3の配線1510、第4の配線1511、第5の配線1524、第6の配線1523及び層間絶縁膜1509上であって画素電極1525の端部を覆って絶縁物1512が形成されている。絶縁物1512としては、例えば、ポジ型の感光性アクリル樹脂膜を用いることができる。

## [0105]

絶縁物1512及び画素電極1525上には有機化合物を含む層1513を有し、有機化合物を含む層1513上には対向電極1514を有する。画素電極1525と対向電極1

20

30

40

50

5 1 4 とで有機化合物を含む層 1 5 1 3 が挟まれる領域に発光素子 1 5 2 8 が形成される。対向電極 1 5 1 4 に用いる材料としては、仕事関数の小さい材料を用いることが望ましい。例えば、アルミニウム(Al)、銀(Ag)、リチウム(Li)、カルシウム(Ca)、若しくはこれらの合金又は、MgAg、MgIn、AlLi、CaF₂、若しくはCa₃N₂などの金属薄膜を用いることができる。こうして薄い金属薄膜を用いることで光を透過させることが可能な陰極を形成することができる。

#### [0106]

こうして、Nチャネル型のトランジスタ1515、Nチャネル型のトランジスタ1516、Pチャネル型トランジスタ1526、容量素子1527、発光素子1528が形成される。Nチャネル型トランジスタ1516、Pチャネル型トランジスタ1516、Pチャネル型トランジスタ1526、容量素子1527、発光素子1528の画素電極1525は、それぞれ図14のスイッチングトランジスタ1402、ダイオード接続トランジスタ1409、駆動トランジスタ1401、容量素子1403、画素電極1404に相当する。なお、ここでは一例として上面射出構造の表示装置の場合について説明したがこれに限定されない。

## [0107]

また、これは一例であって本発明の画素のレイアウトはこれに限定されない。トランジスタの構造もこれに限定されるものでなく、例えば、サイドウォールがない構造であってもよい。

# [0108]

続いて、整流素子109として、マルチゲートトランジスタをダイオード接続したものを用いた構成について図11及び図12を用いて説明する。なお、マルチゲートトランジスタとは、電気的に接続された2本以上のゲート電極がチャネル形成領域上に配置されているものをいう。また、図11及び図12では、マルチゲートトランジスタとして、二つのトランジスタのゲート端子を互いに接続したものを用いて図示しているが、これに限られない。つまり、図11及び図12では、整流素子109としてマルチゲートのトランジスタタをダイオード接続したものを用いた場合の効果を説明するために、二つのトランジスタのゲート端子を互いに接続したものを用いて、マルチゲートのトランジスタであることをより強調しているのであって、本実施の形態において、スイッチングトランジスタ102や、駆動トランジスタ101がマルチゲートのトランジスタであってもよい。

## [0109]

図11の画素は、図1の整流素子109として、Nチャネル型のマルチゲートトランジスタをダイオード接続したものを用いている。ダイオード接続マルチゲートトランジスタ1101の第1端子(ソース端子又はドレイン端子)を駆動トランジスタ101のゲート端子と接続する。また、ダイオード接続マルチゲートトランジスタ1101は、第2端子(ソース端子又はドレイン端子)を2本のゲート電極の接続されたゲート端子と接続するとともに、第2の走査線110に接続する。すると、第2の走査線110がLレベルのときにはダイオード接続マルチゲートトランジスタ1101はゲート端子とソース端子が接続されているため電流が流れないが、第2の走査線110に日レベルの信号を入力したときにダイオード接続マルチゲートトランジスタ1101に電流が流れる。よって、ダイオード接続マルチゲートトランジスタ1101に電流が流れる。よって、ダイオード接続マルチゲートトランジスタ1101は整流作用を奏する。

## [0110]

また、図12の画素は、また、ダイオード接続マルチゲートトランジスタ1201の第1端子(ソース端子又はドレイン端子)を第2の走査線110に接続する。また、ダイオード接続マルチゲートトランジスタ1201は、第2端子(ソース端子又はドレイン端子)を2本のゲート電極の接続されたゲート端子と接続するとともに、駆動トランジスタ101のゲート端子と接続する。すると、第2の走査線110がLレベルのときにはダイオード接続マルチゲートトランジスタ1201はゲート端子とソース端子が接続されているため電流が流れないが、第2の走査線110にHレベルの信号を入力したときにダイオード

接続マルチゲートトランジスタ1201は、第2端子がドレイン端子となるため電流が流れる。よって、ダイオード接続マルチゲートトランジスタ1201は整流作用を奏する。

## [0111]

なお、図11のダイオード接続マルチゲートトランジスタ1101や図12のダイオード接続マルチゲートトランジスタ1201は、2本のゲート電極に限られず3本であってもそれ以上であってもよい。マルチゲートトランジスタとすることにより、トランジスタのゲート電極に流れ込むゲートリーク電流を減少させることができる。よって、画素に書き込まれたビデオ信号(駆動トランジスタ101のゲート電位)がゲートリーク電流によっておかしくなってしまうことを防止することができる。

#### [0112]

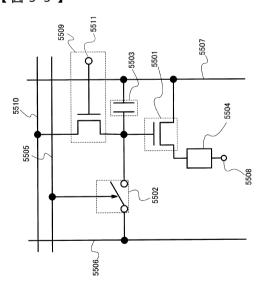

また、整流素子109として、トランジスタをダイオード接続したものを複数用いた構成 について図9及び図10を用いて説明する。

#### [0113]

図9に示す画素は、整流素子109として、Nチャネル型のトランジスタをダイオード接 続したものを二つ用いている。つまり、第1のダイオード接続トランジスタ901と第2 のダイオード接続トランジスタ902とを、整流素子109として用いている。つまり、 ダイオード接続トランジスタ901の第1端子(ソース端子又はドレイン端子)を駆動ト ランジスタ101のゲート端子と接続する。またダイオード接続トランジスタ901は、 第2端子(ソース端子又はドレイン端子)をゲート端子と接続するとともに、第2のダイ オード接続トランジスタ902の第1端子(ソース端子又はドレイン端子)と接続する。 また、ダイオード接続トランジスタ902は、第2端子(ソース端子又はドレイン端子) をゲート端子と接続するともに、第2の走査線110に接続する。すると、第2の走査線 110がLレベルのときには第1のダイオード接続トランジスタ901及び第2のダイオ ード接続トランジスタ902はそれぞれゲート端子とソース端子が接続されているため電 流が流れないが、第2の走査線110にHレベルの信号を入力したときに第1のダイオー ド接続トランジスタ901及び第2のダイオード接続トランジスタ902は第2端子がド レイン端子となるため、第1のダイオード接続トランジスタ901及び第2のダイオード 接続トランジスタ902に電流が流れる。よって、第1のダイオード接続トランジスタ9 0 1 及び第 2 のダイオード接続トランジスタ 9 0 2 は整流作用を奏する。

# [0114]

このように、第2の走査線110のHレベルの電位と、駆動トランジスタ101のゲート端子の電位との電位差を、第1のダイオード接続トランジスタ901のドレインソース間電圧と第2のダイオード接続トランジスタ902のドレインソース間電圧とに分散することにより、一つのトランジスタで整流素子109を構成した場合の耐圧より大きくすることができる。よって、駆動トランジスタ101をオフするのに必要なゲート端子の電位を設定しやすくなる。また、一つあたりのトランジスタのドレインソース間電圧が小さくなるためオフ電流も低減する。

## [0115]

なお、図9では、複数のダイオード接続トランジスタとしてNチャネル型のトランジスタを用いて説明したがPチャネル型トランジスタであっても構わない。また、図9では、二つのダイオード接続トランジスタを用いたが、3つでもそれ以上であっても構わない。

## [0116]

また、図10に示すように、整流素子109として、Nチャネル型のトランジスタ及び Pチャネル型トランジスタをそれぞれダイオード接続したものを組み合わせて用いてもよい

# [0117]

図10に示す画素は、整流素子109として、Nチャネル型のトランジスタをダイオード接続したものとPチャネル型トランジスタをダイオード接続したものを用いている。つまり、Nチャネル型のトランジスタをダイオード接続した第1のダイオード接続トランジスタ 1001とPチャネル型トランジスタをダイオード接続した第2のダイオード接続トラ

10

20

30

40

20

30

40

50

ンジスタ1002とを、整流素子109として用いている。つまり、ダイオード接続トランジスタ1001の第1端子(ソース端子又はドレイン端子)を駆動トランジスタ101のゲート端子と接続する。またダイオード接続トランジスタ1001は、第2端子(ソース端子又はドレイン端子)と接続する。またダイオード接続するとともに、第2のダイオード接続イオード接続トランジスタ1002の第2端子(ソース端子又はドレイン端子)と接続する。また、ダイオード接続トランジスタ1002の第1端子(ソース端子又はドレイン端子)と方に対端子(ソース端子又はドレイン端子)と方に対端子(ソース端子又はドレイン端子)を第2の走査線110に接続する。すると、第2の走査線110に接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001及び第2のダイオード接続トランジスタ1001とは整流作用を奏する。

[0118]

ここで、一般的にNチャネル型のトランジスタはLDD領域を形成し易いため、整流素子109として、LDD領域を有するNチャネル型のトランジスタをダイオード接続して用いることにより、オフ電流の低減を図ることができる。しかし、活性層(チャネル形成領域)に多結晶シリコン膜を用いると、N型化する傾向が強いため、Nチャネル型のトランジスタはややディプレッション型トランジスタになりやすい。このとき、Pチャネル型トランジスタはエンハンスメント型トランジスタになりやすいので、Nチャネル型のトランジスタ及びPチャネル型トランジスタをそれぞれダイオード接続したものを組み合わせて用いることにより、さらにオフ電流を低減することができる。なお、Pチャネル型トランジスタがディプレッション型になってしまった場合にも同様にNチャネル型のトランジスタがエンハンスメント型になりやすくなるので、オフ電流を低減することができる。

[0119]

また、整流素子109として、ダイオード接続トランジスタとPN接合ダイオードを組み合わせて用いてもよい。組み合わせて用いることにより、より効果的にオフ電流を低減することができる。図16は整流素子109として、Nチャネル型のトランジスタをダイオード接続したダイオード接続トランジスタ1601と第2の走査線110との間にPN接合ダイオード1602を適用した場合を示し、図17は整流素子109としてNチャネル型のトランジスタをダイオード接続したダイオード接続トランジスタ1701と駆動トランジスタ101のゲート端子の間にPN接合ダイオード1702を適用した場合を示す。図46は整流素子109として、Pチャネル型トランジスタをダイオード接続したダイオード4602を適用した場合を示し、図42は整流素子109としてPチャネル型トランジスタをダイオード4601と第2の走査線110との間にPN接合ダイオード4601と駆動トランジスタ101のゲート端子の間にPN接合ダイオード4202を適用した場合を示す。

[0120]

まず、図16について簡単に説明する。ダイオード接続トランジスタ1601は、第1端子(ソース端子又はドレイン端子)を駆動トランジスタ101のゲート端子と接続し、ゲート端子を第2端子(ソース端子又はドレイン端子)と接続する。また、ダイオード接続トランジスタ1601の第2端子はPN接合ダイオード1602のN型半導体領域と接続し、PN接合ダイオード1602のP型半導体領域は第2の走査線110と接続する。

[0121]

また、図46について簡単に説明する。ダイオード接続トランジスタ4601は、第2端子(ソース端子又はドレイン端子)をゲート端子と接続し、さらに駆動トランジスタ101のゲート端子と接続する。また、第1端子(ソース端子又はドレイン端子)をPN接合ダイオード4602のN型半導体領域と接続する。PN接合ダイオード4602のP型半

20

30

40

50

導体領域は第2の走査線110と接続する。

## [0122]

また、図17について簡単に説明する。ダイオード接続トランジスタ1701は、第1端子(ソース端子又はドレイン端子)をPN接合ダイオード1702のP型半導体領域と接続し、PN接合ダイオード1702のN型半導体領域は、駆動トランジスタ101のゲート端子と接続する。また、ダイオード接続トランジスタ1701は、第2端子(ソース端子又はドレイン端子)をゲート端子と接続し、さらに第2の走査線110と接続する。

## [0123]

また、図42について簡単に説明する。ダイオード接続トランジスタ4201は、第2端子(ソース端子又はドレイン端子)をゲート端子と接続し、さらに第1端子(ソース端子又はドレイン端子)をPN接合ダイオード4202のP型半導体領域と接続する。PN接合ダイオード4202のN型半導体領域は、駆動トランジスタ101のゲート端子と接続する。また、ダイオード接続トランジスタ4201は、第1端子を第2の走査線110と接続する。

## [0124]

また、整流素子109として、Pチャネル型トランジスタのダイオード接続トランジスタと、Nチャネル型のトランジスタのダイオード接続トランジスタと、PN接合ダイオードとを組み合わせて適用した場合について図41及び図47を用いて説明する。

#### [ 0 1 2 5 ]

また、図41について簡単に説明する。第1のダイオード接続トランジスタ4101と第 2 のダイオード接続トランジスタ 4 1 0 2 と P N 接合ダイオード 4 1 0 3 とを、 整流素子 109として用いている。第1のダイオード接続トランジスタ4101はNチャネル型の トランジスタであり、第2のダイオード接続トランジスタ4102はPチャネル型トラン ジスタである。ダイオード接続トランジスタ4101の第1端子(ソース端子又はドレイ ン端子)を駆動トランジスタ101のゲート端子と接続する。またダイオード接続トラン ジスタ4101は、第2端子(ソース端子又はドレイン端子)をゲート端子と接続すると ともに、PN接合ダイオード4103のN型半導体領域と接続する。また、第2のダイオ ード接続トランジスタ4102は、第2端子(ソース端子又はドレイン端子)をゲート端 子と接続するともに、PN接合ダイオード4103のP型半導体領域に接続する。このよ うに接続することにより、コンタクト数を減らすことができる。また、第2のダイオード 接続トランジスタ4102は第1端子(ソース端子又はドレイン端子)を第2の走査線1 10と接続する。すると、第2の走査線110がLレベルのときには第1のダイオード接 続トランジスタ4101及び第2のダイオード接続トランジスタ4102はそれぞれゲー ト端子とソース端子が接続されているため電流が流れないが、第2の走査線110にHレ ベルの信号を入力したときに第1のダイオード接続トランジスタ4101及び第2のダイ オード接続トランジスタ4102は第2端子がドレイン端子となる。また、このときPN 接合ダイオード4103には順方向バイアスが印加される。よって、第1のダイオード接 続トランジスタ4101、第2のダイオード接続トランジスタ4102及びPN接合ダイ オード4103に電流が流れる。よって、第1のダイオード接続トランジスタ4101、 第2のダイオード接続トランジスタ4102及びPN接合ダイオード4103は整流作用 を奏する。

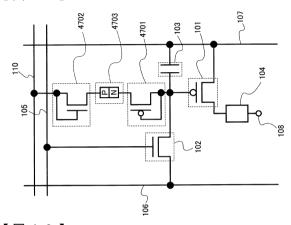

#### [0126]

また、図47について簡単に説明する。また、第1のダイオード接続トランジスタ470 1と第2のダイオード接続トランジスタ4702とPN接合ダイオード4703とを、整 流素子109として用いている。第1のダイオード接続トランジスタ4701はPチャネ ル型トランジスタであり、第2のダイオード接続トランジスタ4702はNチャネル型の トランジスタである。第1のダイオード接続トランジスタ4701は、第2端子(ソース 端子又はドレイン端子)をゲート端子と接続するとともに、駆動トランジスタ101のゲート端子と接続する。また、第1のダイオード接続トランジスタ4701の第1端子(ソース端子又はドレイン端子)をPN接合ダイオード4703のN型半導体領域と接続する 。また、第2のダイオード接続トランジスタ4702は、第2端子(ソース端子又はドレイン端子)をゲート端子と接続するともに、第2の走査線110と接続する。また、第2のダイオード接続トランジスタ4702は第1端子(ソース端子又はドレイン端子)をPN接合ダイオード4703のP型半導体領域に接続する。すると、第2の走査線110がLレベルのときには第1のダイオード接続トランジスタ4701及び第2のダイオード接続トランジスタ4701及び第2のダイオード接続トランジスタ4702は第2端子がド流れないが、第2の走査線110にHレベルの信号を入力したときに第1のダイオード接続トランジスタ4702は第2端子がドレイン端子となる。また、このときPN接合ダイオード4703には順方向バイアスが印加される。よって、第1のダイオード接続トランジスタ4701、第2のダイオード接続トランジスタ4702及びPN接合ダイオード接続トランジスタ4702及びPN接合ダイオード接続トランジスタ4702及びPN接合ダイオード接続トランジスタ4702及びPN接合ダイオード4703に電流が流れる。よって、第1のダイオード接続トランジスタ4702及びPN接合ダイオード4703は整流作用を奏する。

# [0127]

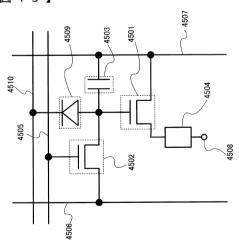

なお、本発明の画素は上記で示した画素のスイッチングトランジスタ102や駆動トランジスタ101の極性を適宜変更してもよい。なお、駆動トランジスタ101の極性を変更する場合には、整流素子109の順方向電流の向きが逆向きになるようにする。一例として、図1の画素において、駆動トランジスタ101にNチャネル型のトランジスタを適用した場合について図45に示す。

# [0128]

駆動トランジスタ4501、スイッチングトランジスタ4502、容量素子4503、発 光素子4504、第1の走査線4505、信号線4506、電源線4507、整流素子4 5 0 9 、 第 2 の走査線 4 5 1 0 を有している。なお、駆動トランジスタ 4 5 0 1 及びスイ ッチングトランジスタ 4 5 0 2 は N チャネル型トランジスタである。スイッチングトラン ジスタ4502は、ゲート端子が第1の走査線4505に接続され、第1端子(ソース端 子又はドレイン端子)が信号線4506に接続され、第2端子(ソース端子又はドレイン 端子)が駆動トランジスタ4501のゲート端子と接続されている。さらに、駆動トラン ジスタ4501のゲート端子は整流素子4509を介して第2の走査線4510と接続さ れている。また、スイッチングトランジスタ4502の第2端子は容量素子4503を介 して電源線4507と接続されている。また、駆動トランジスタ4501は、第2端子( ソース端子又はドレイン端子)が電源線4507に接続され、第1端子(ソース端子又は ドレイン端子)が発光素子4504の第1の電極(画素電極)と接続されている。発光素 子4504の第2の電極(対向電極)4508には低電源電位が設定されている。なお、 低電源電位とは、電源線4507に設定される高電源電位を基準にして低電源電位<高電 源電位を満たす電位であり、低電源電位としては例えばGND、0Vなどが設定されてい ても良い。したがて、発光期間に発光素子4504に印加される電圧が、発光素子450 4の順方向しきい値電圧以上となるように高電源電位及び低電源電位を設定する。

## [0129]

なお、容量素子 4503 は、駆動トランジスタ 4501 のゲート電位を保持できる場所に接続すればよく、例えば、容量素子 4503 は、一方の電極を駆動トランジスタ 4501 のゲート端子、他方の電極を電源線 4507 とは異なる別の配線に接続してもよい。また、容量素子 4503 は駆動トランジスタ 4501 のゲートソース間に配置することもある。また、容量素子 4503 は駆動トランジスタ 4501 のゲート容量を代用して削除しても良い。

## [0130]

続いて、画素の動作について説明する。

#### [0131]

画素への信号の書き込みの際には、第1の走査線4505にスイッチングトランジスタ4502がオンするHレベルの信号を入力する。すると、スイッチングトランジスタ450 2がオンし、信号の書き込みを行う画素が選択される。そして、信号線4506から画素 10

20

30

40

(25)

にビデオ信号が書き込まれる。つまり、ビデオ信号に相当する電圧分の電荷が容量素子4503に蓄積される。そして、第1の走査線4505をLレベルにし、スイッチングトランジスタ4502がオフすると容量素子4503はその電圧を保持する。この電圧は駆動トランジスタ101のゲート端子と第2端子との間の電圧であり、駆動トランジスタ4501のゲートドレイン間電圧に相当する。

### [0132]

なお、第1の走査線4505のHレベルの信号は、画素を点灯にするビデオ信号(駆動トランジスタ4501をオンにするゲート電位Vsig(H))よりもスイッチングトランジスタ4502のしきい値電圧分以上高い電圧とする。また、第1の走査線4505のLレベルの信号が、画素を非点灯にするビデオ信号(駆動トランジスタ4501がオフするゲート電位Vsig(L))と等しい電位であると、Vsig(H)が書き込まれている画素は、他の行の画素への信号書き込みのために信号線106にVsig(L)が入力されると、画素のスイッチングトランジスタ4502のゲートソース間電圧は0Vとなり、オフ電流が流れてしまうことがある。よって、第1の走査線4505のLレベルの信号は、Vsig(L)よりも低い電位とする。

#### [0133]

次に、消去動作について説明する。消去動作時には、第2の走査線4510にLレベルの信号を入力する。すると、整流素子4509に電流が流れ、容量素子4503によって保持されていた駆動トランジスタ4501のゲート電位をある所定の電位になるようにすることができる。つまり、駆動トランジスタ4501のゲート端子の電位が、所定の電位になるようにし、信号書き込み期間に画素へ書き込まれたビデオ信号に関わらず、駆動トランジスタ4501を強制的にオフさせることができる。なお、駆動トランジスタ4501のゲート端子の電位は第2の走査線4510よりも整流素子4509のしきい値電圧分高い電位となる。

# [0134]

このとき、第2の走査線4510に入力するLレベルの信号は、対向電極4508に設定される低電源電位以下の電位とすることが望ましい。このLレベルの信号の電位を適宜設定することにより、消去期間において駆動トランジスタ4501を強制的にオフさせる場合に、駆動トランジスタ4501がノーマリーオンの場合でも駆動トランジスタ4501がノーマリーオンの場合でも駆動トランジスタ4501をオフにし、発光素子4504がわずかに発光してしまうことを防ぐことができる。

## [0135]

なお、消去動作時以外は、第2の走査線4510はHレベルの信号とする。このHレベルの信号の電位は、画素を点灯とするビデオ信号(駆動トランジスタ4501をオンにするゲート電位Vsig(H)以上の電位とすることが望ましい。しかし、このHレベルの電位を高くし過ぎると、画素に非点灯のビデオ信号(駆動トランジスタ4501をオフにするゲート電位Vsig(L)が書き込まれていた場合に、整流素子4509に印加される逆バイアス電圧が大きくなってしまうことにより、整流素子4509へ流れるオフ電流(逆方向電流ともいう)が大きくなってしまう。そして、駆動トランジスタ4501のゲート電位が高くなり、駆動トランジスタ4501のオフ電流が大きくなってしまう。よって、好ましくは、このHレベルの信号の電位は、画素を点灯にするビデオ信号(駆動トランジスタ4501をオンにするゲート電位Vsig(H))と等しくするとよい。

# [0136]

また、駆動トランジスタ4501は、電源線4507に接続された第2端子がソース端子となるため、駆動トランジスタ4501をオンにするビデオ信号Vsig(H)は、電源線4507に入力される電位より駆動トランジスタ4501のしきい値電圧分以上高い電位とすることが好ましい。そうすることにより、発光素子4504の画素電極に電源線4507の電位を入力することができる。

# [0137]

50

10

20

30

20

30

40

50

なお、整流素子4509には、ダイオード接続したトランジスタを用いることが可能である。さらに、ダイオード接続したトランジスタの他にも、PN接合やPIN接合のダイオードやショットキー型のダイオードやカーボンナノチューブで形成されたダイオードなどを用いてもよい。

## [0138]

また、本発明の画素構成は上述したものに限られない。例えば図13に示すような画素に も適用することができる。

## [0139]

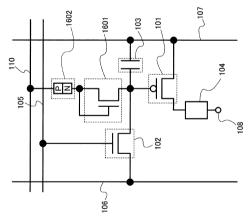

図13に示す画素は、駆動トランジスタ1301、スイッチングトランジスタ1302、 電流制御用トランジスタ1311、容量素子1303、発光素子1304、第1の走査線 1 3 0 5 、第 2 の走査線 1 3 1 0 、信号線 1 3 0 6 、電源線 1 3 0 7 、配線 1 3 1 2 を有 している。なお、駆動トランジスタ1301はPチャネル型トランジスタであり、スイッ チングトランジスタ1302はNチャネル型トランジスタであり、電流制御用トランジス タ1311はPチャネル型トランジスタである。スイッチングトランジスタ1302は、 ゲート端子が第1の走査線1305に接続され、第1端子(ソース端子又はドレイン端子 ) が信号線1306に接続され、第2端子(ソース端子又はドレイン端子)が駆動トラン ジスタ1301のゲート端子と接続されている。また、スイッチングトランジスタ130 2の第2端子は容量素子1303を介して電源線1307と接続されている。さらに、駆 動トランジスタ1301は、第1端子(ソース端子又はドレイン端子)が電源線1307 に接続され、第2端子(ソース端子又はドレイン端子)が、電流制御用トランジスタ13 1 1 の第 1 端子(ソース端子又はドレイン端子)と接続されている。電流制御用トランジ スタ 1 3 1 1 は、第 2 端子 ( ソース端子に又はドレイン端子 ) が発光素子 1 3 0 4 の画素 電極と接続され、ゲート端子が配線1312と接続されている。つまり、駆動トランジス タ1301と電流制御用トランジスタ1311は直列に接続されている。なお、発光素子 1304の対向電極1308には低電源電位が入力されている。なお、低電源電位とは、 電源線1307に設定される高電源電位を基準にして低電源電位<高電源電位を満たす電 位であり、低電源電位としては例えばGND、0Vなどが設定されていても良い。

#### [0140]

また、本画素構成においては、画素の点灯時に一定の電流を発光素子1304に供給するため、電流制御用トランジスタ1311を飽和領域で動作させる。なお容量素子1303 は駆動トランジスタ1301のゲート容量を代用して削除しても良い。

# [0141]

第1の走査線1305にHレベルの信号が入力され、画素が選択されているとき、つまり、スイッチングトランジスタ1302がオンになっているときに信号線1306から画素にビデオ信号が入力される。そして、ビデオ信号に相当する電圧分の電荷が容量素子1303に蓄積され、容量素子1303はその電圧を保持する。この電圧は駆動トランジスタ1301のゲート端子と第1端子間の電圧であり、駆動トランジスタ1301のゲートソース間電圧Vgsに相当する。なお、このとき第2の走査線1310はLレベルにしておく。

## [0142]

そして、駆動トランジスタ1301を十分にオンするか、オフするかの二つの状態となるようなビデオ信号を入力する。つまり、駆動トランジスタ1301は線形領域で動作させる。

# [0143]

よって、駆動トランジスタ1301がオンするビデオ信号であるときには、理想的には電源線1307に入力されている高電源電位 V d d をそのまま電流制御用トランジスタ131の第1端子に入力する。このとき、電流制御用トランジスタ1311の第1端子がソース端子となり、配線1312と電源線1307によって入力される電流制御用トランジスタ1311のゲートソース間電圧によって、発光素子1304に供給される電流が決定される。

### [0144]

つまり、発光素子1304に印加する電流を一定にし、発光素子1304から得られる輝度を一定にすることができる。そして、環境温度の変化や、経時変化に伴う発光素子13 04の輝度変化も抑制することができる。

## [0145]

消去動作時には、第2の走査線1310にHレベルの電位を入力する。すると、整流素子1309に電流が流れ、駆動トランジスタ1301の電位をある電位にすることができる。この電位は駆動トランジスタ1301をオフにし、発光素子1304がわずかに発光してしまうのを防ぐことができる。

## [0146]

よって、本実施の形態に示す画素構成により、例えば図 8 を用いて説明した駆動方法を実現することができる。

#### [0147]

(実施の形態2)

本実施の形態では、電位伝達手段として、三端子を有する回路素子を用いた構成について 説明する。

## [0148]

まず、図53に本実施の形態の基本画素構成について説明する。画素は、トランジスタ5 3 0 1 、スイッチ 5 3 0 2 、電位保持素子 5 3 0 3 、発光素子 5 3 0 4 、第 1 の走査線 5 305、信号線5306、電源線5307、第2の走査線5310、電位伝達素子530 9 を有している。スイッチ 5 3 0 2 は、信号線 5 3 0 6 とトランジスタ 5 3 0 1 のゲート 端子とを導通又は非導通にするように接続されている。また、スイッチ5302の制御端 子は第1の走査線5305と接続されている。よって、第1の走査線5305に入力され る信号にしたがって、スイッチ5302がオンオフし、信号線5306とトランジスタ5 301のゲート端子とを導通又は非導通にすることができる。また、トランジスタ530 1は、第1端子(ソース端子又はドレイン端子)が電源線5307に接続され、第2端子 (ソース端子又はドレイン端子)が発光素子5304の画素電極に接続されている。なお 、発光素子5304の対向電極5308には所定の電位が供給されている。また、電位伝 達素子5309は、第1端子がトランジスタ5301の制御端子に接続され、第2端子が 第2の走査線5310に接続されている。そして、電位伝達素子5309の第3端子53 11には、ある電位が入力されている。この電位伝達素子5309は第3端子5311と 第2端子との電位の関係により、第2端子に入力されている電位を第1端子に供給するか どうかを制御することができ、さらにその電位の大きさも制御することができる。また、 電位保持素子5303はトランジスタ5301のゲート端子に接続されており、トランジ スタ5301のゲート端子に入力された電位を保持する。

## [0149]

続いて、画素の動作について説明する。

## [0150]

画素へ信号の書き込みを行う際には、第1の走査線5305に信号を入力してスイッチ5302をオンにする。そして、信号線5306からトランジスタ5301の制御端子にビデオ信号が入力される。このビデオ信号は電位保持素子5303によって保持される。こうして画素への信号の書き込みが完了する。

## [0151]

そして、画素への信号の書き込みが行われると、電位保持素子5303によって保持された電位に従って、トランジスタ5301はオン又はオフの状態を維持する。つまり、発光素子5304は発光状態又は非発光状態が維持される。

#### [0152]

そして、消去動作時には、第2の走査線5310に信号を入力する。すると、電位伝達素子5309からトランジスタ5301の制御端子に電位が供給される。この制御端子に供給する電位は、トランジスタ5301をオフするのに十分な電位とすることができる。

10

20

30

40

## [0153]

したがって、発光素子 5 3 0 4 を非発光とすべきときに、トランジスタ 5 3 0 1 がオフすることにより、電源線 5 3 0 7 と発光素子 5 3 0 4 の画素電極とを非導通にする。こうして、発光素子 5 3 0 4 の微発光を防ぐことができる。

## [0154]

なお、トランジスタ 5 3 0 1 には、 P チャネル型トランジスタ及び N チャネル型のトランジスタの N ずれを適用することもできる。

## [0155]

トランジスタ5301にPチャネル型トランジスタを適用した場合には、電位伝達素子5309にPチャネル型トランジスタを適用するのが望ましい。この構成について図54を用いて説明する。

[0156]

図 5 4 の画素は、第 1 のトランジスタ 5 4 0 1、スイッチ 5 4 0 2、容量素子 5 4 0 3、 発光素子5404、第1の走査線5405、信号線5406、電源線5407、第2の走 査線5410、第2のトランジスタ5409を有している。なお、第1のトランジスタ5 401及び第2のトランジスタ5409はPチャネル型トランジスタである。スイッチ5 4 0 2 は、信号線 5 4 0 6 と第 1 のトランジスタ 5 4 0 1 のゲート端子とを導通又は非導 通にするように接続されている。また、スイッチ5402の制御端子は第1の走査線54 05と接続されている。よって、第1の走査線5405に入力される信号にしたがって、 スイッチ5402がオンオフし、信号線5406と第1のトランジスタ5401のゲート 端子とを導通又は非導通にすることができる。また、第1のトランジスタ5401は、第 1端子(ソース端子又はドレイン端子)が電源線5407に接続され、第2端子(ソース 端子又はドレイン端子)が発光素子5404の画素電極に接続されている。また、第2の トランジスタ5409は、第1端子(ソース端子又はドレイン端子)が第1のトランジス タ 5 4 0 1 のゲート端子に接続され、第 2 端子 ( ソース端子又はドレイン端子 ) が第 2 の 走査線5410に接続されている。また、第2のトランジスタ5409のゲート端子54 11には、ある電位が入力される。また、容量素子5403は、一方の電極が第1のトラ ンジスタ5401のゲート端子に接続され、他方の電極が電源線5407に接続されてお り、第1のトランジスタ5401のゲート端子に入力された電位を保持する。

## [0157]

続いて画素の動作について説明する。

# [0158]

画素へ信号の書き込みを行う際には、第1の走査線5405に信号を入力してスイッチ5402をオンにする。そして、信号線5406から第1のトランジスタ5401のゲート端子にビデオ信号が入力される。このビデオ信号は容量素子5403によって保持される。こうして画素への信号の書き込みが完了する。なお、このとき第2の走査線5410は、Lレベルにしておく。

## [0159]

そして、画素への信号の書き込みが行われると、容量素子5403によって保持された電位に従って、第1のトランジスタ5401はオン又はオフの状態を維持する。つまり、発光素子5404は発光状態又は非発光状態が維持される。

[0160]

そして、消去動作時には、第2の走査線5410にHレベルの信号を入力する。すると、第2のトランジスタ5409を介して第1のトランジスタ5401のゲート端子に電位が供給される。なお、第2の走査線5410に入力するHレベルの電位は、第2のトランジスタ5409のゲート端子5411に入力する電位や電源線5407に入力する電位より高くするとよい。したがって、第1のトランジスタ5401のゲート端子に供給する電位は、第1のトランジスタ5401をオフするのに十分な電位とすることができる。

## [0161]

また、第2の走査線5410に入力するLレベルの電位は、第2のトランジスタ5409

20

10

30

50

20

30

40

50

のゲート端子に入力する電位から、しきい値電圧の絶対値分低い電位にするとよい。

## [0162]

したがって、発光素子5404を非発光とすべきときに、第1のトランジスタ5401が オフすることにより、電源線5407と発光素子5404の画素電極とを非導通にする。 こうして、発光素子5404の微発光を防ぐことができる。

#### [0163]

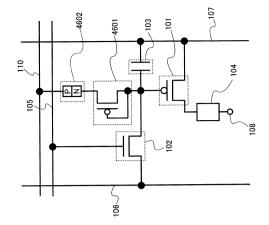

図54の画素の具体例を図44に示す。

## [0164]

また、図44の画素は、実施の形態1の図1で示した画素の整流素子109の代わりに、 トランジスタを用いた構成でもある。よって、図1の画素と共通するところには共通の符 号を用いて説明する。トランジスタ4401の第1端子(ソース端子又はドレイン端子) を 第 2 の 走 査 線 1 1 0 に 接 続 し 、 第 2 端 子 ( ソース 端 子 又 は ドレイン 端 子 )を 駆 動 トラン ジスタ101のゲート端子に接続する。また、トランジスタ4401のゲート端子を電源 線107と接続する。すると、第2の走査線110がLレベルのときには、トランジスタ 4 4 0 1 は、第 1 端子が第 2 の走査線 1 1 0 に接続され、第 2 端子が駆動トランジスタ 1 0 1 のゲート端子に接続されているため、第 1 端子がドレイン端子となり、第 2 端子がソ ース端子となる。このとき画素に書き込まれたビデオ信号(駆動トランジスタのゲート電 位)がHレベルであっても、このHレベルの電位と電源線107の電位が概略等しければ トランジスタ4401には電流が流れない。もちろん、ビデオ信号がLレベルのときにも トランジスタ4401には電流が流れない。一方、第2の走査線110にHレベルが入力 されたとき、トランジスタ4401は、第1端子が第2の走査線110に接続され、第2 端子が駆動トランジスタ101のゲート端子に接続されているため、第1端子がソース端 子となり、第2端子がドレイン端子となる。そして、このHレベルの電位が電源線107 よりも高い電位であれば(正確には、トランジスタ4401のしきい値電圧の絶対値|V th|以上高い電位であれば)、トランジスタ4401はオンし、電流が流れる。そして 駆動トランジスタ101のゲート端子に所定の電位を設定することができる。この場合は 、第2の走査線110のHレベルと同電位とすることができる。つまり、画素に書き込ま れたビデオ信号を消去することができる。

## [0165]

また、トランジスタ5301にNチャネル型のトランジスタを適用した場合には、電位伝達素子5309にNチャネル型のトランジスタを適用するのが望ましい。この構成について図55を用いて説明する。

## [0166]

図 5 5 の画素は、第 1 のトランジスタ 5 5 0 1、スイッチ 5 5 0 2、容量素子 5 5 0 3、 発光素子5504、第1の走査線5505、信号線5506、電源線5507、第2の走 査線5510、第2のトランジスタ5509を有している。なお、第1のトランジスタ5 501及び第2のトランジスタ5509はNチャネル型トランジスタである。スイッチ5 5 0 2 は、信号線 5 5 0 6 と第 1 のトランジスタ 5 5 0 1 のゲート端子とを導通又は非導 通にするように接続されている。また、スイッチ5502の制御端子は第1の走査線55 05と接続されている。よって、第1の走査線5505に入力される信号にしたがって、 スイッチ5502がオンオフし、信号線5506と第1のトランジスタ5501のゲート 端子とを導通又は非導通にすることができる。また、第1のトランジスタ5501は、第 1端子(ソース端子又はドレイン端子)が電源線5507に接続され、第2端子(ソース 端子又はドレイン端子)が発光素子5504の画素電極に接続されている。また、第2の トランジスタ5509は、第1端子(ソース端子又はドレイン端子)が第1のトランジス タ 5 5 0 1 のゲート端子に接続され、第 2 端子 ( ソース端子又はドレイン端子 ) が第 2 の 走査線5510に接続されている。また、第2のトランジスタ5509のゲート端子には ある電位が入力されている。また、容量素子5503は、一方の電極が第1のトランジス タ 5 5 0 1 のゲート端子に接続され、他方の電極が電源線 5 5 0 7 に接続されており、ト ランジスタ5501のゲート端子に入力された電位を保持する。

#### [0167]

続いて画素の動作について説明する。

#### [0168]

画素へ信号の書き込みを行う際には、第1の走査線5505に信号を入力してスイッチ5502をオンにする。そして、信号線5506から第1のトランジスタ5501のゲート端子にビデオ信号が入力される。このビデオ信号は容量素子5503によって保持される。こうして画素への信号の書き込みが完了する。なお、このとき、第2の走査線5510はHレベルにしておく。

#### [0169]

そして、画素への信号の書き込みが行われると、容量素子5503によって保持された第1のトランジスタ5501のゲート端子の電位に従って、第1のトランジスタ5501はオン又はオフの状態を維持する。つまり、第1のトランジスタ5501のゲート端子の電位がHレベルのときには発光素子5504は発光状態となり、Lレベルのときには、非発光状態となる。

## [0170]

そして、消去動作時には、第2の走査線5510にLレベルの信号を入力する。すると、5509からトランジスタ5501のゲート端子に電位が供給される。なお、第2の走査線5510に入力するLレベルの電位は、第1のトランジスタ5501のゲート端子に供給する電位が画素を非点灯にするビデオ信号の電位(Vsig(L))と同じか、それ以下にするのが望ましい。つまり、第2の走査線5510のLレベルの電位はVsig(L)と同じ電位でよい。このゲート端子に供給する電位は、トランジスタ5501をオフするのに分な電位とすることができる。

## [0171]

また、第2の走査線5510に入力するHレベルの電位は、第2のトランジスタ5509のゲート端子に入力する電位から、しきい値電圧の絶対値分高い電位にするとよい。

## [0172]

したがって、発光素子5504を非発光とすべきときに、トランジスタ5501がオフすることにより、電源線5507と発光素子5504の画素電極とを非導通にする。こうして、発光素子5504の微発光を防ぐことができる。

# [0173]

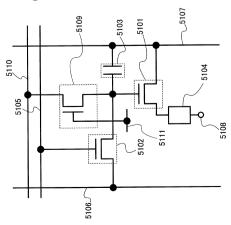

図55の画素の具体例を図51に示す。

# [0174]

図51に示す画素は、駆動トランジスタ5101、スイッチングトランジスタ5102、 容量素子5103、発光素子5104、第1の走査線5105、信号線5106、電源線 5 1 0 7 、トランジスタ 5 1 0 9 、第 2 の走査線 5 1 1 0 を有している。なお、駆動トラ ンジスタ 5 1 0 1 、スイッチングトランジスタ 5 1 0 2 及びトランジスタ 5 1 0 9 は N チ ャネル型トランジスタである。スイッチングトランジスタ5102は、ゲート端子が第1 の走査線5105に接続され、第1端子(ソース端子又はドレイン端子)が信号線510 6に接続され、第2端子(ソース端子又はドレイン端子)が駆動トランジスタ5101の ゲート端子と接続されている。さらに、駆動トランジスタ5101のゲート端子はトラン ジスタ5109の第1端子(ソース端子又はドレイン端子)と接続されている。またトラ ンジスタ 5 1 0 9 は、第 2 端子(ソース端子又はドレイン端子)が第 2 の走査線 5 1 1 0 と接続され、ゲート端子が配線5111と接続されている。また、スイッチングトランジ スタ5102の第2端子は容量素子5103を介して電源線5107と接続されている。 また、駆動トランジスタ5101は、第1端子(ソース端子又はドレイン端子)が電源線 5 1 0 7 に接続され、第 2 端子(ソース端子又はドレイン端子)が発光素子 5 1 0 4 の画 素電極と接続されている。発光素子5104の対向電極5108には低電源電位が入力さ れている。なお、低電源電位とは、電源線5107に設定される高電源電位を基準にして 低電源電位<高電源電位を満たす電位であり、低電源電位としては例えばGND、0Vな どが設定されていても良い。この高電源電位と低電源電位との電位差を発光素子5104

10

20

30

40

に印加して、発光素子5104に電流を流して発光素子5104を発光させるため、高電源電位と低電源電位との電位差が発光素子5104の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

#### [0175]

なお、容量素子5103は、駆動トランジスタ5101のゲート電位を保持できる場所に接続すればよく、例えば、容量素子5103は、一方の電極を駆動トランジスタ5101 のゲート端子、他方の電極を電源線5107とは異なる別の配線に接続してもよい。また、容量素子5103は駆動トランジスタ5101のゲート容量を代用して削除しても良い

## [0176]

続いて、画素の動作について説明する。

#### [0177]

画素への信号の書き込みの際には、第1の走査線5105にスイッチングトランジスタ5102がオンするHレベルの信号を入力する。すると、スイッチングトランジスタ5102がオンし、信号の書き込みを行う画素が選択される。そして、信号線5106から画素にビデオ信号が書き込まれる。つまり、ビデオ信号に相当する電圧分の電荷が容量素子5103に蓄積される。そして、第1の走査線5105をLレベルにし、スイッチングトランジスタ5102がオフすると容量素子5103はその電圧を保持する。なお、駆動トランジスタ5101のゲートドレイン間電圧に相当する。

#### [0178]

ここで、電圧入力電圧駆動方式の場合には、駆動トランジスタ5101のゲート端子には、駆動トランジスタ5101が十分にオンするか、オフするかの二つの状態となるようなビデオ信号Vsig(H)又はVsig(L)を入力する。つまり、駆動トランジスタ5101は線形領域で動作させる。つまり、スイッチとして動作させる。

## [0179]

よって、駆動トランジスタ5 1 0 1 がオンするビデオ信号 V s i g (H) であるときには、理想的には電源線 5 1 0 7 に印加されている電源電位 V d d はそのまま発光素子 5 1 0 4 の第 1 の電極に加わることになる。

## [0180]

なお、第1の走査線5105のHレベルの信号は、画素を点灯にするビデオ信号(駆動トランジスタ5101をオンにするゲート電位Vsig(H))よりもスイッチングトランジスタ5102のしきい値電圧Vth分以上高い電位V1とすることが望ましい。なぜなら、スイッチングトランジスタ5102はNチャネル型のトランジスタであるため、信号線5106にVsig(H)が入力されると、第1端子がドレイン端子となる。したがって、スイッチングトランジスタ5102は、第2端子(このときにはソース端子)がゲート端子の電位より、スイッチングトランジスタ5102のしきい値電圧Vth分低い電位でオフしてしまう。つまり、スイッチングトランジスタ5102のゲート電位がV1より小さいと、信号線5106に入力されたVsig(H)を駆動トランジスタ5101のゲート端子に入力することができなくなってしまうからである。すると、駆動トランジスタ5101をオンにし、発光素子5104の画素電極を電源線5107に入力される電位まで上げることができなくなる。

## [0181]

また、第1の走査線5105のLレベルの信号は、Vsig(L)よりも低い電位とすることが望ましい。例えば、第1の走査線5105のLレベルの信号が、画素を非点灯にするビデオ信号(駆動トランジスタ5101がオフするゲート電位Vsig(L))と等しい電位である場合、Vsig(H)が書き込まれている画素は、他の行の画素への信号書き込みのために信号線5106にVsig(L)が入力されると、画素のスイッチングトランジスタ5102のゲートソース間電圧は0Vとなる。すると、スイッチングトランジスタ5102がノーマリーオンとなってしまっているときにはオフ電流が流れてしまう。

10

20

30

40

20

30

40

50

(32)

したがって、容量素子5103に蓄積された電荷が放電し、駆動トランジスタ5101の ゲート電位が下がってしまい所望の輝度が得られなくなってしまう。

#### [0182]

次に、消去動作について説明する。消去動作時には、第2の走査線5110にLレベルの信号を入力する。すると、トランジスタ5109に電流が流れ、容量素子5103によって保持されていた駆動トランジスタ5101のゲート電位がある所定の電位になるようにすることができる。つまり、駆動トランジスタ5101のゲート端子の電位が、所定の電位になるようにし、信号書き込み期間に画素へ書き込まれたビデオ信号に関わらず、駆動トランジスタ5101を強制的にオフさせることができる。なお、駆動トランジスタ5101のゲート端子の電位は第2の走査線5110よりもトランジスタ5109のしきい値電圧分高い電位となる。

[0183]

このとき、第2の走査線5110に入力するLレベルの信号は、画素を非点灯にするビデオ信号Vsig(L)よりトランジスタ5109のしきい値電圧分低い電位とすることが望ましい。このLレベルの信号の電位を適宜設定することにより、消去期間において駆動トランジスタ5101を強制的にオフさせる場合に、駆動トランジスタ5101のゲート端子の電位をソース端子の電位よりも低くすることができる。したがって、駆動トランジスタ5101をオフにし、発光素子5104がわずかに発光してしまうのを防ぐことができる。

[0184]

なお、第2の走査線5110のHレベルは、第1の走査線5105のHレベルと同じでもよい。その結果、電源数を削減することができる。

[0185]

なお、消去動作時以外は、第2の走査線5110はHレベルの信号とする。このHレベルの信号の電位は、画素を点灯とするビデオ信号(駆動トランジスタ5101をオンにするゲート電位Vsig(H))以上の電位とすることが望ましい。しかし、このHレベルの電位を高くし過ぎると、画素に非点灯のビデオ信号(駆動トランジスタ5101をオフにするゲート電位Vsig(L))が書き込まれていた場合に、トランジスタ5109に印加されるドレインソース間電圧が大きくなってしまい、トランジスタ5109へ流れるオフ電流(逆方向電流ともいう)が大きくなってしまい、容量素子5103に保持した電荷が漏れてしまう。そして、駆動トランジスタ5101のオフ電流が大きくなってしまう。よって、好ましくは、このHレベルの信号の電位は、画素を点灯にするビデオ信号(駆動トランジスタ5101をオンにするゲート電位Vsig(H))と等しくするとよい。

[0186]

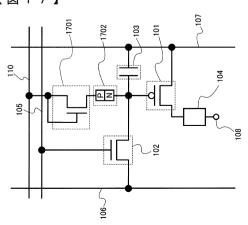

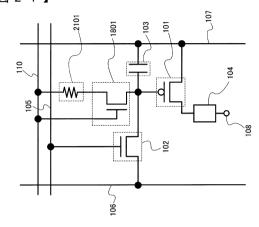

また、実施の形態 1 の図 1 で示した画素の整流素子 1 0 9 の代わりに、トランジスタと電流電圧変換素子とを組み合わせて用いることにより、さらに効果的にオフ電流を低減することができる。ここで適用するトランジスタとしてNチャネル型のトランジスタを適用した場合について図 1 8 を用いて説明する。

[0187]

Nチャネル型のトランジスタ1801は、第1端子(ソース端子又はドレイン端子)を駆動トランジスタ101のゲート端子と接続し、ゲート端子を第2の走査線110に接続する。また、トランジスタ1801の第2端子(ソース端子又はドレイン端子)は電流電圧変換素子1802を介して第2の走査線110と接続する。

[0188]

なお、電流電圧変換素子1802は、電流が流れるとその両端子間に電圧が発生する素子である。

[0189]

つまり、図25(a)の矢印に示すようにトランジスタ1801の第1端子から第2端子に電流が流れるときには、第2端子の電位は第2の走査線110の電位よりも高くなり、

逆に、図25(b)の矢印に示すように第2端子から第1端子に電流が流れるときには、第2端子の電位は第2の走査線110の電位よりも低くなる。

#### [0190]

なお、このとき、上述したように、第2の走査線110に入力するHレベルの信号の電位は、電源線107の電位よりも高い電位とすることが望ましい。すると、駆動トランジスタ101のオフ電流を小さくすることができる。また、第2の走査線110に入力するLレベルの信号の電位は、画素を点灯とするビデオ信号(駆動トランジスタ101をオンにするゲート電位Vsig(L))以下の電位とする。しかし、このLレベルの電位をあまり低くし過ぎると画素に非点灯のビデオ信号(駆動トランジスタ101をオフにする電位Vsig(H))が書き込まれていた場合に、トランジスタ1801のドレインソース間電圧が大きくなってしまいオフ電流が大きくなってしまう。よって、好ましくは、このLレベルの電位は、画素を非点灯にするビデオ信号(駆動トランジスタ101をオンにするゲート電位Vsig(L))と等しくするとよい。

## [0191]

ここで、画素に書き込まれたビデオ信号に関わらず、トランジスタ1801がエンハンスメント型のトランジスタであれば、第2の走査線110がLレベルのときには、トランジスタ1801は第1端子がドレイン端子、第2端子がソース端子となり、トランジスタ1801には電流が流れない。しかし、トランジスタ1801がディプレッション型のトランジスタであると、特に画素を非点灯とするビデオ信号(駆動トランジスタ101をオフにするゲート電位Vsig(H))の場合、トランジスタ1801の第1端子から第2端子に電流が流れてしまうことがある。しかし、電流電圧変換素子1802の両端子間に電圧が発生するので、トランジスタ1801の第2端子は、第2の走査線110のLレベルの電位よりも高くなる。そして、このときトランジスタ1801の第2端子のでの方が高くなる。よって、このときトランジスタ1801に流れる電流が抑制される。つまり、オフ電流が低減される。

## [0192]

一方、第2の走査線110にHレベルの信号を入力すると、トランジスタ1801は第2端子がドレイン端子、第1端子がソース端子となる。そして、トランジスタ1801に電流が流れる。このとき、電流電圧変換素子1802に発生する電圧が小さいときには、トランジスタ1801は飽和領域で動作するが、第1端子がソース端子であるため、トランジスタ1801のゲートソース間電圧は、電流電圧変換素子1802での電圧降下に依存しないため、画素を非点灯にするための駆動トランジスタ101のゲート電位を設定するのは容易である。また、電流電圧変換素子1802に発生する電圧が大きいときであっても、トランジスタ1801は線形領域で動作するため、画素を非点灯にするための駆動トランジスタ101のゲート電位を設定するのは容易である。

# [0193]

なお、電流電圧変換素子1802としては、抵抗や、トランジスタや、整流素子を用いることができる。よって、例えば抵抗を用いた場合の構成を図21に示す。

# [0194]

N チャネル型のトランジスタ 1 8 0 1 は、第 1 端子(ソース端子又はドレイン端子)を駆動トランジスタ 1 0 1 のゲート端子と接続し、ゲート端子を第 2 の走査線 1 1 0 に接続する。また、トランジスタ 1 8 0 1 の第 2 端子(ソース端子又はドレイン端子)は抵抗素子 2 1 0 1 を介して第 2 の走査線 1 1 0 と接続する。なお、抵抗素子 2 1 0 1 に電流が流れると電圧降下が生じるため、図 1 8 の電流電圧変換素子 1 8 0 2 と同じ機能を果たすことができる。

#### [0195]

なお、このように、トランジスタ1801の第2端子と第2の走査線110との間に電流電圧変換素子1802として抵抗素子を有する構成の画素のレイアウト図の一例を図23 及び図24に示す。 10

20

30

40

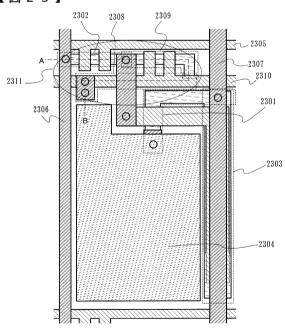

#### [0196]

まず、図23の画素レイアウトについて説明する。画素は、駆動トランジスタ2301、 スイッチングトランジスタ 2 3 0 2 、容量素子 2 3 0 3 、画素電極 2 3 0 4 、第 1 の走査 線 2 3 0 5 、信号線 2 3 0 6 、電源線 2 3 0 7 、抵抗素子 2 3 0 8 、トランジスタ 2 3 0 9、第2の走査線2310を有している。スイッチングトランジスタ2302は、ゲート 端子が第1の走査線2305の一部で構成され、第1端子(ソース端子又はドレイン端子 )が信号線2306に接続され、第2端子(ソース端子又はドレイン端子)が駆動トラン ジスタ2301のゲート端子と接続されている。また、トランジスタ2309は、ゲート 端子が第2の走査線2310の一部で構成され、第1端子(ソース端子又はドレイン端子 )が駆動トランジスタ2301のゲート端子と接続され、第2端子(ソース端子又はドレ イン端子)が抵抗素子2308を介して第2の走査線2310と接続されている。なお、 抵抗素子2308はトランジスタ2309の第1端子となる不純物領域(ソース領域又は ドレイン領域)と同じ層の半導体層であり、第2の走査線2310の下に位置している。 なお、このとき、半導体層の幅の方が第2の走査線2310の幅よりも太くなるようにし てもよい。第2の走査線2310よりもはみ出した部分の半導体層には、不純物を添加す ることが可能なので、不純物の添加される部分の面積を調整することにより、抵抗値を制 御することができる。また、駆動トランジスタ2301は、第1端子(ソース端子又はド レイン端子)が電源線2307に接続され、第2端子(ソース端子又はドレイン端子)が 画素電極2304と接続されている。また、駆動トランジスタ2301のゲート端子を構 成する電極の一部を第1の電極とし、駆動トランジスタ2301の第1端子となる不純物 領域(ソース領域又はドレイン領域)と同じ層の半導体層と電源線2307の一部とで第 2 の電極とする、容量素子 2 3 0 3 が形成されている。なお、図 2 3 の画素レイアウトは 、図21の画素におけるレイアウトの一例であってこれに限定されない。図23の駆動ト ランジスタ2301、スイッチングトランジスタ2302、容量素子2303、第1の走 査線2305、信号線2306、電源線2307、抵抗素子2308、トランジスタ23 0 9 、第 2 の走査線 2 3 1 0 は、それぞれ図 2 1 の駆動トランジスタ 1 0 1 、スイッチン グトランジスタ 1 0 2 、容量素子 1 0 3 、第 1 の走査線 1 0 5 、信号線 1 0 6 、電源線 1 07、抵抗素子2101、トランジスタ1801、第2の走査線110に相当する。また 画素電極2304上に発光層と対向電極が形成されることにより、図21に示す発光素 子104が完成する。

## [0197]

なお、抵抗素子2308の構造をより詳しく説明するため、楕円2311で囲む付近を拡大した図を図26(b)に示す。また、その断面をより詳しく説明するため破線AB間の断面図を図26(a)に示す。なお、図26(b)では、第2の走査線2310の下層に位置する半導体層を点線で示している。

#### [0198]

図 2 6 ( a ) の断面図を用いて説明する。基板 2 6 0 1 上に下地膜 2 6 0 2 を有している。基板 2 6 0 1 としてはガラス基板、石英基板、プラスチック基板、セラミックス基板等の絶縁性基板、金属基板、半導体基板等を用いることができる。下地膜 2 6 0 2 は C V D 法やスパッタ法により形成することができる。例えば S i H  $_4$  、 N  $_2$  O 、 N H  $_3$  を原料に用いた C V D 法により形成した酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を適用することができる。また、これらの積層を用いても良い。なお、下地膜 2 6 0 2 は基板 2 6 0 1 にがら不純物が半導体層に拡散することを防ぐために設けるものであり、基板 2 6 0 1 にガラス基板や石英基板を用いている場合には下地膜 2 6 0 2 は設けなくてもよい。

#### [0199]

下地膜2602上に島状の半導体層を有する。半導体層にはN型のチャネルが形成されるチャネル形成領域2603、ソース領域又はドレイン領域となる不純物領域2605、低濃度不純物領域(LDD領域)2604、抵抗素子として機能する半導体層2606が形成されている。そして、チャネル形成領域2603及び半導体層2606上にゲート絶縁膜2607を介してゲート電極2608及び第1の配線2609を有している。ゲート絶

10

20

30

40

縁膜2607としてはCVD法やスパッタ法により形成される酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を用いることができる。また、ゲート電極2608としてはアルミニウム(A1)膜、銅(Cu)膜、アルミニウム又は銅を主成分とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル(TaN)膜、チタン(Ti)膜、タングステン(W)膜、モリブデン(Mo)膜等を用いることができる。

# [0200]

ゲート電極 2 6 0 8 の脇にはサイドウォール 2 6 1 7 が形成されている。ゲート電極 2 6 0 8 を覆うようにシリコン化合物、例えば、酸化シリコン膜、窒化シリコン膜若しくは酸化窒化シリコン膜を形成した後、エッチバックしてサイドウォール 2 6 1 7 を形成することができる。

## [0201]

なお、LDD領域2604はサイドウォール2617の下部に位置している。つまり、自己整合的にLDD領域2604が形成されている。

## [0202]

ゲート電極2608、サイドウォール2617およびゲート絶縁膜2607上には第1の層間絶縁膜2610を有している。第1の層間絶縁膜2610は下層に無機絶縁膜、上層に樹脂膜を有している。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

# [ 0 2 0 3 ]

また、第1の層間絶縁膜2610上には、第2の配線2611と第3の配線2612と画素電極2613を有している。なお、第2の配線2611はコンタクトホールを介して、純物領域2605と電気的に接続されている。また、第3の配線2612は、コンタクトホールを介して、不純物領域2618と第1の配線2609と接続されている。また、第2の配線2611や第3の配線2612としては、チタン(Ti)膜やアルミニウム(A1)膜や銅(Cu)膜やTiを含むアルミニウム膜などを用いることができる。なおには、五、1)膜や銅(Cu)膜やTiを含むアルミニウム膜などを用いることができる。なおには、第2の配線2611や第3の配線2612と同じ層に信号線などの配線を設ける場合には、近季関数の配線2611を引動を設ける場合には、近季関数のでは、カングステン(W)膜、亜鉛(2m)膜、プラチナ(Pt)膜などの単層膜の他、定りがステン(W)膜、亜鉛(2m)膜、プラチナ(Pt)膜などの単層膜の他、ラングステン(W)膜、亜鉛(2m)膜、プラチナ(Pt)膜などの単層膜の他、充りに、タングステン(W)膜、亜鉛(2m)膜、プラチナ(Pt)膜などの単層膜の他、充めとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とするにまなができる。光を反射する金属膜を用いることで光を透過させない陽極を形成することができる。光を反射する金属膜を用いることで光を透過させない陽極を形成することができる。

#### [0204]

第2の配線2611、第3の配線2612及び第1の層間絶縁膜2610上であって画素電極2613の端部を覆って絶縁物2614が形成されている。絶縁物2614としては、例えば、ポジ型の感光性アクリル樹脂膜を用いることができる。

## [0205]

絶縁物 2614及び画素電極 2613上には有機化合物を含む層 2615を有し、有機化合物を含む層 2615上には対向電極 2616を有する。画素電極 2613と対向電極 2616とで有機化合物を含む層 2615が挟まれる領域に発光素子が形成される。対向電極 2616に用いる材料としては、仕事関数の小さい材料を用いることが望ましい。例えば、アルミニウム(Al)、銀(Ag)、リチウム(Li)、カルシウム(Ca)、若しくはこれらの合金又は、MgAg、MgIn、AlLi、CaF<sub>2</sub>、若しくはCa<sub>3</sub>N<sub>2</sub>などの金属薄膜を用いることができる。こうして薄い金属薄膜を用いることで光を透過させることが可能な陰極を形成することができる。

## [0206]

こうして、トランジスタ2619、トランジスタ2620、抵抗素子2621が形成され

20

10

30

40

20

30

40

50

る。トランジスタ2619、トランジスタ2620、抵抗素子2621はそれぞれ図23のスイッチングトランジスタ2302、トランジスタ2309、抵抗素子2308に相当する。なお、ここでは一例として上面射出構造の表示装置の場合について説明したがこれに限定されない。

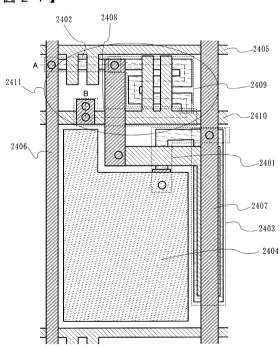

## [0207]

次に、図24の画素レイアウトについて説明する。画素は、駆動トランジスタ2401、 スイッチングトランジスタ 2 4 0 2 、容量素子 2 4 0 3 、画素電極 2 4 0 4 、第 1 の走査 線2405、信号線2406、電源線2407、抵抗素子2408、トランジスタ240 9、第2の走査線2410を有している。スイッチングトランジスタ2402は、ゲート 端子が第1の走査線2405の一部で構成され、第1端子(ソース端子又はドレイン端子 )が信号線2406に接続され、第2端子(ソース端子又はドレイン端子)が駆動トラン ジスタ2401のゲート端子と接続されている。また、トランジスタ2409は、ゲート 端子が第2の走査線2410の一部で構成され、第1端子(ソース端子又はドレイン端子 )が駆動トランジスタ2401のゲート端子と接続され、第2端子(ソース端子又はドレ イン端子)が抵抗素子2408を介して第2の走査線2410と接続されている。なお、 抵抗素子2408はトランジスタ2409の第1端子となる不純物領域(ソース領域又は ドレイン領域)と同じ層の半導体層であり、第2の走査線2410の下に位置している。 なお、このとき、半導体層の幅の方が第2の走査線2410の幅よりも太くなるようにし てもよい。第2の走査線2410よりもはみ出した部分の半導体層には、不純物を添加す ることが可能なので、不純物の添加される部分の面積を調整することにより、抵抗値を制 御することができる。また、駆動トランジスタ2401は、第1端子(ソース端子又はド レイン端子)が電源線2407に接続され、第2端子(ソース端子又はドレイン端子)が 画素電極2404と接続されている。また、駆動トランジスタ2401のゲート端子を構 成する電極の一部を第1の電極とし、駆動トランジスタ2401の第1端子となる不純物 領域(ソース領域又はドレイン領域)と同じ層の半導体層と電源線2407の一部とで第 2の電極とする、容量素子2403が形成されている。なお、図24の画素レイアウトは 、図21の画素におけるレイアウトの一例であってこれに限定されない。図24の駆動ト ランジスタ2401、スイッチングトランジスタ2402、容量素子2403、第1の走 査線2405、信号線2406、電源線2407、抵抗素子2408、トランジスタ24 0 9 、 第 2 の走査線 2 4 1 0 は、それぞれ図 2 1 の駆動トランジスタ 1 0 1 、スイッチン グトランジスタ102、容量素子103、第1の走査線105、信号線106、電源線1 0 7 、抵抗素子2 1 0 1 、トランジスタ 1 8 0 1 、第 2 の走査線 1 1 0 に相当する。また 、画素電極2404上に発光層と対向電極が形成されることにより、図21に示す発光素 子104が完成する。

## [0208]

なお、抵抗素子2408の構造をより詳しく説明するため、楕円2411で囲む付近を拡大した図を図27(b)に示す。また、その断面をより詳しく説明するため破線AB間の断面図を図27(a)に示す。なお、図27(b)では、第2の走査線2410の下層に位置する半導体層を点線で示している。

## [0209]

図 2 7 (a)の断面図を用いて説明する。基板 2 7 0 1上に下地膜 2 7 0 2を有している。基板 2 7 0 1としてはガラス基板、石英基板、プラスチック基板、セラミックス基板等の絶縁性基板、金属基板、半導体基板等を用いることができる。下地膜 2 7 0 2 は CVD 法やスパッタ法により形成することができる。例えば  $SiH_4$ 、 $N_2O$ 、 $NH_3$ を原料に用いた CVD 法により形成した酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を適用することができる。また、これらの積層を用いても良い。なお、下地膜 2 7 0 2 は基板 2 7 0 1 から不純物が半導体層に拡散することを防ぐために設けるものであり、基板 2 7 0 1 にガラス基板や石英基板を用いている場合には下地膜 2 7 0 2 は設けなくてもよい。

#### [0210]

下地膜2702上に島状の半導体層を有する。半導体層にはN型のチャネルが形成される

チャネル形成領域2703、ソース領域又はドレイン領域となる不純物領域2705、低濃度不純物領域(LDD領域)2704、抵抗素子として機能する半導体層2706が形成されている。そして、チャネル形成領域2703及び半導体層2706上にゲート絶縁膜2707を介してゲート電極2708及び第1の配線2709を有している。ゲート絶縁膜2707としてはCVD法やスパッタ法により形成される酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を用いることができる。また、ゲート電極2708としてはアルミニウム(A1)膜、銅(Cu)膜、アルミニウム又は銅を主成分とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル(TaN)膜、チタン(Ti)膜、タングステン(W)膜、モリブデン(Mo)膜等を用いることができる。

## [0211]

ゲート電極 2 7 0 8 の脇にはサイドウォール 2 7 1 7 が形成されている。ゲート電極 2 7 0 8 を覆うようにシリコン化合物、例えば、酸化シリコン膜、窒化シリコン膜若しくは酸化窒化シリコン膜を形成した後、エッチバックしてサイドウォール 2 7 1 7 を形成することができる。

## [0212]

なお、LDD領域 2 7 0 4 はサイドウォール 2 7 1 7 の下部に位置している。つまり、自己整合的にLDD領域 2 7 0 4 が形成されている。

## [0213]

ゲート電極2708、サイドウォール2717およびゲート絶縁膜2707上には第1の層間絶縁膜2710を有している。第1の層間絶縁膜2710は下層に無機絶縁膜、上層に樹脂膜を有している。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

### [0214]

また、第1の層間絶縁膜2710上には、第2の配線2711と第3の配線2712とを有している。なお、第2の配線2711はコンタクトホールを介して不純物領域2705と電気的に接続されている。また、第3の配線2712は、コンタクトホールを介して、不純物領域2718と第1の配線2709と接続されている。また、第2の配線2711や第3の配線2712としては、チタン(Ti)膜やアルミニウム(A1)膜や銅(Cu)膜やTiを含むアルミニウム膜などを用いることができる。なお、第2の配線2711や第3の配線2712と同じ層に信号線などの配線を設ける場合には低抵抗な銅を用いるとよい。

### [0215]

第2の配線2711、第3の配線2712及び第1の層間絶縁膜2710上に絶縁物27 14が形成されている。絶縁物2714としては、例えば、ポジ型の感光性アクリル樹脂膜を用いることができる。

## [0216]

絶縁物 2 7 1 4 上には有機化合物を含む層 2 7 1 5 を有し、有機化合物を含む層 2 7 1 5 上には対向電極 2 7 1 6 を有する。対向電極 2 7 1 6 に用いる材料としては、仕事関数の小さい材料を用いることが望ましい。例えば、アルミニウム(A 1 )、銀(A g )、リチウム(L i )、カルシウム(C a )、若しくはこれらの合金又は、M g A g、M g I n、A l L i、C a F  $_2$ 、若しくはC a  $_3$  N  $_2$  などの金属薄膜を用いることができる。こうして薄い金属薄膜を用いることで光を透過させることが可能な陰極を形成することができる

## [0217]

こうして、トランジスタ2719、トランジスタ2720、抵抗素子2721が形成される。トランジスタ2719、トランジスタ2720、抵抗素子2721はそれぞれ図24のスイッチングトランジスタ2402、トランジスタ2409、抵抗素子2408に相当する。なお、ここでは一例として上面射出構造の表示装置の場合について説明したがこれに限定されない。

10

20

30

20

30

40

50

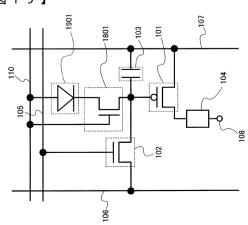

### [0218]

また、電流電圧変換素子1802として整流素子1901を適用した場合の構成を図19に示す。Nチャネル型のトランジスタ1801は、第1端子(ソース端子又はドレイン端子)を駆動トランジスタ101のゲート端子と接続し、ゲート端子を第2の走査線110に接続する。また、トランジスタ1801の第2端子(ソース端子又はドレイン端子)は整流素子1901を介して第2の走査線110と接続する。なお、整流素子1901は、第2の走査線110からトランジスタ1801の第2端子へ流れる電流の方向を順方向電流となるように接続する。

## [0219]

本構成によれば、画素に非点灯とするビデオ信号(駆動トランジスタ101をオフにするゲート電位Vsig(H))が入力され、第2の走査線110がLレベルとなっている場合において、トランジスタ1801がノーマリーオンとなっていても、整流素子1901に印加される電圧は逆方向電圧であるため電流は流れない。また、整流素子1901に逆方向電流(オフ電流)が流れる場合には、一定の電圧が整流素子1901に印加されていることになる。よって、トランジスタ1801の第2端子の電位は第2の走査線110のLレベルの電位より高くなる。つまり、トランジスタ1801は、ゲート端子よりもソース端子の電位が高くなるため、電流が流れにくくなる。つまり、オフ電流が低減される。

### [0220]

なお、整流素子1901は、PIN接合ダイオード、PN接合ダイオード、ショットキーダイオード、カーボンナノチューブを用いたダイオード、トランジスタ、ダイオード接続トランジスタなど、なんでもよい。より好ましくはPN接合ダイオードである。整流素子1901として、PN接合ダイオードを用いた場合について図20を用いて説明する。

## [0221]

Nチャネル型のトランジスタ1801は、第1端子(ソース端子又はドレイン端子)を駆動トランジスタ101のゲート端子と接続し、ゲート端子を第2の走査線110に接続する。また、トランジスタ1801の第2端子(ソース端子又はドレイン端子)はPN接合ダイオード2001のP型半導体領域は第2の走査線110と接続されている。なお、Nチャネル型のトランジスタ1801の第2端子はN型不純物領域を有しているので、PN接合ダイオード2001のN型半導体としてはNチャネル型のトランジスタ1801のN型不純物領域を用いることができる。つまり、トランジスタ1801のゲート端子と第2端子との間にP型の不純物領域を有していればよい。この画素のレイアウトを図14における断面図15(c)を用いて説明する。

## [0222]

本画素構成の特徴は、トランジスタ1516の一方の不純物領域側にP型の不純物領域1 5 2 9 を有する。つまり、図 1 4 におけるレイアウトにおいては、トランジスタ 1 4 0 9 の第2端子側の不純物領域において、チャネル形成領域から近い側がN型、遠い側がP型 の不純物領域となっている。よって、トランジスタ1516の一方の不純物領域の一部と P型の不純物領域1529とでPN接合ダイオード1530が形成される。他の共通する ところは図15(a)での説明を参照されたい。このように、PN接合ダイオード200 1のN型半導体領域はトランジスタ1801の第2端子となるN型の不純物が添加された 不純物領域を用いることができる。そして、この不純物領域が形成される半導体層にP型 の不純物を添加してP型の半導体領域を形成すれば、PN接合ダイオード2001とトラ ンジスタ1801とが直接的に接続されるので、コンタクトのための端子を設ける必要が なくなる。よって、画素のレイアウトにおいて、開口率の向上の観点からも有利である。 なお、P型の不純物領域とN型の不純物領域の間に不純物の添加されていない領域があっ てもよい。その場合にはPN接合ダイオード1602の代わりにPIN接合ダイオードと なる。PIN接合ダイオードだとオフ電流をより減らすことができる。また、PIN接合 ダイオードで発生する電圧がより大きくなるので、トランジスタ1801がよりオフしや すくなる。

20

30

40

50

### [0223]

なお、図20のような構成の画素の場合において、画素に非点灯とするビデオ信号(駆動トランジスタ101をオフにするゲート電位 V s i g (H))が入力され、第2の走査線110が L レベルのときに、トランジスタ1801にオフ電流が流れたとしても、P N 接合ダイオード2001に印加される電圧は逆方向電圧であるため、オフ電流は小さい。また、P N 接合ダイオード2001に逆方向電流が流れる場合、P N 接合ダイオード2001の両端子間には電圧が発生している。つまり、トランジスタ1801の第2端子の電位は、第2の走査線110のL レベルの電位より高くなる。よって、トランジスタ1801はゲート端子よりもソース端子の電位が高くなるため、トランジスタ1801には電流が流れにくくなる。つまり、オフ電流が低減される。

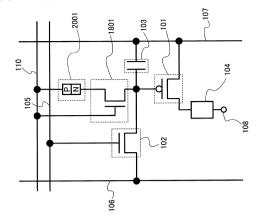

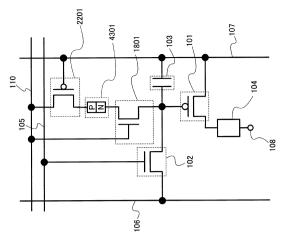

[0224]

また、電流電圧変換素子1802として、Pチャネル型トランジスタを用いることもできる。図22を用いて説明する。トランジスタ1801は、第1端子を駆動トランジスタ101のゲート端子と接続し、第2端子をPチャネル型のトランジスタ2201の第2端子(ソース端子又はドレイン端子)と接続する。また、トランジスタ1801のゲート端子を第2の走査線110と接続する。また、Pチャネル型のトランジスタ2201は、ゲート端子を電源線107と接続し、第1端子(ソース端子又はドレイン端子)を第2の走査線110と接続する。

[0225]

画素に非点灯とするビデオ信号(駆動トランジスタ101をオフにするゲート電位Vsig(H))が入力され、第2の走査線110がLレベルであったときに、トランジスタ1801がノーマリーオンであっても、トランジスタ2201の第2端子の電位はさほど電にはとはならない。そのため、トランジスタ2201は、ゲート端子の接続された電源線107の電位より第2端子の電位が低くなるので、Pチャネル型のトランジスタ2201はオフする。トランジスタ2201の第2端子の電位が低ければ低いほどこのトランジスタ2201に流れるオフ電流は小さくなる。一方、このトランジスタ2201の第2端子の電位が高くなると、トランジスタ1801はゲート端子より第2端子の電位が高くなる。ため、よりトランジスタ1801にはよりオフ電流が流れにくくなる。つまり、この構成によれば大幅なオフ電流の低減を図ることが可能となる。なお、第2の走査線110がトランジスタ1801はオンする。また、このときトランジスタ1801の第2端子は第2の走査線110より低くなるので、トランジスタ1801の第2端子は第2の走査線110より低くなるので、トランジスタ1801もオンする。よって、画素を非点灯にする信号を駆動トランジスタ101のゲート端子に入力することができる。

[0226]

ここで、一般的にNチャネル型のトランジスタはLDD領域を形成し易いため、Nチャネル型のトランジスタを用いることによりオフ電流の低減を図ることができる。しかし、活性層(チャネル形成領域)に多結晶シリコン膜を用いると、N型化する傾向が強いため、Nチャネル型のトランジスタはややディプレッション型トランジスタになりやすい。このとき、Pチャネル型のトランジスタはエンハンスメント型トランジスタになるので、Nチャネル型のトランジスタ及びPチャネル型のトランジスタを組み合わせて用いることにより、効果的にオフ電流を低減することができる。

[0227]

なお、図22のような構成の場合には、トランジスタ1801とトランジスタ2201の間にPN接合ダイオードを設けてもよい。つまり、図43に示すように、トランジスタ1801の第2端子にPN接合ダイオード4301のP型半導体領域を接続し、トランジスタ2201の第2端子にPN接合ダイオード4301のP型半導体領域を接続する。なお、このとき、トランジスタ2201の第2端子となる不純物領域をPN接合ダイオード4301のP型半導体領域として、トランジスタ1801の第2端子となる不純物領域をPN接合ダイオード4301のN型半導体領域として用いることにより、トランジスタ18

01とPN接合ダイオード4301との接続や、Pチャネル型のトランジスタ2201とPN接合ダイオード4301との接続のために、コンタクトを設ける必要がない。これは、図15(c)や、図20の場合と同様である。よって、画素の開口率を高くする観点においても有利である。なお、P型の不純物領域とN型の不純物領域の間に不純物の添加されていない領域があってもよい。その場合にはPN接合ダイオード4301の代わりにPIN接合ダイオードとなる。PIN接合ダイオードだとオフ電流をより減らすことができる。また、PIN接合ダイオードで発生する電圧がより大きくなるので、トランジスタ1801がよりオフしやすくなる。

## [0228]

また、実施の形態1の図1で示した画素の整流素子109の代わりに、Pチャネル型のトランジスタと電流電圧変換素子とを組み合わせて用いる場合について図50を用いて説明する。

### [0229]

Pチャネル型のトランジスタ5001は、第1端子(ソース端子又はドレイン端子)が電流電圧変換素子5002を介して駆動トランジスタ101のゲート端子と接続され、ゲート端子が第2の走査線110に接続されている。また、トランジスタ5001の第2端子(ソース端子又はドレイン端子)は第2の走査線110と接続されている。

### [0230]

なお、電流電圧変換素子5002は、電流が流れるとその両端子間に電圧が発生する素子である。

### [0231]

よって、本実施の形態に示す画素構成により、例えば図8を用いて説明した駆動方法を実現することができる。

### [0232]

## (実施の形態3)

本実施の形態では、画素を非点灯(黒表示)にすべきときに、発光素子がわずかに発光してしまうことを防ぐことがより可能な画素構成を示す。つまり、駆動トランジスタにオフ電流が流れても、発光素子へは電流が流れないようにする。

### [0233]

図56に示す画素は、駆動トランジスタ5601と、相補用トランジスタ5611と、ス イッチングトランジスタ5602と、発光素子5604と、整流素子5609と、第1の 走査線5605と、信号線5606と、電源線5607と、第2の走査線5610とを有 する。なお、駆動トランジスタ5601はPチャネル型トランジスタであり、相補用トラ ン ジ ス 夕 5 6 1 1 及 び ス イ ッ チ ン グ ト ラ ン ジ ス 夕 5 6 0 2 は N チ ャ ネ ル 型 ト ラ ン ジ ス 夕 で ある。そして、スイッチングトランジスタ5602は第1端子(ソース端子又はドレイン 端子)が信号線5606に接続され、第2端子(ソース端子又はドレイン端子)が駆動ト ランジスタ5601及び相補用トランジスタ5611のゲート端子に接続されている。駆 動トランジスタ5601及び相補用トランジスタ5611の第2端子(ソース端子又はド レイン端子)は、発光素子5604の画素電極と接続されている。駆動トランジスタ56 0 1 の第 1 端子は電源線 5 6 0 7 に接続されている。また、相補用トランジスタ 5 6 1 1 の第2端子は配線5612に接続されている。また、駆動トランジスタ5601及び相補 用トランジスタ5611のゲート端子は、容量素子5603の一方の電極と接続されてい る。容量素子5603の他方の電極は電源線5607に接続されている。また、駆動トラ ンジスタ 5 6 0 1 及び相補用トランジスタ 5 6 1 1 のゲート端子が整流素子 5 6 0 9 を介 して第2の走査線5610に接続されている。

## [0234]

なお、電源線5607には、高電源電位が入力され、発光素子5604の対向電極には低電源電位が入力されている。高電源電位と低電源電位とは高電源電位>低電源電位を満たす関係であり、また、高電源電位と低電源電位との電位差が発光素子5604の順方向しきい値電圧となるようにする。

10

20

30

40

#### [0235]

また、配線5612の電位は発光素子5604の対向電極5608の電位と等しいか、又はそれ以下の電位とすることが望ましい。

## [0236]

まず、画素への信号書き込み動作について説明する。画素へ信号の書き込みを行う際には、第1の走査線5605にHレベルの信号を入力し、スイッチングトランジスタ5602をオンにする。そして、信号線5606からビデオ信号を画素へ書き込む。つまり、駆動トランジスタ5601及び相補用トランジスタ5611のゲート端子にビデオ信号を入力する。なお、このとき、第2の走査線5610はLレベルにしておく。

## [0237]

このとき、容量素子5603に電荷が蓄積される。よって、第1の走査線5605にLレベルの信号が入力され、スイッチングトランジスタ5602がオフしても、ビデオ信号の電位は容量素子5603によって保持される。

## [0238]

よって、ビデオ信号が画素を点灯にするVsig(L)の場合には、駆動トランジスタ5601がオンし、相補用トランジスタ5611がオフする。そして、駆動トランジスタ5601を介して電源線5607に入力されている電位を発光素子5604の画素電極へ供給することができる。

## [0239]

また、ビデオ信号が画素を非点灯にするVsig(H)の場合には、駆動トランジスタ5601がオフし、相補用トランジスタ5611がオンする。よって、電源線5607に入力されている電位は発光素子5604の画素電極へ供給されない。しかし、駆動トランジスタ5601がノーマリーオンとなっているときには、駆動トランジスタ5601にわずかに電流が流れてしまうことがある。通常このオフ電流が発光素子に流れてしまうため発光素子がわずかに発光してしまい、画素を非点灯(黒表示)にできず、表示不良を起こしてしまうことがある。しかし、本画素構成によれば、駆動トランジスタ5601に流れるオフ電流が、相補用トランジスタ5611を介して配線5612に流れるため、発光素子5604へは電流が流れない。つまり、画素を非点灯(黒表示)にすることができる。なぜなら、このとき相補用トランジスタ5611はオンしているため、配線5612に電流が流れるからである。

## [0240]

なお、配線5612の電位を発光素子5604の対向電極の電位より低くすることにより、発光素子5604に逆バイアスの電圧を印加することができる。このように、逆方向バイアスの電圧を発光素子5604に印加しても、正常な発光素子5604には電流は流れない。一方、発光素子5604に短絡箇所が有る場合には、その短絡箇所に電流が流れる。すると、短絡箇所に集中して電流が流れ、発光素子5604の短絡箇所が絶縁される。発光素子5604の短絡箇所を絶縁することにより、画素の表示不良を改善することができる。また、発光素子5604の寿命を延ばすことが可能となる。

## [ 0 2 4 1 ]

なお、第1の走査線5605のHレベルの信号は、画素を非点灯にするビデオ信号(駆動トランジスタ5601をオフにするゲート電位Vsig(H))よりもスイッチングトランジスタ5602のしきい値電圧Vth分以上高い電位V1とすることが望ましい。なぜなら、スイッチングトランジスタ5602はNチャネル型のトランジスタであるため、信号線5606にVsig(H)が入力されると、第1端子がドレイン端子となる。したがって、スイッチングトランジスタ5602は、第2端子(このときにはソース端子)がゲート端子の電位より、スイッチングトランジスタ5602のしきい値電圧Vth分低い電位でオフしてしまう。つまり、スイッチングトランジスタ5602のゲート電位がV1より小さいと、信号線5606に入力されたVsig(H)を駆動トランジスタ5601のゲート端子に入力することができなくなってしまうからである。すると、駆動トランジスタ5601を完全にオフにすることができず、発光素子5604がわずかに発光してしま

10

20

30

40

うことがある。

## [0242]

また、第1の走査線5605のLレベルの信号は、Vsig(L)よりも低い電位とすることが望ましい。例えば、第1の走査線5605のLレベルの信号が、画素を点灯にするビデオ信号(駆動トランジスタ5601がオンするゲート電位Vsig(L))と等しい電位である場合、Vsig(H)が書き込まれている画素は、他の行の画素への信号書き込みのために信号線5606にVsig(L)が入力されると、スイッチングトランジスタ5602のゲートソース間電圧は0Vとなる。すると、スイッチングトランジスタ5602がノーマリーオンとなってしまっているときにはオフ電流が流れてしまう。したがって、容量素子5603に蓄積された電荷が放電し、駆動トランジスタ5601のゲート電位が低くなることにより、駆動トランジスタ5601に電流が流れ、発光素子5604がわずかに発光してしまうことがある。

### [0243]

次に消去動作について説明する。第2の走査線5610にHレベルの信号を入力する。すると、整流素子5609に電流が流れる。すると、駆動トランジスタ5601及び相補用トランジスタ5611のゲート端子の電位をある電位にすることができる。この電位は、第2の走査線5610のHレベルの電位より整流素子5609のしきい値電圧分低い電位である。よって、消去動作により、画素を非点灯にするため、第2の走査線5610に入力するHレベルの電位はビデオ信号Vsig(H)より整流素子5609のしきい値電圧分高い電位とするとよい。

### [0244]

このとき、第2の走査線5610に入力するHレベルの信号は、電源線5607に入力される高電源電位以上の電位とすることが望ましい。このHレベルの信号の電位を適宜設定することにより、消去期間において駆動トランジスタ5601を強制的にオフさせる場合に、駆動トランジスタ5601のゲート端子の電位をソース端子の電位よりも高くすることができる。したがって、駆動トランジスタ5601がノーマリーオンの場合でも駆動トランジスタ5601をオフにし、発光素子5604がわずかに発光してしまうのを防ぐことができる。

## [0245]

なお、第2の走査線5610のHレベルは、第1の走査線5605のHレベルと同じでもよい。その結果、電源数を削減することができる。

## [0246]

なお、消去動作時以外は、第2の走査線5610はLレベルの信号とする。このLレベルの信号の電位は、画素を点灯とするビデオ信号(駆動トランジスタ5601をオンにするゲート電位Vsig(L))以下の電位とすることが望ましい。しかし、このLレベルの電位を低くし過ぎると、画素に非点灯のビデオ信号(駆動トランジスタ5601をオフにするゲート電位Vsig(H))が書き込まれていた場合に、整流素子5609に印加される逆バイアス電圧が大きくなってしまうことにより、整流素子5609へ流れるオフ電流(逆方向電流ともいう)が大きくなってしまい、容量素子5603に保持した電荷が漏れてしまう。そして、駆動トランジスタ5601のゲート電位が低くなり、駆動トランジスタ5601のオフ電流が大きくなってしまう。よって、好ましくは、このLレベルの信号の電位は、画素を点灯にするビデオ信号(駆動トランジスタ5601をオンにするゲート電位Vsig(L))と等しくするとよい。

## [0247]

なお、図56の整流素子5609には、抵抗素子、PN接合ダイオード、PIN接合ダイオード、ショットキー型のダイオード、ダイオード接続したトランジスタ、カーボンナノチューブで形成されたダイオードのいずれか一又はそれらの組み合わせを用いることができる。実施の形態1で示した構成を適宜用いることができる。

## [0248]

また、整流素子の代わりに、電位伝達素子を用いることもできる。電位伝達素子としては

10

20

40

30

、実施の形態2で示した様々な構成を用いることができる。

## [0249]

なお、本画素構成では、ビデオ信号の電位や、第2の走査線に入力する電位を適宜設定することにより、駆動トランジスタのオフ電流を低減することができる。さらに、駆動トランジスタと相補的にオンオフする相補用トランジスタを設けることにより、駆動トランジスタにオフ電流が流れても、画素を非点灯(黒表示)にすることができるため、表示不良を防止することができる。

## [0250]

なお、配線 5 6 1 2 と発光素子 5 6 0 4 の対向電極に入力する電位を等しくする場合には、配線 5 6 1 2 と対向電極 5 6 0 8 とを接続することにより、対向電極の抵抗を低くすることができるため消費電力の低減を図ることができる。

10

## [ 0 2 5 1 ]

その場合についての画素の部分断面について図57を用いて説明する。

### [0252]

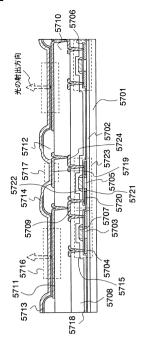

基板 5 7 0 1 上に下地膜 5 7 0 2 を有している。基板 5 7 0 1 としてはガラス基板、石英基板、プラスチック基板、セラミックス基板等の絶縁性基板、金属基板、半導体基板等を用いることができる。下地膜 5 7 0 2 は C V D 法やスパッタ法により形成することができる。例えば S i H  $_4$  、 N  $_2$  O 、 N H  $_3$  を原料に用いた C V D 法により形成した酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を適用することができる。また、これらの積層を用いても良い。なお、下地膜 5 7 0 2 は基板 5 7 0 1 から不純物が半導体層に拡散することを防ぐために設けるものであり、基板 5 7 0 1 にガラス基板や石英基板を用いている場合には下地膜 5 7 0 2 は設けなくてもよい。

20

## [0253]

下地膜5702上に島状の半導体層を有する。半導体層にはP型のチャネルが形成されるチャネル形成領域5703、ソース領域又はドレイン領域となる不純物領域5704、N型のチャネルが形成されるチャネル形成領域5705、ソース又はドレイン領域となる不純物領域5720、低濃度不純物領域(LDD領域)5721が形成されている。そして、チャネル形成領域5703及びチャネル形成領域5705上にゲート絶縁膜5706を介してゲート電極5707を有している。ゲート絶縁膜5706としてはCVD法やスパッタ法により形成される酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を用いることができる。また、ゲート電極5707としてはアルミニウム(A1)膜、銅(Cu)膜、アルミニウム又は銅を主成分とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル(TaN)膜、チタン(Ti)膜、タングステン(W)膜、モリブデン(Mo)膜等を用いることができる。

30

## [0254]

ゲート電極 5 7 0 7 の脇にはサイドウォール 5 7 2 2 が形成されている。ゲート電極 5 7 0 7 を覆うようにシリコン化合物、例えば、酸化シリコン膜、窒化シリコン膜若しくは酸化窒化シリコン膜を形成した後、エッチバックしてサイドウォール 5 7 2 2 を形成することができる。

[0255]

40

なお、LDD領域5721はサイドウォール5722の下部に位置している。つまり、自己整合的にLDD領域5721が形成されている。なお、サイドウォール5722は、LDD領域5721を自己整合的に形成するために設けているのであって、必ずしも設けなくともよい。

## [0256]

ゲート電極 5 7 0 7、サイドウォール 5 7 2 2 およびゲート絶縁膜 5 7 0 6 上には第 1 の層間絶縁膜を有している。第 1 の層間絶縁膜は下層に無機絶縁膜 5 7 1 8、上層に樹脂膜 5 7 0 8を有している。無機絶縁膜 5 7 1 8としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜 5 7 0 8 としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる

## [0257]

第1の層間絶縁膜上には、第1の電極5709及び第2の電極5724を有し、第1の電極5709はコンタクトホールを介して不純物領域5704及び不純物領域5720と電気的に接続されている。また、第2の電極5724はコンタクトホールを介して不純物領域5720と電気的に接続されている。第1の電極5709及び第2の電極5724としては、チタン(Ti)膜やアルミニウム(Al)膜や銅(Cu)膜やTiを含むアルミニウム膜などを用いることができる。なお、第1の電極5709及び第2の電極5724と同じ層に信号線などの配線を設ける場合には低抵抗な銅を用いるとよい。

## [0258]

第1の電極5709、第2の電極5724および第1の層間絶縁膜上に第2の層間絶縁膜5710を有する。第2の層間絶縁膜としては、無機絶縁膜や、樹脂膜、又はこれらの積層を用いることができる。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

### [0259]

第2の層間絶縁膜5710上には画素電極5711および配線5719を有している。画素電極5711および配線5719は同じ材料により形成されている。つまり、同じ層に同時に形成されている。画素電極5711や配線5719に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、窒化チタン(TiN)膜、クロム(Cr)膜、タングステン(W)膜、亜鉛(Zn)膜、プラチナ(Pt)膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜との1個できる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。光を反射する金属膜を用いることで光を透過させない陽極を形成することができる。

### [0260]

画素電極 5 7 1 1 および配線 5 7 1 9 の端部を覆うように絶縁物 5 7 1 2 を有する。例えば、絶縁物 5 7 1 2 としては、ポジ型の感光性アクリル樹脂膜を用いることができる

### [0261]

画素電極5711上に有機化合物を含む層5713が形成され、有機化合物を含む層5713の一部は絶縁物5712上に重なっている。なお、有機化合物を含む層5713は、配線5719上には形成されていない。

## [0262]

有機化合物を含む層 5 7 1 3 、絶縁物 5 7 1 2 および配線 5 7 1 9 上に対向電極 5 7 1 4 を有している。対向電極 5 7 1 4 に用いる材料としては、仕事関数の小さい材料を用いることが望ましい。例えば、アルミニウム(A 1 )、銀(A g )、リチウム(L i )、カルシウム(C a )、若しくはこれらの合金又は、M g A g 、M g I n 、A 1 L i 、C a F  $_2$  、若しくはC a  $_3$  N  $_2$  などの金属薄膜を用いることができる。こうして薄い金属薄膜を用いることで光を透過させることが可能な陰極を形成することができる。

### [0263]

対向電極 5 7 1 4 と画素電極 5 7 1 1 とにより有機化合物を含む層 5 7 1 3 が挟まれた領域では発光素子 5 7 1 6 が形成されている。

### [0264]

また、絶縁物5712により有機化合物を含む層5713が隔離されている領域では、接合部5717が形成され、対向電極5714と配線5719とが接している。よって、配線5719が対向電極5714の補助電極として機能し、対向電極5714を低抵抗化することができる。よって、対向電極5714の膜厚を薄くすることができ、透過率を高くすることができる。したがって、発光素子5716から得られる光を上面から取り出す上

10

20

30

40

20

30

40

50

面射出構造において、より高い輝度を得ることができる。

## [0265]

なお、対向電極 5 7 1 4 をより低抵抗化するため、金属薄膜と透明導電膜(ITO(インジウムスズ酸化物)、インジウム亜鉛酸化物(IZO)、酸化亜鉛(ZnO)等)との積層を用いてもよい。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることによっても光を透過させることが可能な陰極を形成することができる。

### [0266]

なお、不純物領域 5 7 0 4 には P型の不純物がドーピングされている。また、不純物領域 5 7 2 0 には N型の不純物がドーピングされている。よって、トランジスタ 5 7 1 5 は P チャネル型のトランジスタであり、トランジスタ 5 7 2 3 は N チャネル型のトランジスタである。

### [0267]