# UK Patent Application (19) GB (11) 2 143 954 A

(43) Application published 20 Feb 1985

(21) Application No 8319790

(22) Date of filing 22 Jul 1983

(71) Applicant Sharetree Limited (United Kingdom), 70 Westward Road, Stroud, Gloucestershire GL5 4JA

(72) Inventor Michael William Rignall

(74) Agent and/or Address for Service Haseltine Lake & Co, Hazlitt House, 28 Southampton Buildings, Chancery Lane, London WC2A 1AT

(51) INT CL3 G01R 31/02 31/28

(52) Domestic classification G1U C8 U1S 2087 2197 G1U

(56) Documents cited

GB A 2062250 GB 1572154 GB 0959565 GB A 2058363 GB 1306757 GB 0845504 GB A 2025073 GB 1172683

(58) Field of search G1U

#### (54) A capacitive method and apparatus for checking connections of a printed circuit board

(57) A first conductive plate (C1) connected to an a.c. voltage source (V1) is placed adjacent and spaced from a terminal (A2) of a printed circuit board. A conductive track between this terminal (A2) and another terminal (C4) is then energised, a signal being obtained by voltmeter (V) as a result of such energisation and capacitive coupling between the terminal (C4) and the voltmeter (V). In this way, the connections of a printed circuit board can be checked using capacitive coupling and without reliance on an ohmic connection.

### FIG.3.

FIG.3.

2 / 5

|       |   |   |   |   |   |   |   |   | ,      |              |

|-------|---|---|---|---|---|---|---|---|--------|--------------|

| DRIVE | a | р | С | d | е | f | g | h | BINARY | <del>.</del> |

| Δ1    | 1 |   |   |   |   |   |   |   | 129    |              |

| A2    |   | 1 |   |   |   |   |   | 1 | 130    |              |

| Δ3    |   |   | ı |   |   |   |   |   | 132    |              |

| Δ4    |   |   |   | ı |   |   |   | ı | 136    |              |

| B1    |   |   |   |   |   |   | 1 |   | 65     |              |

| B2    |   | 1 |   |   |   |   | 1 |   | 66     | FIG.2A.      |

| B3    |   |   | 1 |   |   |   | 1 |   | 68     |              |

| B4    |   |   |   | 1 |   |   |   |   | 72     |              |

| C1    |   |   |   |   |   | - |   |   | 33     |              |

| C2    |   | 1 |   |   |   | ŀ |   |   | 34     |              |

| C3    |   |   | ı |   |   | 1 |   |   | 36     |              |

| C4    |   |   |   | 1 |   | 1 |   |   | 40     |              |

| 01    |   |   |   |   |   |   |   |   | 17     |              |

|       |   |   |   |   |   |   |   |   |        |              |

| Α1    |   |   |   |   |   |   |   |   | 195    |              |

| A2    |   | 1 |   |   |   |   |   | 1 | 154    |              |

| A3    |   |   | 1 |   |   |   |   | l | 140    |              |

| Δ4    |   |   | 1 |   |   |   |   | 1 | 140    |              |

| B1    |   |   |   |   |   |   |   |   | 65     | FIG.2B.      |

| B2    |   | 1 |   |   |   |   | 1 |   | 195    |              |

| B3    |   |   |   |   |   | 1 | 1 |   | 100    |              |

| B4    |   |   |   |   |   |   | 1 |   | 72     |              |

| C1    |   |   |   |   |   | 1 |   |   | 33     |              |

| C2    |   | 1 |   |   |   | 1 |   |   | 34     |              |

| C3    |   |   |   |   |   |   |   |   | 100    |              |

| C4    |   |   |   |   |   | 1 |   |   | 40     |              |

| D1    |   | 1 |   |   | 1 |   |   |   | 19     |              |

3 / 5

5

#### **SPECIFICATION**

## A method of and apparatus for checking connections of a printed circuit board

The present invention relates to a method of and apparatus for checking connections of a printed circuit board.

The cost of a bare board tester depends on software and on the maximum number of points. In addition, for each new type of printed circuit board (PCB) to be tested, a new pin jig is required.

A pin jig is an array of spring-loaded pins

15 designed to contact each point to be tested.

Such jigs must be jig-drilled to obtain adequate precision, and their cost depends on the number of installed test points. For a PCB manufacturer requiring per annum 15–20 jigs

20 to test, say, a 2000 point PCB a considerable capital outlay is involved.

A lower cost method of making the replaceable jig component of the tester would result in a considerable saving for manufacturers.

According to the present invention from one aspect, there is provided a method of checking the connection via a conductive track between first and second terminals of a 30 printed circuit board, wherein a first electrically conductive member connected to a source of alternating voltage is placed adjacent and spaced from the first terminal for electrically energising the conductive track by 35 capacitive coupling between the first terminal and the first member; and a second electrically conductive member is placed adjacent and spaced from the second terminal for obtaining an output signal, as a result of such 40 energisation of the track and its connection of the first and second terminals, by capacitive coupling between second terminal and the second member.

According to the present invention from

45 another aspect, there is provided an apparatus, for carrying out the method described in the preceding paragraph, comprising: a first electrically conductive member which, in use of the apparatus, is placed adjacent and

50 spaced from the first terminal; applying an alternating voltage to the first member for electrically energising the conductive track by capacitive coupling between the first terminal and the first member; a second electrically

55 conductive member which, in use of the apparatus, is placed adjacent and spaced from the second terminal; and means for obtaining an

of the track and its connection of the first and second terminals by capacitive coupling between the second terminal and the second member.

output signal, as a result of such energisation

For a better understanding of the present invention and to show how the same may be 65 carried into effect, reference will now be

made, by way of example, to the accompanying drawings, in which:-

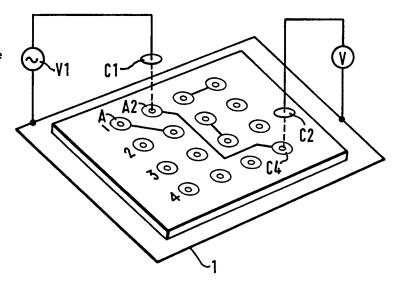

Figure 1 illustrates how a method according to an embodiment of the present invention 70 may be applied to conventional jigs;

Figures 2A and 2B are tables showing respectively typical signatures, from a connected and from an unconnected PCB;

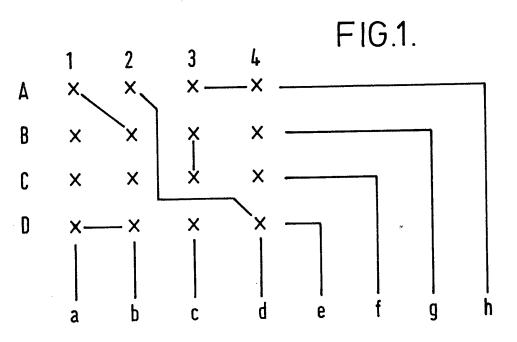

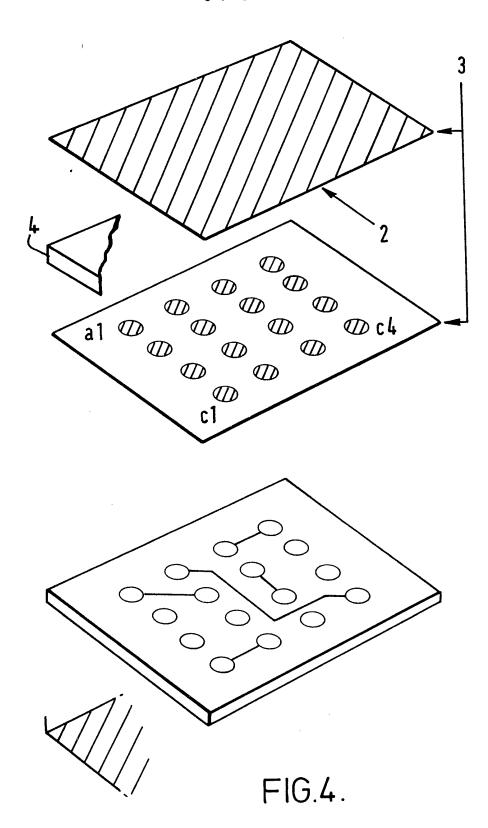

Figure 3 shows the PCB of Fig. 1 in isomet-75 ric form with added components;

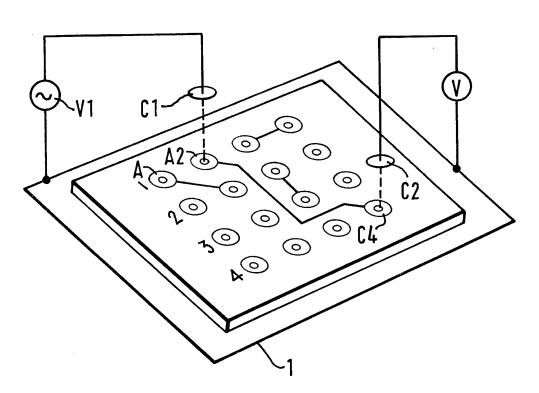

Figure 4 illustrates the construction of the PCB of Figs. 1 and 3;

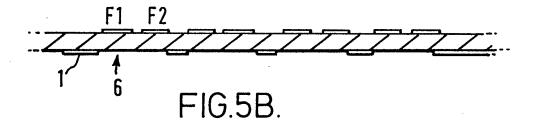

Figures 5A and 5B illustrate the connections of pads on a master PCB;

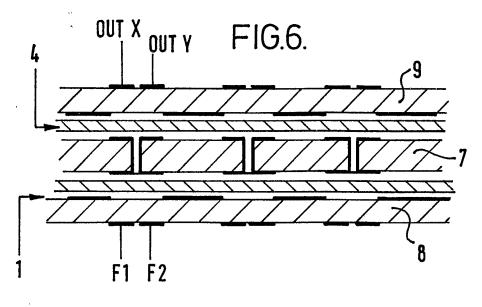

80 Figure 6 shows the construction of a PCB tester; and

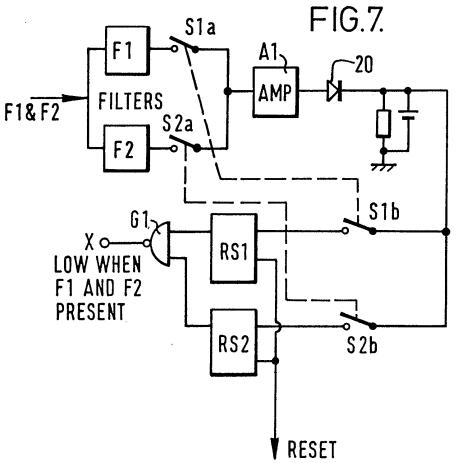

Figure 7 shows one embodiment of a sense amplifier.

In Fig. 1, signature generation is accom-85 plished by sequentially applying a signal to A1, A2, A3, A4, B1, B2, etc. The resultant signature is shown in Fig. 2. Each point is connected to a horizontal row (e - h) AND to a vertical column (a - d) by a diode. Thus, if no 90 links existed on the PCB the signature is as shown in Fig. 2A, which is modified to that shown in Fig. 2B when the PCB is connected.

The points a - h are in practice an 8-bit word, with a binary value as shown in the last column, and are stored in a memory for subsequent comparison with the signature from an untested board. For this system to be cost-effective, a bulk electrically alterable read only memory (EAROM) (for example 2K ×

100 96) must be available for a 2K point system. EAROM is an electrically erasable, hence reusable, memory that retains its data when shut down. The cost of a memory block for a 2K jig is negligible in comparison with the present cost of known jigs.

It can be seen that the above-described principle depends on applying a signal to A1 etc. and detecting its presence on the eight lines a - h. All known systems have used d.c., 110 usually 5V., signals.

The system to be described hereinbelow relies on capacitive coupling to the test area, not on an ohmic connection.

Fig. 3 shows the PCB with tracks. C1 and 115 C2 are small circular discs with a diameter similar to a pad below. Two plates are required, C1 being a transmitter coupled to an r.f. source V1, and C2 being a receiver coupled to a sensitive r.f. volt-meter V. Application of a voltage from source V1 to the approximate.

120 of a voltage from source V1 to the capacitor C1 will cause the track from A2 to C4 to become r.f. "live". This state may be detected by positioning C2 above the output pad C4, as shown in Fig. 3.

125 The choice of frequency is a compromise between a high frequency, with improved coupling between C1 and the pad A2, and a low frequency to reduce points effects which may couple adjacent tracks.

130 In practice both sides of the PCB will be

covered by ground planes 1 with cut-outs 6 at the pad areas (Fig. 5B) to minimise this fringing. This operation will now be described with reference to Fig. 4. A copper capacitor plate 2 at C4 can be automatically positioned above pad A4 etc. by means of a double sided PCB 3. An important point to note is that the PCB comprising the upper capacitor plate at C4 is in fact using the solder resist mask of the PCB below. A PCB manufacturer therefore has the ability to produce this component at low cost in his own plant. Reference numeral 4 denotes an insulating layer.

It can be seen that both input and output 15 capacitor plates are automatically created at the same time.

The next step is to generate a means of scanning all of the test points and converting the result of this scan into an 8-line signal compatible with the standard logic required by Fig. 1.

This could be done by adopting a modified approach employing two frequencies in an XY matrix, with PCB being employed on the input 25 side, the lower surface is used for detection.

This step will require that the system is only usable with double sided PTH boards. In practice, however, as these high complexity boards are the only ones which would nor-30 mally be tested this is not a disadvantage.

The preceding description has illustrated in outline a method of capacitive coupling between a fixed upper plate 2 and a PCB 1.

Next the r.f. signal must be switched from 35 point to point.

An optimum solution to this problem is found by using two frequencies on an XY grid as shown in Fig. 5A.

A series of adjacent semi circular or other

40 shaped copper pads 5 are etched on a master

PCB which is fixed and which constitutes a

fundamental part of the basic tester. One half

of each pad 5 is connected to a frequency F1

while the other half is connected to a fre-

45 quency F2. The signals are sequentially injected into lines 1-4 for F1 and A-D for F2.

As an example, for a master jig of 63.5cm square, 250 lines in X (A-D) and 250 lines in Y (1-4) axes are required, when employing a 50 0.1 pitch.

Each twin pad 5 will be scanned, but only one pad will have both F1 and F2 present. In this manner a complete array of 64K pads may be scanned.

55 In practice, a memory would direct the XY grid to points where pads existed on the PCB under test, thus saving scanning time. The PCB assembly shown in Fig. 5 is a permanent part of the tester and thus represents a single 60 capital cost only.

The remaining problem is now to detect pads 5 on the PCB 7 under test (Fig. 6) where both F1 and F2 are present. This differs from a conventional d.c. tester where only one 65 signal is required for detection.

Fig. 6 shows the construction of a complete tester showing the bottom PCB 8, as shown in Fig. 5, held, for example, by a vacuum in contact with the PCB7 under test. Finally a second PCB 9 of Fig. 5 type is used as the output sensor, the function of which is described in the next section.

At this point, two options are possible, either to use an upper board containing 250 × 250 sensors as a permanent fixture, with the attendant high cost of sense amplifiers for the r.f. on each of 500 lines, or to create a network connected to the 2K points actually used. The economies of these two options will be considered at a later stage.

The capacitance between upper and lower sections of test points on a jig will be of the order of 0.5 pF. This yields a reactance of 30K at 10 MHz. To use a higher frequency would enable lower impedance sense amplifiers to be employed, but would risk more "jump over" between scanning tracks due to standing wave problems.

To use a lower sense of frequency would 90 entail higher impedance amplifiers with the likely risk of stray coupling.

There is a further reason for the use of frequencies of the order of 10 MHz which is best explained with the description of a possible sense amplifier. It should be noted that a sense amplifier is defined as a system capable of detecting both F1 and F2 at a test point.

Fig. 7 shows one such possible system.

Two filters F1 and F2, with passband char-100 acteristics close to 10 MHz, are switched sequentially to an amplifier A1 with a feeding detector 20. If a signal is detected at one frequency either of two RS FLIP-FLOPS RS1, RS2 is set to a high output state. It can be

105 seen that respective second, synchronously operating switches S1a, b; S2a, b route the detector output to either RS1, set by F1, or RS2 set by F2. Only when both are present will the output of a NAND gate G1 fall low.

110 When the test has been performed on one XY pair of sense lines, a RESET pulses is applied at the next change of address to reset the sense amplifier for a new input.

In a dedicated 2K point system, 96 of these 115 amplifiers will be required (they represent, however, only a single capital cost), hence their price must be kept as low as possible.

The choice of 10 MHz as a nominal sense of frequency has two practical advantages 120 namely:

- (i) low cost filters are available at 9 and 10.7 MHz as cheap standard components; and

- (ii) on the drive side, 10 MHz signals are125 easily routed by standard LS series logic gates.

Two separate amplifiers, with associated decoding logic, may become viable depending on the prevailing market.

#### **CLAIMS**

- 1. A method of checking the connection via a conductive track between first and second terminals of a printed circuit board, 5 wherein a first electrically conductive member connected to a source of alternating voltage is placed adjacent and spaced from the first terminal for electrically energising the conductive track by capacitive coupling between the 10 first terminal and the first member; and a second electrically conductive member is placed adjacent and spaced from the second terminal for obtaining an output signal, as a result of such energisation of the track and its 15 connection of the first and second terminals, by capacitive coupling between the second terminal and the second member.

- A method as claimed in claim 1, wherein the connections via each of a plurality

of conductive tracks between respective first and second terminals are checked for a master printed circuit board to produce an output signature representative of the master printed circuit board, the signature being stored in a

storage means for subsequent comparison with an output signature of a printed circuit board under test.

- 3. A method as claimed in claim 1 or 2, the first electrically conductive member being 30 one of a plurality of such members forming an array, each such member comprising first and second parts each part being connectable to a source of voltage at first and second frequencies respectively, in which method the first 35 and second parts of the first electrically conductive members are sequentially connected to the respective voltage sources so that only one member is connected to both the first and second frequency voltage sources, the output 40 signal being obtained at the second electrically conductive member which is connected, via the track between the first and second terminals, energised at both first and second frequencies, by capacitive coupling between 45 the second terminal and the second electrically conductive member, to the one first electrically conductive member.

- 4. An apparatus for checking the connection via a conductive track between first and 50 second terminals of a printed circuit board, the apparatus comprising: a first electrically conductive member which, in use of the apparatus, is placed adjacent and spaced from the first terminal; means for applying an alternat-55 ing voltage to the first member for electrically energising the track by capacitive coupling between the first terminal and the first member; a second electrically conductive member which, in use of the apparatus, is placed 60 adjacent and spaced from the second terminal; and means for obtaining an output signal, as a result of such energisation of the track and its connection of the first and second terminals, by capacitive coupling between the 65 second terminal and the second member.

- 5. An apparatus as claimed in claim 4, comprising first and second electrically conductive components which provide respectively a plurality of such first and second electrically conductive members arranged in an array to check the connections between each of a plurality of such tracks, each electrically conductive member having first and second parts, wherein the means for applying an 75 alternating voltage to each first member consists of means for sequentially applying an alternating voltage at a first frequency to each first part and means for sequentially applying an alternating voltage at a second frequency 80 to each second part for energising one of the tracks at both first and second frequencies, and wherein the means for obtaining an output signal comprises means for providing an output when signals of both first and second 85 frequencies are detected at one of the second electrically conductive members.

- A method of checking the connection via a conductive track between first and second terminals of a printed circuit board substantially as herein described with reference to the accompanying drawings.

- An apparatus for checking the connection via a conductive track between first and second terminals of a printed circuit board substantially as herein described with reference to, and as shown in, Figs. 3 to 7 of the accompanying drawings.

Printed in the United Kingdom for Her Majesty's Stationery Office, Dd 8818935, 1985, 4235. Published at The Patent Office, 25 Southampton Buildings, London, WC2A 1AY, from which copies may be obtained.