# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 113740713 B (45) 授权公告日 2024. 02. 13

**H05K** 3/00 (2006.01) **H05K** 3/46 (2006.01)

#### (56) 对比文件

- CN 105823704 A,2016.08.03

- CN 107509302 A,2017.12.22

- CN 108107342 A.2018.06.01

- CN 201859193 U,2011.06.08

- CN 207215006 U,2018.04.10

- JP 2016025227 A,2016.02.08

- KR 20020023889 A,2002.03.29

- WO 2019019339 A1,2019.01.31

审查员 李妍臻

(21)申请号 202111055227.2

(22)申请日 2021.09.09

(65) 同一申请的已公布的文献号 申请公布号 CN 113740713 A

(43) 申请公布日 2021.12.03

(73) 专利权人 博敏电子股份有限公司 地址 514000 广东省梅州市经济开发试验 区东升工业园梅湖路280号

(72) 发明人 廖金超 吴增坤 郭茂桂 陈世金 许伟廉 黄伟 梁鸿飞

(74) 专利代理机构 广州海心联合专利代理事务 所(普通合伙) 44295 专利代理师 黄为 冼俊鹏

(51) Int.CI.

GO1R 31/28 (2006.01)

# (54) 发明名称

一种检测PCB是否除胶不尽的测试板及其测试方法

#### (57) 摘要

本发明公开了一种检测PCB是否除胶不尽的测试板及其测试方法,针对现有技术中对除胶不尽测试不方便的问题提出本方案。在测试板中设置若干贯通的测试孔,然后在层叠结构中上中下的内层板上进行连接。利用不同测试孔的开闭回路获知除胶不尽的三维位置。优点在于,通过在等离子工序加工过程中放置设计好的测试板,并对其进行导通情况验证,极大概率的降低了对新产品制作过程中因设置不好等离子参数导致后期大量报废问题。无需进行切片观察,反馈速度得到明显提升。

权利要求书2页 说明书4页 附图11页

- 1.一种检测PCB是否除胶不尽的测试方法,其特征在于,包括以下步骤:

- S1、根据同一批次里面待除胶的一PCB总层数制作测试板,令所述测试板的层叠结构总层数与PCB总层数相同;

- S2、调整除胶工作参数;将所述测试板与若干待除胶的PCB放置于工位上进行过机;所述测试板位于工位中部位置;

- S3、得到除胶后的测试板;

- S4、将除胶后的测试板进行上铜工序,令各测试孔内覆铜;

- S5、分别测试各测试模块(11)内的第一导线、第二导线和第三导线对应的电回路;

- S6、若各电回路均为闭路,则判定步骤S2的除胶工作参数正确,已过机及待过机的PCB均能正确除胶,进入步骤S7;若任一电回路存在开路,则判定步骤S2的除胶工作参数不正确,返回步骤S1;

- S7、将剩余待除胶的PCB依次讨机除胶:

所述测试板包括板体(10);所述板体(10)内设有一个以上的测试模块(11),测试模块(11)为多层树脂复合压制的层叠结构;

测试模块(11)中部设有走线区(20),走线区(20)内设有若干第一测试孔(21);在走线区(20)的外侧还设有第二测试孔(22)、第三测试孔(23)、第四测试孔(24)、第五测试孔(25)、第六测试孔(26)和第七测试孔(27);

所有的测试孔均纵向贯穿测试模块(11);

在靠近顶层的内层板设有第一导线,所述第一导线一端连接第二测试孔(22)后,另一端逐一连通各第一测试孔(21)并最终连接第三测试孔(23);

在中位数的内层板设有第二导线,所述第二导线一端连接第六测试孔(26)后,另一端逐一连通各第一测试孔(21)并最终连接第七测试孔(27);

在靠近底层的内层板设有第三导线,所述第三导线一端连接第四测试孔(24)后,另一端逐一连通各第一测试孔(21)并最终连接第五测试孔(25)。

2.根据权利要求1所述一种检测PCB是否除胶不尽的测试方法,其特征在于,所述第一导线在靠近顶层的两层内层板中依次纵向错位连接,形成第一联层结构;

所述第二导线在中位数的两层内层板中依次纵向错位连接,形成第二联层结构;

所述第三导线在靠近底层的两层内层板中依次纵向错位连接,形成第三联层结构。

3.根据权利要求2所述一种检测PCB是否除胶不尽的测试方法,其特征在于,靠近顶层的两层内层板分别为从上至下顺数的第二层和第三层;

靠近底层的两层内层板分别为从下至上倒数的第二层和第三层:

若层叠结构的总层数N是偶数,则中位数的两层内层板分别为第N/2层和第N/2+1层;若层叠结构的总层数N是奇数,则中位数的两层内层板分别为第(N+1)/2层和第(N+1)/2±1层。

- 4.根据权利要求1所述一种检测PCB是否除胶不尽的测试方法,其特征在于,所有的测试孔与层叠结构中各层的连接处均设置为焊盘。

- 5.根据权利要求1所述一种检测PCB是否除胶不尽的测试方法,其特征在于,所述的走线区(20)内,各第一测试孔(21)以两行多列的方式排布;各导线均在走线区(20)中形成U型布线。

- 6.根据权利要求5所述一种检测PCB是否除胶不尽的测试方法,其特征在于,各第一测试孔(21)以两行七列的方式排布,且各列之间间距相等。

- 7.根据权利要求1所述一种检测PCB是否除胶不尽的测试方法,其特征在于,测试模块 (11) 在板体 (10) 中以矩阵方式排布。

- 8.根据权利要求7所述一种检测PCB是否除胶不尽的测试方法,其特征在于,任一测试模块(11)内各测试孔的孔径相同,与同一行及同一列中的其他测试模块(11)孔径不同。

- 9.根据权利要求1所述一种检测PCB是否除胶不尽的测试方法,其特征在于,利用走线区(20)辅助定位除胶不尽的测试孔。

## 一种检测PCB是否除胶不尽的测试板及其测试方法

## 技术领域

[0001] 本发明涉及PCB生产前端工艺,尤其涉及一种检测PCB是否除胶不尽的测试板,还 涉及利用该测试板的测试方法。

## 背景技术

[0002] PCB,即印制电路板,随着科技进步,现有的PCB均使用多层板复合结构。多层板层压之后的介电层(半固化片)本身含有一定量的树脂,即本技术方法需要去除的胶。

[0003] PCB在钻孔的过程中,由于钻咀的高速旋转削切带的热量会让树脂软化。钻咀完成钻孔后,抽出的同时,会将软化的树脂拉扯,软化的树脂会附着在内层环上,随之温度下降。树脂又硬化。

[0004] 除胶的目的就是要把附着在内层环上的树脂清除(又名:除胶)。若不清除环上的树脂,后续上铜的话会由于附着在内层环树脂的阻挡,导致孔壁的铜和内层环没办法起到正常的导通。

[0005] 在生产业内对于高速材料大多数都采用等离子除胶,由于对高速材料新产品(尤其是新材料)的制作并未有足够的经验,实际生产中往往会因为等离子参数设置不准确导致除胶不尽,进而导致整批产品报废。等离子除胶和以往的湿法除胶不同,由于设备自身存在着均匀性问题,造成大小孔除胶速率不同步问题。设备的除胶参数设置不吻合而导致大孔径的除胶情况理想,但小孔径会出现除胶不尽,会导致产品出现除胶不尽导致开路的问题(ICD)。

[0006] 在一个生产批次里面,起码需要过机(经过等离子设备进行除胶)十几二十次,每次过机都有十几件PCB,总量高达百件以上。对于有着成千上万个孔的PCB来说,要每一个孔都打切片进行确认是低效且不现实的(如CN105823704A)。由于除胶后没有一个很好的检测手段,往往是去到最后出厂前电测工序时才发现有因为ICD存在开路。这将给公司带来巨大的损失,同时延误交期。对等离子工序的检测手段成为了关键,若能在工序过程中或完成后检测出存在ICD,能对PCB进行补救,避免损失。

#### 发明内容

[0007] 本发明目的在于提供一种检测PCB是否除胶不尽的测试板及其测试方法,以解决上述现有技术存在的问题。

[0008] 本发明所述一种检测PCB是否除胶不尽的测试板,包括板体,所述板体内设有一个以上的测试模块,测试模块为多层树脂复合压制的层叠结构;

[0009] 测试模块中部设有走线区,走线区内设有若干第一测试孔;在走线区的外侧还设有第二测试孔、第三测试孔、第四测试孔、第五测试孔、第六测试孔和第七测试孔;

[0010] 所有的测试孔均纵向贯穿测试模块;

[0011] 在靠近顶层的内层板设有第一导线,所述第一导线一端连接第二测试孔后,另一端逐一连通各第一测试孔并最终连接第三测试孔;

[0012] 在中位数的内层板设有第二导线,所述第二导线一端连接第六测试孔后,另一端逐一连通各第一测试孔并最终连接第七测试孔;

[0013] 在靠近底层的内层板设有第三导线,所述第三导线一端连接第四测试孔后,另一端逐一连通各第一测试孔并最终连接第五测试孔。

[0014] 所述第一导线在靠近顶层的两层内层板中依次纵向错位连接,形成第一联层结构;

[0015] 所述第二导线在中位数的两层内层板中依次纵向错位连接,形成第二联层结构;

[0016] 所述第三导线在靠近底层的两层内层板中依次纵向错位连接,形成第三联层结构。

[0017] 靠近顶层的两层内层板分别为从上至下顺数的第二层和第三层;

[0018] 靠近底层的两层内层板分别为从下至上倒数的第二层和第三层;

[0019] 若层叠结构的总层数N是偶数,则中位数的两层内层板分别为第N/2层和第N/2+1层;若层叠结构的总层数N是奇数,则中位数的两层内层板分别为第(N+1)/2层和第(N+1)/2 ±1层。

[0020] 所有的测试孔与层叠结构中各层的连接处均设置为焊盘。

[0021] 所述的走线区内,各第一测试孔以两行多列的方式排布;各导线均在走线区中形成U型布线。

[0022] 各第一测试孔以两行七列的方式排布,且各列之间间距相等。

[0023] 测试模块在板体中以矩阵方式排布。

[0024] 任一测试模块内各测试孔的孔径相同,与同一行及同一列中的其他测试模块孔径不同。

[0025] 本发明所述一种检测PCB是否除胶不尽的测试方法,包括以下步骤:

[0026] S1、根据同一批次里面待除胶的一PCB总层数制作所述的测试板,令所述测试板的层叠结构总层数与PCB总层数相同:

[0027] S2、调整除胶工作参数;将所述测试板与若干待除胶的PCB放置于工位上进行过机;所述测试板位于工位中部位置;

[0028] S3、得到除胶后的测试板:

[0029] S4、将除胶后的测试板进行上铜工序,令各测试孔内覆铜;

[0030] S5、分别测试各测试模块内的第一导线、第二导线和第三导线对应的电回路;

[0031] S6、若各电回路均为闭路,则判定步骤S2的除胶工作参数正确,已过机及待过机的 PCB均能正确除胶,进入步骤S7;若任一电回路存在开路,则判定步骤S2的除胶工作参数不正确,返回步骤S1;

[0032] S7、将剩余待除胶的PCB依次过机除胶。

[0033] 利用走线区辅助定位除胶不尽的测试孔。

[0034] 本发明所述一种检测PCB是否除胶不尽的测试板及其测试方法,其优点在于,通过在等离子工序加工过程中放置设计好的测试板,并对其进行导通情况验证,极大概率的降低了对新产品制作过程中因设置不好等离子参数导致后期大量报废问题。从以前的没有具体的量化指标,改为可以凭借测试板的导通情况来判断整批板材的情况。无需进行切片观察,反馈速度得到明显提升。

### 附图说明

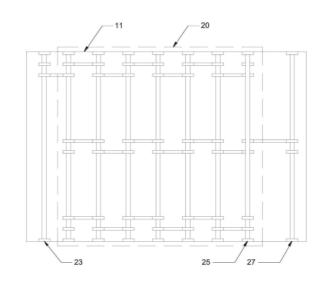

[0035] 图1是本发明所述一种检测PCB是否除胶不尽的测试板的结构示意图。

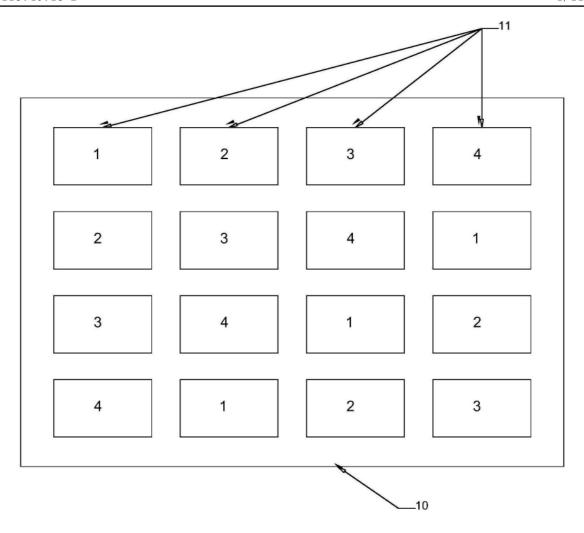

[0036] 图2是本发明所述模块在隐藏布线时的结构示意图:

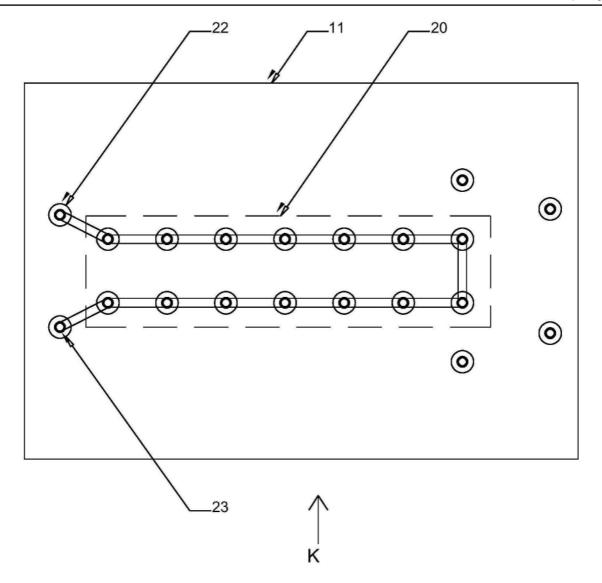

[0037] 图3是图2中K向视图。

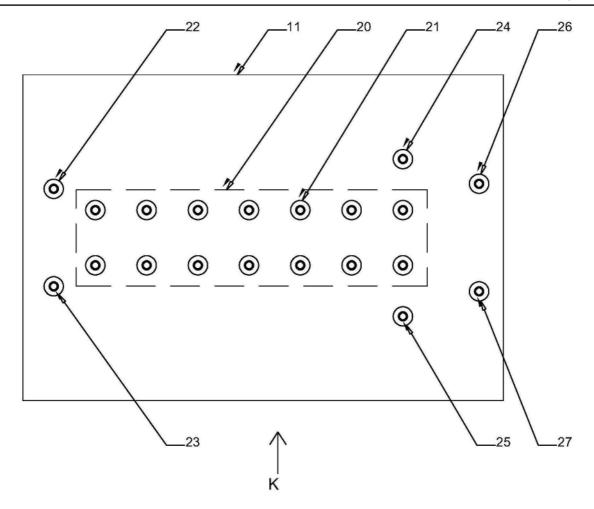

[0038] 图4是本发明所述模块在第二、第三层布线时的结构示意图;

[0039] 图5是图4中K向视图,并简化了其他焊盘展示以及省略了第五测试孔展示。

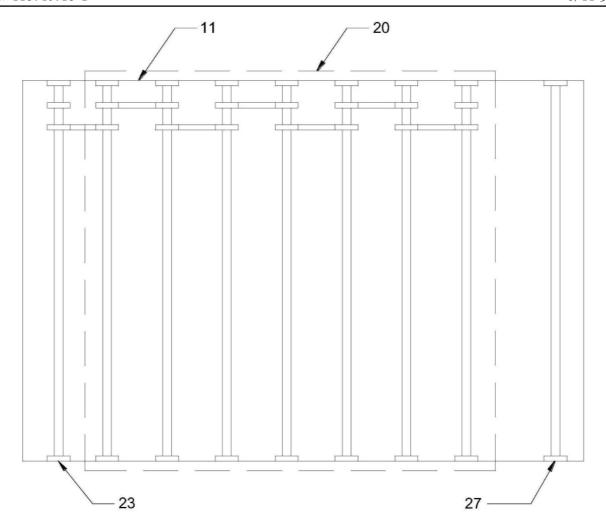

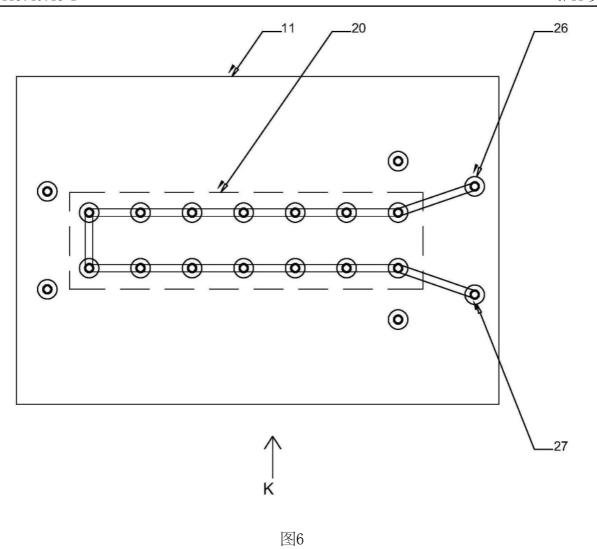

[0040] 图6是本发明所述模块在第九、第十层布线时的结构示意图:

[0041] 图7是图6中K向视图,并简化了其他焊盘展示以及省略了第五测试孔展示。

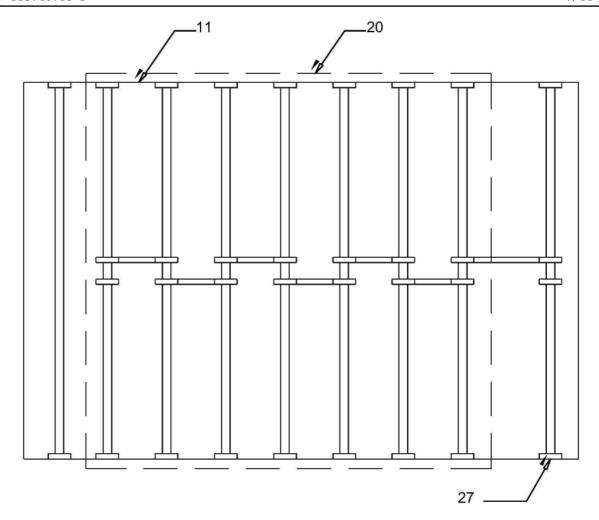

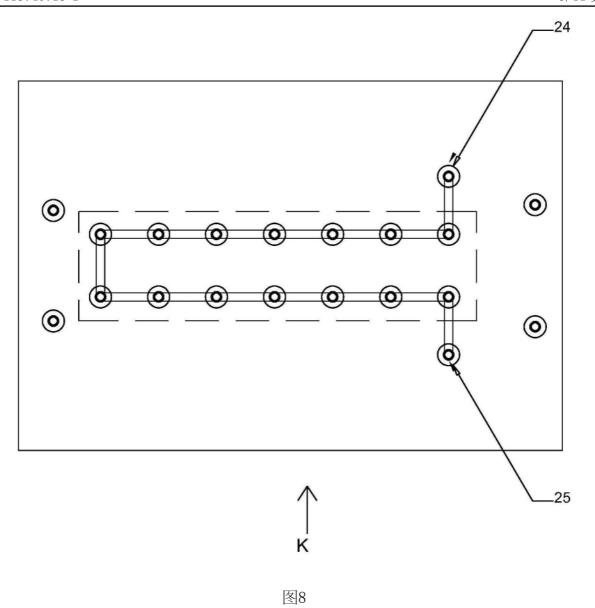

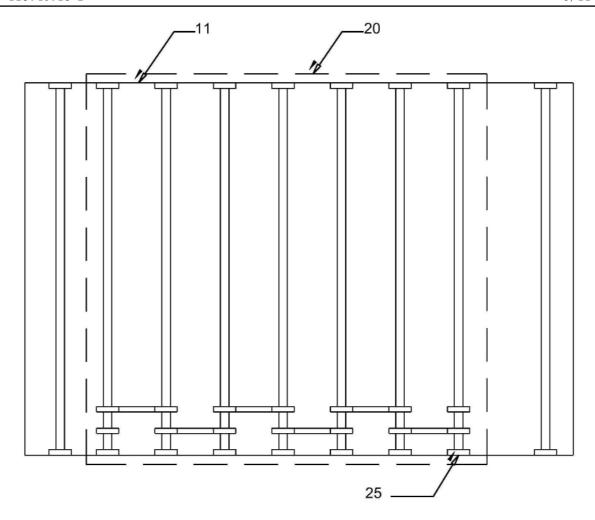

[0042] 图8是本发明所述模块在第十六、第十七层布线时的结构示意图;

[0043] 图9是图8中K向视图,并简化了其他焊盘展示。

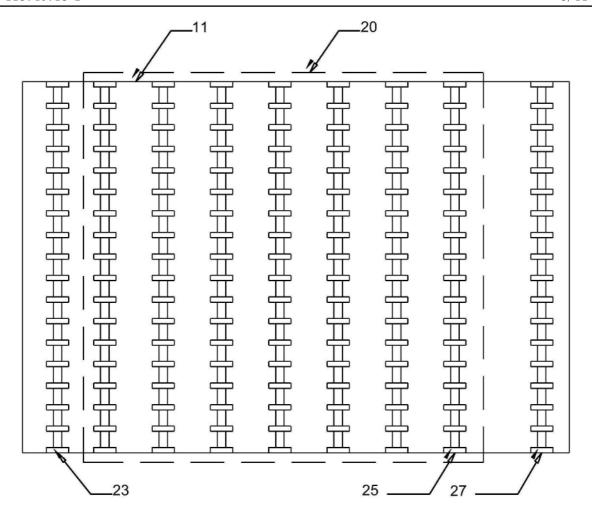

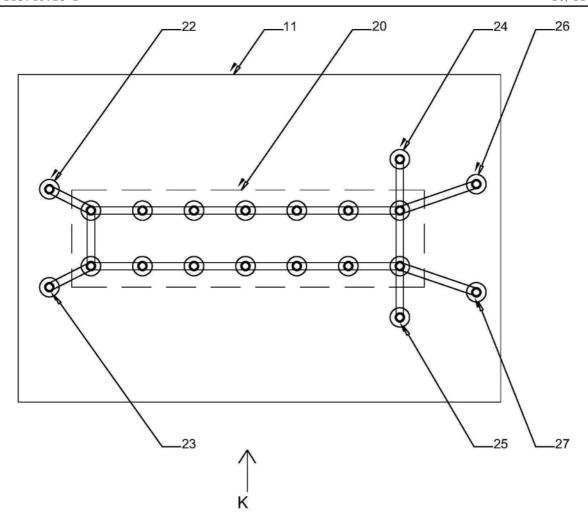

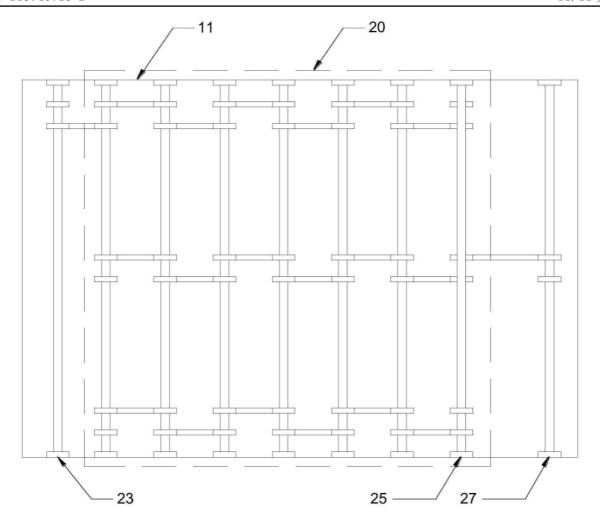

[0044] 图10是本发明所述模块在结合了图4、图6和图8布线时的结构示意图;

[0045] 图11是图10中K向视图,并简化了其他焊盘展示。

[0046] 附图标记:

[0047] 10-板体、11-测试模块;

[0048] 20-走线区、21-第一测试孔、22-第二测试孔、23-第三测试孔、24-第四测试孔、25-第五测试孔、26-第六测试孔、27-第七测试孔。

### 具体实施方式

[0049] 如图1至图3以及图10和图11所示,本发明所述一种检测PCB是否除胶不尽的测试板包括板体10,所述板体10内设有4\*4个矩阵排布的测试模块11,测试模块11为多层树脂复合压制的层叠结构。在本实施例中,层叠结构的总层数N=18。

[0050] 各测试模块11的结构相同,差别在于内置的各测试孔孔径有别,例如在本实施例图2中:1号模块全部测试孔的孔径为0.25mm;2号模块全部测试孔的孔径为0.3mm;3号模块全部测试孔的孔径为0.35mm;4号模块全部测试孔的孔径为0.45mm。排列方式采取正交方式,让每行每列都包含1、2、3、4号模块。

[0051] 测试模块11中部设有走线区20,走线区20内设有两行七列的第一测试孔21;全部第一测试孔21的孔壁间距为0.3mm。

[0052] 在走线区20的外侧还设有第二测试孔22、第三测试孔23、第四测试孔24、第五测试孔25、第六测试孔26和第十测试孔27。

[0053] 所有的测试孔均纵向贯穿测试模块11,且与层叠结构中各层的连接处均设置为焊盘。

[0054] 如图4、图5所示,在第二层和第三层的内层板设有第一导线,所述第一导线一端连接第二测试孔22后,另一端逐一连通各第一测试孔21并最终连接第三测试孔23。所述第一导线在第二层和第三层中依次纵向错位连接,形成第一联层结构。

[0055] 如图6、图7所示,在第九层和第十层的内层板设有第二导线,所述第二导线一端连接第六测试孔26后,另一端逐一连通各第一测试孔21并最终连接第七测试孔27。所述第二导线在第九层和第十层中依次纵向错位连接,形成第二联层结构。

[0056] 若层叠结构的总层数N是偶数,则中位数的两层内层板分别为第N/2层和第N/2+1层;若层叠结构的总层数N是奇数,则中位数的两层内层板分别为第(N+1)/2层和第(N+1)/2

±1层。本实施例中N=18,因此中位数的两层分别为第九层和第十层。若在其他N为奇数的实施例中,例如N=19时,中位数的两层可以为第九层和第十层,或者可以为第十层和第十一层。目的在于检测位于中间部位的除胶情况,因此无需严谨限制具体层数,本领域技术人员在实际操作中可以适当调整为其他近似的层。

[0057] 如图8、图9所示,在第十六层和第十七层的内层板设有第三导线,所述第三导线一端连接第四测试孔24后,另一端逐一连通各第一测试孔21并最终连接第五测试孔25。所述第三导线在第十六层和第十七层中依次纵向错位连接,形成第三联层结构。

[0058] 各导线均在走线区20中形成U型布线。

[0059] 利用本发明所述测试板进行的测试方法具体步骤如下:

[0060] S1、根据同一批次里面待除胶的一PCB总层数制作所述的测试板,令所述测试板的层叠结构总层数与PCB总层数相同;

[0061] S2、调整除胶工作参数;将所述测试板与若干待除胶的PCB放置于工位上进行过机;所述测试板位于工位中部位置;

[0062] S3、得到除胶后的测试板;

[0063] S4、将除胶后的测试板进行上铜工序,令各测试孔内覆铜;

[0064] S5、分别测试各测试模块11内的第一导线、第二导线和第三导线对应的电回路;

[0065] S6、若各电回路均为闭路,则判定步骤S2的除胶工作参数正确,已过机及待过机的 PCB均能正确除胶,进入步骤S7;若任一电回路存在开路,则判定步骤S2的除胶工作参数不正确,返回步骤S1;

[0066] S7、将剩余待除胶的PCB依次过机除胶。

[0067] 在步骤S6中测试的具体过程如下:利用万能表分别接触第二测试孔22和第三测试孔23,测试第一导线的环路情况,若出现短路则利用走线区20辅助定位,第二测试孔22与万能表连接不变,万能表另一端逐一尝试与第一测试孔21接触,即可获知除胶不尽的测试孔。然后用类似方法逐一测试第二导线和第三导线,即可知道测试板中出现除胶不尽的位置在测试模块11内的三维位置。将所有的测试模块11测试完毕后也能获知除胶不尽的位置在板体10内的三维位置。获知了除胶不尽的三维位置将大大利于后续等离子参数的调整工作,使得参数能获得最大效益。

[0068] 对于本领域的技术人员来说,可根据以上描述的技术方案以及构思,做出其它各种相应的改变以及形变,而所有的这些改变以及形变都应该属于本发明权利要求的保护范围之内。

图2

图3

图4

图5

图7

图9

图10

图11