US 20110089426A1

### (19) United States (12) Patent Application Publication (10) Pub. No.: US 2011/0089426 A1

### Kato

### Apr. 21, 2011 (43) **Pub. Date:**

#### (54) INTEGRATED CIRCUIT, SEMICONDUCTOR **DEVICE COMPRISING THE SAME,** ELECTRONIC DEVICE HAVING THE SAME, AND DRIVING METHOD OF THE SAME

- (75) Inventor: Kiyoshi Kato, Sagamihara (JP)

- SEMICONDUCTOR ENERGY (73) Assignee: LABORATORY CO., LTD., Kanagawa-ken (JP)

- 12/977,143 (21) Appl. No.:

- (22) Filed: Dec. 23, 2010

#### **Related U.S. Application Data**

(63) Continuation of application No. 12/474,766, filed on May 29, 2009, now Pat. No. 7,858,985, which is a continuation of application No. 10/793,806, filed on Mar. 8, 2004, now Pat. No. 7,541,614.

#### (30)**Foreign Application Priority Data**

Mar. 11, 2003 (JP) ..... 2003-065314 Mar. 11, 2003 (JP) ..... 2003-065393

#### **Publication Classification**

- (51) Int. Cl. H01L 29/786 (2006.01)

- U.S. Cl. ..... 257/66; 257/E29.273 (52)

#### (57)ABSTRACT

An integrated circuit mounting a DRAM which can realize high integration without complicated manufacturing steps. The integrated circuit according to the invention comprises a DRAM in which a plurality of memory cells each having a thin film transistor are disposed. The thin film transistor comprises an active layer including a channel forming region, and first and second electrodes overlapping with each other with the channel forming region interposed therebetween. By controlling a drain voltage of the thin film transistor according to data, it is determined whether to accumulate holes in the channel forming region or not, and data is read out by confirming whether or not holes are accumulated.

## FIG.1A

SL2

Ī

3 Ō

-5 2 0

2

0

0

0

5 2 0

2

1

\*\*\*

-5

500

## FIG.9B

# FIG.13A

FIG.13B

#### INTEGRATED CIRCUIT, SEMICONDUCTOR DEVICE COMPRISING THE SAME, ELECTRONIC DEVICE HAVING THE SAME, AND DRIVING METHOD OF THE SAME

#### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is a continuation of U.S. application Ser. No. 12/474,766, filed May 29, 2009, now allowed, which is a continuation of U.S. application Ser. No. 10/793, 806, filed Mar. 8, 2004, now U.S. Pat. No. 7,541,614, which claims the benefit of foreign priority applications filed in Japan as Serial No. 2003-065314 and Serial No. 2003-065393 on Mar. 11, 2003, all of which are incorporated by reference.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

**[0003]** The present invention relates to an integrated circuit mounting DRAM formed by using a thin film semiconductor film, and more particularly to a semiconductor display device (semiconductor device) comprising the integrated circuit and a driving method of the integrated circuit.

[0004] 2. Description of the Related Art

**[0005]** Generally, a flat panel display formed by using an inexpensive glass substrate has a problem in that, the periphery of a pixel portion (frame area) which is used for mounting occupies larger area of the substrate as resolution becomes high, and this makes it difficult to produce a compact flat panel display. Therefore, it is considered that there is a limitation with regard to a method for mounting an IC which is formed by using a single crystal silicon wafer on a substrate, and thus technology for monolithically forming an integrated circuit and a pixel portion onto a glass substrate, namely development of a system-on-panel is expected to be advanced.

**[0006]** A configuration of a dual-gate thin film transistor which is one of the semiconductor elements formed on a glass substrate is disclosed in the following Patent Document 1.

#### [0007] [Patent Document 1]

[0008] Japanese Patent Laid-Open No. 2002-359376

[0009] Since an integrated circuit formed on a glass substrate has a lower degree of integration than that formed on a single crystal silicon wafer, the realization of high integration is an important subject in view of its practical use. In particular, enlargement of capacitance of a semiconductor memory is indispensable to achieve a high-performance integrated circuit as well as the high integration. Among semiconductor memories, DRAM (Dynamic Random Access Memory) is superior to other semiconductor memories in its large capacity and low cost. DRAM generally comprises a simple memory cell in which one transistor and one capacitor are arranged, and the smaller number of semiconductor elements are used to configure the DRAM memory cell as compared to other semiconductor memories such as SRAM. Therefore, the large number of memory cells can be embedded into one tip, thus makes it easier to produce an LSI having large memory capacity, leading to low cost per bit as compared to other semiconductor memories.

**[0010]** Thus, DRAM can be thought as one of the essential semiconductor memories in promoting high integration of an integrated circuit which is formed on a glass substrate.

#### SUMMARY OF THE INVENTION

**[0011]** As described above, DRAM plays an important role for achieving large memory capacity, however, when the degree of integration of an LSI is further to be increased while reducing the chip size, an area occupied by the memory needs to be reduced as well as other semiconductor memories. This requires an area of each memory cell to be even smaller. In the case of downsizing a memory cell in a DRAM, storage capacitance has to be maintained at more than the certain value so as to reduce the frequency of refresh operations, to secure an enough time for a sense operation, and to reduce soft errors due to an a ray. Thus far, various attempts have been made to secure storage capacitance while reducing an area occupied by a memory cell, such as optimization of a material used for a dielectric film and three-dimensionalization of a capacitor.

**[0012]** However, there is a limitation for the optimization of a material of a dielectric film, and it is thus difficult to obtain a material having a drastically low dielectric constant. In addition, a DRAM formed with a three-dimensionalized capacitor, such as a stack memory cell and a trench memory cell, is effective for reduction in tip size, however, it is disadvantageous in that cost per bit becomes high as its manufacturing steps are complicated as compared to those of DRAM using a planar memory cell. Therefore, it is difficult to achieve high integration of DRAM by utilizing its advantages of large memory capacity and low cost.

**[0013]** In view of the foregoing, the invention provides an integrated circuit mounting DRAM which can realize high integration without complicated manufacturing steps. In addition, the invention relates to a driving method of the integrated circuit and a semiconductor display device using the integrated circuit.

**[0014]** To solve the above-mentioned problems, a DRAM which is mounted on an integrated circuit of the invention comprises a plurality of memory cells, each of which is disposed with a dual-gate thin film transistor having a first gate electrode, a second gate electrode, an active layer including a channel forming region, a first insulating layer and a second insulating layer. The active layer is interposed between the first gate electrode and the second gate electrode, the first insulating layer is interposed between the active layer and the first gate electrode, and the second insulating layer is interposed between the active layer is interposed between the active layer and the first gate electrode, and the second insulating layer is interposed between the active layer and the second gate electrode. According to the thin film transistor having the above structure of the invention, data is written or read by means of a charge that is accumulated in a channel forming region by impact ionization.

**[0015]** Impact ionization can be controlled by a drain voltage. When a drain voltage is raised to form a high electric field of about 100 kV/cm or more, carriers that have reached threshold energy of ionization cause impact ionization, thereby generating electron-hole pairs. The generated electrons flow into a drain region and the holes flow into a source region. By controlling a potential of the first gate electrode, the generated holes can be accumulated in the channel forming region. Specifically, the holes flow into the source region when a potential of the first gate electrode is equal to or higher than that of the source region, and the holes are accumulated in the channel forming region when a potential of the first gate electrode is equal to or higher than that of the source region when a potential of the first gate a secure accumulated in the channel forming region when a potential of the first gate a secure accumulated in the channel forming region when a potential of the first gate a secure accumulated in the channel forming region when a potential of the first gate a secure accumulated in the channel forming region when a potential of the first gate a secure accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulated in the channel forming region when a potential of the first gate accumulat

electrode is lower than that of the source region. As the accumulation of the holes is kept on until the potential at the first gate electrode side of the channel forming region becomes equal to that of the source region, the cumulative amount of holes can be controlled by a potential of the first gate electrode.

**[0016]** When holes are accumulated in the channel forming region, a threshold voltage shifts as the potential at the first gate electrode side in the channel forming region increases, thus increases a drain current. Therefore, an accumulation state of the holes (charges) can be confirmed according to the magnitude of the obtained drain current. Therefore, data is written by the accumulated charges in the channel forming region, and it is read by the drain current or the threshold voltage.

**[0017]** Since holes are accumulated until a potential at the first gate electrode side of the channel forming region becomes equal to a potential of the source region, the cumulative amount of holes can be controlled by a potential of the first gate electrode. According to the invention, data having three states or more may be written by selecting a plurality of different potentials to be supplied to the first gate electrode in writing data, and making difference in the cumulative amount of holes after writing. Then, by utilizing a characteristic such that a threshold voltage or a drain current is increased in accordance with the increase in the cumulative amount of holes, data having three states or more is read out. According to the above configuration, memory capacity of a DRAM can be increased while reducing an occupying area.

**[0018]** In addition, since accumulated charges can be kept for a certain period of time according to the invention, unlike general DRAMs using capacitors, it is possible to read out data without rewriting the data even after reading out the data by a drain current. Therefore, power saving of DRAMs can be achieved by reducing the number of rewritings when the same data is needed. However, when overwriting new data onto previous data, it is required before writing the new data that the previous data is completely deleted by raising a potential of the first gate electrode to discharge (purge) the accumulated charges.

**[0019]** It is to be noted that, refresh operation is required in the DRAM of the invention as well as general DRAMs. This is because the difference of the amount of charges between when they are accumulated in the channel forming region and when they are not are gradually decreased according mainly to thermal generation of electron-hole pairs. In the refresh operation, data is rewritten after purging the accumulated charges by raising a potential of the first gate electrode in the similar manner to the overwriting of new data.

**[0020]** Also, when a thin film transistor is compared to a transistor formed by using a single crystal semiconductor film, it is generally thought that charges are easily leaked out due to a grain boundary in an active layer, leading to a short holding time of charges. In particular, in the case of multistate data having three states or more, the difference of the charge amount between each state tends to become smaller as the number of states increases as four, five, and more, thus it is difficult to keep accuracy of data. However, as for a transistor formed by using a single crystal semiconductor film, the conventional process has to be made a drastic change in forming two gate electrodes interposing an active layer, thereby leading to more complicated steps and further to a high cost. In view of these problems, the invention uses a semiconductor film, which is crystallized by means of a metal

catalyst, as an active layer of a thin film transistor. It has been verified that in a semiconductor film crystallized by means of metal catalyst, two different crystal grains are joined with very good matching at the grain boundary as disclosed in Japanese Patent Laid-Open No. 2001-5426. In other words, the film has a structure in which crystal lattices are continuously joined at the crystal grain boundary, and which is very hard to create trap levels ascribable to crystal defects and the like. Therefore, there are small regions to become a generative nucleus of an electron-hole pair, and thus a thin film transistor having high charge retention characteristics can be realized even in processing data having multiple states. Also, a step for manufacturing the second gate electrode can be additionally provided with ease without making the overall steps complicated as compared to the case of a single crystal transistor. Therefore, cost rise with the complicated steps can be suppressed unlike the case of forming a single crystal transistor.

**[0021]** It is to be noted that, a thin film transistor of the invention is an SOI (silicon on insulator) of a complete depletion type. A complete depletion SOI transistor can be realized when a film thickness of an active layer is thin, and the depletion layer spreads widely in the active layer. A single crystal SOI substrate has a problem in that it cannot easily provide a very thin single crystal silicon film, whereas a thin film transistor can provide a very thin active layer by depositing a semiconductor layer.

[0022] In addition to the method of using a metal catalyst, other methods such as thermal crystallization using an electrically heated oven, laser crystallization using a laser beam, lamp anneal crystallization using infrared light can be used to crystallize a thin semiconductor layer. However, a semiconductor film crystallized by these methods is inferior in matching of the two different crystal grains at a crystal grain boundary as compared to the case of using a metal catalyst, thus it tends to create a number of trap levels ascribable to crystal defects and the like. When there are a number of such trap levels, electron hole pairs are generated due to the level that serves as a nucleus, therefore, charge retention characteristics are deteriorated. When the charge retention characteristics are low, frequency of refresh operations has to be increased and data writing or reading needs to be performed without overlapping with each other, thus operating rate is lowered.

**[0023]** In addition, in the semiconductor film which is crystallized by means of a metal catalyst, characteristic variations of a thin film transistor for holding charges can be decreased since the size and crystal orientation of crystal grains are relatively uniform as compared to those formed by other crystallization. As an operating condition of a memory is determined based on the distribution (variations) in characteristics of a number of memory cells, it is advantageous to obtain a thin film transistor with small characteristic variations in view of various operating conditions such as a frequency of refresh operations, a potential supplied to a bit line and a word line, thus power consumption and operating rate can be improved.

**[0024]** As described above, according to the invention, data can be stored by using one thin film transistor, thus no additional capacitors are required and a memory cell area can be reduced. Therefore, high integration and large memory capacity of an integrated circuit mounting a DRAM can be realized while cutting costs. Further, according to the high integration and large memory cut, the integrated circuit occupies a smaller area of a sub-

strate on which a pixel portion of a flat panel is formed together, thus high-performance system-on-panel can be implemented.

**[0025]** It is to be noted that, according to the invention, a DRAM can be operated by providing at least one thin film transistor for each memory cell, however, the number of thin film transistors is not limited to this, and a plurality of transistors may also be employed for each memory cell. For example, not only a thin film transistor for storing data, but also a thin film transistor used for switching may be employed so that the former thin film transistor may hold the stored data with accuracy. However, the thin film transistor used for switching may not necessarily be of a dual gate type, and a single gate thin film transistor that is present only in either side of an active layer may also be employed.

**[0026]** It is to be noted that, the integrated circuit of the invention includes all integrated circuits using DRAM such as a microprocessor and an image processing circuit. A semiconductor display device of the invention includes a liquid crystal display device, a light emitting device comprising a light emitting element represented by an organic light emitting diode (OLED) for each pixel, a DMD (Digital Micromirror Device), a PDP (Plasma Display Panel), an FED (Field Emission Display), and other display devices in which circuit elements using semiconductor films are employed in their driver circuits and the like.

**[0027]** Further, according to the invention, a plurality of different potentials to be supplied to a first gate electrode can be selected in writing, and by writing data having three states or more, memory capacity of a DRAM can be increased while reducing its occupying area.

#### BRIEF DESCRIPTION OF THE DRAWINGS

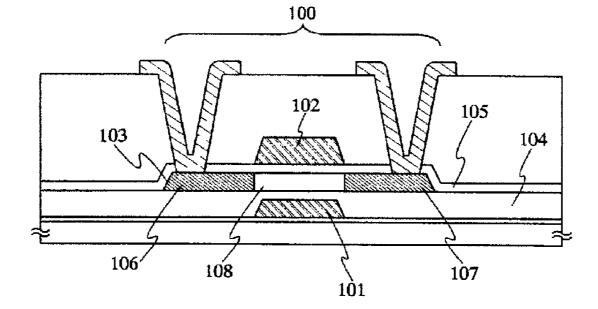

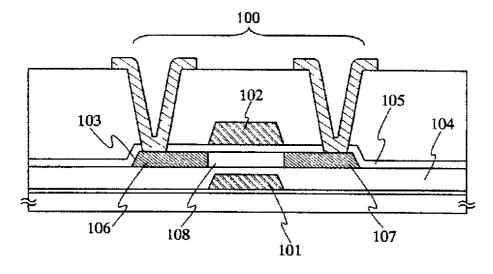

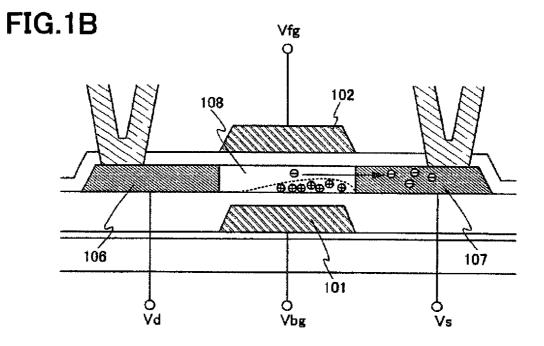

[0028] FIGS. 1A and 1B are cross-sectional views of a TFT which is used as a memory element in the present invention. [0029] FIGS. 2A to 2D are circuit diagrams to explain the operation of a TFT which is used as a memory element.

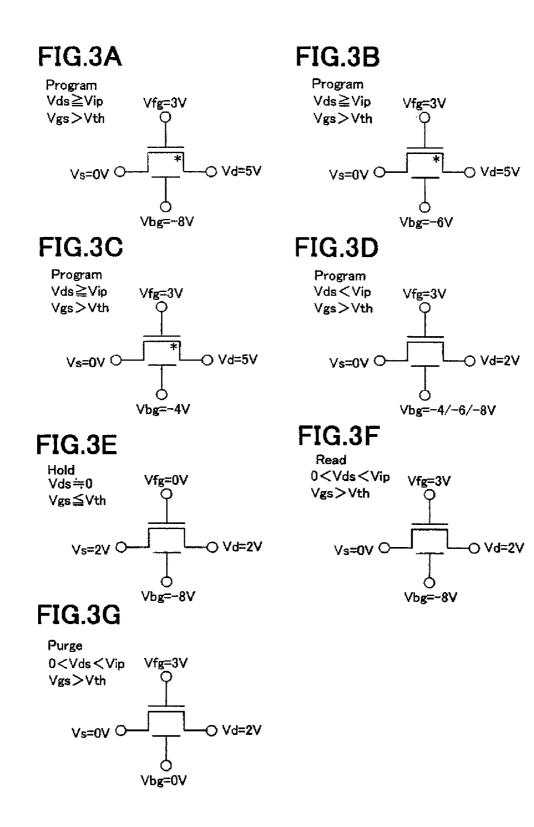

[0030] FIGS. 3A to 3G are circuit diagrams to explain the operation of a TFT which is used as a memory element.

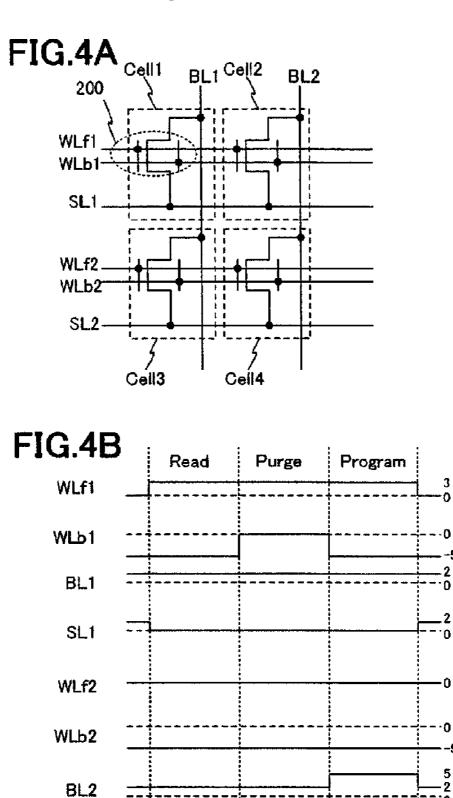

[0031] FIGS. 4A and 4B are a circuit diagram of a cell array of a DRAM and a timing chart respectively.

**[0032]** FIGS. **5**A to **5**E are views showing a method for manufacturing a semiconductor display device of the invention.

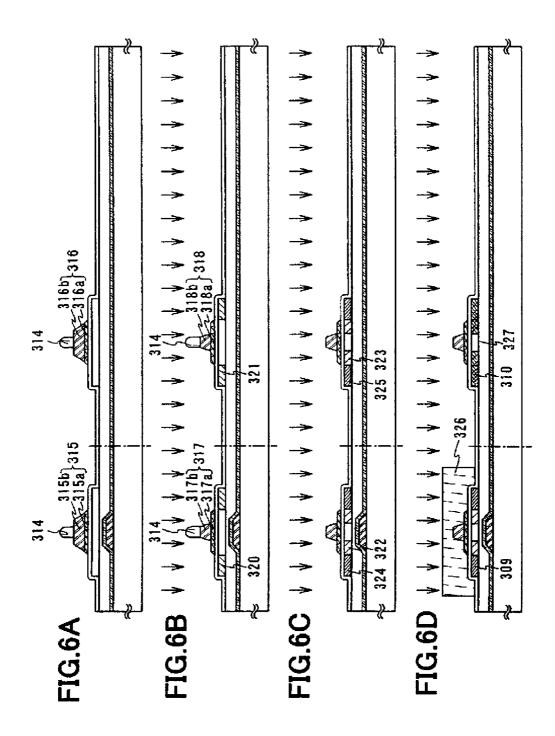

**[0033]** FIGS. **6**A to **6**D are views showing a method for manufacturing a semiconductor display device of the invention.

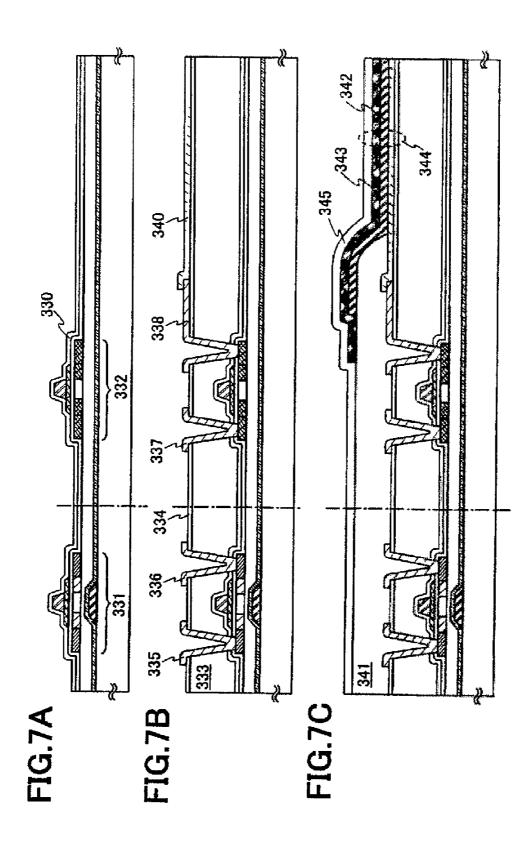

**[0034]** FIGS. 7A to 7C are views showing a method for manufacturing a semiconductor display device of the invention.

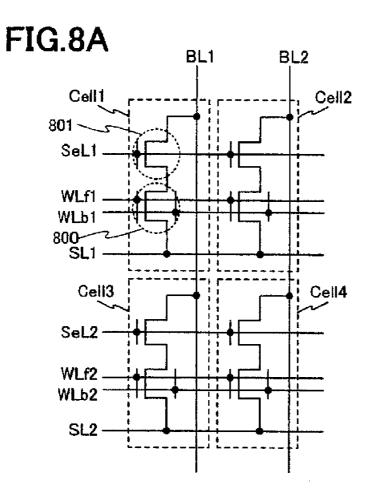

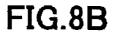

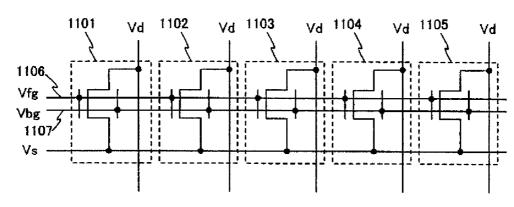

**[0035]** FIGS. **8**A and **8**B are a circuit diagram of a cell array of a DRAM and a timing chart respectively.

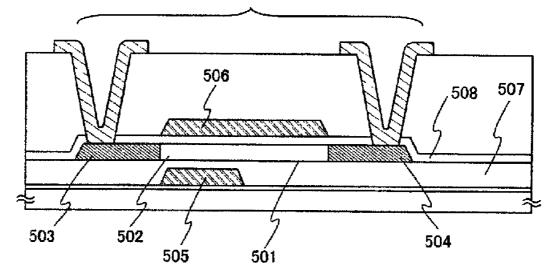

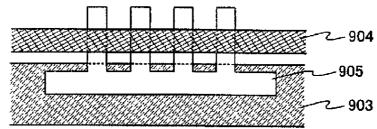

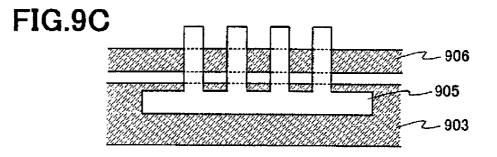

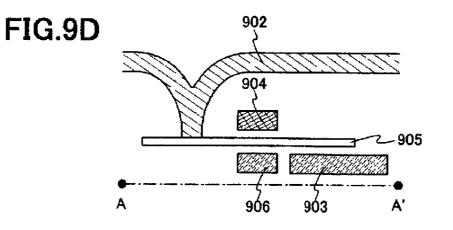

**[0036]** FIG. **9**A is a top plan view showing a memory cell of a DRAM, and FIGS. **9**B to **9**D are cross-sectional views of the same.

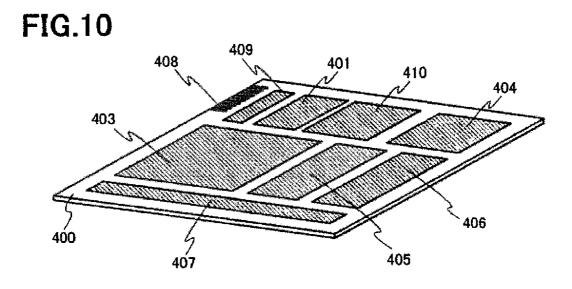

**[0037]** FIG. **10** is a perspective view of a microprocessor as one of the integrated circuits of the invention.

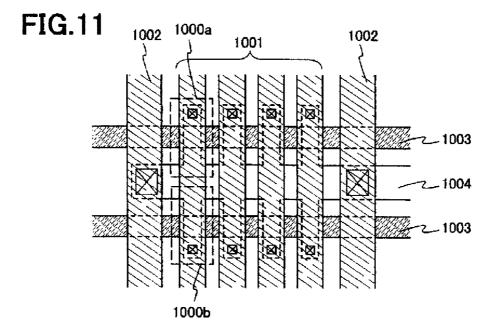

**[0038]** FIG. **11** is a top plan view of a memory cell of a DRAM.

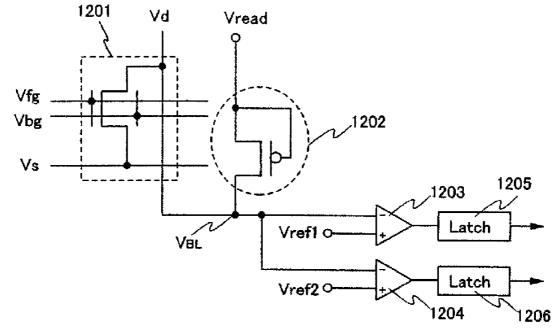

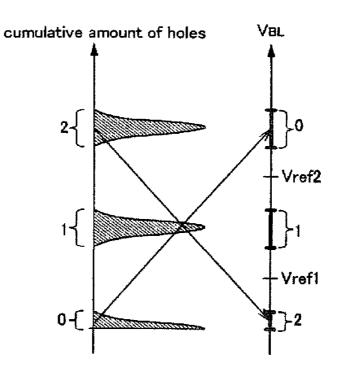

**[0039]** FIG. **12** is a partial circuit diagram of a cell array of a DRAM.

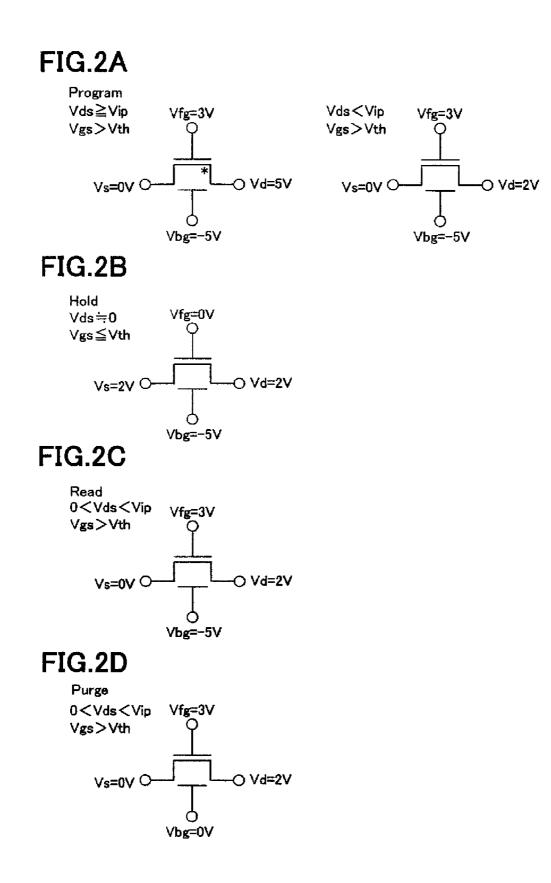

**[0040]** FIGS. **13**A and **13**B are exemplary diagrams showing a memory cell and a method for reading out data from the memory cell respectively.

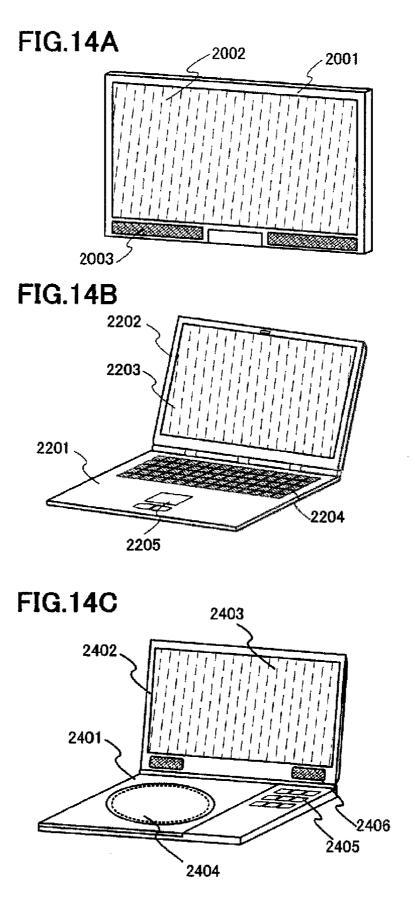

**[0041]** FIGS. **14**A to **14**C are electronic apparatuses to which the semiconductor display device or the integrated circuit of the invention is applied.

#### DETAILED DESCRIPTION OF THE INVENTION

#### Embodiment Mode

**[0042]** With reference to FIGS. 1A and 1B, a structure of a DRAM which is used in an integrated circuit of the present invention is described. FIG. 1A shows a cross-sectional view of a dual gate thin film transistor (TFT) **100** which is disposed in each memory cell.

[0043] The TFT 100, which is used as a memory element in the invention, comprises two electrodes (hereinafter referred to as a first gate electrode 101 and a second gate electrode 102), an active layer 103, a first insulating layer 104, and a second insulating layer 105. The active layer 103 comprises a source region 106, a drain region 107, and a channel forming region sandwiched between the source region 106 and the drain region 107.

[0044] As shown in FIG. 1A, the active layer 103 is sandwiched between the first gate electrode 101 and the second gate electrode 102, and the first insulating layer 104 is sandwiched between the first gate electrode 101 and the active layer 103, and further the second insulating layer is sandwiched between the second gate electrode 102 and the active layer 103.

[0045] It is to be noted that, the structure of the active layer 103 is not limited to the one shown in FIG. 1A, and it may have an LDD (Light Doped Drain) region, and one or a plurality of impurity regions which overlap with the first gate electrode 101 or the second gate electrode 102 for example. Also, a part of the channel forming region 108 may not necessarily overlap with the first gate electrode 101 or the second gate electrode 102.

**[0046]** According to a potential to be supplied to the first gate electrode **101**, the second gate electrode **102**, the source region **106**, and the drain region **107**, various operations of the DRAM can be controlled. Specifically, impact ionization in data writing (Program) can be controlled according to a potential supplied to the source region **106** and the drain region **107**.

[0047] FIG. 1B shows a pattern diagram showing a state where holes are accumulated during impact ionization. FIG. 1B is an enlarged view of the TFT shown in FIG. 1A, in which a potential of the first gate electrode 101 is referred to as Vbg, a potential of the second gate electrode 102 as Vfg, a potential of the source region 106 as Vs, and a potential of the drain region 107 as Vd.

**[0048]** Impact ionization can be caused by raising a drain voltage (referred to as Vds) which is obtained by subtracting the potential Vs of the source region **106** from the potential Vd of the drain region **107**. The drain voltage Vds is adjusted so as to form an electric field that is high enough to reach threshold energy of impact ionization. The value of the drain voltage Vds that causes impact ionization differs depending on the structure or characteristics of a TFT, specifically such as crystallinity of an active layer and an impurity concentration. According to the invention, the value of the drain voltage Vds may be set in such a manner that data can be written or read out based on the variations in threshold voltage or drain current derived from impact ionization.

**[0049]** When impact ionization occurs, electron-hole pairs are generated, and the generated electrons flow into the drain

region, and the holes flow into the source region. Some of the holes are accumulated in the channel forming region **108** as indicated by '+' in FIG. **1B**. By making a potential of the first gate electrode **101** lower than the potential Vs of the source region, the amount of holes to be accumulated can be controlled and further can be held.

**[0050]** Further, according to the invention, the cumulative amount of holes may be controlled by selecting a plurality of different potentials, which are lower than the potential Vs, to supply to the first gate.

**[0051]** When holes are accumulated, a potential at the first gate electrode side of the channel forming region is raised corresponding to the cumulative amount of holes, whereby a threshold voltage and a drain current of the TFT are changed as well. Specifically, the larger the cumulative amount of holes are, the higher the threshold voltage is and the larger the drain current is. Data can be read out by utilizing the threshold voltage or the drain current which is changed according to the impact ionization. Each bit of data may have two states, or three or more states.

**[0052]** Next, a method for controlling a potential of a TFT for storing data at each operation is described with reference to FIGS. **2**A to **2**D.

**[0053]** First, an operation in data writing (Program) is explained. FIG. **2**A shows an example of a circuit diagram of a TFT and potentials which are supplied to each part in data writing. Note that, shown in FIG. **2**A to **2**D are examples in the case of storing data having two states to a DRAM.

[0054] In writing data, a gate voltage (referred to as Vgs) which is obtained by subtracting a potential Vs of a source region from a potential Vfg of a second gate electrode is set higher than a threshold voltage Vth of the TFT so as to turn ON the TFT. A drain voltage Vds is changed depending on whether holes are accumulated by impact ionization or not. In the case of accumulating holes by impact ionization, the drain voltage Vds is set equal to or higher than a voltage that causes impact ionization (referred to as Vip here) as shown in a left diagram of FIG. 2A. On the other hand, in the case of accumulating no holes intentionally, the drain voltage Vds is set lower than the voltage Vip as shown in a right diagram of FIG. 2A. Then, in either case, a potential Vbg of the first gate electrode is kept lower than a potential Vs of the source region so as to hold the state of charges in the channel forming region.

**[0055]** In FIG. **2**A, it is assumed in the left diagram that  $V_s=0 V$ , Vd=5 V, Vbg=-5 V, and Vfg=3 V and in the right diagram that Vs=0 V, Vd=2 V, Vbg=-5 V, and Vfg=3 V.

**[0056]** Next, FIG. **2**B shows an example of a circuit diagram of a TFT and potentials which are supplied to each part in holding data (Hold) which has been written. In holding data, the gate voltage Vgs is set equal to or smaller than the threshold voltage Vth (Vgs $\leq$ Vth) so as to hold the written data, thereby turning OFF the TFT. In order to keep the state of charge without causing impact ionization, Vds is set approximately equal to 0, and the potential Vbg of the first gate electrode is kept lower than the potential Vs of the source region.

[0057] In FIG. 2B, it is assumed that Vs=2 V, Vd=2 V, Vbg=-5 V, and Vfg=0 V.

**[0058]** Next, FIG. **2**C shows an example of a circuit diagram of a TFT and potentials which are supplied to each part in reading data (Read) which has been held in FIG. **2**B. In reading data, the gate voltage Vgs is set higher than the threshold voltage Vth (Vgs>Vth) so as to read out the held data, thereby turning ON the TFT. In order to read out the data without causing impact ionization while keeping the state of charge, 0<Vds<Vip is satisfied and the potential Vbg of the first gate electrode is kept lower than the potential Vs of the source region.

**[0059]** In FIG. **2**C, it is assumed that Vs=0 V, Vd=2 V, Vbg=-5V, and Vfg=3V.

[0060] Next, a purge operation (Purge) which is performed in rewriting or refreshing (Refresh) data is described. An example of a circuit diagram of a TFT and potentials which are supplied to each part in purge operation is shown in FIG. 2D. In purging, the gate voltage Vgs is set higher than the threshold voltage Vth (Vgs>Vth) to release the held charge, thereby turning ON the TFT. In order to release charges without causing impact ionization, 0<Vds<Vip is satisfied. It is to be noted that, the potential Vbg of the first gate electrode is desirably set higher than the potentials in writing, holding, and reading out data. More desirably, the potential Vbg of the first gate electrode is set equal to or higher than the potential Vs of the source region (Vbg≧Vs) though it is not essential since charges can be released when a high potential is supplied to the potential Vfg even in the case where the potential Vbg of the first gate electrode is kept lower than the potential Vs of the source region. However, the above setting contributes to the timesaving of the purge operation.

[0061] In FIG. 2D, it is assumed that Vs=0 V, Vd=2 V, Vbg=0 V, and Vfg=3 V.

**[0062]** As described above, a series of operations including writing, reading, holding, and purging can be performed by using a TFT. It is to be noted that, the specific values of Vs, Vd, Vbg, and Vfg shown in FIGS. **2**A to **2**D are only examples, and the invention is not limited to these.

**[0063]** Next, a method for controlling a potential of a TFT which stores data having four states is described with reference to FIGS. **3**A to **3**G.

**[0064]** First, an operation in data writing (Program) is explained. FIGS. **3**A to **3**D are examples each showing a circuit diagram of a TFT and potentials which are supplied to each part in writing data having four states. It is to be noted that, shown in FIGS. **3**A to **3**D are examples where data having fours states are stored, however, the state of data is not exclusively limited to four, and data may have various states such as three, five, or more.

**[0065]** In writing data, a gate voltage (referred to as Vgs) which is obtained by subtracting a potential Vs of a source region from a potential Vfg of a second gate electrode is set higher than a threshold voltage Vth of the TFT so as to turn ON the TFT in all the circuits shown in FIGS. **3**A to **3**D regardless of a content of data.

[0066] A drain voltage Vds is changed depending on whether holes are accumulated by impact ionization or not. In the case of accumulating holes by impact ionization, the drain voltage Vds is set equal to or higher than a voltage that causes impact ionization (referred to as Vip here) as shown in FIGS. **3**A to **3**C. On the other hand, in the case of accumulating no holes intentionally, the drain voltage Vds is set lower than the voltage Vip as shown in FIG. **3**D.

**[0067]** Then, in all the circuits shown in FIGS. **3**A to **3**D, a potential Vbg of the first gate electrode is kept lower than a potential Vs of the source region so as to hold the state of charge in the channel forming region. Further, according to the invention, each potential Vbg of the first gate electrode is changed in FIGS. **3**A to **3**C so that the cumulative amount of holes in each figure may be different from each other. Spe-

cifically, it is set in the following manner: the potential Vbg of the first gate electrode in FIG. **3**A is set to be the lowest, FIG. **3**B to be the second lowest, and FIG. **3**C to be the highest of the three figures. Therefore, the cumulative amount of charges are larger in the order of FIG. **3**C, FIG. **3**B, and FIG. **3**A.

[0068] In FIG. 3A, it is assumed that Vs=0 V, Vd=5 V, Vbg=-8 V, and Vfg=3 V. In FIG. 3B, it is assumed that Vs=0 V, Vd=5 V, Vbg=-6 V, and Vfg=3 V. In FIG. 3C, it is assumed that Vs=0 V, Vd=5 V, Vbg=-4 V, and Vfg=3 V. In FIG. 3D, it is assumed that Vs=0 V, Vd=5 V, Vbg=-4 V, and Vfg=3 V. [0069] It is to be noted that, in the normal memory cell array, in which memory cells in the same row are connected to a common word line, data writing is performed over a plurality of times for every different data. That is, when the states of FIGS. 3A, 3B, 3C, and 3D are referred to as "3", "2", "1", and "0" in this order for example, a potential of a memory cell to which "1" is written is set at the state of FIG. 3C, and other cells are kept at the state of FIG. 3D (Vbg=-4 V). Similarly, a potential of a memory cell to which "2" is written is set at the state of FIG. 3B, and other memory cells are kept at the state of FIG. 3D (Vbg=-6 V). Further, a potential of a memory cell to which "3" is written is set at the state of FIG. 3A, and other memory cells are kept at the state of FIG. 3D (Vbg=-8 V). In this manner, all the memory cells can be written with the predetermined states. It is to be noted that, the writing order is not exclusively limited to the order of "1" to "3".

**[0070]** FIG. **3**E shows an example of a circuit diagram of a TFT and potentials which are supplied to each part in holding data (Hold), which has been written in FIGS. **3**A to **3**D. In holding data, the gate voltage Vgs is set equal to or lower than the threshold voltage Vth (Vgs≦Vth) so as to hold the written data, thereby turning OFF the TFT. In order to hold the state of charge without causing impact ionization, Vds is set approximate equal to 0, and the potential Vbg of the first gate electrode is kept equal to or lower than the potential in data writing.

**[0071]** In FIG. **3**E, it is assumed that Vs=2 V, Vd=2 V, Vbg=-8 V, and Vfg=0 V to enable data holding regardless of the cumulative amount of holes after writing.

**[0072]** FIG. **3**F shows an example of a circuit diagram of a TFT and potentials which are supplied to each part in reading data (Read), which has been held in FIG. **3**E. In reading data, the gate voltage Vgs is set higher than the threshold voltage Vth (Vgs>Vth) so as to read the data which has been held, thereby turning ON the TFT. In order to hold the state of charge without causing impact ionization, 0<Vds<Vip is satisfied and the potential Vbg of the first gate electrode is kept equal to or lower than the potential in data writing.

**[0073]** By applying such voltages in the above manner, the held data can be read out according to the a threshold voltage of a TFT, which is determined by the cumulative amount of holes, and further to the difference between drain currents or on-resistance. Note that, it is also possible to perform reading of multi-state data through a plurality of times.

[0074] In FIG. 3F, it is assumed that Vs=0 V, Vd=2 V, Vbg=-8 V, and Vfg=3 V.

[0075] Next, purge operation (Purge) which is performed in rewriting or refreshing (Refresh) data is described. An example of a circuit diagram of a TFT and potentials which are supplied to each part in purge operation is shown in FIG. **3**G. In purging, the gate voltage Vgs is set higher than the threshold voltage Vth (Vgs>Vth) to release the held charges, thereby turning ON the TFT. In order to release charges

without causing impact ionization, 0<Vds<Vip is satisfied. It is to be noted that, the potential Vbg of the first gate electrode is desirably set higher than the potentials in writing, holding, and reading out data. More desirably, the potential Vbg of the first gate electrode is set equal to or higher than the potential Vs of the source region (Vbg≧Vs) though it is not essential since charges can be released when a high potential is supplied to the potential Vfg even in the case where the potential Vbg of the first gate electrode is kept lower than the potential Vs of the source region. However, the above setting contributes to the timesaving of purge operation.

[0076] In FIG. 3G, it is assumed that Vs=0 V, Vd=2 V, Vbg=0 V, and Vfg=3 V.

**[0077]** As described above, a series of operations including writing, reading, holding, and purging can be performed by using a TFT. Also, data having multiple states can be stored by selecting a plurality of values for the potential Vbg of the first gate electrode, therefore, 2-bit data such as '11', '10', '01', and '00', for example, can be stored in one memory cell. It is to be noted that, the specific values of Vs, Vd, Vbg, and Vfg shown in FIGS. **3**A to **3**G are only examples, and therefore the invention is not limited to these.

**[0078]** In DRAM, a plurality of memory cells each having the above-described TFT are disposed in a memory cell array in practice. Referring now to FIGS. **4**A and **4**B, each of the above-described operations in a memory cell array comprising a plurality of memory cells is described.

**[0079]** First, an example of wiring connections between each memory cell is shown in FIG. **4**A. FIG. **4**A shows a circuit diagram of a cell array having four memory cells (Cell**1**, Cell**2**, Cell**3**, and Cell**4**), each of which comprises a TFT **200** for storing data. Although four memory cells are disposed in a memory cell array in FIG. **4**A, the number of memory cells is, needless to mention, not limited to this.

**[0080]** The TFT **200** in each memory cell receives potentials Vbg and Vfg from two word lines WLb and WLf respectively, a potential Vd from a bit line BL, and a potential Vs from a source line SL. Note that, the layout of each wiring is not limited to the configuration shown in FIG. **4**A.

[0081] Specifically, In FIG. 4A, the memory cell (Cell1) corresponds to word lines WLb1 and WLf1, a bit line BL1, and a source line SL1, and the memory cell (Cell2) corresponds to the word lines WLb1 and WLf1, a bit line BL2, and the source line SL1. Further, the memory cell (Cell3) corresponds to word lines WLb2 and WLf2, the bit line BL1, and a source line SL2, and the memory cell (Cell4) corresponds to the word lines WLb2 and WLf2, the bit line BL1, and a source line SL2.

**[0082]** FIG. 4B shows an example of a timing chart in which the memory cells (Cell1) and (Cell2) in the first row are refreshed. Although the relationship between the potentials Vs, Vd, Vbg, and Vfg which are supplied to each memory cell during each period is shown with reference to FIGS. 2A to 2D here, FIGS. 3A to 3G may be referred as well.

**[0083]** Refresh operation is carried out in order to prevent data, which is stored in a memory cell, from being lost as the time passes. Specifically, during refresh operation, data which is stored in the memory cell is, after being read out once, rewritten into the same memory cell. Refresh operation needs to be carried out periodically. According to the invention, the period is determined based on the cumulative amount of holes which are held in a channel forming region of a transistor. Refresh operation according to the invention is performed through a series of operations such as reading, purging, and writing. Purge operation is an operation in which holes accumulated in a channel forming region of a transistor are all released, thereby resetting the state of a memory cell. [0084] Purge operation (refresh operation including purge operation) according to the invention is performed at the same time in the memory cells which use the word line WLb in common, namely in one row of memory cells. On the other hand, writing and reading can be individually performed in each memory, or in one row of memory cells at the same time in the same manner as the purge operation. Therefore, according to the invention, reading and writing are performed per bit in accordance with a bus width, or per row of memory cells and the like, while refresh operation is performed per row of memory cells. In addition, as the storage of data having multiple states is sensitive to stress, it is preferable that writing and reading are performed per row of memory cells as well. [0085] Data, which is firstly read out, is once stored in a latch circuit (not shown), and then rewritten into a memory cell after purging. In this embodiment mode, data is written so that the memory cell (Cell1) will have a state in which no holes are accumulated (the "0" state), and the memory cell (Cell2) will have a state in which holes are accumulated (the "1" state). It is to be noted that, in writing, a potential supplied to the memory cell (Cell4) is also changed by the BL2 (stress in writing), and what is important here is that a potential is set so that the holes accumulated in the memory cell (Cell4) are not influenced due to the potential change.

[0086] It is also to be noted that, when writing data immediately after turning ON the switch, there may be cases where charges are already accumulated due to heat, static electricity, or the like, therefore, data is desirably written after purging. [0087] Next, a method for fabricating a light emitting device in which an integrated circuit mounting a DRAM and a pixel portion are formed on the same substrate is described. Here, an example of a TFT for controlling a current supply to an OLED is described in addition to a DRAM mounted on an integrated circuit.

**[0088]** First, as shown in FIG. **5**A, a first electrode **302** of a DRAM of the invention is formed on an insulating surface of a substrate **301**. The first electrode **302** can be formed by using one or a plurality of types of conductive materials selected from a group consisting of aluminum (Al), tungsten (W), molybdenum (Mo), titanium (Ti) and tantalum (Ta). Although W is employed in this embodiment mode, W stacked on TaN may be used as well to form the first electrode **302**. Further, not only a single layer structure, but also a multi-layer structure can be employed.

**[0089]** A glass substrate such as barium borosilicate glass and alumino borosilicate glass, a quartz substrate, a ceramic substrate, and the like may be used as the substrate **301**. Also, a metal substrate including stainless (SUS) substrate or a silicon substrate formed with an insulating film on its surface may be used as the substrate **301**. Further, although a substrate formed from a synthetic resin having flexibility, such as a plastic substrate, generally has a lower heat resistance temperature as compared to the substrate described above, it is possible to use the synthetic resin substrate as long as it can withstand the processing temperatures in the manufacturing steps.

[0090] Next, a first insulating layer 303 is formed so as to cover the first electrode 302. In this embodiment mode, the first insulating layer 303 has a laminated structure of a first insulating layer A 303*a* and a first insulating layer B 303*b*. The first insulating layer A 303*a* is formed of a silicon oxyni-

tride film with a thickness of 10 to 50 nm. The first insulating layer B **303***b* is formed of a silicon oxide film or a silicon oxynitride film with a thickness of 0.5 to 1  $\mu$ m. It is to be noted that, the structure of the first insulating layer **303** is not exclusively limited to this, and it may be formed of a single layer film, or a multi-layer film having three layers or more. In addition, materials are not limited to the above.

[0091] The surface of the first insulating layer 303 (surface of the first insulating layer B 303b here) may have irregularities due to the previously formed first electrode 302. In this case, it is desirable to provide a step for flattening the substrate. In this embodiment mode, flattening is carried out by means of CMP (Chemical Mechanical Polishing). For a polishing agent (slurry) of CMP with respect to the first insulating layer 303, for example, a slurry in which fumed silica particles obtained by thermally decomposing silicon chloride gas are dispersed in a KOH-added aqueous solution may be used. By CMP, the first insulating layer is removed by about 0.1 to 0.5  $\mu$ m so as to make the surface flat.

[0092] Next, an amorphous semiconductor layer 304 having a film thickness of 50 nm is formed on the first insulating layer 303 by plasma CVD (Chemical Vapor Deposition). It is desirable that, although depending upon its hydrogen content, the amorphous semiconductor layer 304 is heated at 400 to 550° C. for several hours to be dehydrogenated, and crystallized with the hydrogen content of 5 atom % or less. Moreover, the amorphous semiconductor layer may be formed by other methods such as sputtering and vapor deposition, however, it is desirable that impurity elements such as oxygen and nitrogen contained in the film have been previously and sufficiently reduced.

[0093] It is to be noted that, not only silicon but also silicon germanium, for example, can be used for the semiconductor layer. When silicon germanium is used, it is desirable that the density of germanium is on the order of 0.01 to 4.5 atom %. [0094] It is also to be noted that, when forming both of the first insulating layer 303 and the amorphous semiconductor layer 304 by plasma CVD, these films may be formed in succession without being exposed to the atmosphere. By forming the films in succession, contamination to the surfaces of the films by atmosphere can be prevented to the utmost, thereby reducing the variations in characteristics of a to be formed.

**[0095]** Subsequently, a catalytic is doped to the amorphous semiconductor layer **304**. In this embodiment mode, a nickel acetate solution containing 1 to 100 ppm of nickel by weight is applied by a spinner. In order to improve hydrophilic to the nickel acetate solution, it may be carried out that the surface of the amorphous semiconductor layer **304** is processed with ozone containing aqueous solution to form a quite thin oxide film, then the oxide film is etched with mixed solution of sulfuric acid and aqueous hydrogen peroxide to clean off the surface, and ozone containing aqueous solution is again used to form another quite thin oxide film. Since a surface of a semiconductor layer is originally hydrophobic, the formation of the oxide film in the above manner makes it possible to apply nickel acetate solution uniformly (FIG. **5**A).

**[0096]** It is needless to mention that, doping of a catalyst to the amorphous semiconductor layer is not limited to the above method, and sputtering, vapor deposition, plasma processing and the like may also be employed.

**[0097]** Next, heat treatment is applied at 500 to  $650^{\circ}$  C. for 4 to 24 hours, for example, at  $570^{\circ}$  C. for 14 hours. By performing heat treatment, crystallization is promoted by a

nickel-containing layer **305**, thus a semiconductor layer with enhanced crystallinity is formed.

**[0098]** As means of the heat treatment, furnace annealing with an electric furnace or RTA (Rapid Thermal Annealing) may be employed. Although a halogen lamp, a metal halide lamp, a xenon arc lamp, a carbon arc lamp, a high-pressure sodium lamp, a high-pressure mercury lamp, or the like is generally used in RTA, gas-heating type RTA, which uses heated inert gas, may also be employed.

**[0099]** In the case of using RTA, a light source of a lamp for heating is turned ON for 1 to 60 seconds, preferably for 30 to 60 seconds, and this operation is repeated once to 10 times, preferably, 2 to 6 times. Although light intensity of the light source of the lamp is optional, it is necessary that the amorphous semiconductor layer **304** be heated instantaneously at a temperature of 600 to  $1000^{\circ}$  C., preferably, 650 to  $750^{\circ}$  C. Even if the temperature is quite high as above, only the semiconductor layer is instantaneously heated, and the substrate **301** is not deformed.

**[0100]** In the case of using furnace annealing, heat treatment is performed at  $500^{\circ}$  C. for 1 hour to discharge hydrogen contained in the amorphous semiconductor layer **304** before the heat treatment for crystallization. Then, heat treatment is performed by using an electric furnace in a nitrogen atmosphere at 550 to  $600^{\circ}$  C., preferably at  $580^{\circ}$  C., for 4 hours to crystallize the amorphous semiconductor layer **304**.

**[0101]** Although nickel (Ni) is used as the catalytic element in this embodiment mode, an element such as germanium (Ge), iron (Fe), palladium (Pa), tin (Sn), lead (Pb), cobalt (Co), platinum (Pt), copper (Cu), and gold (Au) may be adopted.

**[0102]** Described next is gettering of the catalytic element existing within a crystalline semiconductor layer **306**. It is considered that the catalytic element (nickel here) remains with a concentration over  $1 \times 10^{19}$  atoms/cm<sup>3</sup> on average in the crystalline semiconductor layer **306** after the crystallization with the catalytic element. Since there is a possibility of a bad influence brought on TFT characteristics if the catalytic element remains, it is necessary to provide a process for reducing the concentration of the catalytic element.

[0103] Various types of gettering can be employed, and, described in this embodiment mode is an example of gettering which is performed before patterning the crystalline semiconductor layer **306**. First, a barrier layer **307** is formed on the surface of the crystalline semiconductor layer **306** as shown in FIG. **5**B. The barrier layer **307** is provided in order to prevent the crystalline semiconductor layer **306** from being etched in later removing a gettering site.

[0104] A thickness of the barrier layer 307 is set on the order of 1 to 10 nm, and chemical oxide which is formed by processing with ozone water may be used as the barrier layer as well. Further, chemical oxide can also be formed by processing with an aqueous solution in which an acid such as sulfuric acid, hydrochloric acid, or nitric acid is mixed with aqueous hydrogen peroxide. As another method, plasma treatment may be performed in an oxidizing atmosphere, or oxidation treatment may be performed, in which ozone is generated by irradiating ultraviolet light in an oxygen-containing atmosphere. In addition, a clean oven may also be used for heating the film at a temperature on the order of 200 to 350° C. to form a thin oxide film as a barrier layer. Furthermore, an oxide film with a thickness on the order of 1 to 5 nm may also be deposited as a barrier layer by plasma CVD, sputtering, vapor deposition, and the like. In either case, a

film, through which the catalytic element is capable of moving to the gettering site in the step of gettering and no etchant soaks in the step of removing the gettering site (a film which protects the crystalline semiconductor layer **306** from the etchant), for example, such as a chemical oxide film formed by processing with ozone water, a silicon oxide film (SiOx), and a porous film may be used.

**[0105]** Next, as a gettering site **308**, a semiconductor layer for gettering (typically, an amorphous silicon film) containing an inert gas element at a concentration of  $1 \times 10^{20}$  atoms/ cm<sup>3</sup> or more is formed on the barrier layer **307** by sputtering to have a film thickness of 25 to 250 nm. It is desirable that the gettering site **308** which is to be later removed is formed to have a low density in order to obtain a large etching selectivity ratio to the crystalline semiconductor layer **306**.

**[0106]** It is to be noted that an inert gas element which itself is inert in a semiconductor film has no bad influence on the crystalline semiconductor layer **306**. As an inert gas element, one or a plurality of elements selected from the group consisting of helium (He), neon (Ne), argon (Ar), krypton (Kr), and xenon (Xe) are used.

**[0107]** Next, heat treatment with furnace annealing or RTA is performed to achieve gettering (FIG. **5**B). In the case of using furnace annealing, heat treatment is performed in a nitrogen atmosphere at 450 to  $600^{\circ}$  C. for 0.5 to 12 hours. In the case of using RTA, a light source of a lamp for heating is turned on for 1 to 60 seconds, preferably for 30 to 60 seconds, and this operation is repeated 1 to 10 times, preferably, 2 to 6 times. Although light intensity of the light source of the lamp is optional, it is necessary that the semiconductor layer be heated instantaneously at a temperature of 600 to 1000° C., preferably, 700 to 750° C.

**[0108]** According to the above heat treatment, the catalytic element in the crystalline semiconductor layer **306** is released by thermal energy and moved to the gettering site **308** by diffusion as shown by arrows. Thus, gettering depends upon the processing temperature and the higher the temperature is, the faster gettering proceeds.

**[0109]** After the completion of the gettering step, the gettering site **308** is selectively etched to be removed. As a means of etching, there is given dry etching which does not utilize  $CIF_3$  plasma, or wet etching with an alkaline solution such as hydrazine or an aqueous solution containing tetraethyl-ammonium-hydroxide (chemical formula:  $(CH_3)_4NOH$ )). At this time, the barrier layer **307** functions as an etching stopper. After that, the barrier layer **307** is removed with hydrofluoric acid (FIG. **5**C).

[0110] After removing the barrier layer 307, the crystalline semiconductor layer 306 is patterned to form island-shaped semiconductor films 309 and 310 (FIG. 5D). The semiconductor layers 309 and 310 are formed to have a thickness on the order of 25 to 100 nm (preferably from 30 to 60 nm). Subsequently, a second insulating layer 311 is formed so as to cover the semiconductor layers 309 and 310. The film thickness of the second insulating layer 311 is reduced by on the order of 10 to 20 nm during later dry etching for forming a second gate electrode, therefore it is desirable that the film thickness of the second insulating layer 311 be set by taking the reduction into account. Specifically, the second insulating layer 311 is formed to have a thickness on the order of 40 to 150 nm (preferably from 60 to 120 nm).

**[0111]** Silicon oxide, silicon nitride, silicon nitride oxide, and the like can be used for the second insulating layer **311**, for example. Although the second insulating layer **311** has a

single layer structure in this embodiment mode, it may have a laminated structure of two or more insulating layers. Further, plasma CVD, sputtering, and the like can be used as the deposition method. For example, silicon oxide is deposited by plasma CVD to form the second insulating layer **311**, the deposition may be performed by using a mixed gas of tetraethyl orthosilicate (TEOS) and  $O_2$ , at a reaction pressure of 40 Pa, a substrate temperature of 300 to 400° C., and an RF power density (13.56 MHz) of 0.5 to 0.8 W/cm<sup>2</sup>.

**[0112]** Further, aluminum nitride can also be used as the second insulating layer **311**. The thermal conductivity coefficient of aluminum nitride is relatively high, and heat generated in the TFT can be dissipated efficiently. Further, an insulating layer on which aluminum nitride is laminated after forming silicon oxide, silicon oxynitride, or the like, which contain no aluminum, may also be used as the second insulating layer **311**.

[0113] Next, a conductive layer is formed over the second insulating layer 311 (FIG. 5E). In this embodiment mode, a first conductive layer 312a comprising TaN is formed with a thickness of 20 to 100 nm, and a second conductive layer 312b comprising W is formed with a thickness of 100 to 400 nm. Specifically, the first conductive layer 312a of TaN is formed at a deposition speed of about 40 nm/min. This is achieved by using a Ta target having a purity of 99.99%, with an internal chamber temperature set at a room temperature, a gas flow rate for Ar set at 50 ml/min, a gas flow rate for N2 set at 10 ml/min, an internal chamber pressure set at 0.6 Pa, and a deposition power set at 1 kW. Further, the second conductive layer 312b of W is formed at a deposition speed of approximately 390 nm/min. This is achieved by using a W target having a purity of 99.99%, with an internal chamber temperature set at 230° C., a gas flow rate for Ar set at 100 ml/min, an internal chamber pressure set at 1.5 Pa, and a deposition power set at 6 kW.

**[0114]** Described in this embodiment mode is an example in which the second electrode is formed by using a bilayer conductive film, however, a single layer structure or a multilayer structure having three or more layers may also be adopted. In addition, a material for each layer is not exclusively limited to the one shown in this embodiment mode.

[0115] Specifically, for each conductive layer, an element selected from the group consisting of Ta, W, Ti, Mo, Al, and Cu, or alloys or chemical compounds having one of these elements as its main component may be used. For example, a gate electrode in which Ta is used in the first layer and W in the second layer, a gate electrode in which TaN is used in the first layer and Al in the second layer, and a gate electrode in which TaN is used in the first layer and Cu in the second layer can all be considered. Also, a gate electrode in which an Ag-Pd-Cu alloy is used in either the first layer or the second layer may be used. A three-layer structure in which W, an alloy of Al and Si (Al-Si), and TiN are laminated in sequence may also be employed. Further, tungsten nitride may be used as a substitute for W, an alloy of Al and Ti (Al-Ti) may be used as a substitute for the alloy of Al and Si (Al—Si), and Ti may be used as a substitute for TiN as well. However, when forming a plurality of conductive layers, materials that have mutual etching selectivity ratio to each other are used in order to make differences in the width of the gate electrode in the channel length direction between each of the conductive layers.

**[0116]** Note that, it is very important to select optimal gas according to the materials used for conductive layers.

[0117] As shown in FIG. 6A, a mask 314 is formed next and etching is performed on the first conductive layer 312a and the second conductive layer 312b (first etching process). Etching is performed by using inductively coupled plasma (ICP) etching in this embodiment mode. A mixed gas of Cl<sub>2</sub>,  $CF_4$ , and  $O_2$  is used as an etching gas, and pressure of the etching gas within the chamber is set at 1.0 Pa. An RF power (13.56 MHz) of 500 W is applied to a coil shape electrode, thereby generating plasma. Further, an RF power (13.56 MHz) of 150 W is applied to a stage (lower electrode) on which the substrate is placed, thus applying a self-bias voltage to the substrate. The etching gas is then changed to a mixture of  $Cl_2$  and  $CF_4$ , and the total pressure is set at 1.0 Pa. Further, an RF power (13.56 MHz) of 500 W is applied to the coil shape electrode, and an RF power (13.56 MHz) of 20 W is applied to the substrate side (test piece stage).

**[0118]** The etching rate of TaN, of which the first conductive layer **312***a* is formed, and the etching rate of W, of which the second conductive layer **312***b* is formed, become nearly equal to each other when  $CF_4$  and  $Cl_2$  are used as the etching gas, and both can undergo etching to the same level.

[0119] According to the first etching process, a first shape conductive layer 315 which is structured by a lower layer 315*a* and an upper layer 315*b*, and a first shape conductive layer 316 which is structured by a lower layer 316*a* and an upper layer 316*b* are formed. Note that, each sidewall of the lower layers 315*a* and 316*b* and of the upper layers 315*b* and 316*b* take on a slightly tapered shape in the first etching process. Further, when etching is performed so that no conductive film residue remains, a surface of the gate insulating layer 311 that is not covered with the first shape conductive layers 315 and 316 may undergo etching on the order of 5 to 10 nm or more.

**[0120]** Then, as shown in FIG. 6B, etching is performed on the first shape conductive layers **315** and **316** by using the mask **314** which has already been etched its surface and thus has become smaller in width by the first etching process (second etching process). The second etching process also employs ICP etching as the first etching process. A mixed gas of  $SF_6$ ,  $Cl_2$ , and  $O_2$  is used as an etching gas, and pressure of the etching gas within the chamber is set at 1.3 Pa. An RF power (13.56 MHz) of 700 W is applied to a coil shape electrode, generating plasma. Further, an RF power (13.56 MHz) of 10 W is applied to a stage (lower electrode) on which the substrate is placed, thereby applying a self-bias voltage to the substrate.

**[0121]** An etching rate of W is increased and an etching rate of TaN, which forms the lower layers **315***b* and **316***b* of the first shape conductive layers **315** and **316** respectively, is extremely reduced when  $O_2$  is added to the mixed gas of SF<sub>6</sub> and Cl<sub>2</sub>. Higher selectivity ratio (ratio of an etching rate of W to an etching rate of TaN) can therefore be achieved.

[0122] According to the second etching process, a second shape conductive layer 317 (structured by a lower layer 317*a* and an upper layer 317*b*), and a second shape conductive layer 318 (structured by a lower layer 318*a* and an upper layer 318*b*) are formed. The width of the upper layers 317*b* and 318*b* in the channel length direction is shorter than the width of the lower layers 317*a* and 317*b*. The second shape conductive layer 317 functions as a second gate electrode of a DRAM, and the second shape conductive layer 318 functions as a gate electrode of a TFT for controlling current supply to an OLED. Further, a surface of the second shape conductive films

**317** and **318** undergoes etching on the order of 5 to 10 nm or more by the second etching process.

**[0123]** Next, as shown in FIG. 6B, impurities that impart n-type conductivity are added to the semiconductor layers **309** and **310** using the second shape conductive layers **317** and **318** as masks (first doping process). Doping is performed by ion implantation with a dose amount of  $1 \times 10^{13}$  to  $5 \times 10^{14}$  atoms/cm<sup>2</sup>, and an acceleration voltage of 40 to 80 kV. Group 5 elements such as P, As, and Sb, and group 6 elements such as S, Te, and Se, which all function as donors, may be used as the impurity elements that impart n-type conductivity. In this embodiment mode, P is employed. By the first doping process, first impurity regions **320** and **321** are formed in a self-aligning manner. Impurity elements that impart n-type conductivity are doped into the first impurity regions **320** and **321** at a concentration range of  $1 \times 10^{18}$  to  $1 \times 10^{20}$  atoms/cm<sup>3</sup>.

**[0124]** A second doping process is performed next as shown in FIG. 6C, using the upper layers **317***b* and **318***b* of the second shape conductive layers **317** and **318** as masks. The acceleration voltage used in the second doping process is set higher than that used in the first doping process to make the impurities pass through the lower layers **317***a* and **318***a* of the second shape conductive layers **317** and **318**. The second doping process forms an LDD region, and therefore the dose amount of the n-type impurities are set lower than that used in the first doping process. Specifically, the acceleration voltage is set from 60 to 120 kV, and the dose amount is set from  $1 \times 10^{13}$  to  $1 \times 10^{15}$  atoms/cm<sup>2</sup>.

[0125] A third doping process is performed next at an acceleration voltage set lower than that used in the second doping process in order to obtain the state shown in FIG. 6C. The acceleration voltage is set from 50 to 100 kV, and the dose amount is set from  $1 \times 10^{15}$  to  $1 \times 10^{17}$  atoms/cm<sup>2</sup> in the third doping process. Through the second and third doping processes, second impurity regions 322 and 323 which overlap with the lower layers 317a and 318a of the second shape conductive layers 317 and 318 respectively are formed, and further third impurity regions 324 and 325 are formed by doping more impurities into the first impurity regions 320 and 321. The n-type impurities are doped into the second impurity regions 322 and 323 at a concentration range of  $1 \times 10^{18}$  to  $5 \times 10^{19}$  atoms/cm<sup>3</sup>, and the n-type impurities are doped into the third impurity regions 324 and 325 at a concentration range of  $1 \times 10^{19}$  to  $5 \times 10^{21}$  atoms/cm<sup>3</sup>.

**[0126]** The second impurity regions **322** and **323** are formed inside the third impurity regions **324** and **325**. The second impurity regions **322** and **323** function as LDD regions, and the third impurity regions **324** and **325** function as a source or a drain region.

**[0127]** Needless to say, it is also possible to form a low concentration impurity region and a high concentration impurity region by integrating the second doping process and the third doping process into one which is performed at a suitable acceleration voltage.

**[0128]** It is to be noted that, as the island-shaped semiconductor layer **310** on which a p-channel TFT is formed does not need to be doped with n-type impurities through the second and third doping processes shown in FIGS. **6**B and **6**C, it may be covered with a mask during the doping processes of n-type impurities. In addition, it is also possible not to provide masks for the purpose of reducing the number of masks, and increase the concentration of the p-type impurities, thereby inverting the polarity of the island-shaped semiconductor layer into p type. Described in this embodiment mode is an example in which a polarity of the island-shaped semiconductor layer is inverted into p-type.

[0129] As shown in FIG. 6D, by covering the n-channel island-shaped semiconductor layer 309 with a mask 326 including resist, p-type impurities are doped into the islandshaped semiconductor layer 310 (fourth doping process). In the fourth doping process, the upper layers 317b and 318b of the second shape conductive layers 317 and 318 function as masks, thereby forming a fourth impurity region 327 where p-type impurity elements are doped into the island-shaped semiconductor layer 310 which is used for a p-channel TFT. In this embodiment mode, ion doping using diborane  $(B_2H_6)$ is employed. As for the fourth impurity region, the concentration of the n-type impurity region and that of the p-type impurity region are different in the overlapping region of the lower layers 317a and 318a of the second shape conductive layers 317 and 318 and in the other region. However, in either region, by doping p-type impurity elements at a concentration range of  $2 \times 10^{20}$  to  $2 \times 10^{21}$  atoms/cm<sup>3</sup>, the p-type conductivity becomes dominant, thus the fourth impurity region can function as a source region and a drain region of a p-channel TFT without causing problems.

**[0130]** By means of the above-described steps, impurity regions are formed in each of the island-shaped semiconductor layers.

[0131] Next, a first interlayer insulating layer 330 is formed so as to cover the inland-shaped semiconductor layers 309 and 310, the second insulating layer 311, and the second shape conductive layers 317 and 318 (FIG. 7A). An insulating film comprising silicon such as silicon oxide, silicon nitride, and silicon oxynitride may be used as the first interlayer insulating layer 330, and the film thickness is set to be about 100 to 200 nm.

[0132] Next, heat treatment is performed so as to activate the impurity elements doped into the island-shaped semiconductor layers 309 and 310. This step can be performed by thermal annealing using an annealing furnace, laser annealing, or rapid thermal annealing (RTA). For example, when performing activation by thermal annealing, it is performed at a temperature of 400 to  $700^{\circ}$  C. (preferably from 500 to  $600^{\circ}$ C.) under a nitrogen atmosphere containing oxygen at a concentration of 1 ppm or less, preferably 0.1 ppm or less. In addition, heat treatment is performed at 300 to  $450^{\circ}$  C. for 1 to 12 hours in an atmosphere containing hydrogen by 3 to 100%, thus performing hydrogenation of the island-shaped semiconductor layer. This process is performed in order to terminate dangling bonds in the semiconductor layer by using thermally excited hydrogen. Plasma hydrogenation (using hydrogen excited by plasma) may also be employed as another means of hydrogenation. Further, the activation may also be performed before forming the first interlayer insulating layer 330.

**[0133]** In accordance with the series of steps described above, an n-channel TFT **331** which is used as a DRAM and a p-channel TFT **332** which controls the current supply to an OLED can be formed.

[0134] Although the second impurity region 322 which functions as an LDD region wholly overlaps with the lower layers 317a and 318a of the second shape conductive layers 317 and 318 in this embodiment mode, the invention is not limited to this structure. For example, by performing doping between the first etching process and the second etching process, a source or a drain region is formed, and further the

lower layer is etched to have a shorter channel length in the channel length direction by the second etching process. Accordingly, it becomes possible to form both regions that overlap with the lower layers **317***a* and **318***a* of the second shape conductive layers **317** and **318** and other regions that do not overlap.

**[0135]** It is to be noted that, the plasma etching process described above is not limited to ICP etching. For example, electron cyclotron resonance (ECR) etching, RIE etching, helicon wave etching, helical resonance etching, pulse modulation etching, and other plasma etching may also be used.

**[0136]** Although only the crystallization by a catalytic element is exemplified in this embodiment mode, the invention is not limited to this. It is also possible to perform laser light irradiation of pulse oscillation in order to enhance crystallinity after the completion of the crystallization by a catalytic element. In addition, the gettering step of the invention is not limited to the one shown in this embodiment mode. Other methods may also be employed so as to reduce catalytic elements in the semiconductor layer. For example, catalytic elements may be removed by utilizing a gettering action of phosphorus as disclosed in Japanese Patent Application Laidopen No. Hei10-135468 or Hei10-135469.

[0137] Next, a second interlayer insulating layer 333 and a third interlayer insulating layer 334 are formed so as to cover the first interlayer insulating layer 330. In this embodiment mode, an organic resin such as non-photosensitive acryl is used for the second interlayer insulating layer 333. For the third interlayer insulating layer 334, a film that allows with difficulty, in comparison with other insulating layers, transmitting substances such as moisture and oxygen that may cause the deterioration of the OLED is used. Typically, a DLC film, a carbon nitride film, a silicon nitride film formed by means of RF sputtering, and the like may be preferably used. [0138] Subsequently, by etching the second insulating layer 311, the first interlayer insulating layer 330, the second interlayer insulating layer 333, and the third interlayer insulating layer 334, contact holes are formed. Then, wirings 335 to 338 which are in contact with the island-shaped semiconductor layers 309 and 310 are formed.

[0139] By forming a transparent conductive layer, covering the third interlayer insulating layer 334 and the wirings 335 to 338, and then patterning it, a pixel electrode (anode) 340 which is connected to the wiring 338 in contact with the island-shaped semiconductor layer 310 of the p-channel TFT 332 is formed (FIG. 7B). For the pixel electrode 340, a transparent conductive film provided by mixing 2 to 20% of zinc oxide (ZnO) with indium oxide may be used as well as ITO. The pixel electrode 340 may be wiped and polished with CMP by using a PVA (polyvinyl alcohol) porous body to level off the surface. Also, after polishing the surface of the pixel electrode 340 by CMP, it may be subjected to ultraviolet ray irradiation or oxygen plasma treatment and the like.

**[0140]** Then, an organic resin layer **341** which is used as a bank is formed on the third interlayer insulating layer **334**. The organic resin layer **341** is formed to have an opening in the overlapping region with the pixel electrode **340**. The organic resin layer **341**, before a light emitting layer is formed, is heated in a vacuum atmosphere in order to remove absorbed moisture and oxygen. Specifically, heat treatment is applied in a vacuum atmosphere at a temperature of 100 to 200° C. for substantially about 0.5 to 1 hour. The vacuum is desirably set at  $3 \times 10^{-7}$  Torr or less, and if possible, at  $3 \times 10^{-8}$  Torr or less. In the case of depositing a light emitting layer

after applying heat treatment onto the organic resin layer **341** in the vacuum atmosphere, the reliability can be further heightened by maintaining the light emitting layer in the vacuum atmosphere until immediately before the deposition.

**[0141]** As for an end portion in the opening of the organic resin layer **341**, it is desirable to be formed roundish so that the light emitting layer to be formed later will have no holes in the end. Specifically, a curvature radius of the curved line shown by the sectional surface of the organic resin layer **341** in the opening is desirably in the range of 0.2 to 2  $\mu$ m.

**[0142]** In an example shown in FIG. 7C, a positive photosensitive acrylic resin is used as the organic resin layer **341**. Photosensitive organic resin is classified into a positive type and a negative type: if a portion of a resin film that is exposed to an energy beam such as photo, electron, and ion is removed, it is the positive type, and if the exposed portion remains whereas the rest is removed, it is the negative type. In the invention, the negative organic resin layer **341** may also be used. In addition, the organic resin layer **341** may also be formed by using photosensitive polyimide.

[0143] When the organic resin layer 341 is formed by using negative photosensitive acrylic, an end portion in the opening of the organic resin layer 341 takes on an S-shaped cross section. It is desirable that curvature radius of the curved line in an upper end portion and a lower end portion of the opening be from 0.2 to 2  $\mu$ m.

**[0144]** According to the above structure, the coverage of a light emitting layer and a cathode that are formed later can be enhanced. Thus, it can be prevented that the pixel electrode **340** and the cathode are shorted-circuited in the holes that are formed in the light emitting layer. Moreover, by alleviating the stress of the light emitting layer, defect called shrink, in which a light emitting region decreases, can be reduced and the reliability is thus enhanced.

**[0145]** Next, a light emitting layer **342** is formed on the pixel electrode **340**. The light emitting layer **342** comprises one or a plurality of layers, which may include inorganic layers as well as organic layers.

**[0146]** Then, a cathode **343** is formed so as to cover the light emitting layer **342**. For the cathode **343**, as far as being a conductive film having a low work function, any known materials can be used. For example, Ca, Al, CaF, MgAg, AlLi and the like are preferably used.

[0147] The pixel electrode 340, the light emitting layer 342, and the cathode 343 overlap with each other in the opening of the organic resin layer 341, and the overlapping region corresponds to an OLED 344.

**[0148]** A protective layer **345** is formed over the organic resin layer **341** and the cathode **343**. As well as the third interlayer insulating layer **334**, the protective layer **345** is formed of a film that allows with difficulty, in comparison with other insulating films, transmitting substances such as moisture and oxygen that may cause the deterioration of the OLED. Typically, for example, a DLC film, a carbon nitride film, or a silicon nitride film formed by RF sputtering or the like is preferably used. It is also possible to form a protective layer by laminating the above-described film that allows transmitting substances such as moisture and oxygen with difficulty, and a film that allows with ease, in comparison with the former film, transmitting substances such as moisture and oxygen.

**[0149]** Although the example shown in FIG. 7C employs a structure in which light emitted from the OLED is emitted to the substrate **301** side, a structure in which light emitted from the OLED is emitted to the opposite side of the substrate may be employed as well.

**[0150]** Practically, when the device has been completed up to the stage shown in FIG. **7**C, a protective film (a laminate film, an ultraviolet curing resin film or the like) having good airtightness and less degasification or a transparent covering material is desirably used to package (seal) the device without exposing it to air. At that time, the reliability of the OLED is enhanced if the inside of the covering material is filled with an inert atmosphere or a moisture absorption material (e.g., barium oxide) is disposed inside.

**[0151]** By utilizing the above-described fabrication method, the n-channel TFT **331** which is used as a memory element of the DRAM and the p-channel TFT which is formed in the pixel portion can be fabricated on the same substrate.