# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 114787925 A (43) 申请公布日 2022.07.22

(21)申请号 202080086489.2

(22)申请日 2020.11.04

(30) 优先权数据 16/715,004 2019.12.16 US

(85) PCT国际申请进入国家阶段日 2022.06.13

(86) PCT国际申请的申请数据 PCT/US2020/058894 2020.11.04

(87) PCT国际申请的公布数据 W02021/126385 EN 2021.06.24

(71) 申请人 微软技术许可有限责任公司 地址 美国华盛顿州

(72) 发明人 R • 卢奇 A • 安提波夫

(74) **专利代理机构** 北京市金杜律师事务所 11256

专利代理师 董莘

(51) Int.CI.

*G11C* 11/44 (2006.01) *G11C* 11/16 (2006.01)

H01L 39/22 (2006.01)

HO3K 19/195 (2006.01)

**H03K** 19/0944 (2006.01)

权利要求书2页 说明书9页 附图10页

#### (54) 发明名称

具有基于半导体的磁自旋阀的约瑟夫森磁 性存储器

#### (57) 摘要

描述了具有基于半导体的磁自旋阀的约瑟夫森磁性存储器单元。示例存储器单元包括第一超导电极、第二超导电极以及布置在两个超导电极之间的基于半导体的磁自旋阀。基于半导体的磁自旋阀包括半导体层和第一铁磁绝缘体,第一铁磁绝缘体被布置在半导体层附近,被布置在半导体层的第一侧上,被配置为提供在第一方向上定向的固定磁化。基于半导体的磁自旋阀还包括第二铁磁绝缘体,第二铁磁绝缘体被布置在半导体层的与第一侧相对的第二侧上,被配置为提供在第一方向、或者与第一方向相对的第二方向上定向的自由磁化,以便控制与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数。

CN 114787925 A

- 1.一种存储器单元,包括:

- 第一超导电极;

- 第二超导电极:以及

基于半导体的磁自旋阀,被耦合至所述第一超导电极和所述第二超导电极,其中所述基于半导体的磁自旋阀包括:

半导体层,被布置在所述第一超导电极和所述第二超导电极之间,

第一铁磁绝缘体,被布置在所述半导体层附近,其中所述第一铁磁绝缘体被布置在所述半导体层的第一侧上,并且其中所述第一铁磁绝缘体被配置为:提供在第一方向上定向的固定磁化,以及

第二铁磁绝缘体,被布置在所述半导体层附近,其中所述第二铁磁绝缘体被布置在所述半导体层的与所述第一侧相对的第二侧上,并且其中所述第二铁磁绝缘体被配置为:提供在所述第一方向、或者与所述第一方向相对的第二方向上定向的自由磁化,以便控制与从所述第一超导电极、通过所述半导体层到所述第二超导电极的电流的流动相关联的参数。

- 2.根据权利要求1所述的存储器单元,其中与从所述第一超导电极、通过所述半导体层到所述第二超导电极的所述电流的所述流动相关联的所述参数包括:所述电流的所述流动的方向或者所述电流的所述流动的幅度。

- 3.根据权利要求1所述的存储器单元,其中与从所述第一超导电极、通过所述半导体层到所述第二超导电极的所述电流的所述流动相关联的所述参数包括:所述电流的所述流动的幅度。

- 4.根据权利要求1所述的存储器单元,其中所述第一铁磁绝缘体和所述第二铁磁绝缘体中的每个铁磁绝缘体包括硫化铕或氧化铕。

- 5.根据权利要求1所述的存储器单元,其中所述第一超导电极和所述第二超导电极中的每个超导电极包括铌。

- 6.根据权利要求1所述的存储器单元,其中所述半导体层包括砷化镓、砷化铟或者锑化铟。

- 7.根据权利要求1所述的存储器单元,其中所述存储器单元被配置为处于逻辑高状态或逻辑低状态,并且其中所述基于半导体的磁自旋阀被配置为:在所述存储器单元的两种逻辑状态下处于0状态或π状态。

- 8.一种存储器单元,包括:

- 第一超导电极;

- 第二超导电极:以及

基于半导体的磁自旋阀,被耦合至所述第一超导电极和所述第二超导电极,其中所述基于半导体的磁自旋阀包括:

半导体层,被布置在所述第一超导电极和所述第二超导电极之间,

第一铁磁绝缘体,被布置在所述半导体层的至少第一侧上,其中所述第一铁磁绝缘体 被配置为:提供在第一方向上定向的固定磁化,

第二铁磁绝缘体,被布置在所述半导体层的与所述第一侧相对的至少第二侧上,其中 所述第二铁磁绝缘体被配置为:提供在所述第一方向、或者与所述第一方向相对的第二方 向上定向的自由磁化,以便控制与从所述第一超导电极、通过所述半导体层到所述第二超 导电极的电流的流动相关联的参数,以及

控制栅,被布置在所述半导体层的顶部上,位于所述第一铁磁绝缘体和所述第二铁磁绝缘体之间,被配置为控制所述第一铁磁绝缘体和所述第二铁磁绝缘体之间的耦合。

- 9.根据权利要求8所述的存储器单元,其中与从所述第一超导电极、通过所述半导体层到所述第二超导电极的所述电流的所述流动相关联的所述参数包括:所述电流的所述流动的方向或者所述电流的所述流动的幅度。

- 10.根据权利要求8所述的存储器单元,其中与从所述第一超导电极、通过所述半导体层到所述第二超导电极的所述电流的所述流动相关联的所述参数包括:所述电流的所述流动的幅度。

- 11.根据权利要求8所述的存储器单元,其中所述第一铁磁绝缘体和所述第二铁磁绝缘体中的每个铁磁绝缘体包括硫化铕或氧化铕。

- 12.根据权利要求8所述的存储器单元,其中所述第一超导电极和所述第二超导电极中的每个超导电极包括铌。

- 13.根据权利要求8所述的存储器单元,其中所述半导体层包括砷化镓、砷化铟或者锑化铟。

- 14.根据权利要求8所述的存储器单元,其中所述存储器单元被配置为处于逻辑高状态或逻辑低状态,并且其中所述基于半导体的磁自旋阀被配置为:在所述存储器单元的两种逻辑状态下处于0状态或π状态。

- 15.一种存储器单元,包括:

- 第一超导电极;

- 第二超导电极:以及

基于半导体的磁自旋阀,被耦合至所述第一超导电极和所述第二超导电极,其中所述基于半导体的磁自旋阀包括:

半导体层,被布置在所述第一超导电极和所述第二超导电极之间,

第一铁磁绝缘体,被布置在所述半导体层的至少第一侧上,其中所述第一铁磁绝缘体被配置为提供在第一方向上定向的固定磁化,

第二铁磁绝缘体,被布置在所述半导体层的与所述第一侧相对的至少第二侧,其中所述第二铁磁绝缘体被配置为:提供在所述第一方向、或者与所述第一方向相对的第二方向上定向的自由磁化,以便控制与从所述第一超导电极、通过所述半导体层到所述第二超导电极的电流的流动相关联的参数,

第一控制栅,被配置为控制所述第一铁磁绝缘体和所述第二铁磁绝缘体之间的耦合, 以及

第二控制栅,被配置为控制所述半导体层的载流子密度。

# 具有基于半导体的磁自旋阀的约瑟夫森磁性存储器

### 背景技术

[0001] 在电子设备中使用的基于半导体的集成电路(诸如随机存取存储器)包括基于互补金属氧化物半导体(CMOS)技术的数字电路。然而,CMOS技术在设备大小方面正达到其极限。另外,基于CMOS的存储器中的泄漏电流会导致高功耗,即使当这些存储器正未被访问。 [0002] 作为示例,数据中心中的服务器消耗的功率越来越多。即使在CMOS电路处于非活动状态时,功耗也部分地是由于能量耗散造成的功率损耗的结果。这是因为即使在这种电路(诸如随机存取存储器)处于非活动状态并且不消耗任何动态功率时,由于需要维持CMOS晶体管的状态,它们仍会消耗功率。另外,由于CMOS电路使用DC电压供电,因此即使CMOS电路处于非活动状态,也会存在一定量的电流泄漏。因此,即使在这种电路不进行诸如读取/写入等处理操作时,不仅由于需要维持CMOS晶体管的状态,而且由于电流泄漏,功率也被浪

[0003] 基于CMOS技术的存储器的替代方法是约瑟夫森磁性存储器。

### 发明内容

费了。

[0004] 在一个示例中,本公开涉及一种包括第一超导电极的存储器单元。存储器单元还可以包括第二超导电极。存储器单元还可以包括耦合至第一超导电极和第二超导电极的基于半导体的磁自旋阀。基于半导体的磁自旋阀可以包括被布置在第一超导电极和第二超导电极之间的半导体层。基于半导体的磁自旋阀还可以包括第一铁磁绝缘体,第一铁磁绝缘体被布置在半导体层附近,其中第一铁磁绝缘体被布置在半导体层的第一侧上,并且其中第一铁磁绝缘体被配置为:提供在第一方向上定向的固定磁化。基于半导体的磁自旋阀还可以包括第二铁磁绝缘体,第二铁磁绝缘体被布置在半导体层附近,其中第二铁磁绝缘体被布置在半导体层的与第一侧相对的第二侧上,并且其中第二铁磁绝缘体被配置为:提供在第一方向、或者与第一方向相对的第二方向上定向的自由磁化,以便控制与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数。

[0005] 在另一示例中,本公开涉及一种包括第一超导电极的存储器单元。存储器单元还可以包括第二超导电极。存储器单元还可以包括被耦合至第一超导电极和第二超导电极的基于半导体的磁自旋阀可以包括被布置在第一超导电极和第二超导电极之间的半导体层。基于半导体的磁自旋阀还可以包括第一铁磁绝缘体,第一铁磁绝缘体被布置在至少半导体层的第一侧,并且其中第一铁磁绝缘体被配置为:提供在第一方向上定向的固定磁化。基于半导体的磁自旋阀还可以包括第二铁磁绝缘体,第二铁磁绝缘体被布置在半导体层的与第一侧相对的至少第二侧上,并且其中第二铁磁绝缘体被配置为:提供在第一方向、或者与第一方向相对的第二方向上定向的自由磁化,以便控制与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数。基于半导体的磁自旋阀还可以包括控制栅,被布置在半导体层的顶部,位于第一铁磁绝缘体和第二铁磁绝缘体之间的耦合。

[0006] 在再一示例中,本公开涉及一种包括第一超导电极的存储器单元。存储器单元还

可以包括第二超导电极。存储器单元还可以包括被耦合至第一超导电极和第二超导电极和第二超导电极和简点。基于半导体的磁自旋阀可以包括被布置在第一超导电极和第二超导电极之间的半导体层。基于半导体的磁自旋阀还可以包括第一铁磁绝缘体,第一铁磁绝缘体被布置在半导体层的至少第一侧上,其中第一铁磁绝缘体被配置为:提供在第一方向上定向的固定磁化。基于半导体的磁自旋阀还可以包括第二铁磁绝缘体,第二铁磁绝缘体被布置在至少半导体层的与第一侧相对的第二侧,其中第二铁磁绝缘体被配置为:提供在第一方向、或者与第一方向相对的第二方向上定向的自由磁化,以便控制与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数。基于半导体的磁自旋阀还可以包括第一控制栅,第一控制栅被配置为控制第一铁磁绝缘体和第二铁磁绝缘体之间的耦合。基于半导体的磁自旋阀还可以包括第二控制栅,第二控制栅被配置为控制半导体层的载流子密度。

[0007] 该发明内容被提供来以简化的形式介绍对于下面在详细描述中进一步描述的概念的选择。该发明内容不旨在标识要求保护的主题的关键特征或者必要特征,也不旨在被用于限制要求保护的主题的范围。

## 附图说明

[0008] 本公开通过示例图示并且不受附图限制,其中相同的附图标记指示类似的元素。 附图中的元素为了简单和清晰起见图示,并且不一定按比例绘制。

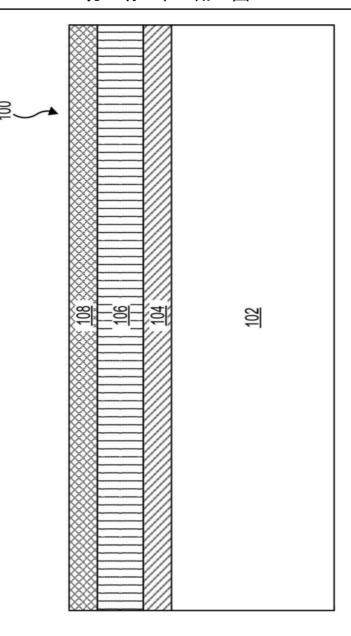

[0009] 图1示出了制造期间的示例存储器单元的截面图;

[0010] 图2示出了制造期间的示例存储器单元的截面图;

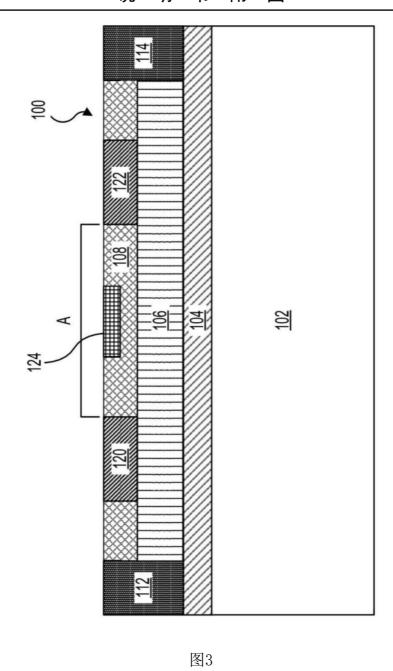

[0011] 图3示出了制造期间的示例存储器单元的截面图;

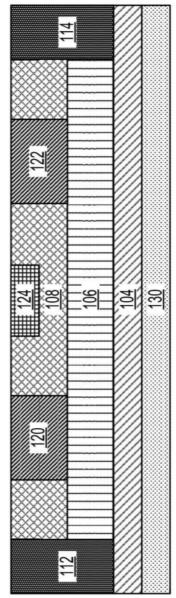

[0012] 图4示出了制造期间的示例存储器单元的截面图;

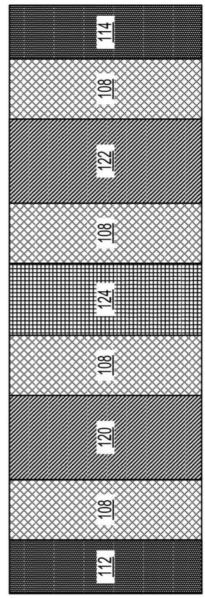

[0013] 图5示出了制造期间的示例存储器单元的顶视图;

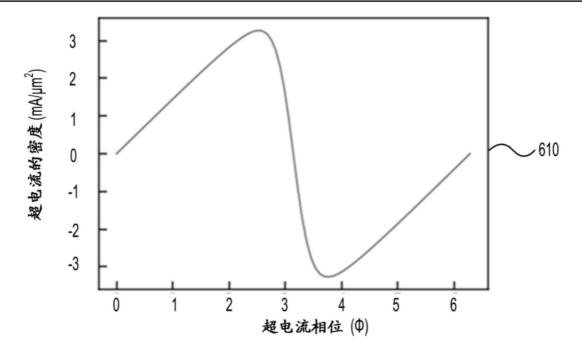

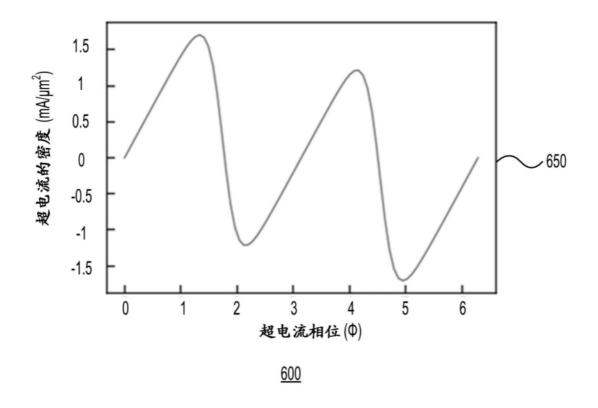

[0014] 图6示出了根据一个示例的流过半导体层的超电流的密度;

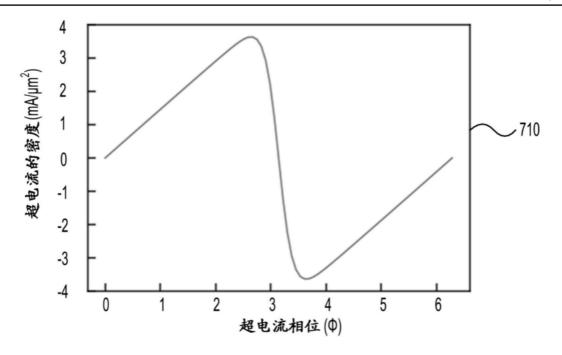

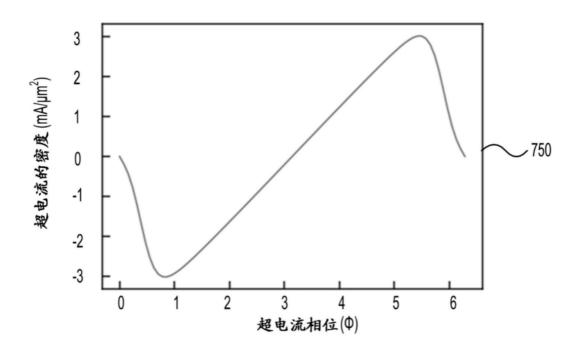

[0015] 图7示出了根据另一示例的流过半导体层的超电流的密度:

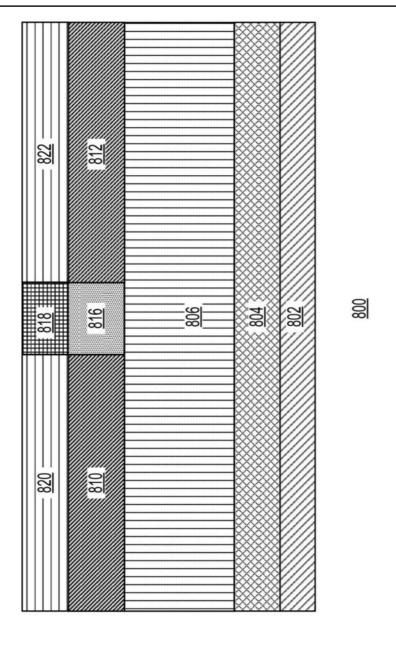

[0016] 图8示出了制造期间的另一示例存储器单元的截面图:

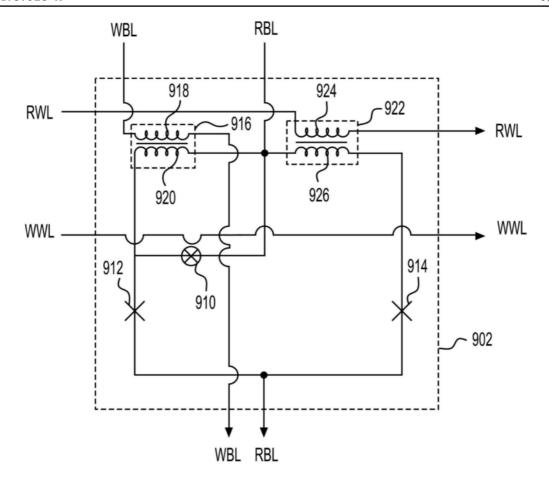

[0017] 图9示出了根据一个示例的存储器单元电路;以及

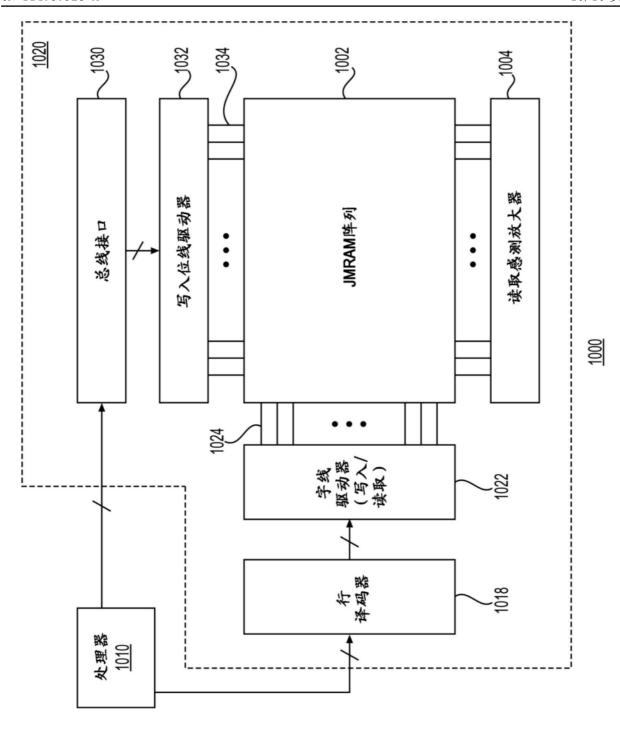

[0018] 图10示出了根据一个示例的包括耦合至处理器的存储器的计算系统。

### 具体实施方式

[0019] 本公开中描述的示例涉及基于超导逻辑的存储器系统,包括具有基于半导体的磁自旋阀的存储器。某些示例还涉及具有基于半导体的磁自旋阀的约瑟夫森磁性随机存取存储器 (JMRAM)。与CMOS晶体管不同,超导设备使用基于约瑟夫森结的设备。

[0020] 包括传输线的各种超导电路可以根据需要通过电感器或其他组件耦合多个约瑟夫森结来形成。单通量量子(SFQ)脉冲可以在至少一个时钟的控制下经由这些传输线传播。SFQ脉冲可以是正的或负的。作为示例,当正弦偏置电流被供应给结时,正脉冲和负脉冲都可以在相反的时钟相位期间在传输线上向右传播。

[0021] 微波信号(例如SFQ脉冲)可以被用于控制存储器单元的状态。在读取/写入操作期间,字线和位线可以由经由地址总线到达的SFQ脉冲选择性地激活。这些脉冲又可以控制字

线和位线驱动器,字线和位线驱动器可以将字线和位线电流提供给相关的存储器单元。作为示例,这种存储器单元的状态可以使用超导量子干涉设备(SQUID)读出。存储器单元电路可以包括SQUID和基于半导体的磁自旋阀设备。

[0022] 存储器单元可以被布置为行和列,使得每行可以通过公共通量偏置(例如读取字线信号)来激活,并且每个位线可以形成传输线,传输线可以在电压状态下将存储器单元的输出传播到列的一端的感测放大器。列中的存储器单元可以由公共电流源串行偏置;例如通量泵。

[0023] 图1示出了制造期间的示例存储器单元100的截面图。在该示例中,作为该步骤的一部分,从衬底102开始,缓冲层104可以被形成。在该示例中,衬底102可以是磷化铟(InP)衬底。缓冲层104可以是砷化铟镓(InGaAs)层。接下来,可以在顶部缓冲层104上形成半导体层106。半导体层106可以包括砷化镓(GaAs)或砷化铟(InAs)。半导体层106还可以包括锑化铟(InSb)。另外,半导体层106也可以是三元合金,包括任何这些材料的组合(例如GaAsSb和InAsSb)。这些层中的每层都可以使用分子束外延(MBE)来形成。作为示例,MBE相关过程可以在允许在真空中沉积适当材料的MBE系统中执行。尽管图1示出了以某种方式布置的一定数量的存储器单元100的层,但是可以有更多或更少数量的层以不同方式布置。

[0024] 图2示出了制造期间的示例存储器单元100的截面图。在该示例中,作为该步骤的一部分,可以在半导体层106的顶部形成电介质层108。电介质层108可以包括任何合适的电介质,包括基于氧化物的电介质。尽管图2示出了以某种方式布置的存储器单元100的一定数量的层,但是可以有更多或更少数量的层以不同方式布置。

[0025] 图3示出了制造期间的示例存储器单元的截面图。在该示例中,作为可以包括多个子步骤的该步骤的一部分,超导电极112和另一超导电极114可以被形成。如图3所示,超导电极112和超导电极114可以被形成,使得在存储器单元100的操作期间,电流可以通过半导体层106从超导电极112流到超导电极114。电流也可以沿着相反方向流动。在该示例中,超导电极112和超导电极114可以通过使用掩模和基于光刻的制造技术来形成。因此,根据需要,半导体层106和电介质层108可以被蚀刻以限定可以形成电极的区域。在该示例中,超导电极112和超导电极114可以包括超导金属,诸如铌。其他铌合金也可以被使用,诸如铌-钛-氮化物(NbTiN)。

[0026] 继续参照图3,电介质层108可以被进一步处理以形成铁磁绝缘体120和另一铁磁绝缘体122。在一个示例中,铁磁绝缘体120和铁磁绝缘体122中的每个铁磁绝缘体可以包括硫化铕(EuS)。在另一示例中,铁磁绝缘体120和铁磁绝缘体122中的每个铁磁绝缘体可以包括氧化铕(Eu0)。铁磁绝缘体120可以与铁磁绝缘体122间隔开所选距离(例如如图3中的A所示)。所选距离(A)的量可以被选择以控制铁磁绝缘体120和铁磁绝缘体122之间的耦合。虽然铁磁绝缘体120和铁磁绝缘体122被示出为被形成在半导体层106的顶部,但它们可以在其他地方被形成,只要它们靠近半导体层106即可。如在本公开中使用的,术语"靠近"包括在半导体层106顶部的铁磁绝缘体的布置,如图3所示。然而,该术语不仅被限于该示例。只要铁磁绝缘体的布置方式可以影响流过半导体层106的超电流的相位,它们就被布置为"靠近"半导体层106。

[0027] 仍然参照图3,作为存储器单元100的一部分,控制栅124可以被形成。控制栅124可以包括合适的金属或合适的叠层。示例金属包括铝、铜、钛或其他金属。在该示例中,控制栅

124可以被配置为控制通过半导体层106中的电子在铁磁绝缘体120和铁磁绝缘体122之间的耦合。耦合可以通过经由控制栅124施加特定电压来控制。在一个示例中,虽然使能量消耗最小化可能很重要,但铁磁绝缘体120和铁磁绝缘体122之间的耦合需要足够弱,使得不受控制的状态变化不会发生。因此,如果两个铁磁体之间存在一些磁矩中断,则控制栅124可以将其最小化以使存储器单元稳定(例如存储器单元状态不会自行翻转,但同时,流过半导体层106的超电流的差异可能足以区分磁化差异)。经由控制栅124施加电压可以被选择以实现这些目标。这是因为经由栅极124施加电压可能会影响半导体层106中的电荷载流子。另外,如上面提到的,铁磁绝缘体之间的距离可以被选择以进一步控制铁磁绝缘体之间的耦合。尽管图3示出了以某种方式布置的存储器单元100的一定数量的层,但是可以有更多或更少数量的层以不同方式布置。另外,存储器单元100的层和其他特征可以以不同的顺序形成。作为示例,电介质层108可以在形成铁磁绝缘体120和铁磁绝缘体122之后沉积,然后控制栅124可以被形成。

[0028] 图4示出了制造期间的示例存储器单元100的截面图。在该示例中,作为该步骤的一部分,背栅130可以被形成。在该示例中,背栅130可以使用衬底102的一部分来形成。因此,作为示例,具有适当掺杂的衬底102的一部分可以用作背栅130。在另一示例中,背栅130可以包括金属合金或金属,诸如铝、铌或铜。背栅130还可以包括叠层,包括多个层。在再一示例中,背栅130可以是半导体层106的掺杂部分。在一个示例中,背栅130可以充当存储器设备100的另一控制栅。因此,向背栅130施加电压可以控制半导体层106中的载流子的密度。尽管图4示出了以某种方式布置的存储器单元100的一定数量的层,但是可以有更多或更少数量的层以不同方式布置。作为示例,存储器单元100可以不包括控制栅124。这是因为铁磁绝缘体之间的耦合可以通过早前描述的那样将它们间隔开来控制。作为另一示例,存储器单元100可以不包括背栅130。这是因为半导体层106中的载流子的密度可以通过控制用于形成存储器单元100的叠层中的掺杂来控制。

[0029] 图5示出了制造期间的示例存储器单元100的顶视图。在该示例中,顶视图示出了示例布置,包括超导电极112、超导电极114、电介质层108、铁磁绝缘体120、铁磁绝缘体122和控制栅124。尽管图5示出了以某种方式布置的存储器单元100的一定数量的层,但是可以有更多或更少数量的层以不同方式布置。作为示例,这些层和组件不需要以平面布置形成。[0030] 就存储器单元100的操作而言,半导体层106中的电子可以携带超电流,这可以经历磁化,并且当两个铁磁绝缘体(例如铁磁绝缘体120和铁磁绝缘体122)中的每个铁磁绝缘体的磁化处于相同方向(例如彼此平行)时,在传输期间累积的相位可以被添加。备选地,当两个铁磁绝缘体(例如铁磁绝缘体120和铁磁绝缘体122)中的每个铁磁绝缘体的磁化方向相反(例如彼此反平行)时,相位可以被抵消。在存储器单元100中,没有超电流流过铁磁绝缘体(例如铁磁绝缘体120和铁磁绝缘体122)。

[0031] 图6示出了流过半导体层106的超电流的密度和超电流的相位之间的关系,这取决于铁磁绝缘体的磁化是平行还是反平行。曲线图610示出了当铁磁绝缘体的磁化平行时,超电流密度  $(mA/\mu m^2)$  和超导相  $(\Phi)$  之间的关系。曲线图650示出了当铁磁绝缘体的磁化反平行时,超电流密度  $(mA/\mu m^2)$  和超导相  $(\Phi)$  之间的关系。如经由曲线图610和650所示,当铁磁绝缘体的磁化平行而不是反平行时,针对某些超导相  $(\Phi)$  值,超电流的幅度较低。类似地,与电流相关联的符号针对相同的相位值是不同的。这些参数中的每个参数可以被控制以影

响存储器单元100的状态的改变。

[0032] 图7示出了流过半导体层106的超电流的密度和超电流的相位之间的关系,这取决于铁磁绝缘体的磁化是平行还是反平行。图7对应于结行为。曲线图710示出了当铁磁绝缘体的磁化平行时,超电流密度(mA/μm²)和超导相(Φ)之间的关系。曲线图750示出了当铁磁绝缘体的磁化反平行时,超电流密度(mA/μm²)和超导相(Φ)之间的关系。如经由曲线图710和750所示,当铁磁绝缘体的磁化平行而不是反平行时,针对某些超导相(Φ)值,超电流的幅度较低。类似地,与电流相关联的符号针对某些相位值是不同的。这些参数中的每个参数可以被控制以影响存储器单元100的状态的改变。相对于图7所示的曲线图中的铁磁绝缘体的耦合强度,铁磁绝缘体的耦合强度在图6所示的曲线图中较弱。因此,在平行配置中,相对于图6所示的曲线图,超电流的幅度超过图7所示的曲线图。

[0033] 有利地,示例存储器单元100包括仅两种材料以形成约瑟夫森结,从而导致可能对存储器单元100的操作产生不利影响的界面更少。然而,常规的JMRAM存储器单元可以包括多个界面一例如铌和铜之间的界面以及铜和铁或镍之间的另一界面。这些界面中的每个界面都可以改变在这些界面上传播的信号的特性。另外,在常规的JMRAM存储器单元中,约瑟夫森结可能使用铜作为间隔物,这在一些实例中可能会导致强自旋轨道耦合,从而导致自旋轨道物理相关问题。然而,存储器单元100不包括这种铜引起的自旋轨道物理相关问题。而且,铁磁绝缘体(诸如EuS)中的铁磁畴非常大,因此多畴物理的任何有害影响被消除。这是因为在典型的铁磁体中,存在彼此干扰的多个磁畴,从而导致多畴效应。

[0034] 另外,对应于超电流的电子可以基于通过铁磁体扩散的电子以抑制超电流的方式受到影响。然而,在存储器单元100中,电子通过超导体层106的运动是弹道的,而不是扩散的,因此超电流的传输更易于管理。弹道传输中的轨迹很简单一轨迹基本上是从一个引线到另一引线的直线轨迹,因此更容易理解和优化具有弹道传输的叠层。然而,在扩散传输的情况下,轨迹是复杂的。电子在携带电子的整个结构中扩散,并且它们的不同轨迹抵消了信号;因此,这种结构中的超电流衰减得非常快。因此,人们可以控制半导体中无序的数量,从而产生具有弹道传输的干净叠层。相比之下,在金属结中,无序是固有的并且不是可控的(例如即使使用控制栅)。

[0035] 另外,如所描述的,在存储器单元的制造期间,高质量的材料叠层可以使用分子束外延(MBE)来生长,该分子束外延(MBE)甚至不易受微弱无序的影响。使用MBE生长的叠层允许对每层沉积进行高度控制。另外,与使用溅射技术形成的设备相比,叠层具有少量界面(例如只有两个界面),其中每种新材料的沉积都会改变叠层的特性。而且,系统的半导体部分(具有沉积的铁磁绝缘体)可以使用制造技术来单独表征。另外,存储器单元100在铁磁绝缘体和超电流之间具有高度可调谐的耦合,这允许优化存储器单元100的操作体制。如早前关于存储器单元100解释的,使用正确的间距和控制栅,磁阀之间的耦合可以被优化。

[0036] 图8示出了制造期间的另一示例存储器单元800的截面图。存储器单元800的各层和其他部分可以使用与早前相对于图1至5描述的类似过程来形成。存储器单元800可以包括背栅802、电介质层804、超导体层806、铁磁绝缘体810、另一铁磁绝缘体812、栅极电介质816、控制栅818、左栅820和右栅822。因此,存储器单元800可以包括附加栅极,左栅820和右栅822。这些栅极中的每个栅极可以被配置为静电栅。向这些栅极施加电压可以被构造为允许单个传输通道通过半导体层806。在一个示例中,半导体层806可以是具有10nm厚度的砷

化镓(GaAs)线。在该示例中,半导体层806可以与铁磁绝缘体中的每个铁磁绝缘体具有大约50nm到100nm长的边界。自旋阀结可以是20nm到50nm长。尽管图8示出了以某种方式布置的存储器单元800的一定数量的层,但是可以有更多或更少数量的层以不同方式布置。

[0037] 就存储器单元800的操作而言,它可以以与存储器单元100类似的方式操作,如早前相对于图6和图7解释的。半导体层806中的电子可以携带超电流,这可以经历磁化,并且当两个铁磁绝缘体(例如铁磁绝缘体810和铁磁绝缘体812)中的每个铁磁绝缘体的磁化处于相同方向(例如彼此平行)时,在传输期间累积的相位可以被添加。备选地,当两个铁磁绝缘体(例如铁磁绝缘体810和铁磁绝缘体812)中的每个铁磁绝缘体的磁化方向相反(例如彼此反平行)时,相位可以被抵消。超电流的幅度和相位的变化可以类似于早前相对于图6和图7解释的。总之,对磁性绝缘体的邻近效应控制超电流的幅度和相位,这取决于磁分裂(例如塞曼感应分裂)的强度和存储器单元的几何形状。在示例存储器单元中,邻近效应是出现在两种材料一超导电极和半导体层一的界面处的效应。靠近超导电极的半导体层将继承超导体的一些特性,因为电子可以在短时间内隧道进入超导体并且感测该材料中存在的相关性。因此,在与存储器单元相关的半导体层中存在邻近感应超导性。来自半导体层的电子在短时间内隧道进入铁磁绝缘体并且经历磁相关。

[0038] 图9示出了根据一个示例的存储器单元电路900的图。在一个示例中,存储器单元电路900可以包括存储器存储元件902,该存储器存储元件902包括至少一个存储器单元设备910(例如存储器单元100或存储器单元700)和至少两个约瑟夫森结912和914,如图9所示。存储器存储元件902还可以包括变压器916。变压器916可以包括两个电感器918和920。存储器存储元件902还可以包括另一变压器922。变压器922可以包括电感器924和926。在一个示例中,约瑟夫森结912和914可以形成读出超导量子干涉设备(SQUID)。

[0039] 继续参照图9,存储器单元电路900可以被耦合至字线和位线以执行各种存储器操作,包括例如读取和写入操作。作为示例,用于执行读取操作的读取字线(RWL)可以被耦合至存储器单元电路900。在该示例中,读取字线(RWL)可以经由变压器922被耦合。用于执行写入操作的写入字线(WWL)可以被耦合至存储器单元电路900。写入字线可以被磁耦合至存储器单元设备910。另外,用于执行读取操作的读取位线(RBL)可以被耦合至存储器单元电路900。用于执行写入操作的写入位线(WBL)也可以被耦合至存储器单元电路900。在该示例中,写入位线(WBL)可以经由变压器916被耦合。存储器单元设备910可以被用作改变存储器单元电路900的状态的控制机制。在一个实例中,与存储器单元设备910的耦合可以使得铁磁绝缘体的磁化可以通过施加局部写入字线电流并且通过施加写入位线电流来改变。

[0040] 在一个示例中,存储器单元设备910可以处于第一状态(例如对应于由铁磁绝缘体提供的磁化是平行时)和第二状态(例如对应于由铁磁绝缘体提供的磁化是反平行时)。在这些状态中的至少一种中,存储器单元设备910可以将通量施加到JJ 912和JJ 914,使得在字读取电流的施加下,由于存储器单元设备910生成的通量和经由变压器922耦合字读取电流,存储器存储元件902中的感应电流可以与施加的位读取电流组合以触发约瑟夫森结912和914,从而将读出SQUID发送给电压状态。该电压可以沿着读取位线生成电流,该电流可以充当具有一定阻抗的传输线。该电流可以使用感测放大器被感测。在一个示例中,一旦被感测放大器放大,电流脉冲的存在或不存在可以将存储器单元电路900的状态确定为逻辑低或逻辑高。

[0041] 在一个示例中,在写入操作期间,写入字线(WWL)和写入位线(WBL)可以从相应驱动器接收电流。通过在SQUID回路中嵌入磁结并且经由超导变压器(例如经由图9中的变压器916)向回路施加通量,通过存储器单元设备910的超电流的幅度或符号可以被控制,并且可以被用于实现磁开关。尽管图9示出了以某种方式布置的一定数量的组件,但是存储器单元电路900可以包括不同布置的附加组件或更少组件。

[0042] 图10示出了根据一个示例的包括耦合至处理器1010的存储器1020的计算系统100。处理器1010可以以早前解释的方式在存储器1020上执行读取或写入操作。存储器1020可以被用作数据中心中的存储装置的一部分,用于递送基于云的服务,诸如软件即服务、平台即服务或其他服务。存储器系统1020可以包括布置为行和列的JMRAM存储器单元的阵列1002。在一个示例中,阵列1002可以是存储器单元电路的阵列,例如存储器单元电路900。存储器系统1020还可以包括可以被配置为对行控制/地址信号进行译码的行译码器1018。行译码器1018还可以被耦合至字线驱动器1022。字线驱动器1022可以包括:用于将字线读取/写入电流提供给与所选字线相关联的存储器单元的子集或全部以用于任何读取或写入操作的电路系统。字线驱动器1022可以经由字线1024提供这种电流。

[0043] 存储器系统1020还可以包括总线接口1030,该总线接口1030可以被配置为从处理器1010接收控制信号或其他信号。总线接口1030还可以被耦合至位线驱动器1032。位线驱动器1032可以包括:用于将位线读取电流提供给与所选位线相关联的存储器单元的子集或全部以用于任何读取或写入操作的电路系统。位线驱动器1032可以经由位线1034提供这种电流。位线1034可以包括读取位线和写入位线。换言之,不同的位线可以被用于向所选存储器单元提供电流以进行读取或写入操作。通过使用行地址和列地址,任何存储器单元可以使用地址来访问。位线中的每个位线(例如位线1034)还可以被耦合至感测放大器1004,用于感测位线以确定存储器单元阵列1002中的每个阵列的逻辑状态。尽管图10示出了以某种方式布置的计算系统1000的一定数量的组件,但是可以有更多或更少数量的组件以不同方式布置。

[0044] 总之,本公开涉及一种包括第一超导电极的存储器单元。存储器单元还可以包括第二超导电极。存储器单元还可以包括耦合至第一超导电极和第二超导电极的基于半导体的磁自旋阀可以包括被布置在第一超导电极和第二超导电极之间的半导体层。基于半导体的磁自旋阀还可以包括第一铁磁绝缘体,第一铁磁绝缘体被布置在半导体层附近,其中第一铁磁绝缘体被布置在半导体层的第一侧上,并且其中第一铁磁绝缘体被配置为:提供在第一方向上定向的固定磁化。基于半导体的磁自旋阀还可以包括第二铁磁绝缘体,第二铁磁绝缘体被布置在半导体层附近,其中第二铁磁绝缘体被布置在半导体层的与第一侧相对的第二侧上,并且其中第二铁磁绝缘体被配置为:提供在第一方向、或者与第一向相对的第二向上定向的自由磁化,以便控制与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数。

[0045] 与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数可以包括:电流的流动的方向或者电流的流动的幅度。与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数可以包括:电流的流动的幅度。

[0046] 第一铁磁绝缘体和第二铁磁绝缘体中的每个铁磁绝缘体可以包括硫化铕或者氧化铕。第一铁磁绝缘体和第二铁磁绝缘体中的每个铁磁绝缘体可以包括铌。

[0047] 半导体层可以包括砷化镓、砷化铟或者锑化铟。存储器单元可以被配置为处于逻辑高状态或逻辑低状态,并且基于半导体的磁自旋阀可以被配置为:在存储器单元的两种逻辑状态下处于0状态或π状态。

[0048] 在另一示例中,本公开涉及一种包括第一超导电极的存储器单元。存储器单元还可以包括第二超导电极。存储器单元还可以包括被耦合至第一超导电极和第二超导电极的基于半导体的磁自旋阀可以包括被布置在第一超导电极和第二超导电极之间的半导体层。基于半导体的磁自旋阀还可以包括第一铁磁绝缘体,第一铁磁绝缘体被布置在至少半导体层的第一侧,并且其中第一铁磁绝缘体被配置为:提供在第一方向上定向的固定磁化。基于半导体的磁自旋阀还可以包括第二铁磁绝缘体,该第二铁磁绝缘体被布置在半导体层的与第一侧相对的至少第二侧上,并且其中第二铁磁绝缘体被配置为:提供在第一方向、或者与第一方向相对的第二方向上定向的自由磁化,以便控制与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数。基于半导体的磁自旋阀还可以包括控制栅,被布置在半导体层的顶部上,位于第一铁磁绝缘体和第二铁磁绝缘体之间的耦合。

[0049] 与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数可以包括:电流的流动的方向或者电流的流动的幅度。与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数可以包括:电流的流动的幅度。

[0050] 第一铁磁绝缘体和第二铁磁绝缘体中的每个铁磁绝缘体可以包括硫化铕或者氧化铕。第一铁磁绝缘体和第二铁磁绝缘体中的每个铁磁绝缘体可以包括铌。

[0051] 半导体层可以包括砷化镓、砷化铟或者锑化铟。存储器单元可以被配置为处于逻辑高状态或逻辑低状态,并且基于半导体的磁自旋阀可以被配置为:在存储器单元的两种逻辑状态下处于0状态或π状态。

[0052] 在再一示例中,本公开涉及一种包括第一超导电极的存储器单元。存储器单元还可以包括第二超导电极。存储器单元还可以包括耦合至第一超导电极和第二超导电极的基于半导体的磁自旋阀可以包括被布置在第一超导电极和第二超导电极之间的半导体层。基于半导体的磁自旋阀还可以包括第一铁磁绝缘体,第一铁磁绝缘体被布置在半导体层的至少第一侧上,其中第一铁磁绝缘体被配置为提供在第一方向上定向的固定磁化。基于半导体的磁自旋阀还可以包括第二铁磁绝缘体被配置为:提供在第一方向、或者与第一方向相对的至少第二侧上,其中第二铁磁绝缘体被配置为:提供在第一方向、或者与第一方向相对的第二方向上定向的自由磁化,以便控制与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数。基于半导体的磁自旋阀还可以包括第一控制栅,第一控制栅被配置为控制第一铁磁绝缘体和第二铁磁绝缘体之间的耦合。基于半导体的磁自旋阀还可以包括第二控制栅,第二控制栅被配置为控制半导体层的载流子密度。

[0053] 与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数可以包括:电流的流动的方向或者电流的流动的幅度。与从第一超导电极、通过半导体层到第二超导电极的电流的流动相关联的参数可以包括:电流的流动的幅度,并且第二控制栅还可以被配置为控制电流的流动的幅度。

[0054] 第一铁磁绝缘体可以与第二铁磁绝缘体间隔开所选距离,并且所选距离可以被选

择以控制第一铁磁绝缘体和第二铁磁绝缘体之间的耦合。存储器单元还可以包括耦合至第一铁磁绝缘体的第三控制栅和耦合至第二铁磁绝缘体的第四控制栅,其中第三控制栅和第四控制栅中的每个控制栅可以被配置为控制半导体层附近的载流子密度。存储器单元可以被配置为处于逻辑高状态或逻辑低状态,并且基于半导体的磁自旋阀可以被配置为:在存储器单元的两种逻辑状态下处于0状态或π状态。

[0055] 要理解的是,本文描绘的方法、模块和组件仅仅是示例性的。备选地或者另外,本文描述的功能性可以至少部分地由一个或多个硬件逻辑组件执行。例如而非限制,可以被使用的说明性类型的硬件逻辑组件包括现场可编程门阵列(FPGA)、专用集成电路(ASIC)、专用标准产品(ASSP)、片上系统(SOC)、复杂可编程逻辑设备(CPLD)等。在抽象但仍然明确的意义上,实现相同功能性的任何组件布置被有效地"关联",使得期望的功能性被实现。因此,本文中组合以实现特定功能性的任何两个组件可以被视为彼此"关联",使得期望的功能性被实现,而与架构或中间组件无关。同样地,如此关联的任何两个组件也可以被视为彼此"可操作地连接"或"耦合",以实现期望的功能性。

[0056] 与本公开中描述的示例相关联的功能性还可以包括存储在非瞬态介质中的指令。本文使用的术语"非瞬态介质"指的是存储数据和/或指令的任何介质,该指令使机器以具体方式操作。示例性非瞬态介质可以包括非易失性介质和/或易失性介质。非易失性介质可以包括例如硬盘、固态驱动器、磁盘或磁带、光盘或光学磁带、闪存、EPROM、NVRAM、PRAM或其他这种介质或者这种介质的联网版本。易失性介质可以包括例如动态存储器,诸如DRAM、SRAM、缓存或其他这种介质。非瞬态介质不同于传输介质,但是可以与传输介质结合使用。传输介质被用于向或从机器传送数据和/或指令。示例性传输介质可以包括同轴电缆、光纤、铜线和无线介质,诸如无线电波。

[0057] 此外,本领域技术人员将认识到,上述操作的功能性之间的边界仅仅是说明性的。 多个操作的功能性可以被组合为单个操作,和/或单个操作的功能性可以被分布在附加操作中。而且,替代实施例可以包括特定操作的多个实例,并且操作的顺序在各种其他实施例中可以更改。

[0058] 虽然本公开提供了具体示例,但是各种修改和改变可以在不脱离下面的权利要求中陈述的本公开的范围的情况下进行。因此,说明书和附图应被认为是说明性的而非限制性的,并且所有这种修改旨在被包括在本公开的范围内。本文关于具体示例描述的任何益处、优点或问题的解决方案不旨在被解释为任何或所有权利要求的关键、必需或基本特征或元素。

[0059] 此外,本文使用的术语"一"或"一个"被定义为一个或多于一个。而且,在权利要求中使用诸如"至少一个"和"一个或多个"等介绍性短语不应被解释为意味着,由不定冠词"一"或"一个"介绍另一权利要求元素将包含这种介绍的权利要求元素的任何特定权利要求限制于仅包含一个这种元素的发明,即使同一权利要求包括介绍性短语"一个或多个"或"至少一个"以及不定冠词(诸如"一"或"一个")时也是如此。这同样适用于定冠词的使用。

[0060] 除非另有规定,否则诸如"第一"和"第二"等术语被用于任意地区分这种术语描述的元素。因此,这些术语不一定旨在指示这种元素的空间、时间或其他优先化。

图1

图2

图4

图5

<u>700</u>

<u>900</u>

图10