#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5720261号 (P5720261)

(45) 発行日 平成27年5月20日 (2015.5.20)

(24) 登録日 平成27年4月3日(2015.4.3)

神奈川県川崎市中原区上小田中4丁目1番

最終頁に続く

1号 富士通株式会社内

| (51) Int.Cl. |       |           | FΙ   |       |         |

|--------------|-------|-----------|------|-------|---------|

| HO1P         | 1/15  | (2006.01) | HO1P | 1/15  |         |

| HO1L         | 23/12 | (2006.01) | HO1L | 23/12 | 3 O 1 C |

| H04B         | 1/44  | (2006.01) | HO4B | 1/44  |         |

| H05K         | 1/02  | (2006.01) | H05K | 1/02  | P       |

請求項の数 7 (全 14 頁)

| (21) 出願番号 | 特願2011-9278 (P2011-9278)      | (73) 特許権都 | 耸 000005223         |

|-----------|-------------------------------|-----------|---------------------|

| (22) 出願日  | 平成23年1月19日(2011.1.19)         |           | 富士通株式会社             |

| (65) 公開番号 | 特開2012-151694 (P2012-151694A) |           | 神奈川県川崎市中原区上小田中4丁目1番 |

| (43) 公開日  | 平成24年8月9日(2012.8.9)           |           | 1号                  |

| 審査請求日     | 平成25年10月7日(2013.10.7)         | (74) 代理人  | 100070150           |

|           |                               |           | 弁理士 伊東 忠彦           |

|           |                               | (74) 代理人  | 100146776           |

|           |                               |           | 弁理士 山口 昭則           |

|           |                               | (72) 発明者  | 藤井 孝郎               |

|           |                               |           | 神奈川県川崎市中原区上小田中4丁目1番 |

|           |                               |           | 1号 株式会社富士通システム統合研究所 |

|           |                               |           | 内                   |

||(72)発明者 赤瀬川 章彦

(54) 【発明の名称】電子回路及び送受信システム

### (57)【特許請求の範囲】

### 【請求項1】

接地導体面と、

前記接地導体面上に設けられた誘電体基板と、

前記誘電体基板上に設けられた第1の配線及び第2の配線と、

前記誘電体基板上に設けられトランジスタを搭載した第1のチップと

を含み、前記第1の配線に前記トランジスタのソースが接続され前記第2の配線に前記トランジスタのドレインが接続され、前記接地導体面は前記トランジスタの前記ソース及び前記ドレインに<u>前記誘電体基板を介して</u>最も近い接地電位面であることを特徴とする電子回路。

#### 【請求項2】

前記接地導体面上に設けられトランジスタを搭載した第2のチップを更に含み、前記第2のチップのトランジスタのソースは前記接地導体面に接地されていることを特徴とする請求項1記載の電子回路。

#### 【請求項3】

前記第1のチップと前記第2のチップとは略同一の厚さの基板を有することを特徴とする請求項2記載の電子回路。

#### 【請求項4】

前記第1のチップは、前記誘電体基板の上面に設けられた金属パターンの上に設けられていることを特徴とする請求項1乃至3何れか一項記載の電子回路。

#### 【請求項5】

前記第1のチップの基板の厚みが200μm以下であることを特徴とする請求項1乃至 4何れか一項記載の電子回路。

#### 【請求項6】

前記誘電体基板の厚みが前記第1の配線及び前記第2の配線を伝搬する信号の波長の1/10以下であることを特徴とする請求項1乃至4何れか一項記載の電子回路。

#### 【請求項7】

第1の増幅器と、

前記第1の増幅器により増幅された信号を通過又は遮断する第1のスイッチと、

前記第1のスイッチを通過した信号を送信するアンテナと、

前記アンテナにより受信された信号を通過又は遮断する第2のスイッチと、

前記第2のスイッチを通過した信号を増幅する第2の増幅器と

を含み、前記第1のスイッチ及び前記第2のスイッチの少なくとも一方は、

接地導体面と、

前記接地導体面上に設けられた誘電体基板と、

前記誘電体基板上に設けられた第1の配線及び第2の配線と、

前記誘電体基板上に設けられトランジスタを搭載した第1のチップと

を含み、前記第1の配線に前記トランジスタのソースが接続され前記第2の配線に前記トランジスタのドレインが接続され、前記接地導体面は前記トランジスタの前記ソース及び前記ドレインに<u>前記誘電体基板を介して</u>最も近い接地電位面であることを特徴とする送受信システム。

【発明の詳細な説明】

#### 【技術分野】

[00001]

本願開示は、一般に電子回路に関し、詳しくはトランジスタをスイッチとして用いた電子回路に関する。

### 【背景技術】

[00002]

混成回路技術において、増幅器応用に用いられるトランジスタを搭載した半導体チップは、一般的にその半導体基板の厚さが薄い。増幅器としてトランジスタを用いる場合、ゲートに入力された高周波信号が、トランジスタにより増幅されて、ドレイン側に出力される。ソースは、金のワイヤボンド等を介して、半導体チップの下面側に位置する接地金属面に接地されている。ソースと接地との間に存在する金のワイヤボンドのインダクタンスは、増幅器用のトランジスタの特性劣化を引き起こす。そこでソースと接地との間のインダクタンスをなるべく小さくするために、トランジスタが搭載されている半導体基板の厚みは薄いものとなっている。また増幅器では、発生する熱を逃がすためにも薄い基板が好まれる。基板が薄くなると、ソース対接地容量が大きくなるが、ソースが接地されるためにソース対接地容量の値はトランジスタの動作に影響を与えない。

#### [0003]

しかしながら、上記のトランジスタを、トランジスタのON及びOFFによりドレイン及びソース間の導通及び非導通を制御するスイッチ応用に用いる場合には、半導体基板の薄さが問題となる。半導体基板が薄いと、トランジスタのソース対接地容量及びドレイン対接地容量が大きくなり、これらの対接地容量を介して、ドレイン側に入力された高周波の信号が接地側に漏洩してしまう。その結果、信号電力の通過損が増大してしまう。このように、増幅器応用に一般的に用いられるトランジスタをスイッチ用として用いた場合には、通過損が大きくなってしまうという問題がある。また大電力を扱う場合、その大電力に耐えるためには、大きなサイズ(広いゲート幅)のトランジスタチップを使用することが好ましい。その場合、ソース対接地容量及びドレイン対接地容量が更に大きくなり、通過損が更に大きくなる。

[0004]

10

20

30

40

特許文献1には、小電力のコードレス電話(周波数1.9GHz)を対象として、インダクタを介して接地電位と接続することにより、高周波スイッチにおけるトランジスタの対接地容量の影響を相殺し、通過損を低減する手法が示されている。しかしながら、ゲート幅が大きく対接地容量が大きな大電力用のトランジスタの場合は、インダクタによる相殺が難しく、帯域幅が狭くなってしまう。

#### [0005]

特許文献 2 には、電流量を増加させるために並列接続された複数のパワー半導体素子がヒートシンク上に固着される構造が示される。低周波の大電力スイッチの場合であれば、周波数特性の低下を問題にする必要はなく、ゲート幅の広いトランジスタの下に大きなヒートシンクを用いて放熱の向上を図ることができる。

[0006]

特許文献3には、受動素子において寄生成分を低減する手法として、作成する誘電体基板の誘電率を変化させる手法が開示されている。しかしトランジスタ等の能動素子にこの手法を用いて、トランジスタが構成されている基板自体の材料を変化させたのでは、トランジスタの寄生容量以外の特性(例えば耐電力性能)にも影響を及ぼしてしまう。

【先行技術文献】

【特許文献】

[0007]

【特許文献1】特開平6-152361号公報

【特許文献2】特開平6-310627号公報

【特許文献3】特開2006-196608号公報

【特許文献4】特開昭58-087837号公報

【特許文献 5 】特開昭 5 3 - 0 0 2 0 7 9 号公報

【特許文献 6 】特開昭 6 3 - 1 8 1 3 7 3 号公報

【特許文献7】特開平01-132141号公報

【特許文献8】特開平11-340709号公報

【発明の概要】

【発明が解決しようとする課題】

[0008]

以上を鑑みると、増幅器応用に用いられる薄い半導体基板のトランジスタチップをスイッチとして用いる際に、トランジスタチップの対接地容量を低減し、広帯域に亘って通過損を低減することが望まれる。

【課題を解決するための手段】

[0009]

電子回路は、接地導体面と、前記接地導体面上に設けられた誘電体基板と、前記誘電体基板上に設けられた第1の配線及び第2の配線と、前記誘電体基板上に設けられトランジスタを搭載した第1のチップとを含み、前記第1の配線に前記トランジスタのソースが接続され前記第2の配線に前記トランジスタのドレインが接続され、前記接地導体面は前記トランジスタの前記ソース及び前記ドレインに<u>前記誘電体基板を介して</u>最も近い接地電位面であることを特徴とする。

[0010]

送受信システムは、第1の増幅器と、前記第1の増幅器により増幅された信号を通過又は遮断する第1のスイッチと、前記第1のスイッチを通過した信号を送信するアンテナと、前記アンテナにより受信された信号を通過又は遮断する第2のスイッチと、前記第2のスイッチを通過した信号を増幅する第2の増幅器とを含み、前記第1のスイッチ及び前記第2のスイッチの少なくとも一方は、接地導体面と、前記接地導体面上に設けられた誘電体基板と、前記誘電体基板上に設けられた第1の配線及び第2の配線と、前記誘電体基板上に設けられトランジスタを搭載した第1のチップとを含み、前記第1の配線に前記トランジスタのソースが接続され前記第2の配線に前記トランジスタのドレインが接続され、前記接地導体面は前記トランジスタの前記ソース及び前記ドレインに前記誘電体基板を介

10

20

30

40

して最も近い接地電位面であることを特徴とする。

#### 【発明の効果】

#### [0011]

本願開示の少なくとも1つの実施例によれば、増幅器応用に用いられる薄い半導体基板のトランジスタチップをスイッチとして用いる際に、トランジスタチップの対接地容量を 低減し、広帯域に亘って通過損を低減することができる。

【図面の簡単な説明】

[0012]

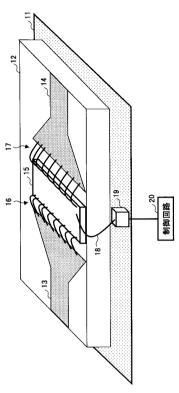

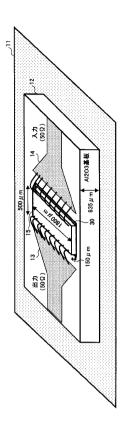

【図1】トランジスタを搭載するチップをスイッチとして用いる電子回路の構成の一例を示す図である。

10

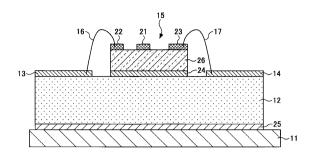

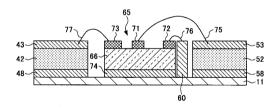

【図2】図1に示す電子回路の断面図である。

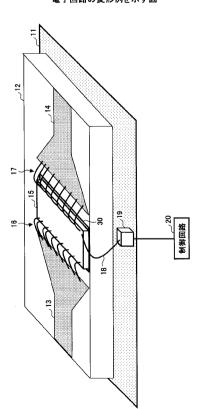

【図3】トランジスタを搭載するチップをスイッチとして用いる電子回路の変形例を示す 図である。

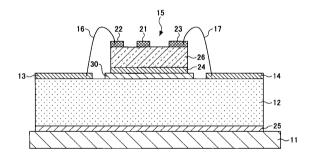

【図4】図3に示す電子回路の断面図である。

【図5】図1の電子回路の模式的なサイズの例を示す図である。

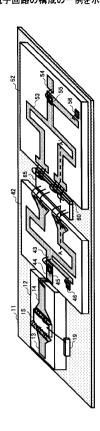

【図 6 】トランジスタを搭載するチップをスイッチ及び増幅器として用いる電子回路の構成の一例を示す図である。

【図7】図6に示す電子回路の断面図である。

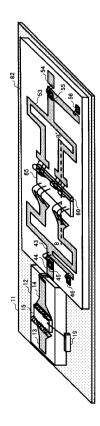

【図8】トランジスタを搭載するチップをスイッチ及び増幅器として用いる電子回路の構成の別の一例を示す図である。

20

30

【図9】図8に示す電子回路の断面図である。

【図10】スイッチ用の電子回路を適用したシステムの一例を示す図である。

【発明を実施するための形態】

[0013]

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

[0014]

図1は、トランジスタを搭載するチップをスイッチとして用いる電子回路の構成の一例を示す図である。図1に示す電子回路は、接地導体面11、誘電体基板12、第1の配線13、第2の配線14、チップ15、ボンディングワイヤ16乃至18、制御バイアス印加回路19、及び制御回路20を含む。接地導体面11上に設けられた誘電体基板12は、裏面(下面)がメタライズ面となっており、接着剤や金錫はんだ等により接地導体面11に接合されている。誘電体基板12上には、第1の配線13及び第2の配線14が、金等の金属導体の配線パターンとして設けられている。また誘電体基板12上には、更に、トランジスタを搭載した半導体装置であるチップ15が設けられる。チップ15は、裏面(下面)がメタライズ面となっており、接着剤により誘電体基板12に接合される。誘電体基板12の材料は、低損失性に優れたAl2O3であってよく、或いは放熱性に優れたAlN等であってもよい。

[0015]

チップ15は、表面(上面)が回路形成面となっており、ドレイン領域、ソース領域、ゲート電極等がチップ15の半導体基板の上面側に形成されている。第1の配線13に、例えば金のボンディングワイヤ16を介してチップ15のトランジスタのソースが接続され、第2の配線14に、例えば金のボンディングワイヤ17を介してチップ15のトランジスタのドレインが電気的に接続される。

[0016]

接地導体面11は、第1の配線13及び第2の配線14の線路に対して接地側の線路として機能する。これにより、接地導体面11及び第1の配線13、又は、接地導体面11及び第2の配線14により、高周波信号を伝送するための伝送線路を形成する。チップ15のトランジスタのゲートは、例えば金のボンディングワイヤ18を介して、制御バイアス印加回路19に電気的に接続される。制御バイアス印加回路19は、例えば抵抗素子、コンデンサ素子、及びインダクタ素子の少なくとも1つを含む。制御バイアス印加回路1

40

9は、制御回路20に接続されている。制御回路20からの制御信号が、制御バイアス印加回路19を介して、チップ15のトランジスタのゲートに印加される。

#### [0017]

チップ15のトランジスタが制御回路20からの制御信号によりON状態となると、スイッチが導通状態となり、第2の配線14から入力された高周波信号が第1の配線13に伝達される。チップ15のトランジスタが制御回路20からの制御信号によりOFF状態となると、スイッチが非導通状態となり、第2の配線14から入力された高周波信号は第1の配線13に伝達されない。

#### [0018]

チップ15は、増幅器応用を想定して製造されたチップであってよい。前述のように、増幅器用のチップは、ソースと接地との間のインダクタンスをなるべく小さくするため、更には発生する熱を逃がすために、半導体基板の厚みが薄いものとなっている。この結果、半導体基板の裏面(下面)の直ぐ下に接地導体面が配置されてしまうと、ソース対接地容量及びドレイン対接地容量が大きい値となってしまう。更には、大電力を扱う場合、大きなサイズ(広いゲート幅)のトランジスタを使用するので、ソース対接地容量及びドレイン対接地容量が更に大きい値となってしまう。図1に示す電子回路の構成では、チップ15の回路形成面とは反対側の面である裏面の直ぐ下には、誘電体基板12が設けられ、その下に接地導体面11が配置される。この構成では、トランジスタのソースと接地導体面11とが、誘電体基板12を間に挟んで接地容量を形成する。またトランジスタのドレインと接地導体面11とが、誘電体基板12を間に挟んで接地容量を形成する。即ち、トランジスタのソース及びドレインに最も近い接地電位面は、トランジスタが設けられる誘電体基板12の面(上面)とは反対側の面(下面)に設けられる接地導体面11である。

## [0019]

従って、トランジスタのソースと接地との間の距離、並びに、トランジスタのドレインと接地との間の距離が開き、チップ15の裏面(下面)の直ぐ下に接地導体面を配置した場合と比較して、対接地容量を実効的に低減することができる。従って、スイッチ用に新規にトランジスタチップを開発することなく、大電力の増幅器用のトランジスタチップを流用して、低損失大電力スイッチを実現することができる。これにより、回路の低コスト化をはかることができる。

## [0020]

図2は、図1に示す電子回路の断面図である。図2において、図1と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。誘電体基板12の裏面(下面)にはメタライズ部25が設けられており、このメタライズ部25が、接着剤又は金錫はんだ等により接地導体面11に固着される。チップ15の半導体基板26の裏面(下面)にはメタライズ部24が設けられており、このメタライズ部24が、接着剤により誘電体基板12に固着される。チップ15の半導体基板26の上面(回路形成面)には、ゲート電極21、ソース電極22、及びドレイン電極23が設けられている。ソース電極22は、ボンディングワイヤ16を介して第1の配線13に電気的に接続される。ドレイン電極23は、ボンディングワイヤ17を介して第2の配線14に電気的に接続される。図2から分かるように、ソース電極22と接地導体面11との距離、並びに、ドレイン電極23と接地導体面11との距離は、誘電体基板12を設けることによりその分増大し、対接地容量が小さくなる。

#### [0021]

図3は、トランジスタを搭載するチップをスイッチとして用いる電子回路の変形例を示す図である。図3において図1と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。図3に示す電子回路は、図1に示す電子回路と比較して、誘電体基板12の上面のチップ15を設ける領域に例えば金等の金属パターン30を形成してある点が異なる。この金属パターン30はチップ15の大きさと同程度以上の大きさであり、この金属パターン30の上に、金錫はんだ等を用いてチップ15が固着される。図1の構成のようにチップ15を接着剤で固定した場合に比較して、チップ15がより強固に固着してはがれ

10

20

30

40

にくくなる。

#### [0022]

図4は、図3に示す電子回路の断面図である。図4において、図3と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。誘電体基板12の上面には、金属パターン30が設けられている。チップ15の半導体基板26の裏面(下面)に設けられたメタライズ部24が、金錫はんだ等により金属パターン30に固着されている。

#### [0023]

図5は、図1の電子回路の模式的なサイズの例を示す図である。図5において、図1と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。チップ15の大きさは、例えば長さ1800μm、幅500μm、厚さ150μmである。チップ150太増幅器用のトランジスタチップであり、厚さは200μm以下であることが好ましい。金属パターン30は、チップ15よりも若干大きい。第1の配線13及び第2の配線14は、一定幅を有する線路部分と、この幅から最大幅が例えばトランジスタチップ15の長さ1800μmと同程度以上にまで広がる接続部とを含む。一定幅を有する線路部分と接地導立スタチップ15の長さ1800μmと同程度以上にまで広がる接続部の長さは例えばトランジスタが0N状態でスイッチが導通となるときに通過損が少なくなるような長さである。誘電体基板12は、厚さが例えば635μmであり、その材質はA1203であり、非誘電率は9.8である。誘電体基板1200厚さは、第1の配線13及び第2の配線14を伝搬する信号の波長の1/10以下であることが好ましい。

#### [0024]

図6は、トランジスタを搭載するチップをスイッチ及び増幅器として用いる電子回路の構成の一例を示す図である。図6において、図1と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。図6の左側に示すように、接地導体面11上には誘電体基板12が設けられ、その誘電体基板12の上には第1のチップ15、第1の配線13、及び第2の配線14が設けられている。この回路部分はスイッチとして機能する部分であり、図1に示す電子回路に相当する。

#### [0025]

図6の中央に示されるように、接地導体面11上には更に誘電体基板42が設けられる。また図6の右側に示されるように、接地導体面11上には更に誘電体基板52が設けられる。誘電体基板42上には、導体の配線パターン43及び44、チップ素子45及び46が設けられる。また誘電体基板52上には、導体の配線パターン53及び54、チップ素子55及び56が設けられる。誘電体基板42と誘電体基板52との間には、トランジスタを搭載した第2のチップ65が接地導体面11に設けられている。この第2のチップ65は、第1のチップ15のように誘電体基板の上に設けられるのではなく、接地導体面11の上面に誘電体基板を介することなく直接に設けられる。

## [0026]

第2のチップ65のトランジスタは、増幅器として用いられる。即ち、第2のチップ65のトランジスタのソースは接地導体面11に接地されている。具体的には、接地導体面11に固着されて電気的に接続された金属ブロック60に、第2のチップ65のトランジスタのソース電極が、ボンディングワイヤを介して電気的に接続される。また第2のチップ65のトランジスタのドレインは、誘電体基板42上に設けられた配線パターン43にボンディングワイヤを介して電気的に接続される。更に第2のチップ65のトランジスタのゲートは、誘電体基板52上に設けられた配線パターン53にボンディングワイヤを介して電気的に接続される。

## [0027]

配線パターン54は、高周波の入力信号を外部から印加するための配線である。配線パターン54は、ボンディングワイヤを介してチップ素子55に接続され、このチップ素子55が配線パターン53に接続される。チップ素子55は、例えば抵抗、コンデンサ、及びインダクタの少なくとも1つを含み、単独で或いは配線パターン53と共に、外部から

10

20

30

40

の入力信号を整合させるための整合回路として機能する。これにより、配線パターン54からの入力信号が、配線パターン53を介して、第2のチップ65のトランジスタのゲートに印加される。チップ素子56は外部の入力側バイアス電源に電気的に接続される。チップ素子56は、例えば抵抗、コンデンサ、及びインダクタの少なくとも1つを含み、単独で或いは配線パターン53と共に入力側バイアス回路として機能する。これにより、チップ素子56を介して印加される入力側バイアス電圧が、配線パターン53を介して、第2のチップ65のトランジスタのゲートに印加される。配線パターン53は途中で2つの線路に分かれており、電力分配回路として機能する。第2のチップ65には複数のトランジスタが設けられており、配線パターン53により分配された電力は、複数のトランジスタのそれぞれに並列に印加される。

### [0028]

第2のチップ65の複数のトランジスタにより増幅された信号は、誘電体基板42上に 設けられた配線パターン43にボンディングワイヤを介して伝達される。配線パターン4 3は、2つの線路が合流する形となっており、電力合成回路として機能する。この電力合 成回路として機能する配線パターン43により、複数のトランジスタのそれぞれにより並 列に増幅された信号が1つの信号に合成される。配線パターン43は、ボンディングワイ ヤを介してチップ素子45に接続され、このチップ素子45が配線パターン44に接続さ れる。配線パターン44は、誘電体基板12上に設けられた第2の配線14にボンディン グワイヤを介して電気的に接続される。チップ素子45は、例えば抵抗、コンデンサ、及 びインダクタの少なくとも1つを含み、単独で或いは配線パターン43及び44と共に、 信号を整合させるための整合回路として機能する。これにより、第2のチップ65のトラ ンジスタにより増幅された信号が、配線パターン43、チップ素子45、及び配線パター ン44を介して第2の配線14に伝達される。配線パターン43はまた、ボンディングワ イヤを介してチップ素子46に電気的に接続される。このチップ素子46は、外部の出力 側バイアス電源に電気的に接続される。チップ素子46は、例えば抵抗、コンデンサ、及 びインダクタの少なくとも1つを含み、単独で或いは配線パターン43と共に出力側バイ アス回路として機能する。これにより、チップ素子46を介して印加される出力側バイア ス電圧が、配線パターン43を介して、第2のチップ65のトランジスタのドレインに印 加される。

## [0029]

上記のようにして、第2の配線14には、第2のチップ65のトランジスタにより増幅された信号が印加される。この第2の配線14は、第1のチップ15にボンディングワイヤを介して接続され、この第1のチップ15が、第1の配線13にボンディングワイヤを介して電気的に接続される。チップ15のトランジスタが制御回路からの制御信号によりON状態となると、スイッチが導通状態となり、第2の配線14に印加された増幅後の高周波信号が第1の配線13に伝達される。チップ15のトランジスタが制御回路からの制御信号によりOFF状態となると、スイッチが非導通状態となり、第2の配線14に印加された増幅後の高周波信号は第1の配線13に伝達されない。

### [0030]

第1のチップ15と第2のチップ65とは、略同一の厚さの基板を有するものであってよい。この第1のチップ15と第2のチップ65とは、増幅器応用を想定して製造されたチップであってよい。前述のように、増幅器用のチップは、ソースと接地との間のインダクタンスをなるべく小さくするため、更には発生する熱を逃がすために、半導体基板の厚みが薄いものとなっている。第2のチップ65は、接地導体面11の上面に直接に接合されているので、半導体基板の薄さのためにソースと接地との間のインダクタンスは無視できるものとなり、増幅器用のトランジスタの特性劣化は生じない。また第1のチップ15は、接地導体面11の上面に直接に接合されるのではなく、接地導体面11上に設けられた誘電体基板12の上に設けられている。従って、トランジスタのソースと接地との間の距離が開き、第1のチップ15の裏面(下面)の直ぐ下に接地導体面を配置した場合と比較して、対接地容量を実効的に低

10

20

30

40

10

20

30

40

50

減することができる。なお第1のチップ15は、増幅器用の第2のチップ65と同一の品種のトランジスタチップ、又は類似の品種のトランジスタチップであってよい。従って、スイッチ用に新規にトランジスタチップを開発することなく、大電力の増幅器用のトランジスタチップを流用して、低損失大電力スイッチを実現することができる。これにより、回路の低コスト化をはかることができる。

#### [0031]

なお誘電体基板 4 2 及び誘電体基板 5 2 は、誘電体基板 1 2 と比較して薄いものであってよい。誘電体基板 4 2 及び誘電体基板 5 2 は、誘電体基板 4 2 上の配線パターン 4 3 や誘電体基板 5 2 上の配線パターン 5 3 等が、高周波信号に対して適切な伝送線路となるような厚みであってよい。誘電体基板 1 2 は、第 1 のチップ 1 5 の対接地容量を小さくするために所定の厚み以上のものであることが望ましいが、誘電体基板 4 2 及び誘電体基板 5 2 については、特に厚くすることに対する要求はない。

#### [0032]

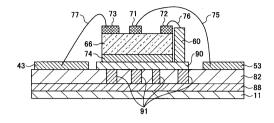

図7は、図6に示す電子回路の断面図である。図7において、図6と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。図7に示すのは、図6に示す電子回路のうち、第2のチップ65及びその周辺部分の線A-A'に沿った断面図である。なお誘電体基板12及びその上に搭載された第1のチップ15の部分の断面図は、図2に示すものと同様である。

#### [0033]

図7において、誘電体基板42の裏面(下面)にはメタライズ部48が設けられており、このメタライズ部48が、接着剤又は金錫はんだ等により接地導体面11に固着される。同様に、誘電体基板52の裏面(下面)にはメタライズ部58が設けられており、このメタライズ部58が、接着剤又は金錫はんだ等により接地導体面11に固着される。第2のチップ65の半導体基板66の裏面(下面)にはメタライズ部74が設けられており、このメタライズ部74が、接着剤又は金錫はんだ等により接地導体面11に固着される。第2のチップ65の半導体基板66の上面(回路形成面)には、ゲート電極71、ソース電極72、及びドレイン電極73が設けられている。ソース電極72は、ボンディングワイヤ76及び金属ブロック60を介して接地導体面11に電気的に接続される(接地される)。ドレイン電極73は、ボンディングワイヤ77を介して、誘電体基板42上の配線パターン43に電気的に接続される。

## [0034]

図8は、トランジスタを搭載するチップをスイッチ及び増幅器として用いる電子回路の構成の別の一例を示す図である。図8において、図1と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。図8の左側に示すように、接地導体面11上には誘電体基板12が設けられ、その誘電体基板12の上には第1のチップ15、第1の配線13、及び第2の配線14が設けられている。この回路部分はスイッチとして機能する部分であり、図1に示す電子回路に相当する。

#### [0035]

図8の中央から右に示されるように、接地導体面11上には更に誘電体基板82が設けられる。誘電体基板82上には、導体の配線パターン43及び44、チップ素子45及び46、導体の配線パターン53及び54、チップ素子55及び56、トランジスタを搭載した第2のチップ65、及び金属ブロック60が設けられる。第2のチップ65及び金属ブロック60が設けられる。第2のチップ65及び金属プロック60が設けられる位置において、誘電体基板82には例えば金属ビアホールが設けられてよい。この金属ビアホールを介して、第2のチップ65の下面のメタライズ部が接地導体面11に電気的に接続される(接地される)。図6の場合と同様に、第2のチップ65のトランジスタのソースは接地導体面11に接地されている。具体的には、接地導体面11に上記金属ビアホールを介して電気的に接続された金属ブロック60に、第2のチップ65のトランジスタのソース電極が、ボンディングワイヤを介して電気的に接続される。第2のチッ

プ65及び金属ブロック60以外の回路要素、即ち導体の配線パターン43及び44、チップ素子45及び46、導体の配線パターン53及び54、並びにチップ素子55及び56の構成及び機能は、図6において説明したものと同様である。

#### [0036]

第1のチップ15と第2のチップ65とは、略同一の厚さの基板を有するものであってよい。この第1のチップ15と第2のチップ65とは、増幅器応用を想定して製造されたチップであってよい。前述のように、増幅器用のチップは、ソースと接地との間のインダクタンスをなるべく小さくするため、更には発生する熱を逃がすために、半導体基板の厚みが薄いものとなっている。第2のチップ65の裏面(下面)のメタライズ部は、金属ビアホールを介して接地導体面11に電気的に接続され接地電位となっている。従って、半導体基板の薄さのためにソースと接地との間のインダクタンスは無視できるものとなり、増幅器用のトランジスタの特性劣化は生じない。

#### [0037]

誘電体基板 8 2 は、誘電体基板 1 2 と比較して薄いものであってよい。誘電体基板 8 2 は、誘電体基板 8 2 上の配線パターン 4 3 や配線パターン 5 3 等が、高周波信号に対して適切な伝送線路となるような厚みであってよい。誘電体基板 1 2 は、第 1 のチップ 1 5 の対接地容量を小さくするために所定の厚み以上のものであることが望ましいが、誘電体基板 8 2 については、特に厚くすることに対する要求はない。

#### [0038]

図9は、図8に示す電子回路の断面図である。図9において、図7及び8と同一の構成要素は同一の番号で参照し、その説明は適宜省略する。図9に示すのは、図8に示す電子回路のうち、第2のチップ65及びその周辺部分の線B-B'に沿った断面図である。なお誘電体基板12及びその上に搭載された第1のチップ15の部分の断面図は、図2に示すものと同様である。

#### [0039]

図9において、誘電体基板82の裏面(下面)にはメタライズ部88が設けられており、このメタライズ部88が、接着剤又は金錫はんだ等により接地導体面11に固着される。第2のチップ65の半導体基板66の裏面(下面)にはメタライズ部74が設けられており、このメタライズ部74が、誘電体基板82上に設けられたメタライズ部90に接着剤又は金錫はんだ等により固着される。また金属ブロック60が、メタライズ部90に接着剤又は金錫はんだ等により固着される。メタライズ部90は、誘電体基板82を貫通して設けられた金属ビアホール91及びメタライズ部88を介して、接地導体面11に電気的に接続される。なお金属ビアホール91を、メタライズ部90を介することなく直接にメタライズ部74及び金属ブロック60に接続してもよい。この場合、メタライズ部90は不要となる。

#### [0040]

第2のチップ65の半導体基板66の上面(回路形成面)には、ゲート電極71、ソース電極72、及びドレイン電極73が設けられている。ソース電極72は、ボンディングワイヤ76を介して金属ブロック60に電気的に接続される(接地される)。ドレイン電極73は、ボンディングワイヤ77を介して、誘電体基板82上の配線パターン43に電気的に接続される。ゲート電極71は、ボンディングワイヤ75を介して、誘電体基板82上の配線パターン53に電気的に接続される。

#### [0041]

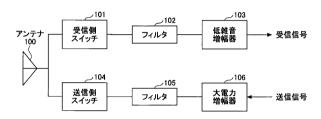

図10は、図1や図3に示したスイッチ用の電子回路を適用したシステムの一例を示す 図である。図10に示すシステムは、レーダー用の送受信システムを想定している。この 送受信システムは、アンテナ100、受信側スイッチ101、フィルタ102、低雑音増 幅器103、送信側スイッチ104、フィルタ105、及び大電力増幅器106を含む。 受信側スイッチ101及び送信側スイッチ104に、図1や図3に示したスイッチ用の電 子回路を用いてよい。

### [0042]

50

10

20

30

レーダー波の送信時には、受信側スイッチ101をOFFにして、送信側スイッチ104をONにする。内部回路から供給された送信信号が、大電力増幅器106により大電力の信号に増幅され、その後、フィルタ105によりフィルタリング処理される。増幅され更にフィルタリング処理された後の大電力信号は、送信側スイッチ104を介してアンテナ100から送信される。

#### [0043]

レーダー波の受信時には、受信側スイッチ101をONにして、送信側スイッチ104をOFFにする。アンテナ100により受信された受信信号は、受信側スイッチ101を介してフィルタ102に印加される。フィルタ102によりフィルタリング処理された後の受信信号は、低雑音増幅器103により増幅され、増幅後の受信信号として内部回路に供給される。

[0044]

このように、大電力増幅器 1 0 6 により増幅された信号を通過又は遮断する送信側スイッチ 1 0 4 と、送信側スイッチ 1 0 4 を通過した信号を送信するアンテナ 1 0 0 とを設ける。また更に、アンテナ 1 0 0 により受信された信号を通過又は遮断する受信側スイッチ 1 0 1 と、受信側スイッチ 1 0 1 を通過した信号を増幅する低雑音増幅器 1 0 3 とを設ける。そして、受信側スイッチ 1 0 1 及び送信側スイッチ 1 0 4 の少なくとも一方は、図 1 や図 3 に示したスイッチ 用の電子回路を用いる。この構成では、スイッチ用に新規にトランジスタチップを開発することなく、大電力の増幅器用のトランジスタチップを流用することができる。これにより、回路の低コスト化をはかることができる。

[0045]

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

【符号の説明】

#### [0046]

- 11 接地導体面

- 12 誘電体基板

- 13 第1の配線

- 14 第2の配線

- 15 チップ

- 16~18 ボンディングワイヤ

- 19 制御バイアス印加回路

- 20制御回路

10

20

# 【図1】

トランジスタを搭載するチップをスイッチとして用いる 電子回路の構成の一例を示す図

【図3】

トランジスタを搭載するチップをスイッチとして用いる 電子回路の変形例を示す図

## 【図2】

図1に示す電子回路の断面図

【図4】

図3に示す電子回路の断面図

# 【図5】

図1の電子回路の模式的なサイズの例を示す図

## 【図7】

図6に示す電子回路の断面図

# 【図6】

トランジスタを搭載するチップをスイッチ及び増幅器として用いる 電子回路の構成の一例を示す図

【図8】

トランジスタを搭載するチップをスイッチ及び増幅器として用いる 電子回路の構成の別の一例を示す図

# 【図9】

図8に示す電子回路の断面図

# 【図10】

## スイッチ用の電子回路を適用したシステムの一例を示す図

## フロントページの続き

## 審査官 米倉 秀明

## (56)参考文献 特開2002-208848(JP,A)

特開2009-159059(JP,A)

実開平06-085501(JP,U)

特開2001-177359(JP,A)

特開2003-110302(JP,A)

西嶋将明、藤本裕雅、石川修,マルチチップGaAs増幅器の試作,1992年電子情報通信学会秋季大会,日本,電子情報通信学会,1992年 9月15日,2-390

## (58)調査した分野(Int.CI., DB名)

H01P 1/15

H01L 23/12

H 0 4 B 1 / 4 4

H 0 5 K 1 / 0 2