(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5833961号 (P5833961)

(45) 発行日 平成27年12月16日(2015.12.16)

(24) 登録日 平成27年11月6日(2015.11.6)

(51) Int. Cl. FL

HO4N 19/593 (2014.01)HO4N 19/593 HO4N 19/42 (2014.01)HO4N 19/42 HO4N 1/413 (2006.01) HO4N 1/413

D

請求項の数 6 (全 14 頁)

(21) 出願番号 特願2012-68124 (P2012-68124) (22) 出願日 平成24年3月23日 (2012.3.23) (65) 公開番号 特開2013-201562 (P2013-201562A) (43) 公開日 平成25年10月3日(2013.10.3) 平成26年2月6日(2014.2.6) 審查請求日

||(73)特許権者 000003078 株式会社東芝

東京都港区芝浦一丁目1番1号

|(74)代理人 | 100111121

弁理士 原 拓実

(74)代理人 100142088

弁理士 野木 新治

(74)代理人 100200104

弁理士 渡邊 実

||(74)代理人 100176599

弁理士 高橋 拓也

|(74)代理人 100122220

弁理士 黒田 久美子

|(74)代理人 100138807

弁理士 大西 邦幸

最終頁に続く

(54) 【発明の名称】画像圧縮装置、画像処理システム、及び画像圧縮方法

## (57)【特許請求の範囲】

# 【請求項1】

前置審查

ベイヤーパターンに従って配列された、少なくとも3種類の色成分を有する画像データ から、前記画像データの第1ライン及び第2ライン上に含まれる第1色成分に対応する第 1 画素と、前記第1ライン上に含まれる第2色成分に対応する第2画素と、前記第2ライ ンに含まれる第3色成分に対応する第3画素と、を抽出する画像データ制御部と、

前記画像データにおいて、符号化すべきターゲット第1画素に対してカラム方向に最近 接する参照第1画素を参照して、前記ターゲット第1画素を符号化することにより、第1 符号化画素を生成する第1符号化部と、

前記画像データにおいて、符号化すべきターゲット第2画素に対してライン方向に最近 接する参照第2画素を参照して、前記ターゲット第2画素を符号化することにより、第2 符号化画素を生成する第2符号化部と、

前記画像データにおいて、符号化すべきターゲット第3画素に対してライン方向に最近 接する参照第3画素を参照して、前記ターゲット第3画素を符号化することにより、第3 符号化画素を生成する第3符号化部と、

前記第1符号化画素と、前記第2符号化画素と、前記第3符号化画素と、を合成するこ とにより、符号化データを生成する符号化データ生成部と、を備え、

前記画像データ制御部は、

前記第1ライン及び前記第2ライン上に含まれる前記第1画素乃至第3画素を2ライン 1カラム毎に前記第1符号化部乃至第3符号化部へ供給することを特徴とする画像圧縮装

20

# 【請求項2】

前記画像データ制御部は、

前記画像データをライン単位で記憶するラインメモリと、

前記ラインメモリに記憶された前記画像データを、前記第1符号化部乃至第3符号化部 へ供給するメモリ制御部と、を備える、請求項1に記載の画像圧縮装置。

(2)

#### 【請求項3】

前記メモリ制御部は、前記第1画素及び前記第3画素のセットと、前記第1画素及び前記第2画素のセットと、を前記ラインメモリから読み出す、請求項1又は2に記載の画像 圧縮装置。

【請求項4】

前記第1画素が、毎サイクル連続して前記第1符号化部へ供給され、前記第2画素が、2サイクル毎に前記第2符号化部へ供給され、前記第3画素が、2サイクル前に、且つ、前記第2画素が供給されないサイクルに、前記第3符号化部へ供給されるように、前記画像データの配列を並べ替える並べ替え部を備える、請求項1乃至3の何れかに記載の画像圧縮装置。

## 【請求項5】

前記第1画素と、前記第2画素と、前記第3画素と、に基づいて、前記第1符号化部、前記第2符号化部、及び前記第3符号化部の符号量を制御する、符号量制御部をさらに備える、請求項1乃至4の何れかに記載の画像圧縮装置。

【請求項6】

前記符号量制御部は、

前記第1画素に対して複数の符号量を用いた符号化処理を適用することにより、第1サンプルデータを生成する第1サンプル生成部と、

前記第2画素に対して複数の符号量を用いた符号化処理を適用することにより、第2サンプルデータを生成する第2サンプル生成部と、

前記第3画素に対して複数の符号量を用いた符号化処理を適用することにより、第3サンプルデータを生成する第3サンプル生成部と、

前記第1サンプルデータ、前記第2サンプルデータ、及び前記第3サンプルデータに基づいて、最適符号量を選択し、前記最適符号量を、前記第1符号化部と、前記第2符号化部と、前記第3符号化部とへ供給する、符号量選択部と、を備える、請求項5に記載の画像圧縮装置。

【発明の詳細な説明】

【技術分野】

[ 0 0 0 1 ]

本発明の実施形態は、画像圧縮装置、画像処理システム、及び画像圧縮方法に関する。

【背景技術】

[0002]

従来、画像の符号化方法としては、予測画素を計算し、計算により得られた予測画素を量子化し、量子化により得られた量子化データを符号化する方法が知られている。予測画素の計算方法としては、SMIA(Standard Mobile Imaging Architecture)で、ベイヤーパターンに従って配列されたRGBデータに対して、色成分毎に、水平方向に近接する複数の参照画素を用いる方法が知られている。ベイヤーパターンでは、色成分が、水平方向に1画素間隔で配列されている。即ち、予測画素は、予測の対象となる原画素と、原画素から水平方向に2画素分離れた参照画素と、を用いて計算される。

[0003]

しかしながら、原画素と予測画素との間の差分値は、参照画素と予測対象画素の距離に応じて、大きくなる。また、差分値が大きくなるほど、量子化誤差も大きくなる。即ち、 従来の符号化方法の量子化誤差は、2画素分の距離に相当する。 10

20

30

40

#### [0004]

一般に、量子化誤差が大きくなるほど、符号化における信号雑音比(以下「SN比」という)が低下する。SN比の低下は、符号化データを復号して得られる復号データ(即ち、画像データ)を再生したときの画質に悪影響を及ぼす。

## [0005]

また、ベイヤーパターンでは、水平方向については、画素間の感度差はないが、垂直方向については、画素間の感度差がある。従って、垂直方向の間隔が1画素以下であったとしても、垂直方向に最も近い位置の元画素に基づいて予測画素を計算すると、符号化処理の際にSN比が低下する。

【先行技術文献】

10

20

30

40

【特許文献】

[0006]

【特許文献 1 】特開 2 0 0 5 - 1 9 1 9 3 9 号公報

【発明の概要】

【発明が解決しようとする課題】

[0007]

本発明が解決しようとする課題は、符号化処理の際のSN比の低下を防ぐことである。

【課題を解決するための手段】

[0008]

本発明の実施形態の画像圧縮装置は、画像データ制御部と、第1符号化部と、第2符号 化部と、第3符号化部と、符号化データ生成部と、を備える。画像データ制御部は、ベイ ヤーパターンに従って配列された、少なくとも3種類の色成分を有する画像データから、 前記画像データの第1ライン及び第2ライン上に含まれる第1色成分に対応する第1画素 と、前記第1ライン上に含まれる第2色成分に対応する第2画素と、前記第2ライン上に 含まれる第3色成分に対応する第3画素と、を抽出する。第1符号化部は、前記画像デー タにおいて、符号化すべきターゲット第1画素に対してカラム方向に最近接する参照第1 画素を参照して、前記ターゲット第1画素を符号化することにより、第1符号化画素を生 成する。第2符号化部は、前記画像データにおいて、符号化すべきターゲット第2画素に 対してライン方向に最近接する参照第2画素を参照して、前記ターゲット第2画素を符号 化することにより、第2符号化画素を生成する。第3符号化部は、前記画像データにおい て、符号化すべきターゲット第3画素に対してライン方向に最近接する参照第3画素を参 照して、前記ターゲット第3画素を符号化することにより、第3符号化画素を生成する。 符号化データ生成部は、前記第1符号化画素と、前記第2符号化画素と、前記第3符号化 画素と、を合成することにより、符号化データを生成する。さらに画像データ制御部は、 前記第1ライン及び前記第2ライン上に含まれる前記第1画素乃至第3画素を2ライン 1カラム毎に前記第1符号化部乃至第3符号化部へ供給する。

【図面の簡単な説明】

[0009]

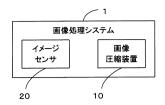

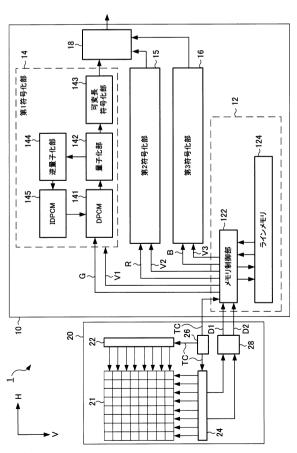

- 【図1】本実施形態の画像処理システム1のブロック図。

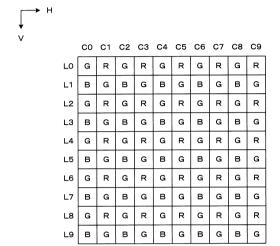

- 【図2】本実施形態の画像データの概略図。

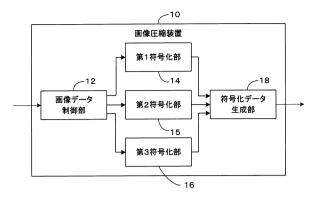

- 【図3】第1実施形態の画像圧縮装置10のブロック図。

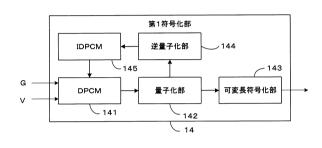

- 【図4】第1実施形態の第1符号化部14のブロック図。

- 【図5】第1実施形態の画像処理システム1のブロック図。

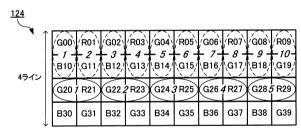

- 【図6】第1実施形態のメモリ制御部122及びラインメモリ124の動作の説明図。

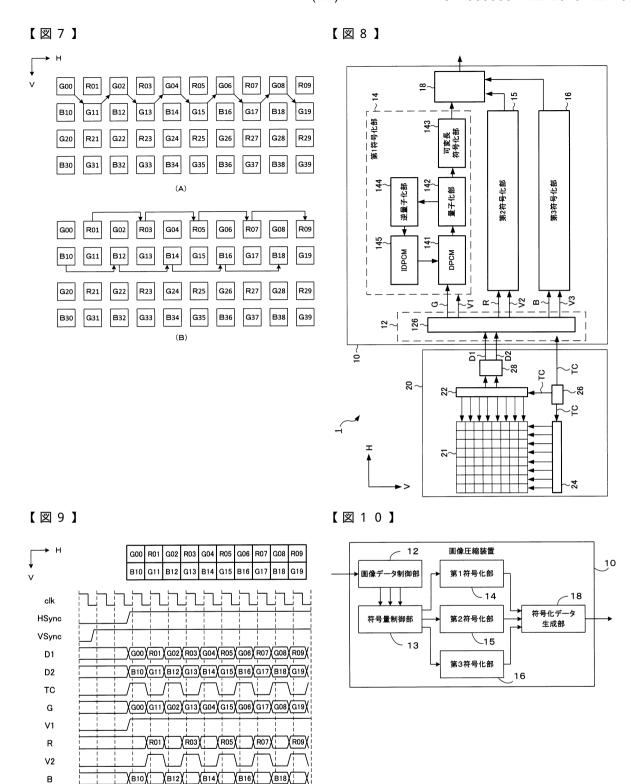

- 【図7】第1実施形態のDPCM141及びIDPCM142の動作の説明図。

- 【図8】第2実施形態の画像処理システム1のブロック図。

- 【図9】第2実施形態の並べ替え部126の動作の説明図。

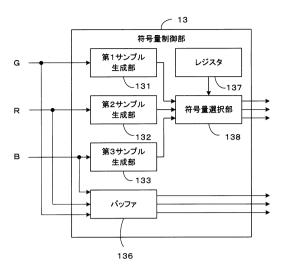

- 【図10】第3実施形態の画像圧縮装置10のブロック図。

- 【図11】第3実施形態の符号量制御部13のブロック図。

【発明を実施するための形態】

#### [0010]

本実施形態について、図面を参照して説明する。はじめに、本実施形態の画像処理システム1の構成について説明する。図1は、本実施形態の画像処理システム1のブロック図である。画像処理システム1は、画像圧縮装置10と、イメージセンサ20と、を備える。イメージセンサ20は、画像データ(例えば、RGBデータ)を生成するモジュール(例えば、CMOS(Complementary Metal Oxide Semiconductor)センサ)である。画像圧縮装置10は、イメージセンサ20が生成した画像データを圧縮する。

## [0011]

本実施形態の画像データについて説明する。図 2 は、本実施形態の画像データの概略図である。図 2 は、ライン方向(H方向)に 1 0 カラム(C 0 ~ C 9)、且つ、カラム方向(V 方向)に 1 0 ライン(L 0 ~ L 9)のマトリクスに、ベイヤーパターンに従って配列された 1 0 0 画素を示している。画像データは、 3 種類の色成分(第 1 ~ 第 3 色成分)に対応する画素(第 1 画素 G、第 2 画素 R、及び第 3 画素 B)を含む。例えば、画像データは、 B a y e r R A W データである。

#### [0012]

第1画素 G は、全ラインLn{n:0~9}及び全カラムCm{m:0~9}上に現れる画素である。第1画素 G は、H方向及びV方向に、1画素間隔で配列されている。即ち、H方向及びV方向において第1画素 G (Ln,Cm)に近接する第1画素は、H方向及びV方向に1画素分離れた第1画素 G (L(n+1),C(m+1))である。例えば、H方向及びV方向において第1画素 G (L0,C0)に近接する第1画素は、第1画素 G (L1,C1)である。

## [0013]

第2画素 R は、偶数 ライン L (2 j) { j: 0 ~ 4 } 及び 奇数 カラム C (2 i + 1 ) { i: 0 ~ 4 } 上に現れる 画素である。第2 画素 R は、H 方向及 び V 方向に、1 画素 間隔で配列 されている。即ち、H 方向及 び V 方向において 第2 画素 R (L (2 j), C (2 i + 1)) に近接する 第2 画素 は、H 方向に 2 画素 分離れた 第2 画素 R (L (2 j), C (2 i + 1)) である。例えば、H 方向及 び V 方向において 第2 画素 R (L 0, C 1) に近接する 第2 画素 は、第2 画素 R (L 0, C 3) 及 び R (L 2, C 1) である。

#### [0014]

第3画素 B は、奇数 ライン L (2 j + 1) 及び偶数 カラム C (2 i ) 上に現れる画素である。第3 画素 B は、H 方向及び V 方向に、1 画素間隔で配列されている。即ち、H 方向及び V 方向において第3 画素 B (L (2 j + 1), C (2 i )) に近接する第3 画素は、H 方向に2 画素分離れた第3 画素 B (L (2 j + 1), C (2 i + 2)) 及び V 方向に2 画素分離れた第3 画素 B (L (2 j + 3), C (2 i )) である。例えば、H 方向及び V 方向において第3 画素 B (L 1, C 0) に近接する第3 画素は、第3 画素 B (L 1, C 2) 及び B (L 3, C 0) である。

# [0015]

#### (第1実施形態)

第1実施形態は、ラインメモリを用いて量子化誤差を低減する、画像圧縮装置10の例である。図3は、第1実施形態の画像圧縮装置10のブロック図である。画像圧縮装置10は、画像データ制御部12と、第1~第3符号化部14~16と、符号化データ生成部18と、を備える。

# [0016]

画像データ制御部12は、第1~第3符号化部14~16へ供給すべきデータを制御する。具体的には、画像データ制御部12は、イメージセンサ20から画像データを取得し、当該画像データから、第1画素Gと、第2画素Rと、第3画素Bと、を抽出し、第1画素Gを第1符号化部14へ供給し、第2画素Rを第2符号化部15へ供給し、第3画素Bを第3符号化部16へ供給する。

10

20

30

#### [0017]

第1符号化部14は、全ライン(即ち、偶数ライン及び奇数ライン)上に含まれる画素に対して、符号化処理を適用する。具体的には、第1符号化部14は、画像データのライン方向及びカラム方向において、符号化すべき第1画素(以下「ターゲット第1画素」という)G を参照して、ターゲット第1画素Gを符号化することにより、第1符号化画素を生成する。

#### [0018]

第2符号化部15は、偶数ライン上に含まれる画素に対して、符号化処理を適用する。 具体的には、第2符号化部15は、画像データのライン方向において、符号化すべき第2 画素(以下「ターゲット第2画素」という)Rに最も近い第2画素(以下「参照第2画素」という)R´を参照して、ターゲット第2画素Rを符号化することにより、第2符号化画素を生成する。

#### [0019]

第3符号化部16は、奇数ライン上に含まれる画素に対して、符号化処理を適用する。 具体的には、第3符号化部16は、画像データのライン方向において、符号化すべき第3 画素(以下「ターゲット第3画素」という)Bに最も近い第3画素(以下「参照第3画素」という)B´を参照して、ターゲット第3画素Bを符号化することにより、第3符号化画素を生成する。

## [0020]

符号化データ生成部 1 8 は、符号化データを生成する。具体的には、符号化データ生成部 1 8 は、第 1 ~ 第 3 符号化画素を合成することにより、符号化データを生成する。符号化データは、画像処理システム 1 の外部に接続されたモジュール ( 例えば、外部メモリ及びデコーダ ) に供給される。

#### [0021]

第1実施形態の第1~第3符号化部14~16の構成について説明する。図4は、第1 実施形態の第1符号化部14のブロック図である。なお、第2及び第3符号化部15及び 16の構成は、第1符号化部14と同様である。

#### [0022]

第1符号化部14は、差分パルス符号変調部(以下「DPCM(Differential Pulse Code Modulatior)」という)141と、量子化部142と、可変長符号化部143と、逆量子化部144と、逆差分パルス符号変調部(以下「IDPCM(Inverse DPCM)」という)145と、を備える。

#### [0023]

DPCM141は、有効信号 V に応じて、IDPCM145からフィードバックされるフィードバック画素と、第1画素 G と、に対してパルス符号変調処理を適用することにより、フィードバック画素と第1画素 G との差分値を示す第1差分信号を生成する。量子化部142は、DPCM141により生成された第1差分信号を量子化することにより、第1量子化信号を生成する。可変長符号化部143は、第1量子化信号に対して可変長符号化処理を適用することにより、第1符号化画素を生成する。逆量子化部144は、第1量子化信号を逆量子化することにより、第1差分信号を生成する。IDPCM145は、逆量子化部144により生成された第1差分信号に対して逆パルス符号変調処理を適用することにより、フィードバック画素を生成する。

## [0024]

第1実施形態の画像処理システム1の構成について説明する。図5は、第1実施形態の画像処理システム1のブロック図である。イメージセンサ20は、センサコア21と、第1及び第2リードコントローラ22,24と、タイミングジェネレータ26と、アナログデジタル変換器(以下「ADC(Analogue to Digital Converter」という)28と、を備える。画像データ制御部12は、メモリ制御部122と、ラインメモリ124と、を備える。

## [0025]

50

10

20

30

センサコア 2 1 は、レンズ(図示せず)を介して入力された光を、電気信号に変換する。センサコア 2 1 は、ライン方向(H方向)及びカラム方向(V方向)に配列された複数の撮像素子を備える。センサコア 2 1 の出力(電気信号)は、画像を表す信号である。

## [0026]

タイミングジェネレータ 2 6 は、タイミング制御信号 T C を生成する。タイミング制御信号 T C は、第 1 及び第 2 リードコントローラ 2 2 , 2 4、並びにメモリ制御部 1 2 2 の動作タイミングを制御する。

## [0027]

第1リードコントローラ22は、1又は複数のライン毎に、読み出しラインを指定する第1制御信号を生成する。第2リードコントローラ24は、1又は複数のカラム毎に、H方向の読み出し画素位置を指定する第2制御信号を生成し、第1制御信号が指定する読み出しラインに基づいて、読み出し画素位置を特定し、センサコア21が変換した電気信号を読み出す。例えば、第1及び第2リードコントローラ22,24は、シフトレジスタを備える。

## [0028]

ADC28は、第2リードコントローラ24により読み出された電気信号を、デジタル信号(図2の画像データ)に変換する。デジタル信号の数は、第2リードコントローラ24により読み出されるカラムの数に応じて決まる。例えば、第2リードコントローラ24が2カラム毎に電気信号を読み出す場合には、デジタル信号は、第1及び第2デジタル信号D1,D2である。

#### [0029]

ラインメモリ124は、ADC28の出力(画像データ)をライン単位で記憶する。メモリ制御部122は、ラインメモリ124への画像データの書き込みと、ラインメモリ124からの画像データの読み出しと、第1~第3符号化部14~16の動作と、を制御する。例えば、ラインメモリ制御部122は、第1順に従って、複数ライン(例えば、4ライン)の画像データをラインメモリ124から画像データを読み出し、読み出した画像データG,R,Bと、第1~第3符号化制御信号V1~V3と、を第1~第3符号化部14~16へ供給する。

# [0030]

メモリ制御部122及びラインメモリ124の動作例について説明する。図6は、第1実施形態のメモリ制御部122及びラインメモリ124の動作の説明図である。図6では、破線が読み出し動作を示し、実線が書き込み動作を示し、「G00」等が図2の第1画素G(L0,C0)等に対応し、「R01」等が図2の第2画素R(L0,C1)等に対応し、「B10」等が図2の第3画素B(L1,C0)等に対応する。

## [0031]

書き込み動作では、第1順に従って、1ライン2カラム毎に、2画素が書き込まれる。例えば、第1画素G20及び第2画素R21が書き込まれた後は、第1画素G22及び第2画素R23が書き込まれる。

## [0032]

読み出し動作では、第2順に従って、2ライン1カラム毎に、2画素が読み出される。例えば、第1画素G00及び第3画素B10が読み出された後は、第2画素R01及び第1画素G11が読み出される。即ち、メモリ制御部122は、2ラインの奇数カラム上に含まれる第1及び3画素G,Bのセットと、2ラインの偶数カラム上に含まれる第1及び第2画素G,Rのセットと、を順次ラインメモリ122から読み出す。

# [0033]

即ち、メモリ制御部122は、第1画素 G (例えば、G 0 0 )を第1符号化部14へ供給した後に、カラム方向において当該第1画素(即ち、ターゲット第1画素) G に近接する第1画素(即ち、参照第1画素) G (例えば、G 1 1 )を、第1符号化部14へ供給する。また、メモリ制御部122は、第2画素 R (例えば、R 0 1 )を第2符号化部15へ

10

20

30

40

供給した後に、ライン方向において当該第2画素(即ち、ターゲット第2画素)Rに近接する第2画素(即ち、参照第2画素)R(例えば、R03)を、第2符号化部15へ供給する。また、メモリ制御部122は、第3画素B(例えば、B10)を第3符号化部16へ供給した後に、ライン方向において当該第3画素(即ち、ターゲット第3画素)Bに近接する第3画素(即ち、参照第3画素)B(例えば、B12)を、第3符号化部16へ供給する。

#### [0034]

第1実施形態のDPCM141及びIDPCM142の動作について説明する。図7は、第1実施形態のDPCM141及びIDPCM142の動作の説明図である。図7では、G00が図2の第1画素G(L0,C0)に対応し、R01が図2の第2画素R(L0,C1)に対応し、B10が図2の第3画素B(L1,C0)に対応する。

[0035]

図 7 ( A ) は、第 1 画素 G 1 1 について差分信号を生成するときのフィードバック画素が第 1 画素 G 0 0 であり、第 1 画素 G 0 2 について差分信号を生成するときのフィードバック画素が第 1 画素 G 1 1 であることを示している。

[0036]

第1符号化部14において、DPCM141が第1画素G02について差分信号を生成するときに、IDPCM145は、HV空間において最も近接する第1画素G11をフィードバック画素として、DPCM141へ供給する。次いで、DPCM141は、第1画素G11,G02との差分値を示す差分信号を生成する。

[0037]

図7(B)は、第2画素R03について差分信号を生成するときのフィードバック画素が第2画素R01であり、第3画素B12について差分信号を生成するときのフィードバック画素が第3画素B10であることを示している。

[0038]

第2符号化部15において、DPCM141が第2画素R03について差分信号を生成するときに、IDPCM145は、H方向に近接する(即ち、H方向に2画素分離れた)第2画素R01をフィードバック画素として、DPCM141へ供給する。次いで、DPCM141は、第2画素R03,R01との差分値を示す差分信号を生成する。

[0039]

第3符号化部16において、DPCM141が第3画素B12について差分信号を生成するときに、IDPCM145は、H方向に近接する(即ち、H方向に2画素分離れた)第3画素B10をフィードバック画素として、DPCM141へ供給する。次いで、DPCM141は、第3画素B12,B10との差分値を示す差分信号を生成する。

[0040]

換言すると、第2及び第3符号化部15,16は、符号化の対象となるターゲット画素について差分信号を生成するときに、H方向の距離を考慮して参照画素を選択する。一方、第1符号化部14は、H方向及びV方向の両方の距離(即ち、直線距離)を考慮して、参照画素を選択する。

[0041]

第1実施形態によれば、量子化誤差を低減することができ、ひいては、符号化の際のSN比の低下を防ぐことができる。

[0042]

(第2実施形態)

第2実施形態は、ラインメモリの代わりに、並び替え部を用いて、量子化誤差を低減する、画像圧縮システム1の例である。なお、第1実施形態と同様の説明は省略する。第2実施形態の画像処理システム1の構成について説明する。図8は、第2実施形態の画像処理システム1のブロック図である。タイミングジェネレータ26は、クロック信号、水平同期信号、及び垂直同期信号を生成する。ADC28は、第2リードコントローラ24ではなく、第1リードコントローラ22により読み出された電気信号を、デジタル信号であ

10

20

30

40

る画像データ(図2)に変換する。画像データ制御部12は、第1実施形態のメモリ制御部122及びラインメモリ124ではなく、並べ替え部126を備える。

## [0043]

第2実施形態の並べ替え部126の動作について説明する。図9は、第2実施形態の並べ替え部126の動作の説明図である。図9では、「G00」、「R01」、及び「B10」等は図6と同様であり、「clk」はクロック信号であり、「Hsync」は水平同期信号であり、「Vsync」は垂直同期信号であり、「D1」、「D2」、「TC」、「G」、「R」、「B」、及び「V1」~「V3」は、図8と同様である。

## [0044]

第1デジタル信号 D1は、初期サイクル t0から所定サイクル経過後のサイクル t1から、第1画素 G00、第2画素 R01、第1画素 G02の順(即ち、H方向)に、偶数ライン上の画素が配列された信号である。第2デジタル信号 D2は、サイクル t1から、第3画素 B10、第1画素 G11、第3画素 B12の順(即ち、H方向)に、奇数ライン上の画素が配列された信号である。タイミング制御信号 TCは、サイクル t1から、1サイクル毎に、ハイとロウとが交互に切り替わる。

#### [0045]

第1画素 G は、「G 0 0 」、「G 1 1 」、「G 0 2 」の順に(即ち、偶数ライン上の第1画素 G と奇数ライン上の第1画素 G とが交互に切り替わるように)、第1符号化部14に供給される。第1有効信号 V 1の信号レベルは、サイクル t 1から、常にハイ(即ち、第1符号化部14を有効化する信号)である。第1画素 G は、第1有効信号 V 1がハイのときに、第1符号化部14へ供給される。即ち、第1画素 G は、サイクル t 1から、毎サイクル連続して供給される。

## [0046]

第2画素 R は、「R 0 1」、「R 0 3」、「R 0 5」の順に(即ち、偶数ライン上の第2画素 R が連続するように)、第2符号化部15に供給される。第2有効信号 V 2 の信号レベルは、サイクル t 1 から1サイクル経過後のサイクル t 2 から、1サイクル毎に、ハイ(即ち、第2符号化部15を有効化する信号)と口ウとが交互に切り替わる。第2画素 R は、第2有効信号 V 2 がハイのときに、第2符号化部15へ供給される。即ち、第2画素 R は、サイクル t 2 から、2 サイクル毎に供給される。

## [0047]

第3画素 B は、「B 1 0」、「B 1 2」、「B 1 4」の順に(即ち、奇数ライン上の第3 画素 B が連続するように)、第2 符号化部15 に供給される。第3 有効信号 V 3 の信号 レベルは、サイクル t 1 から、1 サイクル毎に、ハイ(即ち、第3 符号化部16 を有効化する信号)と口ウとが交互に切り替わる。第3 画素 B は、第3 有効信号 V 3 がハイのときに、第3 符号化部16 へ供給される。即ち、第3 画素 B は、サイクル t 1 から、2 サイクル毎に供給される。

# [0048]

第2実施形態によれば、第1実施形態と比べて、画像データ制御部12のサイズを低減することができる。

## [0049]

# (第3実施形態)

第3実施形態は、第1又は第2実施形態と同様の機能に加えて、符号量を制御する、画像圧縮装置10の例である。なお、第1又は第2実施形態と同様の説明は省略する。図10は、第3実施形態の画像圧縮装置10のブロック図である。画像圧縮装置10は、第1実施形態と同様の構成(画像データ制御部12、第1~第3符号化部14~16、及び符号化データ生成部18)に加えて、符号量制御部13を備える。

#### [0050]

符号量制御部13は、符号量制御信号を生成する。符号量制御信号は、第1~第3符号化部14~16の符号量(例えば、量子化係数)を制御する。具体的には、符号量制御部13は、画像データ制御部12から画像データ(第1画素G、第2画素R、及び第3画素

10

20

30

40

B)を取得し、当該画像データに基づいて符号量制御信号を生成し、当該画像データ及び 当該符号量制御信号を、第1~第3符号化部14~16へ供給する。第1~第3符号化部 14~16はそれぞれ、符号量制御信号に基づいて、ターゲット第1画素~ターゲット第 3画素を符号化する。

# [0051]

第3実施形態の符号量制御部13の構成について説明する。図11は、第3実施形態の符号量制御部13のブロック図である。符号量制御部13は、第1~第3サンプル生成部131~133と、バッファ136と、レジスタ137と、符号量選択部138と、を備える。

## [0052]

第1~第3サンプル部131~133は、それぞれ、第1~第3画素G,R,Bに対して、複数の符号量を用いた符号化処理を適用することにより、第1~第3サンプルデータを生成する。第1~第3サンプルデータとは、それぞれ、符号量毎の第1~第3画素G,R,Bの符号化データの集合である。

#### [0053]

レジスタ137は、サンプルデータと最適符号量との関係を示すマッチングテーブルを 記憶する。マッチングテーブルは、固定情報であっても良いし、可変情報(例えば、符号 量制御部13の外部から更新可能な情報)であっても良い。

#### [0054]

符号量選択部 1 3 8 は、第 1 ~ 第 3 サンプル部 1 3 1 ~ 1 3 3 により生成された第 1 ~ 第 3 サンプルデータとレジスタ 1 3 7 に記憶されたマッチングテーブルとを用いて、第 1 ~ 第 3 符号化部 1 4 ~ 1 6 の第 1 ~ 第 3 最適符号量を選択し、第 1 ~ 第 3 最適符号量を示す第 1 ~ 第 3 符号量制御信号を、第 1 ~ 第 3 符号化部 1 4 ~ 1 6 へ供給する。

# [0055]

バッファ136は、第1~第3画素G,R,Bが符号量選択部138に供給されてから、第1~第3符号量制御信号が生成されるまでの間、第1~第3画素G,R,Bを記憶する。バッファ136に記憶された第1~第3画素G,R,Bは、第1~第3符号量制御信号とともに、出力される。

## [0056]

第3実施形態によれば、第1又は第2実施形態と比べて、符号化データの符号量を最適値にすることができる。

# [0057]

なお、本実施形態では、画像データが、3種類の色成分に対応する画素を含む例について説明したが、画像データは、4種類以上の画素を含んでも良い。即ち、本実施形態の画像データは、少なくとも3種類の色成分に対応する画素を含むものである。

#### [0058]

本実施形態に係る画像処理システム1の少なくとも一部は、ハードウェアで構成しても良いし、ソフトウェアで構成しても良い。ソフトウェアで構成する場合には、画像処理システム1の少なくとも一部の機能を実現するプログラムをフレキシブルディスクやCD-ROM等の記録媒体に収納し、コンピュータに読み込ませて実行させても良い。記録媒体は、磁気ディスクや光ディスク等の着脱可能なものに限定されず、ハードディスク装置やメモリなどの固定型の記録媒体でも良い。

## [0059]

また、本実施形態に係る画像処理システム1の少なくとも一部の機能を実現するプログラムを、インターネット等の通信回線(無線通信も含む)を介して頒布しても良い。さらに、同プログラムを暗号化したり、変調をかけたり、圧縮した状態で、インターネット等の有線回線や無線回線を介して、あるいは記録媒体に収納して頒布しても良い。

#### [0060]

なお、本発明は、上述した実施形態に限定されるものではなく、その要旨を逸脱しない 範囲で構成要素を変形して具体化される。また、上述した実施形態に開示されている複数 10

20

30

40

の構成要素の適宜な組み合わせにより、種々の発明が形成可能である。例えば、上述した 実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる 実施形態にわたる構成要素を適宜組み合わせてもよい。

## 【符号の説明】

# [0061]

- 1 画像処理システム

- 10 画像圧縮装置

- 12 画像データ制御部

- 1 2 2 メモリ制御部

- 124 ラインメモリ

- 126 並び替え部

- 13 符号量制御部

- 131 第1サンプル生成部

- 132 第2サンプル生成部

- 133 第3サンプル生成部

- 136 バッファ

- 137 レジスタ

- 138 符号量選択部

- 14 第1符号化部

- 141 DPCM

- 1 4 2 量子化部

- 143 可变長符号化部

- 144 逆量子化部

- 145 IDPCM

- 15 第2符号化部

- 1 6 第 3 符号化部

- 18 符号化データ生成部

- 20 イメージセンサ

- 21 センサコア

- 22 第1リードコントローラ

- 24 第2リードコントローラ

- 26 タイミングジェネレータ

- 28 ADC

10

20

# 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

# 【図11】

# フロントページの続き

(74)代理人 100165375

弁理士 石川 隆史

(72)発明者 中 西 圭 里

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 堀井 啓明

(56)参考文献 特開平04-065975 (JP,A)

特開2011-239424(JP,A)

特開2005-191939(JP,A)

特開2011-015347(JP,A)

特開2002-171531(JP,A)

特開2006-332955(JP,A)

特開2011-130275(JP,A)

特開2000-354193(JP,A)

特開2011-239456(JP,A)

(58)調査した分野(Int.CI., DB名)

H04N19/00-19/98

H04N1/41-1/419