# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl.

H01L 29/78 (2006.01)

H01L 21/336 (2006.01)

(45) 공고일자 2007년01월29일 (11) 등록번호 10-0675290

(24) 등록일자 2007년01월22일

(21) 출원번호10-2005-0113133(22) 출원일자2005년11월24일심사청구일자2005년11월24일

(65) 공개번호 (43) 공개일자

(73) 특허권자 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 안영준

대전 유성구 구성동 한국과학기술원 동측기숙사 6302호

이충호

경기 성남시 분당구 구미동 까치마을신원아파트 신원305-503

강희수

경기 안양시 동안구 호계3동 대림 e-편한세상아파트 102동 704호

(74) 대리인 박상수

(56) 선행기술조사문헌 KR1020050081389 A US6373095 B1

KR1020060000275 A US6562665 B1

\* 심사관에 의하여 인용된 문헌

심사관: 박근용

전체 청구항 수 : 총 22 항

# (54) 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터를갖는 반도체소자의 제조방법 및 관련된소자

#### (57) 요약

하나의 기판 상에 다중채널 전계효과트랜지스터와 핀 전계효과트랜지스터를 갖는 반도체소자의 제조방법을 제공한다. 기판을 준비하고, 상기 기판 상에 제 1 하드마스크패턴 및 제 2 하드마스크패턴을 형성한다. 상기 제 2 하드마스크패턴은 상기 제 1 하드마스크패턴보다 좁은 폭을 갖는다. 상기 하드마스크패턴들을 식각마스크로 이용하여 상기 기판을 부분적으로 제거하여 예비 다중 핀 및 단일 핀(single fin)을 형성한다. 상기 예비 다중 핀은 상기 제 1 하드마스크패턴 하부에 형성되고, 상기 단일 핀은 상기 제 2 하드마스크패턴 하부에 형성된다. 상기 예비 다중 핀 내에 오목한 부분을 형성하여 다중 핀 (multi fin)을 형성한다. 상기 오목한 부분은 상기 다중 핀(multi fin)의 가운데에 정렬되도록 형성할 수 있다. 상기 다중 핀 및 상기 단일 핀은 실질적으로 동일한 높이를 갖도록 형성할 수 있다.

#### 대표도

도 12

## 특허청구의 범위

## 청구항 1.

기판을 제공하고,

상기 기판 상에 제 1 하드마스크패턴 및 상기 제 1 하드마스크패턴보다 좁은 폭을 갖는 제 2 하드마스크패턴을 형성하고,

상기 하드마스크패턴들을 식각마스크로 이용하여 상기 기판을 부분적으로 제거하여 상기 제 1 하드마스크패턴 하부에 예비 다중 핀 및 상기 제 2 하드마스크패턴 하부에 단일 핀(single fin)을 형성하고,

상기 예비 다중 핀 내에 오목한 부분을 형성하여 다중 핀(multi fin)을 형성하는 것을 포함하는 반도체소자의 제조방법.

#### 청구항 2.

제 1 항에 있어서,

상기 하드마스크패턴들은 질화막으로 형성하는 것을 특징으로 하는 반도체소자의 제조방법.

#### 청구항 3.

제 1 항에 있어서,

상기 오목한 부분은 상기 다중 핀(multi fin)의 가운데에 정렬되도록 형성하는 것을 특징으로 하는 반도체소자의 제조방법.

#### 청구항 4.

제 1 항에 있어서,

상기 오목한 부분을 형성하는 것은

상기 기판 상에 다중채널마스크를 형성하되, 상기 다중채널마스크는 상기 예비 다중 핀의 상면을 부분적으로 노출시키는 제 1 개구부를 갖고.

상기 다중채널마스크를 식각마스크로 이용하여 상기 예비 다중 핀을 이방성식각하는 것을 포함하는 반도체소자의 제조방법.

#### 청구항 5.

제 4 항에 있어서,

상기 다중채널마스크를 형성하는 것은

풀백(pull back) 공정을 이용하여 상기 하드마스크패턴들을 식각하여 상기 예비 다중 핀 상에 제 1 하드마스크 축소패턴을 형성하고,

상기 기판을 덮고 상기 제 1 하드마스크 축소패턴의 상면을 노출시키는 희생막을 형성하고,

상기 희생막 및 상기 제 1 하드마스크 축소패턴을 패터닝하여 상기 예비 다중 핀 및 상기 단일 핀 상을 가로지르는 희생라인을 형성하되, 상기 희생라인은 희생패턴 및 제 1 희생마스크를 구비하고,

상기 희생라인 양측의 상기 기판 상에 보호막을 형성하고,

상기 제 1 희생마스크를 선택적으로 제거하는 것을 포함하는 반도체소자의 제조방법.

#### 청구항 6.

제 5 항에 있어서,

상기 풀백(pull back) 공정은 상기 제 2 하드마스크패턴이 완전히 제거될 때 까지 수행하는 것을 특징으로 하는 반도체소 자의 제조방법.

## 청구항 7.

제 4 항에 있어서,

상기 다중채널마스크를 형성하는 것은

풀백(pull back) 공정을 이용하여 상기 하드마스크패턴들을 부분적으로 제거하여 제 1 하드마스크 축소패턴 및 제 2 하드마스크 축소패턴을 형성하고,

상기 기판을 덮고 상기 하드마스크 축소패턴들의 상면들을 노출시키는 희생막을 형성하고,

상기 희생막 및 상기 하드마스크 축소패턴들을 패터닝하여 상기 예비 다중 핀 및 상기 단일 핀 상을 가로지르는 희생라인을 형성하되, 상기 희생라인은 희생패턴, 제 1 희생마스크 및 제 2 희생마스크를 구비하고,

상기 희생라인 양측의 상기 기판 상에 보호막을 형성하고,

상기 희생마스크들을 선택적으로 제거하여 상기 제 1 개구부 및 제 2 개구부를 형성하고,

상기 제 1 개구부의 측벽에 스페이서를 형성하고 상기 제 2 개구부 내에 희생플러그를 형성하는 것을 포함하는 반도체소 자의 제조방법.

#### 청구항 8.

제 7 항에 있어서,

상기 풀백(pull back) 공정은 상기 하드마스크패턴들을 등방성 식각하는 것을 포함하는 반도체소자의 제조방법.

#### 청구항 9.

제 7 항에 있어서,

상기 희생막 및 상기 보호막은 상기 하드마스크패턴들에 대하여 식각선택비를 갖는 물질막으로 형성하는 것을 특징으로 하는 반도체소자의 제조방법.

## 청구항 10.

제 7 항에 있어서,

상기 스페이서 및 상기 희생플러그를 형성하는 것은

상기 제 2 개구부를 채우고 상기 제 1 개구부의 내벽을 덮는 스페이서막을 형성하고,

상기 제 1 개구부의 바닥에 상기 예비 다중 핀의 상면이 노출될 때 까지 상기 스페이서막을 이방성식각하는 것을 포함하는 반도체소자의 제조방법.

#### 청구항 11.

제 1 항에 있어서,

상기 다중 핀 및 상기 단일 핀은 실질적으로 동일한 높이를 갖도록 형성하는 것을 특징으로 하는 반도체소자의 제조방법.

#### 청구항 12.

기판을 제공하고,

상기 기판으로부터 돌출된 예비 다중 핀 및 단일 핀(single fin)을 형성하되, 상기 예비 다중 핀은 상기 단일 핀(single fin) 보다 넓은 폭을 갖고,

상기 예비 다중 핀 내에 오목한 부분을 형성하여 다중 핀(multi fin)을 형성하고,

상기 다중 핀 및 상기 단일 핀 상에 게이트유전막을 형성하고,

상기 다중 핀을 가로지르는 제 1 게이트전극 및 상기 단일 핀을 가로지르는 제 2 게이트전극을 형성하는 것을 포함하는 에 스램 셀(SRAM cell)의 제조방법.

#### 청구항 13.

제 12 항에 있어서,

상기 핀들(fins)을 형성하는 것은

상기 기판 상에 서로 이격된 제 1 하드마스크패턴 및 상기 제 1 하드마스크패턴보다 좁은 폭을 갖는 제 2 하드마스크패턴을 형성하고,

상기 하드마스크패턴들을 식각마스크로 이용하여 상기 기판을 부분적으로 제거하는 것을 포함하되, 상기 제 1 하드마스크패턴 하부에 상기 예비 다중 핀이 형성되고, 상기 제 2 하드마스크패턴 하부에 상기 단일 핀이 형성되는 것을 특징으로 하는 에스램 셀(SRAM cell)의 제조방법.

#### 청구항 14.

제 13 항에 있어서,

상기 하드마스크패턴들은 질화막으로 형성하는 것을 특징으로 하는 에스램 셀(SRAM cell)의 제조방법.

#### 청구항 15.

제 13 항에 있어서.

상기 오목한 부분을 형성하는 것은

상기 기판 상에 다중채널마스크를 형성하되, 상기 다중채널마스크는 상기 예비 다중 핀의 상면을 부분적으로 노출시키는 제 1 개구부를 갖고,

상기 다중채널마스크를 식각마스크로 이용하여 상기 예비 다중 핀을 이방성식각하는 것을 포함하는 에스램 셀(SRAM cell)의 제조방법.

## 청구항 16.

제 15 항에 있어서,

상기 다중채널마스크를 형성하는 것은

풀백(pull back) 공정을 이용하여 상기 하드마스크패턴들을 부분적으로 제거하여 제 1 하드마스크 축소패턴 및 제 2 하드마스크 축소패턴을 형성하고,

상기 기판을 덮고 상기 하드마스크 축소패턴들의 상면들을 노출시키는 희생막을 형성하고,

상기 희생막 및 상기 하드마스크 축소패턴들을 패터닝하여 상기 예비 다중 핀 및 상기 단일 핀 상을 가로지르는 희생라인을 형성하되, 상기 희생라인은 희생패턴, 제 1 희생마스크 및 제 2 희생마스크를 구비하고,

상기 희생라인 양측의 상기 기판 상에 보호막을 형성하고,

상기 희생마스크들을 선택적으로 제거하여 상기 제 1 개구부 및 제 2 개구부를 형성하고,

상기 제 1 개구부의 측벽에 스페이서를 형성하고 상기 제 2 개구부 내에 희생플러그를 형성하는 것을 포함하는 에스램 셀(SRAM cell)의 제조방법.

## 청구항 17.

제 16 항에 있어서,

상기 희생막 및 상기 보호막은 상기 하드마스크패턴들에 대하여 식각선택비를 갖는 물질막으로 형성하는 것을 특징으로 하는 에스램 셀(SRAM cell)의 제조방법.

#### 청구항 18.

제 12 항에 있어서,

상기 제 1 게이트전극은 상기 오목한 부분 내부를 채우고 상기 다중 핀의 적어도 일 측벽을 덮도록 형성하고, 상기 제 2 게이트전극은 상기 단일 핀의 적어도 일 측벽을 덮도록 형성하는 것을 특징으로 하는 에스램 셀(SRAM cell)의 제조방법.

## 청구항 19.

기판;

상기 기판으로부터 돌출되고 그 내부에 오목한 부분을 갖는 다중 핀(multi fin);

상기 기판으로부터 돌출되고 상기 다중 핀(multi fin)보다 좁은 폭을 갖는 단일 핀(single fin);

상기 다중 핀을 가로지르는 제 1 게이트전극;

상기 단일 핀을 가로지르며 상기 단일 핀의 적어도 일 측벽을 덮는 제 2 게이트전극; 및

상기 핀들(fins)과 상기 게이트전극들 사이에 개재된 게이트유전막을 포함하는 반도체소자.

## 청구항 20.

제 19 항에 있어서,

상기 오목한 부분은 상기 다중 핀의 가운데에 정렬되고, 상기 제 1 게이트전극은 상기 오목한 부분 내부를 채우고 상기 다중 핀의 적어도 일 측벽을 덮는 것을 특징으로 하는 반도체소자.

## 청구항 21.

제 19 항에 있어서,

상기 다중 핀 및 상기 단일 핀은 실질적으로 동일한 높이를 갖는 것을 특징으로 하는 반도체소자.

#### 청구항 22.

제 19 항에 있어서.

상기 제 2 게이트전극은 상기 단일 핀의 양 측벽들을 덮는 것을 특징으로 하는 반도체소자.

## 명세서

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체소자 및 그 제조방법에 관한 것으로, 특히 하나의 기판 상에 다중채널 전계효과트랜지스터와 핀 전계효과 트랜지스터를 갖는 반도체소자의 제조방법 및 관련된 소자에 관한 것이다. 반도체소자의 고집적화 필요에 따라 전계효과트랜지스터의 크기를 축소하려는 연구가 지속적으로 이루어지고 있다. 종래의 평면 트랜지스터(planar transistor)를 구비하는 반도체소자의 경우, 트랜지스터의 크기를 축소하는 것은 트랜지스터의 채널 길이(channel length)와 채널 폭(channel width)이 줄어드는 것을 의미한다. 상기 채널길이가 줄어들면서, 집적도의증가뿐만 아니라 반도체소자의 동작속도가 빨라지는 등 성능 또한 향상되었다. 그러나 상기 채널길이의 감소는 단채널효과(short channel effect)라 불려지는 많은 문제점들을 야기한다. 상기 채널 폭의 축소는 상기 트랜지스터의 전류구동능력을 감소시킨다.

이러한 문제점들을 개선하기 위하여 핀 전계효과트랜지스터(finFET)가 제안된 바 있다. 상기 핀 전계효과트랜지스터는 기 판으로부터 상대적으로 돌출된 실리콘 핀, 및 상기 실리콘 핀의 양 측벽들 및 상면을 덮는 절연된 게이트전극을 구비한다. 상기 게이트전극 양측의 상기 실리콘 핀 내에 소스/드레인 영역이 배치된다. 이에 따라, 상기 핀 전계효과트랜지스터의 채 널영역은 상기 양 측벽들 및 상면의 표면에 형성된다. 즉, 상기 핀 전계효과트랜지스터의 유효채널 폭(effective channel width)은 같은 평면적을 갖는 평면 트랜지스터에 비하여 상대적으로 증가한다. 또한, 상기 게이트전극이 상기 채널영역의 양측을 덮도록 배치됨으로써, 상기 게이트전극의 상기 채널영역에 대한 제어능력을 향상시킬 수 있다. 특히, 상기 양 측벽들 간의 거리가 채널공핍깊이(channel depletion depth)의 2배 이하인 경우에, 상기 실리콘 핀은 완전공핍(fully depletion)되어 우수한 전기적 특성을 보일 수 있다.

그런데 상기 반도체소자는 하나의 기판 상에 서로 다른 온 전류(on current)를 갖는 전계효과트랜지스터들을 필요로 할 수 있다. 예를 들면, 디램(dynamic random access memory; DRAM)과 같은 메모리소자는 셀 트랜지스터 및 주변회로 트랜지스터를 구비한다. 상기 주변회로 트랜지스터는 상기 셀 트랜지스터 보다 큰 온 전류(on current)를 필요로 할 수 있다. 상기 실리콘 핀의 높이를 서로 다르게 하여 상기 서로 다른 온 전류(on current)를 갖는 전계효과트랜지스터들을 구현하는 방법이 있다. 그러나 상기 실리콘 핀의 높이를 서로 다르게 하는 것은 공정을 매우 복잡하게 한다. 다른 방법으로, 상기 실리콘 핀의 상면을 넓히는 방법이 있다. 이 경우에, 상기 실리콘 핀의 두께가 두꺼워 짐에 따라 상기 핀 전계효과트랜지스터의 특성을 살릴 수 없게 된다. 또한, 상기 실리콘 핀의 상면을 넓히는 방법은 상기 반도체소자의 고집적화를 어렵게 한다.

한편, 상기 서로 다른 온 전류(on current)를 갖는 전계효과트랜지스터들이 미국특허 제 6,911,383 B2호에 "하이브리드 평면 및 핀펫 시모스 소자(HYBRID PLANAR AND FINFET CMOS DEVICES)" 라는 제목으로 도리스 등(Doris et al.)에 의해 개시된 바 있다.

도리스 등(Doris et al.)에 따르면, 동일 에스오아이(silicon on insulator; SOI) 기판 상에 평면 전계효과트랜지스터 (planar FET) 및 핀 전계효과트랜지스터(finFET)를 구비하는 반도체소자가 제공된다.

다른 한편, 상기 전계효과트랜지스터의 유효채널 폭을 증가시키기 위한 다른 방법이 미국특허 제 6,872,647 B1 호에 "반도체소자의 다중 핀 형성방법(METHOD FOR FORMING MULTIPLE FINS IN A SEMICONDUCTOR DEVICE)" 이라는 제목으로 유 등(Yu et al.)에 의해 개시된 바 있다.

유 등(Yu et al.)에 따르면, 에스오아이(silicon on insulator; SOI) 기판과 같은 반도체기판 상에 상면 및 측면들을 갖는 구조를 형성한다. 상기 구조의 측면들에 스페이서들을 형성한다. 상기 스페이서들을 식각마스크로 이용하여 상기 반도체기판을 선택적으로 제거하여 핀들(fins)을 형성한다.

그럼에도 불구하고, 하나의 기판 상에 서로 다른 온 전류(on current)를 갖는 전계효과트랜지스터들을 형성하는 기술은 지속적인 개선을 필요로 한다.

#### 발명이 이루고자 하는 기술적 과제

본 발명이 이루고자 하는 기술적 과제는 상술한 종래기술의 문제점을 개선하기 위한 것으로서, 하나의 기판 상에 서로 다른 온 전류(on current)를 갖는 전계효과트랜지스터들을 동시에 형성하는 방법을 제공하는데 있다.

본 발명이 이루고자 하는 다른 기술적 과제는, 하나의 기판 상에 다중채널 전계효과트랜지스터와 핀 전계효과트랜지스터를 갖는 반도체소자를 제공하는데 있다.

#### 발명의 구성

상기 기술적 과제를 달성하기 위하여 본 발명은, 하나의 기판 상에 다중채널 전계효과트랜지스터와 핀 전계효과트랜지스터를 갖는 반도체소자의 제조방법을 제공한다. 기판을 준비하고, 상기 기판 상에 제 1 하드마스크패턴 및 제 2 하드마스크 패턴을 형성한다. 상기 제 2 하드마스크패턴은 상기 제 1 하드마스크패턴보다 좁은 폭을 갖는다. 상기 하드마스크패턴들을 식각마스크로 이용하여 상기 기판을 부분적으로 제거하여 예비 다중 핀 및 단일 핀(single fin)을 형성한다. 상기 예비 다중 핀은 상기 제 1 하드마스크패턴 하부에 형성되고, 상기 단일 핀은 상기 제 2 하드마스크패턴 하부에 형성된다. 상기 예비 다중 핀 내에 오목한 부분을 형성하여 다중 핀(multi fin)을 형성한다.

본 발명의 몇몇 실시 예에 있어서, 상기 하드마스크패턴들은 질화막으로 형성할 수 있다.

다른 실시 예에 있어서, 상기 오목한 부분은 상기 다중 핀(multi fin)의 가운데에 정렬되도록 형성할 수 있다.

또 다른 실시 예에 있어서, 상기 오목한 부분을 형성하는 것은 상기 기판 상에 다중채널마스크를 형성하는 것을 포함할 수 있다. 상기 다중채널마스크는 상기 예비 다중 핀의 상면을 부분적으로 노출시키는 제 1 개구부를 갖도록 형성할 수 있다. 상기 다중채널마스크를 식각마스크로 이용하여 상기 예비 다중 핀을 이방성 식각할 수 있다.

또 다른 실시 예에 있어서, 상기 다중채널마스크를 형성하는 것은 풀백(pull back) 공정을 이용하여 상기 하드마스크패턴들을 식각하여 상기 예비 다중 핀 상에 제 1 하드마스크 축소패턴을 형성하는 것을 포함할 수 있다. 상기 풀백(pull back) 공정은 상기 제 2 하드마스크패턴이 완전히 제거될 때 까지 수행할 수 있다. 상기 기판을 덮고 상기 제 1 하드마스크 축소패턴의 상면을 노출시키는 희생막을 형성할 수 있다. 상기 희생막 및 상기 제 1 하드마스크 축소패턴을 패터닝하여 상기 예비 다중 핀 및 상기 단일 핀 상을 가로지르는 희생라인을 형성할 수 있다. 상기 희생라인은 희생패턴 및 제 1 희생마스크를 구비하도록 형성할 수 있다. 상기 희생라인 양측의 상기 기판 상에 보호막을 형성할 수 있다. 상기 제 1 희생마스크를 선택적으로 제거할 수 있다.

또 다른 실시 예에 있어서, 상기 다중채널마스크를 형성하는 것은 풀백(pull back) 공정을 이용하여 상기 하드마스크패턴들을 부분적으로 제거하여 제 1 하드마스크 축소패턴 및 제 2 하드마스크 축소패턴을 형성하는 것을 포함할 수 있다. 상기 기판을 덮고 상기 하드마스크 축소패턴들의 상면들을 노출시키는 희생막을 형성할 수 있다. 상기 희생막 및 상기 하드마스크 축소패턴들을 패터닝하여 상기 예비 다중 핀 및 상기 단일 핀 상을 가로지르는 희생라인을 형성할 수 있다. 상기 희생라인은 희생패턴, 제 1 희생마스크 및 제 2 희생마스크를 구비하도록 형성할 수 있다. 상기 희생라인 양측의 상기 기판 상에 보호막을 형성할 수 있다. 상기 희생막 및 상기 보호막은 상기 하드마스크패턴들에 대하여 식각선택비를 갖는 물질막으로 형성할 수 있다. 상기 희생마스크들을 선택적으로 제거하여 상기 제 1 개구부 및 제 2 개구부를 형성할 수 있다. 상기 제 1 개구부의 측벽에 스페이서를 형성하고 상기 제 2 개구부에 희생플러그를 형성할 수 있다. 상기 희생플러그는 상기 제 2 개구부를 완전히 매립하도록 형성할 수 있다.

또 다른 실시 예에 있어서, 상기 다중 핀 및 상기 단일 핀은 실질적으로 동일한 높이를 갖도록 형성할 수 있다.

또한, 본 발명은, 에스램 셀(SRAM cell)의 제조방법을 제공한다. 기판을 준비하고, 상기 기판으로부터 돌출된 예비 다중 핀 및 단일 핀(single fin)을 형성한다. 상기 예비 다중 핀은 상기 단일 핀(single fin) 보다 넓은 폭을 갖도록 형성한다. 상기 예비 다중 핀 내에 오목한 부분을 형성하여 다중 핀(multi fin)을 형성한다. 상기 다중 핀 및 상기 단일 핀 상에 게이트유 전막을 형성한다. 상기 다중 핀을 가로지르는 제 1 게이트전극 및 상기 단일 핀을 가로지르는 제 2 게이트전극을 형성한다.

몇몇 실시 예에 있어서, 상기 제 1 게이트전극은 상기 오목한 부분 내부를 채우고 상기 다중 핀의 적어도 일 측벽을 덮도록 형성할 수 있다. 상기 제 2 게이트전극은 상기 단일 핀의 적어도 일 측벽을 덮도록 형성할 수 있다.

이에 더하여, 본 발명은, 하나의 기판 상에 다중채널 전계효과트랜지스터와 핀 전계효과트랜지스터를 갖는 반도체소자를 제공한다. 이 소자는 기판 및 상기 기판으로부터 돌출되고 그 내부에 오목한 부분을 갖는 다중 핀(multi fin)을 구비한다. 또한, 상기 기판으로부터 돌출되고 상기 다중 핀(multi fin)보다 좁은 폭을 갖는 단일 핀(single fin)이 제공된다. 상기 다중 핀을 가로지르는 제 1 게이트전극이 배치된다. 상기 단일 핀을 가로지르며 상기 단일 핀의 적어도 일 측벽을 덮는 제 2 게이트전극이 배치된다. 상기 핀들(fins)과 상기 게이트전극들 사이에 게이트유전막이 개재된다.

몇몇 실시 예에 있어서, 상기 오목한 부분은 상기 다중 핀의 가운데에 정렬될 수 있다. 상기 제 1 게이트전극은 상기 오목한 부분 내부를 채우고 상기 다중 핀의 적어도 일 측벽을 덮을 수 있다.

다른 실시 예에 있어서, 상기 다중 핀 및 상기 단일 핀은 실질적으로 동일한 높이를 갖는 것일 수 있다.

이하, 첨부한 도면들을 참조하여 본 발명의 바람직한 실시 예들을 상세히 설명하기로 한다. 그러나 본 발명은 여기서 설명되어지는 실시 예들에 한정되지 않고 다른 형태로 구체화될 수도 있다. 오히려, 여기서 소개되는 실시 예들은 개시된 내용이 철저하고 완전해질 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 제공되어지는 것이다. 도면들에 있어서, 충 및 영역들의 두께는 명확성을 기하기 위하여 과장되어진 것이다. 또한, 충이 다른 충 또는 기판 "상"에 있다고 언급되어지는 경우에 그것은 다른 충 또는 기판 상에 직접 형성될 수 있거나 또는 그들 사이에 제3의 충이 개재될 수도 있다. 명세서 전체에 걸쳐서 동일한 참조번호로 표시된 부분들은 동일한 구성요소들을 의미한다.

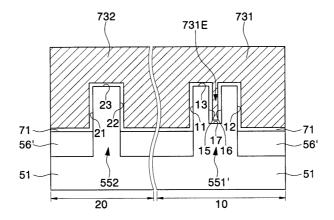

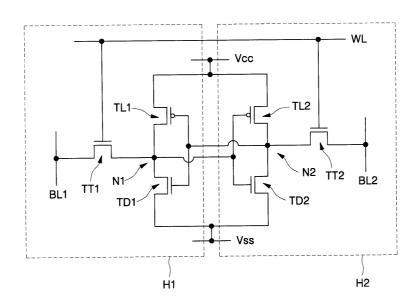

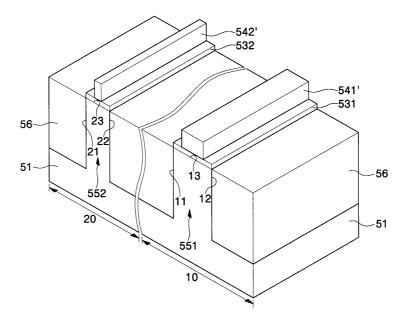

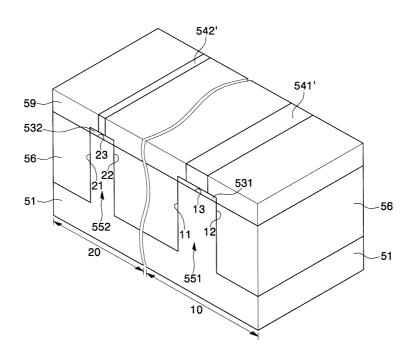

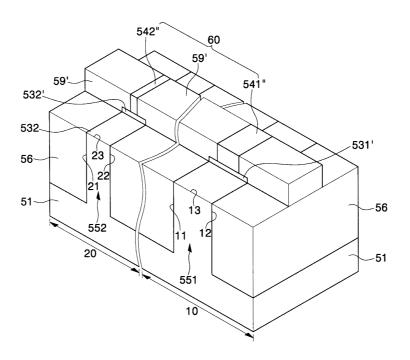

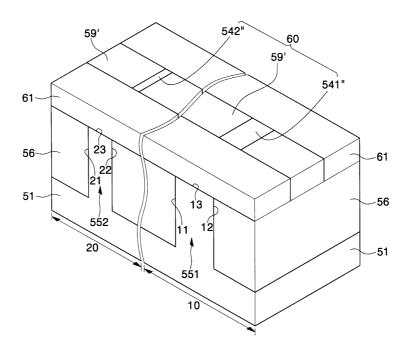

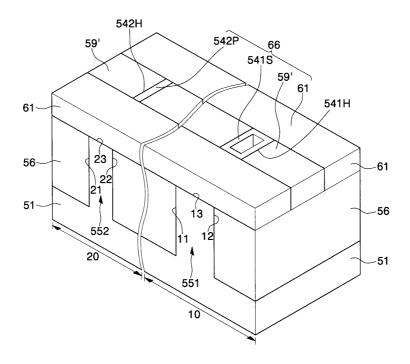

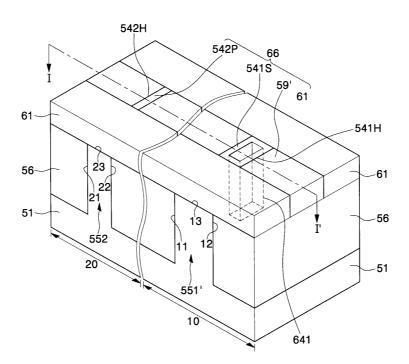

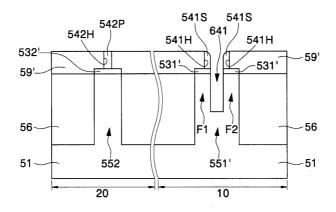

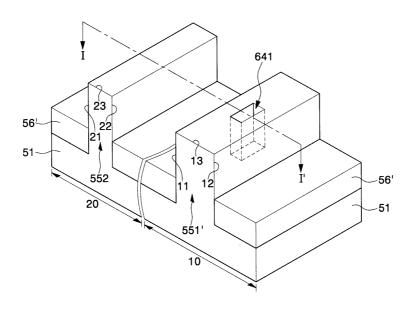

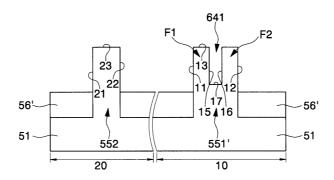

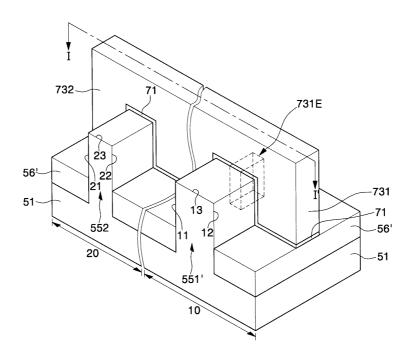

도 1 내지 도 7, 도 9 및 도 11은 본 발명의 실시 예에 따른 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터를 갖는 반도체소자의 제조방법을 설명하기 위한 사시도들이다. 도 8은 도 7의 절단선 I-I'에 따라 취해진 단면도이고, 도 10은 도 9의 절단선 I-I'에 따라 취해진 단면도이며, 도 12는 도 11의 절단선 I-I'에 따라 취해진 단면도이다.

먼저, 도 1 내지 도 12를 참조하여 본 발명의 실시 예에 따른 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터를 갖는 반도체소자의 제조방법을 설명하기로 한다.

도 1을 참조하면, 기판(51) 상의 소정영역에 제 1 하드마스크패턴(541) 및 제 2 하드마스크패턴(542)을 형성한다. 상기 제 1 하드마스크패턴(541)은 상기 제 2 하드마스크패턴(542) 보다 넓은 폭을 갖도록 형성할 수 있다.

상기 기판(51)은 실리콘웨이퍼 또는 에스오아이(silicon on insulator; SOI) 웨이퍼와 같은 반도체기판일 수 있다. 상기 기판(51)은 제 1 영역(10) 및 제 2 영역(20)을 구비할 수 있다. 상기 제 1 영역(10)은 반도체소자의 주변회로 영역일 수 있고, 상기 제 2 영역(20)은 셀 영역일 수 있다. 또한, 상기 제 1 영역(10)은 에스램 셀(static random access memory cell; SRAM cell)의 풀다운 트랜지스터(pull-down transistor) 영역일 수 있고, 상기 제 2 영역(20)은 상기 에스램 셀(SRAM cell)의 패스 트랜지스터(pass transistor) 영역일 수 있다. 상기 제 1 하드마스크패턴(541)은 상기 제 1 영역(10) 상에 형성할 수 있으며, 상기 제 2 하드마스크패턴(542)은 상기 제 2 영역(20) 상에 형성할 수 있다.

상기 제 1 및 제 2 하드마스크패턴들(541, 542)을 형성하는 것은, 상기 기판(51) 상에 하드마스크막을 형성하고, 사진 및 식각 공정을 이용하여 상기 하드마스크막을 패터닝하는 것을 포함할 수 있다. 상기 제 1 및 제 2 하드마스크패턴들(541, 542)은 상기 기판(51)에 대하여 식각선택비를 갖는 물질막으로 형성하는 것이 바람직하다. 예를 들면, 상기 제 1 및 제 2 하드마스크패턴들(541, 542)은 실리콘질화막과 같은 질화막으로 형성할 수 있다.

상기 하드마스크막을 형성하기 전에, 상기 기판(51) 상에 완충막(pad layer)을 형성할 수 있다. 상기 완충막은 열산화막으로 형성할 수 있다. 상기 완충막은 상기 하드마스크막 및 상기 기판(51) 사이에 가해지는 스트레스를 완화시키는 역할을할 수 있다. 이 경우에, 상기 완충막은 상기 하드마스크막을 패터닝하는 동안 함께 패터닝되어 제 1 완충패턴(531) 및 제 2 완충패턴(532)이 형성될 수 있다. 상기 제 1 완충패턴(531)은 상기 제 1 하드마스크패턴(541)의 하부에 정렬될 수 있으며, 상기 제 2 완충패턴(532)은 상기 제 2 하드마스크패턴(542)의 하부에 정렬될 수 있다. 그러나 상기 제 1 완충패턴(531) 및 상기 제 2 완충패턴(532)은 생략될 수 있다.

상기 제 1 및 제 2 하드마스크패턴들(541, 542)을 식각마스크로 이용하여 상기 기판(51)을 식각하여 예비 다중 핀 (preliminary multi fin; 551) 및 단일 핀(single fin; 552)을 한정하는 트렌치를 형성한다. 상기 기판(51)을 식각하는 것은 이방성식각 공정을 이용하여 수행할 수 있다. 상기 예비 다중 핀(551)은 서로마주보는 제 1 및 제 2 측벽들(11, 12) 및 상 면(13)을 갖도록 형성된다. 상기 단일 핀(552) 또한 제 1 및 제 2 측벽들(21, 22) 및 상면(23)을 갖도록 형성된다. 상기 예비 다중 핀(551)은 상기 제 1 하드마스크패턴(541)의 하부에 정렬될 수 있으며, 상기 단일 핀(552)은 상기 제 2 하드마스크패턴(542)의 하부에 정렬될 수 있다. 이에 따라, 상기 예비 다중 핀(551)은 상기 단일 핀(552) 보다 넓은 폭을 갖도록 형성할 수 있다. 즉, 상기 예비 다중 핀(551)의 상면(13)은 상기 단일 핀(552)의 상면(23) 보다 큰 폭을 갖도록 형성할 수 있다.

그 결과, 상기 핀들(fins; 551, 552)은 상기 기판(51)으로부터 돌출되도록 형성될 수 있다. 상기 예비 다중 핀(551) 및 상기 단일 핀(552)은 실질적으로 같은 높이를 갖도록 형성할 수 있다. 즉, 상기 예비 다중 핀(551)의 제 1 및 제 2 측벽들(11, 12), 및 상기 단일 핀(552)의 제 1 및 제 2 측벽들(21, 22)은 실질적으로 같은 높이를 갖도록 형성할 수 있다.

도 2를 참조하면, 상기 트렌치를 채우는 소자분리막(56)을 형성한다. 상기 소자분리막(56)은 실리콘산화막과 같은 절연막으로 형성할 수 있다. 예를 들면, 상기 소자분리막(56)은 상기 트렌치를 채우고 상기 기판(51) 상을 덮는 절연막을 형성한

후, 상기 제 1 및 제 2 하드마스크패턴들(541, 542)의 상면 및 측벽들이 노출될 때 까지 상기 절연막을 에치백(etch back) 하여 형성할 수 있다. 상기 소자분리막(56)의 상면은 상기 예비 다중 핀(551)의 상면(13) 및 상기 단일 핀(552)의 상면(23) 과 실질적으로 동일 레벨을 이루도록 형성할 수 있다.

풀백(pull back)공정을 이용하여 제 1 및 제 2 하드마스크 축소패턴들(541', 542')을 형성한다. 상기 풀백(pull back)공정은 상기 제 1 및 제 2 하드마스크패턴들(541, 542)을 등방성식각하는 것을 포함할 수 있다. 예를 들면, 상기 풀백(pull back)공정은 상기 제 2 하드마스크 축소패턴(542')의 폭이 10nm 이하로 될 때 까지 수행할 수 있다. 상기 풀백(pull back) 공정이 수행되는 동안, 상기 제 1 및 제 2 하드마스크패턴들(541, 542)은 노출된 면적에 비례하여 균등한 비율로 식각될 수 있다.

이에 따라, 상기 제 1 하드마스크 축소패턴(541')은 상기 제 2 하드마스크 축소패턴(542') 보다 넓은 폭을 갖도록 형성할 수 있다. 이에 더하여, 상기 제 2 하드마스크패턴(542)은 완전히 제거할 수도 있다. 즉, 상기 풀백( $pull\ back$ )공정은 상기 제 2 하드마스크패턴(542)이 완전히 제거될 때 까지 수행할 수도 있다.

도 3을 참조하면, 상기 제 1 및 제 2 하드마스크 축소패턴들(541', 542')을 갖는 기판(51) 상에 희생막(59)을 형성한다. 상기 희생막(59)은 상기 제 1 및 제 2 하드마스크 축소패턴들(541', 542')의 상면들을 노출시키도록 형성할 수 있다.

구체적으로, 상기 희생막(59)은 상기 제 1 및 제 2 하드마스크 축소패턴들(541', 542')에 대하여 식각선택비를 갖는 물질 막을 상기 기판(51) 상에 형성한 후, 상기 물질막을 평탄화하여 형성할 수 있다. 상기 제 1 및 제 2 하드마스크 축소패턴들 (541', 542')이 상기 질화막인 경우, 상기 희생막(59)은 실리콘산화막으로 형성할 수 있다. 상기 물질막을 평탄화하는 것은 화학기계적연마(chemical mechanical polishing; CMP) 공정 또는 에치백(etch back)공정을 이용하여 수행할 수 있다.

도 4를 참조하면, 상기 희생막(59) 및 상기 제 1 및 제 2 하드마스크 축소패턴들(541', 542')을 패터닝하여 상기 핀들(551, 552)을 가로지르는 희생라인(60)을 형성한다. 상기 패터닝하는 것은 상기 희생막(59), 상기 제 1 및 제 2 하드마스크 축소패턴들(541', 542') 상에 포토레지스트패턴을 형성하고, 상기 포토레지스트패턴을 식각마스크로 이용하여 상기 희생막(59), 상기 제 1 및 제 2 하드마스크 축소패턴들(541', 542')을 이방성식각하는 것을 포함할 수 있다. 이 경우에, 상기 이방성식각은 상기 희생라인(60)의 양측에 상기 핀들(551, 552)의 상면들(13, 23)이 노출될 때 까지 수행할 수 있다.

그 결과, 상기 희생막(59) 및 상기 제 1 및 제 2 하드마스크 축소패턴들(541', 542')은 패터닝되어 희생패턴(59'), 제 1 및 제 2 희생마스크들(541", 542")이 형성될 수 있다. 상기 희생패턴(59'), 상기 제 1 및 제 2 희생마스크들(541", 542")은 상기 희생라인(60)을 구성할 수 있다. 즉, 상기 제 1 희생마스크(541")는 상기 예비 다중 핀(551) 상에 상기 희생패턴(59')을 분할하도록 잔존할 수 있다. 이와 마찬가지로, 상기 제 2 희생마스크(542")는 상기 단일 핀(552) 상에 상기 희생패턴(59')을 분할하도록 잔존할 수 있다.

한편, 상기 희생라인(60)을 형성하는 동안 상기 제 1 및 제 2 완충패턴들(531, 532) 또한 패터닝되어 제 1 및 제 2 희생완충패턴들(531', 532')이 형성될 수 있다. 상기 제 1 희생완충패턴(531')은 상기 예비 다중 핀(551) 및 상기 제 1 희생마스 크(541") 사이에 잔존할 수 있다. 상기 제 2 희생완충패턴(532')은 상기 단일 핀(552) 및 상기 제 2 희생마스크(542") 사이에 잔존할 수 있다.

도 5를 참조하면, 상기 핀들(551, 552)의 노출된 상면들(13, 23)을 덮는 보호막(61)을 형성한다. 상기 보호막(61)은 상기 제 1 및 제 2 희생마스크들(541", 542")에 대하여 식각선택비를 갖는 물질막으로 형성하는 것이 바람직하다. 상기 제 1 및 제 2 희생마스크들(541", 542")이 질화막인 경우 상기 보호막(61)은 실리콘산화막으로 형성할 수 있다.

상기 보호막(61)을 형성하는 것은 상기 희생라인(60)을 갖는 기판(51) 전면 상에 상기 실리콘산화막을 형성하고, 상기 제1 및 제2 희생마스크들(541", 542")의 상면들이 노출될 때 까지 상기 실리콘산화막을 평탄화하는 것을 포함할 수 있다. 이 경우에, 상기 보호막(61), 상기 희생패턴(59'), 및 상기 제1 및 제2 희생마스크들(541", 542")의 상면들은 실질적으로 동일평면 상에 노출될 수 있다.

도 6을 참조하면, 상기 제 1 및 제 2 희생마스크들(541", 542")을 선택적으로 제거하여 제 1 및 제 2 개구부들(541H, 542H)을 형성한다.

상기 제 1 및 제 2 희생마스크들(541", 542")은 상기 희생패턴(59') 및 상기 보호막(61)에 대하여 식각선택비를 갖는다. 그러므로 상기 제 1 및 제 2 개구부들(541H, 542H)은 상기 제 1 및 제 2 희생마스크들(541", 542")을 선택적으로 제거할 수있는 등방성식각 공정을 이용하여 수행할 수 있다.

그 결과, 상기 제 1 개구부(541H)의 바닥에는 상기 예비 다중 핀(551)의 상면(13)이 노출될 수 있다. 상기 제 1 희생완충 패턴(531')이 형성된 경우, 상기 제 1 개구부(541H)의 바닥에 상기 제 1 희생완충패턴(531')이 노출될 수도 있다. 이와 마찬가지로, 상기 제 2 개구부(542H)의 바닥에는 상기 단일 핀(552)의 상면(23)이 노출될 수 있다. 상기 제 2 희생완충패턴(532')이 형성된 경우, 상기 제 2 개구부(542H)의 바닥에 상기 제 2 희생완충패턴(532')이 노출될 수도 있다.

이어서, 상기 제 2 개구부(542H)를 채우고 상기 제 1 개구부(541H)의 내벽을 덮는 스페이서막을 형성할 수 있다. 상기 스페이서막은 상기 예비 다중 핀(551)에 대하여 식각선택비를 갖는 물질막으로 형성할 수 있다. 예를 들면, 상기 스페이서막은 실리콘산화막으로 형성할 수 있다. 상기 스페이서막을 이방성식각하여 희생플러그(542P) 및 스페이서(541S)를 형성할 수 있다. 상기 이방성식각은 상기 제 1 개구부(541H)의 바닥에 상기 예비 다중 핀(551)의 상면(13)이 노출될 때 까지 수행할 수 있다.

상기 스페이서(541S)를 형성하는 동안 상기 제 1 희생완충패턴(531') 또한 함께 식각될 수 있다. 상기 희생플러그(542P)는 상기 제 2 개구부(542H)를 완전히 채우도록 형성할 수 있다. 상기 보호막(61), 상기 희생패턴(59'), 상기 희생플러그(542P) 및 상기 스페이서(541S)의 상면들은 실질적으로 동일평면 상에 노출될 수 있다.

이와는 달리, 상기 제 1 하드마스크 축소패턴(541')을 형성하는 동안 상기 제 2 하드마스크패턴(542)을 완전히 제거한 경우, 상기 희생플러그(542P)는 생략될 수 있다. 이 경우에, 상기 단일 핀(552)은 상기 보호막(61) 및 상기 희생패턴(59')으로 덮일 수 있다.

여기서, 상기 보호막(61), 상기 희생패턴(59'), 상기 희생플러그(542P) 및 상기 스페이서(541S)는 다중채널마스크(66)를 구성할 수 있다. 상술한바와 같이, 상기 다중채널마스크(66)는 상기 예비 다중 핀(551)의 상면(13)을 부분적으로 노출시키는 상기 제 1 개구부(541H)를 구비할 수 있다. 상기 제 1 개구부(541H)는 상기 예비 다중 핀(551)의 가운데에 정렬될 수 있다.

도 7 및 도 8을 참조하면, 상기 예비 다중 핀(551)에 오목한 부분(641)을 형성하여 다중 핀(multi fin; 551')을 형성한다.

상기 오목한 부분(641)은 상기 다중채널마스크(66)를 식각마스크로 이용하여 상기 예비 다중 핀(551)을 이방성식각하여 형성할 수 있다. 상기 오목한 부분(641)은 상기 제 1 개구부(541H)의 하부에 형성될 수 있다. 이에 따라, 상기 오목한 부분(641)은 상기 다중 핀(551')의 가운데에 정렬될 수 있다. 또한, 상기 다중 핀(551')은 상기 오목한 부분(641)에 의하여 제 1 및 제 2 핀(F1, F2)으로 분할될 수 있다.

상술한 바와 같이, 상기 제 2 개구부(542H)는 상기 희생플러그(542P)에 의하여 완전히 채워진다. 이에 따라, 상기 이방성 식각이 수행되는 동안 상기 단일 핀(552)은 보호될 수 있다. 즉, 상기 오목한 부분(641)은 상기 다중 핀(551')에 선택적으로 형성될 수 있다.

도 9 및 도 10을 참조하면, 상기 다중 핀(551') 및 상기 단일 핀(552)을 노출시킨다.

구체적으로, 등방성식각 공정을 이용하여 상기 다중채널마스크(66)를 제거할 수 있다. 예를 들면, 상기 등방성식각 공정은 불산(hydro fluoric acid)을 함유하는 산화막 식각용액(oxide etchant)을 사용하여 수행할 수 있다. 상기 등방성식각 공정이 수행되는 동안, 상기 제 1 희생완충패턴(531') 및 상기 제 2 희생완충패턴(532') 또한 함께 제거될 수 있다. 또한, 상기 등방성식각 공정은 서로 다른 식각조건을 사용하여 2회 이상 나누어 수행할 수도 있다. 계속하여, 상기 소자분리막(56)을 식각하여 아래로 리세스 시킨다. 상기 소자분리막(56)의 식각 또한 상기 등방성식각 공정을 이용하여 수행할 수 있다.

그 결과, 상기 핀들(551', 552)의 상면들(13, 23) 보다 하부에 잔존하는 리세스된 소자분리막(56')이 형성될 수 있다. 즉, 상기 핀들(551', 552)의 측벽들(11, 12, 21, 22) 및 상면들(13, 23)을 노출시킬 수 있다. 또한, 상기 오목한 부분(641)에도 상기 다중 핀(551')의 제 3 측벽(15), 제 4 측벽(16) 및 바닥면(17)이 노출될 수 있다. 이 경우에, 상기 제 1 핀(F1)은 상기 제 1 측벽(11). 상기 제 3 측벽(15) 및 상기 상면(13)을 구비할 수 있으며, 상기 제 2 핀(F2)은 상기 제 2 측벽(12). 상기 제 4 측벽(16) 및 상기 상면(13)을 구비할 수 있다.

도 11 및 도 12를 참조하면, 상기 다중 핀(551') 및 상기 단일 핀(552) 상에 게이트유전막(71)을 형성한다. 상기 게이트유전막(71)은 실리콘산화막, 실리콘질화막, 실리콘산질화막, 고유전막(high-k dielectrics), 또는 이들의 조합막으로 형성할 수 있다. 상기 게이트유전막(71)은 상기 오목한 부분(641)의 내벽에도 형성될 수 있다.

상기 게이트유전막(71)을 갖는 기판(51) 상에 게이트도전막을 형성한다. 상기 게이트도전막은 폴리실리콘막 또는 금속막으로 형성할 수 있다. 상기 게이트도전막을 패터닝하여 상기 다중 핀(551')을 가로지르는 제 1 게이트전극(731) 및 상기단일 핀(552)을 가로지르는 제 2 게이트전극(732)을 형성한다.

상기 제 1 게이트전극(731)은 상기 다중 핀(551')의 측벽들(11, 12) 및 상면(13)을 덮도록 형성할 수 있다. 상기 게이트도 전막을 형성하는 동안, 상기 오목한 부분(641)에도 상기 게이트도전막으로 채워질 수 있다. 이에 따라, 상기 제 1 게이트전 극(731)은 상기 오목한 부분(641) 내부로 삽입된 게이트연장부(731E)를 갖도록 형성될 수 있다. 상기 게이트연장부(731E)는 상기 오목한 부분(641)을 완전히 채우도록 형성할 수 있다. 이 경우에, 상기 다중 핀(551')의 상기 제 3 측벽(15) 및 상기 제 4 측벽(16)은 유효채널 폭(effective channel width)을 연장해주는 역할을 할 수 있다.

상기 제 2 게이트전극(732)은 상기 단일 핀(552)의 측벽들(21, 22) 및 상면(23)을 덮도록 형성할 수 있다. 이와는 달리, 상기 제 2 게이트전극(732)은 상기 단일 핀(552)의 일 측벽만을 덮도록 형성할 수도 있다.

이후 상기 다중 핀(551') 및 상기 단일 핀(552) 내에 소스/드레인 영역들 형성과 같은 통상의 반도체제조공정을 이용하여 반도체소자를 완성할 수 있다.

상기 다중 핀(551'), 상기 게이트유전막(71) 및 상기 제 1 게이트전극(731)은 다중채널 전계효과트랜지스터를 구성할 수 있다. 또한, 상기 단일 핀(552), 상기 게이트유전막(71) 및 상기 제 2 게이트전극(732)은 핀 전계효과트랜지스터를 구성할 수 있다.

이제 도 11 및 도 12를 다시 참조하여 본 발명의 실시 예에 따른 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터 를 갖는 반도체소자를 설명하기로 한다.

도 11 및 도 12를 다시 참조하면, 기판(51) 상에 다중 핀(multi fin; 551') 및 단일 핀(single fin; 552)이 배치된다.

상기 기판(51)은 실리콘웨이퍼 또는 에스오아이(silicon on insulator; SOI) 웨이퍼와 같은 반도체기판일 수 있다. 상기 기판(51)은 제 1 영역(10) 및 제 2 영역(20)을 구비할 수 있다. 상기 제 1 영역(10)은 반도체소자의 주변회로 영역일 수 있고, 상기 제 2 영역(20)은 셀 영역일 수 있다. 또한, 상기 제 1 영역(10)은 에스램 셀(static random access memory cell; SRAM cell)의 풀다운 트랜지스터(pull-down transistor) 영역일 수 있고, 상기 제 2 영역(20)은 상기 에스램 셀(SRAM cell)의 패스 트랜지스터(pass transistor) 영역일 수 있다. 상기 다중 핀(551')은 상기 제 1 영역(10)에 배치될 수 있으며, 상기 단일 핀(552)은 상기 제 2 영역(20)에 배치될 수 있다.

상기 다중 핀(551')은 상기 기판(51)으로부터 돌출되고 그 내부에 오목한 부분(541)을 구비한다. 상기 오목한 부분(641)은 상기 다중 핀(551')의 가운데에 정렬될 수 있다. 상기 다중 핀(551')은 서로마주보는 제 1 및 제 2 측벽들(11, 12) 및 상면 (13)을 구비한다. 또한, 상기 다중 핀(551')은 상기 오목한 부분(641) 내부에 제 3 측벽(15), 제 4 측벽(16) 및 바닥면(17)을 구비한다.

상기 단일 핀(552)은 상기 기판(51)으로부터 돌출되고 상기 다중 핀(551') 보다 좁은 폭을 갖는다. 상기 단일 핀(552) 또한 제 1 및 제 2 측벽들(21, 22) 및 상면(23)을 구비한다.

상기 다중 핀(551')의 제 1 및 제 2 측벽들(11, 12), 및 상기 단일 핀(552)의 제 1 및 제 2 측벽들(21, 22)은 실질적으로 같은 높이를 갖는다. 즉, 상기 다중 핀(551') 및 상기 단일 핀(552)은 실질적으로 동일한 높이를 갖는다.

상기 다중 핀(551') 및 상기 단일 핀(552) 주변의 상기 기판(51) 상에 리세스된 소자분리막(56')이 제공될 수 있다. 상기 리세스된 소자분리막(56')은 의 상부면은 상기 핀들(fins; 551', 552)의 상면들(13, 23)보다 하부레벨에 위치할 수 있다. 상기리세스된 소자분리막(56')은 실리콘산화막과 같은 절연막일 수 있다.

상기 리세스된 소자분리막(56')을 갖는 기판(51) 상에 제 1 게이트전극(731) 및 제 2 게이트전극(732)이 제공된다. 상기 게이트전극들(731, 732)은 폴리실리콘막 또는 금속막일 수 있다. 상기 핀들(551', 552)과 상기 게이트전극들(731, 732) 사이에 게이트유전막(71)이 개재된다. 상기 게이트유전막(71)은 실리콘산화막, 실리콘질화막, 실리콘산질화막, 고유전막(high-k dielectrics), 또는 이들의 조합막일 수 있다.

상기 제 1 게이트전극(731)은 상기 다중 핀(551')을 가로지르도록 배치된다. 상기 제 1 게이트전극(731)은 상기 오목한 부분(641)의 내부에 삽입된 게이트연장부(731E)를 구비할 수 있다. 상기 게이트연장부(731E)는 상기 오목한 부분(641)의 내부를 완전히 채울 수 있다. 또한, 상기 제 1 게이트전극(731)은 상기 다중 핀(551')의 상기 제 1 및 제 2 측벽들(11, 12)을 덮도록 배치될 수 있다.

상기 제 2 게이트전극(732)은 상기 단일 핀(552)을 가로지르도록 배치된다. 또한, 상기 제 2 게이트전극(732)은 상기 단일 핀(552)의 상기 제 1 및 제 2 측벽들(21, 22)을 덮도록 배치될 수 있다.

도 13은 본 발명의 실시 예에 따른 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터를 갖는 시모스 에스램 셀 (CMOS SRAM cell)의 등가회로도이다.

도 13을 참조하면, 상기 시모스 에스램 셀은 한 쌍의 구동 트랜지스터들(a pair of driver transistors; TD1, TD2), 한 쌍의 전송 트랜지스터들(a pair of transfer transistors; TT1, TT2) 및 한 쌍의 부하 트랜지스터들(a pair of load transistors; TL1, TL2)를 구비한다. 상기 구동 트랜지스터들(TD1, TD2)은 풀다운 트랜지스터(pull-down transistor)라고 하고, 상기 전송 트랜지스터들(TT1, TT2)은 패스 트랜지스터(pass transistor)라고 하며, 상기 부하 트랜지스터들(TL1, TL2)은 풀업 트랜지스터(pull-up transistor)라고 하기도 한다. 상기 한 쌍의 구동 트랜지스터들(TD1, TD2) 및 상기 한 쌍의 전송 트랜지스터들(TT1, TT2)은 모두 NMOS 트랜지스터들인 반면에, 상기 한 쌍의 부하 트랜지스터들(TL1, TL2)은 모두 PMOS 트랜지스터들이다.

상기 제1 구동 트랜지스터(TD1)와 상기 제1 전송 트랜지스터(TT1)는 서로 직렬 연결된다. 상기 제1 구동 트랜지스터 (TD1)의 소스 영역은 접지선(ground line; Vss)에 전기적으로 연결되고, 상기 제1 전송 트랜지스터(TT1)의 드레인 영역은 제1 비트라인(BL1)에 전기적으로 연결된다. 이와 마찬가지로, 상기 제2 구동 트랜지스터(TD2)와 상기 제2 전송 트랜지스터(TT2) 또한 서로 직렬 연결된다. 상기 제2 구동 트랜지스터(TD2)의 소스 영역은 상기 접지선(Vss)에 전기적으로 연결되고, 상기 제2 전송 트랜지스터(TT2)의 드레인 영역은 제2 비트라인(BL2)에 전기적으로 연결된다.

한편, 상기 제1 부하 트랜지스터(TL1)의 소스 영역 및 드레인 영역은 각각 전원선(power supply line; Vcc) 및 상기 제1 구동 트랜지스터(TD1)의 드레인 영역에 전기적으로 연결된다. 이와 마찬가지로, 상기 제2 부하 트랜지스터(TL2)의 소스 영역 및 드레인 영역 또한 각각 상기 전원선(Vcc) 및 상기 제2 구동 트랜지스터(TD2)의 드레인 영역에 전기적으로 연결된다. 상기 제1 부하 트랜지스터(TL1)의 드레인 영역, 상기 제1 구동 트랜지스터(TD1)의 드레인 영역 및 상기 제1 전송 트랜지스터(TT1)의 소스 영역은 제1 노드(N1)에 해당한다. 또한, 상기 제2 부하 트랜지스터(TL2)의 드레인 영역, 상기 제2 구동 트랜지스터(TD2)의 드레인 영역 및 상기 제2 전송 트랜지스터(TT2)의 소스 영역은 제2 노드(N2)에 해당한다. 상기제1 구동 트랜지스터(TD1)의 게이트 전극 및 상기 제1 부하 트랜지스터(TL1)의 게이트 전극은 상기 제2 노드(N2)에 전기적으로 연결되고, 상기 제2 구동 트랜지스터(TD2)의 게이트 전극 및 상기 제2 부하 트랜지스터(TL2)의 게이트 전극은 상기제1 노드(N1)에 전기적으로 연결된다. 또한, 상기 제1 및 제2 전송 트랜지스터들(TT1, TT2)의 게이트 전극들은 위드라인(WL)에 전기적으로 접속된다.

상기 제1 구동 트랜지스터(TD1), 상기 제1 전송 트랜지스터(TT1) 및 상기 제1 부하 트랜지스터(TL1)는 제1 하프 셀(H1)을 구성하고, 상기 제2 구동 트랜지스터(TD2), 상기 제2 전송 트랜지스터(TT2) 및 상기 제2 부하 트랜지스터(TL2)는 제 2 하프 셀(H2)을 구성한다.

한편, 상기 전송 트랜지스터들(TT1, TT2)을 흐르는 온 전류(on current)는 Ips로 표시할 수 있으며, 상기 구동 트랜지스터들(TD1, TD2)을 흐르는 온 전류(on current)는 Ipd로 표시할 수 있다. 또한, 상기 Ipd를 상기 Ips로 나눈 값은 셀 레이시오(cell ratio)로 표시할 수 있다. 상기 시모스 에스램 셀은 상기 셀 레이시오(cell ratio)가 1 이상일 때 우수한 전기적 특성을 보인다. 예를 들면, 상기 시모스 에스램 셀은 상기 셀 레이시오(cell ratio)가 1.2 이상인 것이 요구되기도 한다.

도 11, 도 12 및 도 13을 다시 참조하면, 상기 다중 핀(551'), 상기 게이트유전막(71) 및 상기 제 1 게이트전극(731)은 다중 채널 전계효과트랜지스터를 구성할 수 있다. 또한, 상기 단일 핀(552), 상기 게이트유전막(71) 및 상기 제 2 게이트전극(732)은 핀 전계효과트랜지스터를 구성할 수 있다. 상기 다중 핀(551')의 상기 제 3 측벽(15) 및 상기 제 4 측벽(16)은 유효채널 폭(effective channel width)을 연장해주는 역할을 할 수 있다.

일반적으로, 전계효과트랜지스터의 온 전류(on current)는 상기 유효채널 폭(effective channel width)에 비례하여 증가한다. 상기 다중채널 전계효과트랜지스터는 상기 구동 트랜지스터들(TD1, TD2)의 역할을 하도록 배치할 수 있다. 상기

핀 전계효과트랜지스터는 상기 전송 트랜지스터들(TT1, TT2)의 역할을 하도록 배치할 수 있다. 이 경우에, 상기 셀 레이시오(cell ratio)는 1 이상을 얻을 수 있다. 본 발명에 따르면, 상기 다중채널 전계효과트랜지스터 및 상기 핀 전계효과트랜지스터를 동시에 하나의 기판 상에 형성할 수 있다. 즉, 우수한 전기적 특성을 갖는 시모스 에스램 셀을 구현할 수 있다.

본 발명은 상술한 실시 예들에 한정되지 않고 본 발명의 사상 내에서 여러 가지의 다른 형태로 변형될 수 있다. 예를 들면, 본 발명은 디램(DRAM), 에스램(SRAM), 또는 다른 반도체소자 및 그 제조방법에도 적용될 수 있다.

#### 발명의 효과

상술한 바와 같이 본 발명에 따르면, 다중 핀(multi fin) 및 단일 핀(single fin)을 하나의 기판 상에 동시에 형성할 수 있다. 이에 따라, 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터를 한꺼번에 형성할 수 있다. 즉, 서로 다른 온 전류(on current)를 갖는 전계효과트랜지스터들을 동시에 형성할 수 있다. 결과적으로, 우수한 전기적 특성을 갖는 반도체소자의 양산효율을 극대화 할 수 있다.

#### 도면의 간단한 설명

도 1 내지 도 7, 도 9 및 도 11은 본 발명의 실시 예에 따른 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터를 갖는 반도체소자의 제조방법을 설명하기 위한 사시도들이다.

도 8은 도 7의 절단선 I-I'에 따라 취해진 단면도이다.

도 10은 도 9의 절단선 I-I'에 따라 취해진 단면도이다.

도 12는 도 11의 절단선 I-I'에 따라 취해진 단면도이다.

도 13은 본 발명의 실시 예에 따른 다중채널 전계효과트랜지스터 및 핀 전계효과트랜지스터를 갖는 시모스 에스램 셀 (CMOS SRAM cell)의 등가회로도이다.

#### 도면

# 五型1 542 532 541 531 552 11 12 551 551

도면3

도면5

도면9

도면10

도면12