(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4829015号 (P4829015)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月22日(2011.9.22)

(51) Int. Cl. FL

HO1L 21/8247 (2006, 01) HO1L 29/788 (2006, 01)

HO1L 29/792 (2006.01) HO1L 27/115 (2006, 01) HO1L 29/78 371 HO1L 27/10 434

> 請求項の数 10 (全 22 頁)

特願2006-170225 (P2006-170225) (21) 出願番号 (22) 出願日 平成18年6月20日 (2006.6.20)

(65) 公開番号 特開2008-4622 (P2008-4622A)

(43) 公開日 平成20年1月10日 (2008.1.10) 平成20年8月29日 (2008.8.29) 審査請求日

||(73)特許権者 000003078 株式会社東芝

東京都港区芝浦一丁目1番1号

||(74)代理人 100091351

弁理士 河野 哲

||(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100108855

弁理士 蔵田 昌俊

||(74)代理人 100075672

弁理士 峰 隆司

|(74)代理人 100109830|

弁理士 福原 淑弘

|(74)代理人 100084618

弁理士 村松 貞男

最終頁に続く

## (54) 【発明の名称】不揮発性半導体記憶装置

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板と、

前記半導体基板を複数の素子領域に分離する素子分離領域と、

素子領域上に、それぞれ、第1の絶縁膜を介して形成された複数の浮遊ゲート電極と、 前記複数の浮遊ゲート電極上にそれぞれ第2の絶縁膜を介して設けられ、その一部が、 互いに対向する前記複数の浮遊ゲート電極間に埋め込まれた制御ゲート電極と

#### を具備し、

前記複数の浮遊ゲート電極は、それぞれ、上部のチャネル幅方向の幅が下部のチャネル 幅方向の幅よりも短く、かつ、少なくとも互いに対向する側の側面が、前記第2の絶縁膜 に接する第1の面と、前記素子分離領域と接する第2の面とを有して形成され、前記第1 の面は、その一端が素子分離絶縁膜と接する第1接面と、前記第1接面の他端と接する第 2接面とからなり、

前記第2の絶縁膜は、垂直方向の最大膜厚が、前記第2の絶縁膜の最下面から最上面ま での垂直方向の距離よりも小さく、前記複数の浮遊ゲート電極は、前記第2接面と前記第 2の面との間に段差を有し、前記第1接面の端部と前記第2の面の端部との高さは等しい ことを特徴とする不揮発性半導体記憶装置。

### 【請求項2】

半導体基板と、

前記半導体基板を複数の素子領域に分離する素子分離領域と、

素子領域上に、それぞれ、第1の絶縁膜を介して形成された複数の浮遊ゲート電極と、前記複数の浮遊ゲート電極上にそれぞれ第2の絶縁膜を介して設けられ、その一部が、 互いに対向する前記複数の浮遊ゲート電極間に埋め込まれた制御ゲート電極と を具備し、

前記複数の浮遊ゲート電極は、それぞれ、上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短く、かつ、少なくとも互いに対向する側の側面が、前記第2の絶縁膜に接する第1の面と、前記素子分離領域と接する第2の面とを有して形成され、前記第1の面は、その一端が素子分離絶縁膜と接する第1接面と、前記第1接面の他端と接する第2接面とからなり、

前記複数の浮遊ゲート電極は、前記第<u>2接</u>面と前<u>記第</u>2<u>の面</u>との間に段差を有し、前記第1接面の端部と前記第2の面の端部との高さは等しく、

前記<u>第2接</u>面と垂直方向とのなす第1の角が、前記第2<u>の面</u>と垂直方向とのなす第2の 角よりも大きいことを特徴とする不揮発性半導体記憶装置。

## 【請求項3】

半導体基板と、

前記半導体基板を複数の素子領域に分離する素子分離領域と、

素子領域上に、それぞれ、第1の絶縁膜を介して形成された複数の浮遊ゲート電極と、 前記複数の浮遊ゲート電極上にそれぞれ第2の絶縁膜を介して設けられ、その一部が、 互いに対向する前記複数の浮遊ゲート電極間に埋め込まれた制御ゲート電極と

を具備し、

前記複数の浮遊ゲート電極は、それぞれ、上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短く、かつ、少なくとも互いに対向する側の側面が、前記第2の絶縁膜に接する第1の面と、前記素子分離領域と接する第2の面とを有して形成され、前記第1の面は、その一端が素子分離絶縁膜と接する第1接面と、前記第1接面の他端と接する曲面である第2接面とからなり、

前記複数の浮遊ゲート電極は、前記第<u>2接</u>面と前<u>記第</u>2<u>の面</u>との間に段差を有し、前記第<u>1接</u>面の端部と前記第2<u>の面</u>の端部との高さは等しいことを特徴とする不揮発性半導体記憶装置。

## 【請求項4】

半導体基板と、

前記半導体基板を複数の素子領域に分離する素子分離領域と、

素子領域上に、それぞれ、第1の絶縁膜を介して形成された複数の浮遊ゲート電極と、 前記複数の浮遊ゲート電極上にそれぞれ第2の絶縁膜を介して設けられ、その一部が、 互いに対向する前記複数の浮遊ゲート電極間に埋め込まれた制御ゲート電極と

を具備し、

前記複数の浮遊ゲート電極は、それぞれ、上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短く、上面が曲面で構成され、かつ、下面が平面で構成され、少なくとも互いに対向する側の面が第1の面と、前記素子分離領域と接する第2の面とを有して形成され、前記第1の面は、その一端が素子分離絶縁膜と接する第1接面と、前記第1接面の他端と接する曲面である第2接面とからなり、

前記複数の浮遊ゲート電極は、前記第<u>2接</u>面と前<u>記第</u>2<u>の面</u>との間に段差を有し、前記第<u>1接</u>面の端部と前記第2<u>の面</u>の端部との高さは等しいことを特徴とする不揮発性半導体記憶装置。

## 【請求項5】

前記複数の浮遊ゲート電極は、それぞれ、互いに対向する浮遊ゲート電極間の最小間隔が、前記第2の絶縁膜の膜厚を2倍にした値と前記制御ゲート電極が空乏化する距離とを足し合わせた値よりも小さいことを特徴とする請求項1,2,3,4のいずれかに記載の不揮発性半導体記憶装置。

### 【請求項6】

前記第2の絶縁膜は、垂直方向の最大膜厚が、前記第2の絶縁膜の最下面から最上面ま

10

20

40

50

での垂直方向の距離よりも小さいことを特徴とする請求項2,3,4のいずれかに記載の不揮発性半導体記憶装置。

#### 【請求項7】

\_\_前記<u>第2接面</u>と垂直方向とのなす第1の角が、前記第2<u>の面</u>と垂直方向とのなす第2の 角よりも大きいことを特徴とする請求項3,4のいずれかに記載の不揮発性半導体記憶装 置。

#### 【請求項8】

前記第2の角が0度であることを特徴とする請求項2,7のいずれかに記載の不揮発性 半導体記憶装置。

## 【請求項9】

前記曲面は、上に凸形状を有することを特徴とする請求項3に記載の不揮発性半導体記憶装置。

#### 【請求項10】

前記曲面は、下に凸形状を有することを特徴とする請求項3に記載の不揮発性半導体記憶装置。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、不揮発性半導体記憶装置に関するもので、特に、浮遊ゲート電極と制御ゲート電極とからなる二層ゲート電極を有してメモリセルが構成されてなる不揮発性半導体記憶装置に関する。

#### 【背景技術】

### [0002]

メモリセルが浮遊ゲート電極と制御ゲート電極とからなる二層ゲート電極を有して構成されてなる不揮発性半導体記憶装置の例として、NAND型の不揮発性半導体記憶装置が知られている。NAND型の不揮発性半導体記憶装置は、直列に接続された複数のメモリセルと、この直列に接続されたメモリセル列のドレイン側およびソース側にそれぞれ接続された選択トランジスタとによって構成されている。また、各選択トランジスタに隣接して、ビット線に電気的に接続されたビット線コンタクト電極とソース線に電気的に接続されたソース線コンタクト電極とが配置されている。

#### [0003]

各メモリセルは、上述したように、浮遊ゲート電極上にゲート間絶縁膜を介して制御ゲート電極が積層されてなる、二層ゲート電極を有して構成されている。制御ゲート電極によって構成されるワード線に沿う方向(チャネル幅方向:チャネル電流が流れる方向と直交する方向)においては、互いに対向する浮遊ゲート電極間に、ゲート間絶縁膜を介して、制御ゲート電極の一部が埋め込まれて、メモリセルのカップリング比が確保されている

#### [0004]

しかしながら、メモリセルの微細化によって、たとえば、浮遊ゲート電極間の距離がゲート間絶縁膜の膜厚の 2 倍よりも小さくなると、浮遊ゲート電極間がゲート間絶縁膜のみによって埋め込まれることになる。すると、浮遊ゲート電極と制御ゲート電極との間の容量が低下し、メモリセルのカップリング比を確保できなくなって、メモリセルの特性が劣化するという問題があった。

## [0005]

特に、制御ゲート電極がシリコンによって形成されている場合、浮遊ゲート電極間に埋め込まれた制御ゲート電極の幅が小さくなりやすく、メモリセルの動作時に完全に空乏化してしまうと、浮遊ゲート電極と制御ゲート電極との間の容量が低下し、メモリセルのカップリング比を確保できなくなって、メモリセルの特性が劣化するという問題があった。

### [0006]

なお、フローティングゲート電極の幅方向に沿った断面を凸型形状とし、フローティン

10

20

30

40

グゲート電極間の容量を低減してしきい値変動を抑制できるようにした積層ゲート型の半 導体メモリがすでに提案されている(たとえば、特許文献 1 参照)。しかしながら、この 提案の場合、フローティングゲート電極の段差が、フローティングゲート電極間に埋め込 まれたゲート間絶縁膜のエッチングを困難にするという問題があった。

【特許文献1】特開2004-022819

【発明の開示】

【発明が解決しようとする課題】

### [0007]

本発明は、上記の問題点を解決すべくなされたもので、メモリセルのカップリング比が低下するのを抑制でき、メモリセルの特性を向上させることが可能な不揮発性半導体記憶装置を提供することを目的としている。

【課題を解決するための手段】

#### [00008]

本願発明の一態様によれば、半導体基板と、前記半導体基板を複数の素子領域に分離する素子分離領域と、素子領域上に、それぞれ、第1の絶縁膜を介して形成された複数の浮遊ゲート電極と、前記複数の浮遊ゲート電極上にそれぞれ第2の絶縁膜を介して設けられ、その一部が、互いに対向する前記複数の浮遊ゲート電極間に埋め込まれた制御ゲート電極とを具備し、前記複数の浮遊ゲート電極は、それぞれ、上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短く、かつ、少なくとも互いに対向する側の側面が、前記第2の絶縁膜に接する第1の面と、前記素子分離領域と接する第2の面とを有して形成され、前記第1の面は、その一端が素子分離絶縁膜と接する第1接面と、前記第1接面の他端と接する第2接面とからなり、前記第2の絶縁膜は、垂直方向の最大膜厚が、前記第2の絶縁膜の最下面から最上面までの垂直方向の距離よりも小さく、前記複数の浮遊ゲート電極は、前記第2接面と前記第2の面との間に段差を有し、前記第1接面の端部と前記第2の面の端部との高さは等しいことを特徴とする不揮発性半導体記憶装置が提供される。

## 【発明の効果】

## [0009]

上記の構成により、メモリセルのカップリング比が低下するのを抑制でき、メモリセルの特性を向上させることが可能な不揮発性半導体記憶装置を提供できる。

【発明を実施するための最良の形態】

## [0010]

以下、本発明の実施の形態について図面を参照して説明する。ただし、図面は模式的なものであり、各図面の寸法や比率などは現実のものとは異なることに留意すべきである。また、図面の相互間においても、互いの寸法の関係や比率が異なる部分が含まれていることは勿論である。特に、以下に示すいくつかの実施の形態は、本発明の技術思想を具体化するための装置や方法を例示したものであって、構成部品の形状、構造、配置などによって、本発明の技術思想が特定されるものではない。この発明の技術的思想は、その要旨を逸脱しない範囲において、種々の変更を加えることができる。

### [0011]

## [第1の実施形態]

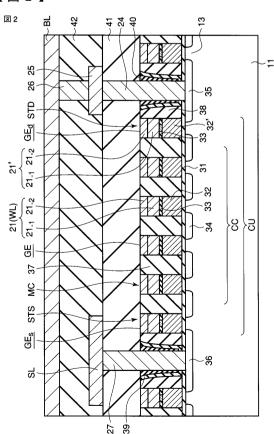

図1は、本発明の第1の実施形態にしたがった、不揮発性半導体記憶装置の基本構成を示すものである。なお、ここでは、浮遊ゲート電極と制御ゲート電極とからなる二層ゲート電極を有してメモリセルが構成されてなる不揮発性半導体記憶装置の例として、NAND型の不揮発性半導体記憶装置に適用した場合について説明する。また、メモリセル列におけるメモリセルの個数を「4」とした場合の例である。

### [0012]

図1に示すように、このNAND型の不揮発性半導体記憶装置は、複数のNANDセルユニットCUを有して構成されている。各NANDセルユニットCUは、半導体基板(たとえば、シリコン基板)11上の素子分離領域12によって区分された素子領域13にお

10

20

30

40

いて、直列に接続された4個のメモリセルMCからなるメモリセル列CCに、ドレイン側選択トランジスタSTDとソース側選択トランジスタSTSとが接続された構成となっている。

#### [0013]

図1の、左右方向であるワード線に沿う方向に配列された複数(この例では、2つ)のメモリセルMCは、それぞれ、共通の制御ゲート線(ワード線WL)21に接続されている。ドレイン側選択トランジスタSTDおよびソース側選択トランジスタSTSは、それぞれ、共通のドレイン側選択ゲート線22および共通のソース側選択ゲート線23に接続されている。ドレイン側選択トランジスタSTDには、ビット線コンタクト24を介して、第1配線層からなるビット線接続部25が接続され、さらに、配線間コンタクト26を介して、第2層配線からなるビット線BLが接続されている。ソース側選択トランジスタSTSには、ソース線コンタクト27を介して、第1配線層からなるソース線SLが接続されている。

## [0014]

本実施形態の場合、4個のメモリセルMCと、ドレイン側選択トランジスタSTDと、ソース側選択トランジスタSTSとによって1つのNANDセルユニットCUが構成され、このような構成の複数のNANDセルユニットCUが、ビット線コンタクト24およびソース線コンタクト27を介して、ビット線方向に互いに隣接して配置されて1つのメモリセルアレイMCAが実現されている。

## [0015]

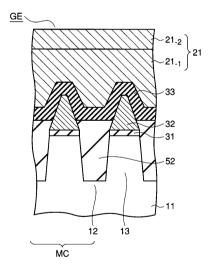

図2は、図1のII・II線に沿った、NAND型の不揮発性半導体記憶装置の断面構造を示すものである。図2に示すように、1つのNANDセルユニットCUにおける4個のメモリセルMCは、半導体基板11のウェル領域(図示していない)上に形成された素子領域13に、ゲート絶縁膜(第1の絶縁膜)31を介して設けられたメモリセルゲート電極GEを有している。各メモリセルゲート電極GEは、電荷蓄積層となる浮遊ゲート電極32、浮遊ゲート電極32上に形成されたゲート間絶縁膜(第2の絶縁膜)33、ゲート間絶縁膜33上に形成された制御ゲート電極21を有している。制御ゲート電極21は、シリコン層21-1とシリサイド層21-2との積層膜によって形成されている。シリサイド層21-2には、たとえばコバルトシリサイドを利用できる。制御ゲート電極21は、他のメモリセルMCとの間でそれぞれ共有されてワード線WLとなっている。

#### [0016]

なお、4個のメモリセルMCは、素子領域13上に設けられたソースおよびドレインとなる拡散層領域34を介して、互いに直列に接続されている。

#### [0017]

さらに、4個のメモリセルMCの一端(この例の場合、右端)には、ドレイン側選択トランジスタSTDのゲート電極GEdが配置されている。このゲート電極GEdは、ゲート絶縁膜31を介して、上記半導体基板11の素子領域13上に形成されている。ドレイン側選択トランジスタSTDのゲート電極GEdの、メモリセルMCと反対側の素子領域13には、ビット線コンタクト拡散層35が形成されている。

## [0018]

また、4個のメモリセルMCの他端(この例の場合、左端)には、ソース側選択トランジスタSTSのゲート電極GEsが配置されている。このゲート電極GEsは、ゲート絶縁膜31を介して、上記半導体基盤1の素子領域13上に形成されている。ソース側選択トランジスタSTSのゲート電極GEsの、メモリセルMCと反対側の素子領域13には、ソース線コンタクト拡散層36が形成されている。

## [0019]

ここで、ドレイン側選択トランジスタSTDのゲート電極GEdおよびソース側選択トランジスタSTSのゲート電極GEsは、ゲート間絶縁膜33の一部が除去されて、上記浮遊ゲート電極32に対応する第1の制御ゲート電極32′と上記制御ゲート電極21に対応する第2の制御ゲート電極21′とが電気的に接続されている。第2の制御ゲート電

10

20

30

40

20

30

40

50

極 2 1 ' は、上記シリコン層 2 1 -1と上記シリサイド層 2 1 -2との積層膜によって形成されている。

## [0020]

すなわち、メモリセルゲート電極GEと、その両端の素子領域13に設けられた拡散層34とで、メモリセルMCが構成されている。また、ドレイン側選択トランジスタSTDのゲート電極GEdと、そのメモリセルMC側の素子領域13に設けられた拡散層11と、ビット線コンタクト拡散層35とによって、ドレイン側選択トランジスタSTDが構成されている。さらに、ソース側選択トランジスタSTSのゲート電極GEsと、そのメモリセルMC側の素子領域13に設けられた拡散層34と、ソース線コンタクト拡散層36とによって、ソース側選択トランジスタSTSが構成されている。

[0021]

このように、4個のメモリセルMCが、拡散層34により互いにコンタクトなしで直列に接続されて、メモリセル列CCが構成されている。そして、メモリセル列CCの各端に、拡散層34を介して、ドレイン側選択トランジスタSTDとソース側選択トランジスタSTSとが接続されて、NANDセルユニットCUが構成されている。

[0022]

メモリセルゲート電極GEの相互間、および、メモリセルゲート電極GEとドレイン側選択トランジスタSTDのゲート電極GEdおよびソース側選択トランジスタSTSのゲート電極GEsとの間には、たとえば酸化シリコン膜からなる絶縁膜37が形成されている。ドレイン側選択トランジスタSTDのゲート電極GEdおよびソース側選択トランジスタSTSのゲート電極GEsの、メモリセルゲート電極GEと反対側の側面には、絶縁膜(たとえば、酸化シリコン膜)38が形成され、絶縁膜38上には絶縁膜39が形成されている。絶縁膜39は、絶縁膜38とはエッチングレートが異なる膜、たとえば、シリコン窒化膜を利用できる。絶縁膜39上には、絶縁膜40が設けられている。絶縁膜40は、たとえばBPSG膜(ホウ素を含むシリコン酸化膜)により形成できる。

[0023]

絶縁膜37,38,39,40およびゲート電極GE,GEd,GEs上には、層間絶縁膜41が設けられている。層間絶縁膜41は、たとえばTEOS膜(Tetra Ethoxy Silane膜)により形成できる。

[0024]

層間絶縁膜41、絶縁膜38,39,40、および、ゲート絶縁膜31を貫いて、ビット線コンタクト電極24とソース線コンタクト電極27とが設けられている。ビット線コンタクト電極27は、それぞれ、ビット線コンタクト拡散層35およびソース線コンタクト拡散層36に接続されている。

[0025]

ビット線コンタクト電極 2 4 上には、第 1 配線層からなるビット線接続部 2 5 が設けられ、さらに、配線間コンタクト 2 6 を介して、第 2 配線層からなるビット線 B L が設けられている。ソース線コンタクト電極 2 7 上には、第 1 配線層からなるソース線 S L が設けられている。このソース線 S L、ビット線接続部 2 5 および配線間コンタクト 2 6 は、配線間絶縁膜 4 2 で覆われて、その上に、ビット線 B L が形成されている。

[0026]

NANDセルユニットCUのメモリセル列CCは、ここでは4個のメモリセルMCが選択トランジスタSTD,STSに挟まれた形で形成されているが、メモリセルMCの個数は4個に限定されるものではなく、たとえば16個または32個など、任意の数で形成できる。

[0027]

なお、ウェル領域をP型とした場合、各拡散層34,35,36はN型であり、ウェル領域をN型とした場合、各拡散層34,35,36はP型となる。

[0028]

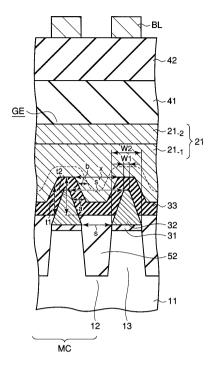

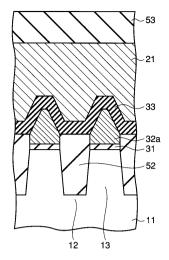

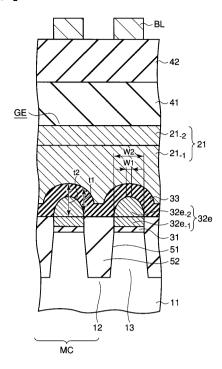

図3は、図1のIII-III線に沿った、NAND型の不揮発性半導体記憶装置の断面構造

を示すものである。図3に示すように、半導体基板11のウェル領域中に素子分離領域1 2が設けられ、この素子分離領域12によって素子領域13が画定されている。そして、この素子領域13上に、ゲート絶縁膜31を介して、メモリセルMCのメモリセルゲート電極GEが形成されている。

### [0029]

すなわち、ゲート絶縁膜31上に浮遊ゲート電極32が設けられ、その浮遊ゲート電極32の上面および側面上に形成されたゲート間絶縁膜33を介して、制御ゲート電極21が形成されている。シリコン層21-1とシリサイド層21-2との積層膜からなる制御ゲート電極21は、その一部である上記シリコン層21-1が、互いに対向する浮遊ゲート電極32間に埋め込まれている。

### [0030]

制御ゲート電極 2 1 上には層間絶縁膜 4 1 が設けられており、その層間絶縁膜 4 1 上には配線間絶縁膜 4 2 が設けられている。この配線間絶縁膜 4 2 上には、ビット線 B L が設けられている。

#### [0031]

なお、本実施形態の場合、素子分離の方法としてSTI(Shallow Trench Isolation)構造を用いているが、LOCOS(Local Oxidation of Silicon)など、別の方法を用いてもよい。

#### [0032]

ここで、本実施形態のNAND型の不揮発性半導体記憶装置においては、浮遊ゲート電極32の上部のチャネル幅方向の幅W1が、下部のチャネル幅方向の幅W2よりも短くなっている。すなわち、浮遊ゲート電極32は、たとえば図3に示すように、チャネル幅方向の断面において、上部のチャネル幅方向の幅W1が下部のチャネル幅方向の幅W2よりも短く、かつ、少なくともゲート間絶縁膜33に接する各側面が1つの平面からなる台形形状を有して形成されている。これにより、制御ゲート電極21の一部が、互いに対向する浮遊ゲート電極32間に十分に埋め込まれるようになる。したがって、メモリセルMCのカップリング比の低下を防止することが可能となり、微細化にともなってメモリセルMCの特性が劣化するのを防止できるようになるものである。

## [0033]

このとき、互いに対向する浮遊ゲート電極32間に埋め込まれている制御ゲート電極21の幅(最大幅×)は、制御ゲート電極21がゲート間絶縁膜33との界面において空乏化する距離(b)の2倍よりも大きくなるようにする(x>2b)。制御ゲート電極21がシリコンによって形成される場合、その空乏化する距離(b)は、形成条件および動作条件によっても異なるが、通常は最大で3nm程度である。すなわち、浮遊ゲート電極32は、たとえば、互いに対向する浮遊ゲート電極32間の最小間隔(S)が、ゲート間絶縁膜33の膜厚(a)を2倍にした値と制御ゲート電極21が空乏化する距離(b)とを足し合わせた値よりも小さく(S<2(a+b))、かつ、互いに対向する浮遊ゲート電極32間の最大間隔(S')が、ゲート間絶縁膜33の膜厚(a)を2倍にした値と制御ゲート電極21が空乏化する距離(b)とを足し合わせた値よりも大きく(S'>2(a+b))なるように、それぞれ形成されている。

## [0034]

ただし、制御ゲート電極 2 1 がシリコン層 2 1 -1とシリサイド層 2 1 -2との積層膜でなく、完全にシリサイド化されている場合または金属で形成されている場合には、互いに対向する浮遊ゲート電極 3 2 間に埋め込まれる制御ゲート電極 2 1 の幅 (x)は、制御ゲート電極 2 1 がゲート間絶縁膜 3 3 との界面において空乏化する距離 (b)の 2 倍よりも大きくする必要はない。

#### [0035]

本実施形態の場合、浮遊ゲート電極32の側面を平面によって構成するようにしているため、1回のエッチング工程により加工することが可能であり、工程数を増加させることなしに形成することができる。

10

20

30

40

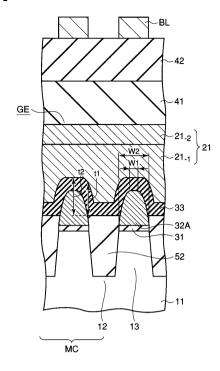

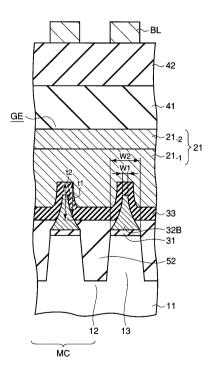

#### [0036]

なお、浮遊ゲート電極の側面は、たとえば図4に示すように、上に凸形状を有するような外側に湾曲した曲面を備えてなる構成(32A)としてもよいし、たとえば図5に示すように、下に凸形状を有するような内側に湾曲した曲面を備えてなる構成(32B)としてもよい。つまり、段差のない形状であれば、工程数を増加させたりすることなく、制御性よく形成することが可能である。

### [0037]

特に、上記した浮遊ゲート電極32,32A,32Bのように、上部のチャネル幅方向の幅W1が、下部のチャネル幅方向の幅W2よりも短い構造においては、メモリセルゲート電極GEの加工時に、浮遊ゲート電極32,32A,32Bの側面のゲート間絶縁膜33を完全に除去することが可能となる。すなわち、本実施形態の構成によれば、浮遊ゲート電極32,32A,32Bの側面に形成されたゲート間絶縁膜33の垂直方向の膜厚(最大膜厚)t1が、ゲート間絶縁膜33の最下面から最上面までの垂直方向の距離t2よりも小さくなることから、ゲート間絶縁膜33の加工を容易にしつつ、上記の効果を得ることができる。

#### [0038]

以下に、図6~図10を参照して、上記した構成のNAND型の不揮発性半導体記憶装置の製造方法について簡単に説明する。各図は、それぞれ図1のIII-III線に沿う断面を示すものである。ここでは、図3に示した構造の浮遊ゲート電極32を形成する場合を例に説明する。

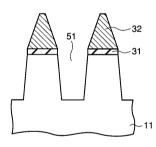

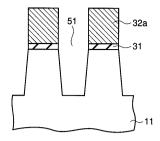

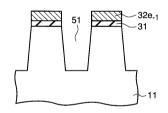

#### [0039]

まず、たとえば図6に示すように、半導体基板11の表面部にウェル領域およびチャネル領域(いずれも図示していない)を形成した後、全面にゲート絶縁膜31を形成する。次に、ゲート絶縁膜31上に浮遊ゲート電極32となる多結晶シリコンを堆積した後、リソグラフィー法により、順次、浮遊ゲート電極32、ゲート絶縁膜31、および、半導体基板11をエッチングして、半導体基板11の表面部に溝部51を形成する。このとき、浮遊ゲート電極32の上部のチャネル幅方向の幅W1が下部のチャネル幅方向の幅W2よりも短くなるようにするために、エッチングの条件として、たとえばHBr/O2系ガスを用い、圧力を50mTorr以上、バイアスを100W以下に設定する。

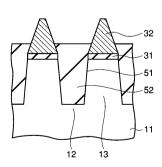

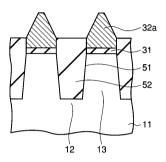

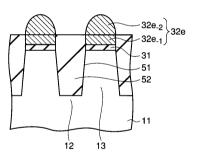

## [0040]

次に、たとえば図7に示すように、溝部51内にシリコン酸化膜からなる素子分離絶縁膜52を埋め込んだ後、適当な高さまで素子分離絶縁膜52をエッチバックして、素子分離領域12を形成するとともに、その素子分離領域12によって画定された素子領域13を形成する。

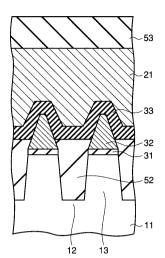

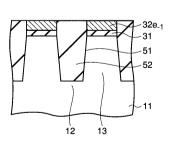

## [0041]

次に、たとえば図8に示すように、浮遊ゲート電極32上および素子分離領域12上に、順次、ゲート間絶縁膜(たとえば、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の積層膜)33、多結晶シリコンからなる制御ゲート電極21、および、シリコン窒化膜からなるゲートマスク材53を形成する。このとき、選択トランジスタSTD,STSのゲート電極GEd,GEsを形成する部分(領域)では、一部のゲート間絶縁膜33を除去し、浮遊ゲート電極32に対応する第1の制御ゲート電極32°と制御ゲート電極21に対応する第2の制御ゲート電極21°とが電気的に接続されるようにする。

## [0042]

次に、フォトリソグラフィー法によってゲートマスク材53をエッチングし、引き続き、そのゲートマスク材53に対して自己整合的に、制御ゲート電極21、ゲート間絶縁膜33、および、浮遊ゲート電極32をエッチングする。これにより、メモリセルゲート電極GE、ドレイン側選択トランジスタSTDのゲート電極GEd、および、ソース側選択トランジスタSTSのゲート電極GEsを同時に形成する。さらに、ゲート加工時のダメージを回復させるための後酸化を行った後、拡散層34,35,36を形成するための不純物をイオン注入する。

10

20

30

20

30

40

50

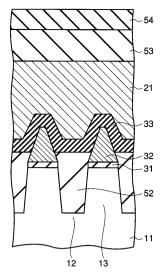

#### [0043]

次に、たとえば図9に示すように、絶縁膜37,38を形成するためのシリコン酸化膜54を形成する。このシリコン酸化膜54は、メモリセルゲート電極GEの相互間、メモリセルゲート電極GEとドレイン側選択トランジスタSTDのゲート電極GEdとの間、および、メモリセルゲート電極GEとソース側選択トランジスタSTSのゲート電極GEsの間を完全に埋め込み、かつ、ドレイン側選択トランジスタSTDのゲート電極GEdの相互間およびソース側選択トランジスタSTSのゲート電極GEsの相互間は完全に埋め込まない膜厚で形成する。

### [0044]

次に、シリコン酸化膜54をエッチバックし、メモリセルMCのメモリセルゲート電極GEの相互間、メモリセルゲート電極GEとドレイン側選択トランジスタSTDのゲート電極GEdとの間、および、メモリセルゲート電極GEとソース側選択トランジスタSTSのゲート電極GEsとの間に、それぞれ、絶縁膜37を形成する。また、ドレイン側選択トランジスタSTDのゲート電極GEdの相互間およびソース側選択トランジスタSTSのゲート電極GEsの相互間には、それぞれ、シリコン酸化膜54が側壁として残る形で絶縁膜38を形成する。

### [0045]

次に、シリコン窒化膜からなる絶縁膜39とBPSG膜からなる絶縁膜40を順に堆積し、ドレイン側選択トランジスタSTDのゲート電極GEdの相互間およびソース側選択トランジスタSTSのゲート電極GEsの相互間を埋め込んだ後、たとえば図10に示すように、制御ゲート電極21の上面にコバルトを堆積し、熱工程を加えることにより、多結晶シリコンとコバルトとを反応させることによって、シリコン層21-1上にシリサイド層21-2を形成する。この結果、制御ゲート電極21は、シリコン層21-1とシリサイド層21-2との積層構造となる。こうして、メモリセルMCのメモリセルゲート電極GEが完成される。

### [0046]

次に、層間絶縁膜41を堆積し、ビット線コンタクト拡散層35とソース線コンタクト拡散層36とにコンタクトを取るためのコンタクト孔を開口した後、コンタクト孔内にアルミニウムまたはタングステンなどの金属あるいは低抵抗の半導体を埋め込んで、ビット線コンタクト電極24およびソース線コンタクト電極27を形成する。

#### [0047]

この後、層間絶縁膜41上に金属配線層(第1の配線層)を形成することによって、ビット線接続部25およびソース線SLを形成する。さらに、配線間絶縁膜42を堆積し、ビット線接続部25にコンタクトを取るためのコンタクト孔を開口した後、コンタクト孔内にアルミニウムまたはタングステンなどの金属あるいは低抵抗の半導体を埋め込んで、配線間コンタクト26を形成す。そして、配線間絶縁膜42上に、配線間コンタクト26につながるビット線BLを形成することによって、たとえば図3に示したような断面形状を有する浮遊ゲート電極32を備えたNAND型の不揮発性半導体記憶装置が完成する。

## [0048]

上記したように、ゲート間絶縁膜を介して、浮遊ゲート電極と制御ゲート電極とを積層してなる構造のメモリセルゲート電極を有するNAND型の不揮発性半導体記憶装置において、浮遊ゲート電極を、その上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短く、かつ、少なくともゲート間絶縁膜に接する側面が1つの平面または1つの上に凸形状の曲面または1つの下に凸形状の曲面を有してなる構造とすることにより、たとえ対向する浮遊ゲート電極間の最小距離がゲート間絶縁膜の膜厚の2倍よりも小さいメモリセルの場合にも、浮遊ゲート電極間に制御ゲート電極の一部を十分に埋め込むことが可能となる結果、メモリセルのカップリング比の低化を防止でき、メモリセルの特性を向上させることが可能となる。

#### [0049]

特に、ゲート間絶縁膜の垂直方向の膜厚(最大膜厚)を、その最下面から最上面までの

20

30

40

50

垂直方向の距離よりも小さくすることにより、浮遊ゲート電極の加工時の工程数を増加させることなく、しかも、ゲート間絶縁膜のエッチングを容易なものとすることができる。

#### [0050]

また、互いに対向する浮遊ゲート電極間の最小間隔を、ゲート間絶縁膜の膜厚を 2 倍に した値と制御ゲート電極が空乏化する距離とを足し合わせた値よりも小さくすることによって、互いに対向する浮遊ゲート電極間が最小となる部分に対しても、制御ゲート電極の 一部をより確実に埋め込むことが可能となる。

### [0051]

なお、図3に示した構造の浮遊ゲート電極32を形成する場合を例に説明したが、これに限らず、図4に示した構造の浮遊ゲート電極32Aを形成する場合および図5に示した構造の浮遊ゲート電極32Bを形成する場合についても同様である。

## [0052]

#### 「第2の実施形態]

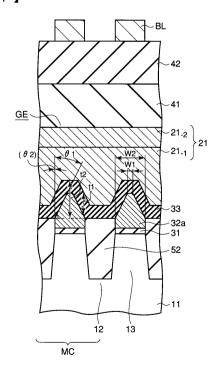

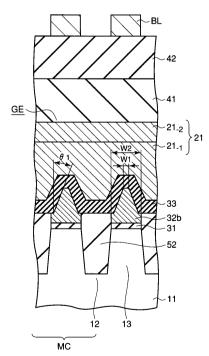

図11は、本発明の第2の実施形態にしたがった、不揮発性半導体記憶装置の基本構成を示すものである。ここでは、第1の実施形態に示したNAND型の不揮発性半導体記憶装置(図1参照)の、III・III線に沿う断面に対応する部分の構造を示している。なお、第1の実施形態のNAND型の不揮発性半導体記憶装置と同一部分には同一符号を付して、詳しい説明は割愛する。

### [0053]

図11に示すように、本実施形態の場合、上部のチャネル幅方向の幅W1が下部のチャネル幅方向の幅W2よりも短く、かつ、少なくともゲート間絶縁膜33に接する側面が1つの平面を有してなる構造の浮遊ゲート電極32aにおいて、さらに、その側面のうち、ゲート間絶縁膜33に接する部分と垂直方向とのなす角 1が、素子分離領域12の素子分離絶縁膜52に接する部分(第2の絶縁膜に接しない部分)と垂直方向とのなす角 2よりも大きくなるように形成されている(この例の場合、 2はほぼ0度)。すなわち、浮遊ゲート電極32aは、その側面に、ゲート間絶縁膜33に接する部分(第1の平面)と素子分離領域12の素子分離絶縁膜52に接する部分(第2の平面)とを有してなる構造とされている。

## [0054]

このような構造とした場合にも、制御ゲート電極 2 1 の一部を、互いに対向する浮遊ゲート電極 3 2 a 間に十分に埋め込むことが可能となる結果、メモリセルMCのカップリング比の低下を防止でき、メモリセルMCの特性が劣化するのを防止することが可能となるものである。

#### [0055]

なお、本実施形態の構成とした場合にも、互いに対向する浮遊ゲート電極32a間に埋め込まれている制御ゲート電極21の幅が、制御ゲート電極21がゲート間絶縁膜33との界面において空乏化する距離の2倍よりも大きくなるようにする必要があるが、制御ゲート電極21がシリコン層21-1とシリサイド層21-2との積層膜でなく、完全にシリサイド化されている場合または金属で形成されている場合には、互いに対向する浮遊ゲート電極32a間に埋め込まれる制御ゲート電極21の幅は、制御ゲート電極21がゲート間絶縁膜33との界面において空乏化する距離の2倍よりも大きくする必要はない。

#### [0056]

また、この浮遊ゲート電極 3 2 a の側面のうち、少なくともゲート間絶縁膜 3 3 に接する第 1 の平面を 1 つの面によって構成するようにしているため、浮遊ゲート電極 3 2 a のゲート間絶縁膜 3 3 に接する部分は 1 回のエッチング工程により加工することが可能であり、工程数を増加させることなしに形成することができる。

#### [0057]

なお、浮遊ゲート電極32aの側面のうち、ゲート間絶縁膜33に接する部分および素子分離領域12に接する部分は、上に凸形状の曲面を有して構成するようにしてもよいし、下に凸形状の曲面を有して構成するようにしてもよい。つまり、傾斜角の異なる複数の

面からなる、段差のない形状であれば、工程数を増加させたりすることなく、制御性よく 形成することが可能である。

#### [0058]

このような構造においても、メモリセルゲート電極GEの加工時に、浮遊ゲート電極32aの側面のゲート間絶縁膜33を完全に除去する必要があるため、ゲート間絶縁膜33の加工を容易にするという観点からは、第1の実施形態の場合と同様に、浮遊ゲート電極32aの側面に形成されるゲート間絶縁膜33の垂直方向の膜厚(最大膜厚)t1が、ゲート間絶縁膜33の最下面から最上面までの垂直方向の距離t2よりも小さくなるように形成するのが望ましい。

## [0059]

以下に、図12~図14を参照して、上記した構成のNAND型の不揮発性半導体記憶装置の製造方法について簡単に説明する。各図は、それぞれ図1のIII-III線に沿う断面に対応する部分を示すものである。

## [0060]

まず、たとえば図12に示すように、半導体基板11の表面部にウェル領域およびチャネル領域(いずれも図示していない)を形成した後、全面にゲート絶縁膜31を形成する。次に、ゲート絶縁膜31上に浮遊ゲート電極32aとなる多結晶シリコンを堆積した後、リソグラフィー法により、順次、浮遊ゲート電極32a、ゲート絶縁膜31、および、半導体基板11をエッチングして、半導体基板11の表面部に溝部51を形成する。

### [0061]

次に、たとえば図13に示すように、溝部51内にシリコン酸化膜からなる素子分離絶縁膜52を埋め込んだ後、適当な高さまで素子分離絶縁膜52をエッチバックして、素子分離領域12を形成するとともに、その素子分離領域12によって画定された素子領域13を形成する。このとき、素子分離絶縁膜52のエッチバックを、たとえばCF4:CHF3の比が5:1とされたガスを用いて行うことにより、浮遊ゲート電極32aの側面のうち、ゲート間絶縁膜33に接する部分と垂直方向とのなす角 1が、素子分離領域12に接する部分と垂直方向とのなす角 2よりも大きくなるようにする。

#### [0062]

次に、たとえば図14に示すように、浮遊ゲート電極32a上および素子分離領域12上に、順次、ゲート間絶縁膜(たとえば、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の積層膜)33、多結晶シリコンからなる制御ゲート電極21、および、シリコン窒化膜からなるゲートマスク材53を形成する。

#### [0063]

これ以後、上述した第1の実施形態に示した工程(たとえば、図9~参照)と同様の工程を行うことにより、図11に示した断面構造を有する浮遊ゲート電極32aを備えたNAND型の不揮発性半導体記憶装置が完成する。

#### [0064]

ここで、上記した第2の実施形態にかかる、いくつかの変形例(他の構成例)について 簡単に説明する。

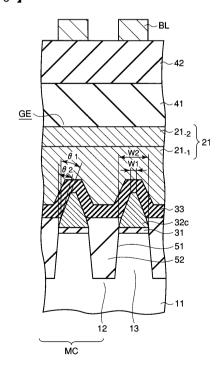

### [0065]

図15は、第2の実施形態にしたがったNAND型の不揮発性半導体記憶装置の、第1の変形例を示すものである。この第1の変形例の場合、浮遊ゲート電極32bの側面のうち、ゲート間絶縁膜33に接する部分(第1の平面)と素子分離領域12に接する部分(第2の平面)との間に段差が設けられている点で、図11に示した構造の浮遊ゲート電極32aと異なっている。

## [0066]

すなわち、この浮遊ゲート電極 3 2 b は、上部のチャネル幅方向の幅W 1 が下部のチャネル幅方向の幅W 2 よりも短く、かつ、少なくともゲート間絶縁膜 3 3 に接する側面が 1 つの平面を有するとともに、その垂直方向とのなす角が 1 ( 1 > 2)となるように形成されたゲート間絶縁膜 3 3 に接する部分と、その垂直方向とのなす角が 2 ( 2 =

10

20

30

40

0)となるように形成された素子分離領域12に接する部分との間に段差が設けられてなる構造とされている。

### [0067]

このような構造は、以下の方法により形成できる。まず、たとえば図13に示したように、溝部51内に埋め込んだ素子分離絶縁膜52をエッチバックして、素子分離領域12を形成するとともに、素子領域13を画定する。その際に、浮遊ゲート電極32bの側面のうち、ゲート間絶縁膜33に接する部分と垂直方向とのなす角 1が、素子分離領域12に接する部分と垂直方向とのなす角 1を維持するように、たとえばホットリン酸を用いたウエットエッチングを行うことにより、浮遊ゲート電極32bの側面のうち、ゲート間絶縁膜33に接する部分と素子分離領域12に接する部分との間に段差を形成する。それ以後は、上述した第1の実施形態に示した工程(たとえば、図8~参照)と同様の工程を行うことにより、図15に示した断面構造を有する浮遊ゲート電極32bを備えたNAND型の不揮発性半導体記憶装置が完成する。

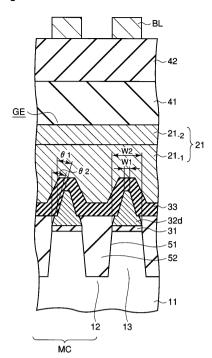

#### [0068]

図16は、第2の実施形態にしたがったNAND型の不揮発性半導体記憶装置の、第2の変形例(他の構成例)を示すものである。この第2の変形例の場合、浮遊ゲート電極32cの側面のうち、素子分離領域12に接する部分(第2の絶縁膜に接しない第2の平面)と垂直方向とのなす角 2が0度よりも大きくなるように形成されている点で、図11に示した構造の浮遊ゲート電極32aと異なっている(ただし、2<1)。

#### [0069]

すなわち、この浮遊ゲート電極32cは、上部のチャネル幅方向の幅W1が下部のチャネル幅方向の幅W2よりも短く、かつ、少なくともゲート間絶縁膜33に接する側面が1つの平面(第1の平面)を有するとともに、その垂直方向とのなす角が 1となるように形成されたゲート間絶縁膜33に接する部分と、その垂直方向とのなす角が 2( 1>2>0)となるように形成された素子分離領域12に接する部分とによって、側面が形成されてなる構造とされている。

#### [0070]

このような構造は、以下の方法により形成できる。まず、たとえば図6に示したように、浮遊ゲート電極32cをエッチングにより加工する際に、浮遊ゲート電極32cの上部のチャネル幅方向の幅W1が下部のチャネル幅方向の幅W2よりも短くなるようにした後、溝部51内にシリコン酸化膜からなる素子分離絶縁膜52を埋め込む。次に、素子分離絶縁膜52を適当な高さまでエッチバックする工程において、たとえば図16に示すように、浮遊ゲート電極32cの側面のうち、ゲート間絶縁膜33に接する部分と垂直方向とのなす角 1が、素子分離領域12に接する部分と垂直方向とのなす角 2よりも大きくなるように形成する。それ以降は、上記した第1の実施形態に示した工程(たとえば、図8~参照)と同様の工程を行うことにより、図16に示した断面構造を有する浮遊ゲート電極32cを備えたNAND型の不揮発性半導体記憶装置が完成する。

#### [0071]

図17は、第2の実施形態にしたがったNAND型の不揮発性半導体記憶装置の、第3の変形例(他の構成例)を示すものである。この第3の変形例の場合、浮遊ゲート電極32dの側面のうち、素子分離領域12に接する部分(第2の平面)と垂直方向とのなす角2が0度より大きく、かつ、ゲート間絶縁膜33に接する部分(第1の平面)と素子分離領域12に接する部分との間に段差が設けられている点で、図11に示した構造の浮遊ゲート電極32aと異なっている。

## [0072]

すなわち、この浮遊ゲート電極 3 2 d は、上部のチャネル幅方向の幅W 1 が下部のチャネル幅方向の幅W 2 よりも短く、かつ、少なくともゲート間絶縁膜 3 3 に接する側面が 1 つの平面を有するとともに、その垂直方向とのなす角が 1 ( 1 > 2)となるように形成されたゲート間絶縁膜 3 3 に接する部分と、その垂直方向とのなす角が 2 ( 1 >

10

20

30

40

20

30

40

50

2 > 0 )となるように形成された素子分離領域12に接する部分との間に段差が設けられてなる構造とされている。

### [0073]

このような構造は、以下の方法により形成できる。まず、たとえば図6に示したように、浮遊ゲート電極32dをエッチングにより加工する際に、浮遊ゲート電極32dの上部のチャネル幅方向の幅W1が下部のチャネル幅方向の幅W2よりも短くなるようにした後、溝部51内にシリコン酸化膜からなる素子分離絶縁膜52を埋め込む。次に、素子分離に、浮遊ゲート電極32dの側面のうち、ゲート間絶縁膜33に接する部分と素子分離領域12に接する部分との間に段差を形成し、かつ、ゲート間絶縁膜33に接する部分と垂直方向とのなす角 1が、素子分離領域12に接する部分と垂直方向とのなす角 2よりも大きくなるように形成する。それ以降は、上記した第1の実施形態に示した工程(たとえば、図8~参照)と同様の工程を行うことにより、図17に示した断面構造を有する浮遊ゲート電極32dを備えたNAND型の不揮発性半導体記憶装置が完成する。

#### [0074]

上記したように、図15~図17に示したいずれの構造の浮遊ゲート電極32b,32c,32dにおいても、図11に示した構造の浮遊ゲート電極32aと同様の効果を得ることができる。すなわち、上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短く、かつ、側面のうち、少なくともゲート間絶縁膜に接する側面を1つの平面により構成してなる構造の浮遊ゲート電極においては、ゲート間絶縁膜に接する部分と垂直方向とのなす角(0度)よりも大きくなるように形成した場合、または、ゲート間絶縁膜に接する部分と素子分離領域に接するお分との間に段差を形成するようにした場合にも、制御ゲート電極の一部を、互いに対向する浮遊ゲート電極間に十分に埋め込むことが可能となる結果、浮遊ゲート電極の加工の工程数を増加させることなく、メモリセルのカップリング比の低下を抑制でき、メモリセルの特性を向上させることが可能となる。

## [0075]

### 「第3の実施形態]

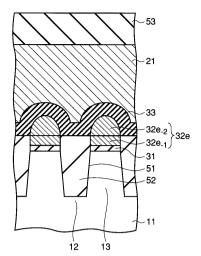

図18は、本発明の第3の実施形態にしたがった、不揮発性半導体記憶装置の基本構成を示すものである。ここでは、第1の実施形態に示したNAND型の不揮発性半導体記憶装置(図1参照)の、III・III線に沿う断面に対応する部分の構造を示している。なお、第1の実施形態のNAND型の不揮発性半導体記憶装置と同一部分には同一符号を付して、詳しい説明は割愛する。

## [0076]

図18に示すように、本実施形態の場合、上部のチャネル幅方向の幅W1が下部のチャネル幅方向の幅W2よりも短く、かつ、少なくともゲート間絶縁膜33に接する側面が1つの曲面を有してなる構造の浮遊ゲート電極32eを備えて構成されている。すなわち、浮遊ゲート電極32eは、その側面に、素子分離領域12の素子分離絶縁膜52に接する部分32e-1とゲート間絶縁膜33に接する部分32e-2とを有し、そのゲート間絶縁膜33に接する部分32e-2(浮遊ゲート電極32eの上部側)が、上に凸形状を有するような外側に湾曲した曲面を備えてなる構成とされている。

#### [0077]

このような構造とした場合にも、制御ゲート電極 2 1 の一部を、互いに対向する浮遊ゲート電極 3 2 e 間に十分に埋め込むことが可能となる結果、メモリセルMCのカップリング比の低下を防止でき、メモリセルMCの特性が劣化するのを防止することが可能となるものである。

#### [0078]

なお、本実施形態の構成とした場合にも、互いに対向する浮遊ゲート電極32e間に埋め込まれている制御ゲート電極21の幅が、制御ゲート電極21がゲート間絶縁膜33との界面において空乏化する距離の2倍よりも大きくなるようにする必要があるが、制御ゲ

20

30

40

50

ート電極 2 1 がシリコン層 2 1 -1とシリサイド層 2 1 -2との積層膜でなく、完全にシリサイド化されている場合または金属で形成されている場合には、互いに対向する浮遊ゲート電極 3 2 e 間に埋め込まれる制御ゲート電極 2 1 の幅は、制御ゲート電極 2 1 がゲート間絶縁膜 3 3 との界面において空乏化する距離の 2 倍よりも大きくする必要はない。

## [0079]

このような構造においても、メモリセルゲート電極GEの加工時に、浮遊ゲート電極32 eの側面のゲート間絶縁膜33を完全に除去する必要があるため、ゲート間絶縁膜33の加工を容易にするという観点からは、第1の実施形態の場合と同様に、浮遊ゲート電極32 eの側面に形成されるゲート間絶縁膜33の垂直方向の膜厚(最大膜厚) t 1 が、ゲート間絶縁膜33の最下面から最上面までの垂直方向の距離 t 2 よりも小さくなるように形成するのが望ましい。

[0800]

以下に、図19~図22を参照して、上記した構成のNAND型の不揮発性半導体記憶装置の製造方法について簡単に説明する。各図は、それぞれ図1のIII-III線に沿う断面に対応する部分を示すものである。

[0081]

まず、たとえば図19に示すように、半導体基板11の表面部にウェル領域およびチャネル領域(いずれも図示していない)を形成した後、全面にゲート絶縁膜31を形成する。次に、ゲート絶縁膜31上に浮遊ゲート電極32eとなる多結晶シリコンを堆積した後、リソグラフィー法により、順次、下部側の浮遊ゲート電極32e-1、ゲート絶縁膜31、および、半導体基板11をエッチングして、半導体基板11の表面部に溝部51を形成する。

[0082]

次に、たとえば図20に示すように、溝部51内にシリコン酸化膜からなる素子分離絶縁膜52を埋め込んだ後、浮遊ゲート電極32e-1の上面の高さまで素子分離絶縁膜52をエッチバックして、素子分離領域12を形成するとともに、その素子分離領域12によって画定された素子領域13を形成する。この際、CMP(化学機械研磨)法を用いて、表面を平坦化してもよい。

[0083]

次に、たとえば図21に示すように、浮遊ゲート電極32e-1上に選択エピタキシャル成長などを用いてシリコンを成長させ、上に凸形状の曲面を有する上部側の浮遊ゲート電極32e-2を形成する。この結果、浮遊ゲート電極32eは、下部側の浮遊ゲート電極32e-2とからなる積層構造となる。

[0084]

次に、たとえば図22に示すように、浮遊ゲート電極32e上および素子分離領域12上に、順次、ゲート間絶縁膜(たとえば、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の積層膜)33、多結晶シリコンからなる制御ゲート電極21、シリコン窒化膜からなるゲートマスク材53を形成する。

[0085]

これ以後、上述した第1の実施形態に示した工程(たとえば、図9~参照)と同様の工程を行うことにより、図18に示した断面構造を有する浮遊ゲート電極32eを備えたNAND型の不揮発性半導体記憶装置が完成する。

[0086]

上記したように、ゲート間絶縁膜を介して、浮遊ゲート電極と制御ゲート電極とを積層してなる構造のメモリセルゲート電極を有するNAND型の不揮発性半導体記憶装置において、浮遊ゲート電極を、その上部のチャネル幅方向の幅が下部のチャネル幅方向の幅よりも短く、かつ、少なくともゲート間絶縁膜に接する側面は1つの上に凸形状の曲面を有し、ゲート間絶縁膜に接しない側面は平面を有してなる構造とすることにより、たとえ対向する浮遊ゲート電極間の最小距離がゲート間絶縁膜の膜厚の2倍よりも小さいメモリセルの場合にも、浮遊ゲート電極間に制御ゲート電極の一部を十分に埋め込むことが可能と

なる結果、メモリセルのカップリング比の低化を防止でき、メモリセルの特性を向上させることが可能となる。

[0087]

特に、浮遊ゲート電極の側面に形成されるゲート間絶縁膜の垂直方向の膜厚(最大膜厚)を、ゲート間絶縁膜の最下面から最上面までの垂直方向の距離よりも小さくすることによって、ゲート間絶縁膜のエッチングを容易なものとすることができる。

[0088]

なお、上述した各実施形態においては、いずれもNAND型の不揮発性半導体記憶装置を例に説明したが、これに限らず、たとえばNOR型およびAND型など、浮遊ゲート電極を備える全ての不揮発性半導体記憶装置に適用できる。

[0089]

その他、本願発明は、上記(各)実施形態に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で種々に変形することが可能である。さらに、上記(各)実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の発明が抽出され得る。たとえば、(各)実施形態に示される全構成要件からいくつかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題(の少なくとも1つ)が解決でき、発明の効果の欄で述べられている効果(の少なくとも1つ)が得られる場合には、その構成要件が削除された構成が発明として抽出され得る

【図面の簡単な説明】

[0090]

【図1】本発明の第1の実施形態にしたがった、不揮発性半導体記憶装置(NAND型)の構成例を示す平面図。

- 【図2】図1に示した不揮発性半導体記憶装置のⅡ-Ⅱ線に沿う断面図。

- 【図3】図1に示した不揮発性半導体記憶装置のIII-III線に沿う断面図。

- 【図4】図1に示した不揮発性半導体記憶装置の他の構成例を示す断面図。

- 【図5】図1に示した不揮発性半導体記憶装置のさらに別の構成例を示す断面図。

- 【図 6 】図 1 に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程断面図。

- 【図7】図1に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程断面図。

- 【図8】図1に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程断面図。

- 【図9】図1に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程断面図。

- 【図10】図1に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程断 面図

- 【図11】本発明の第2の実施形態にしたがった、不揮発性半導体記憶装置の構成例を示す断面図。

- 【図12】図11に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程 40 断面図。

- 【図13】図11に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程 断面図。

- 【図14】図11に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程 断面図。

- 【図15】図11に示した不揮発性半導体記憶装置の、第1の変形例を示す断面図。

- 【図16】図11に示した不揮発性半導体記憶装置の、第2の変形例を示す断面図。

- 【図17】図11に示した不揮発性半導体記憶装置の、第3の変形例を示す断面図。

- 【図18】本発明の第3の実施形態にしたがった、不揮発性半導体記憶装置の構成例を示す断面図。

10

20

30

【図19】図18に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程 断面図。

【図 2 0 】図 1 8 に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程 断面図。

【図21】図18に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程 断面図。

【図22】図18に示した不揮発性半導体記憶装置の製造方法を説明するために示す工程 断面図。

## 【符号の説明】

## [0091]

1 1 ... 半導体基板、 1 2 ... 素子分離領域、 1 3 ... 素子領域、 2 1 ... 制御ゲート電極、 3 1 ... ゲート絶縁膜、 3 2 , 3 2 A , 3 2 B , 3 2 a , 3 2 b , 3 2 c , 3 2 d , 3 2 e ... 浮遊ゲート電極、 3 3 ... ゲート間絶縁膜、 G E ... メモリセルゲート電極。

## 【図1】

STD 22

25 24

26

STD 22

MC 21

CU III III CC

STS 23

STS 27

SL

MCA 11

## 【図2】

【図3】

図 3

【図4】

図 4

【図5】

図 5

【図6】

図 6

【図7】

【図8】

図 8

【図9】

図 9

【図10】

図 10

【図11】

【図12】

図 12

【図13】

図 13

【図14】

図 14

【図15】

図 15

【図16】

【図17】

図 17

【図18】

図 18

【図19】

図 19

【図21】

図 21

【図20】

図 20

# 【図22】

## フロントページの続き

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 八重樫 利武

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

審査官 井原 純

(56)参考文献 特開2004-022819(JP,A)

特開平11-163304(JP,A)

特開2003-289114(JP,A)

特開2005-277035(JP,A)

特開2007-157893(JP,A)

特開2006-303308(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792